## 10BASE-T/100BASE-TX Physical Layer Transceiver

#### **Highlights**

- Single-Chip Ethernet Physical Layer Transceiver (PHY)

- Quiet-Wire<sup>®</sup> technology to reduce line emissions and enhance immunity

- · Ultra-Deep Sleep standby mode

- · AEC-Q100 Grade 2 Automotive Qualified

#### **Target Applications**

- · Industrial Control

- · Vehicle On-Board Diagnostics (OBD)

- · Automotive Gateways

- · Camera and Sensor Networking

- Infotainment

#### **Key Benefits**

- · Quiet-Wire Programmable EMI Filter

- RMII Interface with MDC/MDIO Management Interface for Register Configuration

- On-Chip Termination Resistors for Differential Pairs

- LinkMD®+ Receive Signal Quality Indicator

- Fast Start-Up and Link

- Ultra Deep Sleep Standby Mode; CPU or Signal Detect Activated

- · Loopback Modes for Diagnostics

- · Programmable Interrupt Output

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### **Table of Contents**

| 1.0 Introduction                                               | 4  |

|----------------------------------------------------------------|----|

| 2.0 Pin Description and Configuration                          | ŗ. |

| 3.0 Functional Description                                     | 9  |

| 4.0 Negisiei wap                                               |    |

| 5.0 Operational Characteristics 6.0 Electrical Characteristics | 38 |

| 6.0 Electrical Characteristics                                 | 39 |

| 7.0 Timing Diagrams                                            | 42 |

| 8.0 Reset Circuit                                              | 46 |

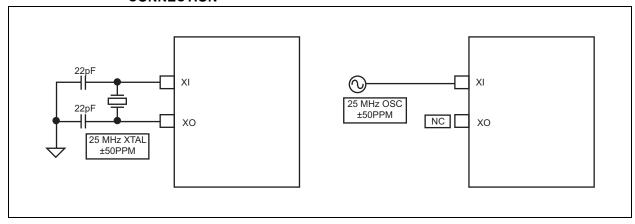

| 9.0 Reference Clock Connection and Selection - KSZ8061RNB      |    |

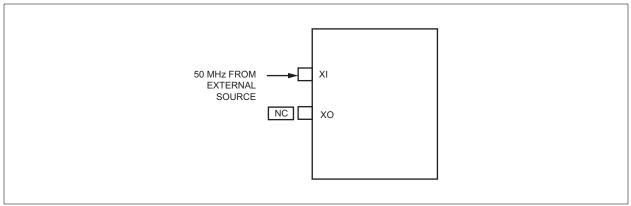

| 10.0 Reference Clock Connection - KSZ8061RND                   | 48 |

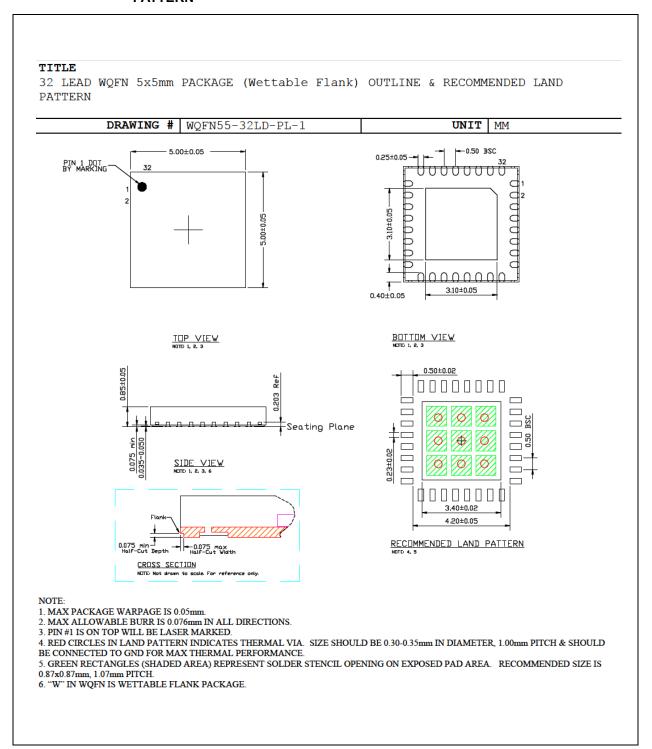

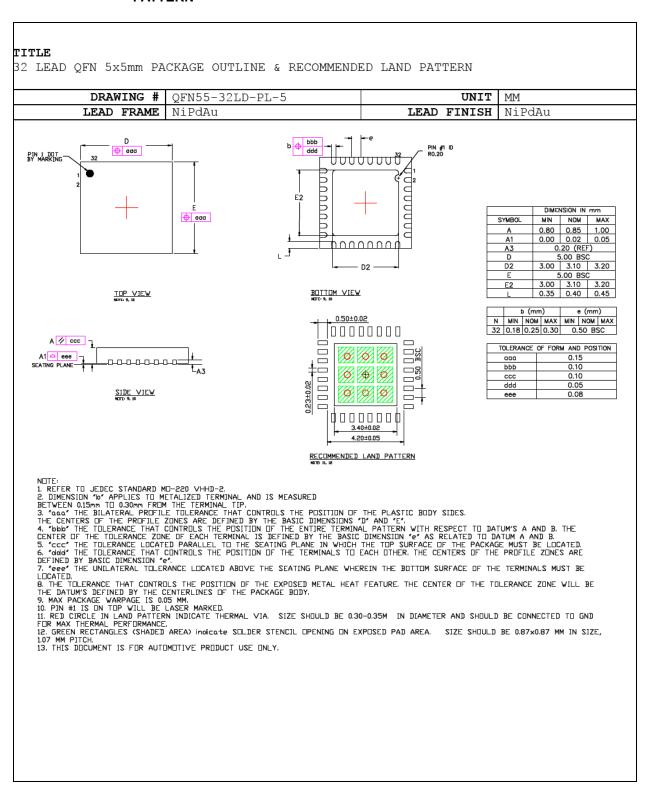

| 11.0 Package Outlines                                          | 49 |

| Appendix A. Data Sheet Revision History                        | 51 |

| The Microchip Web Site                                         | 52 |

| Customer Change Notification Service                           | 52 |

| Customer Support                                               | 52 |

| Product Identification System                                  | 53 |

#### 1.0 INTRODUCTION

#### 1.1 General Description

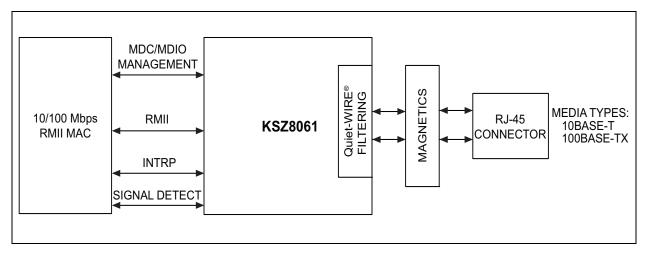

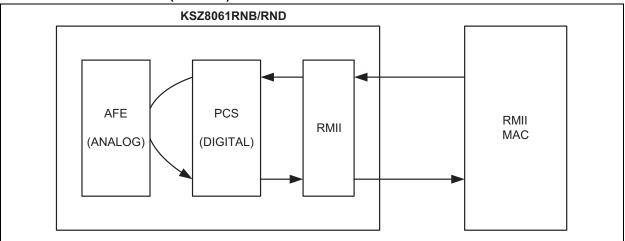

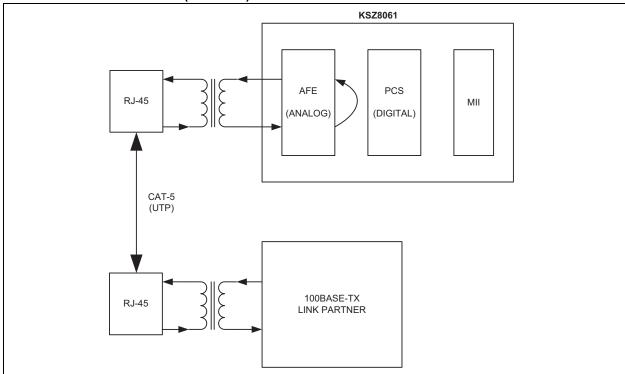

The KSZ8061RNB/RND is a single-chip 10BASE-T/100BASE-TX Ethernet physical layer transceiver for transmission and reception of data over an unshielded twisted pair (UTP) cable.

The KSZ8061RNB/RND features Quiet-Wire<sup>®</sup> internal filtering to reduce line emissions. It is ideal for applications, such as automotive or industrial networks, where stringent radiated emission limits must be met. Quiet-Wire can utilize low-cost unshielded cable, where previously only shielded cable solutions were possible. The KSZ8061RNB/RND also features enhanced immunity to environmental EM noise.

The KSZ8061RNB/RND features a Reduced Media Independent Interface (RMII) for direct connection with RMII-compliant Ethernet MAC processors and switches.

The KSZ8061RNB generates a 50-MHz RMII reference clock for use by the connected MAC device. In contrast, the KSZ8061RND receives the 50-MHz RMII reference clock as an input.

The KSZ8061RNB/RND meets Automotive AEC-Q100 and EMC requirements, with an extended temperature range of -40°C to +105°C. It is supplied in 32-pin, 5 mm × 5 mm QFN and WQFN packages.

The KSZ8061MNX and KSZ8061MNG devices have an MII interface and are described in a separate data sheet.

FIGURE 1-1: SYSTEM BLOCK DIAGRAM

#### 2.0 PIN DESCRIPTION AND CONFIGURATION

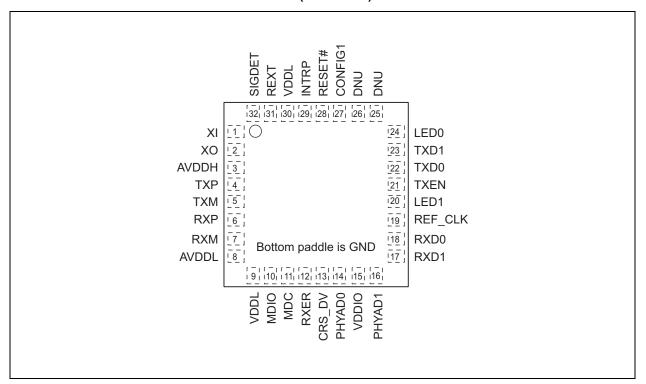

FIGURE 2-1: 32-QFN PIN ASSIGNMENT (TOP VIEW)

TABLE 2-1: SIGNALS

| Pin Number | Name  | Buffer<br>Type Note | Description                                                                                                                                  |

|------------|-------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | ΧI    |                     | KSZ8061RNB: 25-MHz Crystal/Oscillator/External Clock Input. This input references the AVDDH power supply.                                    |

| 1          | λl    | ľ                   | KSZ8061RND: 50-MHz RMII Reference Clock Input. This input references the AVDDH power supply.                                                 |

| 2          | хо    | 0                   | KSZ8061RNB: Crystal feedback for 25-MHz crystal. This pin is a no connect if oscillator or external clock source is used.                    |

|            |       |                     | KSZ8061RND: This pin is unused. Leave it unconnected.                                                                                        |

| 3          | AVDDH | PWR                 | 3.3V Supply for analog TX drivers and XI/XO oscillator circuit.                                                                              |

| 4          | TXP   | I/O                 | Physical transmit or receive signal (+ differential) Transmit when in MDI mode; Receive when in MDI-X mode.                                  |

| 5          | TXM   | I/O                 | Physical transmit or receive signal (– differential) Transmit when in MDI mode; Receive when in MDI-X mode.                                  |

| 6          | RXP   | I/O                 | Physical receive or transmit signal (+ differential) Receive when in MDI mode; Transmit when in MDI-X mode.                                  |

| 7          | RXM   | I/O                 | Physical receive or transmit signal (– differential)<br>Receive when in MDI mode; Transmit when in MDI-X mode.                               |

| 8          | AVDDL | PWR                 | 1.2V (nominal) supply for analog core                                                                                                        |

| 9          | VDDL  | PWR                 | 1.2V (nominal) supply for digital core                                                                                                       |

| 10         | MDIO  | IPU/OPU             | Management Interface (MIIM) Data I/O This pin has a weak pull-up, is open-drain like, and requires an external $1-k\Omega$ pull-up resistor. |

TABLE 2-1: SIGNALS (CONTINUED)

| TABLE 2-1: | SIGNALS (C            | ONTINUEL            | 9)                                                                                                                                                                                                                                                                                                                              |       |                                                                                                                                                                                                         |

|------------|-----------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Name                  | Buffer<br>Type Note | Description                                                                                                                                                                                                                                                                                                                     |       |                                                                                                                                                                                                         |

| 11         | MDC                   | IPU                 | Management Interface (MIIM) Clock Input This clock pin is synchronous to the MDIO data pin.                                                                                                                                                                                                                                     |       |                                                                                                                                                                                                         |

| 12         | RXER / QWF            | IPD/O               | RMII Receive Error Output Config Mode: The pull-up or pull-down value is latched as QWF at the deassertion of reset. See Table 2-2, "Strap-in Options" for details.                                                                                                                                                             |       |                                                                                                                                                                                                         |

| 13         | CRS_DV /<br>CONFIG2   | IPD/O               | RMII Carrier Sense/Receive Data Valid Output Config Mode: The pull-up or pull-down value is latched as CONFIG2 at the deassertion of reset. See Table 2-2, "Strap-in Options" for details.                                                                                                                                      |       |                                                                                                                                                                                                         |

| 14         | PHYAD0                | IPU/O               | No function during normal operation<br>Config Mode: The pull-up or pull-down value is latched as PHYADDR[0]<br>at the deassertion of reset. See Table 2-2, "Strap-in Options" for details.                                                                                                                                      |       |                                                                                                                                                                                                         |

| 15         | VDDIO                 | PWR                 | 3.3V or 2.5V supply for digital I/O                                                                                                                                                                                                                                                                                             |       |                                                                                                                                                                                                         |

| 16         | PHYAD1                | IPD/O               | No function during normal operation Config Mode: The pull-up or pull-down value is latched as PHYADDR[1] at the deassertion of reset. See Table 2-2, "Strap-in Options" for details.                                                                                                                                            |       |                                                                                                                                                                                                         |

| 17         | RXD1 /<br>PHYAD2      | IPD/O               | RMII Receive Data Output[1] (Note 2-2) Config Mode: The pull-up or pull-down value is latched as PHYADDR[2] at the deassertion of reset. See Table 2-2, "Strap-in Options" for details.                                                                                                                                         |       |                                                                                                                                                                                                         |

| 18         | RXD0 /<br>AUTONEG     | IPU/O               | RMII Receive Data Output[0] (Note 2-2) Config Mode: The pull-up or pull-down value is latched as AUTONEG at the deassertion of reset. See Table 2-2, "Strap-in Options" for details.                                                                                                                                            |       |                                                                                                                                                                                                         |

| REF CI     | REF CLK/              | REF_CLK/            | REF_CLK/                                                                                                                                                                                                                                                                                                                        | IPD/O | KSZ8061RNB: RMII 50-MHz Reference Clock Output to the MAC Config Mode: The pull-up or pull-down value is latched as CONFIG0 at the deassertion of reset. See Table 2-2, "Strap-in Options" for details. |

| 19 CONFIGO |                       | IPD/O               | KSZ8061RND: This pin is unused during normal operation. Leave it unconnected except as required for Config Mode.  Config Mode: The pull-up or pull-down value is latched as CONFIG0 at the deassertion of reset. See Table 2-2, "Strap-in Options" for details.                                                                 |       |                                                                                                                                                                                                         |

| 20         | LED1                  | 0                   | LED1 Output Active low. Its function is programmable; by default it indicates link speed.                                                                                                                                                                                                                                       |       |                                                                                                                                                                                                         |

| 21         | TXEN                  | I                   | PMII Transmit Enable Input                                                                                                                                                                                                                                                                                                      |       |                                                                                                                                                                                                         |

| 22         | TXD0                  | I                   | RMII Transmit Data Input[0 (Note 2-3)                                                                                                                                                                                                                                                                                           |       |                                                                                                                                                                                                         |

| 23         | TXD1                  | I                   | RMII Transmit Data Input[1] (Note 2-3)                                                                                                                                                                                                                                                                                          |       |                                                                                                                                                                                                         |

| 24         | LED0                  | IPD/O               | LED0 Output Active low. Its function is programmable; by default it indicates link/activity.                                                                                                                                                                                                                                    |       |                                                                                                                                                                                                         |

| 25         | DNU                   | I                   | Do Not Use. This unused input must be pulled to a logic-low level.                                                                                                                                                                                                                                                              |       |                                                                                                                                                                                                         |

| 26         | DNU                   | I                   | Do Not Use. This unused input should be pulled to a logic-low level.                                                                                                                                                                                                                                                            |       |                                                                                                                                                                                                         |

| 27         | CONFIG1               | IPD/O               | No function during normal operation<br>Config Mode: The pull-up or pull-down value is latched as CONFIG1 at<br>the deassertion of reset. See Table 2-2, "Strap-in Options" for details.                                                                                                                                         |       |                                                                                                                                                                                                         |

| 28         | RESET#                | IPU                 | Chip Reset (active-low)                                                                                                                                                                                                                                                                                                         |       |                                                                                                                                                                                                         |

| 29         | INTRP /<br>NAND_TREE# | IPU/O               | Programmable Interrupt Output (active-low [default] or active-high) This pin has a weak pull-up, is open-drain like, and requires an external 1.0-k $\Omega$ pull-up resistor. Config Mode: The pull-up or pull-down value is latched as NAND_Tree# at the deassertion of reset. See Table 2-2, "Strap-in Options" for details. |       |                                                                                                                                                                                                         |

| 30         | VDDL                  | PWR                 | 1.2V (nominal) supply for digital (and analog)                                                                                                                                                                                                                                                                                  |       |                                                                                                                                                                                                         |

|            |                       |                     |                                                                                                                                                                                                                                                                                                                                 |       |                                                                                                                                                                                                         |

#### TABLE 2-1: SIGNALS (CONTINUED)

| Pin Number       | Name   | Buffer<br>Type Note | Description                                                                                  |

|------------------|--------|---------------------|----------------------------------------------------------------------------------------------|

| 31               | REXT   | 1                   | Set PHY transmit output current. Connect a $6.04\Omega$ 1% resistor from this pin to ground. |

| 32               | SIGDET | 0                   | Signal Detect, active-high                                                                   |

| Bottom<br>Paddle | GND    | GND                 | Ground. Bottom paddle.                                                                       |

Note 2-1 Pwr = Power supply

Gnd = Ground

I = Input

O = Output

I/O = Bi-directional

Ipu = Input with internal pull-up (see Electrical Characteristics for value)

Ipd = Input with internal pull-down (see Electrical Characteristics for value)

Ipu/O = Input with internal pull-up (see Electrical Characteristics for value) during power-up or reset; output pin otherwise.

Ipd/O = Input with internal pull-down (see Electrical Characteristics for value) during power-up or reset; output pin otherwise.

Ipu/Opu = Input and output with internal pull-up (see Electrical Characteristics for value)

Note 2-2 RMII Mode: The RXD[3:0] bits are synchronous with RXC. When RXDV is asserted, RXD[3:0] presents valid data to the MAC device.

Note 2-3 RMII Mode: The TXD[3:0] bits are synchronous with TXC. When TXEN is asserted, TXD[3:0] accepts valid data from the MAC device.

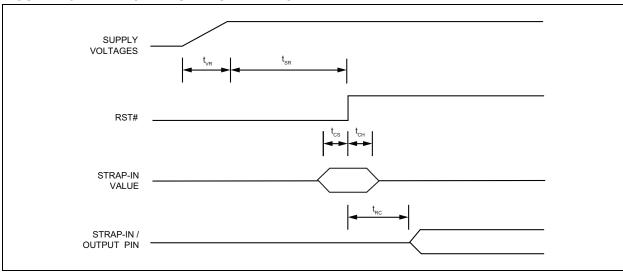

The strap-in pins are latched at the deassertion of reset. In some systems, the MAC RMII receive input pins may drive high or low during power-up or reset, and consequently cause the PHY strap-in pins on the RMII signals to be latched to the unintended high or low states. In this case, external pull-up or pull-down resistors (4.7 k $\Omega$ ) should be added on these PHY strap-in pins to ensure the intended values are strapped in correctly.

TABLE 2-2: STRAP-IN OPTIONS

| Pin<br>Number | Name                 | Buffer<br>Type<br>Note 2-4 | Description                                                                                                                                                                                  |                                                                        |                           |                        |

|---------------|----------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------|------------------------|

| 17            | RXD1/PHYAD2          | IPD/O                      | The PHY Address                                                                                                                                                                              | The PHY Address is latched at the deassertion of reset and is configu- |                           |                        |

| 16            | PHYAD1               | IPD/O                      | rable to any value The default PHY                                                                                                                                                           |                                                                        |                           |                        |

| 14            | PHYAD0               | IPU/O                      |                                                                                                                                                                                              | [4:3] are set to 00 by defaul                                          | t.                        |                        |

| 13            | CRS_DV/              | IPD/O                      | The CONFIG[2:0]                                                                                                                                                                              | strap-in pins are latched at                                           | the deassertion of reset. |                        |

| 13            | CONFIG2              | II D/O                     | 000                                                                                                                                                                                          | Reserved                                                               | - not used                |                        |

|               |                      |                            | 001                                                                                                                                                                                          | RMII normal mode                                                       | Auto MDI/MDI-X disabled   |                        |

| 27            | CONFIG1              | IPD/O                      | 010 - 100                                                                                                                                                                                    | Reserved                                                               | - not used                |                        |

|               |                      |                            | 101                                                                                                                                                                                          | RMII Back-to-Back                                                      | Auto MDI/MDI-X enabled    |                        |

| 19            | REF_CLK/CON-         | IPD/O                      | 110                                                                                                                                                                                          | Reserved                                                               | - not used                |                        |

| 19            | FIG0                 | FIG0                       | IPD/O                                                                                                                                                                                        | 111                                                                    | RMII normal mode          | Auto MDI/MDI-X enabled |

| 18            | RXD0/<br>AUTONEG     | IPU/O                      | Auto-Negotiation Disable Pull-up (default) = Disable Auto-Negotiation Pull-down = Enable Auto-Negotiation At the deassertion of reset, this pin value is latched into register 0h, bit [12]. |                                                                        |                           |                        |

| 29            | INTRP/<br>NAND_TREE# | IPU/O                      | NAND Tree Mode Pull-up (default) = Disable NAND Tree (normal operation) Pull-down = Enable NAND Tree At the deassertion of reset, this pin value is latched by the chip.                     |                                                                        |                           |                        |

| 12            | RXER/QWF             | IPD/O                      | Quiet-Wire Filtering Disable Pull-up = Disable Quiet-Wire Filtering Pull-down (default) = Enable Quiet-Wire Filtering At the deassertion of reset, this pin value is latched by the chip.    |                                                                        |                           |                        |

Note 2-4 Ipu/O = Input with internal pull-up during power-up or reset; output pin otherwise. (See the Electrical Characteristics section for each value.) Ipd/O = Input with internal pull-down (see the Electrical Characteristics section for each value during power-up/reset; output pin otherwise.

#### 3.0 FUNCTIONAL DESCRIPTION

The KSZ8061RNB/RND is an integrated Fast Ethernet transceiver that features Quiet-Wire internal filtering to reduce line emissions. When Quiet-Wire filtering is disabled, it is fully compliant with the IEEE 802.3 specification. The KSZ8061RNB/RND also has a high noise immunity.

On the copper media side, the KSZ8061RNB/RND supports 10BASE-T and 100BASE-TX for transmission and reception of data over a standard CAT-5 or a similar unshielded twisted pair (UTP) cable, and HP Auto MDI/MDI-X for reliable detection of and correction for straight-through and crossover cables.

On the MAC processor side, the KSZ8061RNB/RND offers the Reduced Media Independent Interface (RMII) for direct connection with RMII-compliant Ethernet MAC processors and switches.

The RMII management bus gives the MAC processor complete access to the KSZ8061RNB/RND control and status registers. Additionally, an interrupt pin eliminates the need for the processor to poll for PHY status change.

Auto-negotiation and Auto MDI/MDIX can be disabled at power-on to significantly reduce initial time to link up.

A signal detect pin (SIGDET) is available to indicate when the link partner is inactive. An option is available for the KSZ8061RNB/RND to automatically enter Ultra-Deep Sleep mode when SIGDET is deasserted. Ultra-Deep Sleep mode may also be entered by command of the MAC processor. Additional low power modes are available.

#### 3.1 10BASE-T/100BASE-TX Transceiver

#### 3.1.1 100BASE-TX TRANSMIT

The 100BASE-TX transmit function performs parallel-to-serial conversion, 4B/5B encoding, scrambling, NRZ-to-NRZI conversion, and MLT3 encoding and transmission.

The circuitry starts with a parallel-to-serial conversion, which converts the RMII data from the MAC into a 125-MHz serial bit stream. The data and control stream is then converted into 4B/5B coding and followed by a scrambler. The serialized data is further converted from NRZ-to-NRZI format, and then transmitted in MLT3 current output. The output current is set by a precision external resistor on REXT for the 1:1 transformer ratio.

The output signal has a typical rise or fall time of 4 ns and complies with the ANSITP-PMD standard regarding amplitude balance, overshoot, and timing jitter. The wave-shaped 10BASE-T output is also incorporated into the 100BASE-TX transmitter.

#### 3.1.2 100BASE-TX RECEIVE

The 100BASE-TX receiver function performs adaptive equalization, DC restoration, MLT3-to-NRZI conversion, data and clock recovery, NRZI-to-NRZ conversion, descrambling, 4B/5B decoding, and serial-to-parallel conversion.

The receiving side starts with the equalization filter to compensate for inter-symbol interference (ISI) over the twisted pair cable. Because the amplitude loss and phase distortion is a function of the cable length, the equalizer must adjust its characteristics to optimize performance. In this design, the variable equalizer makes an initial estimation based on comparisons of incoming signal strength against some known cable characteristics, and then tunes itself for optimization. This is an ongoing process and self-adjusts against environmental changes, such as temperature variations.

Next, the equalized signal goes through a DC restoration and data conversion block. The DC restoration circuit is used to compensate for the effect of baseline wander and to improve the dynamic range. The differential data conversion circuit converts the MLT3 format back to NRZI. The slicing threshold is also adaptive.

The clock recovery circuit extracts the 125-MHz clock from the edges of the NRZI signal. This recovered clock is then used to convert the NRZI signal into the NRZ format. This signal is sent through the descrambler followed by the 4B/5B decoder. Finally, the NRZ serial data is converted to the RMII format and provided as the input data to the MAC.

#### 3.1.3 SCRAMBLER/DE-SCRAMBLER (100BASE-TX ONLY)

The scrambler is used to spread the power spectrum of the transmitted signal to reduce EMI and baseline wander. The descrambler is needed to recover the scrambled signal.

#### 3.1.4 10BASE-T TRANSMIT

The 10BASE-T drivers are incorporated with the 100BASE-TX drivers to allow for transmission using the same magnetic. The drivers perform internal wave-shaping and pre-emphasis, then output 10BASE-T signals with a typical amplitude of 2.5V peak. The 10BASE-T signals have harmonic contents that are at least 27 dB below the fundamental frequency when driven by an all-ones Manchester-encoded signal.

#### 3.1.5 10BASE-T RECEIVE

On the receive side, input buffer and level detecting squelch circuits are employed. A differential input receiver circuit and a PLL performs the decoding function. The Manchester-encoded data stream is separated into clock signal and NRZ data. A squelch circuit rejects signals with levels less than 400 mV or with short pulse widths to prevent noise at the RXP and RXM inputs from falsely triggering the decoder. When the input exceeds the squelch limit, the PLL locks onto the incoming signal and the KSZ8061RNB/RND decodes a data frame. The receive clock is kept active during idle periods in between data reception.

#### 3.1.6 PLL CLOCK SYNTHESIZER

The KSZ8061RNB/RND generates all internal clocks and all external clocks for system timing from the clock received at the XI pin. For the KSZ8061RNB, this is an external 25-MHz crystal, oscillator, or reference clock. For the KSZ8061RND, this is the externally supplied RMII 50-MHz reference clock.

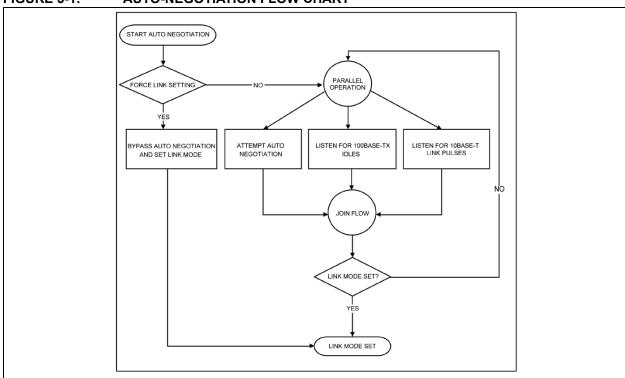

#### 3.1.7 AUTO-NEGOTIATION

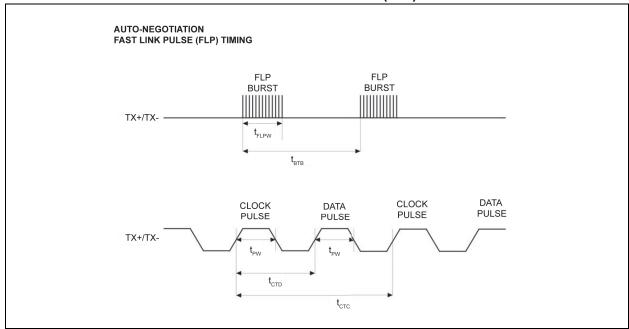

The KSZ8061RNB/RND conforms to the auto-negotiation protocol, defined in Clause 28 of the IEEE 802.3 Specification.

Auto-negotiation allows unshielded twisted pair (UTP) link partners to select the highest common mode of operation.

During auto-negotiation, link partners advertise capabilities across the UTP link to each other, and then compare their own capabilities with those they received from their link partners. The highest speed and duplex setting that is common to the two link partners is selected as the mode of operation.

The following list shows the speed and duplex operation mode from highest to lowest priority:

- Priority 1: 100BASE-TX, full-duplex

- · Priority 2: 100BASE-TX, half-duplex

- · Priority 3: 10BASE-T, full-duplex

- Priority 4: 10BASE-T, half-duplex

If the KSZ8061RNB/RND is using auto-negotiation, but its link partner is not, then the KSZ8061RNB/RND sets its operating speed by observing the signal at its receiver. This is known as parallel detection, and allows the KSZ8061RNB/RND to establish a link by listening for a fixed signal protocol in the absence of auto-negotiation advertisement protocol. Duplex is set by register 0h, bit [8] because the KSZ8061RNB/RND cannot determine duplex by parallel detection.

If auto-negotiation is disabled, the speed is set by register 0h, bit [13], and the duplex is set by register 0h, bit [8]. The default is 100BASE-TX, full-duplex.

Auto-negotiation is enabled or disabled by hardware pin strapping (AUTONEG) and by software (register 0h, bit [12]). By default, auto-negotiation is disabled after power-up or hardware reset, but it may be enabled by pulling the RXD0 pin low at that time. Afterwards, auto-negotiation can be enabled or disabled by register 0h, bit [12].

When the link is 10BASE-T or the link partner is using auto-negotiation and the Ultra-Deep Sleep mode is used, then the Signal Detect assertion timing delay bit, register 14h bit [1], must be set.

The auto-negotiation link-up process is shown in Figure 3-1.

#### FIGURE 3-1: AUTO-NEGOTIATION FLOW CHART

### 3.2 Quiet-Wire<sup>®</sup> Filtering

Quiet-Wire is a feature to enhance 100BASE-TX EMC performance by reducing both conducted and radiated emissions from the TXP/M signal pair. It can be used either to reduce absolute emissions or to enable replacement of shielded cable with unshielded cable, all while maintaining interoperability with standard 100BASE-TX devices.

Quiet-Wire filtering is implemented internally, with no additional external components required. It is enabled or disabled at power-up and reset by a strapping option on the RXER pin. Once the KSZ8061 is powered up, Quiet-Wire filtering can be disabled by writing to register 16h, bit [12]. Note that Quiet-Wire cannot be enabled via this register bit.

The default setting for Quiet-Wire reduces emissions primarily above 60 MHz, with less reduction at lower frequencies. Several dB of reduction is possible. Signal attenuation is approximately equivalent to increasing the cable length by 10 to 20 meters, thus reducing cable reach by that amount. For applications needing more modest improvement in emissions, the level of filtering can be reduced by writing a series of registers.

#### 3.3 Fast Link-Up

Link-up time is normally determined by the time it takes to complete auto-negotiation. Additional time may be added by the auto MDI/MDI-X feature. The total link-up time from power-up or cable connect is typically a second or more.

Fast Link-up mode significantly reduces 100BASE-TX link-up time by disabling both auto-negotiation and auto MDI/MDI-X, and fixing the TX and RX channels. This is done via the CONFIG[2:0] and AUTONEG strapping options. Because these are strapping options, fast link-up is available immediately upon power-up. Fast Link-up is available only for 100BASE-TX link speed. To force the link speed to 10BASE-TX requires a register write.

Fast Link-up mode is intended for specialized applications where both link partners are known in advance. The link must also be known so that the fixed transmit channel of one device connects to the fixed receive channel of the other device, and vice versa.

If a device in Fast Link-up mode is connected to a normal device (auto-negotiate and auto-MDI/MDI-X), there are no problems linking, but the speed advantage of Fast Link-up is realized only on one end.

#### 3.4 Internal and External RX Termination

By default, the RX differential pair is internally terminated. This minimizes the board component count by eliminating all components between the KSZ8061RNB/RND and the magnetics (transformer and common mode choke). The KSZ8061RNB/RND has the option to turn off the internal termination, to allow the use of external termination. External termination does increase the external component count, but these external components can be of tighter tolerance than the internal termination resistors. Enabling or disabling of the internal RX termination is controlled by register 14h, bit [2].

If external termination is used in place of the internal termination, it should consist of two  $50\Omega$  resistors in series between RXP and RXM, with a 0.1  $\mu$ F to 1  $\mu$ F capacitor from the midpoint of the two resistors to ground.

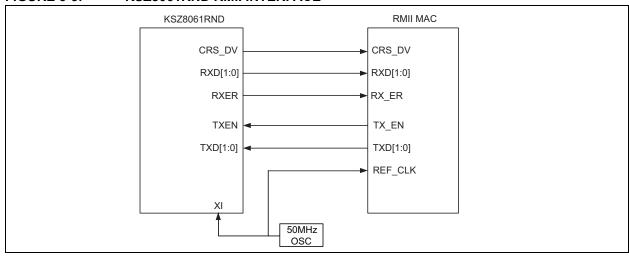

#### 3.5 RMII Interface

The Reduced Media Independent Interface (RMII) specifies a low pin count Media Independent Interface. It provides a common interface between RMII PHYs and MACs and has the following key characteristics:

- Pin count is 8 pins (3 pins for data transmission, 4 pins for data reception, and 1 pin for the 50-MHz reference clock).

- 10-Mbps and 100-Mbps data rates are supported at both half- and full-duplex.

- Data transmission and reception are independent and belong to separate signal groups.

- · Transmit data and receive data are each 2-bit wide, a di-bit.

#### 3.6 RMII Signal Definition

Table 3-1 describes the RMII signals. Refer to RMII Specification v1.2 for detailed information.

| <b>TABLE 3-1:</b> | RMII SIGNAI | DEFINITION |

|-------------------|-------------|------------|

|                   |             |            |

| RMII Signal<br>Name | KSZ8061RNB/RND Signal and<br>Direction            | Direction<br>(with respect to<br>MAC device) | Description                              |

|---------------------|---------------------------------------------------|----------------------------------------------|------------------------------------------|

| REF_CLK             | KSZ8061RNB REF_CLK, Output Input Synchronous 50-N |                                              | Synchronous 50-MHz reference clock for   |

|                     | KSZ8061RND XI, Input                              | Input or Output                              | receive, transmit, and control interface |

| TX_EN               | TXEN, Input                                       | Output                                       | Transmit Enable                          |

| TXD[1:0]            | TXD[1:0], Input                                   | Output                                       | Transmit Enable                          |

| CRS_DV              | CRS_DV, Output                                    | Input                                        | Carrier Sense/Receive Data Valid         |

| RXD[1:0]            | RXD[1:0], Output                                  | Input                                        | Receive Data [1:0]                       |

| RX_ER               | RXER, Output                                      | Input                                        | Receive Error                            |

#### 3.6.1 REFERENCE CLOCK (REF CLK)

REF\_CLK is a continuous 50-MHz clock that provides the timing reference for TXEN, TXD[1:0], CRS\_DV, RXD[1:0], and RXER. The KSZ8061RNB generates and outputs the 50-MHz RMII REF\_CLK to the MAC device at REF\_CLK (pin 19). The KSZ8061RND receives the 50-MHz RMII REF\_CLK from the MAC or system board at XI (pin 1), and leaves the REF\_CLK (pin 19) as no connect.

#### 3.6.2 TRANSMIT ENABLE (TXEN)

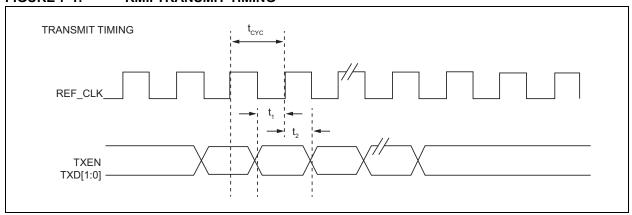

TXEN indicates the MAC is presenting di-bits on TXD[1:0] for transmission. It is asserted synchronously with the first di-bit of the preamble and remains asserted while all di-bits to be transmitted are presented on the RMII. It is negated prior to the first REF\_CLK following the final di-bit of a frame.

TXEN transitions synchronously with respect to REF CLK.

#### 3.6.3 TRANSMIT DATA [1:0] (TXD[1:0])

When TXEN is asserted, the PHY accepts TXD[1:0] for transmission. When TXEN is deasserted, the MAC drives TXD[1:0] to 00 for the idle state.

TXD[1:0] transitions synchronously with respect to REF CLK.

#### 3.6.4 CARRIER SENSE/RECEIVE DATA VALID (CRS\_DV)

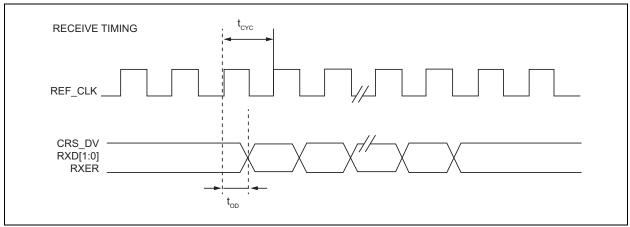

The PHY asserts CRS\_DV when the receive medium is non-idle. It is asserted asynchronously when a carrier is detected. This happens when squelch is passed in 10 Mbps mode and when two non-contiguous 0s in 10 bits are detected in 100 Mbps mode. Loss of carrier results in the deassertion of CRS\_DV.

While carrier detection criteria are met, CRS\_DV remains asserted continuously from the first recovered di-bit of the frame though the final recovered di-bit. It is negated before the first REF\_CLK that follows the final di-bit. The data on RXD[1:0] is considered valid after CRS\_DV is asserted. However, because the assertion of CRS\_DV is asynchronous relative to REF\_CLK, the data on RXD[1:0] is 00 until receive signals are properly decoded.

#### 3.6.5 RECEIVE DATA[1:0] (RXD[1:0])

For each clock period in which CRS\_DV is asserted, RXD[1:0] transfers a di-bit of recovered data from the PHY. When CRS\_DV is deasserted, the PHY drives RXD[1:0] to 00 for the idle state.

RXD[1:0] transitions synchronously with respect to REF CLK.

#### 3.6.6 RECEIVE ERROR (RXER)

When CRS\_DV is asserted, RXER is asserted for one or more REF\_CLK periods to indicate that a symbol error (for example, a coding error that a PHY can detect that may otherwise be undetectable by the MAC sub-layer) is detected somewhere in the frame that is being transferred from the PHY to the MAC.

RXER transitions synchronously with respect to REF CLK.

#### 3.6.7 RMII SIGNAL DIAGRAMS

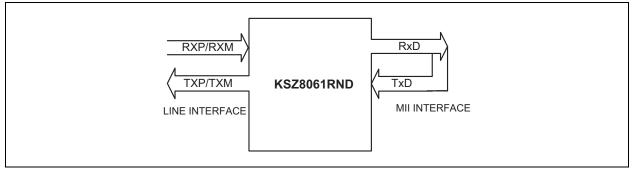

The KSZ8061RNB RMII pin connections to the MAC are shown in Figure 3-2. The connections for the KSZ8061RND are shown in Figure 3-3.

RMII MAC KSZ8061RNB CRS\_DV CRS\_DV RXD[1:0] RXD[1:0] **RXFR** RX\_ER **TXEN** TX\_EN TXD[1:0] TXD[1:0] REF\_CLK REF\_CLK ΧO ΧI 25 MHz **XTAL**

FIGURE 3-2: KSZ8061RNB RMII INTERFACE

FIGURE 3-3: KSZ8061RND RMII INTERFACE

#### 3.7 Back-to-Back Mode - 100 Mbps Repeater

Two KSZ8061RND devices can be connected back-to-back to form a 100BASE-TX to 100BASE-TX repeater. For testing purposes, it can also be used to loopback data on the RMII bus by physically connecting the RMII receive bus to the RMII transmit bus.

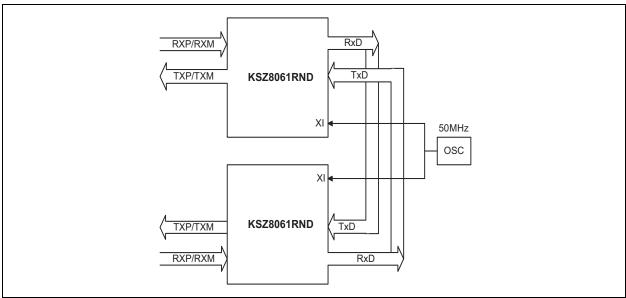

FIGURE 3-4: KSZ8061RND TO KSZ8061RND BACK-TO-BACK REPEATER

FIGURE 3-5: KSZ8061RND BACK-TO-BACK FOR RMII BUS LOOPBACK

#### 3.8 RMII Back-to-Back Mode

In RMII back-to-back mode, a KSZ8061RND interfaces with another KSZ8061RND to provide a complete 100-Mbps repeater solution.

The KSZ8061RND devices are configured to RMII Back-to-Back mode after power-up or reset with the following:

- Strapping pin CONFIG[2:0] set to '101'

- A common 50-MHz reference clock connected to XI of both KSZ8061RND devices

- RMII signals connected as shown in Table 3-2

TABLE 3-2: RMII SIGNAL CONNECTION FOR RMII BACK-TO-BACK MODE

| KSZ8061RND (100BASE-TX)<br>[Device 1] |          |          | (100BASE-TX)<br>e 1 or 2] |

|---------------------------------------|----------|----------|---------------------------|

| Pin Name                              | Pin Type | Pin Name | Pin Type                  |

| CRS_DV                                | OUTPUT   | TXEN     | INPUT                     |

| RXD1                                  | OUTPUT   | TXD1     | INPUT                     |

| RXD0                                  | OUTPUT   | TXD0     | INPUT                     |

| TXEN                                  | INPUT    | CRS_DV   | OUTPUT                    |

| TXD1                                  | INPUT    | RXD1     | OUTPUT                    |

| TXD0                                  | INPUT    | RXD0     | OUTPUT                    |

#### 3.9 MII Management (MIIM) Interface

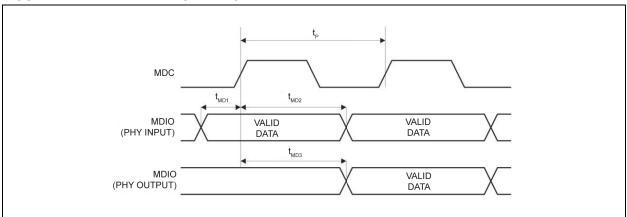

The KSZ8061RNB/RND supports the IEEE 802.3 MII Management Interface, also known as the Management Data Input/Output (MDIO) Interface. This interface enables an upper-layer device, like a MAC processor, to monitor and control the state of the KSZ8061RNB/RND. An external device with MIIM capability is used to read the PHY status, or to configure the PHY settings, or both. Further details on the MIIM interface can be found in Clause 22.2.4 of the IEEE 802.3 Specification.

The MIIM interface consists of the following:

- · A physical connection that incorporates the clock line (MDC) and the data line (MDIO).

- A specific protocol that operates across the aforementioned physical connection that allows the external controller to communicate with one or more PHY devices.

- A set of 16-bit MDIO registers. Supported registers [0:8] are standard registers, and their functions are defined per the IEEE 802.3 specification. The additional registers are provided for expanded functionality. See "Register Map" section for details.

The KSZ8061RNB/RND supports unique PHY addresses 1 to 7, and broadcast PHY address 0. The broadcast address is defined per the IEEE 802.3 specification, and can be used to write to multiple KSZ8061RNB/RND devices simultaneously.

The PHYAD[2:0] strapping pins are used to assign a unique PHY address between 1 and 7 to each KSZ8061RNB/RND device.

Table 3-3 shows the MII Management frame format.

TABLE 3-3: MII MANAGEMENT FRAME FORMAT

|       | Preamble | Start of Frame | Read/Write<br>OP Code | PHY<br>Address<br>Bits [4:0] | REG<br>Address<br>Bits [4:0] | TA | Data<br>Bits [15:0] | ldle |

|-------|----------|----------------|-----------------------|------------------------------|------------------------------|----|---------------------|------|

| Read  | 32 1's   | 01             | 10                    | 00AAA                        | RRRRR                        | Z0 | DDDDDDDD_DDDDDDD    | Z    |

| Write | 32 1's   | 01             | 01                    | 00AAA                        | RRRRR                        | 10 | DDDDDDDD_DDDDDDD    | Z    |

#### 3.10 LED Output Pins

The LED0 and LED1 pins indicate link status and is intended for driving LEDs. They are active low and can sink current directly from the LEDs. By default, LED0 indicates Link/Activity, and LED1 indicates Link Speed. Bits [5:4] in register 1Fh allow the definition of these pins to be changed to Link Status and Activity, respectively.

- · Link Status: The LED indicates that the serial link is up.

- Link/Activity: When the link is up, but there is no traffic, the LED is on. When packets are being received or transmitted, the LED blinks.

- · Activity: The LED blinks when packets are received or transmitted. It is off when there is no activity.

- Speed: When the link is up, the LED is on to indicate a 100BASE-TX link and is off to indicate a 10BASE-T link.

#### 3.11 Interrupt (INTRP)

INTRP is an interrupt output signal that may be used to inform the external controller that there has been a status update to the KSZ8061RNB/RND PHY register. This eliminates the need for the processor to poll the PHY for status changes such as link up or down.

Register 1Bh, bits [15:8] are the interrupt control bits to enable and disable the conditions for asserting the INTRP signal. Register 1Bh, bits [7:0] are the interrupt status bits to indicate which interrupt conditions have occurred. The interrupt status bits are cleared after reading register 1Bh.

Register 1Fh, bit [9] sets the interrupt level to active-high or active-low. The default is active-low.

RX+

RX-

#### 3.12 HP Auto MDI/MDI-X

HP Auto MDI/MDI-X configuration eliminates the confusion of whether to use a straight cable or a crossover cable between the KSZ8061RNB/RND and its link partner. This feature allows the KSZ8061RNB/RND to use either type of cable to connect with a link partner that is in either MDI or MDI-X mode. The auto-sense function detects transmit and receive pairs from the link partner and then assigns transmit and receive pairs of the KSZ8061RNB/RND accordingly.

Auto MDI/MDI-X is initially enabled or disabled at hardware reset by hardware pin strapping (CONFIG[2:0]). Afterwards, it can be enabled or disabled by register 1Fh, bit [13]. When Auto MDI/MDI-X is disabled, serial data is normally transmitted on the pin pair TXP/TXM, and data is received on RXP/RXM. However, this may be reversed by writing to register 1Fh, bit [14].

An isolation transformer with symmetrical transmit and receive data paths is recommended to support Auto MDI/MDI-X. Table 3-4 illustrates how the IEEE 802.3 Standard defines MDI and MDI-X.

| M         | DI     | МС        | DI-X   |

|-----------|--------|-----------|--------|

| RJ-45 Pin | Signal | RJ-45 Pin | Signal |

| 1         | TX+    | 1         | RX+    |

| 2         | TX-    | 2         | RX-    |

3

6

TABLE 3-4: MDI/MDI-X PIN DEFINITION

#### 3.13 Straight Cable

3

6

A straight cable connects an MDI device to an MDI-X device, or an MDI-X device to an MDI device. Figure 3-6 depicts a typical straight cable connection between a NIC card (MDI device) and a switch, or hub (MDI-X device).

TX+

TX-

10/100 ETHERNET 10/100 ETHERNET MEDIA DEPENDENT INTERFACE MEDIA DEPENDENT INTERFACE TRANSMIT PAIR RECEIVE PAIR 2 STRAIGHT 3 3 CABLE 4 RECEIVE PAIR RANSMIT PAIR 5 5 6 6 7 7 8 8 MODULAR CONNECTOR MODULAR CONNECTOR (RJ-45) (RJ-45) NIC HUB (REPEATER OR SWITCH)

FIGURE 3-6: TYPICAL STRAIGHT CABLE CONNECTION

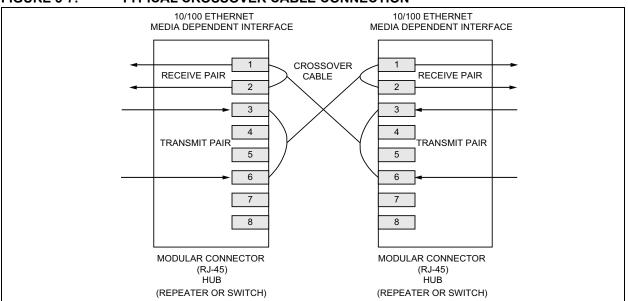

#### 3.14 Crossover Cable

A crossover cable connects an MDI device to another MDI device, or an MDI-X device to another MDI-X device. Figure 3-7 depicts a typical crossover cable connection between two switches or hubs (two MDI-X devices).

FIGURE 3-7: TYPICAL CROSSOVER CABLE CONNECTION

#### 3.15 Loopback Modes

The KSZ8061RNB/RND supports the following loopback operations to verify analog and/or digital data paths:

- · Local (Digital) Loopback

- · Remote (Analog) Loopback

#### 3.15.1 LOCAL (DIGITAL) LOOPBACK MODE

This loopback mode is a diagnostic mode for checking the RMII transmit and receive data paths between KSZ8061RNB/RND and an external MAC, and is supported for both speeds (10/100 Mbps) at full-duplex.

The loopback data path is shown in Figure 3-8.

- RMII MAC transmits frames to KSZ8061RNB/RND.

- 2. Frames are wrapped around inside KSZ8061RNB/RND.

- 3. KSZ8061RNB/RND transmits frames back to RMII MAC.

FIGURE 3-8: LOCAL (DIGITAL) LOOPBACK

The following programming steps and register settings are used for Local Loopback mode.

For 10/100 Mbps loopback:

Set Register 0h,

Bit [14] = 1 // Enable Local Loopback mode

Bit [13] = 0 / 1 // Select 10 Mbps / 100 Mbps speed

Bit [12] = 0 // Disable Auto-Negotiation

Bit [12] = 0 // Disable Auto-Negotiation

Bit [8] = 1 // Select full-duplex mode

Set Register 1Ch,

• Bit [5] = 1

#### 3.15.2 REMOTE (ANALOG) LOOPBACK

This loopback mode checks the line (differential pairs, transformer, RJ-45 connector, Ethernet cable) transmit and receive data paths between KSZ8061RNB/RND and its link partner, and is supported for 100BASE-TX full-duplex mode only.

The loopback data path is shown in Figure 3-9.

- Fast Ethernet (100BASE-TX) PHY link partner transmits frames to KSZ8061RNB/RND.

- Frames are wrapped around inside KSZ8061RNB/RND.

- KSZ8061RNB/RND transmits frames back to fast Ethernet (100BASE-TX) PHY link partner.

FIGURE 3-9: REMOTE (ANALOG) LOOPBACK

The following programming steps and register settings are used for Remote Loopback mode.

Set Register 0h,

Bit [13] = 1 // Select 100 Mbps speed

Bit [12] = 0 // Disable Auto-Negotiation

Bit [8] = 1 // Select full-duplex mode

Or simply auto-negotiate and link up at 100BASE-TX full-duplex mode with link partner.

Set Register 1Fh,

• Bit [2] = 1 // Enable Remote Loopback mode

## 3.16 LinkMD<sup>®</sup> Cable Diagnostics

The LinkMD<sup>®</sup> function utilizes time domain reflectometry (TDR) to analyze the cabling plant for common cabling problems, such as open circuits, short circuits, and impedance mismatches.

LinkMD works by sending a pulse of known amplitude and duration down the MDI or MDI-X pair, and then analyzing the shape of the reflected signal to determine the type of fault. The time duration for the reflected signal to return provides the approximate distance to the cabling fault. The LinkMD function processes this TDR information and presents it as a numerical value that can be translated to a cable distance.

LinkMD is initiated by accessing the LinkMD Control/Status Register (register 1Dh) and the PHY Control 2 Register (register 1Fh). The latter register is used to disable auto MDI/MDIX and to select either MDI or MDI-X as the cable differential pair for testing.

A two-step process is used to analyze the cable. The first step uses a small pulse (for short cables), while the second step uses a larger pulse (for long cables). The steps are as follows:

#### Step 1:

- Write MMD address 1Bh, register 0, bits [7:4] = 0x2. Note that this is the power-up default value.

- Write register 13h, bit [15] = 0. Note that this is the power-up default value.

- Write register 1Fh. Disable auto MDI/MDI-X in bit [13], and select either MDI or MDI-X in bit [14] to specify the

twisted pair to test.

- · Write register 1Dh bit [15] to initiate the LinkMD test.

• Read register 1Dh to determine the result of the first step. Bit [15] = 0 indicates that the test is complete. After that, the result is read in bits [14:12]. Remember the result.

#### Step 2:

- Write MMD address 1Bh, register 0, bits [7:4] = 0x7.

- Write register 13h, bit [15] = 1.

- · Write register 1Dh bit [15] to initiate the LinkMD test.

- Read register 1Dh to determine the result of the first step. Bit [15] = 0 indicates that the test is complete. After that, the result is read in bits [14:12].

- If either step reveals a short, then there is a short. If either step reveals an open, then there is an open. If both tests indicate normal, then the cable is normal.

### 3.17 LinkMD®+ Enhanced Diagnostics: Receive Signal Quality Indicator

The KSZ8061RN provides a receive Signal Quality Indicator (SQI) feature, which indicates the relative quality of the 100BASE-TX receive signal. It approximates a signal-to-noise ratio, and is affected by cable length, cable quality, and coupled of environmental noise.

The raw SQI value is available for reading at any time from indirect register: MMD 1Ch, register ACh, bits [14:8]. A lower value indicates better signal quality, while a higher value indicates worse signal quality. Even in a stable configuration in a low-noise environment, the value read from this register may vary. The value should therefore be averaged by taking multiple readings. The update interval of the SQI register is 2  $\mu$ s, so measurements taken more frequently than 2  $\mu$ s are redundant. In a quiet environment, 6 to 10 readings are suggested for averaging. In a noisy environment, individual readings are unreliable, so a minimum of 30 readings are suggested for averaging. The SQI circuit does not include any hysteresis.

Table 3-5 lists typical SQI values for various CAT5 cable lengths when linked to a typical 100BASE-TX device in a quiet environment. In a noisy environment or during immunity testing, the SQI value increases.

| TABLE 3-5: | TYPICAL | SOI VAI | HES |

|------------|---------|---------|-----|

|            |         |         |     |

| CAT5 Cable Length | Typical SQL Value (MMD 1Ch, register ACh, bits [14:8]) |

|-------------------|--------------------------------------------------------|

| 10m               | 2                                                      |

| 30m               | 2                                                      |

| 50m               | 3                                                      |

| 80m               | 3                                                      |

| 100m              | 4                                                      |

| 130m              | 5                                                      |

#### 3.18 NAND Tree Support

The KSZ8061RNB/RND provides parametric NAND tree support for fault detection between chip I/Os and board. The NAND tree is a chain of nested NAND gates in which each KSZ8061RNB/RND digital I/O (NAND tree input) pin is an input to one NAND gate along the chain. At the end of the chain, the CONFIG1 pin provides the output for the next NAND gates.

The NAND tree test process includes:

- · Enabling NAND tree mode

- · Pulling all NAND tree input pins high

- Driving low each NAND tree input pin sequentially per the NAND tree pin order

- Checking the NAND tree output to ensure there is a toggle high-to-low or low-to-high for each NAND tree input driven low

Table 3-6 lists the NAND tree pin order.

TABLE 3-6: KSZ8061RNB/RNDNAND TREE TEST PIN ORDER

| Pin Number | Pin Name | NAND Tree Description |  |

|------------|----------|-----------------------|--|

| 10         | MDIO     | INPUT                 |  |

| 11         | MDC      | INPUT                 |  |

| 12         | RXER     | INPUT                 |  |

| 13         | CRS_DV   | INPUT                 |  |

| 14         | PHYAD0   | INPUT                 |  |

| 16         | PHYAD1   | INPUT                 |  |

| 17         | RXD1     | INPUT                 |  |

| 18         | RXD0     | INPUT                 |  |

| 19         | REF_CLK  | INPUT                 |  |

| 20         | DNU      | INPUT                 |  |

| 21         | TXEN     | INPUT                 |  |

| 22         | TXD0     | INPUT                 |  |

| 23         | TXD1     | INPUT                 |  |

| 24         | LED0     | INPUT                 |  |

| 25         | DNU      | INPUT                 |  |

| 26         | DNU      | INPUT                 |  |

| 29         | INTRP    | INPUT                 |  |

| 27         | CONFIG   | OUTPUT                |  |

#### 3.19 NAND Tree I/O Testing

The following procedure can be used to check for faults on the KSZ8061RNB/RND digital I/O pin connections to the board:

- Enable NAND tree mode by INTRP pin strapping option.

- Use board logic to drive all KSZ8061RNB/RND NAND tree input pins high.

- 3. Use board logic to drive each NAND tree input pin, per KSZ8061RNB/RND NAND Tree pin order, as follows:

- a) Toggle the first pin (MDIO) from high to low, and verify the CONFIG1 pin switch from high to low to indicate that the first pin is connected properly.

- b) Leave the first pin (MDIO) low.

- c) Toggle the second pin (MDC) from high to low, and verify the CONFIG1 pin switch from low to high to indicate that the second pin is connected properly.

- d) Leave the first pin (MDIO) and the second pin (MDC) low.

- e) Toggle the third pin (RXER) from high to low, and verify the CONFIG1 pin switch from high to low to indicate that the third pin is connected properly.

- f) Continue with this sequence until all KSZ8061RNB/RND NAND tree input pins have been toggled.

Each KSZ8061RNB/RND NAND tree input pin must cause the CONFIG1 output pin to toggle high-to-low or low-to-high to indicate a good connection. If the CONFIG1 pin fails to toggle when the KSZ8061RNB/RND input pin toggles from high to low, the input pin has a fault.

#### 3.20 Power Management

The KSZ8061RNB/RND offers the following power management modes which are enabled and disabled by register control.

#### 3.20.1 POWER SAVING MODE

Power Saving mode is used to reduce the transceiver power consumption when the cable is unplugged. This mode does not interfere with normal device operation. It is enabled by writing a one to register 1Fh, bit [10], and is in effect when auto-negotiation mode is enabled and the cable is disconnected (no link). In this mode, the KSZ8061RNB/RND shuts down all transceiver blocks except for the transmitter, energy detect, and PLL circuits. By default, Power Saving mode is disabled after power-up.

#### 3.20.2 ENERGY-DETECT POWER-DOWN MODE

Energy-Detect Power-Down (EDPD) mode is used to further reduce the transceiver power consumption when the cable is unplugged, relative to Power Saving mode. This mode does not interfere with normal device operation. It is enabled by writing a zero to register 18h, bit [11], and is in effect when auto-negotiation mode is enabled and cable is disconnected (no link).

EDPD mode can be optionally enhanced with a PLL Off feature, which turns off all KSZ8061RNB/RND transceiver blocks, except for transmitter and energy detect circuits. PLL Off is set by writing a one to register 10h, bit [4].

Further power reduction is achieved by extending the time interval in between transmissions of link pulses while in this mode. The periodic transmission of link pulses is needed to ensure two link partners in the same low powered state with auto MDI/MDI-X disabled can wake up when the cable is connected between them.

By default, EDPD mode is disabled after power-up.

#### 3.20.3 POWER-DOWN MODE

Power-Down mode is used to power down the KSZ8061RNB/RND when it is not in use after power-up. It is enabled by writing a one to register 0h, bit [11].

In this mode, the KSZ8061RNB/RND disables all internal functions except the MII management interface. The KSZ8061RNB/RND exits (disables) the Power-Down mode after register 0h, bit [11] is set back to zero.

#### 3.20.4 SLOW OSCILLATOR MODE

Slow Oscillator mode is used to disconnect the input reference crystal/clock on XI (pin 1) and select the on-chip slow oscillator when the KSZ8061RNB/RND is not in use after power-up. It is enabled by writing a one to register 11h, bit [6].

Slow Oscillator mode works in conjunction with Power-Down mode to put the KSZ8061RNB/RND into a lower power state with all internal functions disabled, except for the MII management interface. To properly exit this mode and return to normal PHY operation, use the following programming sequence:

- 1. Disable Slow Oscillator mode by writing a zero to register 11h, bit [6].

- 2. Disable Power-Down mode by writing a zero to register 0h, bit [11].

- 3. Initiate software reset by writing a one to register 0h, bit [15].

#### 3.20.5 ULTRA-DEEP SLEEP MODE

Ultra-Deep Sleep mode is used to achieve the lowest possible power consumption while retaining the ability to detect activity on the Tx/Rx cable pairs, and is intended for achieving negligible battery drain during long periods of inactivity. It is controlled by several register bits, and Ultra-Deep Sleep mode may be entered by writing to a register, or it may be initiated automatically when Signal Detect (SIGDET) is deasserted. Details are given in the Signal Detect (SIGDET) and Ultra-Deep Sleep mode section.

In Ultra-Deep Sleep mode, the KSZ8061RNB/RND disables all internal functions and I/Os except for the ultra-low power signal detect circuit and the Signal Detect pin (SIGDET), which are powered from VDDIO. For lowest power consumption, the 1.2V supply (VDDL and AVDDL) may be turned off externally. Hardware reset is required to exit Ultra-Deep Sleep mode.

#### 3.20.6 NON-VOLATILE REGISTERS

Most of the logic circuitry of the KSZ8061RNB/RND, including the status and control registers, is powered by the 1.2V supply. When the 1.2V supply is turned off in Ultra-Deep Sleep mode, the content of the registers is lost. Because of the importance of register 14h and bit [0] of register 13h, which control the various power modes, these bits are duplicated in a logic block powered by the 3.3V supply. These register bits are therefore "non-volatile" while in Ultra-Deep Sleep mode.

To access the non-volatile (3.3V) registers, bit [4] of register 14h must first be set. Otherwise, writes to these registers modify only the volatile versions of these registers, and not the non-volatile versions.

#### 3.21 Signal Detect (SIGDET) and Ultra-Deep Sleep Mode

SIGDET is an output signal which may be used for power reduction, either by directly turning off selected power or by signaling to a host controller when no signal is detected on the line interface. It is asserted when sufficient energy is detected on either of the differential pairs, and is deasserted when cable energy is not detected. The signal detection circuit consumes almost no power from the VDDIO supply, and does not use the 1.2V supply at all.

Ultra-Deep Sleep mode may be entered either automatically in unison with the Signal Detect signal (Automatic method), or manually by setting a register bit (CPU Control method).

The signal detect feature and Ultra-Deep Sleep mode are controlled via multiple bits in register 14h:

| <ul> <li>Register 14h, bit [6]</li> </ul> | Ultra-Deep Sleep method: either Automatic or CPU Control                                                                               |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Register 14h, bit [5]</li> </ul> | Manually enter Ultra Deep Sleep mode when CPU Control method is selected                                                               |

| Register 14h, bit [4]                     | Enable R/W access to non-volatile versions of register 14h and bits [9:8] and [1:0] of register 13h. Set this bit when bit [3] is set. |

| <ul> <li>Register 14h, bit [3]</li> </ul> | Enable Ultra Deep Sleep Mode and SIGDET                                                                                                |

| <ul> <li>Register 14h, bit [1]</li> </ul> | Extend timing for SIGDET deassertion and entry into Ultra-Deep Sleep mode                                                              |

| <ul> <li>Register 14h, bit [0]</li> </ul> | SIGDET output polarity                                                                                                                 |

#### 3.21.1 CPU CONTROL METHOD (MIIM INTERFACE)

- KSZ8061RNB/RND drives SIGDET signal to the CPU.

- SIGDET defaults to force high, to not interfere with PHY initialization by the CPU. At power-on, the KSZ8061RNB/ RND drives SIGDET high, without consideration of cable energy level.

- During initialization, the CPU writes data 0x0058 to register 14h.

- Bit [4] enables access to the non-volatile copy of register 14h.

- Enable Ultra-Deep Sleep mode and SIGDET by setting register 14h, bit [3].

- Automatic Ultra-Deep Sleep functionality is disabled by setting register 14h, bit [6].

- SIGDET is now enabled and changes state as cable energy changes.

- In response to the deassertion of SIGDET, the CPU puts KSZ8061RNB/RND into Ultra-Deep Sleep mode by setting register 14h, bit [5]. To further reduce power, the CPU may disable the 1.2V supply to the KSZ8061RNB/RND.

- The KSZ8061RNB/RND asserts SIGDET when energy is detected on the cable.

- To activate the KSZ8061RNB/RND, the CPU enables the 1.2V supply and asserts hardware reset (RESET#) to the KSZ8061RNB/RND. Because the KSZ8061RNB/RND is completely reset, the registers must be re-initialized.

- Alternately, it is possible to maintain register access during Ultra-Deep Sleep mode by preserving the 1.2V power supply and setting register 13h, bit [0] to enable slow oscillator mode. Ultra-Deep Sleep mode can then be exited by writing to register 14h. The 1.2V supply results in increased power consumption.

#### 3.21.2 AUTOMATIC STANDBY METHOD

- The board may be designed such that the KSZ8061RNB/RND SIGDET signal enables the 1.2V power supply to KSZ8061RNB/RND.

- At power-on, the KSZ8061RNB/RND drives SIGDET high, without consideration of cable energy level.

- During initialization, CPU writes data 0x001A or 0x0018 to register 14h.

- Bit [4] enables access to the non-volatile copy of register 14h.

- Enable Ultra-Deep Sleep mode and SIGDET by setting register 14h, bit [3].

- Automatic Ultra-Deep Sleep functionality is enabled by clearing register 14h, bit [6].

- SIGDET timing bit [1] must be set unless the link partner is not using auto-negotiation, auto-MDI/MDI-X is dis-

abled, and link is at 100 Mbps.

- When the KSZ8061RNB/RND detects signal loss, it automatically enters Ultra-Deep Sleep mode and deasserts SIGDET. SIGDET may be used to disable the 1.2V supply.

- When the KSZ8061RNB/RND detects a signal, it asserts SIGDET (which enables the 1.2V supply) and automatically wakes up. SIGDET may be used to wake up the CPU, which then re-initializes the KSZ8061RNB/RND.

- Alternatively, a hardware reset (RESET#) brings the KSZ8061RNB/RND out of Ultra-Deep Sleep mode.

- The contents of register 14h and bits [9:8] and [1:0] of register 13h are preserved during Ultra-Deep Sleep mode, but are lost during hardware reset.

#### 4.0 REGISTER MAP

The register space within the KSZ8061RNB/RND consists of two distinct areas:

Standard registers

// Direct register access

MDIO Manageable device (MMD) registers

// Indirect register access

#### TABLE 4-1: STANDARD REGISTERS

| Register Number (hex)     | Description                                     |

|---------------------------|-------------------------------------------------|

| IEEE-Defined Registers    |                                                 |

| 0h                        | Basic Control                                   |

| 1h                        | Basic Status                                    |

| 2h                        | PHY Identifier 1                                |

| 3h                        | PHY Identifier 2                                |

| 4h                        | Auto-Negotiation Advertisement                  |

| 5h                        | Auto-Negotiation Link Partner Ability           |

| 6h                        | Auto-Negotiation Expansion                      |

| 7h                        | Auto-Negotiation Next Page                      |

| 8h                        | Auto-Negotiation Link Partner Next Page Ability |

| 9h - Ch                   | Reserved                                        |

| Dh                        | MMD Access Control Register                     |

| Eh                        | MMD Access Address Data Register                |

| Fh                        | Reserved                                        |

| Vendor-Specific Registers |                                                 |

| 10h                       | Digital Control                                 |

| 11h                       | AFE Control 0                                   |

| 12h                       | AFE Control 1                                   |

| 13h                       | AFE Control 2                                   |

| 14h                       | AFE Control 3                                   |

| 15h                       | RXER Counter                                    |

| 16h                       | Operation Mode                                  |

| 17h                       | Operation Mode Strap Status                     |

| 18h                       | Expanded Control                                |

| 19h - 1Ah                 | Reserved                                        |

| 1Bh                       | Interrupt Control/Status                        |

| 1Ch                       | Function Control                                |

| 1Dh                       | LinkMD® Control/Status                          |

| 1Eh                       | PHY Control 1                                   |

| 1Fh                       | PHY Control 2                                   |

#### TABLE 4-2: MMD REGISTERS

| Device Address (Hex) | Register Address (Hex) | Description    |

|----------------------|------------------------|----------------|

| 7h                   | 3Ch                    | Reserved       |

|                      | 3Dh                    | Reserved       |

| 1Bh                  | 0h                     | AFED Control   |

| 1Ch                  | ACh                    | Signal Quality |

#### 4.1 Standard Registers

Standard registers provide direct read/ or write access to a 32-register address space, as defined in Clause 22 of the IEEE 802.3 standard. Within this address space, the first 16 registers (0h to Fh) are defined according to the IEEE specification, while the remaining 16 registers (10h to 1Fh) are defined specific to the PHY vendor.

TABLE 4-3: STANDARD REGISTER DESCRIPTION