# **CMOS High-Speed 8-Bit Bidirectional CMOS/TTL Interface** Level Converter

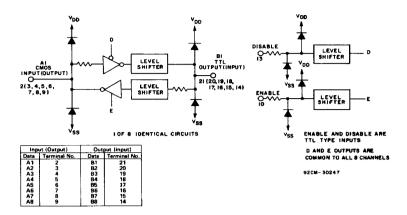

The RCA-CD40115 is a high-speed 8-bit integrated circuit designed to interface CMOS logic levels with TTL logic levels on the data bus of microprocessor-based systems. CMOS/ TTL interface is provided by eight parallel bidirectional buffer/level converters. Buffer INPUT/OUTPUT terminals are either inputs or outputs depending on the desired direction of data flow. A low on both the ENABLE and DISABLE control inputs selects the direction of data flow from CMOS Inputs to TTL Outputs. A high on both control inputs selects the direction of data flow from TTL Inputs to CMOS Outputs. A low on the ENABLE and a high on the DISABLE inhibits data flow in either direction and places the CMOS Outputs in a high-imped-

The TTL Input/Output terminals and the ENABLE and DISABLE control inputs are TTL-compatible without the use of external pull-up resistors. The TTL input logic 0 to logic 1 transition occurs at a level of approximately 1.5 volts. The ENABLE and DISABLE inputs may be driven to the VDD rail; therefore, either TTL or CMOS logic drivers, capable of sinking one TTL load, may be used to determine the direction of data flow. The large CMOS and TTL output

from case for 10 s max.

ance (3-state) mode.

#### Features:

- Eight inverting channels with 5V-to-12V or 12V-to-5V level conversion

- Three operating modes: CMOS-to-TTL level conversion TTL-to-CMOS level conversion Interface off; high-impedance

- Low propagation delay time: CMOS-to-TTL conversion — 10 ns typ. TTL-to-CMOS conversion — 30 ns typ.

- High TTL sink current 30 mA typ.

CMOS input/output

- No external TTL input pull-up resistors required

- High speed drive of large data bus capacitances

- Input/output and power supply terminals located for ease of PC board layout

buffers in this device have high output sink and source current capability and can drive the data bus capacitance with a transition time of approximately 0.1 ns/pF. This fast output transition time, together with the small propagation delay time of the device, allow high-speed operation.

The CD40115 is supplied in a 22-lead hermetic dual-in-line ceramic package.

### Applications:

- Interface CMOS microprocessor with

- TTL memories and peripheral devices Interface between and within logic systems which combine CMOS and TTL devices

#### MAXIMUM RATINGS, Absolute-Maximum Values: DC SUPPLY-VOLTAGE RANGE (Voltages referenced to VSS Terminal) v<sub>DD</sub> . . . . . . . . . . -0.5 to +6 V Data Inputs, CMOS to TTL -0.5 to V<sub>DD</sub>+0.5 V Data Inputs, TTL to CMOS -0.5 to V<sub>CC</sub>+0.5 V Enable, Disable Inputs -0.5 to V<sub>DD</sub>+0.5 V POWER DISSIPATION PER PACKAGE (PD): Derate Linearly at 12 mW/OC to 200 mW DEVICE DISSIPATION PER OUTPUT TRANSISTOR For TA = Full Package-Temperature Range . . OPERATING TEMPERATURE RANGE (TA) . -55 to +125°C STORAGE TEMPERATURE RANGE (T<sub>stg</sub>) . . . LEAD TEMPERATURE (DURING SOLDERING): -65 to +150°C At distance of 1/16 ± 1/32 inch (1.59 ± 0.79 mm)

| CMOS INPUT/OUTPUT | 'ss —  | 1 2 3 4 5 6 7 8 9 10 11 TOP VII | 22 VCC<br>21 81 10 20 82 10 10 10 10 10 10 10 10 10 10 10 10 10 |  |

|-------------------|--------|---------------------------------|-----------------------------------------------------------------|--|

| NC ·              | NO CON | NECTION                         | 92CS-30245                                                      |  |

|                   |        |                                 |                                                                 |  |

**TERMINAL ASSIGNMENT**

| IRUIH TABLE |                  |                                 |  |  |

|-------------|------------------|---------------------------------|--|--|

| ENABLE      | DISABLE FUNCTION |                                 |  |  |

| 0           | 0                | Convert CMOS Level to TTL Level |  |  |

| 1           | 1                | Convert TTL Level to CMOS Level |  |  |

| 0           | 1                | High Impedance (Z)              |  |  |

| _ 1         | 0                | Invalid*                        |  |  |

0 = Low Level 1 = High Level

Z = High Impedance on CMOS Output side; TTL side are inputs. INVALID = Both CMOS and TTL sides are ON as outputs.

See Operating and Handling Considerations - Bypessing and Unused Inputs.

Excessively high currents from  $V_{DD}$  to  $V_{SS}$  could flow in this mode during power turn-on or turn-off if other IC's drive into the bus lines (on either the TTL or CMOS side). This high current condition could occur during a transient or steady-state invalid mode.

+265°C

## CD40115

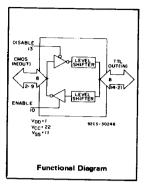

Fig. 1 — Functional block diagram.

## STATIC ELECTRICAL CHARACTERISTICS At $T_A = 25^{\circ}$ C, $V_{DD} = 12$ V, $V_{CC} = 5$ V

| CHARACTERISTIC                                                                                     |                               | TEST CONDITIONS                                                                                   | TYPICAL VALUES    | UNITS    |  |

|----------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------|-------------------|----------|--|

| Data Flow — CMOS Inputs to TT                                                                      | L Outputs                     |                                                                                                   |                   |          |  |

| Quiescent Device Current,<br>From V <sub>DD</sub> Supply,<br>From V <sub>CC</sub> Supply,          | I <sub>DD</sub>               |                                                                                                   | 4<br>5            | mΑ<br>μΑ |  |

| Input Current,                                                                                     | IN                            | V <sub>IN</sub> =0,12 V; Any CMOS input                                                           | ± 50              | μΑ       |  |

| Output Current,                                                                                    | lOH<br>lOL                    | V <sub>OH</sub> =3 V, V <sub>IL</sub> =2 V<br>V <sub>OL</sub> =0.4 V, V <sub>IH</sub> =10 V       | 15<br>30          | mA       |  |

| Data Flow — TTL Inputs to CMO                                                                      | S Outputs                     |                                                                                                   |                   | •        |  |

| Quiescent Device Current, From V <sub>DD</sub> Supply, From V <sub>CC</sub> Supply, Input Current, | IDD<br>ICC                    | V <sub>IL</sub> =0 to 0.7 V; Any TTL input                                                        | 4<br>5<br>–250    | mΑ<br>μΑ |  |

| mpat sarront,                                                                                      | liH.                          | V <sub>IH</sub> =2.3 V; Any TTL input                                                             | 50                | μА       |  |

| Output Current,                                                                                    | I <sub>OH</sub>               | V <sub>OH</sub> =11.5 V, V <sub>IL</sub> =0.7 V<br>V <sub>OL</sub> =0.5 V, V <sub>IH</sub> =2.3 V | 20<br>20          | mA       |  |

| CMOS 3-State Output Leakage<br>Current,                                                            | lоит                          | V <sub>O</sub> =0,12 V, V <sub>IN</sub> =0,5 V                                                    | ± 50              | μΑ       |  |

| Enable and Disable Inputs                                                                          |                               |                                                                                                   |                   |          |  |

| Input Current,                                                                                     | <sup>1</sup> 1Е<br>11Н<br>11Н | V <sub>IL</sub> =0 to 0.7 V<br>V <sub>IH</sub> =2.3 V (TTL)<br>V <sub>IH</sub> =12 V (CMOS)       | -250<br>-50<br>50 | μА       |  |

### DYNAMIC ELECTRICAL CHARACTERISTICS At TA = 25°C, VDD = 12 V, VCC = 5 V

|                                                                                                                |                 |             | - 00           |                        |        |  |

|----------------------------------------------------------------------------------------------------------------|-----------------|-------------|----------------|------------------------|--------|--|

| CHARACTERISTIC                                                                                                 | TEST CONDITIONS |             | TYPICAL VALUES |                        | UNITS  |  |

| CHARACTERISTIC                                                                                                 | INPUT           | OUTPUT      | CL=50 pF       | C <sub>L</sub> =200 pF | פוואטך |  |

| Propagation Delay Times,<br>Data-In to Data-Out,<br><sup>†</sup> PHL <sup>, †</sup> PLH                        | CMOS<br>TTL     | TTL<br>CMOS | 10<br>30       | 15<br>40               | ns     |  |

| Enable or Disable to<br>Data-Out,<br><sup>t</sup> PHZ <sup>, t</sup> PZH <sup>, t</sup> PLZ <sup>, t</sup> PZL |                 |             | 35             |                        | ns     |  |

| Transition Time, tTHL, tTLH                                                                                    | CMOS            | TTL         | 10             | 15                     | ns     |  |

|                                                                                                                | TTL             | CMOS        | 10             | 15                     | 1      |  |