# **NEC**

# **User's Manual**

# $\mu$ PD789467 Subseries

# **8-Bit Single-Chip Microcontrollers**

$\mu$ PD789462  $\mu$ PD789464  $\mu$ PD789466  $\mu$ PD789467  $\mu$ PD78F9468

Document No. U15552EJ2V1UD00 (2nd edition) Date Published January 2004 N CP(K)

# [MEMO]

#### NOTES FOR CMOS DEVICES -

#### (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### ② HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### 3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

FIP and EEPROM are trademarks of NEC Electronics Corporation.

Windows and Windows NT are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation.

HP9000 series 700 and HP-UX are trademarks of Hewlett-Packard Company.

SPARCstation is a trademark of SPARC International, Inc.

Solaris and SunOS are trademarks of Sun Microsystems, Inc.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of January, 2004. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of a customer's equipment shall be done under the full

responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by

customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC Electronics product in your application, please contact the NEC Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### [GLOBAL SUPPORT]

http://www.necel.com/en/support/support.html

### NEC Electronics America, Inc. (U.S.) NEC Electronics (Europe) GmbH NEC Electronics Hong Kong Ltd.

Santa Clara, California Tel: 408-588-6000 800-366-9782

Duesseldorf, Germany Tel: 0211-65 03 01

#### • Sucursal en España

Madrid, Spain Tel: 091-504 27 87

#### Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-675800

#### • Filiale Italiana

Milano, Italy Tel: 02-66 75 41

### Branch The Netherlands

Eindhoven. The Netherlands Tel: 040-2445845

#### Tyskland Filial

Taeby, Sweden Tel: 08-63 80 820

#### United Kingdom Branch

Milton Keynes, UK Tel: 01908-691-133

Hong Kong Tel: 2886-9318

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-558-3737

#### NEC Electronics Shanghai, Ltd.

Shanghai, P.R. China Tel: 021-6841-1138

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377

#### **NEC Electronics Singapore Pte. Ltd.**

Novena Square, Singapore Tel: 6253-8311

J03.4

# **Major Revisions in This Edition**

| Page                           | Description                                                                                                                                                                                                                                                      |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout                     | Deletion of development status indication "under development" for µPD789466 and 789467                                                                                                                                                                           |

| p. 35                          | Addition of description on pin connections in 2.2.15 VPP (µPD78F9468 only)                                                                                                                                                                                       |

| p. 55                          | Table 3-3 Special-Function Registers  Change of attribute of port 8 (P8) to read-only and change of value after reset to undefined  Modification of oscillation stabilization time selection register (OSTS) to allow use of 1-bit manipulation instruction.     |

| p. 74                          | Modification of Caution 2 in Figure 4-10 Format of Port Function Register 8                                                                                                                                                                                      |

| p. 79                          | Addition of Note on feedback resistor in Figure 5-3 Format of Suboscillation Mode Register                                                                                                                                                                       |

| p. 91                          | 6.2 Configuration of 8-Bit Timers 30 and 40  Modification of Figure 6-3 Block Diagram of Output Controller (Timer 40)  Addition of description to (2) 8-bit compare register 40 (CR40)  Addition of description to (3) 8-bit H width compare register 40 (CRH40) |

| p. 96                          | Addition to Cautions in Figure 6-6 Format of Carrier Generator Output Control Register 40                                                                                                                                                                        |

| p. 109                         | Addition to Cautions in 6.4.3 Operation as carrier generator                                                                                                                                                                                                     |

| p. 115                         | Modification of description in 6.5 Notes on Using 8-Bit Timers 30 and 40                                                                                                                                                                                         |

| p. 137                         | Addition of (8) Input impedance of ANI0 pin to 9.5 Cautions Related to 8-Bit A/D Converter                                                                                                                                                                       |

| pp. 141, 142                   | Addition to Notes and Cautions in Figure 10-2 Format of LCD Display Mode Register 0                                                                                                                                                                              |

| p. 159                         | Addition to Cautions in Figure 12-2 Format of Interrupt Request Flag Register 0                                                                                                                                                                                  |

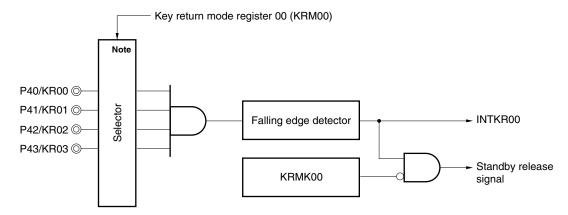

| p. 161                         | Addition to Cautions in Figure 12-6 Format of Key Return Mode Register 00                                                                                                                                                                                        |

| p. 169                         | Modification of oscillation stabilization time selection register (OSTS) to allow use of 1-bit manipulation instruction in 13.1.2 Register controlling standby function                                                                                          |

| p. 183                         | Modification of Table 15-3 Communication Mode List                                                                                                                                                                                                               |

| pp. 200, 202, 204,<br>205, 210 | CHAPTER 18 ELECTRICAL SPECIFICATIONS  Change from target values to formal specifications  Addition of Note 1 to Absolute Maximum Ratings  Addition of recommended oscillator constants for mask ROM versions  Modification of Write and Erase Characteristics    |

| p. 212                         | Addition of recommended conditions for µPD789466 and 789467 in <b>CHAPTER 20 RECOMMENDED SOLDERING CONDITIONS</b>                                                                                                                                                |

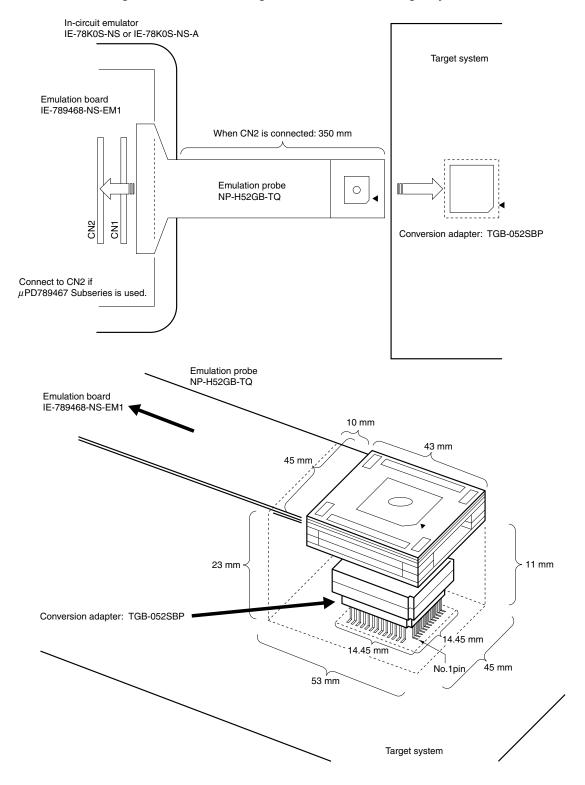

| p. 217                         | Change of name "conversion connector" and "conversion socket" to "conversion adapter (TGB-052SBP)" in A.5 Debugging Tools (Hardware)                                                                                                                             |

| p. 224                         | Addition of APPENDIX C REVISION HISTORY                                                                                                                                                                                                                          |

The mark ★ shows major revised points.

#### INTRODUCTION

**Target Readers**

This manual is intended for users who wish to understand the functions of the  $\mu$ PD789467 Subseries and to design and develop application systems and programs using these microcontrollers.

Target products:

• μPD789467 Subseries: μPD789462, 789464, 789466, 789467, 78F9468

**Purpose**

This manual is intended to give users an understanding of the functions described in the organization below.

Organization

The  $\mu$ PD789467 Subseries User's Manual is divided into two parts: this manual and instructions (common to the 78K/0S Series).

$\mu$ PD789467 Subseries User's Manual

- Pin functions

- Internal block functions

- Interrupt functions

- · Other on-chip peripheral functions

- · Electrical specifications

78K/0S Series Instructions User's Manual

- CPU function

- · Instruction set

- Explanation of each instruction

**How to Use This Manual**

It is assumed that the reader of this manual has general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

- To understand the functions in general:

- → Read this manual in the order of the contents.

- How to interpret the register format:

- → For a bit whose number is enclosed in brackets, the bit name is defined as a reserved word in the assembler, and already defined in the header file named sfrbit.h in the C compiler.

- When you know a register name and want to confirm its details:

- $\rightarrow$  Read APPENDIX B REGISTER INDEX.

- To know the 78K/0S Series instruction functions in detail:

- → Read 78K/0S Series Instructions User's Manual (U11047E).

- $\bullet$  To know the electrical specifications of the  $\mu \mbox{PD789467}$  Subseries:

- ightarrow Read CHAPTER 18 ELECTRICAL SPECIFICATIONS.

Conventions

Data significance: Higher digits on the left and lower digits on the right

Active low representation:  $\overline{xxx}$  (overscore over pin or signal name)

Note: Footnote for item marked with Note in the text

Caution: Information requiring particular attention

Remark: Supplementary information

Numerical representation: Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

#### **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

#### **Documents Related to Devices**

| Document Name                            | Document No. |

|------------------------------------------|--------------|

| μPD789467 Subseries User's Manual        | This manual  |

| 78K/0S Series Instructions User's Manual | U11047E      |

#### **Documents Related to Development Tools (Software) (User's Manuals)**

| Document Name                                          |                                                  | Document No. |

|--------------------------------------------------------|--------------------------------------------------|--------------|

| RA78K0S Assembler Package                              | Operation                                        | U14876E      |

|                                                        | Language                                         | U14877E      |

|                                                        | Structured Assembly Language                     | U11623E      |

| CC78K0S C Compiler                                     | Operation                                        | U14871E      |

|                                                        | Language                                         | U14872E      |

| SM78K Series System Simulator Ver. 2.30 or Later       | Operation (Windows™ Based)                       | U15373E      |

|                                                        | External Part User Open Interface Specifications | U15802E      |

| ID78K Series Integrated Debugger<br>Ver. 2.30 or Later | Operation (Windows Based)                        | U15185E      |

| Project Manager Ver. 3.12 or Later (Windows Based)     |                                                  | U14610E      |

### **Documents Related to Development Tools (Hardware) (User's Manuals)**

| Document Name                     | Document No.   |

|-----------------------------------|----------------|

| IE-78K0S-NS In-Circuit Emulator   | U13549E        |

| IE-78K0S-NS-A In-Circuit Emulator | U15207E        |

| IE-789468-NS-EM1 Emulation Board  | To be prepared |

# **Documents Related to Flash Memory Writing**

| Document Name                                | Document No. |

|----------------------------------------------|--------------|

| PG-FP3 Flash Memory Programmer User's Manual | U13502E      |

| PG-FP4 Flash Memory Programmer User's Manual | U15260E      |

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document for designing.

#### **Other Related Documents**

| Document Name                                                                      | Document No. |

|------------------------------------------------------------------------------------|--------------|

| SEMICONDUCTOR SELECTION GUIDE - Products and Packages - (CD-ROM)                   | X13769X      |

| Semiconductor Device Mount Manual                                                  | Note         |

| Quality Grades on NEC Semiconductor Devices                                        | C11531E      |

| NEC Semiconductor Device Reliability/Quality Control System                        | C10983E      |

| Guide to Prevent Damage for Semiconductor Devices by Electrostatic Discharge (ESD) | C11892E      |

Note See the "Semiconductor Device Mount Manual" website (http://www.necel.com/pkg/en/mount/index.html)

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document for designing.

# **CONTENTS**

| CHAPT | ER 1 (  | GENERAL                                              | 21 |

|-------|---------|------------------------------------------------------|----|

| 1.1   | Featur  | res                                                  | 21 |

| 1.2   | Applic  | cations                                              | 21 |

| 1.3   | Orderi  | ing Information                                      | 22 |

| 1.4   | Pin Co  | onfiguration (Top View)                              | 23 |

| 1.5   | 78K/0   | S Series Lineup                                      | 25 |

| 1.6   | Block   | Diagram                                              | 28 |

| 1.7   | Overv   | iew of Functions                                     | 29 |

| СНАРТ | ER 2 F  | PIN FUNCTIONS                                        | 31 |

| 2.1   | List of | f Pin Functions                                      | 31 |

| 2.2   |         | iption of Pin Functions                              |    |

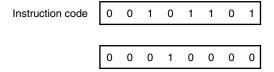

|       | 2.2.1   | P00 to P03 (Port 0)                                  | 33 |

|       | 2.2.2   | P10, P11 (Port 1)                                    |    |

|       | 2.2.3   | P40 to P43 (Port 4)                                  |    |

|       | 2.2.4   | P60, P61 (Port 6)                                    |    |

|       | 2.2.5   | P80 to P85 (Port 8)                                  |    |

|       | 2.2.6   | S0 to S16                                            |    |

|       | 2.2.7   | COM0 to COM3                                         | 32 |

|       | 2.2.8   | VLC0 to VLC2                                         |    |

|       | 2.2.9   | CATH, CAPL                                           |    |

|       | 2.2.10  | RESET                                                |    |

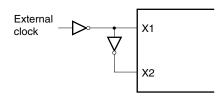

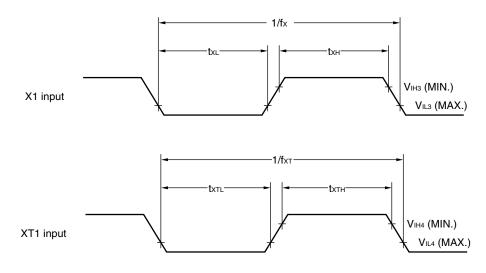

|       | 2.2.11  | X1, X2                                               | 34 |

|       | 2.2.12  | XT1, XT2                                             | 34 |

|       | 2.2.13  | V <sub>DD</sub>                                      | 34 |

|       | 2.2.14  | Vss                                                  | 34 |

|       | 2.2.15  | V <sub>PP</sub> (μPD78F9468 only)                    | 35 |

|       | 2.2.16  | IC0 (mask ROM version only)                          | 35 |

| 2.3   | Pin I/C | Circuits and Recommended Connection of Unused Pins   | 36 |

| СНАРТ | ER 3 (  | CPU ARCHITECTURE                                     | 38 |

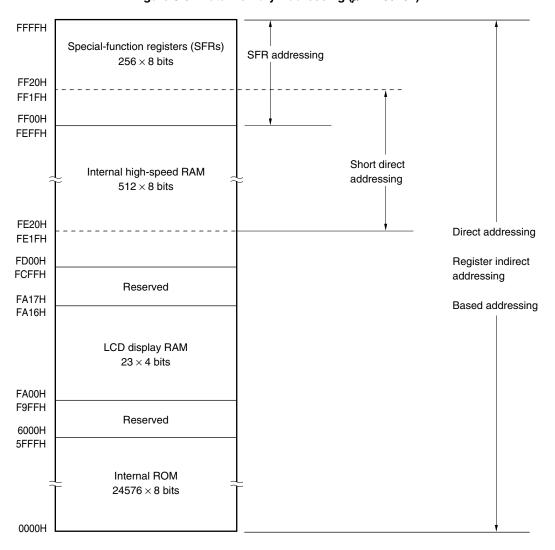

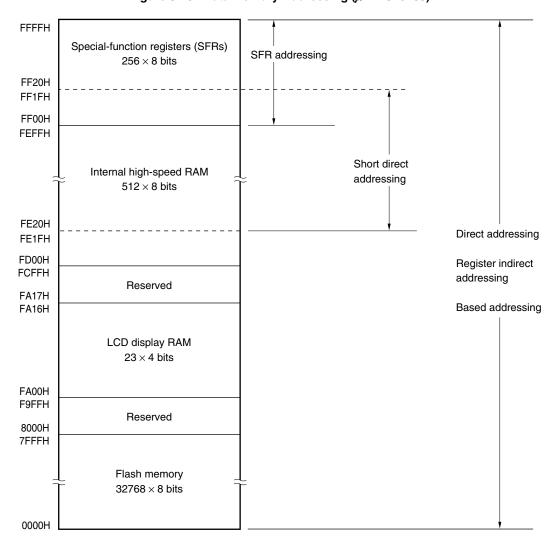

| 3.1   | Memo    | ry Space                                             | 38 |

|       | 3.1.1   | Internal program memory space                        | 43 |

|       | 3.1.2   | Internal data memory (internal high-speed RAM) space | 44 |

|       | 3.1.3   | Special-function register (SFR) area                 | 44 |

|       | 3.1.4   | Data memory addressing                               | 45 |

| 3.2   | Proces  | ssor Registers                                       | 50 |

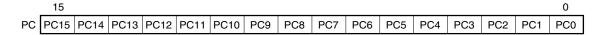

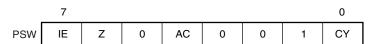

|       | 3.2.1   | Control registers                                    | 50 |

|       | 3.2.2   | General-purpose registers                            | 53 |

|       | 3.2.3   | Special-function registers (SFRs)                    | 54 |

| 3.3   | Instru  | ction Address Addressing                             | 56 |

|       | 3.3.1   | Relative addressing                                  | 56 |

| 6.2        | Confi          | guration of 8-Bit Timers 30 and 40                             | Configuration of 8-Bit Timers 30 and 4088 |  |  |

|------------|----------------|----------------------------------------------------------------|-------------------------------------------|--|--|

| 6.1        | Funct          | tions of 8-Bit Timers 30 and 40                                | 87                                        |  |  |

| CHAPT      | ER 6           | 8-BIT TIMERS 30 AND 40                                         | 87                                        |  |  |

|            | 5.6.2          | Switching between system clock and CPU clock                   | 86                                        |  |  |

|            | 5.6.1<br>5.6.2 | Time required for switching between system clock and CPU clock |                                           |  |  |

| 5.6        | •              | ging Setting of System Clock and CPU Clock                     |                                           |  |  |

| 5.5<br>5.6 |                | Generator Operation                                            |                                           |  |  |

|            | 5.4.5          | When no subsystem clock is used                                |                                           |  |  |

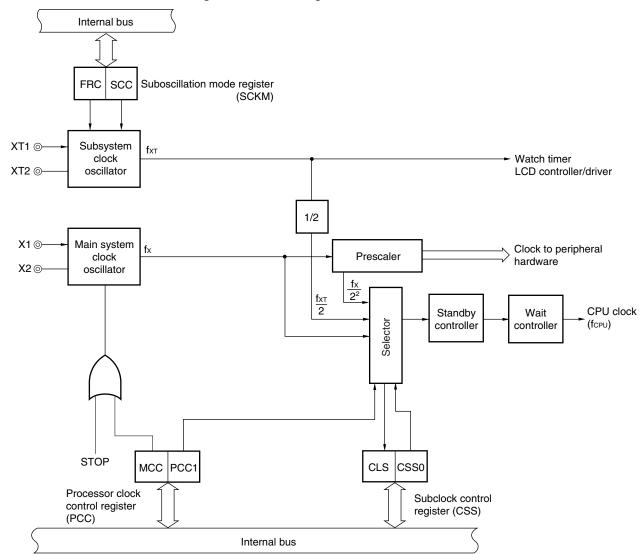

|            | 5.4.4          | Divider                                                        |                                           |  |  |

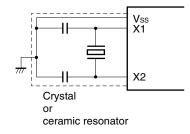

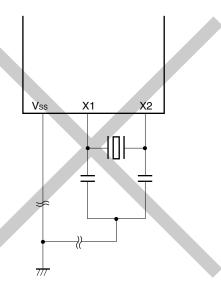

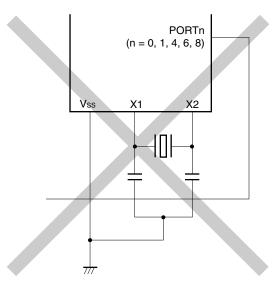

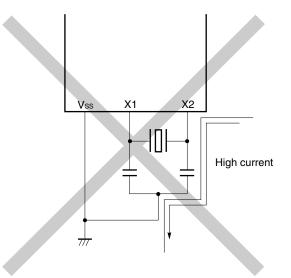

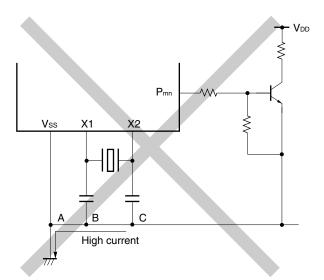

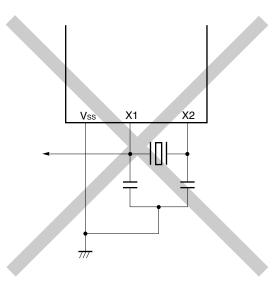

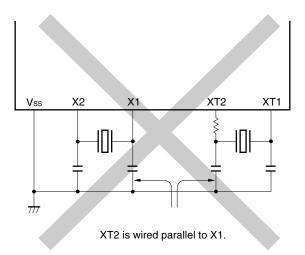

|            | 5.4.3          | Example of incorrect resonator connection                      |                                           |  |  |

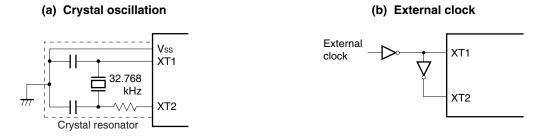

|            | 5.4.2          | Subsystem clock oscillator                                     |                                           |  |  |

|            | 5.4.1          | Main system clock oscillator                                   |                                           |  |  |

| 5.4        | •              | m Clock Oscillators                                            |                                           |  |  |

| 5.3        | _              | eters Controlling Clock Generator                              |                                           |  |  |

| 5.2        |                | Generator Configuration                                        |                                           |  |  |

| 5.1        |                | Generator Functions                                            | _                                         |  |  |

| CHAPT      |                | CLOCK GENERATOR                                                |                                           |  |  |

|            |                |                                                                |                                           |  |  |

|            | 4.4.3          | Arithmetic operation of I/O port                               |                                           |  |  |

|            | 4.4.2          | Reading from I/O port                                          |                                           |  |  |

|            | 4.4.1          | Writing to I/O port                                            |                                           |  |  |

| 4.4        | _              | Function Operation                                             |                                           |  |  |

| 4.3        |                | sters Controlling Port Function                                |                                           |  |  |

|            | 4.2.5          | Port 8                                                         |                                           |  |  |

|            | 4.2.4          | Port 6                                                         |                                           |  |  |

|            | 4.2.3          | Port 4                                                         |                                           |  |  |

|            | 4.2.1          | Port 1                                                         |                                           |  |  |

| T.6        | 4.2.1          | Port 0                                                         |                                           |  |  |

| 4.2        |                | Configuration                                                  |                                           |  |  |

| 4.1        | Port F         | -<br>unctions                                                  | 65                                        |  |  |

| CHAPT      | ER 4           | PORT FUNCTIONS                                                 | 65                                        |  |  |

|            | 3.4.7          | Stack addressing                                               | 64                                        |  |  |

|            | 3.4.6          | Based addressing                                               |                                           |  |  |

|            | 3.4.5          | Register indirect addressing                                   |                                           |  |  |

|            | 3.4.4          | Register addressing                                            |                                           |  |  |

|            | 3.4.3          | Special-function register (SFR) addressing                     |                                           |  |  |

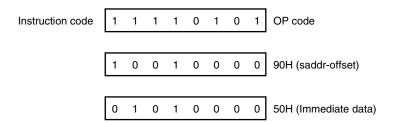

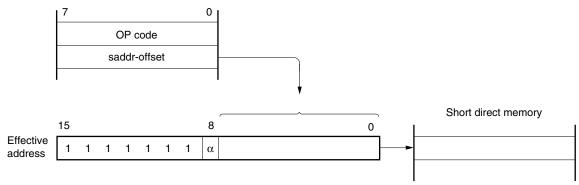

|            | 3.4.2          | Short direct addressing                                        |                                           |  |  |

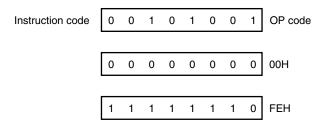

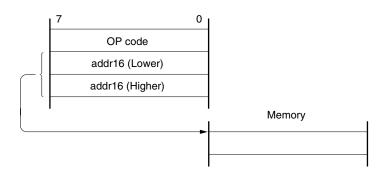

|            | 3.4.1          | Direct addressing                                              |                                           |  |  |

| 3.4        | -              | and Address Addressing                                         |                                           |  |  |

| 2.4        | 3.3.4          | Register addressing                                            |                                           |  |  |

|            | 3.3.3          | Table indirect addressing                                      |                                           |  |  |

|            | 3.3.2          | Immediate addressing                                           |                                           |  |  |

|            | 222            | Immediate addressing                                           | E7                                        |  |  |

| 6.3   | Registers Controlling 8-Bit Timers 30 and 40                      |      |  |

|-------|-------------------------------------------------------------------|------|--|

| 6.4   | Operation of 8-Bit Timers 30 and 40                               | 98   |  |

|       | 6.4.1 Operation as 8-bit timer counter                            | 98   |  |

|       | 6.4.2 Operation as 16-bit timer counter                           | 105  |  |

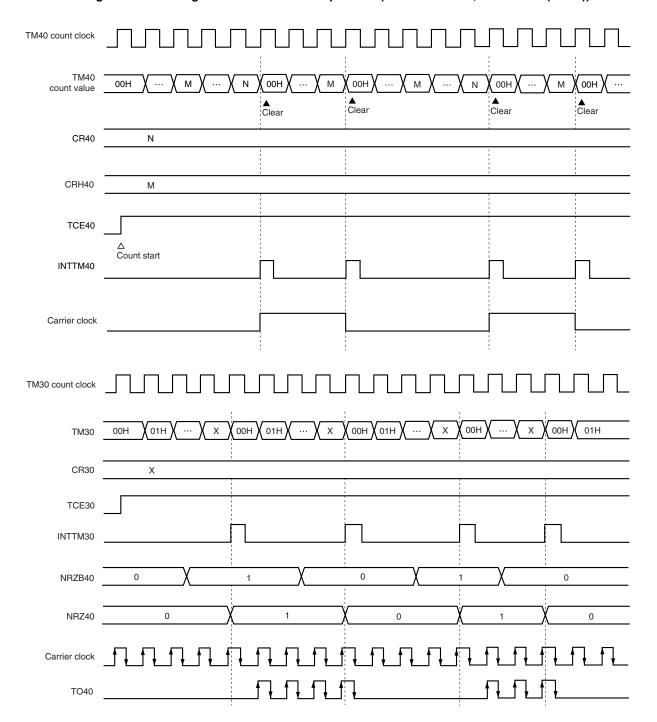

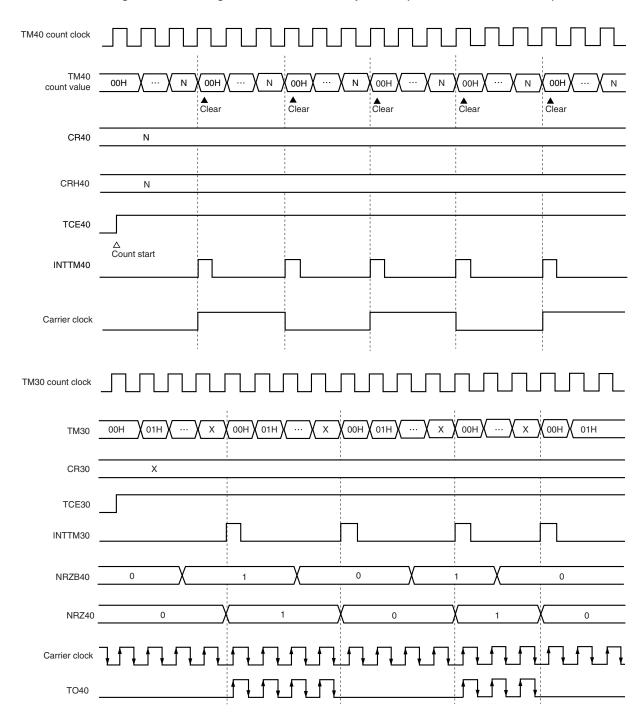

|       | 6.4.3 Operation as carrier generator                              | 109  |  |

|       | 6.4.4 Operation as PWM output (timer 40 only)                     | 113  |  |

| 6.5   | Notes on Using 8-Bit Timers 30 and 40                             | 115  |  |

| СНАРТ | ER 7 WATCH TIMER                                                  | 116  |  |

| 7.1   | Watch Timer Functions                                             | 116  |  |

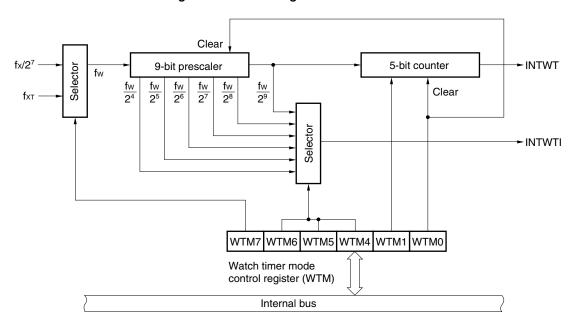

| 7.2   | Watch Timer Configuration                                         | 117  |  |

| 7.3   | Register Controlling Watch Timer                                  | 118  |  |

| 7.4   | Watch Timer Operation                                             | 119  |  |

|       | 7.4.1 Operation as watch timer                                    | 119  |  |

|       | 7.4.2 Operation as interval timer                                 | 119  |  |

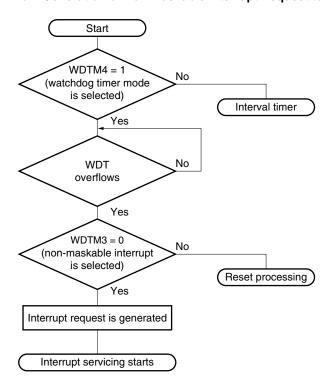

| CHAPT | ER 8 WATCHDOG TIMER                                               | 121  |  |

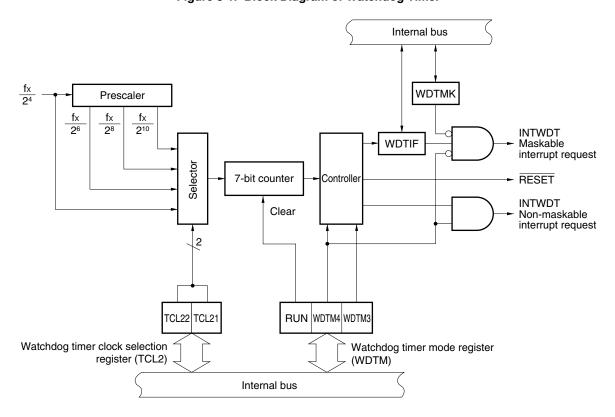

| 8.1   | Watchdog Timer Functions                                          | 121  |  |

| 8.2   | Watchdog Timer Configuration                                      | 122  |  |

| 8.3   | Registers Controlling Watchdog Timer                              | 123  |  |

| 8.4   | Watchdog Timer Operation                                          | 125  |  |

|       | 8.4.1 Operation as watchdog timer                                 | 125  |  |

|       | 8.4.2 Operation as interval timer                                 | 126  |  |

| СНАРТ | ER 9 8-BIT A/D CONVERTER                                          | 127  |  |

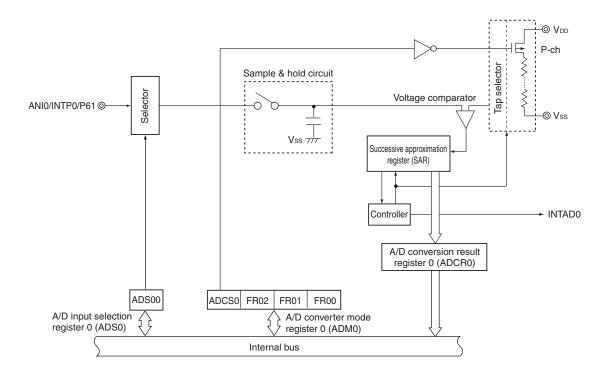

| 9.1   | Functions of 8-Bit A/D Converter                                  | 127  |  |

| 9.2   | Configuration of 8-Bit A/D Converter                              | 127  |  |

| 9.3   | Registers Controlling 8-Bit A/D Converter                         | 130  |  |

| 9.4   | 8-Bit A/D Converter Operation                                     | 132  |  |

|       | 9.4.1 Basic operation of 8-bit A/D converter                      | 132  |  |

|       | 9.4.2 Input voltage and conversion result                         | 133  |  |

|       | 9.4.3 Operation mode of 8-bit A/D converter                       | 134  |  |

| 9.5   | Cautions Related to 8-Bit A/D Converter                           | 135  |  |

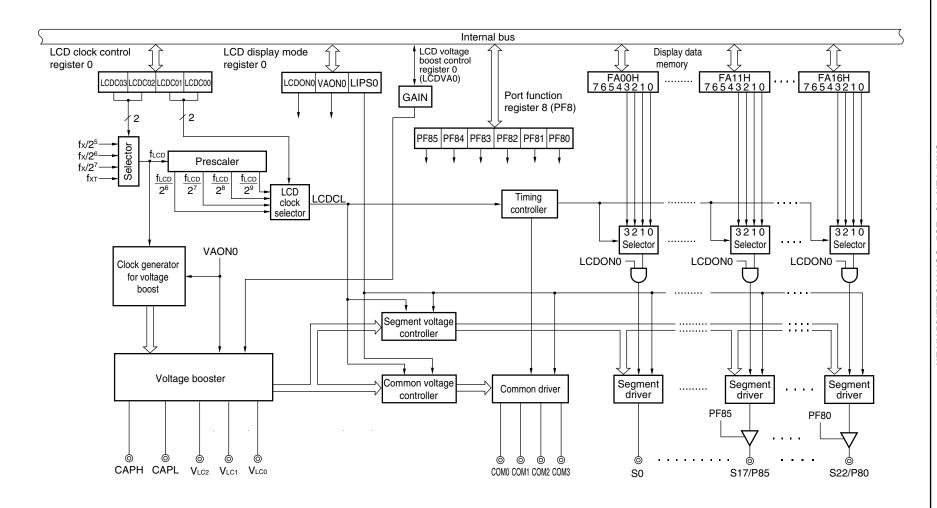

| CHAPT | ER 10 LCD CONTROLLER/DRIVER                                       | 139  |  |

| 10.1  | Functions of LCD Controller/Driver                                | 139  |  |

|       | Configuration of LCD Controller/Driver                            |      |  |

| 10.3  | Registers Controlling LCD Controller/Driver                       | 141  |  |

| 10.4  | Setting LCD Controller/Driver                                     |      |  |

|       | 10.4.1 Setting before starting display                            | 145  |  |

|       | 10.4.2 Setting until disabling display and stopping voltage boost | 145  |  |

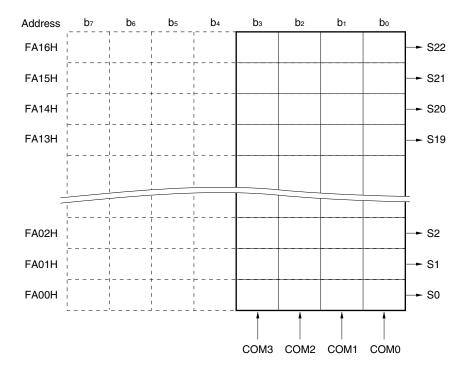

|       | LCD Display Data Memory                                           |      |  |

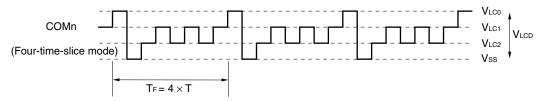

|       | Common and Segment Signals                                        |      |  |

| 10.7  | Display Modes                                                     |      |  |

|       | 10.7.1 Four-time-slice display example                            | 1/10 |  |

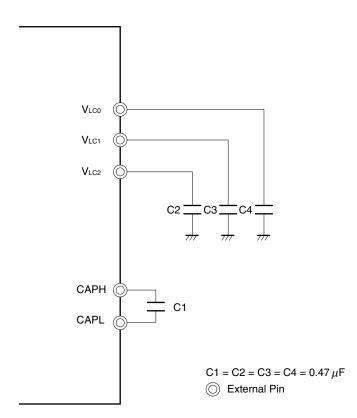

| 10.8   | Supplying LCD Drive Voltages VLC0, VLC1, and VLC2              | 152 |

|--------|----------------------------------------------------------------|-----|

| CHAPTI | ER 11 POWER-ON-CLEAR CIRCUIT                                   | 153 |

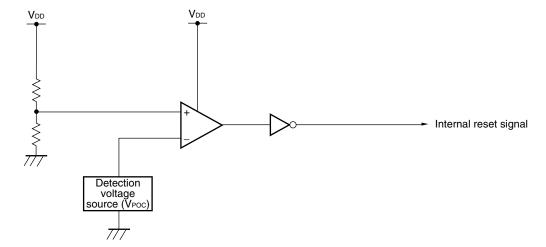

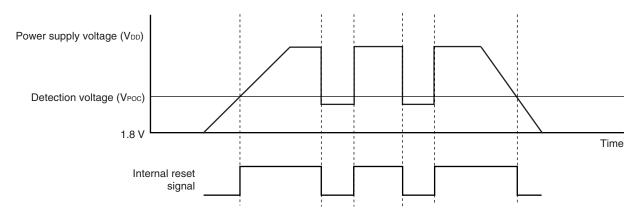

| 11.1   | Functions of Power-on-Clear Circuit                            | 153 |

| 11.2   | Configuration of Power-on-Clear Circuit                        | 153 |

| 11.3   | Power-on-Clear Circuit Operation                               | 154 |

| CHAPTI | ER 12 INTERRUPT FUNCTION                                       | 155 |

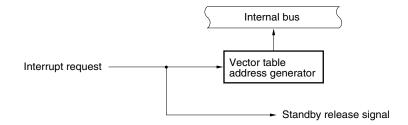

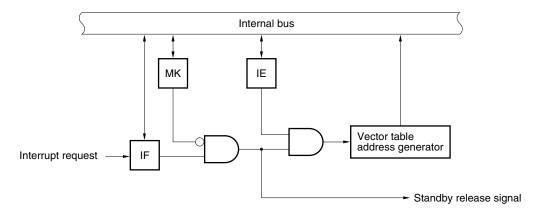

| 12.1   | Interrupt Types                                                | 155 |

| 12.2   | Interrupt Sources and Configuration                            | 155 |

| 12.3   | Registers Controlling Interrupt Function                       | 158 |

| 12.4   | Interrupt Servicing Operation                                  |     |

|        | 12.4.1 Non-maskable interrupt request acknowledgment operation | 162 |

|        | 12.4.2 Maskable interrupt request acknowledgment operation     | 164 |

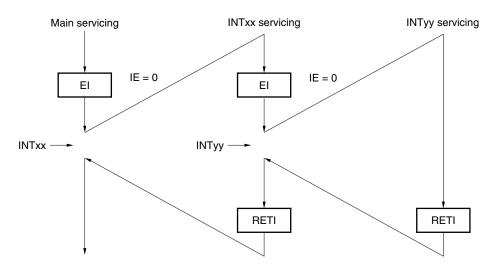

|        | 12.4.3 Multiple interrupt servicing                            | 165 |

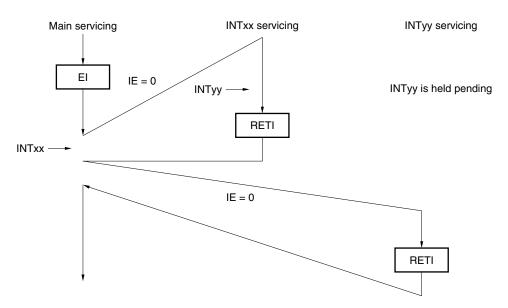

|        | 12.4.4 Putting interrupt requests on hold                      | 167 |

| CHAPTI | ER 13 STANDBY FUNCTION                                         | 168 |

| 13.1   | Standby Function and Configuration                             | 168 |

|        | 13.1.1 Standby function                                        | 168 |

|        | 13.1.2 Register controlling standby function                   | 169 |

| 13.2   | Standby Function Operation                                     | 170 |

|        | 13.2.1 HALT mode                                               | 170 |

|        | 13.2.2 STOP mode                                               | 173 |

| CHAPTI | ER 14 RESET FUNCTION                                           | 176 |

| CHAPTI | ER 15 <i>μ</i> PD78F9468                                       | 180 |

| 15.1   | Flash Memory Characteristics                                   | 182 |

|        | 15.1.1 Programming environment                                 | 182 |

|        | 15.1.2 Communication mode                                      | 183 |

|        | 15.1.3 On-board pin processing                                 | 185 |

|        | 15.1.4 Connection on flash memory writing adapter              | 188 |

| CHAPTI | ER 16 MASK OPTION                                              | 189 |

| CHAPTI | ER 17 INSTRUCTION SET                                          | 190 |

| 17.1   | Operation                                                      | 190 |

|        | 17.1.1 Operand identifiers and description methods             |     |

|        | 17.1.2 Description of "Operation" column                       |     |

|        | 17.1.3 Description of "Flag" column                            | 191 |

| 17.2   | Operation List                                                 |     |

| 17.3   | Instructions Listed by Addressing Type                         | 197 |

| CHAPTER      | R 18 ELECTRICAL SPECIFICATIONS                       | 200 |

|--------------|------------------------------------------------------|-----|

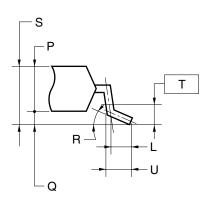

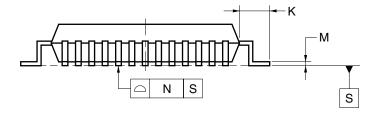

| CHAPTE       | R 19 PACKAGE DRAWING                                 | 211 |

| CHAPTE       | R 20 RECOMMENDED SOLDERING CONDITIONS                | 212 |

| APPENDI      | X A DEVELOPMENT TOOLS                                | 213 |

| A.1          | Software Package                                     | 215 |

|              | Language Processing Software                         |     |

| A.3          | Control Software                                     | 216 |

| A.4 I        | Flash Memory Writing Tools                           | 217 |

| <b>A.5</b> I | Debugging Tools (Hardware)                           | 217 |

| A.6 I        | Debugging Tools (Software)                           | 218 |

| A.7          | Cautions When Designing Target System                | 219 |

| APPENDI      | X B REGISTER INDEX                                   | 220 |

| B.1 I        | Register Index (Alphabetic Order of Register Name)   | 220 |

|              | Register Index (Alphabetic Order of Register Symbol) |     |

| APPENDI      | X C. REVISION HISTORY                                | 224 |

# LIST OF FIGURES (1/4)

| Figure | No.                                              | le Pa      | ıge |

|--------|--------------------------------------------------|------------|-----|

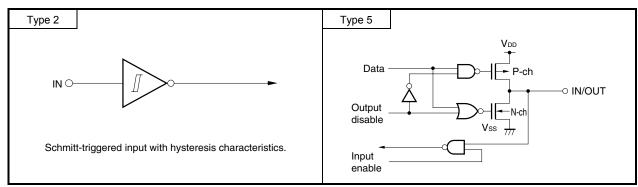

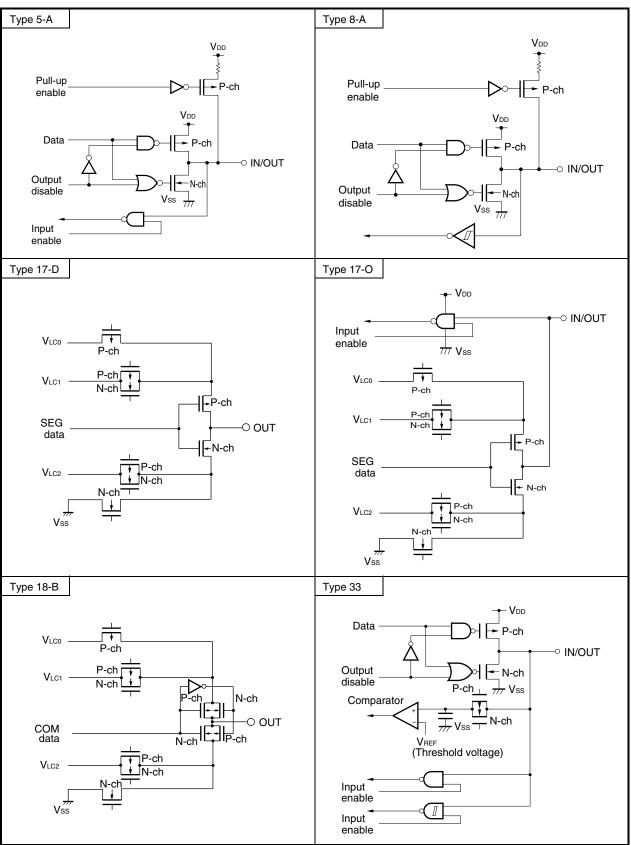

| 2-1    | I/O Circuit Types                                |            | 36  |

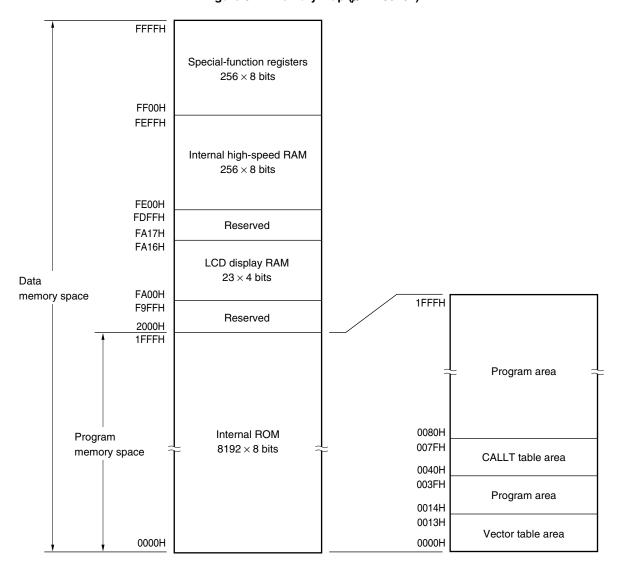

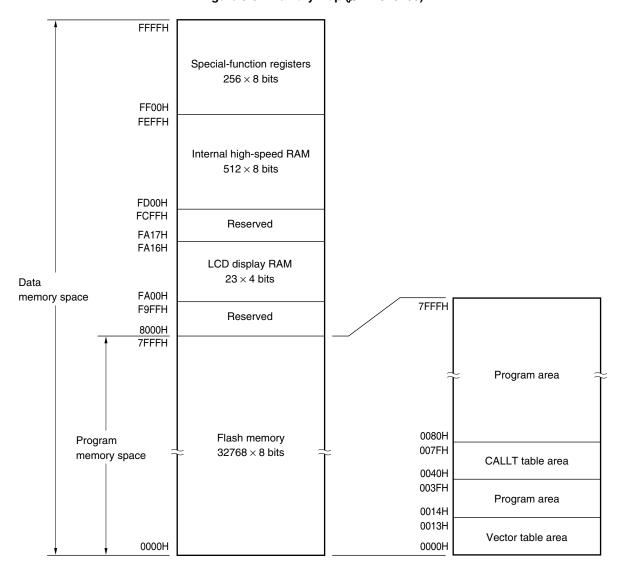

| 3-1    | Memory Map (μPD789462)                           |            | 38  |

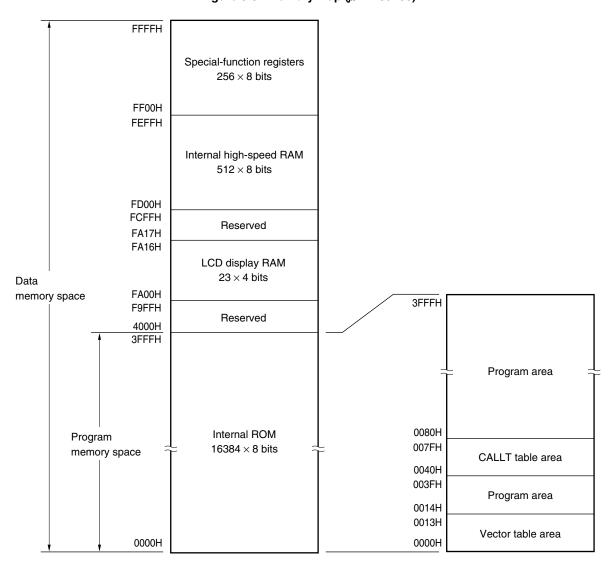

| 3-2    | Memory Map (μPD789464)                           |            | 39  |

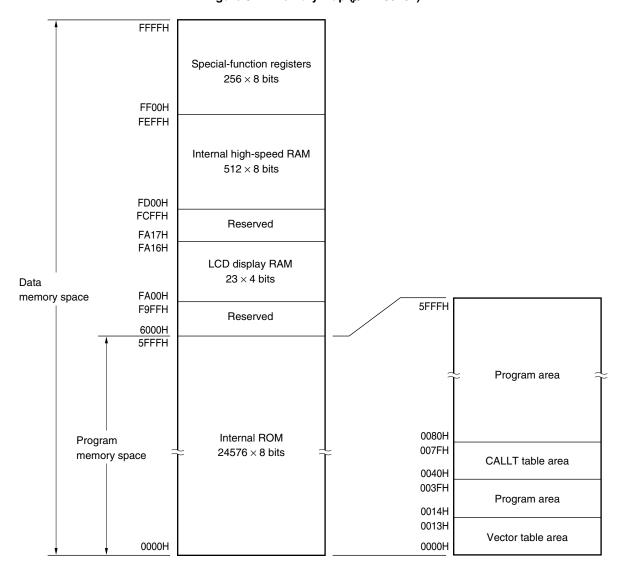

| 3-3    | Memory Map (μPD789466)                           |            | 40  |

| 3-4    | Memory Map (μPD789467)                           |            | 41  |

| 3-5    | Memory Map (μPD78F9468)                          |            | 42  |

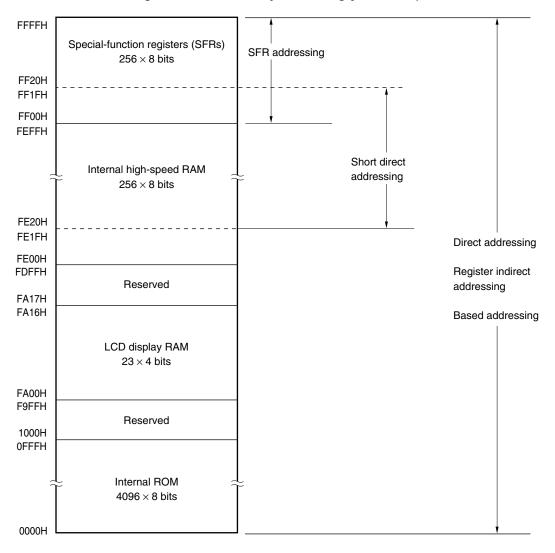

| 3-6    | Data Memory Addressing (µPD789462)               |            | 45  |

| 3-7    | Data Memory Addressing (µPD789464)               |            | 46  |

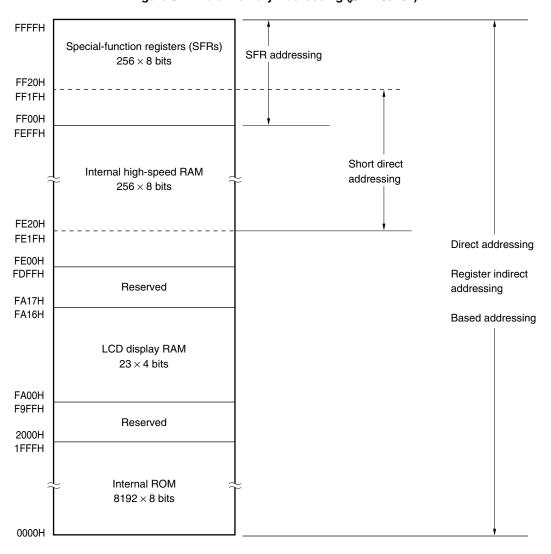

| 3-8    | Data Memory Addressing (µPD789466)               |            | 47  |

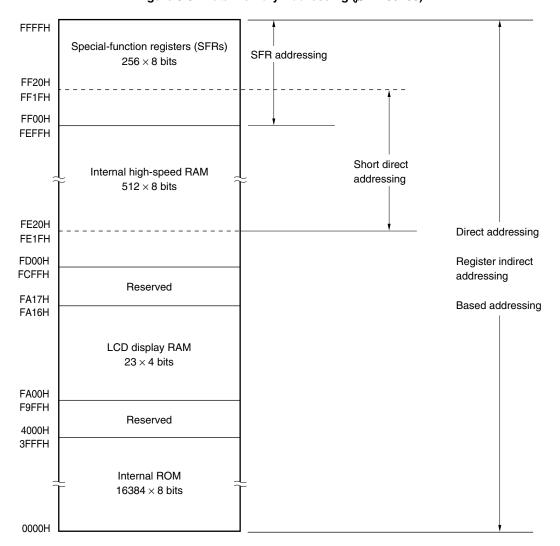

| 3-9    | Data Memory Addressing (µPD789467)               |            | 48  |

| 3-10   | Data Memory Addressing (µPD78F9468)              |            | 49  |

| 3-11   | Program Counter Configuration                    |            | 50  |

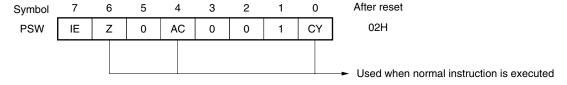

| 3-12   | Program Status Word Configuration                |            | 50  |

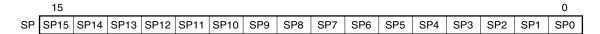

| 3-13   | Stack Pointer Configuration                      |            | 52  |

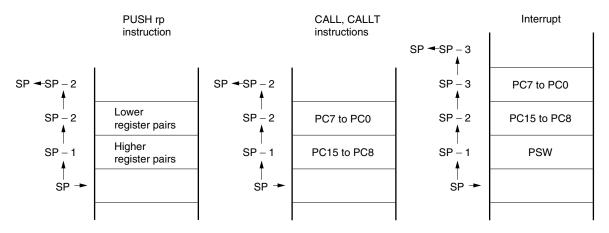

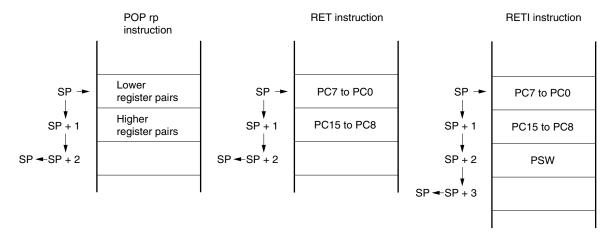

| 3-14   | Data to Be Saved to Stack Memory                 |            | 52  |

| 3-15   | Data to Be Restored from Stack Memory            |            | 52  |

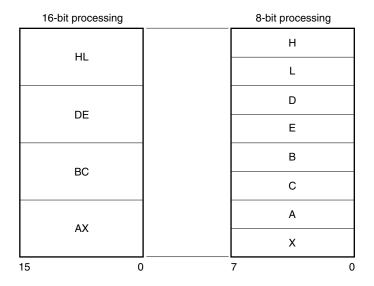

| 3-16   | General-Purpose Register Configuration           |            | 53  |

| 4-1    | Port Types                                       |            | 65  |

| 4-2    | Block Diagram of P00 to P03                      |            | 66  |

| 4-3    | Block Diagram of P10 and P11                     |            | 67  |

| 4-4    | Block Diagram of P40 to P43                      |            | 68  |

| 4-5    | Block Diagram of P60                             |            | 69  |

| 4-6    | Block Diagram of P61                             |            | 70  |

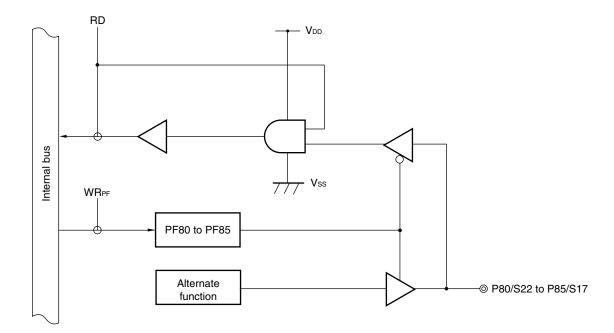

| 4-7    | Block Diagram of P80 to P85                      |            | 71  |

| 4-8    | Format of Port Mode Register                     |            | 72  |

| 4-9    | Format of Pull-up Resistor Option Register 0     |            | 73  |

| 4-10   | Format of Port Function Register 8               |            | 74  |

| 5-1    | Block Diagram of Clock Generator                 |            | 77  |

| 5-2    | Format of Processor Clock Control Register       |            | 78  |

| 5-3    | Format of Suboscillation Mode Register           |            | 79  |

| 5-4    | Format of Subclock Control Register              |            | 79  |

| 5-5    | External Circuit of Main System Clock Oscillator |            | 80  |

| 5-6    | External Circuit of Subsystem Clock Oscillator   |            | 81  |

| 5-7    | Examples of Incorrect Resonator Connection       |            | 82  |

| 5-8    | Example of Switching Between System Clock and    | CPLI Clock | 86  |

# LIST OF FIGURES (2/4)

| Figure | No. Title                                                                                           | Page |

|--------|-----------------------------------------------------------------------------------------------------|------|

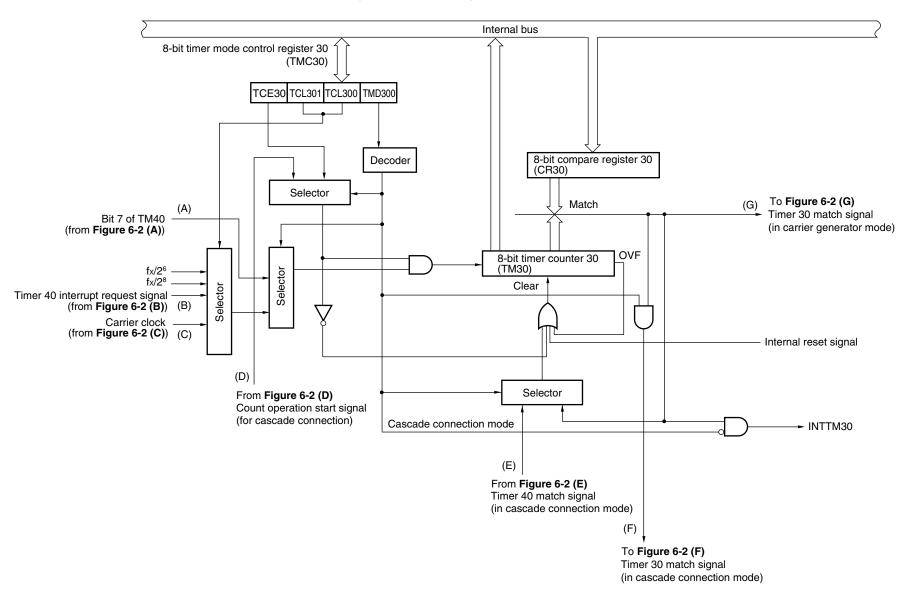

| 6-1    | Block Diagram of Timer 30                                                                           | 80   |

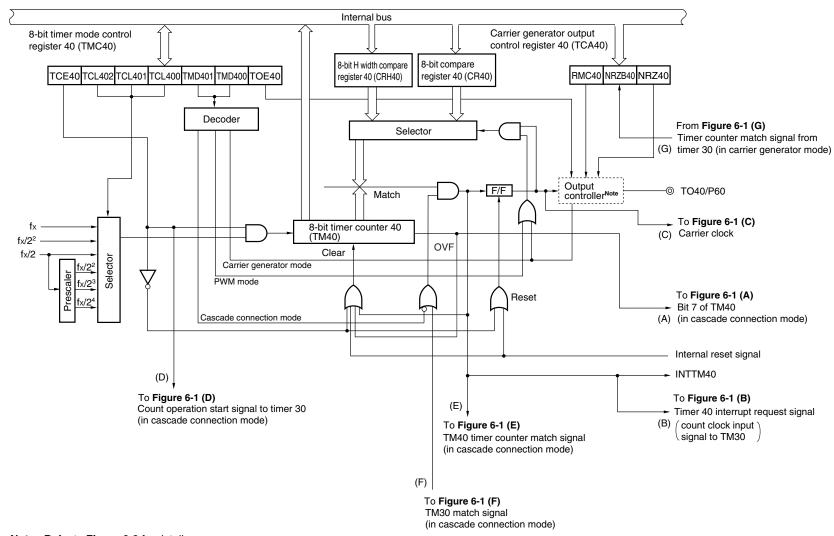

| 6-2    | Block Diagram of Timer 40                                                                           |      |

| 6-3    | Block Diagram of Output Controller (Timer 40)                                                       |      |

| 6-4    | Format of 8-Bit Timer Mode Control Register 30                                                      |      |

| 6-5    | Format of 8-Bit Timer Mode Control Register 40                                                      |      |

| 6-6    | Format of Carrier Generator Output Control Register 40                                              |      |

| 6-7    | Format of Port Mode Register 6                                                                      |      |

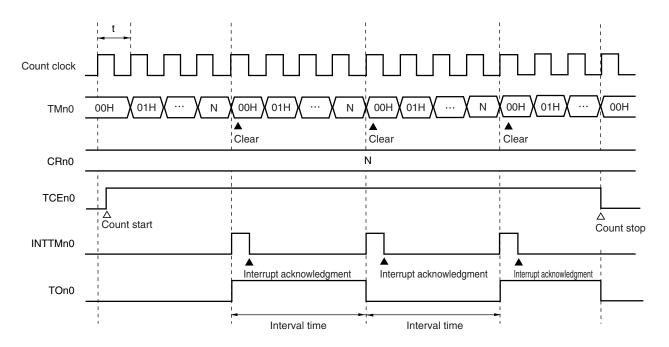

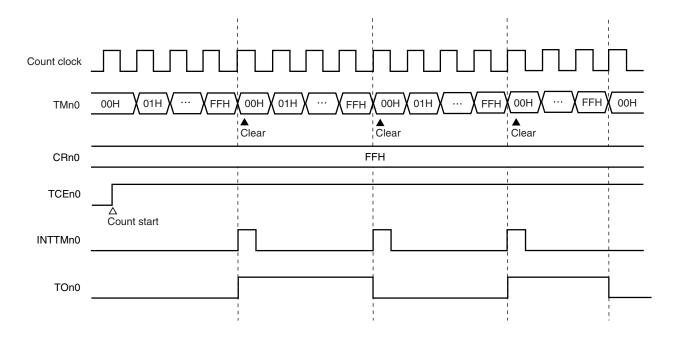

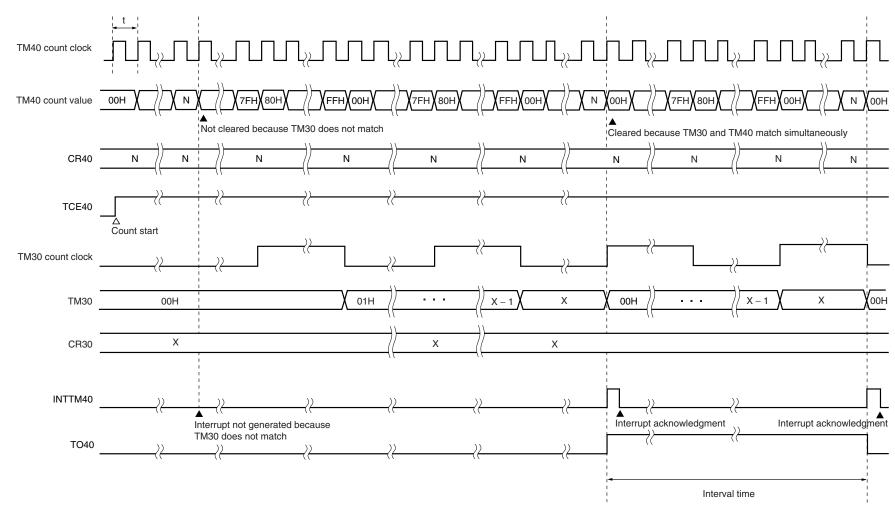

| 6-8    | Timing of Interval Timer Operation with 8-Bit Resolution (Basic Operation)                          |      |

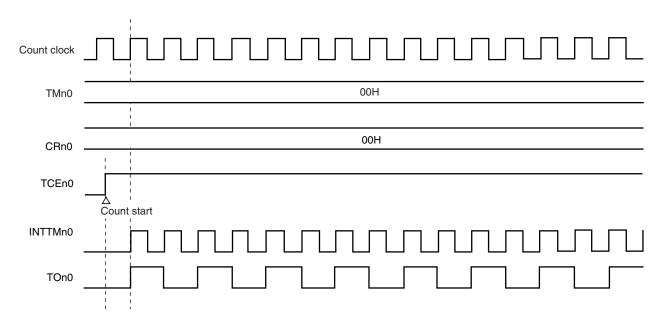

| 6-9    | Timing of Interval Timer Operation with 8-Bit Resolution (When CRn0 Is Set to 00H)                  |      |

| 6-10   | Timing of Interval Timer Operation with 8-Bit Resolution (When CRn0 Is Set to FFH)                  |      |

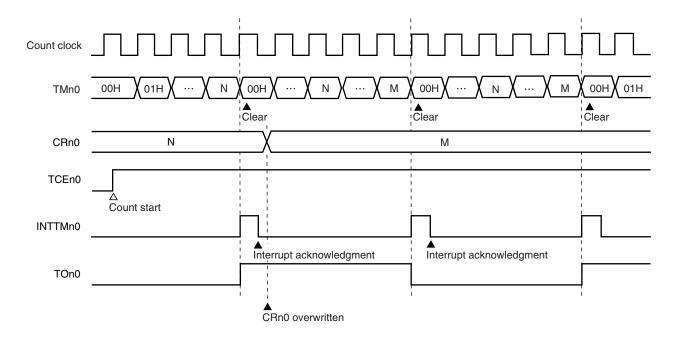

| 6-11   | Timing of Interval Timer Operation with 8-Bit Resolution (When CRn0 Changes from N to M (N < M))    |      |

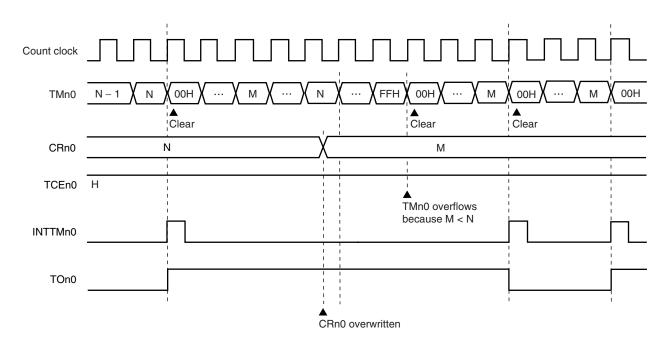

| 6-12   | Timing of Interval Timer Operation with 8-Bit Resolution (When CRn0 Changes from N to M (N > M))    |      |

| 6-13   | iming of Interval Timer Operation with 8-Bit Resolution (When Timer 40 Match Signal Is Selected for |      |

|        | Timer 30 Count Clock)                                                                               | 102  |

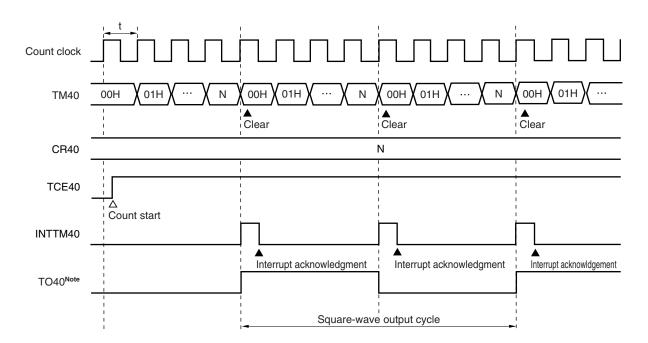

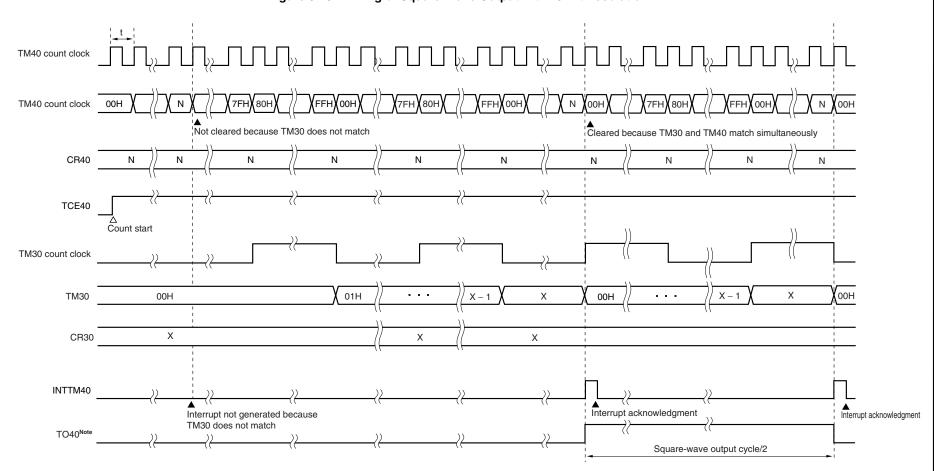

| 6-14   | Timing of Square-Wave Output with 8-Bit Resolution                                                  |      |

| 6-15   | Timing of Interval Timer Operation with 16-Bit Resolution                                           |      |

| 6-16   | Timing of Square-Wave Output with 16-Bit Resolution                                                 |      |

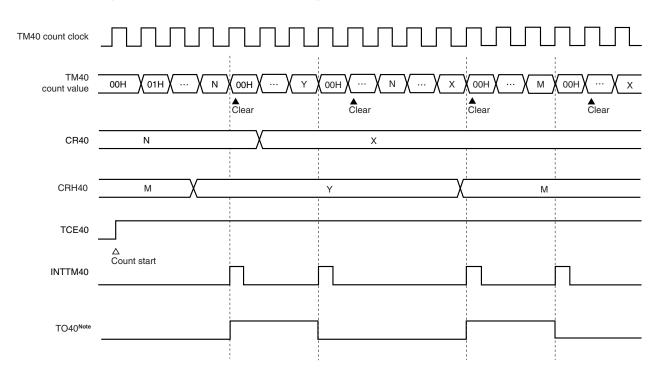

| 6-17   | Timing of Carrier Generator Operation (When CR40 = N, CRH40 = M (M > N))                            |      |

| 6-18   | Timing of Carrier Generator Operation (When CR40 = N, CRH40 = M (M < N))                            |      |

| 6-19   | Timing of Carrier Generator Operation (When CR40 = CRH40 = N)                                       | 112  |

| 6-20   | PWM Output Mode Timing (Basic Operation)                                                            |      |

| 6-21   | PWM Output Mode Timing (When CR40 and CRH40 Are Overwritten)                                        |      |

| 6-22   | Case in Which Error of 1.5 Clocks (Max.) Occurs                                                     |      |

| 7-1    | Block Diagram of Watch Timer                                                                        | 116  |

| 7-2    | Format of Watch Timer Mode Control Register                                                         | 118  |

| 7-3    | Watch Timer/Interval Timer Operation Timing                                                         | 120  |

| 8-1    | Block Diagram of Watchdog Timer                                                                     | 122  |

| 8-2    | Format of Watchdog Timer Clock Selection Register                                                   | 123  |

| 8-3    | Format of Watchdog Timer Mode Register                                                              | 124  |

| 9-1    | Block Diagram of 8-Bit A/D Converter                                                                | 128  |

| 9-2    | Format of A/D Converter Mode Register 0                                                             | 130  |

| 9-3    | Format of A/D Input Selection Register 0                                                            | 131  |

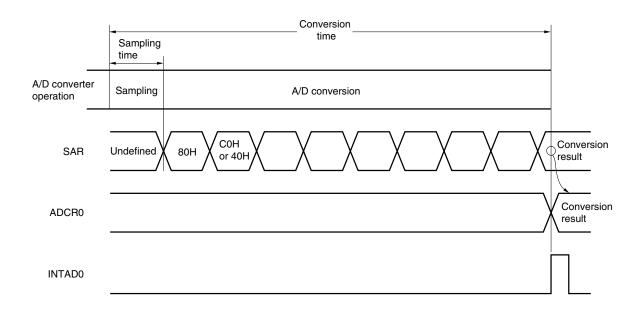

| 9-4    | Basic Operation of 8-Bit A/D Converter                                                              | 132  |

| 9-5    | Relationship Between Analog Input Voltage and A/D Conversion Result                                 | 133  |

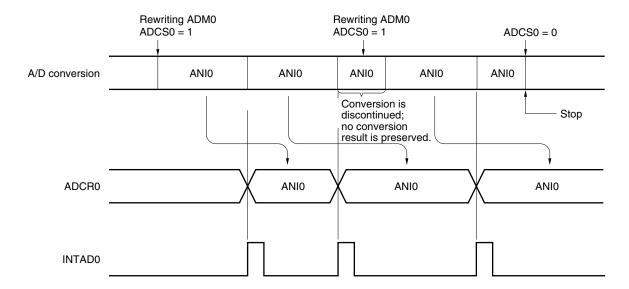

| 9-6    | Software-Started A/D Conversion                                                                     | 134  |

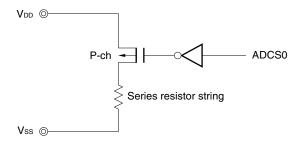

| 9-7    | How to Reduce Current Consumption in Standby Mode                                                   | 135  |

# LIST OF FIGURES (3/4)

| Figure | No. Title                                                                                        | Page |

|--------|--------------------------------------------------------------------------------------------------|------|

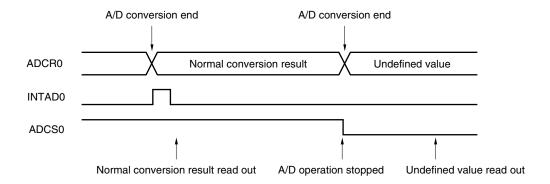

| 9-8    | Conversion Result Readout Timing (When Conversion Result Is Undefined Value)                     | 136  |

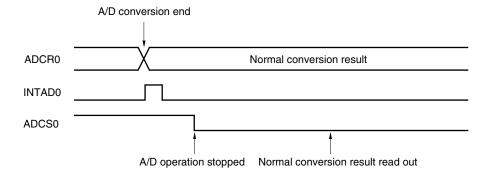

| 9-9    | Conversion Result Readout Timing (When Conversion Result Is Normal Value)                        | 136  |

| 9-10   | Analog Input Pin Handling                                                                        | 137  |

| 9-11   | A/D Conversion End Interrupt Request Generation Timing                                           | 138  |

| 10-1   | Block Diagram of LCD Controller/Driver                                                           | 140  |

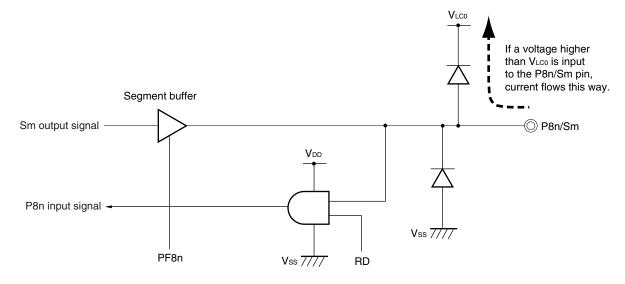

| 10-2   | Format of LCD Display Mode Register 0                                                            | 141  |

| 10-3   | Format of LCD Clock Control Register 0                                                           | 143  |

| 10-4   | Format of LCD Voltage Boost Control Register 0                                                   | 144  |

| 10-5   | Format of Port Function Register 8                                                               | 144  |

| 10-6   | Relationship Between LCD Display Data Memory Contents and Segment/Common Outputs                 | 146  |

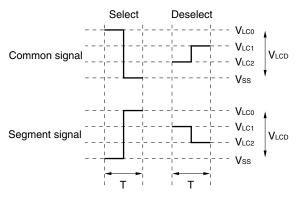

| 10-7   | Common Signal Waveforms                                                                          | 148  |

| 10-8   | Voltages and Phases of Common and Segment Signals                                                | 148  |

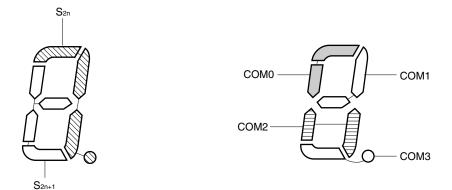

| 10-9   | Four-Time-Slice LCD Display Pattern and Electrode Connections                                    | 149  |

| 10-10  | Example of Connecting Four-Time-Slice LCD Panel                                                  | 150  |

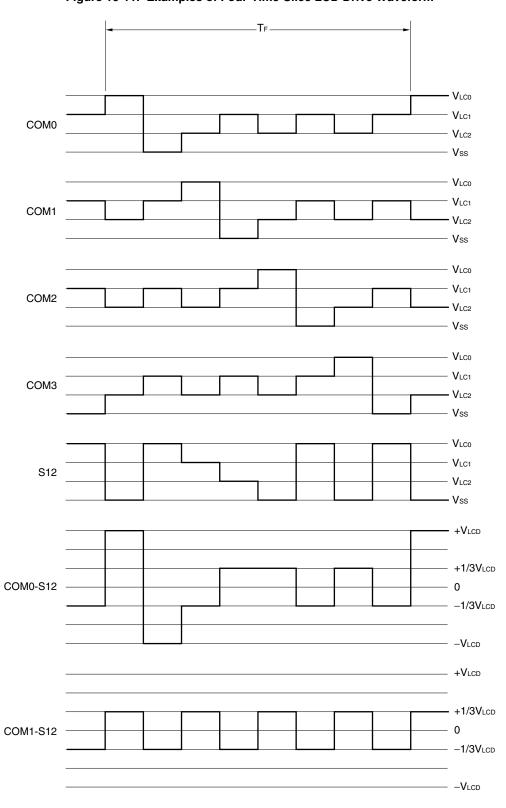

| 10-11  | Examples of Four-Time-Slice LCD Drive Waveform                                                   | 151  |

| 10-12  | Example of Pin Connection for LCD Driver                                                         | 152  |

| 11-1   | Block Diagram of Power-on-Clear Circuit                                                          | 153  |

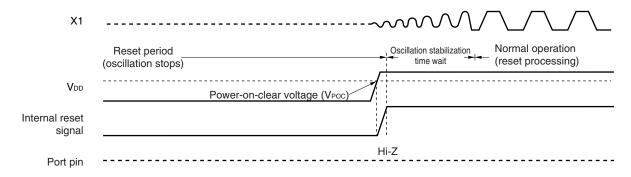

| 11-2   | Timing of Internal Reset Signal Generation of POC Circuit                                        | 154  |

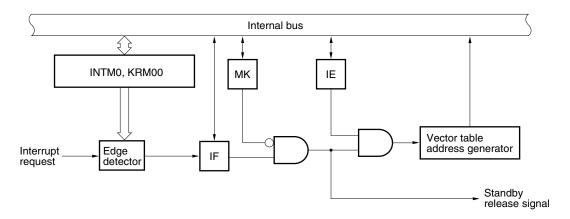

| 12-1   | Basic Configuration of Interrupt Function                                                        | 157  |

| 12-2   | Format of Interrupt Request Flag Register 0                                                      | 159  |

| 12-3   | Format of Interrupt Mask Flag Register 0                                                         | 159  |

| 12-4   | Format of External Interrupt Mode Register 0                                                     | 160  |

| 12-5   | Configuration of Program Status Word                                                             | 160  |

| 12-6   | Format of Key Return Mode Register 00                                                            | 161  |

| 12-7   | Block Diagram of Falling Edge Detector                                                           | 161  |

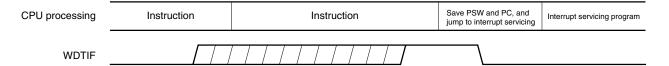

| 12-8   | Flow from Generation of Non-Maskable Interrupt Request to Acknowledgment                         | 163  |

| 12-9   | Timing of Non-Maskable Interrupt Request Acknowledgment                                          | 163  |

| 12-10  | Non-Maskable Interrupt Request Acknowledgment                                                    | 163  |

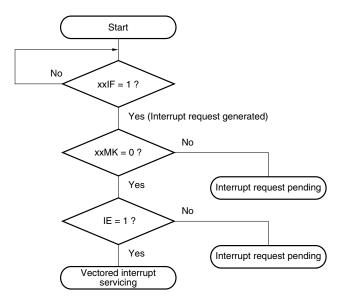

| 12-11  | Interrupt Request Acknowledgment Program Algorithm                                               | 164  |

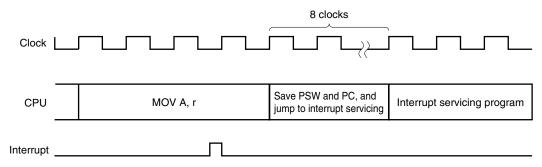

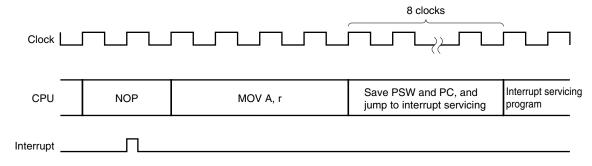

| 12-12  | Interrupt Request Acknowledgment Timing (Example: MOV A, r)                                      | 165  |

| 12-13  | Interrupt Request Acknowledgment Timing (When Interrupt Request Flag Is Generated in Final Clock |      |

|        | Under Execution)                                                                                 | 165  |

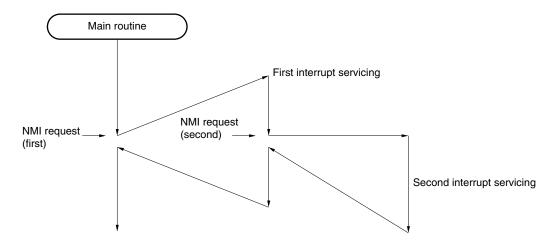

| 12-14  | Example of Multiple Interrupt Servicing                                                          | 166  |

| 13-1   | Format of Oscillation Stabilization Time Selection Register                                      | 169  |

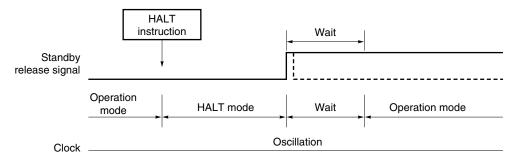

| 13-2   | Releasing HALT Mode by Interrupt                                                                 | 171  |

# LIST OF FIGURES (4/4)

| Figure     | No. Title                                                                   | Page |

|------------|-----------------------------------------------------------------------------|------|

|            |                                                                             |      |

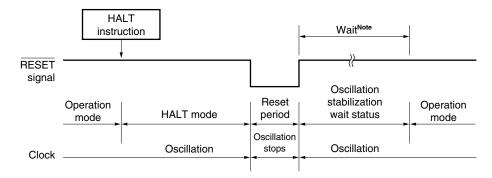

| 13-3       | Releasing HALT Mode by RESET Input                                          | 172  |

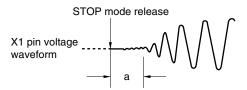

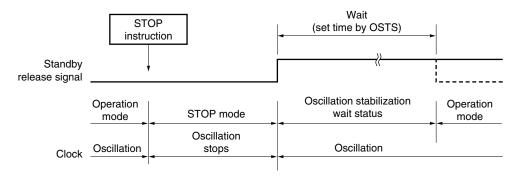

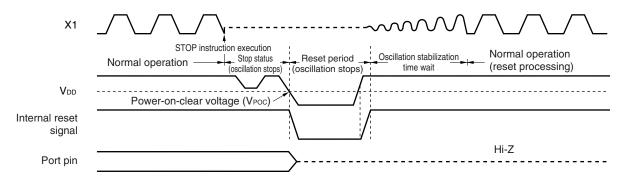

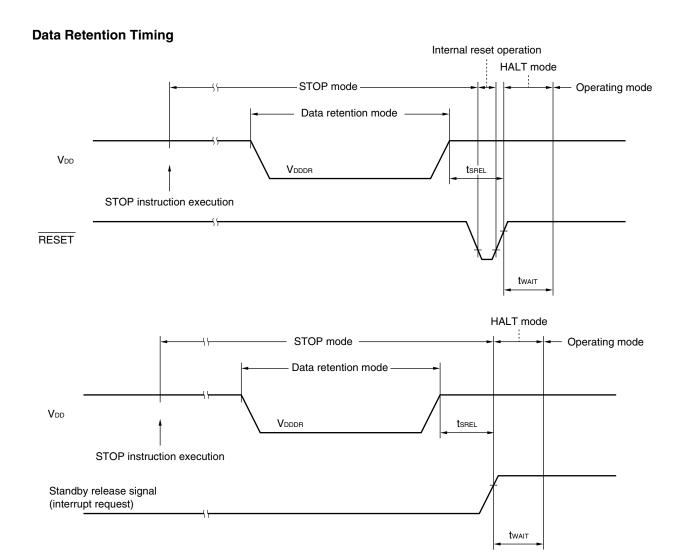

| 13-4       | Releasing STOP Mode by Interrupt                                            | 174  |

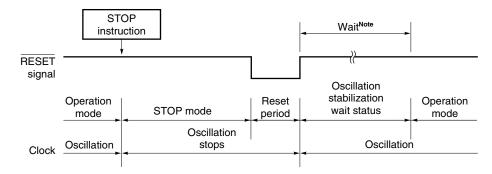

| 13-5       | Releasing STOP Mode by RESET Input                                          | 175  |

|            |                                                                             | 4=0  |

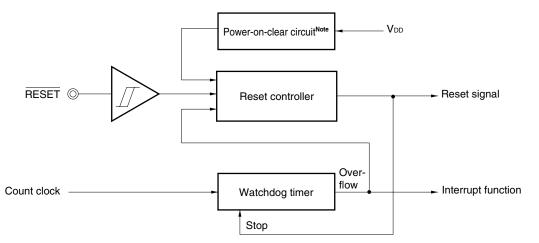

| 14-1       | Block Diagram of Reset Function                                             |      |

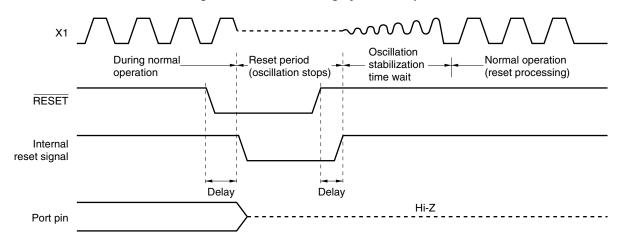

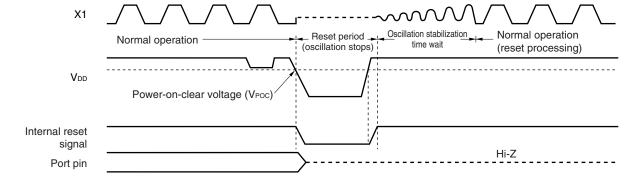

| 14-2       | Reset Timing by RESET Input                                                 |      |

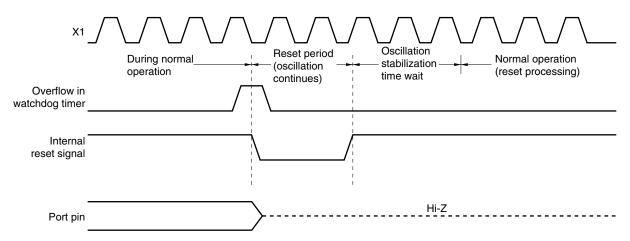

| 14-3       | Reset Timing by Overflow in Watchdog Timer                                  | 177  |

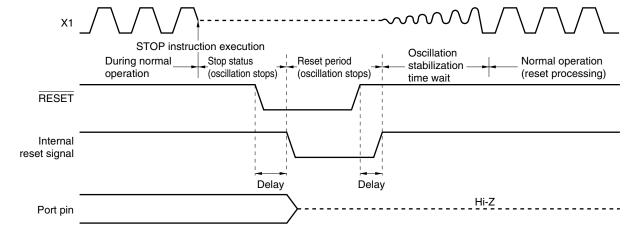

| 14-4       | Reset Timing by RESET Input in STOP Mode                                    | 177  |

| 14-5       | Reset Timing by Power-on Clear                                              | 178  |

|            |                                                                             |      |

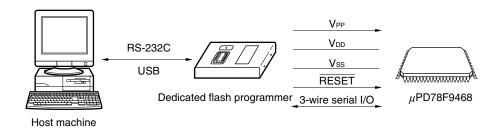

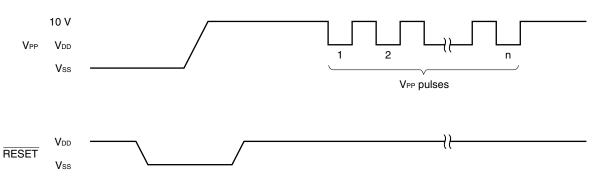

| 15-1       | Environment for Writing Program to Flash Memory                             | 182  |

| 15-2       | Communication Mode Selection Format                                         | 183  |

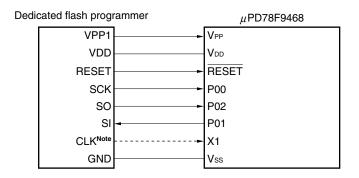

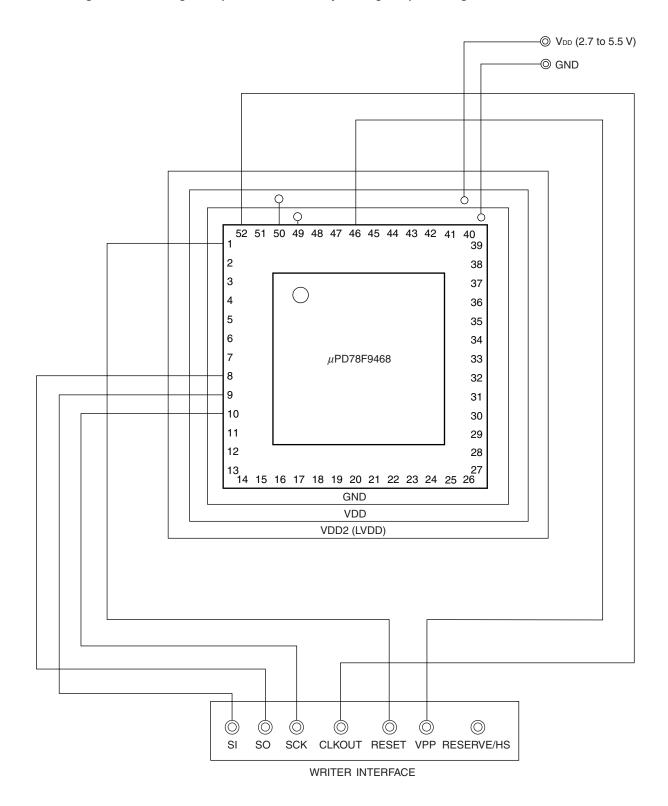

| 15-3       | Example of Connection with Dedicated Flash Programmer                       | 184  |

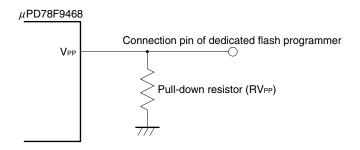

| 15-4       | VPP Pin Connection Example                                                  | 185  |

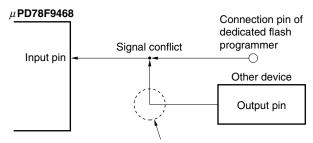

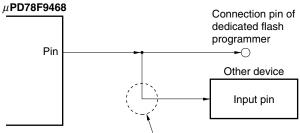

| 15-5       | Signal Conflict (Input Pin of Serial Interface)                             | 186  |

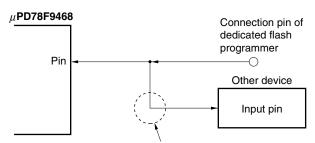

| 15-6       | Abnormal Operation of Other Device                                          | 186  |

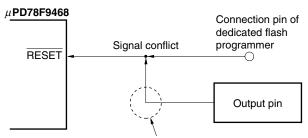

| 15-7       | Signal Conflict (Reset Pin)                                                 | 187  |

| 15-8       | Wiring Example of Flash Memory Writing Adapter Using 3-Wire Serial I/O Mode | 188  |

| A-1        | Development Tools                                                           | 214  |

| A-1<br>A-2 | ·                                                                           |      |

| H-2        | Condition Diagram of Connection to Target System                            | 219  |

# LIST OF TABLES (1/2)

| Table | No. Title                                                                    | Page |

|-------|------------------------------------------------------------------------------|------|

| 2-1   | Types of Pin I/O Circuits and Recommended Connection of Unused Pins          | 36   |

| 3-1   | Internal ROM Capacity                                                        | 43   |

| 3-2   | Vector Table                                                                 | 43   |

| 3-3   | Special-Function Registers                                                   | 55   |

| 4-1   | Port Functions                                                               | 65   |

| 4-2   | Configuration of Port                                                        | 66   |

| 4-3   | Port Mode Registers and Output Latch Settings When Using Alternate Functions | 73   |

| 5-1   | Configuration of Clock Generator                                             | 76   |

| 5-2   | Maximum Time Required for Switching CPU Clock                                | 85   |

| 6-1   | Operation Modes                                                              | 87   |

| 6-2   | Configuration of 8-Bit Timers 30 and 40                                      | 88   |

| 6-3   | Interval Time of Timer 30 (at fx = 5.0 MHz Operation)                        | 99   |

| 6-4   | Interval Time of Timer 40 (at fx = 5.0 MHz Operation)                        | 99   |

| 6-5   | Square-Wave Output Range of Timer 40 (at fx = 5.0 MHz Operation)             | 103  |

| 6-6   | Interval Time with 16-Bit Resolution (at fx = 5.0 MHz Operation)             | 105  |

| 6-7   | Square-Wave Output Range with 16-Bit Resolution (at fx = 5.0 MHz Operation)  | 107  |

| 7-1   | Interval Time of Interval Timer                                              | 117  |

| 7-2   | Configuration of Watch Timer                                                 | 117  |

| 7-3   | Interval Time of Interval Timer                                              | 119  |

| 8-1   | Program Loop Detection Time of Watchdog Timer                                | 121  |

| 8-2   | Interval Time of Watchdog Timer                                              | 121  |

| 8-3   | Configuration of Watchdog Timer                                              | 122  |

| 8-4   | Program Loop Detection Time of Watchdog Timer                                |      |

| 8-5   | Interval Time of Watchdog Timer                                              | 126  |

| 9-1   | Configuration of 8-Bit A/D Converter                                         | 127  |

| 10-1  | Maximum Number of Pixels                                                     | 139  |

| 10-2  | Configuration of LCD Controller/Driver                                       | 139  |

| 10-3  | Frame Frequencies (Hz)                                                       | 143  |

| 10-4  | COM Signals                                                                  | 147  |

| 10-5  | Select and Deselect Voltages (COM0 to COM3)                                  | 149  |

| 10-6  | Output Voltages of VLC0 to VLC2 Pins                                         | 152  |

# LIST OF TABLES (2/2)

| Table | No. Title                                                                    | Page  |

|-------|------------------------------------------------------------------------------|-------|

|       |                                                                              |       |

| 12-1  | Interrupt Source List                                                        | 156   |

| 12-2  | Flags Corresponding to Interrupt Request Signal Names                        | 158   |

| 12-3  | Time from Generation of Maskable Interrupt Request to Servicing              | 164   |

| 13-1  | Operation Statuses in HALT Mode                                              | 170   |

| 13-2  | Operation After Releasing HALT Mode                                          | 172   |

| 13-3  | Operation Statuses in STOP Mode                                              | 173   |

| 13-4  | Operation After Releasing STOP Mode                                          | 175   |

| 14-1  | Hardware Status After Reset                                                  | 179   |

| 15-1  | Differences Between $\mu$ PD78F9468 and Mask ROM Versions                    | 180   |

| 15-2  | Differences in LCD Controller/Driver of $\mu$ PD78F9468 and Mask ROM Version | on181 |

| 15-3  | Communication Mode List                                                      | 183   |

| 15-4  | Pin Connection List                                                          | 184   |

| 17-1  | Operand Identifiers and Description Methods                                  | 190   |

| 20-1  | Surface Mounting Type Soldering Conditions                                   | 212   |

#### **CHAPTER 1 GENERAL**

#### 1.1 Features

· ROM and RAM capacities

|             | Item | Program      | Memory | Data Memory                |                 |  |  |  |

|-------------|------|--------------|--------|----------------------------|-----------------|--|--|--|

| Part Number |      | (RO          | M)     | Internal High-Speed<br>RAM | LCD Display RAM |  |  |  |

| μPD789462   |      | Mask ROM     | 4 KB   | 256 bytes                  | 23 × 4 bits     |  |  |  |

| μPD789464   |      |              | 8 KB   |                            |                 |  |  |  |

| μPD789466   |      |              | 16 KB  | 512 bytes                  |                 |  |  |  |

| μPD789467   |      |              | 24 KB  |                            |                 |  |  |  |

| μPD78F9468  |      | Flash memory | 32 KB  |                            |                 |  |  |  |

- Minimum instruction execution time can be changed from high-speed (0.4  $\mu$ s: @ 5.0 MHz operation with main system clock) to ultra-low-speed (122  $\mu$ s: @ 32.768 kHz operation with subsystem clock)

- I/O ports: 18

- 8-bit resolution A/D converter: 1 channel

- Timer: 4 channels

- 8-bit timer: 2 channelsWatch timer: 1 channelWatchdog timer: 1 channel

- LCD controller/driver (on-chip voltage booster)

Segment signals: 23, common signals: 4

- Vectored interrupt sources: 9

- On-chip power-on clear circuit (mask option for mask ROM versions)

- Power supply voltage:  $V_{DD} = 1.8 \text{ to } 5.5 \text{ V}^{\text{Note}}$

- Operating ambient temperature: T<sub>A</sub> = -40 to +85°C

Note For mask ROM versions when the use of the POC circuit is selected or for flash memory versions, the minimum value of the operation power supply voltage is the POC detection voltage (1.9  $\pm$ 0.1 V).

#### 1.2 Applications

Remote controllers, healthcare equipment, etc.

# 1.3 Ordering Information

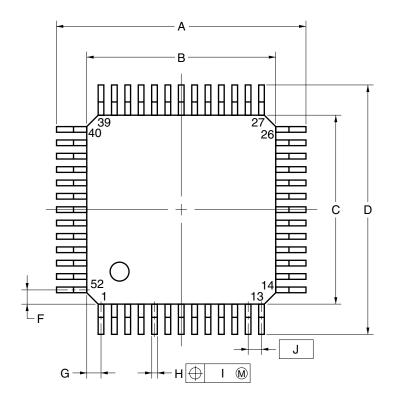

| Part Number                              | Package                                | Internal ROM |

|------------------------------------------|----------------------------------------|--------------|

| μPD789462GB-×××-8ET                      | 52-pin plastic LQFP (10 $\times$ 10)   | Mask ROM     |

| $\mu$ PD789464GB- $\times$ $\times$ -8ET | 52-pin plastic LQFP (10 $\times$ 10)   | Mask ROM     |

| $\mu$ PD789466GB- $\times$ $\times$ -8ET | 52-pin plastic LQFP (10 $\times$ 10)   | Mask ROM     |

| $\mu$ PD789467GB- $\times$ $\times$ -8ET | 52-pin plastic LQFP ( $10 \times 10$ ) | Mask ROM     |

| $\mu$ PD78F9468GB-8ET                    | 52-pin plastic LQFP (10 $\times$ 10)   | Flash memory |

**Remark** ××× indicates ROM code suffix.

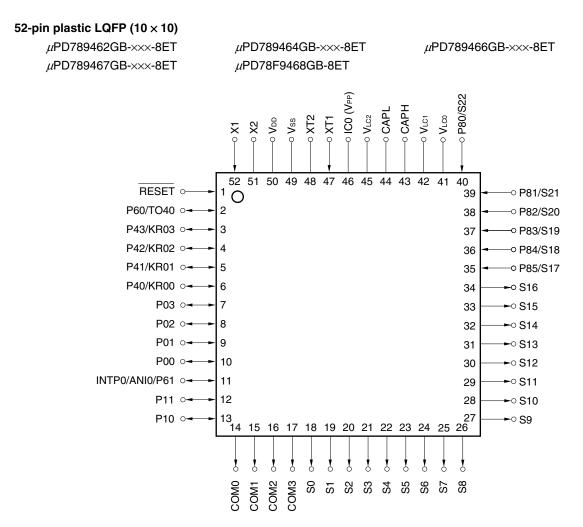

# 1.4 Pin Configuration (Top View)

Caution Connect the IC0 (Internally Connected) pin directly to Vss.

**Remark** The parenthesized values apply to the  $\mu$ PD78F9468.

#### **CHAPTER 1 GENERAL**

ANI0: Analog input

CAPH, CAPL: LCD power supply capacitance

control

COM0 to COM3: Common output

IC0: Internally connected

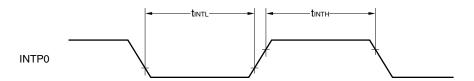

INTP0: External interrupt input

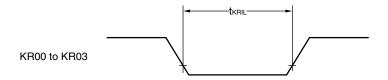

KR00 to KR03: Key return

P00 to P03: Port 0

P10, P11: Port 1

P40 to P43: Port 4

P60, P61: Port 6

P80 to P85: Port 8

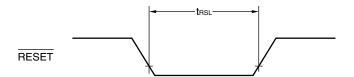

RESET: Reset

S0 to S22: Segment output

TO40: Timer output

VDD: Power supply

$V_{\text{LC0}}\,\text{to}\,\,V_{\text{LC2}}\text{:}\qquad \text{Power supply for LCD}$

VPP: Programming power supply

Vss: Ground

X1, X2: Crystal (main system clock)XT1, XT2: Crystal (subsystem clock)

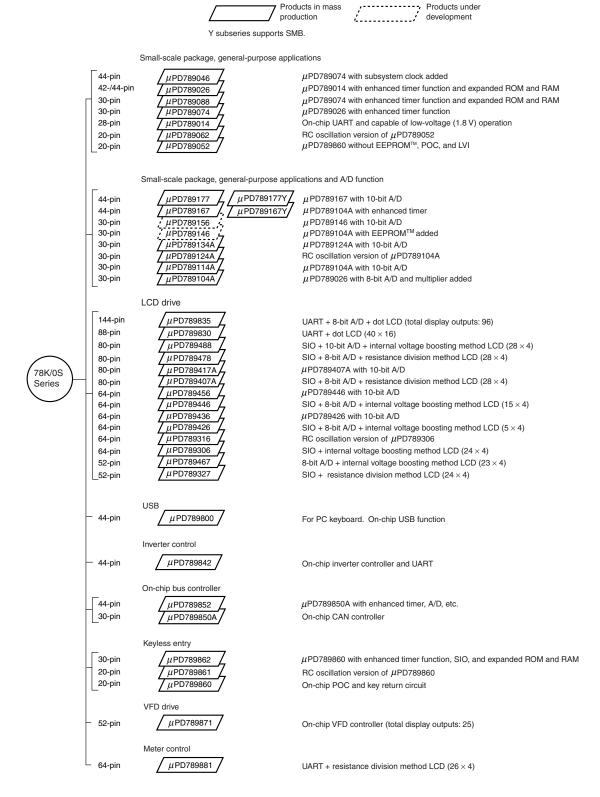

#### 1.5 78K/0S Series Lineup

The products in the 78K/0S Series are listed below. The names enclosed in boxes are subseries names.

**Remark** VFD (Vacuum Fluorescent Display) is referred to as FIP™ (Fluorescent Indicator Panel) in some documents, but the functions of the two are the same.

The major functional differences among the subseries are listed below.

# Series for General-Purpose Applications and LCD Drive

|                      | Function   | ROM            |       | Tir    | mer   |      |      | 10-Bit | Serial Interface | I/O | V <sub>DD</sub>       | Remarks                |

|----------------------|------------|----------------|-------|--------|-------|------|------|--------|------------------|-----|-----------------------|------------------------|

| Subseries            |            | Capacity       | 8-Bit | 16-Bit | Watch | WDT  | A/D  | A/D    |                  |     | MIN.Value             |                        |

| Small-               | μPD789046  | 16 KB          | 1 ch  | 1 ch   | 1 ch  | 1 ch | _    | _      | 1 ch (UART: 1ch) | 34  | 1.8 V                 | -                      |

| scale                | μPD789026  | 4 KB to 16 KB  |       |        | -     |      |      |        |                  |     |                       |                        |

| package,<br>general- | μPD789088  | 16 KB to 32 KB | 3 ch  |        |       |      |      |        |                  | 24  |                       |                        |

| purpose              | μPD789074  | 2 KB to 8 KB   | 1 ch  |        |       |      |      |        |                  |     |                       |                        |

| applica-<br>tions    | μPD789014  | 2 KB to 4 KB   | 2 ch  | _      |       |      |      |        |                  | 22  |                       |                        |

| tions                | μPD789062  | 4 KB           |       |        |       |      |      |        | -                | 14  |                       | RC-oscillation version |

|                      | μPD789052  |                |       |        |       |      |      |        |                  |     |                       | _                      |

| Small-               | μPD789177  | 16 KB to 24 KB | 3 ch  | 1 ch   | 1 ch  | 1ch  | _    | 8 ch   | 1 ch (UART: 1ch) | 31  | 1.8 V                 | -                      |

| scale<br>package,    | μPD789167  |                |       |        |       |      | 8 ch | _      |                  |     |                       |                        |

| general-             | μPD789156  | 8 KB to 16 KB  | 1 ch  |        | -     |      | _    | 4 ch   |                  | 20  |                       | On-chip                |

| purpose              | μPD789146  |                |       |        |       |      | 4 ch | _      |                  |     |                       | EEPROM                 |

| applica-<br>tions +  | μPD789134A | 2 KB to 8 KB   |       |        |       |      | _    | 4 ch   |                  |     |                       | RC-oscillation         |

| A/D                  | μPD789124A |                |       |        |       |      | 4 ch | _      |                  |     |                       | version                |

| converter            | μPD789114A |                |       |        |       |      | _    | 4 ch   |                  |     |                       | -                      |

|                      | μPD789104A |                |       |        |       |      | 4 ch | _      |                  |     |                       |                        |

| LCD                  | μPD789835  | 24 KB to 60 KB | 6 ch  | _      | 1 ch  | 1 ch | 3 ch | _      | 1 ch (UART: 1ch) | 37  | 1.8 V <sup>Note</sup> | Dot LCD                |

| drive                | μPD789830  | 24 KB          | 1 ch  | 1 ch   |       |      | _    |        |                  | 30  | 2.7 V                 | supported              |

|                      | μPD789488  | 32 KB to 48 KB | 3 ch  |        |       |      |      | 8 ch   | 2 ch (UART: 1ch) | 45  | 1.8 V                 | _                      |

|                      | μPD789478  | 24 KB to 48 KB |       |        |       |      | 8 ch | _      |                  |     |                       |                        |

|                      | μPD789417A | 12 KB to 24 KB |       |        |       |      | _    | 7 ch   | 1 ch (UART: 1ch) | 43  |                       |                        |

|                      | μPD789407A |                |       |        |       |      | 7 ch | _      |                  |     |                       |                        |

|                      | μPD789456  | 12 KB to 16 KB | 2 ch  |        |       |      | _    | 6 ch   |                  | 30  |                       |                        |

|                      | μPD789446  |                |       |        |       |      | 6 ch | _      |                  |     |                       |                        |

|                      | μPD789436  |                |       |        |       |      | _    | 6 ch   |                  | 40  |                       |                        |

|                      | μPD789426  |                |       |        |       |      | 6 ch | _      |                  |     |                       |                        |

|                      | μPD789316  | 8 KB to 16 KB  |       |        |       |      | _    |        | 2 ch (UART: 1ch) | 23  |                       | RC-oscillation version |

|                      | μPD789306  |                |       |        |       |      |      |        |                  |     |                       |                        |

|                      | μPD789467  | 4 KB to 24 KB  |       | _      |       |      | 1 ch |        | _                | 18  |                       |                        |

|                      | μPD789327  |                |       |        |       |      | _    |        | 1 ch             | 21  |                       |                        |

Note Flash memory version: 3.0 V

# **Series for ASSP**

|                  | Function   | ROM           |       | Tir    | mer   |      | 8-Bit | 10-Bit | Serial Interface  | I/O | V <sub>DD</sub>         | Remarks                                         |

|------------------|------------|---------------|-------|--------|-------|------|-------|--------|-------------------|-----|-------------------------|-------------------------------------------------|

| Subserie         | s          | Capacity      | 8-Bit | 16-Bit | Watch | WDT  | A/D   | A/D    |                   |     | MIN.Value               |                                                 |

| USB              | μPD789800  | 8 KB          | 2 ch  | _      | -     | 1 ch | -     | ı      | 2 ch (USB: 1ch)   | 31  | 4.0 V                   | -                                               |

| Inverter control | μPD789842  | 8 KB to 16 KB | 3 ch  | Note 1 | 1 ch  | 1 ch | 8 ch  | ı      | 1 ch (UART: 1ch)  | 30  | 4.0 V                   | -                                               |

| On-chip<br>bus   | μPD789852  | 24 KB to 32KB | 3 ch  | 1 ch   | -     | 1 ch | -     | 8 ch   | 3 ch (UART: 2 ch) | 31  | 4.0 V                   | _                                               |

| controller       | μPD789850A | 16 KB         | 1 ch  |        |       |      | 4 ch  | 1      | 2 ch (UART: 1ch)  | 18  |                         |                                                 |

| Keyless<br>entry | μPD789861  | 4 KB          | 2 ch  | -      |       | 1 ch | -     | -      | _                 | 14  | 1.8 V                   | RC-oscillation<br>version,<br>on-chip<br>EEPROM |

|                  | μPD789860  |               |       |        |       |      |       |        |                   |     |                         | On-chip                                         |

|                  | μPD789862  | 16 KB         | 1 ch  | 2 ch   |       |      |       |        | 1 ch (UART: 1ch)  | 22  |                         | EEPROM                                          |

| VFD<br>drive     | μPD789871  | 4 KB to 8 KB  | 3 ch  | _      | 1 ch  | 1 ch | ı     | ı      | 1 ch              | 33  | 2.7 V                   | -                                               |

| Meter<br>control | μPD789881  | 16 KB         | 2 ch  | 1 ch   | -     | 1 ch | -     | -      | 1 ch (UART: 1 ch) | 28  | 2.7 V <sup>Note 2</sup> | -                                               |

Notes 1. 10-bit timer: 1 channel

2. Flash memory version: 3.0 V

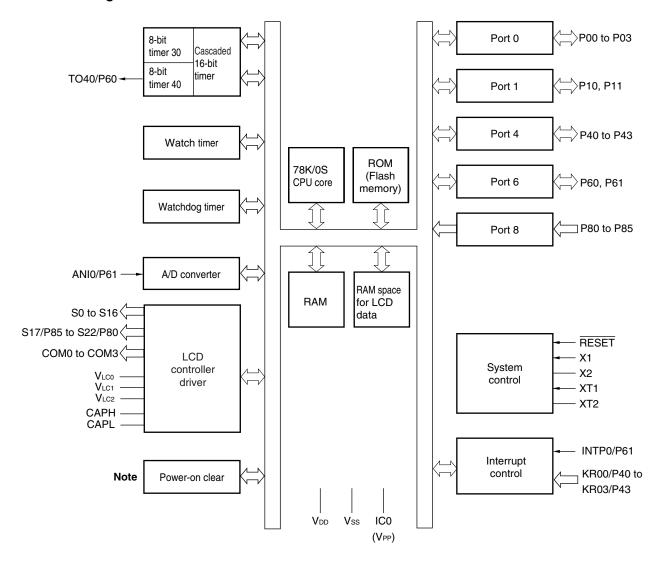

#### 1.6 Block Diagram

- ★ Note Only when use of the POC circuit is selected by a mask option in the case of the mask ROM version (µPD789462, 789464, 789466, and 789467).

- Remarks 1. The internal ROM and RAM capacities vary depending on the product.

- **2.** The parenthesized values apply to the  $\mu$ PD78F9468.

#### 1.7 Overview of Functions

|                       | Part Number           | μPD789462                                                                                                      | μPD789464                  | μPD789466          | μPD789467   | μPD78F9468 |  |  |

|-----------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|-------------|------------|--|--|

| Item                  |                       |                                                                                                                |                            |                    |             |            |  |  |

| Internal memory       | ROM                   | Mask ROM                                                                                                       | Mask ROM F                 |                    |             |            |  |  |

|                       |                       | 4 KB                                                                                                           | 8 KB                       | 16 KB              | 24 KB       | 32 KB      |  |  |

|                       | High-speed RAM        | 256 bytes                                                                                                      |                            | 512 bytes          |             |            |  |  |

|                       | LCD display RAM       | 23 × 4 bits                                                                                                    |                            |                    |             |            |  |  |

| Main system clock (os | scillation frequency) | Ceramic/crysta                                                                                                 | l oscillation (1.0 to      | 5.0 MHz)           |             |            |  |  |

| Subsystem clock (osc  | cillation frequency)  | Crystal oscillati                                                                                              | on (32.768 kHz)            |                    |             |            |  |  |

| Minimum instruction 6 | execution time        | 0.4 μs/1.6 μs (@                                                                                               | 9 5.0 MHz operat           | tion with main sys | stem clock) |            |  |  |

|                       |                       | 122 μs (@ 32.7                                                                                                 | '68 kHz operation          | with subsystem of  | clock)      |            |  |  |

| General-purpose regi  | sters                 | 8 bits × 8 regist                                                                                              | ers                        |                    |             |            |  |  |

| Instruction set       |                       | <ul><li>16-bit operat</li><li>Bit manipulat</li></ul>                                                          | ions<br>tions (such as set | , reset, and test) |             |            |  |  |

| I/O ports             |                       | Total: 18 <sup>Note 1</sup>                                                                                    |                            |                    |             |            |  |  |

|                       |                       | CMOS I/O: 12                                                                                                   |                            |                    |             |            |  |  |

|                       |                       | CMOS input: 6 <sup>Note 1</sup>                                                                                |                            |                    |             |            |  |  |

| Timers                |                       | 8-bit timer: 2 channels     Watch timer: 1 channel                                                             |                            |                    |             |            |  |  |

|                       |                       | Watchdog timer: 1 channel .                                                                                    |                            |                    |             |            |  |  |

| Timer outputs         |                       | 1                                                                                                              |                            |                    |             |            |  |  |

| A/D converter         |                       | 8-bit resolution × 1 channel                                                                                   |                            |                    |             |            |  |  |

| LCD controller/driver |                       | <ul> <li>Segment signal outputs: 23<sup>Note 1</sup></li> <li>Common signal outputs: 4</li> </ul>              |                            |                    |             |            |  |  |

| Vectored interrupt    | Maskable              | Internal: 6, external: 2                                                                                       |                            |                    |             |            |  |  |

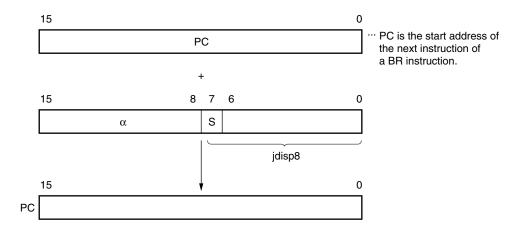

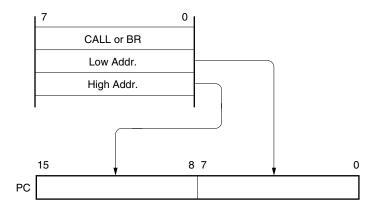

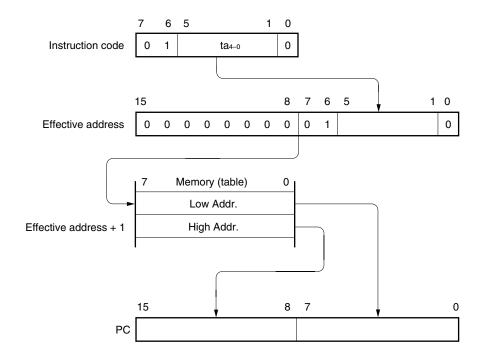

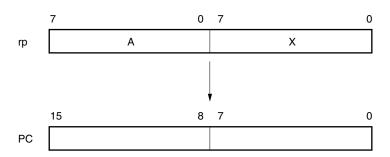

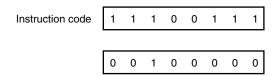

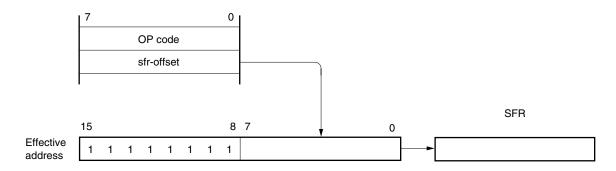

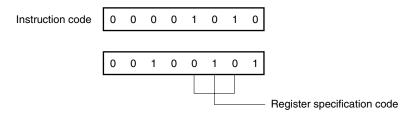

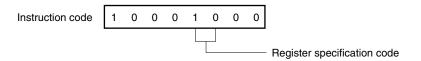

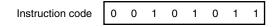

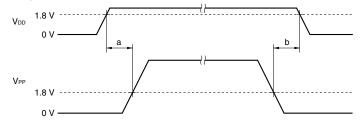

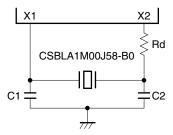

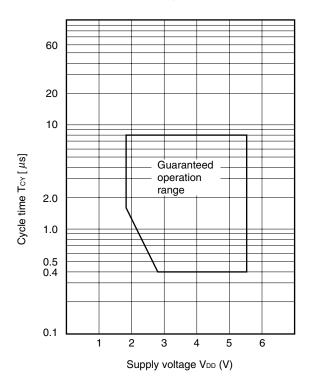

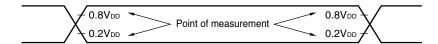

| sources               | Non-maskable          | Internal: 1                                                                                                    |                            |                    |             |            |  |  |