**CYPRESS****W48S87-72**

## Desktop/Notebook Frequency Generator

### Features

- Maximized EMI suppression using Cypress's Spread Spectrum technology

- $\pm 0.5\%$  Spread Spectrum clocking

- Equivalent to the W48S67-72 with Spread Spectrum for Tilamook, MMO, and Deschutes processors

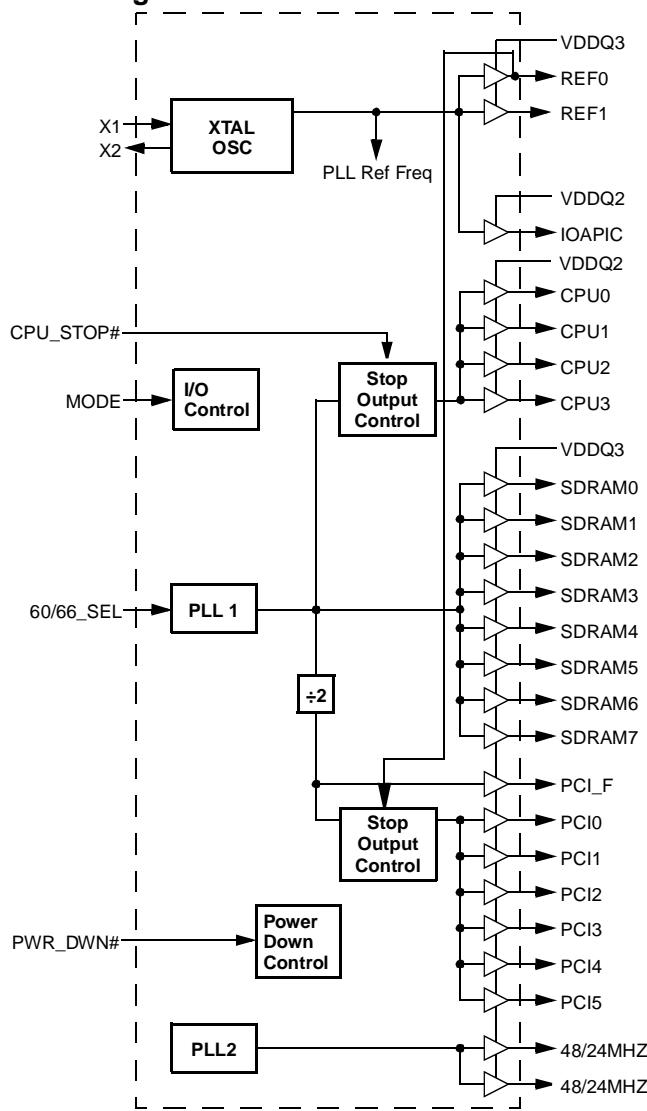

- Generates system clocks for CPU, IOAPIC, SDRAM, PCI, USB plus 14.318-MHz (REF0:1)

- Serial data interface (SDATA, SCLOCK inputs) provides additional CPU/PCI clock frequency selections, individual output clock disabling and other functions

- MODE input pin selects optional power management input control pins (reconfigures pins 26 and 27)

- Two fixed outputs separately selectable as 24-MHz or 48-MHz (default = 48-MHz)

- $V_{DDQ3} = 3.3V \pm 5\%$ ,  $V_{DDQ2} = 2.5V \pm 5\%$

- Uses external 14.318-MHz crystal

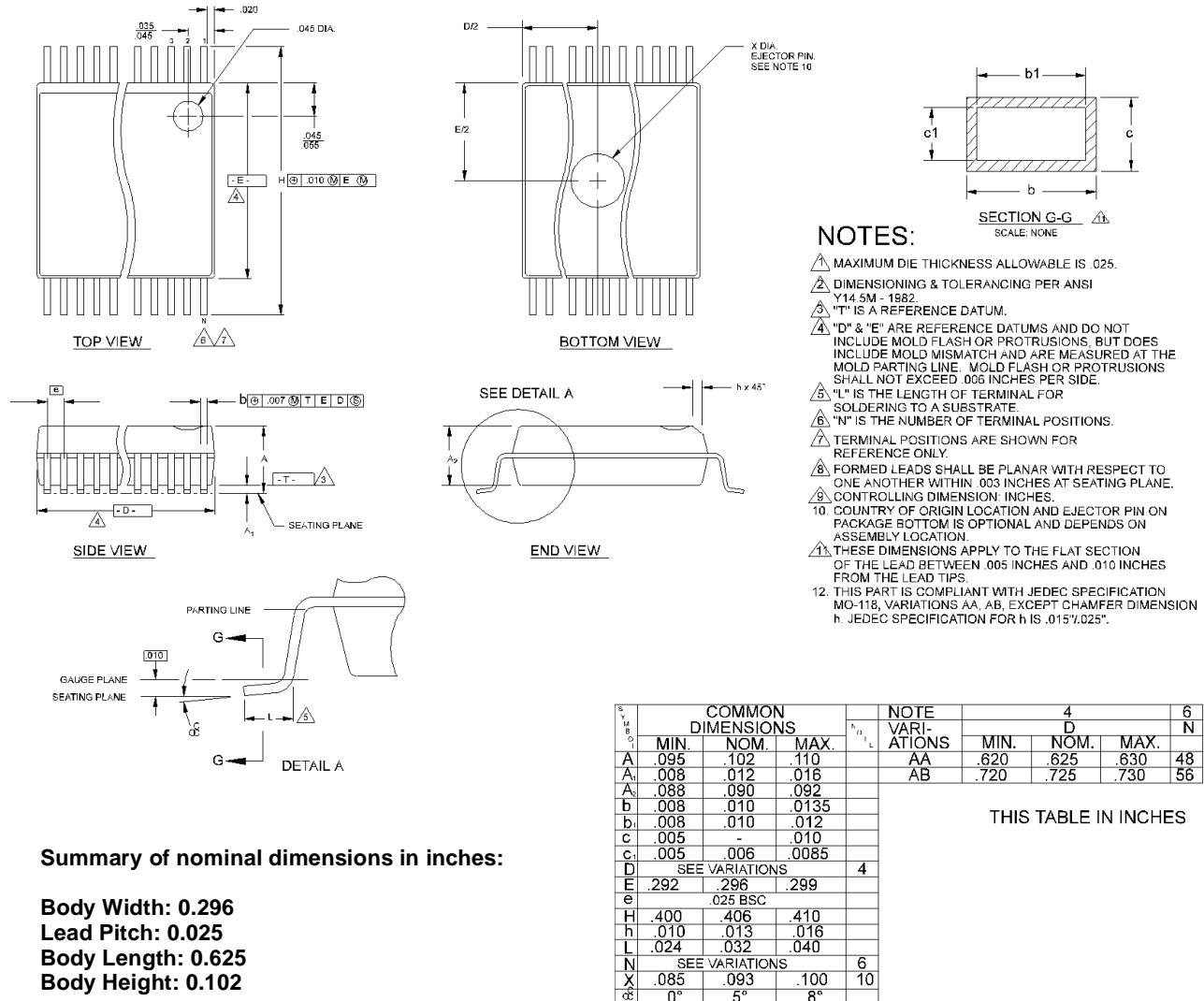

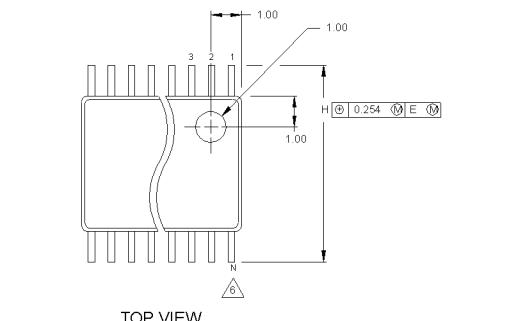

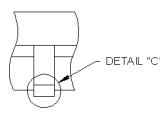

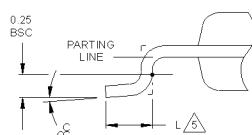

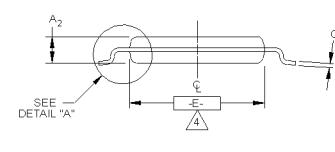

- Available in 48-pin SSOP (300 mils)

- $10\Omega$  CPU output impedance

**Table 1. Pin Selectable Frequency<sup>[1]</sup>**

| 60/66_SEL | CPU, SDRAM Clocks (MHz) | PCI Clocks (MHz) |

|-----------|-------------------------|------------------|

| 0         | 60                      | 30               |

| 1         | 66.8                    | 33.4             |

### Block Diagram

### Pin Configuration

|           |    |    |                  |

|-----------|----|----|------------------|

| REF1      | 1  | 48 | VDDQ3            |

| REF0      | 2  | 47 | CPU2.5#          |

| GND       | 3  | 46 | VDDQ2            |

| X1        | 4  | 45 | IOAPIC           |

| X2        | 5  | 44 | PWR_DWN#         |

| MODE      | 6  | 43 | GND              |

| VDDQ3     | 7  | 42 | CPU0             |

| PCI_F     | 8  | 41 | CPU1             |

| PCI0      | 9  | 40 | VDDQ2            |

| GND       | 10 | 39 | CPU2             |

| PCI1      | 11 | 38 | CPU3             |

| PCI2      | 12 | 37 | GND              |

| PCI3      | 13 | 36 | SDRAM0           |

| PCI4      | 14 | 35 | SDRAM1           |

| VDDQ3     | 15 | 34 | VDDQ3            |

| PCI5      | 16 | 33 | SDRAM2           |

| GND       | 17 | 32 | SDRAM3           |

| 60/66_SEL | 18 | 31 | GND              |

| SDATA     | 19 | 30 | SDRAM4           |

| SCLOCK    | 20 | 29 | SDRAM5           |

| VDDQ3     | 21 | 28 | VDDQ3            |

| 48/24MHZ  | 22 | 27 | SDRAM6/CPU_STOP# |

| 48/24MHZ  | 23 | 26 | SDRAM7/PCI_STOP# |

| GND       | 24 | 25 | VDDQ3            |

**W48S87-72****Note:**

- Additional frequency selections provided by serial data interface; refer to Table 5 on page 8.

**Pin Definitions**

| Pin Name         | Pin No.                | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU0:3           | 42, 41, 39, 38         | O        | <b>CPU Outputs 0 through 3:</b> These four CPU outputs are controlled by the CPU_STOP# control pin. Output voltage swing is controlled by voltage applied to VDDQ2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PCI0:5           | 9, 11, 12, 13, 14, 16  | O        | <b>PCI Bus Outputs 0 through 5:</b> These six PCI outputs are controlled by the PCI_STOP# control pin. Output voltage swing is controlled by voltage applied to VDDQ3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PCI_F            | 8                      | O        | <b>Free Running PCI Output:</b> Unlike PCI0:5 outputs, this output is not controlled by the PCI_STOP# control pin. Output voltage swing is controlled by voltage applied to VDDQ3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SDRAM0:5         | 36, 35, 33, 32, 30, 29 | O        | <b>SDRAM Clock Outputs 0 through 5:</b> These six SDRAM clock outputs run synchronous to the CPU clock outputs. Output voltage swing is controlled by voltage applied to VDDQ3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SDRAM6/CPU_STOP# | 27                     | I/O      | <p><b>SDRAM Clock Output 6 or CPU Clock Output Stop Control:</b> This pin has dual functions, selectable by the MODE input pin. When MODE = 0, this pin becomes the CPU_STOP# input. When MODE = 1, this pin becomes SDRAM clock output 6.</p> <p>Regarding use as a CPU_STOP# input: When brought LOW, clock outputs CPU0:3 are stopped LOW after completing a full clock cycle (2-3 CPU clock latency). When brought HIGH, clock outputs CPU0:3 are started beginning with a full clock cycle (2-3 CPU clock latency).</p> <p>Regarding use as a SDRAM clock: Output voltage swing is controlled by voltage applied to VDDQ3.</p>                          |

| SDRAM7/PCI_STOP# | 26                     | I/O      | <p><b>SDRAM Clock Output 7 or PCI Clock Output Stop Control:</b> This pin has dual functions, selectable by the MODE input pin. When MODE = 0, this pin becomes the PCI_STOP# input. When MODE = 1, this pin becomes SDRAM clock output 7.</p> <p>PCI_STOP# input: When brought LOW, clock outputs PCI0:5 are stopped LOW after completing a full clock cycle. When brought HIGH, clock outputs PCI0:5 are started beginning with a full clock cycle. Clock latency provides one PCI_F rising edge of PCI clock following PCI_STOP# state change.</p> <p>Regarding use as a SDRAM clock: Output voltage swing is controlled by voltage applied to VDDQ3.</p> |

| IOAPIC           | 45                     | O        | <b>I/O APIC Clock Output:</b> Provides 14.318-MHz fixed frequency. The output voltage swing is controlled by VDDQ2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 48/24MHz         | 22, 23                 | O        | <b>48-MHz / 24-MHz Output:</b> Fixed clock outputs that default to 48 MHz following device power-up. Either or both can be changed to 24 MHz through use of the serial data interface (Byte 0, bits 2 and 3). Output voltage swing is controlled by voltage applied to VDDQ3                                                                                                                                                                                                                                                                                                                                                                                 |

| REF0:1           | 2, 1                   | O        | <b>Fixed 14.318-MHz Outputs 0 through 1:</b> Used for various system applications. Output voltage swing is controlled by voltage applied to VDDQ3. REF0 is stronger than REF1 and should be used for driving ISA slots.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CPU_2.5#         | 47                     | I        | Set to logic 0 for V <sub>DDQ2</sub> = 2.5V (0 to 2.5V CPU output swing).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 60/66_SEL        | 18                     | I        | <b>60- or 66-MHz Input Selection:</b> Selects power-up default CPU clock frequency as shown in Table 1 on page 1 (also determines SDRAM and PCI clock frequency selections). Can be used to change CPU clock frequency while device is in operation if serial data port bits 0-2 of Byte 7 are logic 1 (default power-up condition).                                                                                                                                                                                                                                                                                                                         |

| X1               | 4                      | I        | <b>Crystal Connection or External Reference Frequency Input:</b> This pin has dual functions. It can be used as an external 14.318-MHz crystal connection or as an external reference frequency input.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| X2               | 5                      | I        | <b>Crystal Connection:</b> An input connection for an external 14.318-MHz crystal. If using an external reference, this pin must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

**Pin Definitions** (continued)

| Pin Name | Pin No.                         | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|---------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWR_DWN# | 44                              | I        | <b>Power-Down Control:</b> When this input is LOW, the device goes into a low-power standby condition. All outputs are actively held LOW while in power-down. CPU, SDRAM, and PCI clock outputs are stopped LOW after completing a full clock cycle (2–4 CPU clock cycle latency). When brought HIGH, CPU, SDRAM, and PCI outputs start with a full clock cycle at full operating frequency (3 ms maximum latency). |

| MODE     | 6                               | I        | <b>Mode Control:</b> This input selects the function of device pin 26 (SDRAM7/PCI_STOP#) and pin 27 (SDRAM6/CPU_STOP#). Refer to description for those pins.                                                                                                                                                                                                                                                        |

| SDATA    | 19                              | I/O      | <b>Serial Data Input:</b> Data input for Serial Data Interface. Refer to Serial Data Interface section that follows.                                                                                                                                                                                                                                                                                                |

| SCLOCK   | 20                              | I        | <b>Serial Clock Input:</b> Clock input for Serial Data Interface. Refer to Serial Data Interface section that follows.                                                                                                                                                                                                                                                                                              |

| VDDQ3    | 7, 15, 21, 25<br>28, 34, 48     | P        | <b>Power Connection:</b> Power supply for PCI0:5, REF0:1, and 48/24MHz output buffers. Connected to 3.3V supply.                                                                                                                                                                                                                                                                                                    |

| VDDQ2    | 46, 40                          | P        | <b>Power Connection:</b> Power supply for IOAPIC0, CPU0:3 output buffer. Connected to 2.5V supply.                                                                                                                                                                                                                                                                                                                  |

| GND      | 3, 10, 17,<br>24, 31, 37,<br>43 | G        | <b>Ground Connection:</b> Connect all ground pins to the common system ground plane.                                                                                                                                                                                                                                                                                                                                |

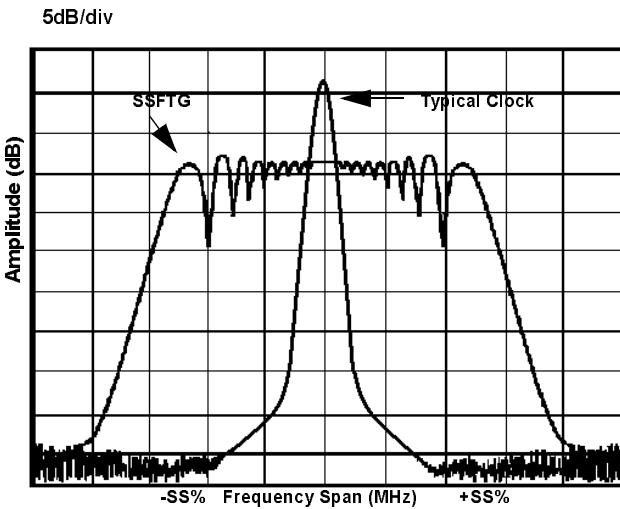

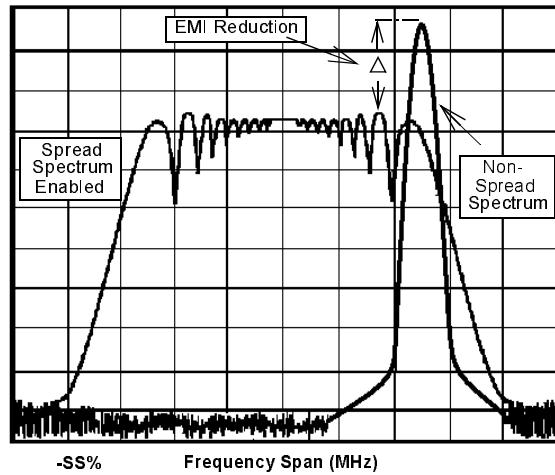

## Spread Spectrum Generator

The device generates a clock that is frequency modulated in order to increase the bandwidth that it occupies. By increasing the bandwidth of the fundamental and its harmonics, the amplitudes of the radiated electromagnetic emissions are reduced. This effect is depicted in *Figure 1*.

As depicted in *Figure 1*, a harmonic of a modulated clock has a much lower amplitude than that of an unmodulated signal. The reduction in amplitude is dependent on the harmonic number and the frequency deviation or spread. The equation for the reduction is

$$dB = 6.5 + 9 * \log_{10}(P) + 9 * \log_{10}(F)$$

Where  $P$  is the percentage of deviation and  $F$  is the frequency in MHz where the reduction is measured.

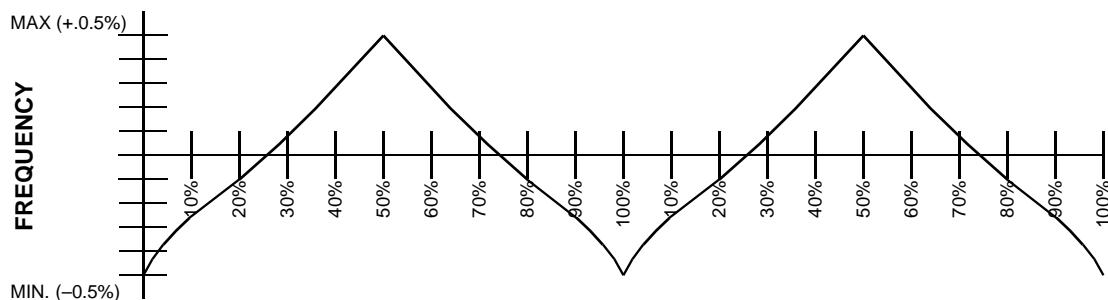

The output clock is modulated with a waveform depicted in *Figure 2*. This waveform, as discussed in "Spread Spectrum Clock Generation for the Reduction of Radiated Emissions" by Bush, Fessler, and Hardin produces the maximum reduction in the amplitude of radiated electromagnetic emissions. The deviation selected for this chip is  $\pm 0.5\%$  of the center frequency. *Figure 2* details the Cypress spreading pattern. Cypress does offer options with more spread and greater EMI reduction. Contact your local Sales representative for details on these devices.

Spread Spectrum clocking is activated or deactivated by selecting the appropriate values for bits 1–0 in data byte 0 of the I<sup>2</sup>C data stream. Refer to *Table 4* for more details.

**Figure 1. Clock Harmonic with and without SSCG Modulation Frequency Domain Representation**

**Figure 2. Typical Modulation Profile**

## Serial Data Interface

The W48S87-72 features a two-pin, serial data interface that can be used to configure internal register settings that control particular device functions. Upon power-up, the W48S87-72 initializes with default register settings, therefore the use of this serial data interface is optional. The serial interface is write-only (to the clock chip) and is the dedicated function of device pins SDATA and SCLOCK. In motherboard applications, SDATA and SCLOCK are typically driven by two logic outputs

of the chipset. Clock device register changes are normally made upon system initialization, if any are required. The interface can also be used during system operation for power management functions. *Table 2* summarizes the control functions of the serial data interface.

### Operation

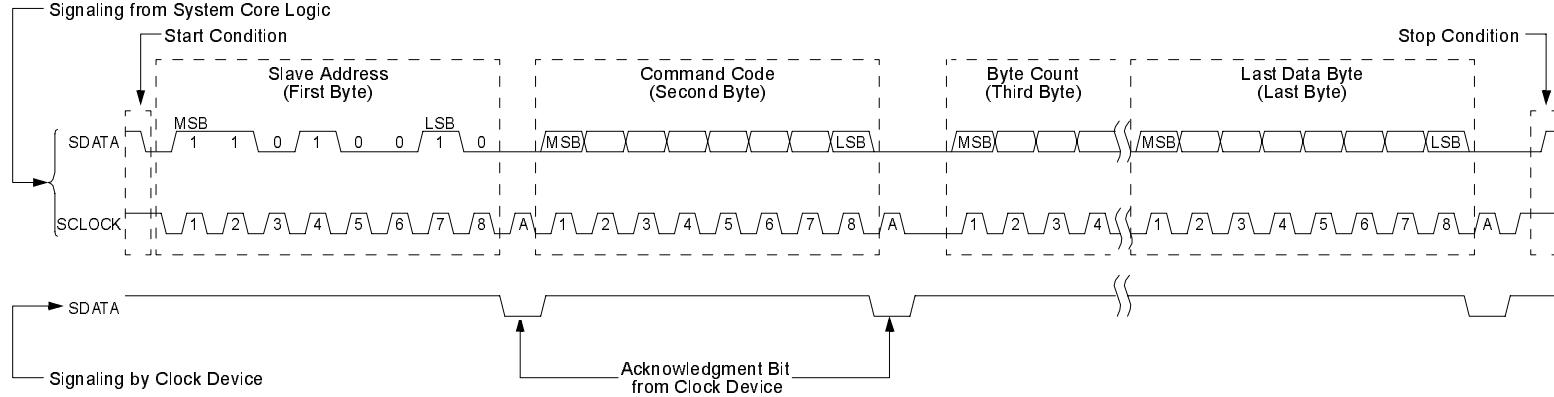

Data is written to the W48S87-72 in ten bytes of eight bits each. Bytes are written in the order shown in *Table 3*.

**Table 2. Serial Data Interface Control Functions Summary**

| Control Function                            | Description                                                                                                                                                                        | Common Application                                                                                                                              |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Output Disable                        | Any individual clock output(s) can be disabled. Disabled outputs are actively held LOW.                                                                                            | Unused outputs are disabled to reduce EMI and system power. Examples are clock outputs to unused SDRAM DIMM socket or PCI slot.                 |

| 48-/24-MHz Clock Output Frequency Selection | 48-/24-MHz clock outputs can be set to 48 MHz or 24 MHz.                                                                                                                           | Provides flexibility in Super I/O and USB device selection.                                                                                     |

| CPU Clock Frequency Selection               | Provides CPU/PCI frequency selections beyond the 60- and 66.6-MHz selections that are provided by the SEL60/66 input pin. Frequency is changed in a smooth and controlled fashion. | For alternate CPU devices, and power management options. Smooth frequency transition allows CPU frequency change under normal system operation. |

| Output Three-state                          | Puts all clock outputs into a high-impedance state.                                                                                                                                | Production PCB testing.                                                                                                                         |

| Test Mode                                   | All clock outputs toggle in relation with X1 input, internal PLL is bypassed. Refer to <i>Table 4</i> .                                                                            | Production PCB testing.                                                                                                                         |

| (Reserved)                                  | Reserved function for future device revision or production device testing.                                                                                                         | No user application. Register bit must be written as 0.                                                                                         |

**Table 3. Byte Writing Sequence**

| Byte Sequence | Byte Name     | Bit Sequence            | Byte Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | Slave Address | 11010010                | Commands the W48S87-72 to accept the bits in Data Bytes 0–7 for internal register configuration. Since other devices may exist on the same common serial data bus, it is necessary to have a specific slave address for each potential receiver. The slave receiver address for the W48S87-72 is 11010010. Register setting will not be made if the Slave Address is not correct (or is for an alternate slave receiver). |

| 2             | Command Code  | Don't Care              | Unused by the W48S87-72, therefore bit values are ignored (don't care). This byte must be included in the data write sequence to maintain proper byte allocation. The Command Code Byte is part of the standard serial communication protocol and may be used when writing to another addressed slave receiver on the serial data bus.                                                                                    |

| 3             | Byte Count    | Don't Care              | Unused by the W48S87-72, therefore bit values are ignored (don't care). This byte must be included in the data write sequence to maintain proper byte allocation. The Byte Count Byte is part of the standard serial communication protocol and may be used when writing to another addressed slave receiver on the serial data bus.                                                                                      |

| 4             | Data Byte 0   | Refer to <i>Table 4</i> | The data bits in Data Bytes 0–7 set internal W48S87-72 registers that control device operation. The data bits are only accepted when the Address Byte bit sequence is 11010010, as noted above. For description of bit control functions, refer to <i>Table 4</i> , Data Byte Serial Configuration Map.                                                                                                                   |

| 5             | Data Byte 1   |                         |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6             | Data Byte 2   |                         |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7             | Data Byte 3   |                         |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8             | Data Byte 4   |                         |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9             | Data Byte 5   |                         |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10            | Data Byte 6   |                         |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11            | Data Byte 7   |                         |                                                                                                                                                                                                                                                                                                                                                                                                                           |

**Writing Data Bytes**

Each bit in the data bytes control a particular device function except for the "reserved" bits which must be written as a logic 0. Bits are written MSB (most significant bit) first, which is bit 0.

7. *Table 4* gives the bit formats for registers located in Data Bytes 0–7.

*Table 5* details additional frequency selections that are available through the serial data interface.

*Table 6* details the select functions for Byte 0, bits 1 and 0.

**Table 4. Data Bytes 0–7 Serial Configuration Map**

| Bit(s)             | Affected Pin |          | Control Function                            | Bit Control                                                                                                                           |        | Default |

|--------------------|--------------|----------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------|---------|

|                    | Pin No.      | Pin Name |                                             | 0                                                                                                                                     | 1      |         |

| <b>Data Byte 0</b> |              |          |                                             |                                                                                                                                       |        |         |

| 7                  | --           | --       | (Reserved)                                  | --                                                                                                                                    | --     | 0       |

| 6                  | --           | --       | (Reserved)                                  | Refer to <i>Table 5</i>                                                                                                               |        | 0       |

| 5                  | --           | --       | SEL_4                                       | Refer to <i>Table 5</i>                                                                                                               |        | 0       |

| 4                  | --           | --       | SEL_3                                       | Refer to <i>Table 5</i>                                                                                                               |        | 0       |

| 3                  | 23           | 48/24MHZ | 48-/24-MHz Clock Output Frequency Selection | 24 MHz                                                                                                                                | 48 MHz | 0       |

| 2                  | 22           | 48/24MHZ | 48-/24-MHz Clock Output Frequency Selection | 24 MHz                                                                                                                                | 48 MHz | 0       |

| 1–0                | --           | --       | Bit 1 Bit 0<br>0 0<br>0 1<br>1 0<br>1 1     | Function (See <i>Table 6</i> for function details)<br>Normal Operation<br>Test Mode<br>Spread Spectrum On<br>All Outputs Three-stated |        | 00      |

| <b>Data Byte 1</b> |              |          |                                             |                                                                                                                                       |        |         |

| 7                  | 23           | 48/24MHZ | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 6                  | 22           | 48/24MHZ | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 5                  | --           | --       | (Reserved)                                  | --                                                                                                                                    | --     | 0       |

| 4                  | --           | --       | (Reserved)                                  | --                                                                                                                                    | --     | 0       |

| 3                  | 38           | CPU3     | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 2                  | 39           | CPU2     | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 1                  | 41           | CPU1     | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 0                  | 42           | CPU0     | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| <b>Data Byte 2</b> |              |          |                                             |                                                                                                                                       |        |         |

| 7                  | --           | --       | (Reserved)                                  | --                                                                                                                                    | --     | 0       |

| 6                  | 8            | PCI_F    | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 5                  | 16           | PCI5     | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 4                  | 14           | PCI4     | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 3                  | 13           | PCI3     | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 2                  | 12           | PCI2     | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 1                  | 11           | PCI1     | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 0                  | 9            | PCI0     | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| <b>Data Byte 3</b> |              |          |                                             |                                                                                                                                       |        |         |

| 7                  | 26           | SDRAM7   | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 6                  | 27           | SDRAM6   | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 5                  | 29           | SDRAM5   | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 4                  | 30           | SDRAM4   | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 3                  | 32           | SDRAM3   | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 2                  | 33           | SDRAM2   | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 1                  | 35           | SDRAM1   | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

| 0                  | 36           | SDRAM0   | Clock Output Disable                        | Low                                                                                                                                   | Active | 1       |

**Table 4. Data Bytes 0–7 Serial Configuration Map (continued)**

| Bit(s)             | Affected Pin |          | Control Function     | Bit Control      |        | Default |

|--------------------|--------------|----------|----------------------|------------------|--------|---------|

|                    | Pin No.      | Pin Name |                      | 0                | 1      |         |

| <b>Data Byte 4</b> |              |          |                      |                  |        |         |

| 7                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 6                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 5                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 4                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 3                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 2                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 1                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 0                  | --           | --       | (Reserved)           | --               | --     | 0       |

| <b>Data Byte 5</b> |              |          |                      |                  |        |         |

| 7                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 6                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 5                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 4                  | 45           | IOAPIC   | Clock Output Disable | Low              | Active | 1       |

| 3                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 2                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 1                  | 1            | REF1     | Clock Output Disable | Low              | Active | 1       |

| 0                  | 2            | REF0     | Clock Output Disable | Low              | Active | 1       |

| <b>Data Byte 6</b> |              |          |                      |                  |        |         |

| 7                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 6                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 5                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 4                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 3                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 2                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 1                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 0                  | --           | --       | (Reserved)           | --               | --     | 0       |

| <b>Data Byte 7</b> |              |          |                      |                  |        |         |

| 7                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 6                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 5                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 4                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 3                  | --           | --       | (Reserved)           | --               | --     | 0       |

| 2                  | --           | --       | SEL_2                | Refer to Table 5 |        | 1       |

| 1                  | --           | --       | SEL_1                | Refer to Table 5 |        | 1       |

| 0                  | --           | --       | SEL_0                | Refer to Table 5 |        | 1       |

**Table 5. Additional Frequency Selections through Serial Data Interface Data Bytes**

| Date Byte 0    |                | 60/66_SEL<br>(Pin 18) | Date Byte 7    |                |                | CPU0:3<br>SDRAM0:7 | PCI_F<br>PCI0:5 | Spread<br>Spectrum% |

|----------------|----------------|-----------------------|----------------|----------------|----------------|--------------------|-----------------|---------------------|

| Bit 5<br>SEL_4 | Bit 4<br>SEL_3 |                       | Bit 2<br>SEL_2 | BIT 1<br>SEL_1 | BIT 0<br>SEL_0 |                    |                 |                     |

| 0              | 0              | X                     | 0              | 0              | 0              | 75.0               | CPU/2           | $\pm 0.5$           |

| 0              | 0              | X                     | 0              | 0              | 1              | 75.0               | 32              | $\pm 0.5$           |

| 0              | 0              | X                     | 0              | 1              | 0              | 83.31              | 32              | $\pm 0.5$           |

| 0              | 0              | X                     | 0              | 1              | 1              | 33.41              | CPU/2           | $\pm 0.5$           |

| 0              | 0              | X                     | 1              | 0              | 0              | 50.11              | CPU/2           | $\pm 0.5$           |

| 0              | 0              | X                     | 1              | 0              | 1              | 68.52              | CPU/2           | $\pm 0.5$           |

| 0              | 0              | X                     | 1              | 1              | 0              | 60.0               | CPU/2           | $\pm 0.5$           |

| 0              | 0              | 0                     | 1              | 1              | 1              | 60.0               | CPU/2           | $\pm 0.5$           |

| 0              | 0              | 1                     | 1              | 1              | 1              | 66.82              | CPU/2           | $\pm 0.5$           |

| 0              | 1              | 0                     | X              | X              | X              | 60.0               | CPU/2           | $\pm 0.5$           |

| 0              | 1              | 1                     | X              | X              | X              | 66.6               | CPU/2           | -0.5                |

| 1              | 0              | 0                     | X              | X              | X              | 60.0               | CPU/2           | $\pm 0.5$           |

| 1              | 0              | 1                     | X              | X              | X              | 66.6               | CPU/2           | -0.5                |

| 1              | 1              | 0                     | X              | X              | X              | 60.0               | CPU/2           | $\pm 0.5$           |

| 1              | 1              | 1                     | X              | X              | X              | 66.6               | CPU/2           | -0.5                |

**Table 6. Select Function for Data Byte 0, Bits 0:1**

| Function           | Input Conditions |       | Output Conditions  |                  |                |              |

|--------------------|------------------|-------|--------------------|------------------|----------------|--------------|

|                    | Data Byte 0      |       | CPU0:3,<br>SRAM0:7 | PCI_F,<br>PCI0:5 | REF0:2, IOAPIC | 48/24MHZ     |

|                    | Bit 1            | Bit 0 |                    |                  |                |              |

| Normal Operation   | 0                | 0     | Note 2             | Note 2           | 14.318 MHz     | 48 or 24 MHz |

| Test Mode          | 0                | 1     | X1/2               | X1/4             | X1             | Note 3       |

| Spread Spectrum On | 1                | 0     | Note 2             | Note 2           | 14.318 MHz     | 48 or 24 MHz |

| Three-state        | 1                | 1     | Hi-Z               | Hi-Z             | Hi-Z           | Hi-Z         |

**Notes:**

2. CPU, SDRAM, and PCI frequency selections are listed in *Table 1* and *Table 5*.

3. In Test Mode, the 48-/24-MHz clock outputs are:

- X1/2 if 48-MHz is selected.

- X1/4 if 24-MHz is selected.

## How To Use the Serial Data Interface

### Electrical Requirements

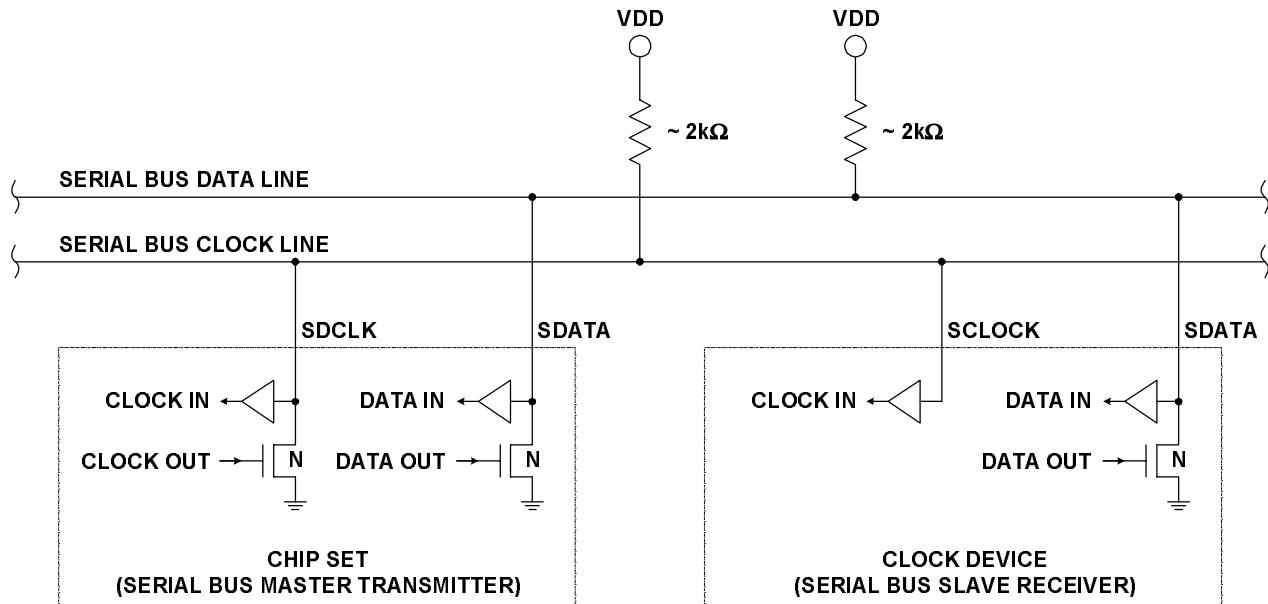

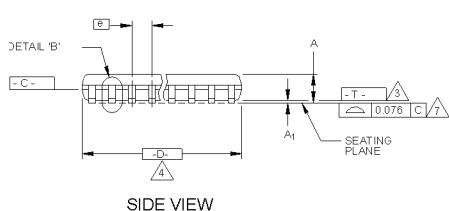

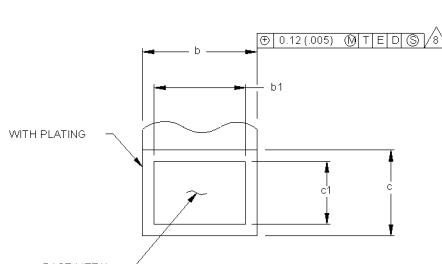

Figure 3 illustrates electrical characteristics for the serial interface bus used with the W48S87-72. Devices send data over the bus with an open drain logic output that can (a) pull the bus line LOW, or (b) let the bus default to logic 1. The pull-up resistors on the bus (both clock and data lines) establish a default logic 1. All bus devices generally have logic inputs to receive data.

Although the W48S87-72 is a receive-only device (no data write-back capability), it does transmit an “acknowledge” data pulse after each byte is received. Thus, the SDATA line can both transmit and receive data.

The pull-up resistor should be sized to meet the rise and fall times specified in AC parameters, taking into consideration total bus line capacitance.

Figure 3. Serial Interface Bus Electrical Characteristics

### Signaling Requirements

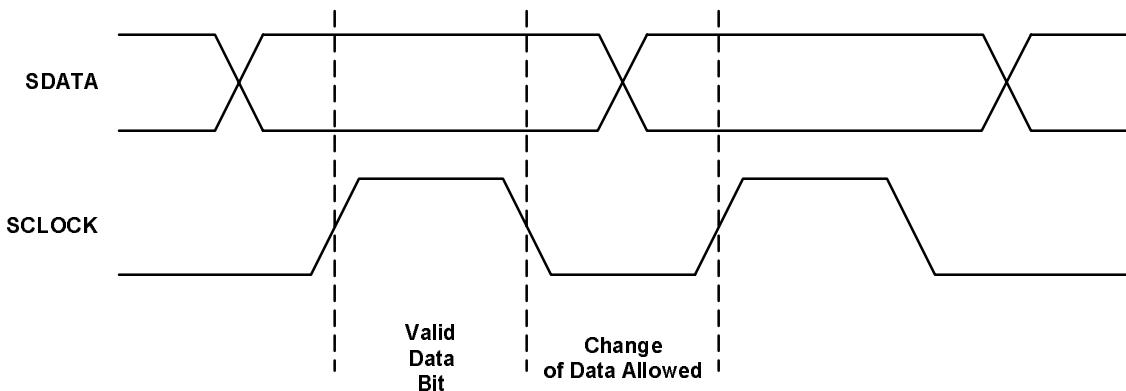

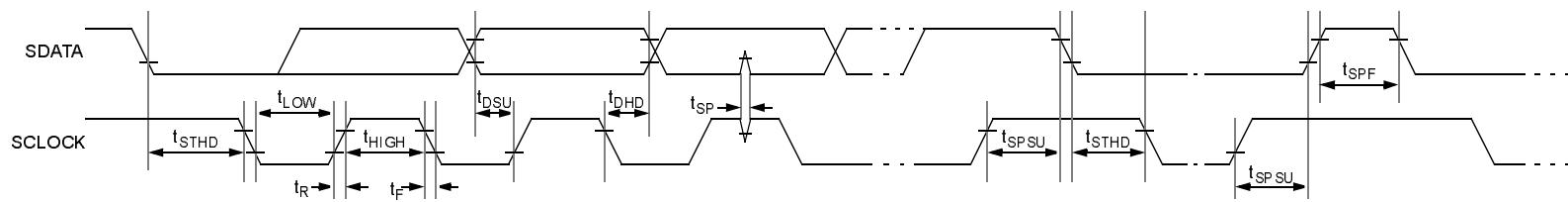

As shown in *Figure 4*, valid data bits are defined as stable logic 0 or 1 condition on the data line during a clock HIGH (logic 1) pulse. A transitioning data line during a clock HIGH pulse may be interpreted as a start or stop pulse (it will be interpreted as a start or stop pulse if the start/stop timing parameters are met).

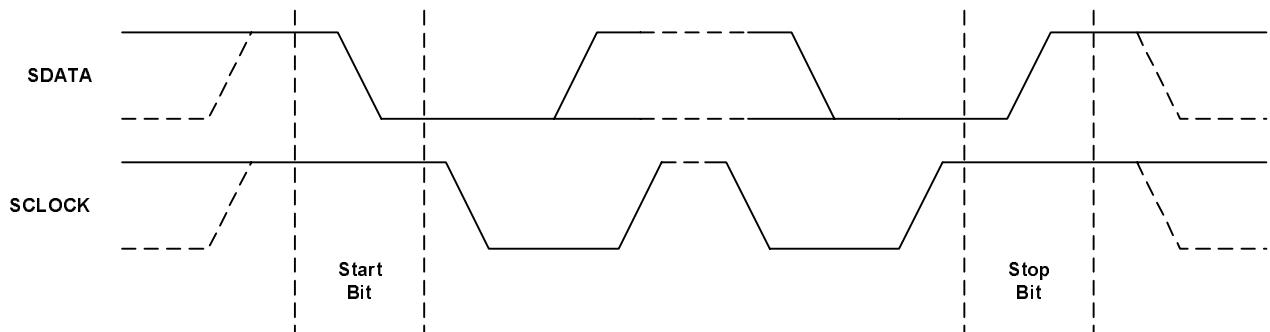

A write sequence is initiated by a “start bit” as shown in *Figure 5*. A “stop bit” signifies that a transmission has ended.

As stated previously, the W48S87-72 sends an “acknowledge” pulse after receiving eight data bits in each byte as shown in *Figure 6*.

### Sending Data to the W48S87-72

The device accepts data once it has detected a valid start bit and address byte sequence. Device functionality is changed upon the receipt of each data bit (registers are not double buffered). Partial transmission is allowed meaning that a transmission can be truncated as soon as the desired data bits are transmitted (remaining registers will be unmodified). Transmission is truncated with either a stop bit or new start bit (restart condition).

**Figure 4. Serial Data Bus Valid Data Bit**

**Figure 5. Serial Data Bus Start and Stop Bit**

Figure 6. Serial Data Bus Write Sequence

Figure 7. Serial Data Bus Timing Diagram

## Absolute Maximum Ratings

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions

above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter           | Description                            | Rating       | Unit |

|---------------------|----------------------------------------|--------------|------|

| $V_{DD}$ , $V_{IN}$ | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| $T_{STG}$           | Storage Temperature                    | -65 to +150  | °C   |

| $T_A$               | Operating Temperature                  | 0 to +70     | °C   |

| $T_B$               | Ambient Temperature under Bias         | -55 to +125  | °C   |

| ESD <sub>PROT</sub> | Input ESD Protection                   | 2 (min.)     | kV   |

## DC Electrical Characteristics:

$T_A = 0^\circ\text{C}$  to  $+70^\circ\text{C}$ ,  $V_{DDQ3} = 3.3\text{V}\pm5\%$  (3.135–3.465V)  $f_{XTL} = 14.31818\text{ MHz}$ ,  $V_{DDQ2} = 2.5\pm5\%$

| Parameter             | Description                       |               | Test Condition                                    | Min. | Typ. | Max. | Unit |

|-----------------------|-----------------------------------|---------------|---------------------------------------------------|------|------|------|------|

| <b>Supply Current</b> |                                   |               |                                                   |      |      |      |      |

| $I_{DDQ3}$            | Supply Current (3.3V)             |               | CPUCLK =66.8 MHz<br>Outputs Loaded <sup>[4]</sup> | 120  | 150  | 200  | mA   |

| $I_{DDQ2}$            | Supply Current (2.5V)             |               | CPUCLK =66.8 MHz<br>Outputs Loaded <sup>[4]</sup> |      |      | 50   | mA   |

| <b>Logic Inputs</b>   |                                   |               |                                                   |      |      |      |      |

| $V_{IL}$              | Input Low Voltage                 |               |                                                   |      |      | 0.8  | V    |

| $V_{IH}$              | Input High Voltage                |               |                                                   | 2.0  |      |      | V    |

| $I_{IL}$              | Input Low Current <sup>[5]</sup>  |               |                                                   |      |      | 10   | µA   |

| $I_{IH}$              | Input High Current <sup>[5]</sup> |               |                                                   |      |      | 10   | µA   |

| <b>Clock Outputs</b>  |                                   |               |                                                   |      |      |      |      |

| $V_{OL}$              | Output Low Voltage                |               | $I_{OL} = 1\text{ mA}$                            |      |      | 50   | mV   |

| $V_{OH}$              | Output High Voltage               |               | $I_{OH} = -1\text{ mA}$                           | 3.1  |      |      | V    |

| $V_{OH}$              | Output High Voltage (CPU, IOAPIC) |               | $I_{OH} = -1\text{ mA}$                           | 2.2  |      |      | V    |

| $I_{OL}$              | Output Low Current                | CPU0:3        | $V_{OL} = 1.25\text{V}$                           |      | 155  |      | mA   |

|                       |                                   | SDRAM0:7      | $V_{OL} = 1.5\text{V}$                            |      | 100  |      | mA   |

|                       |                                   | PCI_F, PCI0:5 | $V_{OL} = 1.5\text{V}$                            |      | 95   |      | mA   |

|                       |                                   | IOAPIC        | $V_{OL} = 1.25\text{V}$                           |      | 85   |      | mA   |

|                       |                                   | REF0          | $V_{OL} = 1.5\text{V}$                            |      | 75   |      | mA   |

|                       |                                   | REF1          | $V_{OL} = 1.5\text{V}$                            |      | 60   |      | mA   |

|                       |                                   | 48/24MHz      | $V_{OL} = 1.5\text{V}$                            |      | 60   |      | mA   |

| $I_{OH}$              | Output High Current               | CPU0:3        | $V_{OL} = 1.25\text{V}$                           |      | 125  |      | mA   |

|                       |                                   | SDRAM0:7      | $V_{OL} = 1.5\text{V}$                            |      | 95   |      | mA   |

|                       |                                   | PCI_F, PCI0:5 | $V_{OL} = 1.5\text{V}$                            |      | 100  |      | mA   |

|                       |                                   | IOAPIC        | $V_{OL} = 1.25\text{V}$                           |      | 80   |      | mA   |

|                       |                                   | REF0          | $V_{OL} = 1.5\text{V}$                            |      | 80   |      | mA   |

|                       |                                   | REF1          | $V_{OL} = 1.5\text{V}$                            |      | 65   |      | mA   |

|                       |                                   | 48/24MHz      | $V_{OL} = 1.5\text{V}$                            |      | 60   |      | mA   |

### Notes:

4. All clock outputs loaded with maximum lump capacitance test load specified in AC Electrical Characteristics section.

5. W48S87-72 logic inputs have internal pull-up devices. (Not CMOS level.)

**DC Electrical Characteristics: (continued)**

$T_A = 0^\circ\text{C}$  to  $+70^\circ\text{C}$ ,  $V_{DDQ3} = 3.3\text{V}\pm5\%$  (3.135–3.465V)  $f_{XTL} = 14.31818\text{ MHz}$ ,  $V_{DDQ2} = 2.5\pm5\%$

| Parameter                         | Description                                                       | Test Condition                     | Min.        | Typ. | Max.        | Unit          |

|-----------------------------------|-------------------------------------------------------------------|------------------------------------|-------------|------|-------------|---------------|

| <b>Crystal Oscillator</b>         |                                                                   |                                    |             |      |             |               |

| $V_{TH}$                          | X1 Input Threshold Voltage <sup>[6]</sup>                         | $V_{DD} = 3.3\text{V}$             |             | 1.65 |             | V             |

| $C_{LOAD}$                        | Load Capacitance, Imposed on External Crystal <sup>[7]</sup>      |                                    |             | 14   |             | pF            |

| $C_{IN,X1}$                       | X1 Input Capacitance <sup>[8]</sup>                               | Pin X2 unconnected                 |             | 28   |             | pF            |

| <b>Pin Capacitance/Inductance</b> |                                                                   |                                    |             |      |             |               |

| $C_{IN}$                          | Input Pin Capacitance                                             | Except X1 and X2                   |             | 5    |             | pF            |

| $C_{OUT}$                         | Output Pin Capacitance                                            |                                    |             | 6    |             | pF            |

| $L_{IN}$                          | Input Pin Inductance                                              |                                    |             | 7    |             | nH            |

| <b>Serial Input Port</b>          |                                                                   |                                    |             |      |             |               |

| $V_{IL}$                          | Input Low Voltage                                                 | $V_{DD} = 3.3\text{V}$             |             | 0.4  | $0.3V_{DD}$ | V             |

| $V_{IH}$                          | Input High Voltage                                                | $V_{DD} = 3.3\text{V}$             | $0.7V_{DD}$ | 2.4  |             | V             |

| $I_{IL}$                          | Input Low Current                                                 | No internal pull-up/down on SCLOCK |             | 10   | 10          | $\mu\text{A}$ |

| $I_{IH}$                          | Input High Current                                                | No internal pull-up/down on SCLOCK |             | 10   | 10          | $\mu\text{A}$ |

| $I_{OL}$                          | Sink Current into SDATA or SCLOCK, Open Drain N-Channel Device On | $I_{OL} = 0.3V_{DD}$               | 5           | 10   | 15          | mA            |

| $C_{IN}$                          | Input Capacitance of SDATA and SCLOCK                             |                                    |             | 5    | 10          | pF            |

| $C_{SDATA}$                       | Total Capacitance of SDATA Bus                                    |                                    |             |      | 400         | pF            |

| $C_{SCLOCK}$                      | Total Capacitance of SCLOCK Bus                                   |                                    |             |      | 400         | pF            |

**Notes:**

6. X1 input threshold voltage (typical) is  $V_{DDQ3}/2$ .

7. The W48S87-72 contains an internal crystal load capacitor between pin X1 and ground and another between pin X2 and ground. Total load placed on crystal is 14 pF; this includes typical stray capacitance of short PCB traces to crystal.

8. X1 input capacitance is applicable when driving X1 with an external clock source (X2 is left unconnected).

## AC Electrical Characteristics

$T_A = 0^\circ\text{C to } +70^\circ\text{C}$ ,  $V_{DD} = V_{DDQ3} = 3.3\text{V}\pm5\%$  ( $3.135\text{--}3.465\text{V}$ )  $f_{XTL} = 14.31818\text{ MHz}$ ,  $V_{DDQ2} = 2.5\pm5\%$

AC clock parameters are tested and guaranteed over stated operating conditions using the stated lump capacitive load at the clock output.

### CPU Clock Outputs, CPU0:3 (Lump Capacitance Test Load = 20 pF)

| Parameter | Description                                        | Test Condition/Comments                                                                                             | CPU = 66.8 MHz |      |      | CPU = 60 MHz |        |      | Unit     |

|-----------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------|------|------|--------------|--------|------|----------|

|           |                                                    |                                                                                                                     | Min.           | Typ. | Max. | Min.         | Typ.   | Max. |          |

| $t_P$     | Period                                             | Measured on rising edge at 1.5V                                                                                     | 15             |      |      | 16.7         |        |      | ns       |

| $f$       | Frequency, Actual                                  | Determined by PLL divider ratio                                                                                     |                | 66.8 |      |              | 59.876 |      | MHz      |

| $t_H$     | High Time                                          | Duration of clock cycle above 2.4V                                                                                  | 5.2            |      |      | 6            |        |      | ns       |

| $t_L$     | Low Time                                           | Duration of clock cycle below 0.4V                                                                                  | 5              |      |      | 5.8          |        |      | ns       |

| $t_R$     | Output Rise Edge Rate                              | Measured from 0.4V to 2.4V                                                                                          | 1              |      | 4    | 1            |        | 4    | V/ns     |

| $t_F$     | Output Fall Edge Rate                              | Measured from 2.4V to 0.4V                                                                                          | 1              |      | 4    | 1            |        | 4    | V/ns     |

| $t_D$     | Duty Cycle                                         | Measured on rising and falling edge at 1.25V                                                                        | 45             | 52   | 55   | 45           | 52     | 55   | %        |

| $t_{JC}$  | Jitter, Cycle-to-Cycle                             | Measured on rising edge at 1.25V. Maximum difference of cycle time between two adjacent cycles.                     |                |      | 250  |              |        | 250  | ps       |

| $t_{SK}$  | Output Skew                                        | Measured on rising edge at 1.25V                                                                                    |                |      | 250  |              |        | 250  | ps       |

| $f_{ST}$  | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |                |      | 3    |              |        | 3    | ms       |

| $Z_o$     | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |                | 10   |      |              | 10     |      | $\Omega$ |

### SDRAM Clock Outputs, SDRAM0:7 (Lump Capacitance Test Load = 30 pF)

| Parameter | Description                                        | Test Condition/Comments                                                                                             | CPU = 66.8 MHz |      |      | CPU = 60 MHz |        |      | Unit     |

|-----------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------|------|------|--------------|--------|------|----------|

|           |                                                    |                                                                                                                     | Min.           | Typ. | Max. | Min.         | Typ.   | Max. |          |

| $t_P$     | Period                                             | Measured on rising edge at 1.5V                                                                                     | 15             |      |      | 16.7         |        |      | ns       |

| $f$       | Frequency, Actual                                  | Determined by PLL divider ratio                                                                                     |                | 66.8 |      |              | 59.876 |      | MHz      |

| $t_R$     | Output Rise Edge Rate                              | Measured from 0.4V to 2.4V                                                                                          | 1              |      | 4    | 1            |        | 4    | V/ns     |

| $t_F$     | Output Fall Edge Rate                              | Measured from 2.4V to 0.4V                                                                                          | 1              |      | 4    | 1            |        | 4    | V/ns     |

| $t_D$     | Duty Cycle                                         | Measured on rising and falling edge at 1.5V                                                                         | 45             | 50   | 55   | 45           | 50     | 55   | %        |

| $t_{JC}$  | Jitter, Cycle-to-Cycle                             | Measured on rising edge at 1.5V. Maximum difference of cycle time between two adjacent cycles.                      |                |      | 250  |              |        | 250  | ps       |

| $t_{SK}$  | Output Skew                                        | Measured on rising edge at 1.5V                                                                                     |                | 100  |      |              | 100    |      | ps       |

| $t_{SK}$  | CPU to SDRAM Clock Skew                            | Covers all CPU/SDRAM outputs. Measured on rising edge at 1.5V.                                                      |                |      | 500  |              |        | 500  | ps       |

| $f_{ST}$  | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |                |      | 3    |              |        | 3    | ms       |

| $Z_o$     | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |                | 16   |      |              | 16     |      | $\Omega$ |

**PCI Clock Outputs, PCI0:5 (Lump Capacitance Test Load = 30 pF)**

| Parameter | Description                                        | Test Condition/Comments                                                                                             | CPU = 66.8 MHz |      |      | CPU = 60 MHz |        |      | Unit     |

|-----------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------|------|------|--------------|--------|------|----------|

|           |                                                    |                                                                                                                     | Min.           | Typ. | Max. | Min.         | Typ.   | Max. |          |

| $t_P$     | Period                                             | Measured on rising edge at 1.5V                                                                                     | 30             |      |      | 33.3         |        |      | ns       |

| $f$       | Frequency, Actual                                  | Determined by PLL divider ratio                                                                                     |                | 33.4 |      |              | 29.938 |      | MHz      |

| $t_H$     | High Time                                          | Duration of clock cycle above 2.4V                                                                                  | 12             |      |      | 13.3         |        |      | ns       |

| $t_L$     | Low Time                                           | Duration of clock cycle below 0.4V                                                                                  | 12             |      |      | 13.3         |        |      | ns       |

| $t_R$     | Output Rise Edge Rate                              |                                                                                                                     | 1              |      | 4    | 1            |        | 4    | V/ns     |

| $t_F$     | Output Fall Edge Rate                              |                                                                                                                     | 1              |      | 4    | 1            |        | 4    | V/ns     |

| $t_D$     | Duty Cycle                                         | Measured on rising and falling edge at 1.5V                                                                         | 45             | 51   | 55   | 45           | 51     | 55   | %        |

| $t_{JC}$  | Jitter, Cycle-to-Cycle                             | Measured on rising edge at 1.5V. Maximum difference of cycle time between two adjacent cycles.                      |                |      | 250  |              |        | 250  | ps       |

| $t_{SK}$  | Output Skew                                        | Measured on rising edge at 1.5V                                                                                     |                |      | 250  |              |        | 250  | ps       |

| $t_O$     | CPU to PCI Clock Skew                              | Covers all CPU/PCI outputs. Measured on rising edge at 1.5V. CPU leads PCI output.                                  | 1              |      | 4    | 1            |        | 4    | ns       |

| $f_{ST}$  | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |                |      | 3    |              |        | 3    | ms       |

| $Z_o$     | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |                | 30   |      |              | 30     |      | $\Omega$ |

**I/O APIC Clock Output (Lump Capacitance Test Load = 20 pF)**

| Parameter | Description                                        | Test Condition/Comments                                                                                             | CPU = 60/66.8 MHz |          |      | Unit     |

|-----------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------|----------|------|----------|

|           |                                                    |                                                                                                                     | Min.              | Typ.     | Max. |          |

| $f$       | Frequency, Actual                                  | Frequency generated by crystal oscillator                                                                           |                   | 14.31818 |      | MHz      |

| $t_R$     | Output Rise Edge Rate                              |                                                                                                                     | 1                 |          | 4    | V/ns     |

| $t_F$     | Output Fall Edge Rate                              |                                                                                                                     | 1                 |          | 4    | V/ns     |

| $t_D$     | Duty Cycle                                         | Measured on rising and falling edge at 1.25V                                                                        | 45                | 52.5     | 55   | %        |

| $f_{ST}$  | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |                   |          | 1.5  | ms       |

| $Z_o$     | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |                   | 15       |      | $\Omega$ |

**REF0 Clock Output (Lump Capacitance Test Load = 45 pF)**

| Parameter       | Description                                        | Test Condition/Comments                                                                                             | CPU = 60/66.8 MHz |          |      | Unit |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------|----------|------|------|

|                 |                                                    |                                                                                                                     | Min.              | Typ.     | Max. |      |

| f               | Frequency, Actual                                  | Frequency generated by crystal oscillator                                                                           |                   | 14.31818 |      | MHz  |

| t <sub>R</sub>  | Output Rise Edge Rate                              | Measured from 0.4V to 2.4V                                                                                          | 1                 |          | 4    | V/ns |

| t <sub>F</sub>  | Output Fall Edge Rate                              | Measured from 2.4V to 0.4V                                                                                          | 1                 |          | 4    | V/ns |

| t <sub>D</sub>  | Duty Cycle                                         | Measured on rising and falling edge at 1.5V                                                                         | 45                | 50       | 55   | %    |

| f <sub>ST</sub> | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |                   |          | 1.5  | ms   |

| Z <sub>o</sub>  | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |                   | 16       |      | Ω    |

**REF1 Clock Output (Lump Capacitance Test Load = 20 pF)**

| Parameter       | Description                                        | Test Condition/Comments                                                                                             | CPU = 60/66.8 MHz |          |      | Unit |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------|----------|------|------|

|                 |                                                    |                                                                                                                     | Min.              | Typ.     | Max. |      |

| f               | Frequency, Actual                                  | Frequency generated by crystal oscillator                                                                           |                   | 14.31818 |      | MHz  |

| t <sub>R</sub>  | Output Rise Edge Rate                              |                                                                                                                     | 0.5               |          | 2    | V/ns |

| t <sub>F</sub>  | Output Fall Edge Rate                              |                                                                                                                     | 0.5               |          | 2    | V/ns |

| t <sub>D</sub>  | Duty Cycle                                         | Measured on rising and falling edge at 1.5V                                                                         | 45                |          | 55   | %    |

| f <sub>ST</sub> | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |                   |          | 1.5  | ms   |