# LatticeECP2M PCI Express Development Kit User's Guide

Version 1.1

For use with the LatticeECP2M

PCle Solutions Board

Lattice Semiconductor Corporation 5555 NE Moore Court Hillsboro, OR 97124 (503) 268-8000

September 4, 2008

#### Copyright

Copyright © 2008 Lattice Semiconductor Corporation.

This document may not, in whole or part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior written consent from Lattice Semiconductor Corporation.

#### **Technical Support**

**Hotline (North America)**:1-800-LATTICE (North America) **Hotline (**Outside North America): +1-503-268-8001

**e-mail**: techsupport@latticesemi.com **Internet**: www.latticesemi.com

Part Number: DK-PCIE-ECP2M-GUIDE

#### **Trademarks**

Lattice Semiconductor Corporation, L Lattice Semiconductor Corporation (logo), L (stylized), L (design), Lattice (design), LSC, E2CMOS, GAL, GDX, Generic Array Logic, ISP, ispATE, ispCLOCK, ispDOWNLOAD, ispGAL, ispGDS, ispGDX, ispGDXV, ispGDX2, ispGENERATOR, ispJTAG, ispLEVER, ispLEVERCORE, ispLSI, ispMACH, ispPAC, ispTRACY, ispTURBO, ispVIRTUAL MACHINE, ispVM, ispXP, ispXPGA, ispXPLD, LatticeEC, LatticeECP-DSP, LatticeECP2, LatticeXP, LatticeSC, MACH, MachXO, ORCA, PAC, PAC-Designer, PAL, Performance Analyst, Silicon Forest, Speedlocked, Speed Locking, SuperBIG, SuperCOOL, SuperFAST, SuperWIDE, sysCLOCK, sysCONFIG, sysDSP, sysHSI, sysI/O, sysMEM, LatticeMico32, The Simple Machine for Complex Design, TransFR, UltraMOS, XPIO, and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries in the United States and/or other countries. ISP and Bringing the Best Together are service marks of Lattice Semiconductor Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE SEMICONDUCTOR CORPORATION (LSC) OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED ON THIS SITE, EVEN IF LSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

LSC may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. LSC makes no

commitment to update this documentation. LSC reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. LSC recommends its customers obtain the latest version of the relevant information to establish, before ordering, that the information being relied upon is current.

#### **Type Conventions Used in This Document**

| Convention        | Meaning or Use                                                                                                     |

|-------------------|--------------------------------------------------------------------------------------------------------------------|

| Bold              | Items in the user interface that you select or click. Text that you type into the user interface.                  |

| <italic></italic> | Variables in commands, code syntax, and path names.                                                                |

| Ctrl+F            | The + means press the two keys at the same time.                                                                   |

| Courier           | Code examples. Messages, reports, and prompts from the software.                                                   |

|                   | Omitted material in a line of code.                                                                                |

|                   | Omitted lines in code and report examples.                                                                         |

| [ ]               | In syntax descriptions, square brackets indicate optional items. In bus specifications, the brackets are required. |

| ( )               | In syntax descriptions, parentheses indicate grouped items.                                                        |

|                   | In syntax descriptions, a vertical bar indicates a choice between items.                                           |

| ı | LatticeFCP2M | PCI Eynress | Develonme | nt Kit I Isa | r's Guide |

|---|--------------|-------------|-----------|--------------|-----------|

# Contents

|           | Contents v                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 | Introduction 1                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | About this Guide 1 Using the Kit User Documentation 1 Learning Objectives 2                                                                                                                                                                                                                                                                                                                                         |

|           | Related Documentation 3                                                                                                                                                                                                                                                                                                                                                                                             |

| Chapter 2 | Getting Started with the Development Kit 5  Before You Start 5  Development Kit Contents 5  Development Tools 6  Installing ispLEVER (Windows/Linux) 6  Device Configuration Software and Cable 8  Hardware Requirements 9  Software Requirements 9  Installing the PCIe Development Kit 9                                                                                                                          |

| Chapter 3 | PCIe Solutions Board Setup and Installation 11  The PCIe Solutions Board 11  Unpacking and Inspecting the Solutions Board 12  Hardware Installation 13  Installing the Solutions Board Hardware 13  Installing Solutions Board Drivers 15  Installing Hardware into a Different Slot 16  Verifying Correct Board Operation 16  LED Definitions 16  Default Switch Settings 18  Reprogramming the Solutions Board 18 |

Contents

| Cnapter 4  | Before You Begin 21 Resource References 22 Hardware Resources 22 Software Resources 22 Basic Demo Operations Overview 22 Running the PCle Basic Demo Software 23 Touring the PCle Basic Demo Interface 24 Rebuilding the PCle Basic Demo Design 30 Modifying the PCle Basic Demo Design 31                                                                                                      |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 5  | Running the PCI Express Throughput Demo 33  Before You Begin 33  Resource References 34  Hardware Resources 34  Software Resources 34  Throughput Demo Operations Overview 34  Running the Throughput Demo 35  Touring the PCIe Throughput Demo Interface 36  Known Issues 43                                                                                                                   |

| Chapter 6  | Running the PCI Express DMA Demos 45  Before You Begin 45  Resource References 46  Hardware Resources 46  Software Resources 46  DMA Demo Operations Overview 47  Scatter-Gather DMA Overview 48  Running the DMA Demos 50  Running Multiple DMA Demos 52  PCIe DMA ColorBars Demo 52  PCIe DMA ImageMove Demo 54                                                                               |

| Appendix A | Installing and Running the Development Kit in Linux 57 Installing the PCIe Development Kit on Linux 57 Installing the PCIe Demo Package 58 Before You Begin 58 Installation Overview 59 Installing Solutions Board Hardware 59 Demo Package Software Installation 60 Building Demo Binaries from Source Code 61 Installing a Java Runtime Environment 61 Uninstalling the PCIe Demo Software 62 |

| Appendix B | Troubleshooting 63  Troubleshooting Demo Software Installation 63  Troubleshooting the Solutions Board 63  Troubleshooting Driver Installation 64  Troubleshooting Demo Operation 64                                                                                                                                                                                                            |

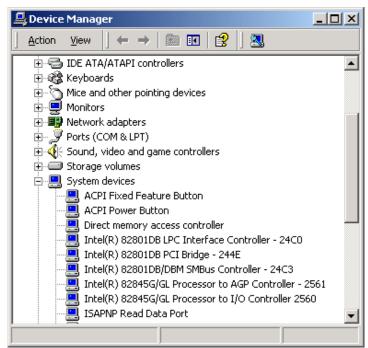

Using Device Manager to Debug Installation 65

Index 67

1

# Introduction

Thank you for choosing the Lattice Semiconductor PCI Express (PCIe) Development Kit! This guide describes how to start using the PCIe Development Kit, a low-cost platform for demonstrating the PCI Express reference design for evaluating solutions for your own specific application.

Along with the LatticeECP2M-50 PCI Express solutions board and accessories, this kit includes all the software development tools and documentation that you need to begin developing your PCI Express solution.

# **About this Guide**

This guide will familiarize you with the contents of the kit and walk you through the process of setting up your PCI Express development environment. The chapters are set up in a sequential manner and assumes you do not have any associated tools installed on your system. For Linux users, corresponding installation instructions are provided in Appendix A.

# **Using the Kit User Documentation**

If you are new to ispLEVER and Lattice development kits, we recommend that you go through the chapters in this user's guide in a sequential manner and perform the tasks related to the platform you are using, either Windows or Linux.

If you are familiar with Lattice products or just want to get a quick feel of what this kit provides, use the *LatticeECP2M PCIe Demo Quick Start Guide* included with this kit to get started and use this guide to reference more detailed information. Please be aware that it is not necessary to install the ispLEVER software to set up your board and run the demos.

Introduction About this Guide

# **Learning Objectives**

After you complete the steps in this guide, you will learn how to do the following:

- Set up the solutions board properly and become familiar with its main features.

- Install all applicable development tools and the PCI Express demonstration applications.

- Establish communication with the solutions board through the PCIe link.

- Run the PCIe Basic demo, which allows you to run the preset LED light sequence, interactively light LED segments, and familiarize yourself with other features of the software.

- Run the PCIe Throughput demo, which allows you to see the performance of the Lattice PCI Express SERDES hardware and PCI Express IP core in terms of maximum data rates for writes/reads to and from your system memory.

- Run the DMA demos and observe how the Scatter-Gather DMA IP core, together with the PCIe IP core, demonstrate data transfer between the Lattice FPGA and system memory using the solutions board.

- Use what each demo teaches you about designing Lattice PCI Express solutions.

- Become familiar with an approach that will enable you to modify and rebuild the PCle Basic demo for your own purposes.

- Become familiar with the software development tools and major design flow steps employed in this kit.

- Use other existing documentation in conjunction with this guide.

You can obtain more detailed information on specific board features by referring to the *EB33*, *LatticeECP2M PCI Express Evaluation Board User's Guide* document. See the "Related Documentation" section for instructions for obtaining all related documentation.

In addition to reading this guide, you should visit the LatticeECP2M PCI Express Development Kit web page on the Lattice Semiconductor Web site and familiarize yourself with the set of other documents related to PCIe and refer to other user guides and references that may provide more detail. See "Related Documentation" for details. This document assumes that you have already installed ispLEVER and are familiar with basics tasks in Project Navigator. If not, you must also refer to the ispLEVER Help system.

Introduction Related Documentation

# **Related Documentation**

In addition to using this guide to help you get started developing the PCI Express solution on your device, you can refer to other documents applicable to this guide that may contain more detailed information that is beyond the scope of this guide. See the <kit\_dir>\Documentation folder contents for most related documentation.

All of the following documents can be obtained on the Lattice web site at www.latticesemi.com or are contained within the kit installation:

- LatticeECP2M PCIe Demo Quick Start Guide This guide, which is included in this kit, provides the basics of board setup and instructions for quickly running the demo applications without having to install the ispLEVER software. This guide is for Windows PC users.

- ◆ EB33, LatticeECP2M PCI Express Solutions Evaluation Board User's Guide – Describes board features, power requirements, device programming, clock management, and board schematics in detail. This document is available within the kit installation.

- IPUG75, LatticeECP2M PCI Express 1.1 x1, x4 Endpoint IP Cores User's Guide Describes the features that the x1 and x4 Endpoint IP Cores support and provides a functional description of the IPs, parameters, signals, port lists, timing diagrams, memory maps, and step-by-step procedures for creating the core in IPexpress. This document is also available within the kit installation.

- ◆ UG06, Lattice PCI Express x4 Scatter-Gather DMA Demo Verilog Source Code User's Guide – Provides details of the Verilog code used for the Lattice PCI Express x4 Scatter-Gather DMA demo application.

- UG07, Lattice PCI Express x4 SFIF Demo Verilog Source Code User's Guide – Provides details of the Verilog code used for the Lattice PCI Express x4 SFIF Demo, referred to in this document as the Throughput demo.

- UG15, Lattice PCI Express Basic Demo Verilog Source Code User's Guide – Provides details of the Verilog code used for the Lattice PCI Express Basic demo, a block diagram of the design, and descriptions of design modules. Instructions for building the demo design in ispLEVER are also included.

- Lattice PCI Express Software Development Resources An HTML page named PCIeDocIndex.html is included in this kit in the <kit\_dir>\Software path. This page links to many other reference documents that provide information on the demo source code, device drivers, API library, and development environment.

- PCI Express Development Kit for LatticeECP2M Web Page Visit this web page on the Lattice web site for updates to this and other related documents. You can also download kit installation files from this page as an alternative to using kit CD-ROMs. To access this web page, go to www.latticesemi.com and go to the Products > DevKits and Hardware > Development Kits hyperlink. Click on the LatticeECP2M PCI Express Development Kit hyperlink.

Introduction Related Documentation

◆ LatticeECP2M PCI Express x4 Evaluation Board Web Page – Links to the web page on the Lattice Semiconductor Web site for this part. On the Lattice web site, go to www.latticesemi.com/boards, click Low-Cost FPGA Boards, and then click LatticeECP2M PCI Express x4 Evaluation Board.

- ◆ PCI Express x1 Endpoint Optimized for LatticeECP2M Web Page Links to the web page on the Lattice Semiconductor Web site for this IP core. On the Lattice web site, go to the Products > Intellectual Property > Lattice IP Cores > PCI Express x1 Endpoint hyperlink. Be aware that the core for this design is not compatible with this kit.

- ◆ PCI Express x4 Endpoint Optimized for LatticeECP2M Web Page Links to the web page on the Lattice Semiconductor Web site for this IP core. On the Lattice web site, go to the Products > Intellectual Property > Lattice IP Cores > PCI Express x4 Endpoint hyperlink.

- ispLEVER Installation Guides Links to the web page on the Lattice Semiconductor web site for downloading the Windows and Linux versions of this document which describes ispLEVER design software installation. On the Lattice web site, go to the Documents > Installation Guides > ispLEVER link.

- ispDOWNLOAD<sup>TM</sup> Cables For Programming Lattice ISP Devices −

Describes all aspects of the download cable designed for use with this kit.

#### Note

Go to the Documentation directory in the kit to access the PDF documents or access these references by going out to the Lattice web site at www.latticesemi.com. The ispLEVER Help system is available from within the software. The PDF file of this document that is included with this kit contains active hyperlinks to directly access these files.

# Getting Started with the Development Kit

This chapter describes all of the items that come with your Lattice PCI Express (PCIe) Development Kit, including the necessary software and all installation information for the PCIe Demo Software. We recommend that you familiarize yourself with the contents of this chapter before proceeding to board setup and running the software tools.

# **Before You Start**

Review this section to understand what is included in this kit.

# **Development Kit Contents**

The following items are included in your PCIe Development Kit. Please ensure that your kit contains these items listed below:

- LatticeECP2M-50 PCI Express Solutions Board (x1 and x4)

- ispDOWNLOAD<sup>TM</sup> (USBN-2A) cable

- 12V DC wall adapter

- All ispLEVER 7.1 software CD-ROMs are included for Windows and Linux. This is a full-featured version with a 60-day evaluation license.

- Two kit CD-ROMs:

- LatticeECP2M PCI Express Development Kit (Windows Version)

- LatticeECP2M PCI Express Development Kit (Linux Version)

These CD-ROMs include the hardware reference design, PCIe IP Demo software, IP cores, ispVM software, and any related kit documentation.

If you are missing any of the above items, please contact technical support at at techsupport@latticesemi.com.

# **Development Tools**

This section describes the development software contained in this kit and required licensing. The kit CD-ROM contains the following software and tools necessary to successfully use this kit:

- Lattice ispLEVER 7.1 or later design software (Windows and Linux)

- Lattice PCIe IP Demo Designs and Application Software (Windows and Linux)

- Lattice ispVM Download System Software (Windows and Linux)

The ispLEVER software is a comprehensive FPGA design environment to be used in conjunction with the PCI Express IP Demo. Using the ispLEVER software, you can develop hardware design files, synthesize your netlist, and output a bitstream file to configure your target FPGA. Use the ispLEVER design software to locate your I/O pins, apply timing constraints, and to perform timing analysis on your FPGA design. The ispVM software is bundled with ispLEVER.

# Installing ispLEVER (Windows/Linux)

This kit includes the ispLEVER 7.1 FPGA design software. Separate installation CDs are included for both Windows and Linux. If you do not already have a licensed copy of ispLEVER 7.1, install the supplied 60-day evaluation version on your system.

#### Note:

For more information, see the ispLEVER installation notice for both Windows and Linux versions. You can access this documentation on the Lattice web site at www.latticesemi.com. Go to the **Documents > Installation Guides** navigation menu option.

To install ispLEVER for Windows:

- 1. Insert the ispLEVER software CD-ROM 1 or the DVD-ROM into the drive.

- In the ispLEVER Setup window, click Install ispLEVER Design Tools and follow the rest of the wizard prompts to install into the desired directory location.

To install ispLEVER for Linux:

- Insert the ispLEVER software CD-ROM 1 or DVD into the disk drive and mount the installation disk. If you are installing from a network, mount the drive by making a directory mount point and using the proper mount argument.

- 2. Specify a path location for installing the ispLEVER software, create a directory, and change to that directory, as in this example:

```

mkdir <path>/<install_path>

cd <path>/<install_path>

```

3. Execute the **install.csh** script located on the disk with the path to the installation disk as its argument:

```

<CD/DVD_Mount_Path>/install.csh <CD/DVD_Mount_Path>

```

Enter "Y" in the command line when prompted with the question, "Do you want to install all of ispLEVER Design Tools? ([Y]/N)." Make other selections based on your specific needs.

#### Licensing ispLEVER

You must have a licensed version of the ispLEVER FPGA design software (7.1 version or later) to work with this kit. The copy of the ispLEVER software included in this kit provides a 60-day evaluation license of the full production version of the software.

To license the kit's ispLEVER software on the Lattice web site:

1. Go to www.latticesemi.com/license. The Software Licensing page opens.

#### Note:

If you are not logged in, you will by prompted to do so on the Lattice Account Sign In page. If you do not have a user account you will have to set one up by following the instructions. You may have to return to the Software Licensing page after online user registration is completed.

- Under ispLEVER Design Kit, click Request a license.

- 3. In the **Software License Request Form**, provide the following information to complete licensing:

- Your full contact information, if you do not already have an account with this information.

- Development kit serial number (included on the SAVE ME card in the package)

- NIC/MAC address or server host ID. A NIC (Network Interface Card) or MAC (Media Access Controller) address is your machine's physical address.

On PC, enter **ipconfig -all** or **ipconfig/all** in the DOS command prompt. A machine profile appears that lists a Physical Address, a 12-digit hexadecimal number that should start with a zero, similar to 00-08-75-C6-59-01. If you get two physical addresses, do not use the one that begins with a 4. For Linux, use the **arp -a** command, look for your machine name in the ARP table listing, and your physical address will be shown in far right column.

4. After entering all required information in the form, click **Submit**.

You can also send your licensing information to the e-mail address lic\_admn@latticesemi.com if for some reason you do not have access to this web site.

#### Installing ispVM System Software

To ensure proper device configuration and support, you must upgrade your currently installed version of ispVM with the one supplied with the kit. These upgrades are also available for download on the web.

To install ispVM on Windows:

Unzip the ispvmsystem.zip file on the Windows development kit CD and extract its contents into the <isplever\_install\_dir>\ispvmsystem directory to overwrite the present files.

To install ispVM on Linux:

Unzip and untar the ispvm\_v17\_2\_1\_linux.tar.gz in the Linux development kit CD and extract its contents into the <isplever\_install\_dir> directory to overwrite the present files. Documentation for installation and environment variable setup is provided.

#### Downloading the Kit from the Web

You can download and install all of the necessary kit installation files and this document on the *PCI Express Development Kit for LatticeECP2M Web Page*. To access this web page, go to www.latticesemi.com/pciedevkit.

# **Device Configuration Software and Cable**

The LatticeECP2M PCIe Solutions board is already pre-programmed with a hardware reference design that supports the PCIe Basic demo. There is no need to download anything to the device on the board to complete this demonstration but the other demos require downloading appropriate bitstream included in the kit.

When need to reconfigure the device to run a different demo, you will need to use the ispVM System software for download and the necessary download cable. See the section "Reprogramming the Solutions Board" on page 18 for details on how to reprogram the on-board device.

- You can use the Lattice ispVM software for downloading bitstreams for device configuration. This tool is integrated with the ispLEVER software. The latest version of ispVM System is always available for download from the Lattice web site at www.latticesemi.com/ispvm.

- ispDOWNLOAD<sup>TM</sup> cable is used for connection to and programming of the device. See the ispDownload Cable for PCs web page on the Lattice web site for more information and to obtain the ispDOWNLOAD Cables data sheet that is available online. On the Lattice web site, go to the Products > Dev Kits and Hardware > Programming Cables hyperlink.

#### **Hardware Requirements**

To install the kit design and run the demo software, a single computer with a PCIe x16, x8, x4, or x1 slot is required. You must also have a powered USB port. All of the other hardware and drivers are included in the kit.

#### **Software Requirements**

Please be aware of the following software requirements to ensure you obtain the expected results for the procedures described in this guide:

- For Windows, the Lattice PCI Express IP demo is compatible with Microsoft Windows 2000, Windows XP Professional, or Windows Server 2003 32-bit platforms.

- For Linux, the supplied files were built and tested for Red Hat Workstation 4.0, Update 4 on a 32-bit machine; however, instructions in Appendix A are provided for building necessary drivers for any kernel version you may be running. Refer to Appendix A, "Installing and Running the Development Kit in Linux" on page 57 for all Linux install instructions.

- The Verilog HDL demo design projects in this kit are built with ispLEVER 7.1. If you do not have an existing licensed copy of this version already installed on your machine, you can install the supplied ispLEVER 7.1 60day evaluation software.

- If you are using ispVM device configuration software for your downloads, ensure you are using the latest version to ensure proper bitstream downloading results. The kit includes ispVM on the Windows and Linux kit CD-ROMs. You can also obtain this software on the Lattice web site at www.latticesemi.com/ispvm.

- To develop PCIe designs, your computer must meet minimum system requirements as described in the ispLEVER Installation Notice. You can obtain a copy on the Lattice web site at www.latticesemi.com. Choose Documents > Installation Guides in the main navigation bar.

# Installing the PCIe Development Kit

This section provides Windows installation instructions for the PCIe development kit files and demo applications. See Appendix A for corresponding Linux kit installation instructions.

To install the development kit on Windows:

- Load the kit CD-ROM in your CD drive and navigate to it using Windows Explorer.

- On the kit CD-ROM, double click the setup.exe file.

- 3. If the **Install Program as Other User** dialog appears, choose to install as the current user if you have Administrator privileges or select another user with those privileges and click **OK**.

- Click Next to start the installation. You must have administrative privileges to install the kit.

- 5. Click **Yes** to accept the license agreement.

- 6. Click **Next** to install the kit in the default *C:\Lattice\_DevKits* location on your hard drive or install in the desired location by using the **Browse** button.

- 7. If desired, click **Yes** to accept prompt to create shortcut desktop icons for the kit demo applications.

- 8. Click **Finish** to complete the kit installation. Figure 1 on page 10 shows the directory structure of the installed PCIe development kit.

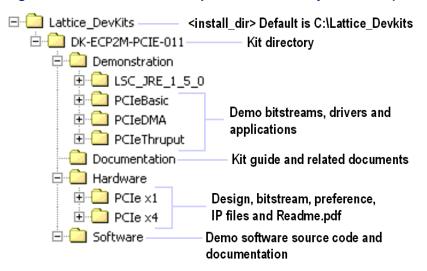

Figure 1: Installed PCIe Development Kit Directory Structure (Windows)

Figure 1 above shows the default installation path for Windows. Please note that whenever the kit directory or <kit\_dir> is referred to in this document, it refers to the <install\_dir>\DK-ECP2M-PCIE-011\ file path, where the default <install\_dir> path is C:\Lattice\_Devkits.

The demo software source code is provided in the <code><kit\_dir>\Software</code> directory in the various demo subdirectories. Readme text and HTML files are available for demos and IP cores in the Demonstration demo subdirectories in the applicable Hardware subdirectories. Applicable bitstream files for each demo design are located in the Bitstream folder in the directory path <code><kit\_dir>\Demonstration\PCle<demo\_name></code>, for example, the PCleBasic folder is the first of three demo folders that contain bitstream configuration and demo application files.

After you install the development kit, on PC, you will also see Start Menu shortcuts for running demo applications if you opted to create them during installation. Please go to the following sections for further sequential instructions.

# PCIe Solutions Board Setup and Installation

This part of this document describes what you need to know to get started using the solutions board for the PCI Express (PCIe) Development Kit.

# **The PCIe Solutions Board**

The LatticeECP2M-50 PCIe solutions board can be used as a basis for prototyping complex PCI Express solutions.

The PCIe solutions board is equipped with a Lattice ECP2M-50 FPGA device. The board is already pre-configured with the PCIe Basic demo reference design that is also available on the CD-ROM that comes with this kit.

An enhanced form-factor of the PCI Express add-in card specification, the board allows for full x1 form-factor compliance. The x4 is available for demonstration purposes but with some non-standard form-factor issues. To demonstrate both x1 and x4 configurations you can simply change the mounting hardware. The board has several debugging and analysis features. See the document EB33, LatticeECP2M PCI Express Evaluation Board User's Guide for more details on board specifications and features outside the scope of this kit document.

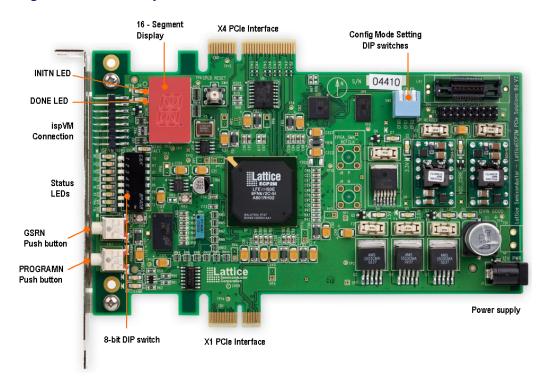

Figure 2, "Interface Layout of the PCIe Solutions Board" on page 12 shows you the various LED indicators and other on-board interfaces that you will encounter during an evaluation of the solutions board. This diagram is given to simply provide a quick overview of these features.

To learn more about the details of the board design and features, refer to the *EB33, LatticeECP2M PCI Express Evaluation Board User's Guide*. The scope of that guide goes into much more detail about the hardware components and their features than the scope of this document.

Figure 2: Interface Layout of the PCle Solutions Board

# **Unpacking and Inspecting the Solutions Board**

This section describes the proper steps to take to unpack the board to visually inspect its layout. There is very little setup necessary for this kit.

To unpack and inspect the Lattice PCIe solutions board:

- Remove the PCIe solutions board and accessories from its antistatic packaging and compare the kit's contents to the packaging list. Ensure that you avoid situations that would create electrostatic discharge (ESD) during setup or use of the board.

- 2. Position the board to view the x1 mode side as shown in the Figure 2 diagram and familiarize yourself with its basic layout and features. This document uses the x1 mode in procedures. You can test in the x4 mode but procedures will no longer apply in most cases.

- Ensure that all configuration mode setting SW1 dip switches are pushed down toward the board as shown in Figure 3, "Configuration Mode Setting Dip Switches in "On" Position" on page 13.

- 4. Follow the procedures in the section, "Hardware Installation" which begin on page 13. You must have a PC with a PCle slot available to proceed.

Figure 3: Configuration Mode Setting Dip Switches in "On" Position

# **Hardware Installation**

The procedures in this section provide step-by-step instructions for installing hardware and drivers to ensure proper board and PC communication and operation. These procedures are meant to supplement the section "Unpacking and Inspecting the Solutions Board" on page 12.

# **Installing the Solutions Board Hardware**

After board setup, you can install the hardware. You must have administrative privileges on Windows to perform this installation. See Appendix A for Linux corresponding instructions.

#### Caution:

Lattice is not liable for any loss of data or damages that may result from the installation of the hardware and execution of the kit demo software tools. Do not install and operate on mission-critical systems.

To install the Lattice PCI Express Solutions Board for Windows:

- 1. Shut down Windows, turn off the PC and unplug the power cord.

- **IMPORTANT:** This step is necessary because PC power supplies have standby voltages that are present even when the PC power light and fan are turned off. Unplugging the PC is the safest way to ensure the board will not be "hot-swapped".

- 2. Locate an available PCI Express slot. The board can be installed in any slot that is larger than the finger edges in use, x1, x4, or x16.

- 3. Ensure that the solutions board is *not* connected to any external power supply before proceeding.

- 4. Using ESD precautions, install the LatticeECP2M PCI Express Solutions Board in the PCI Express slot in the x1 position.

#### Note:

This guide's procedures do not describe the x4 implementation on the other side of the LatticeECP2M solutions board; however, you can use this in a similar fashion.

- 5. Power-on the PC and observe that it boots normally to the Windows login screen. If anything abnormal occurs, refer to Appendix B, "Troubleshooting" on page 63.

- 6. Log in as a user with administrative privileges. During the login process Windows will detect the new hardware and ask if you want to install it.

#### **Installing Solutions Board Drivers**

This section describes installation of the solutions board device driver software on a Windows PC. This procedure pertains specifically to the PCIe Basic demo application. For the PCIe Throughput and DMA demos, you will need to load the appropriate drivers from the respective demo folders.

Also note that this procedure describes the installation on the Windows XP platform only. This may vary slightly on Windows 2000 or Windows Server 2003. See Appendix A for corresponding Linux instructions.

#### Note:

The **Found New Hardware** popup dialog in Windows appears when the PC is first booted with the solutions board installed. If this screen does not appear, the solutions board was not properly detected by the PC BIOS or by Windows. Refer to Appendix B, "Troubleshooting" on page 63 for more information.

To install the solutions board drivers on Windows:

- 1. In the Found New Hardware popup dialog, choose the **Install from** specific location option and click **Next**.

- 2. Use the **Browse** button to navigate to where you installed the demo package, locate the *Demonstration\PCleBasic* directory path on the top level of the kit directory, and select the *Driver* folder.

#### Note:

For the PCIe Throughput and DMA demos used in this kit, you will have to install the appropriate drivers located in the similar directory path but in the *PCIe Thruput* and *PCIeDMA* folders, *respectively*.

Click Next. Windows now copies the driver files and will display a screen indicating this. Upon completion, a capital "I" representing initialization will be displayed on the 16-segment solutions board LED.

To verify proper driver installation and device recognition on Windows:

- 1. Right click on the **My Computer** icon on your Windows desktop and choose **Properties** from the popup menu. Confirm the installation and verify that Windows properly detects the solutions board hardware.

- In the System Properties dialog, choose the Hardware tab and click the Device Manager button. The Lattice Evaluation Board (LSC\_PCI Express) should be in the list of hardware devices in your system.

- Right click on the Lattice Eval Board icon and select Properties to show the resources assigned to the device and the driver information.

- Memory ranges corresponding to the configured BAR registers will be assigned to the board. If this is all present, then the demo program is able to run and access the hardware on the solutions board.

# **Installing Hardware into a Different Slot**

Windows identifies PCI/PCI Express hardware devices using the bus, slot, vendor ID, and device ID fields. If you install the board into a different slot, the slot number will change. This will cause Windows to display the **Found New Hardware** popup screen when the system powers up.

The full procedure described in the previous section "Installing Solutions Board Drivers" to install the driver is unnecessary since the driver has already been installed. If the board is installed in a new slot, simply choose to allow Windows to search for the driver or the **Install the software automatically (Recommended)** option and install automatically. Windows will then associate the newly created device registry tag (bus, slot, vendor and device ID) with the *Iscpcie.sys* driver and the demo GUI will work with the board in the new slot.

Now that your board is set up and hardware is installed on your computer, you can proceed on to the next chapter which describes software installation, execution, and tasks to complete the demo. The remaining sections in this chapter supplement what is described in the board setup procedure.

# **Verifying Correct Board Operation**

The section lists checks you should make to ensure proper functioning of the board. Also refer to related documentation on this board described in the document *EB33, LatticeECP2M PCI Express Solutions Evaluation Board User's Guide.* For part references, see Figure 2, "Interface Layout of the PCIe Solutions Board" on page 12.

There are four status LED lights on the board that will go through a light sequence when the device is first powered on. To verify the PCIe link is functioning properly, examine these indicators at the time of powering up. The PCIe demonstration software used later in the kit verifies board operation. In addition, you can also check that the Status LED lights are functioning at normal conditions in the sections below.

#### Note:

All boards leave the manufacturer fully tested. See the document *EB33*, *LatticeECP2M PCI Express Solutions Evaluation Board User's Guide* for details.

#### **LED Definitions**

The Status LEDs on the LatticeECP2M PCI Express Solutions Board are located vertically along the left edge, middle portion of the board. Refer to the diagram shown in Figure 2, "Interface Layout of the PCIe Solutions Board" on page 12.

The LEDs are in the following order and have the following functions shown in the tables below.

**Table 1: LED Order and Functionality**

| LED Name                               | LED Number                | Color  | Usage                                                                                                             |

|----------------------------------------|---------------------------|--------|-------------------------------------------------------------------------------------------------------------------|

| U0                                     | D20 (x1)                  | Blue   | User LED. Off by default.                                                                                         |

|                                        | D28 (x4)                  |        |                                                                                                                   |

| U1                                     | D21(x1)                   | Blue   | User LED. Off by default.                                                                                         |

|                                        | D29 (x4)                  |        |                                                                                                                   |

| U2                                     | D16 (x1)                  | Red    | User LED. Off by default.                                                                                         |

|                                        | D25 (x4)                  |        |                                                                                                                   |

| U3                                     | D17 (x1)                  | Red    | User LED. Off by default.                                                                                         |

|                                        | D24 (x4)                  |        |                                                                                                                   |

| DL_UP                                  | D14 (x1)                  | Green  | Data Link up, ready for packets at                                                                                |

|                                        | D22 (x4)                  |        | Transaction Layer (PCI enumeration of config registers).                                                          |

| LO                                     | D15 (x1)                  | Green  | L0 training sequences completed,                                                                                  |

|                                        | D23 (x4)                  |        | PHY Layer up and ready for flow control.                                                                          |

| POLL                                   | D18 (x1)                  | Yellow | Polling.                                                                                                          |

|                                        | D26 (x4)                  |        |                                                                                                                   |

| PLL                                    | D19 (x1)                  | Yellow | PLL locked to PCI Express 100MHz                                                                                  |

|                                        | D27 (x4)                  |        | clock.                                                                                                            |

| 16-Segment<br>Display                  | On board                  | Red    | 16-seg will display states with letter codes as described below:                                                  |

|                                        |                           |        | <ul><li>I – Initialization; driver is loaded<br/>and initializes the board</li></ul>                              |

|                                        |                           |        | O – Open; demo program is run and driver opens access to board.                                                   |

|                                        |                           |        | C – Close; demo exits and driver closes access to board.                                                          |

|                                        |                           |        | R – Remove; driver reads that board is removed from system, as in uninstalled device.                             |

|                                        |                           |        | E = Error; driver detects board hardware error during initialization.                                             |

| 16-Segment<br>Display<br>Decimal Point | On display in lower right | Red    | Blinks to indicate PCIe transaction is accessing registers or memory in demo IP. Indicates PCIe bus transactions. |

Table 2: Normal x4 and x1 Link Status

| PLL | POLL | L0  | DL_UP |

|-----|------|-----|-------|

| YLW | YLW  | GRN | GRN   |

# **Default Switch Settings**

The following table shows the default switch settings on the board.

| Switch | Default Setting                                                                                                                                                     |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW1    | All ON, (in towards circuit board). The FPGA CFG pins are set on the board for a particular programming mode via the SW1 DIP switch for the x1 board configuration. |

# **Reprogramming the Solutions Board**

The PCIe solutions board comes pre-programmed with the PCIe Basic demo bitstream. Other demos included with this kit require that you reprogram the device with the appropriate bitstream for that particular demo.

That is, each demo, including x1 and x4 variations, has bitstreams that contain different PCI Subsystem IDs that uniquely identify the demo and associates it with a particular device driver and demo application. So, if using the x1 side of the board, ensure that you use the bitstream (or XCF file) with the x1 identifier in the file name.

#### Important:

Only connect or disconnect the ispVM download cable from the solutions board when the power is off. Damage to the devices in the JTAG scan can occur if the board is turned on. This means that if you have a board installed in the PC running ispVM, you must shut down the PC before connecting the cable to the board. It can remain connected thereafter.

To reprogram the solutions board with new bitstream:

- 1. After ensuring that ispVM has been installed and configured, attach the programming cable to the board with the power off.

- 2. After the cable has been attached, power on the board.

- From the Windows Start menu, click Start > Programs > Lattice

Semiconductor 7.1 > Accessories > ispVM System to open ispVM.

- 4. Click **File > Open** and navigate to the appropriate XCF file. For the PCIe Basic demo, go to the <install\_dir>\Demonstration\PCIeBasic\Bitstreams path to the file **PCIeSBx1\_ECP2M50\_PCIeBasic.xcf**.

#### Note:

Ignore any messages you may encounter about the file being modified. The date and time of the file may have been changed during installation and no longer matches the XCF file's internal date.

- 5. In the ispVM main window, double click the appropriate XCF file.

- Observe the selected options in the Device Information dialog. The Device Access Option should be set to **SPI Flash Programming**. Verify that the **File Name** shows the appropriate x1 configuration, (i.e., as opposed to x4) and select **Edit Device** and change the .bit file if necessary. Go to **ispVM > Options > Cable and I/O Port Setup > Cable Type** and ensure you use the **USB** cable type.

- 6. Click the **Go** button to initiate your download. You must wait while the flash chip on the board is programmed.

- Check the Chain Configuration status to see if the download received a **Pass** status. A processing status bar appears to show you the progress of the download. Upon completion, bitstream is programmed into SPI flash memory.

- 7. Push in the PROGRAM button on the board to program your device from SPI flash memory.

- 8. After programming the device, shut down and then reboot your PC. You must do this so Windows recognizes the new PCI registers and loads the proper driver.

- 9. If this is the first time this demo bitstream has been run, Windows will identify the board as new hardware and the driver for that demo needs to be loaded. The corresponding driver is in the Driver directory of each demo. See "Installing Solutions Board Drivers" on page 15 for instructions.

#### Note:

If an error about starting the device occurs during driver installation, use the Device Manager to disable and then re-enable the board. Or, you can reboot your PC.

4

# Running the PCI Express Basic Demo

Once you have installed your PCIe solutions board in your computer and installed all necessary software, you can run the PCI Express (PCIe) Basic demo which consists of hardware, IP and software. This part of the document describes what you need to know to get started and successfully complete this demo.

# **Before You Begin**

Before beginning this demo, you must do the following operations.

Use ispVM to download the bitstream for this demo to the solutions board.

You can find the x1 and x4 bitstreams and the XCF file necessary for ispVM in the <kit\_dir>\Demonstration\PCleBasic\Bitstreams directory path.

For general information ispDOWNLOAD cable on ispVM configuration software usage, see the following:

- Download procedure described in the section, "Reprogramming the Solutions Board" on page 18.

- General introduction to device configuration with ispDOWNLOAD cable and ispVM software described in section, "Device Configuration Software and Cable" on page 8.

- ispVM Help system

- Install the board drivers for the application.

You can find the driver files necessary for proper demo installation in the <a href="https://kit\_dir>\Demonstration\PCleBasic\Driver">kit\_dir>\Demonstration\PCleBasic\Driver</a> directory path. See the procedure in section, "Installing Solutions Board Drivers" on page 15 for guidance.

#### **Resource References**

Please be aware of the specific companion documentation for supplementing your knowledge when using this demo:

#### **Hardware Resources**

The PCIe Basic Demo x1 bitstream is built from the ispLEVER project located in Hardware\PCIex1\ecp2m50\_PCIeBASIC\_SBx1\Implementation\ ecp2m50\_PCIeBasic\_SBx1 directory. The Verilog source code is located in the project Source\ directory.

The Verilog design architecture is explained in Documentation\ECP2M PCI Express Basic Reference Design User Guide\UG15.pdf. This document describes the purpose and functionality of the Verilog modules used in PCIe Basic Demo design.

#### **Software Resources**

The PCIe Basic Demo uses the Iscpcie2.sys device driver. The source code for this device driver is located in Software\Iscpcie2\_Win2kXP\drvr. The architecture of the Iscpcie2 device driver is explained in the "Iscpcie2 Driver Reference Manual" which can be accessed through the Software\PCIeDocIndex.html link.

The PCIe Basic Demo application source code is located in Software\PCIeBasic\_Win2kXP\BasicGUI\DemoUI. This directory contains the Java project source code to create the user interface. The GUI also uses the PCIeAPI\_Lib\_Win2kXP API library.

The architecture of the PCIe Basic Demo application is explained in the "PCIe Basic Demo Reference Manual" and "PCIe API Reference Manual" which can be accessed through the Software\ PCIeDocIndex.html link.

# **Basic Demo Operations Overview**

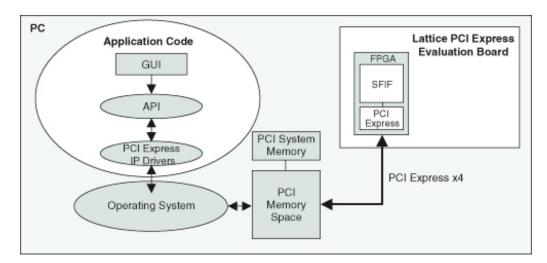

The PCIe Basic demo shows the capabilities of the Lattice FPGA and the PCI Express IP core functioning in a PCI Express slot in a Windows PC. The demo is easy to use and requires no test equipment.

This demo software allows you to access memory and registers on the board and provides real-time interaction with the solutions board hardware to demonstrate a functional PCI Express communications path between the application and driver software (running on the PC CPU) and the FPGA IP. Device driver and application source code are available so you can modify and extend the behavior of the tests or use them as a starting point for new PCIe designs.

If you experience any problems running this demo, please refer to Appendix B, "Troubleshooting" on page 63.

# **Running the PCIe Basic Demo Software**

This section describes how to run the PCI Demo software after installation. You can access the PCIe Basic demo software from the Windows Start Menu.

To run the PCIe Basic demo software from your PC:

From the Windows desktop, choose Start > Programs > LatticeECP2M

PCI Express Development Kit > PCle Basic Demo.

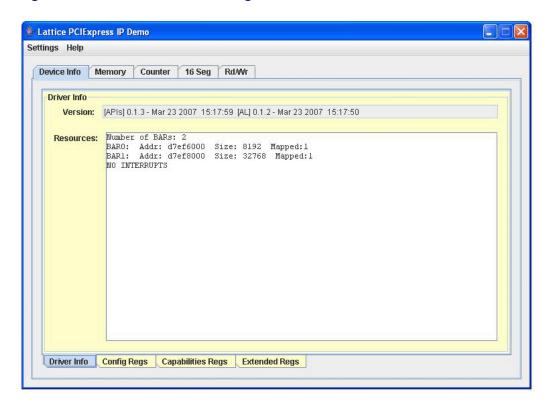

The graphical user interface opens the PCIe Basic demo software with the Device Info tab activated as shown in Figure 4 below.

Figure 4: PCIe Demo Device Info Page

The Device Info page displays information about the device driver and the device's PCI configuration registers. The data displayed is for informational purposes only and cannot be edited. Descriptions of all of the information you can view in this page are available in the beginning of the next section "Touring the PCIe Basic Demo Interface".

# **Touring the PCIe Basic Demo Interface**

After opening the PCIe Basic demo software, this section will describe the pages and features in the interface.

In the Device Info page, click on the **Device Info sub tabs** and observe

the structure of the information that is displayed in each. The following

table describes what information is available for viewing by clicking each

of the sub tabs that you can select and are located at the bottom of the

page dialog.

**Table 3: Device Info Page Sub Tab Descriptions**

| Sub Tab Page      | Information Description                                                                                                                                                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Driver Info       | Obtained from the Lattice solutions board PCI Config space registers by the Lattice PCI Express driver when the demo is started. Displays Windows resources assigned to the device driver to access the solutions board. |

| Config Regs       | Displays the standard PCI Config type 0 registers with each field annotated. Displaying this page causes the driver to issue PCI Config Type 0 read requests and redisplays the register values.                         |

| Capabilities Regs | Displays the PCI Express capabilities structures that are found in the register range 0x40 to 0xff. The applicable bit-fields of registers are parsed and displayed in readable format.                                  |

| Extended Regs     | Displays PCI Express extended configuration registers which are not used in this demo. These are inaccessible through the PC.                                                                                            |

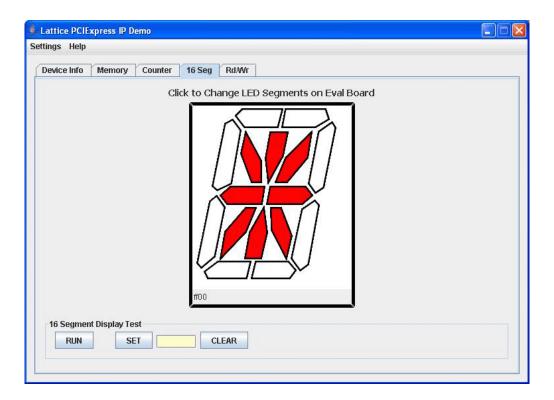

- Now click on the 16 Seg tab to see the contents of the 16 Segment Control page. In this page, you will be running a demonstration LED sequence and controlling the display on your board from this console. See Figure 5, "PCIe Basic Demo 16 Segment Control Page" on page 25.

- The 16-Segment Control page provides a way to interactively light segments on the display. You can preset character sequences from this page or select single characters and run them to light the display.

- The states of the LED segments are converted to a 16-bit word value (each segment is controlled by a bit) and written to the LED control register in the GPIO portion of the IP in the FPGA. This demonstrates a memory write across the PCI Express bus.

- 3. In the 16 Segment Control page, click the **Run** button. Notice on the board how the sequence of LED lights run in a certain pattern on the display.

- The 16-segment display has two test modes. In the first mode demonstrated here, a pre-set sequence of segments are lit and characters are written to the display.

This LED sequence run takes approximately 30 seconds to complete. You must observe the 16-segment LEDs to see if it is operating correctly. The correct sequence is:

- Light all segments, one at a time, around the perimeter.

- Light all inner segments in a clock-wise order.

- Turn off all inner segments in reverse order.

- Turn off all outer segments in reverse order.

- Write the characters "LATTICE\*" one at a time to the display.

- ◆ The "\*" will be displayed when the test ends.

Figure 5: PCIe Basic Demo 16 Segment Control Page

See the Table 4 below for details about features on the 16 Segment Control page.

**Table 4: 16 Segment Control Page Features**

| Feature     | Description                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------|

| LED Display | Allows you to interactively change the LED display using mouse clicks to toggle segments on and off. |

| RUN         | Starts an LED light sequence or command operation.                                                   |

**Table 4: 16 Segment Control Page Features**

| Feature | Description                                                                                |

|---------|--------------------------------------------------------------------------------------------|

| SET     | Sets a user-defined LED light command operation based on input characters in the text box. |

| CLEAR   | Turns off all segments in the display.                                                     |

- Now click on any segment in the interactive segment display in 16

Segment Control page. Notice that any selection will immediately cause the corresponding segment on the LED to light on your solutions board's LED display.

- Clicking on a segment will turn it on or off (toggles). The 16-bit value written to the LED register in the FPGA is shown on the bottom left.

- 5. Now type any character in the text box and click the **Set** button. The character will be configured in the display.

- This second mode of operation allows a single character to be sent to the display. Any printable ASCII character can be displayed (lower case is displayed as upper case). You cannot write a blank character using SET.

- Click the Clear button. This turns off all segments of the LED display.

Right-clicking on the background area behind the segments will clear the entire display.

- The interactive 16 Segment Control page demonstration you just performed illustrates that a functional PCI Express communications path exists between the application and driver software that is running on the CPU and the FPGA IP. Continue on to learn more about the other pages in the PCIe Basic demo software and their features.

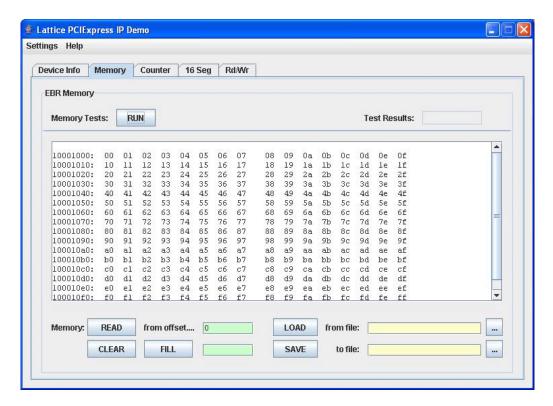

- 7. Next, click on the Memory tab to open the **Memory page**. The Memory tab has various memory access tests that can be run to show that the IP is accessible from host software via the PCI Express bus. Refer to graphic in Figure 6.

The page contains text boxes for entering data to be sent to device registers in the FPGA design. These text boxes are color coded to indicate the data format they accept. See the Table 5 below for details about these codes.

**Table 5: Memory Page Text Box Color Codes**

|            | , ,                                                                                                      |

|------------|----------------------------------------------------------------------------------------------------------|

| Color Code | Description                                                                                              |

| Green      | Indicates hex value fields. Do not include any prefixes (0x) or suffixes (H). Only digits are allowable. |

| Yellow     | Indicates character string fields, e.g., ones containing file names, paths, or letter values.            |

| Blue       | Indicates decimal (base 10) value fields.                                                                |

The Memory Page features allow you to test the access to the 16KB of EBR internal to the FPGA. Accesses are done on a byte basis. All 16KB memory locations are accessed successively, testing the PCIe link to the

memory interface. See Table 6, "Memory Page Features" on page 27 to see what actions can be performed in this page.

Figure 6: PCle Basic Demo Memory Page

The following table provides descriptions of all of the Memory page features.

**Table 6: Memory Page Features**

| Feature       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pattern Tests | Pressing Run starts a test to check that all locations of the EBR can be read and written and that the contents are correct. First, all 16KB are cleared to 0 and verified. Then various patterns (AA, 55, 01, FF) are written to all locations and verified. If everything passes, PASS is displayed. If a memory location has an incorrect value the test aborts and displays ERRORS! The memory contents are left with an incrementing pattern 00 01 02 that is displayed when the test successfully finishes. |

| READ          | The contents of the EBR memory are read from the value entered in the offset field. 256 bytes are read and displayed in the list box above.                                                                                                                                                                                                                                                                                                                                                                       |

| CLEAR         | Sets all 16KB to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FILL          | Writes the byte value entered in the field to all 16KB locations.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

**Table 6: Memory Page Features**

| Feature | Description                                                                                                                                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOAD    | Loads 16KB of binary data from the file specified (or as much data as is in the file) into EBR memory, starting at location 0. This can be used to load a known pattern into the EBR memory by using a file created by another tool. |

| SAVE    | Writes all 16KB of EBR memory to the file specified. This can be used to save the contents of EBR memory for off-line processing (i.e., to verify that the pattern loaded in with LOAD is correctly saved in the EBR).               |

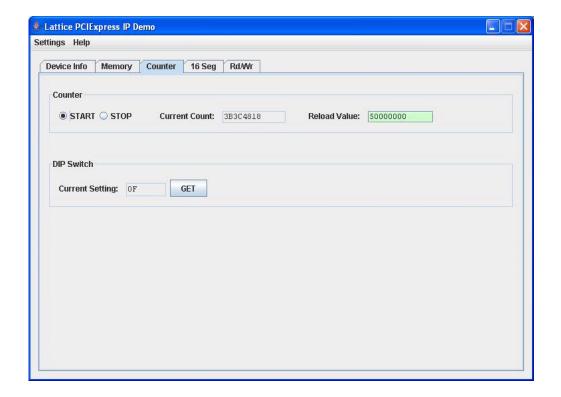

8. Next click on the Counter tab to open the **Counter page**. The Counter page allows you to control a 32-bit down counter in the FPGA hardware. The page is illustrated in Figure 7 below. Table 7, "Counter Page Features" on page 29 provides descriptions of the page's features.

The counter is driven by the 125 MHz clock that feeds the IP. The counter is started by selecting the Start radio button. Counting begins from the value entered into the Reload Value field. The current count value is displayed in the Current Count field.

Figure 7: PCIe Basic Demo Counter Page

The following table provides descriptions of all of the Counter page features.

**Table 7: Counter Page Features**

| Feature       | Description                                                                                                                                                                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START/STOP    | Starts and stops the 32-bit down counter in the FPGA hardware.                                                                                                                                                                                                  |

| Current Count | Displays the current count value.                                                                                                                                                                                                                               |

| Reload Value  | Sets the number from which counting begins.                                                                                                                                                                                                                     |

| DIP Switch    | The DIP switch section shows that user changes to the switches on the solutions board are seen by the application software on the PC. The GUI polls the DIP switch register 10 times per second and displays the value read from the 8-bit DIP switch register. |

| Get button    | Used to immediately update the value. This is active if No Polling was selected from the Settings dropdown menu.                                                                                                                                                |

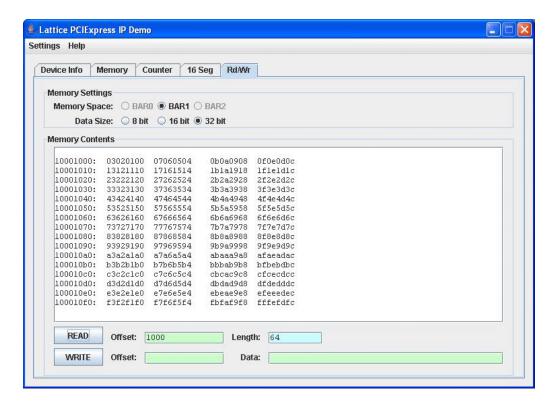

Finally, click on the Rd/Wr tab to open the Read/Write page. The Read/ Write page is used for looking at and poking at registers and EBR memory values in the application IP. Refer to Figure 8, "PCIe Basic Demo Read/ Write Page" on page 30.

The Read/Writer is primarily used for debugging and diagnosing the application IP registers. The following table provides descriptions of all of the Read/Write page features.

Table 8: Read/Write Page Features

| Feature         | Description                                                       |

|-----------------|-------------------------------------------------------------------|

| Memory Space    | Indicates the base address register (BAR) memory space to access. |

| Data Size       | Indicates bit size. Options are 8-bit, 16-bit, and 32-bit.        |

| Memory Contents | Displays memory contents.                                         |

| READ            | Starts a read data access based on offset and length settings.    |

| WRITE           | Starts a write data access based on offset and data settings.     |

Data accesses can be specified as byte, short or word operations by selecting the Data Size. Access is done to the selected Base Address Register (BAR). The memory contents are displayed in the window. In the address, the upper nibble (31:28) specifies the BAR being accessed. The following example shows reading the EBR memory (BAR 1, starting at offset 0x1000) in the application IP and displaying them in word format.

Data can be written to registers using the WRITE button. Specify the BAR Offset to start writing at and the hex data in the Data field. Separate each

Figure 8: PCIe Basic Demo Read/Write Page

value with a space. Data size should match the Data Size selected at the top of the page in Memory Settings.

Only BAR1 is accessible in the current demo. See the IP Register Memory Map section of *UG08 - Lattice PCI Express Demo User's Guide* for a list of valid device addresses. This document is available on the Lattice web site.

# Rebuilding the PCle Basic Demo Design

You can rebuild the PCIe Basic demo IP reference design by running the source HDL design files through a design flow in the ispLEVER software. All source HDL files and necessary project files are included in the kit installation. This document assumes that you have already installed ispLEVER and are familiar with basics tasks in Project Navigator. Refer to the figure, "Installed PCIe Development Kit Directory Structure (Windows)" on page 10 to understand where various files referenced in this section are located.

We recommend that you copy the files from the install location to a new working location. This allows you to quickly move back to the original configuration without re-installing this kit.

#### Implementing the PCIe Basic Demo Design

The **top.syn** ispLEVER project file is included in this kit. This file contains information regarding options to use when implementing the Demo design. The **top.lpf** logical preference file specifies timing constraints and ECP2M I/O pin assignments with respect to the ECP2M Standard PCIe board. The working directory is the Implementation directory.

To implement the demo design using the EDIF/NGO flow:

- 1. Open ispLEVER Project Navigator.

- 2. Click File > Open Project.

- 3. In the Open Project dialog, navigate to and the select the **top.syn** file in the <*kit\_dir>\Hardware\PCle x1\ecp2m50\_PCleBasic\_SBx1\*Implementation\ecp2m50\_PCleBasic\_SBx1 directory path.

- 4. Click **Open**. All of the HDL files are imported into the project.

- 5. In the Processes window, right click on **Build Database** and select Properties from the popup menu.

- 6. In the Properties dialog, verify that **Macro Search Path** is set to the directory path, **..\ispLeverGenCore\ecp2m\pciex4d1\** for Windows. Your path would have forward slashes for Linux.

- In ispLEVER Project Navigator, verify that the device select is a LFE2M50E-6F672C.

- 8. In Project Navigator, double click the **Generate Bitstream Data** process.

# Modifying the PCIe Basic Demo Design

This section provides a very simple alteration to the HDL to demonstrate a change in the behavior of the function of the LED light in the demo display. It will involve a small change in the HDL code in the source file.

To modify the PCIe Basic demo design:

- Open the top\_basic.v file with an ASCII editing tool or the internal ASCII editing tool in Project Navigator. This file is located in the <a href="https://kit\_dir>\Hardware\Source\ecp2m">kit\_dir>\Hardware\Source\ecp2m</a> directory path, where <a href="https://kit\_dir>represents the path">kit\_dir>\DK-ECP2M-PCIE-011</a>.

- 2. On or about the line 390 as shown below, delete the **tilde** character (~) that appears before the (**led\_out\_int**) parameter.

```

led_out <= ~(led_out_i);</pre>

```

- 3. After making this small change, click **File > Save** and close the editor.

- This modification to the code will cause the 16-segment LED to operate in reverse, that is, all of the lights will be on when the demo starts instead of off.

- Open the top.syn project file in ispLEVER's Project Navigator. This file is located in the ecp2m50\_PCleBasic\_SBx1 folder in the Hardware\PCle x1\ecp2m50\_PCleBasic\_SBx1\Implementation\ecp2m50\_PCleBasic\_SB x1 path.

- 5. Double click the **Generate Bitstream Data** process in the Processes window to generate a **top.bit** file in the directory <a href="https://kit\_dir>\textrm{Hardware\textrm{Implementation}}.">https://kit\_dir>\textrm{Implementation}.</a>

- 6. Start ispVM and perform the steps described in the section "Reprogramming the Solutions Board" on page 18 to download the new bitstream to the board's SPI flash memory.

- 7. Push in the PROGRAM button on the board to program your device from SPI flash memory.

- 8. Reboot the PC so that the BIOS recognizes the new PCIe endpoint device configuration.

- 9. Verify that the status LEDs are correct and note that all the LED segments are now on.

- 10. Rerun the LED test described in the section, "Touring the PCIe Basic Demo Interface" on page 24. Notice that the state of the 16-segment LED on the board is the inverse of what is displayed in the GUI.

You have completed the Lattice PCIe Basic demo and have successfully completed all of the learning objectives of this kit.

# Running the PCI Express Throughput Demo

This chapter describes the Lattice PCI Express (PCIe) Throughput demo that you can run within this kit on a Windows system (Microsoft Windows2000, Windows XP SP2, Server2003).

# **Before You Begin**

Before beginning this demo, you must do the following operations.

Use ispVM to download the bitstream for this demo to the solutions board.

You can find the x1 and x4 bitstreams and the XCF file necessary for ispVM in the <kit\_dir>\Demonstration\PCleThruput\Bitstreams directory path.

For general information ispDOWNLOAD cable on ispVM configuration software usage, see the following:

- Download procedure described in the section, "Reprogramming the Solutions Board" on page 18.

- General introduction to device configuration with ispDOWNLOAD cable and ispVM software described in section, "Device Configuration Software and Cable" on page 8.

- ispVM Help system

- Install the board drivers for the application.

You can find the driver files necessary for proper demo installation in the <hit\_dir>\Demonstration\PCleThruput\Driver directory path. See the procedure in section, "Installing Solutions Board Drivers" on page 15 for guidance.

### **Resource References**

Please be aware of the specific companion documentation for supplementing your knowledge when using this demo:

#### **Hardware Resources**

The PCIe Throughput Demo x1 bitstream is built from the ispLEVER project located in *Hardware\PCIe x1\ecp2m50\_PCIeThruput\_SBx1\Implementation* \\ecp2m50\_PCIeThruput\_SBx1. The Verilog source code is located in the project Source\ directory.

The Verilog design architecture is explained in Documentation\ ECP2M PCI Express Throughput Reference Design User Guide\UG07.pdf. This document describes the purpose and functionality of the Verilog modules used in PCIe Throughput Demo design.

#### **Software Resources**

The PCIe Throughput Demo uses the Iscpcie2.sys device driver. The source code for this device driver is located in Software\lscpcie2\_Win2kXP\drvr. The architecture of the Iscpcie2 device driver is explained in the "Iscpcie2 Driver Reference Manual" which can be accessed through the Software\PCIeDocIndex.html link.

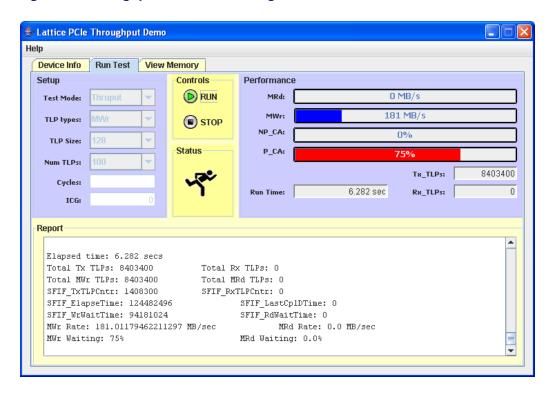

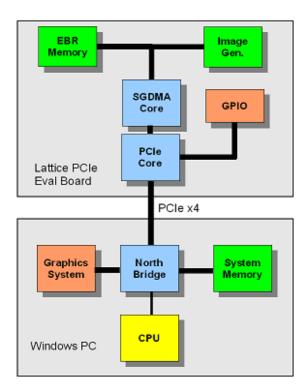

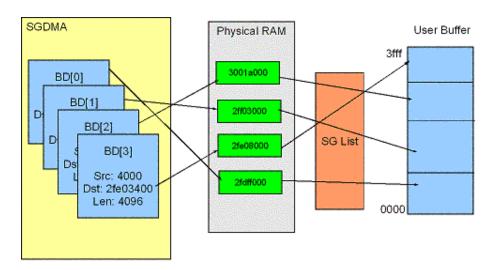

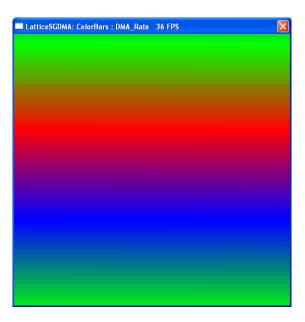

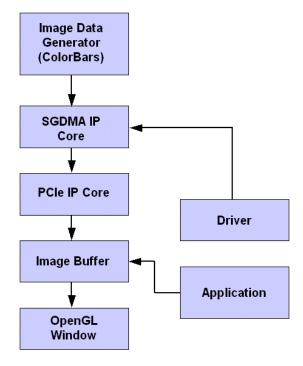

The PCIe Throughput Demo application source code is located in Software\PCIeSFIF\_Win2kXP\SFIF\_GUI\SFIF\_UI. This directory contains the Java project source code to create the user interface. The GUI also uses the PCIeAPI\_Lib\_Win2kXP API library.