# Cool-Power® ZVS Switching Regulators

PI332x-00

## 14 – 42V<sub>IN</sub> Cool-Power ZVS Buck Regulator

#### **Product Description**

The PI332x-00 is a family of high input voltage, wide input range DC-DC ZVS Buck regulators integrating controller, power switches, and support components all within a high density System-in-Package (SiP).

The integration of a high-performance Zero-Voltage Switching (ZVS) topology, within the PI332x-00 series, increases point of load performance providing best in class power efficiency. The PI332x-00 requires only an external inductor, two voltage selection resistors and minimal capacitors to form a complete DC-DC switch mode buck regulator.

| Davisa         | Ou   | I May      |                      |

|----------------|------|------------|----------------------|

| Device         | Set  | Range      | I <sub>OUT</sub> Max |

| PI3325-00-LGIZ | 5.0V | 4.0 – 6.5V | 20A                  |

#### **Features & Benefits**

- · High Efficiency HV ZVS Buck Topology

- Wide input voltage range of 14 42V

- Power-up into pre-biased load ≤ 6.0V

- Parallel capable with single wire current sharing

- Input Over/Undervoltage Lockout (OVLO/UVLO)

- Output Overvoltage Protection (OVP)

- Overtemperature Protection (OTP)

- Fast and slow current limits

- · Differential amplifier for output remote sensing

- User adjustable soft start & tracking

- –40 to 120°C operating range (T<sub>INT</sub>)

#### **Applications**

- HV to PoL Buck Regulator Applications

- Computing, Communications, Industrial, Automotive Equipment

#### **Package Information**

• 10 x 14 x 2.6mm LGA SiP

#### **Contents**

| Order Information                                           | 3          |

|-------------------------------------------------------------|------------|

| Thermal, Storage and Handling Information                   | 3          |

| Absolute Maximum Ratings                                    | 3          |

| Functional Block Diagram                                    | 4          |

| Pin Description                                             | 5          |

| Package Pinout                                              | 6          |

| PI332x-00 Common Electrical Characteristics                 | 7          |

| PI3325-00 (5.0V <sub>OUT</sub> ) Electrical Characteristics | 8          |

| Functional Description                                      | <u>15</u>  |

| ENABLE (EN)                                                 | <u>15</u>  |

| Remote Sensing                                              | <u>15</u>  |

| Soft Start                                                  | <u>15</u>  |

| Output Voltage Selection                                    | 15         |

| Output Current Limit Protection                             | 15         |

| Input Undervoltage Lockout                                  | 15         |

| Input Overvoltage Lockout                                   | 16         |

| Output Overvoltage Protection                               | <u> 16</u> |

| Overtemperature Protection                                  | <u> 16</u> |

| Pulse Skip Mode (PSM)                                       | <u> 16</u> |

| Variable Frequency Operation                                | <u> 16</u> |

| Thermal Characteristics                                     | 16         |

| SiP Power Dissipation as Percentage of Total System Losses  | 19         |

| Application Description               |    |

|---------------------------------------|----|

| Output Voltage Set Point              | 20 |

| Soft Start Adjust and Tracking        | 20 |

| Inductor Pairing                      | 21 |

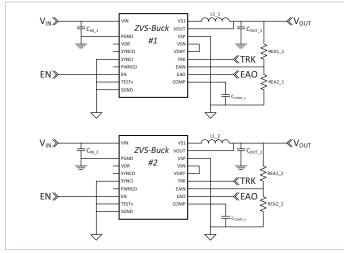

| Parallel Operation                    | 21 |

| Filter Considerations                 | 21 |

| VDR Bias Regulator                    | 22 |

| Layout Guidelines                     | 23 |

| Recommended PCB Footprint and Stencil | 24 |

| Package Drawings                      | 25 |

| Revision History                      | 26 |

| Product Warranty                      | 27 |

#### **Order Information**

| Product        | Nominal Output | Rated I <sub>OUT</sub> | Package         | Transport Media |

|----------------|----------------|------------------------|-----------------|-----------------|

| PI3325-00-LGIZ | 5.0V           | 20A                    | 10mm x 14mm LGA | TRAY            |

### **Thermal, Storage and Handling Information**

| Name                                   | Rating                         |

|----------------------------------------|--------------------------------|

| Storage Temperature                    | −65 to 150°C                   |

| Internal Operating Temperature         | −40 to 120°C                   |

| Soldering Temperature for 20 seconds   | 245°C                          |

| MSL Rating                             | 3                              |

| ESD Rating, JESD22-A114F, JESD22-C101F | 2kV HBM; 1kV CDM, respectively |

#### **Absolute Maximum Ratings**

| Name                                                                     | Rating                     |

|--------------------------------------------------------------------------|----------------------------|

| V <sub>IN</sub>                                                          | -0.7V to 55V               |

| VS1                                                                      | -0.7V <sub>DC</sub> to 55V |

| V <sub>OUT</sub>                                                         | -0.5V to 25V               |

| SGND                                                                     | ±100mA                     |

| TRK                                                                      | −0.3V to 5.5V, ±30mA       |

| VDR, SYNCI, SYNCO, PWRGD, EN, COMP,<br>EAO, EAIN, VDIFF, VSN, VSP, TESTx | -0.3V to 5.5V, ±5mA        |

**Notes:** Stresses beyond these limits may cause permanent damage to the device. Operation at these conditions or conditions beyond those listed in the Electrical Specifications table is not guaranteed. All voltages are referenced to PGND unless otherwise noted.

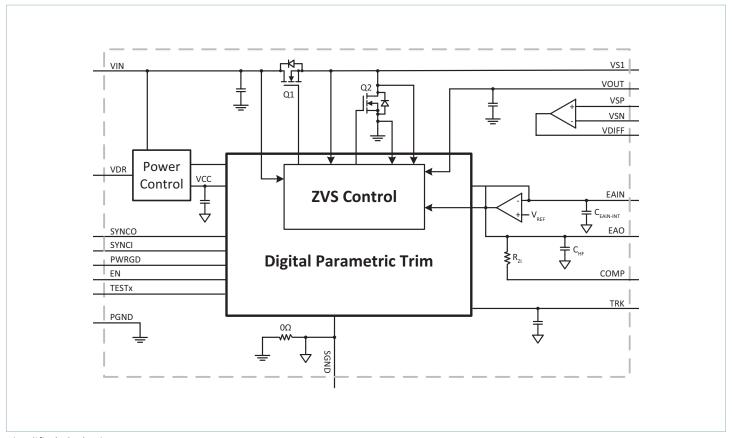

## **Functional Block Diagram**

Simplified Block Diagram

## **Pin Description**

| Name  | Location | I/O   | Description                                                                                                                                                                                                                                                                                                                                           |  |

|-------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VS1   | Block 1  | Power | Switching Node: and ZVS sense for power switches.                                                                                                                                                                                                                                                                                                     |  |

| VIN   | Block 3  | Power | Input Voltage: and sense for UVLO, OVLO and feed forward ramp.                                                                                                                                                                                                                                                                                        |  |

| VDR   | 5K       | I/O   | <b>Gate Driver VCC:</b> Internally generated 5.1V. May be used as a bias supply for low power external loads. See Application Description for important considerations.                                                                                                                                                                               |  |

| SYNCI | 4K       | I     | <b>Synchronization Input:</b> Synchronize to the falling edge of external clock frequency. SYNCI is a high impedance digital input node and should always be connected to SGND when not in use. The PI332x-00 family is not optimized for external synchronization functionality. Refer to Application Description of Parallel Operation for details. |  |

| SYNCO | 3K       | 0     | <b>Synchronization Output:</b> Outputs a high signal at the start of each clock cycle for the longer of ½ of the minimum period or the on time of the high-side power MOSFET.                                                                                                                                                                         |  |

| TEST1 | 2K       | I/O   | <b>Test Connections:</b> Use only with factory guidance. Connect to SGND for proper operation.                                                                                                                                                                                                                                                        |  |

| TEST2 | 1K       | I/O   | <b>Test Connections:</b> Use only with factory guidance. Connect to SGND for proper operation.                                                                                                                                                                                                                                                        |  |

| TEST3 | 1J       | I/O   | <b>Test Connections:</b> Use only with factory guidance. Connect to SGND for proper operation.                                                                                                                                                                                                                                                        |  |

| TEST4 | 1H       | I/O   | <b>Test Connections:</b> Use only with factory guidance. Connect to SGND for proper operation.                                                                                                                                                                                                                                                        |  |

| TEST5 | 1E       | I/O   | <b>Test Connections:</b> Use only with factory guidance. Connect to SGND for proper operation.                                                                                                                                                                                                                                                        |  |

| PWRGD | 1G       | 0     | <b>Power Good:</b> High impedance when regulator is operating and $V_{\text{OUT}}$ is in regulation. Otherwise pulls to SGND.                                                                                                                                                                                                                         |  |

| EN    | 1F       | I/O   | <b>Enable Input:</b> Regulator enable control. When asserted active or left floating: regulator is enable Otherwise regulator is disabled.                                                                                                                                                                                                            |  |

| SGND  | Block 5  |       | <b>Signal Ground:</b> Internal logic ground for EA, TRK, SYNCI, SYNCO communication returns. SGND and PGND are star connected within the regulator package.                                                                                                                                                                                           |  |

| TRK   | 1C       | I     | <b>Soft Start and Track Input:</b> An external capacitor may be connected between TRK pin and SGND to increase the rise time of the internal reference during soft start.                                                                                                                                                                             |  |

| СОМР  | 1B       | 0     | <b>Compensation Capacitor:</b> Connect capacitor for control loop dominant pole. See Error Amplifier section for details. A default $C_{\text{COMP}}$ of 4.7nF is used in the example.                                                                                                                                                                |  |

| EAO   | 1A       | 0     | Error Amp Output: External connection for additional compensation and current sharing.                                                                                                                                                                                                                                                                |  |

| EAIN  | 2A       | I     | Error Amp Inverting Input: Connection for the main Vout feedback divider tap                                                                                                                                                                                                                                                                          |  |

| VDIFF | 3A       | 0     | Independent Amplifier Output: Active only when module is enabled.                                                                                                                                                                                                                                                                                     |  |

| VSN   | 4A       | I     | Independent Amplifier Inverting Input: If unused connect in unity gain.                                                                                                                                                                                                                                                                               |  |

| VSP   | 5A       | I     | Independent Amplifier Non-Inverting Input: If unused connect to SGND.                                                                                                                                                                                                                                                                                 |  |

| VOUT  | 6A,B     | Power | <b>Direct V<sub>OUT</sub> Connect:</b> for per-cycle internal clamp node and feed-forward ramp.                                                                                                                                                                                                                                                       |  |

| PGND  | Block2   | Power | <b>Power Ground:</b> V <sub>IN</sub> and V <sub>OUT</sub> power returns.                                                                                                                                                                                                                                                                              |  |

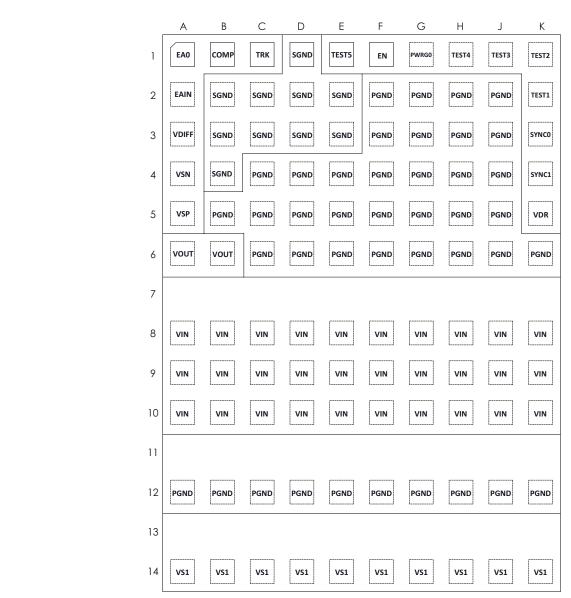

#### **Package Pinout**

PI332x & PI352x

TOP THROUGH VIEW OF PRODUCT

#### 110 Pad LGA SiP (10 x 14mm)

| Pin Block Name | Group of pins                                                        |

|----------------|----------------------------------------------------------------------|

| VIN            | A8-10, B8-10, C8-10, D8-10, E8-10, F8-10, G8-10, H8-10, J8-10, K8-10 |

| VS1            | A14, B14, C14, D14, E14, F14, G14, H14, J14, K14                     |

| PGND           | A12, B12, C12, D12, E12, F12, G12, H12, J12, K12                     |

| PGND           | B5, C4-6, D4-6, E4-6, F2-6, G2-6, H2-6, J2-6, K6                     |

| VOUT           | A6, B6                                                               |

| SGND           | B2-4, C2-3, D1-3, E2-3                                               |

#### PI332x-00 Common Electrical Characteristics

Specifications apply for -40 °C <  $T_{INT}$  < 120 °C,  $V_{IN}$  = 24V, EN = High, unless otherwise noted.

| Parameter                                   | Symbol                 | Conditions                                | Min  | Тур  | Max | Unit                  |

|---------------------------------------------|------------------------|-------------------------------------------|------|------|-----|-----------------------|

|                                             |                        |                                           |      |      |     |                       |

|                                             |                        | Differential Amp                          |      |      |     |                       |

| Open Loop Gain                              |                        | [b]                                       | 96   | 120  | 140 | dB                    |

| Small Signal Gain-Bandwidth                 |                        | [b]                                       | 5    | 7    | 12  | MHz                   |

| Input Offset                                |                        |                                           |      | 0.5  | 1   | mV                    |

| Common Mode Input Range                     |                        |                                           | -0.1 |      | 2.5 | V                     |

| Differential Mode Input Range               |                        |                                           |      |      | 2   | V                     |

| Input Bias Current                          |                        |                                           | -1   |      | 1   | μΑ                    |

| Output Current                              |                        |                                           | -1   |      | 1   | mA                    |

| Maximum V <sub>OUT</sub>                    |                        | $I_{VDIFF} = -1 \text{mA}$                | 4.85 |      |     | V                     |

| Minimum V <sub>OUT</sub>                    |                        | $I_{VDIFF} = -1mA$                        |      |      | 20  | mV                    |

| Capacitive Load Range for Stability         |                        | [b]                                       | 0    |      | 50  | pF                    |

| Slew Rate                                   |                        |                                           |      | 11   |     | V/µs                  |

|                                             |                        |                                           |      |      |     |                       |

| '                                           |                        | PWRGD                                     |      |      |     |                       |

| V <sub>OUT</sub> Rising Threshold           | $V_{PG\_HI\%}$         |                                           | 78   | 84   | 90  | % V <sub>OUT_DO</sub> |

| V <sub>OUT</sub> Falling Threshold          | V <sub>PG_LO%</sub>    |                                           | 75   | 81   | 87  | % V <sub>OUT_DO</sub> |

| PWRGD Output Low                            | $V_{PG\_SAT}$          | Sink = 4mA                                |      |      | 0.4 | V                     |

|                                             |                        |                                           |      |      |     |                       |

|                                             |                        | VDR                                       |      |      |     |                       |

| Voltage Setpoint                            | $V_{VDR}$              | $V_{IN\_DC} > 10V$                        | 4.9  | 5.05 | 5.2 | V                     |

| External Loading                            | I <sub>VDR</sub>       | See Application Description for details   | 0    |      | 2   | mA                    |

|                                             |                        |                                           |      |      |     |                       |

|                                             |                        | Enable                                    |      | I    | I   |                       |

| High Threshold                              | V <sub>EN_HI</sub>     |                                           | 0.9  | 1.0  | 1.1 | V                     |

| Low Threshold                               | V <sub>EN_LO</sub>     |                                           | 0.7  | 0.8  | 0.9 | V                     |

| Threshold Hysteresis                        | V <sub>EN_HYS</sub>    |                                           | 100  | 200  | 300 | mV                    |

| Pull Up Voltage Level for<br>Source Current | $V_{\text{EN\_PU}}$    |                                           |      | 2    |     | V                     |

| Pull Up Current                             | I <sub>EN_PU_POS</sub> | $V_{IN}$ > 8V, excluding $t_{FR\_DLY}$    |      | 50   |     | μΑ                    |

|                                             |                        |                                           |      |      |     |                       |

|                                             |                        | Reliability                               |      |      |     |                       |

| MTBF                                        |                        | MIL-HDBK-217, 25°C, Ground Benign: GB     |      | 14.6 |     | MHrs                  |

|                                             |                        | Telcordia SR-332, 25°C, Ground Benign: GB |      | 201  |     | MHrs                  |

<sup>[</sup>a] All parameters reflect regulator and inductor system performance. Measurements were made using a standard PI332x evaluation board with 3 x 3" dimensions and four-layer, 2oz copper. Refer to inductor pairing table within Application Description section for specific inductor manufacturer and value.

<sup>[</sup>b] Regulator is assured to meet performance specifications by design, test correlation, characterization, and/or statistical process control. Output voltage is determined by an external feedback divider ratio.

<sup>[</sup>c] Output current capability may be limited and other performance may vary from noted electrical characteristics when V<sub>OUT</sub> is not set to nominal.

<sup>[</sup>d] Refer to Output Ripple plots.

$<sup>^{\</sup>hbox{\scriptsize [e]}}$  Refer to Load Current vs. Ambient Temperature curves.

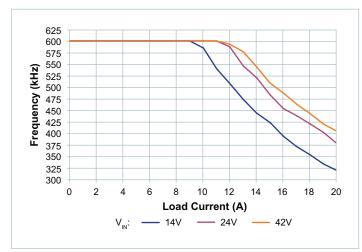

$<sup>^{[</sup>f]}$  Refer to Switching Frequency vs. Load current curves.

Specifications apply for -40°C  $< T_{INT} < 120$ °C,  $V_{IN} = 24$ V, EN = High, unless otherwise noted.

| Parameter                                                     | Symbol                                | Conditions                                                                    | Min   | Тур   | Max   | Unit              |

|---------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------|-------|-------|-------|-------------------|

|                                                               |                                       |                                                                               |       |       |       |                   |

|                                                               |                                       | Input Specifications                                                          |       | I     | I     | I                 |

| Input Voltage                                                 | V <sub>IN_DC</sub>                    |                                                                               | 14    | 24    | 42    | V                 |

| Input Current                                                 | I <sub>IN_DC</sub>                    | $V_{IN} = 24V, T_{CASE} = 25^{\circ}C, I_{OUT} = 20A$                         |       | 4.41  |       | А                 |

| Input Current At Output Short<br>(Fault Condition Duty Cycle) | I <sub>IN_Short</sub>                 | Short at terminals                                                            |       | 5     |       | mA                |

| Input Quiescent Current                                       | I <sub>Q_VIN</sub>                    | Disabled                                                                      |       | 0.94  | 1.6   | mA                |

| Input Quiescent Current                                       | I <sub>Q_VIN</sub>                    | Enabled, no load, T <sub>CASE</sub> = 25°C                                    |       | 4.2   |       | mA                |

| Input Voltage Slew Rate                                       | $V_{IN\_SR}$                          | [b]                                                                           |       |       | 1     | V/µs              |

| Input capacitance, Internal                                   | C <sub>IN_INT</sub>                   | Effective value $V_{IN} = 24V$ , 25°C                                         |       | 0.7   |       | μF                |

|                                                               |                                       | Output Specifications                                                         |       |       |       |                   |

| FAINI \/altaga Tatal Degulation                               | N/                                    | [b]                                                                           | 0.075 | 0.000 | 1 005 | \/                |

| EAIN Voltage Total Regulation                                 | V <sub>EAIN</sub>                     | [b] [c]                                                                       | 0.975 | 0.990 | 1.005 | V                 |

| Output Voltage Trim Range                                     | V <sub>OUT_DC</sub>                   |                                                                               | 4.0   | 5.0   | 6.5   | V                 |

| Line Regulation                                               | ΔV <sub>OUT</sub> / ΔV <sub>IN</sub>  | @ 25°C, 14V < V <sub>IN</sub> < 42V                                           |       | 0.10  |       | %                 |

| Load Regulation                                               | ΔV <sub>OUT</sub> / ΔI <sub>OUT</sub> | @ 25°C, 2A < I <sub>OUT</sub> < 20A                                           |       | 0.10  |       | %                 |

| Output Voltage Ripple                                         | V <sub>OUT_AC</sub>                   | I <sub>OUT</sub> = 20A, C <sub>OUT</sub> = 12 x 47μF, 20MHz BW <sup>[d]</sup> |       | 55.7  |       | mV <sub>P-P</sub> |

| Output Current                                                | I <sub>OUT_DC</sub>                   | [e]                                                                           | 0     |       | 20    | А                 |

| Current Limit                                                 | I <sub>OUT_CL</sub>                   | Typical current limit based on nominal 230nH inductor.                        |       | 24    |       | А                 |

| Maximum Array Size                                            | N <sub>PARALLEL</sub>                 | [b]                                                                           |       |       | 3     | Modules           |

| Output Current, Array of 2                                    | I <sub>OUT_DC_ARRAY2</sub>            | Total array capability, <sup>[b]</sup> see applications section for details   | 0     |       | [g]   | А                 |

| Output Current, Array of 3                                    | I <sub>OUT_DC_ARRAY3</sub>            | Total array capability, [b] see applications section for details              | 0     |       | [g]   | А                 |

|                                                               |                                       | Protection                                                                    |       |       |       |                   |

| Input UVLO Start Threshold                                    | V <sub>UVLO_START</sub>               |                                                                               |       | 12.9  | 13.8  | V                 |

| Input UVLO Stop Hysteresis                                    | V <sub>UVLO_HYS</sub>                 |                                                                               | 0.85  | 1.21  | 1.75  | V                 |

| Input UVLO Response Time                                      | - UVLU_RTS                            |                                                                               |       | 1.25  |       | μs                |

| Input OVLO Stop Threshold                                     | V <sub>OVLO</sub>                     |                                                                               | 44    | 47    |       | V                 |

| Input OVLO Start Hysteresis                                   | V <sub>OVLO_HYS</sub>                 | Hysteresis active when OVLO present for at least t <sub>FR DLY</sub>          | 0.5   | 0.9   | 1.3   | V                 |

| Input OVLO Response Time                                      | t <sub>f</sub>                        |                                                                               | 0.5   | 1.25  |       | μs                |

| Output Overvoltage Protection,<br>Relative                    | V <sub>OVP_REL</sub>                  | Above set V <sub>OUT</sub>                                                    |       | 20    |       | %                 |

| Output Overvoltage Protection,<br>Absolute                    | V <sub>OVP_ABS</sub>                  |                                                                               | 6.7   | 7.37  |       | V                 |

<sup>[</sup>a] All parameters reflect regulator and inductor system performance. Measurements were made using a standard PI332x evaluation board with 3 x 3" dimensions and four-layer, 2oz copper. Refer to inductor pairing table within Application Description section for specific inductor manufacturer and value.

<sup>[</sup>b] Regulator is assured to meet performance specifications by design, test correlation, characterization, and/or statistical process control.

Output voltage is determined by an external feedback divider ratio.

<sup>[</sup>c] Output current capability may be limited and other performance may vary from noted electrical characteristics when V<sub>OUT</sub> is not set to nominal.

<sup>[</sup>d] Refer to Output Ripple plots.

<sup>[</sup>e] Refer to Load Current vs. Ambient Temperature curves.

<sup>&</sup>lt;sup>[f]</sup> Refer to Switching Frequency vs. Load current curves.

<sup>[</sup>g] Contact factory applications for array derating and layout best practices to minimize sharing errors.

Specifications apply for -40°C <  $T_{INT}$  < 120°C,  $V_{IN}$  = 24V, EN = High, unless otherwise noted.

| Parameter                        | Symbol                | Conditions                                                                                                                                 | Min | Тур  | Max | Unit |

|----------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                                  |                       |                                                                                                                                            |     |      |     |      |

|                                  |                       | Timing                                                                                                                                     |     |      |     |      |

| Switching Frequency              | f <sub>s</sub>        | <sup>[f]</sup> While in Discontinuous Conduction Mode (DCM) only, SYNCI grounded                                                           | 564 | 600  | 636 | kHz  |

| Fault Restart Delay              | t <sub>FR_DLY</sub>   |                                                                                                                                            |     | 30   |     | ms   |

|                                  |                       |                                                                                                                                            |     |      |     |      |

|                                  |                       | Synchronization Input (SYNCI)                                                                                                              |     |      |     |      |

| Synchronization Frequency Range  | f <sub>SYNCI</sub>    | -50% and $+10%$ relative to set switching frequency (f <sub>S</sub> ), while in DCM operating mode only. <sup>[c]</sup> and <sup>[f]</sup> | 300 |      | 660 | kHz  |

| SYNCI Threshold                  | V <sub>SYNCI</sub>    |                                                                                                                                            |     | 2.5  |     | V    |

|                                  |                       |                                                                                                                                            |     |      |     |      |

|                                  |                       | Synchronization Output (SYNCO)                                                                                                             |     |      |     |      |

| SYNCO High                       | V <sub>SYNCO_HI</sub> | Source 1mA                                                                                                                                 | 4.5 |      |     | V    |

| SYNCO Low                        | V <sub>SYNCO_LO</sub> | Sink 1mA                                                                                                                                   |     |      | 0.5 | V    |

| SYNCO Rise Time                  | t <sub>SYNCO_RT</sub> | 20pF load                                                                                                                                  |     | 10   |     | ns   |

| SYNCO Fall Time                  | t <sub>SYNCO_FT</sub> | 20pF load                                                                                                                                  |     | 10   |     | ns   |

|                                  |                       |                                                                                                                                            |     |      |     |      |

|                                  |                       | Soft Start, Tracking and Error Amplifier                                                                                                   |     |      |     |      |

| TRK Active Range (Nominal)       | $V_{TRK}$             |                                                                                                                                            | 0   |      | 1.4 | V    |

| TRK Enable Threshold             | V <sub>TRK_OV</sub>   |                                                                                                                                            | 20  | 40   | 60  | mV   |

| TRK to EAIN Offset               | V <sub>EAIN_OV</sub>  |                                                                                                                                            | 40  | 80   | 120 | mV   |

| Charge Current (Soft Start)      | I <sub>TRK</sub>      |                                                                                                                                            | 30  | 50   | 70  | μΑ   |

| Discharge Current (Fault)        | I <sub>TRK_DIS</sub>  | $V_{TRK} = 0.5V$                                                                                                                           |     | 8.7  |     | mA   |

| TRK Capacitance, Internal        | C <sub>TRK_INT</sub>  |                                                                                                                                            |     | 47   |     | nF   |

| Soft-Start Time                  | t <sub>SS</sub>       | $C_{TRK\_EXT} = 0\mu F$                                                                                                                    | 0.6 | 0.94 | 1.6 | ms   |

| Error Amplifier Transconductance | GM <sub>EAO</sub>     |                                                                                                                                            |     | 7.6  |     | mS   |

| PSM Skip Threshold               | PSM <sub>SKIP</sub>   |                                                                                                                                            |     | 0.8  |     | V    |

| EAIN Capacitance, Internal       | C <sub>EAIN_INT</sub> |                                                                                                                                            |     | 56   |     | pF   |

| Error Amplifier Output Impedance | R <sub>OUT</sub>      | [b]                                                                                                                                        | 1   |      |     | МΩ   |

| Internal Compensation Capacitor  | C <sub>HF</sub>       |                                                                                                                                            |     | 56   |     | pf   |

| Internal Compensation Resistor   | R <sub>ZI</sub>       |                                                                                                                                            |     | 5    |     | kΩ   |

<sup>[</sup>a] All parameters reflect regulator and inductor system performance. Measurements were made using a standard PI332x evaluation board with 3 x 3" dimensions and four-layer, 2oz copper. Refer to inductor pairing table within Application Description section for specific inductor manufacturer and value.

<sup>[</sup>b] Regulator is assured to meet performance specifications by design, test correlation, characterization, and/or statistical process control. Output voltage is determined by an external feedback divider ratio.

<sup>[</sup>c] Output current capability may be limited and other performance may vary from noted electrical characteristics when V<sub>OUT</sub> is not set to nominal.

<sup>[</sup>d] Refer to Output Ripple plots.

<sup>[</sup>e] Refer to Load Current vs. Ambient Temperature curves.

<sup>&</sup>lt;sup>[f]</sup> Refer to Switching Frequency vs. Load current curves.

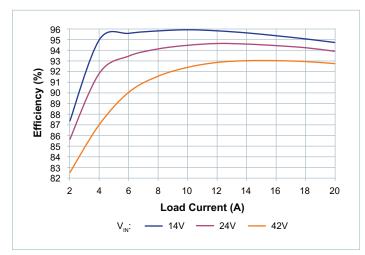

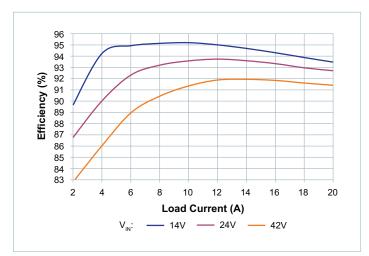

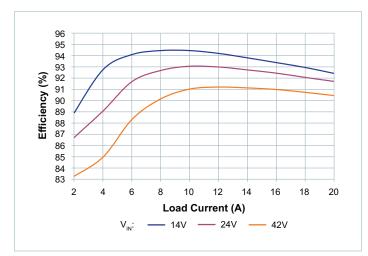

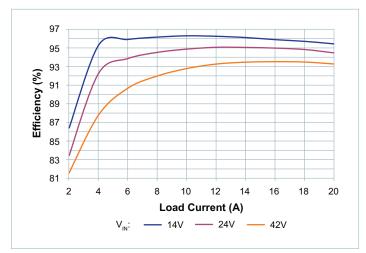

**Figure 1** — System Efficiency, Nominal Trim, Board Temperature = 25°C

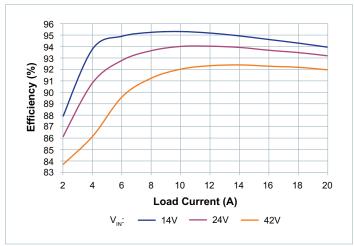

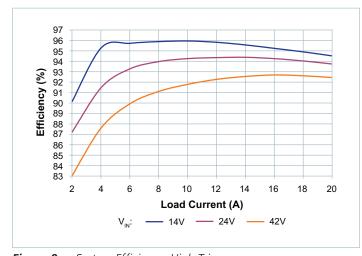

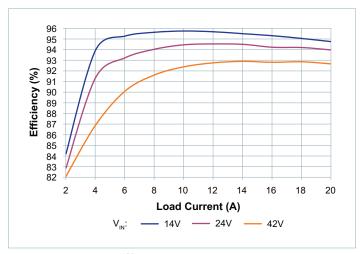

**Figure 2** — System Efficiency, Low Trim, Board Temperature = 25°C

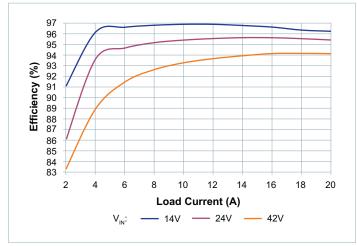

**Figure 3** — System Efficiency, High Trim, Board Temperature = 25°C

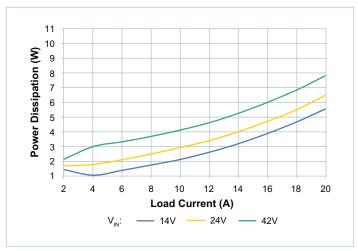

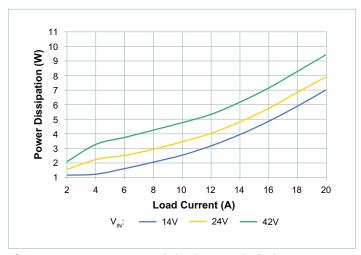

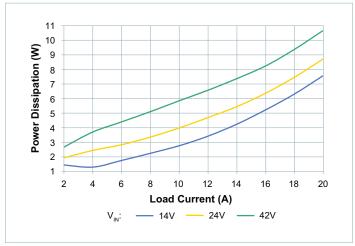

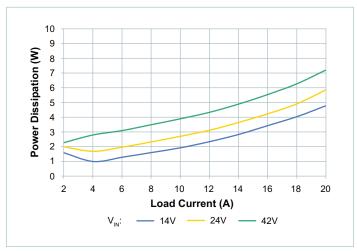

**Figure 4** — System Power Dissipation, Nominal Trim, Board Temperature = 25°C

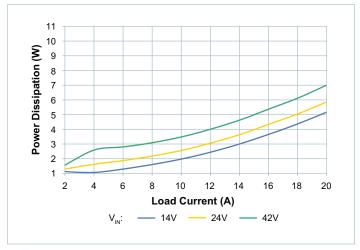

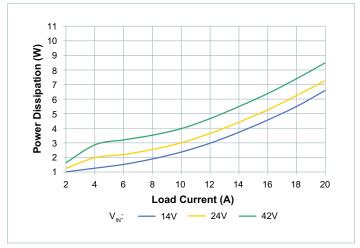

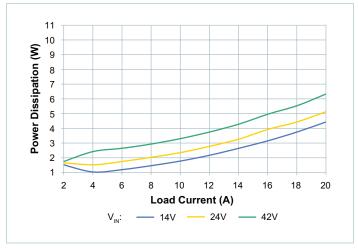

**Figure 5** — System Power Dissipation, Low Trim, Board Temperature = 25°C

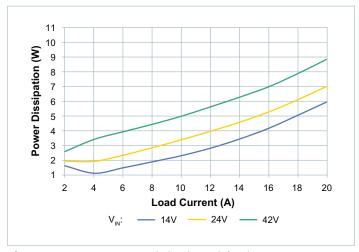

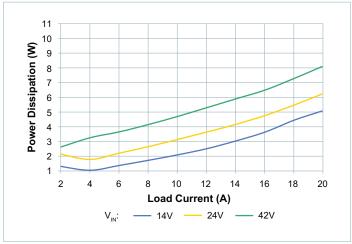

**Figure 6** — System Power Dissipation, High Trim, Board Temperature = 25°C

**Figure 7** — System Efficiency, Nominal Trim, Board Temperature = 90°C

**Figure 8** — System Efficiency, Low Trim, Board Temperature = 90°C

**Figure 9** — System Efficiency, High Trim, Board Temperature = 90°C

**Figure 10** — System Power Dissipation, Nominal Trim, Board Temperature = 90°C

**Figure 11** — System Power Dissipation, Low Trim, Board Temperature = 90°C

**Figure 12** — System Power Dissipation, High Trim, Board Temperature = 90°C

**Figure 13** — System Efficiency, Nominal Trim, Board Temperature = −40°C

**Figure 14** — System Efficiency, Low Trim, Board Temperature = -40°C

**Figure 15** — System Efficiency, High Trim, Board Temperature = −40°C

**Figure 16** — System Power Dissipation, Nominal Trim, Board Temperature = −40°C

**Figure 17** — System Power Dissipation, Low Trim, Board Temperature = -40°C

**Figure 18** — System Power Dissipation, High Trim, Board Temperature = −40°C

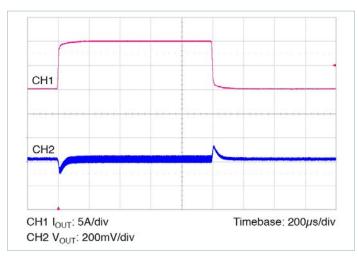

**Figure 19** — Transient Response: 50% to 100% load, at 1A/ $\mu$ s. Nominal Line, Nominal Trim,  $C_{OUT} = 12 \times 47 \mu$ F Ceramic

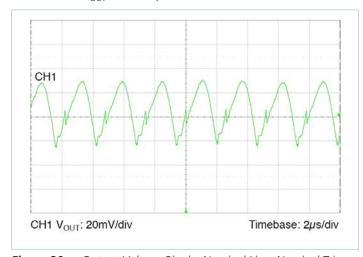

**Figure 20** — Output Voltage Ripple: Nominal Line, Nominal Trim, 100% load,  $C_{OUT} = 12 \times 47 \mu F$  Ceramic

Figure 21 — Switching Frequency vs. Load, Nominal Trim

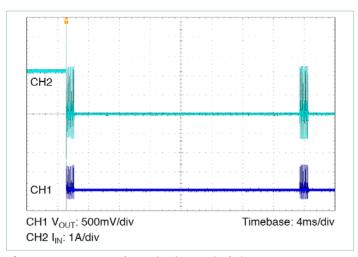

Figure 22 — Output Short Circuit, Nominal Line

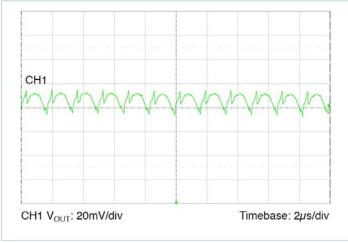

**Figure 23** — Output Voltage Ripple: Nominal Line, Nominal Trim, 50% load, C<sub>OUT</sub> = 12 x 47μF Ceramic

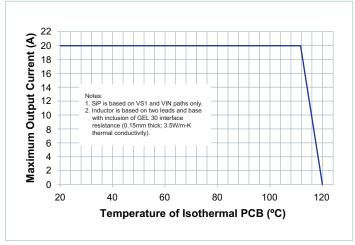

**Figure 24** — System Thermal Specified Operating Area: Max I<sub>OUT</sub> at Nominal Trim vs. temperature at locations noted

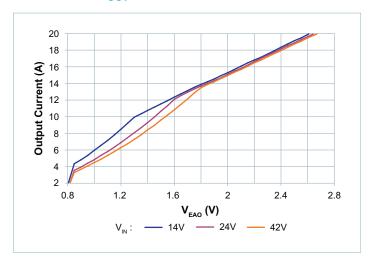

**Figure 25** — Output Current vs.  $V_{EAO}$ , Nominal Trim

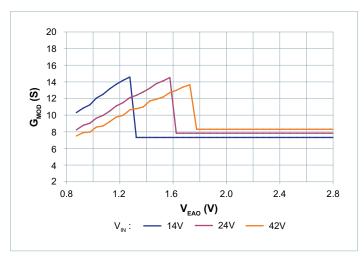

**Figure 26** — Small Signal Modulator Gain vs.  $V_{EAO}$ , Nominal Trim

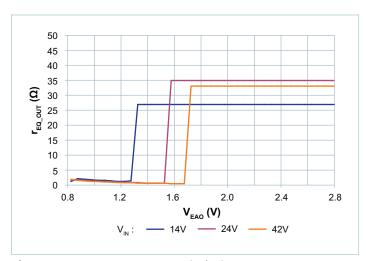

**Figure 27** —  $r_{EQ\_OUT}$  vs  $V_{EAO}$ , Nominal Trim

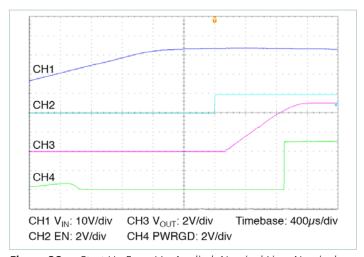

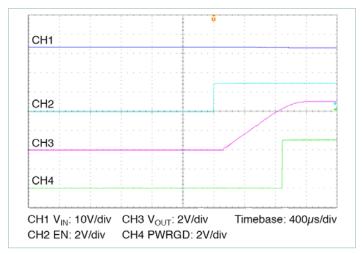

**Figure 28** — Start Up From  $V_{IN}$  Applied, Nominal Line, Nominal Trim, Typical Timing, Pl3325 Shown

**Figure 29** — Start Up From EN, V<sub>IN</sub> Pre-Applied, Nominal Line, Nominal Trim, Typical Timing, Pl3325 Shown

#### **Functional Description**

The PI332x-00 is a family of highly integrated ZVS Buck regulators. The PI332x-00 has an output voltage that can be set within a prescribed range shown in Table 1. Performance and maximum output current are characterized with a specific external power inductor (see Table 3).

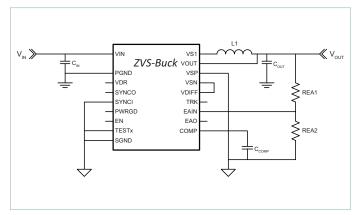

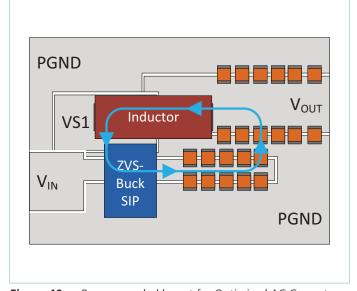

**Figure 30** — ZVS Buck with required components

For basic operation, Figure 30 shows the connections and components required. No additional design or settings are required.

#### **ENABLE (EN)**

EN is the enable pin of the converter. The EN Pin is referenced to SGND and permits the user to turn the regulator on or off. The EN default polarity is a positive logic assertion. If the EN pin is left floating or asserted high, the converter output is enabled. Pulling EN pin below  $V_{\text{EN\_LO}}$  with respect to SGND will disable the regulator output.

#### **Remote Sensing**

If remote sensing is required, the PI332x-00 product family is equipped with a general purpose op-amp. This amplifier can allow full differential remote sense by configuring it as a differential follower and connecting the V<sub>DIFF</sub> pin to the EAIN pin.

#### **Soft Start**

The PI332x-00 includes an internal soft-start capacitor to control the rate of rise of the output voltage. See the Electrical Characteristics Section for the default value. Connecting an external capacitor from the TRK pin to SGND will increase the start-up ramp period. See, "Soft Start Adjustment and Track," in the Applications Description section for more details.

#### **Output Voltage Selection**

The PI332x-00 output voltage is set with REA1 and REA2 as shown in Figure 30. Table 1 defines the allowable operational voltage ranges for the PI332x-00 family. Refer to the Output Voltage Set Point Application Description for details.

| Device         | Output Voltage |              |  |  |

|----------------|----------------|--------------|--|--|

| Device         | Nom.           | Range        |  |  |

| PI3325-00-LGIZ | 5.0V           | 4.0V to 6.5V |  |  |

**Table 1** — PI332x-00 family output voltage ranges

#### **Output Current Limit Protection**

The PI332x-00 has a current limit protection, which prevents the output from sourcing current higher than the regulator's maximum rated current. If the output current exceeds the Current Limit ( $I_{OUT\_CL}$ ) for 1024 $\mu$ s, a slow current limit fault is initiated and the regulator is shutdown which eliminates output current flow. After Fault Restart Delay ( $I_{FR\_DLY}$ ), a soft-start cycle is initiated. This restart cycle will be repeated indefinitely until the excessive load is removed.

The PI332x-00 also has short circuit protection which can rapidly stop switching to protect against catastrophic failure of an external component such as a saturated inductor. If short circuit protection is triggered the PI332x-00 will complete the current cycle and stop switching. The module will attempt to soft start after Fault Restart Delay ( $t_{\rm FR\ DIY}$ ).

#### **Input Undervoltage Lockout**

If  $V_{\rm IN}$  falls below the input Undervoltage Lockout (UVLO) threshold, but remains high enough to power the internal bias supply, the PI332x-00 will complete the current cycle and stop switching. The system will soft start once the input voltage is reestablished and after the Fault Restart Delay.

#### **Input Overvoltage Lockout**

If  $V_{IN}$  exceeds the input Overvoltage Lockout (OVLO) threshold ( $V_{OVLO}$ ), while the controller is running, the PI332x-00 will complete the current cycle and stop switching. If  $V_{IN}$  remains above OVLO for at least  $t_{FR\_DLY}$ , then the input voltage is considered reestablished once  $V_{IN}$  goes below  $V_{OVLO}-V_{OVLO\_HYS}$ . If  $V_{IN}$  goes below OVLO before  $t_{FR\_DLY}$  elapses, then the input voltage is considered reestablished once  $V_{IN}$  goes below  $V_{OVLO}$ . The system will soft start once the input voltage is reestablished and after the Fault Restart Delay.

#### **Output Overvoltage Protection**

The PI332x-00 family is equipped with output Overvoltage Protection (OVP) to prevent damage to input voltage sensitive devices. If the output voltage exceeds  $V_{\rm OVP-REL}$  or  $V_{\rm OVP-ABS}$ , the regulator will complete the current cycle and stop switching. The system will resume operation once the output voltage falls below the OVP threshold and after Fault Restart Delay.

#### **Overtemperature Protection**

The PI332x features an over temperature protection (OTP), which will not engage until after the product is operated above the maximum rated temperature. The OTP circuit is only designed to protect against catastrophic failure due to excessive temperatures and should not be relied upon to ensure the device stays within the recommended operating temperature range. Thermal shutdown terminates switching and discharges the soft-start capacitor. The PI332x will restart after the excessive temperature has decreased by 30°C.

#### Pulse Skip Mode (PSM)

PI332x-00 features a Pulse Skip Mode (PSM) to achieve high efficiency at light loads. The regulators are setup to skip pulses if EAO falls below a PSM threshold (PSM<sub>SKIP</sub>). Depending on conditions and component values, this may result in single pulses or several consecutive pulses followed by skipped pulses. Skipping cycles significantly reduces gate drive power and improves light load efficiency. The regulator will leave PSM once the EAO rises above the Pulse Skip Mode threshold.

#### Variable Frequency Operation

Each PI332x-00 is preprogrammed to a base operating frequency, with respect to the power stage inductor (see Table 2), to operate at peak efficiency across line and load variations. At low line and high load applications, the base frequency will decrease to accommodate these extreme operating ranges. By stretching the frequency, the ZVS operation is preserved throughout the total input line voltage range therefore maintaining optimum efficiency.

#### Thermal Characteristics

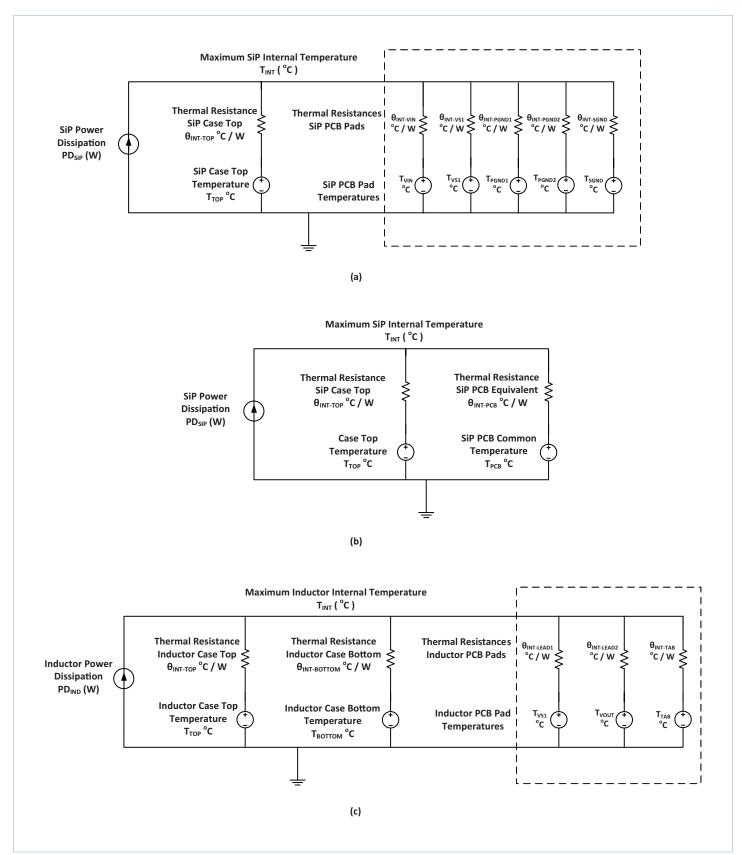

Figure 31(a) and 31(c) thermal impedance models that can predict the maximum temperature of the hottest component for a given operating condition. This model assumes that all customer PCB connections are at one temperature, which is PCB equivalent Temperature  $T_{PCB}$  °C.

The SiP model can be simplified as shown in Figure 31(b). which assumes all PCB nodes are at the same temperature.

Figure 31 — Pl332x-00 Thermal model (a), SiP simplified version (b) and inductor thermal model (c)

#### Where the symbol in Figure 31(a) and (b) is defined as the following:

| $\theta_{INT-TOP}$         | the thermal impedance from the hottest component inside the SiP to the top side                                                                         |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\theta_{INT-PCB}$         | the thermal impedance from the hottest component inside the SiP to the customer PCB, assuming all pins are at one temperature.                          |

| $\theta_{INT-VIN}$         | the thermal impedance from the hottest component inside the SiP to the circuit board VIN pads.                                                          |

| $\theta_{\text{INT-VS1}}$  | the thermal impedance from the hottest component inside the SiP to the circuit board VS1 pads.                                                          |

| $\theta_{INT-PGND1}$       | the thermal impedance from the hottest component inside the SiP to the circuit board at the PGND1 pads. PGND1 is pins 12A-K.                            |

| θ <sub>INT-PGND2</sub>     | the thermal impedance from the hottest component inside the SiP to the circuit board at the PGND2 pads . PGND2 is pins 2F-J, 3F-J, 4C-J, 5B-J and 6C-K. |

| $\theta_{INT\text{-SGND}}$ | the thermal impedance from the hottest component inside the SiP to the circuit board at the SGND pads.                                                  |

#### Where the symbol in Figure 31(c) is defined as the following:

| $\theta_{INT-TOP}$          | the thermal impedance from the hot spot to the top surface of the core.                                                                                                   |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\theta_{INT-BOT}$          | the thermal impedance from the hot spot to the bottom surface of the core.                                                                                                |

| $\theta_{INT-TAB}$          | the thermal impedance from the hot spot to the metal mounting tab on the core body, if applicable.                                                                        |

| $\theta_{INT\text{-LEAD1}}$ | the thermal impedance from the hot spot to one of the mounting leads. Since the leads are the same thermal impedance, there is no need to specify by explicit pin number. |

| $\theta_{INT\text{-LEAD2}}$ | the thermal impedance from the hot spot to the other mounting lead.                                                                                                       |

The following equation can predict the junction temperature based on the heat load applied to the SiP and the known ambient conditions with the simplified thermal circuit model:

$$T_{INT} = \frac{PD + \frac{T_{TOP}}{\theta_{INT-TOP}} + \frac{T_{PCB}}{\theta_{INT-PCB}}}{\frac{I}{\theta_{INT-PCB}} + \frac{I}{\theta_{INT-PCB}}}$$

(1)

| Product | Simplified SiP<br>Thermal Impedances |                                  | Detailed SiP Thermal Impedances |                                  |                                  |                            |                            |                           |

|---------|--------------------------------------|----------------------------------|---------------------------------|----------------------------------|----------------------------------|----------------------------|----------------------------|---------------------------|

| System  | θ <sub>INT-TOP</sub><br>(°C / W)     | θ <sub>INT-PCB</sub><br>(°C / W) | θ<br>(°C / W)                   | θ <sub>INT-VIN</sub><br>(°C / W) | θ <sub>INT-VS1</sub><br>(°C / W) | θ<br>INT-PGND1<br>(°C / W) | θ<br>INT-PGND2<br>(°C / W) | θ<br>INT-SGND<br>(°C / W) |

| PI3325  | 106.08                               | 1.72                             | 106.08                          | 3.35                             | 4.76                             | 33.28                      | 32.93                      | 91.35                     |

**Table 2** — PI332x-00 SiP Thermal Impedance

|        | Product | Inductor Part                    | Effective Thermal Impedances                              |                                            |                                  |     |  |  |

|--------|---------|----------------------------------|-----------------------------------------------------------|--------------------------------------------|----------------------------------|-----|--|--|

| System | Number  | θ <sub>INT-TOP</sub><br>(°C / W) | $\theta_{\text{INT-LEAD1}}$ , $\theta_{\text{INT-LEAD2}}$ | <sup>θ</sup> інт-воттом<br><b>(°C / W)</b> | <sup>θ</sup> int-tab<br>(°C / W) |     |  |  |

|        | PI3325  | FP2207R1-R230-R                  | 10.94                                                     | 9.42                                       | 6.84                             | N/A |  |  |

**Table 3** — Inductor effective thermal model parameters

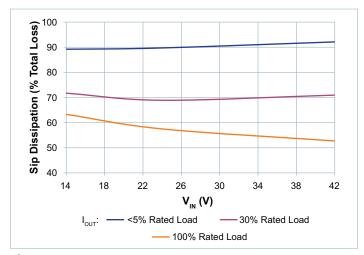

## **SiP Power Dissipation as Percentage of Total System Losses**

Figure 32 — PI3325-00-LGIZ

#### **Application Description**

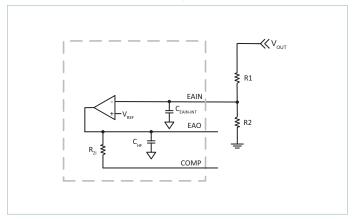

#### **Output Voltage Set Point**

The PI332x-00 family of Buck Regulators utilizes  $V_{REF}$ , an internal reference for regulating the output voltage. The output voltage setting is accomplished using external resistors as shown in Figure 33. Select R2 to be at or around  $1k\Omega$  for best noise immunity. Use Equations 2 and 3 to determine the proper value based on the desired output voltage.

Figure 33 — External resistor divider network

$$V_{OUT} = V_{REF} \bullet \frac{R1 + R2}{R2} \tag{2}$$

$$RI = R2 \bullet \frac{V_{OUT} - V_{REF}}{V_{RFF}} \tag{3}$$

where

$$V_{REF} = V_{EAIN}$$

**Note:** When using the above method of trimming by adjusting the value of R1, the compensation of the control loops is modified and additional Cout may be needed depending on the model. When the PI3526-00-LGIZ is trimmed below 10V, the effective  $C_{OUT}$  must be at least 120 $\mu$ F, including tolerance and voltage coefficient.

#### **Soft Start Adjust and Tracking**

The TRK pin offers a means to increase the regulator's soft-start time or to track with additional regulators. The soft-start slope is controlled by an internal capacitor and a fixed charge current to provide a Soft-Start Time  $t_{SS}$  for all Pl332x-00 regulators. By adding an additional external capacitor to the TRK pin, the soft-start time can be increased further. The following equation can be used to calculate the proper capacitor for a desired soft-start time in excess of  $t_{SS}$ :

$$C_{TRK} = (t_{TRK} \bullet I_{TRK}) - C_{TRK\_INT}$$

(4)

where  $t_{TRK}$  is the soft-start time and  $I_{TRK}$  is a 50 $\mu$ A internal charge current (see Electrical Characteristics for limits).

In applications such as battery or super-capacitor charging where the load is pre-biased, the PI332x can start into output voltages up to the externally applied trim setpoint, or the minimum absolute OVP, provided the value does not exceed 6V. For startup into loads which are pre-biased above 6V, an

ORing FET or equivalent sub-circuit is required to decouple the buck output from the load during startup. In any application with a CV type load, the regulator must be configured in a constant-current mode of operation; the built-in current limit is a fault protection only.

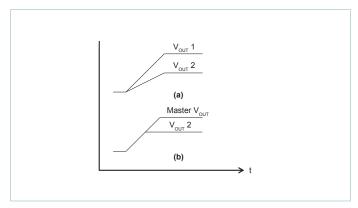

There is typically either proportional or direct tracking implemented within a design. For proportional tracking between several regulators at startup, simply connect all PI332x-00 device TRK pins together. This type of tracking will force all connected regulators to startup and reach regulation at the same time (see Figure 34a).

Figure 34 — PI332x-00 tracking responses

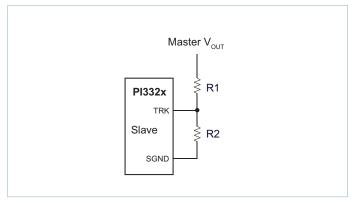

For Direct Tracking, choose the Pl332x-00 with the highest output voltage as the master and connect the master to the TRK pin of the other Pl332x-00 regulators through a divider (Figure 35) with the same ratio as the slave's feedback divider.

Figure 35 — Voltage divider connections for direct tracking

All connected PI332x-00 regulator soft-start slopes will track with this method. Direct tracking timing is demonstrated in Figure 34b. All tracking regulators should have their Enable (EN) pins connected together to work properly.

#### **Inductor Pairing**

The PI332x-00 utilizes an external inductor. This inductor has been optimized for maximum efficiency performance. Table 3 details the specific inductor value and part number utilized for each PI332x-00.

| Product<br>System | Value<br>(nH) | MFR   | Part Number     | Max Operating<br>Temp (°C) |

|-------------------|---------------|-------|-----------------|----------------------------|

| PI3325            | 230           | Eaton | FP2207R1-R230-R | 125                        |

**Table 3** — PI332x-00 Inductor pairing

The same inductor model may have different effective thermal impedances, depending on the model ZVS Buck paired with it. The thermal impedances are used in a virtual model of the inductor to estimate the maximum temperature, and the location of the maximum temperature may vary depending on the ZVS Buck model that the inductor is used with. This is because the effective thermal impedances are not only based on the geometry and materials used in the inductor, but include how the inductor power dissipation is distributed among core losses, DC copper losses, and AC copper losses. This distribution is dependent on the ZVS buck model that uses the inductor.

Figure 36 — PI332x-00 parallel operation

#### **Parallel Operation**

Multiple Pl332x-00 can be connected in parallel to increase the output capability of a single output rail. When connecting modules in parallel, each EAO, TRK, and EN pin should be connected together. EAIN pins should remain separated, each with an REA1 and REA2, to reject noise differences between different modules' SGND pins. Current sharing will occur automatically in this manner so long as each inductor is the same value. Refer to the Electrical Characteristics table for maximum array size and array rated output current. Current sharing may be considered independent of synchronization and/or interleaving. Modules do not have to be interleaved or synchronized to share current.

Due to the high output current capability of a single module and Critical Conduction Mode (CrCM) occurring at approximately 50% rated load, interleaving is not supported.

Use of the PI332x-00 SYNCI pin is practical only under a limited set of conditions. Synchronizing to another converter or to a fixed external clock source can result in a significant reduction in output power capability or higher than expected ripple.

#### **Filter Considerations**

The PI332x-00 requires low impedance ceramic input capacitors (X7R/X5R or equivalent) to ensure proper start up and high frequency decoupling for the power stage. The PI332x-00 will draw nearly all of the high frequency current from the low impedance ceramic capacitors when the main high side MOSFET(s) are conducting. During the time the MOSFET(s) are off, the input capacitors are replenished from the source. Table 6 shows the recommended input and output capacitors to be used for the PI332x-00 as well as per capacitor RMS ripple current and the input and output ripple voltages. Table 5 lists the recommended input and output ceramic capacitors manufacturer and part numbers. It is very important to verify that the voltage supply source as well as the interconnecting lines are stable and do not oscillate.

## Input filter case 1 — Inductive source and local, external, input decoupling capacitance with negligible ESR (i.e., ceramic type):

The voltage source impedance can be modeled as a series  $R_{\text{LINE}}$  circuit. The high performance ceramic decoupling capacitors will not significantly damp the network because of their low ESR; therefore in order to guarantee stability the following conditions must be verified:

$$R_{LINE} > \frac{L_{LINE}}{\left(C_{IN\_INT} + C_{IN\_EXT}\right) \cdot \left|r_{EQ\_IN}\right|} \tag{5}$$

$$R_{LINE} << \left| r_{EQ\_IN} \right| \tag{6}$$

Where  $r_{EQ\_IN}$  can be calculated by dividing the lowest line voltage by the full load input current. It is critical that the line source impedance be at least an octave lower than the converter's dynamic input resistance, Equation 6. However,  $R_{LINE}$  cannot be made arbitrarily low otherwise Equation 5 is violated and the system will show instability, due to an under-damped RLC input network.

## Input filter case 2 — Inductive source and local, external input decoupling capacitance with significant $R_{C_{IN\_EXT}}$ ESR (i.e., electrolytic type):

In order to simplify the analysis in this case, the voltage source impedance can be modeled as a simple inductor  $L_{\rm LINE}$ .

Notice that the high performance ceramic capacitors  $C_{\text{IN\_INT}}$  within the PI332x-00 should be included in the external electrolytic capacitance value for this purpose. The stability criteria will be:

$$\left| r_{EQ\_IN} \right| > R_{C_{IN\_EXT}} \tag{7}$$

$$\frac{L_{LINE}}{C_{IN\_INT} \cdot R_{C_{IN\_EXT}}} < |r_{EQ\_IN}| \tag{8}$$

Equation 8 shows that if the aggregate ESR is too small – for example by using very high quality input capacitors ( $C_{\text{IN\_EXT}}$ ) – the system will be under-damped and may even become destabilized. As noted, an octave of design margin in satisfying Equation 7 should be considered the minimum. When applying an electrolytic capacitor for input filter damping the ESR value must be chosen to avoid loss of converter efficiency and excessive power dissipation in the electrolytic capacitor.

#### **VDR Bias Regulator**

The VDR internal bias regulator is a ZVS switching regulator that resides internal to the PI332x-00 SiP. It is intended primarily to power the internal controller and driver circuitry. The power capability of this regulator is sized for the PI332x-00, with adequate reserve for the application it was intended for.

It may be used for as a pullup source for open collector applications and for other very low power uses with the following restrictions:

1. The total external loading on VDR must be less than I<sub>VDR</sub>.

- 2. No direct connection is allowed. Any noise source that can disturb the VDR voltage can also affect the internal controller operation. A series impedance is required between the VDR pin and any external circuitry.

- **3.** All loads must be locally de-coupled using a  $0.1\mu F$  ceramic capacitor. This capacitor must be connected to the VDR output through a series resistor no smaller than  $1k\Omega$ , which forms a low-pass filter.

#### **Additional System Design Considerations**

- 1. Inductive loads: As with all power electronic applications, consideration must be given to driving inductive loads that may be exposed to a fault in the system which could result in consequences beyond the scope of the power supply primary protection mechanisms. An inductive load could be a filter, fan motor or even excessively long cables. Consider an instantaneous short circuit through an un-damped inductance that occurs when the output capacitors are already at an initial condition of fully charged. The only thing that limits the current is the inductance of the short circuit and any series resistance. Even if the power supply is off at the time of the short circuit, the current could ramp up in the external inductor and store considerable energy. The release of this energy will result in considerable ringing, with the possibility of ringing nodes connected to the output voltage below ground. The system designer should plan for this by considering the use of other external circuit protection such as load switches, fuses, and transient voltage protectors. The inductive filters should be critically damped to avoid excessive ringing or damaging voltages. Adding a high current Schottky diode from the output voltage to PGND close to the PI332x-00 is recommended for these applications.

- 2. Low voltage operation: There is no isolation from an SELV (Safety-Extra-Low-Voltage) power system. Powering low voltage loads from input voltages as high as 60V may require additional consideration to protect low voltage circuits from excessive voltage in the event of a short circuit from input to output. A fast TVS (transient voltage suppressor) gating an external load switch is an example of such protection.

| Manufacturer | Part Number       | Value | Description        |

|--------------|-------------------|-------|--------------------|

| Murata       | GRM32ER71A476KE15 | 47μF  | 47μF 10V 1210 X7R  |

| Murata       | GRM32ER71A476K    | 4.7μF | 4.7μF 80V 1210 X7R |

**Table 5** — Recommended input and output capacitor components

| Product | Load<br>Current<br>(A) | C <sub>IN</sub> | C <sub>OUT</sub> | C <sub>IN</sub><br>Ripple<br>Current<br>(I <sub>RMS</sub> ) | C <sub>OUT</sub><br>Ripple<br>Current<br>(I <sub>RMS</sub> ) | V <sub>IN</sub><br>Ripple<br>(mVpp) | V <sub>out</sub><br>Ripple<br>(mVpp) | Load<br>Step<br>(% Rating)<br>(1A/µs) | Transient<br>Deviation<br>Excluding<br>Ripple<br>(mVpk) | V <sub>OUT</sub><br>Recovery<br>Time (μs) |

|---------|------------------------|-----------------|------------------|-------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------|--------------------------------------|---------------------------------------|---------------------------------------------------------|-------------------------------------------|

| PI3325  | 20                     | 6 x<br>4.7μF    | 12 x 47μF        | 10.43                                                       | 13.25                                                        | 512                                 | 55.7                                 | 50 – 100                              | 90                                                      | <80                                       |

**Table 6** — Recommended input and output capacitor quantity and performance at nominal line, nominal trim.

#### **Layout Guidelines**

To optimize maximum efficiency and low noise performance from a PI332x-00 design, layout considerations are necessary. Reducing trace resistance and minimizing high current loop returns along with proper component placement will contribute to optimized performance.

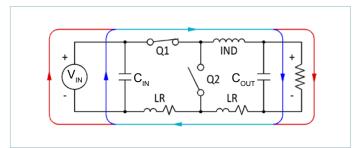

A typical buck converter circuit is shown in Figure 37. The potential areas of high parasitic inductance and resistance are the circuit return paths, shown as LR below.

Figure 37 — Typical Buck Regulator

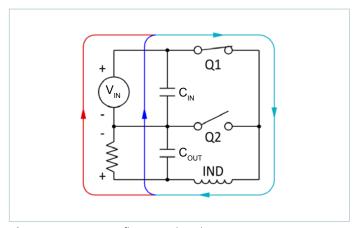

The path between the  $C_{OUT}$  and  $C_{IN}$  capacitors is of particular importance since the AC currents are flowing through both of them when Q1 is turned on. Figure 38, schematically, shows the reduced trace length between input and output capacitors. The shorter path lessens the effects that copper trace parasitics can have on the PI332x-00 performance.

Figure 38 — Current flow: Q1 closed

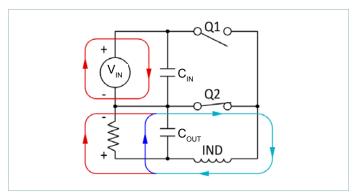

When Q1 is on and Q2 is off, the majority of  $C_{\text{IN}}$ 's current is used to satisfy the output load and to recharge the  $C_{\text{OUT}}$  capacitors. When Q1 is off and Q2 is on, the load current is supplied by the inductor and the  $C_{\text{OUT}}$  capacitor as shown in Figure 39. During this period  $C_{\text{IN}}$  is also being recharged by the  $V_{\text{IN}}$ . Minimizing  $C_{\text{IN}}$  loop inductance is important to reduce peak voltage excursions when Q1 turns off. Also, the difference in area between the  $C_{\text{IN}}$  loop and  $C_{\text{OUT}}$  loop is vital to minimize switching and GND noise.

Figure 39 — Current flow: Q2 closed

Figure 40 illustrates the tight path between  $C_{IN}$  and  $C_{OUT}$  (and  $V_{IN}$  and  $V_{OUT}$ ) for the high AC return current. The PI332x-00 evaluation board uses a layout optimized for performance in this way.

**Figure 40** — Recommended layout for Optimized AC Current within the SiP, Inductor, and Ceramic Input and Output Capacitors

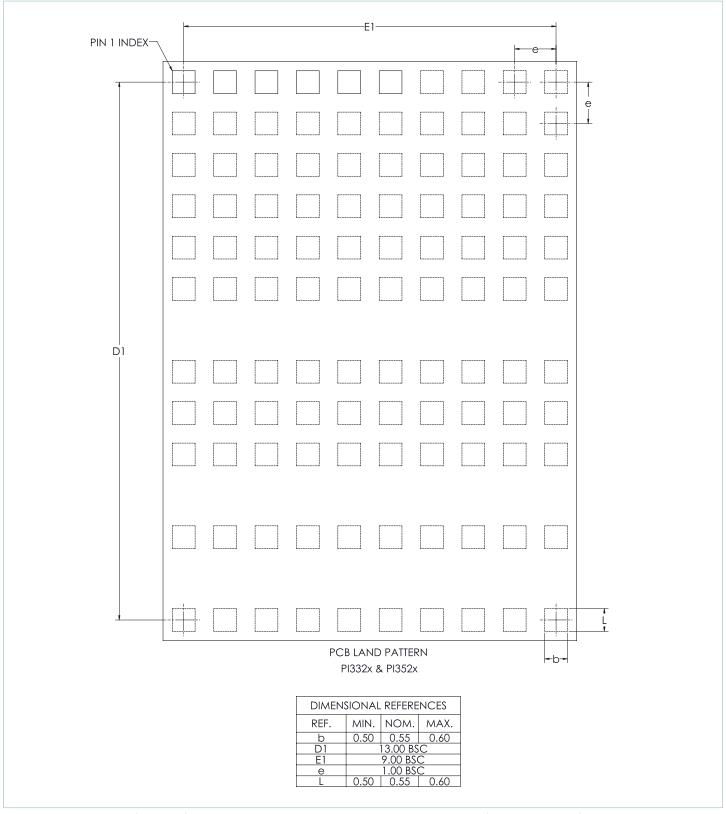

### **Recommended PCB Footprint and Stencil**

Recommended receiving footprint for PI332x-00 10 x 14mm package. All pads should have a final copper size of  $0.55 \times 0.55$ mm, whether they are solder-mask defined or copper defined, on a 1 x 1mm grid. All stencil openings are 0.45mm when using either a 5mil or 6mil stencil.

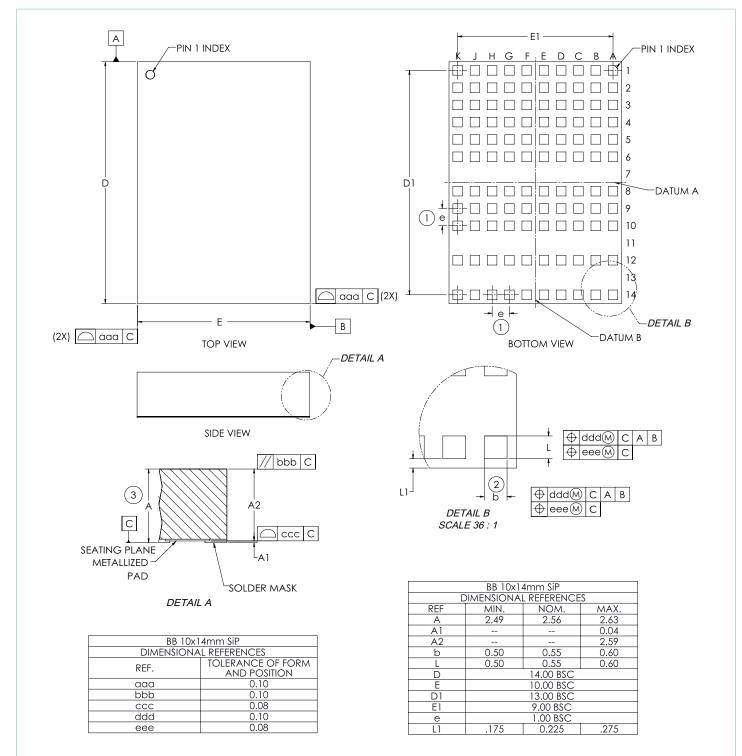

#### **Package Drawings**

#### NOTES:

- 1. 'e' REPRESENTS THE BASIC TERMINAL PITCH. SPECIFIES THE GEOMETRIC POSITION OF THE TERMINAL AXIS.

- 2. DIMENSION 'b' APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.00mm AND 0.25mm FROM TERMINAL TIP.

- 3. DIMENSION 'A' INCLUDES PACKAGE WARPAGE.

- 4. EXPOSED METALLIZED PADS ARE CU PADS WITH SURFACE FINISH PROTECTION.

- 5. ALL DIMENSIONS ARE IN MM UNLESS OTHERWISE SPECIFIED.

- 6. Rohs Compliant Per CST-0001 Latest Revision.

## **Revision History**

| Revision | Date     | Description                      | Page Number(s) |

|----------|----------|----------------------------------|----------------|

| 1.0      | 12/05/17 | Initial release                  | n/a            |

| 1.1      | 02/06/18 | Added typical start-up waveforms | 14             |

#### Vicor's comprehensive line of power solutions includes high density AC-DC and DC-DC modules and accessory components, fully configurable AC-DC and DC-DC power supplies, and complete custom power systems.

Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility is assumed by Vicor for its use. Vicor makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication. Vicor reserves the right to make changes to any products, specifications, and product descriptions at any time without notice. Information published by Vicor has been checked and is believed to be accurate at the time it was printed; however, Vicor assumes no responsibility for inaccuracies. Testing and other quality controls are used to the extent Vicor deems necessary to support Vicor's product warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

Specifications are subject to change without notice.

Visit <a href="http://www.vicorpower.com/dc-dc-converters-board-mount/cool-power-pi33xx-and-pi34xx">http://www.vicorpower.com/dc-dc-converters-board-mount/cool-power-pi33xx-and-pi34xx</a> for the latest product information.

#### **Vicor's Standard Terms and Conditions and Product Warranty**

All sales are subject to Vicor's Standard Terms and Conditions of Sale, and Product Warranty which are available on Vicor's webpage (http://www.vicorpower.com/termsconditionswarranty) or upon request.

#### **Life Support Policy**

VICOR'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF VICOR CORPORATION. As used herein, life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness. Per Vicor Terms and Conditions of Sale, the user of Vicor products and components in life support applications assumes all risks of such use and indemnifies Vicor against all liability and damages.

#### **Intellectual Property Notice**

Vicor and its subsidiaries own Intellectual Property (including issued U.S. and Foreign Patents and pending patent applications) relating to the products described in this data sheet. No license, whether express, implied, or arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Interested parties should contact Vicor's Intellectual Property Department.

The products described on this data sheet are protected by U.S. Patents. Please see <a href="https://www.vicorpower.com/patents">www.vicorpower.com/patents</a> for the latest patent information.

Contact Us: http://www.vicorpower.com/contact-us

#### **Vicor Corporation**

25 Frontage Road Andover, MA, USA 01810 Tel: 800-735-6200 Fax: 978-475-6715 www.vicorpower.com

#### email

Customer Service: custserv@vicorpower.com Technical Support: <a href="mailto:apps@vicorpower.com">apps@vicorpower.com</a>

©2017 – 2018 Vicor Corporation. All rights reserved. The Vicor name is a registered trademark of Vicor Corporation. All other trademarks, product names, logos and brands are property of their respective owners.