# 56F8014

Data Sheet

*Technical Data*

**56F8000**

**16-bit Digital Signal Controllers**

MC56F8014

Rev. 11

05/2008

[freescale.com](http://freescale.com)

## Document Revision History

| Version History | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 0           | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Rev 1           | <p>Updates to <a href="#">Part 10, Specifications</a>,<br/> <a href="#">Table 10-1</a>, added maximum clamp current, per pin<br/> <a href="#">Table 10-11</a>, clarified variation over temperature table and graph<br/> <a href="#">Table 10-15</a>, added LIN slave timing</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

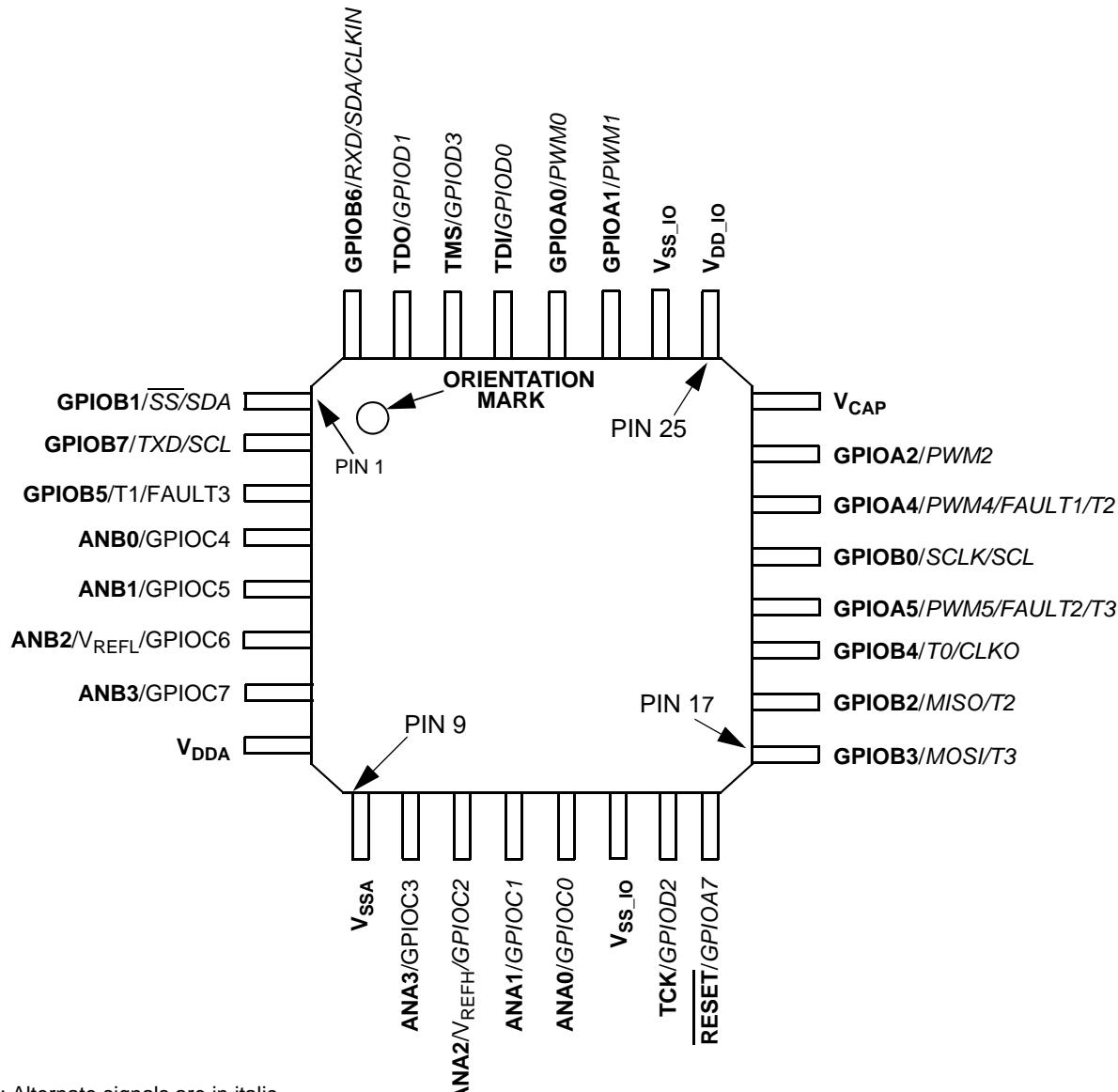

| Rev 2           | Added alternate pins to <a href="#">Figure 11-1</a> and <a href="#">Table 11-1</a> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Rev 3           | Corrected bit selects in Timer Channel 3 Input (TC3_INP) bit 9, <a href="#">Section 6.3.1.7</a> , clarified <a href="#">Section 1.4.1</a> , and simplified notes in <a href="#">Table 10-9</a> ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Rev 4           | Added clarification on sync inputs in <a href="#">Section 1.4.1</a> , added voltage difference specification to <a href="#">Table 10-1</a> and <a href="#">Table 10-4</a> , deleted formula for Ambient Operating Temperature in <a href="#">Table 10-4</a> , and a note for pin group 3, corrected <a href="#">Table 8-1</a> , error in Port C peripheral function configuration, updated notes in <a href="#">Table 10-9</a> . Added RoHs and “pb-free” language to back cover.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

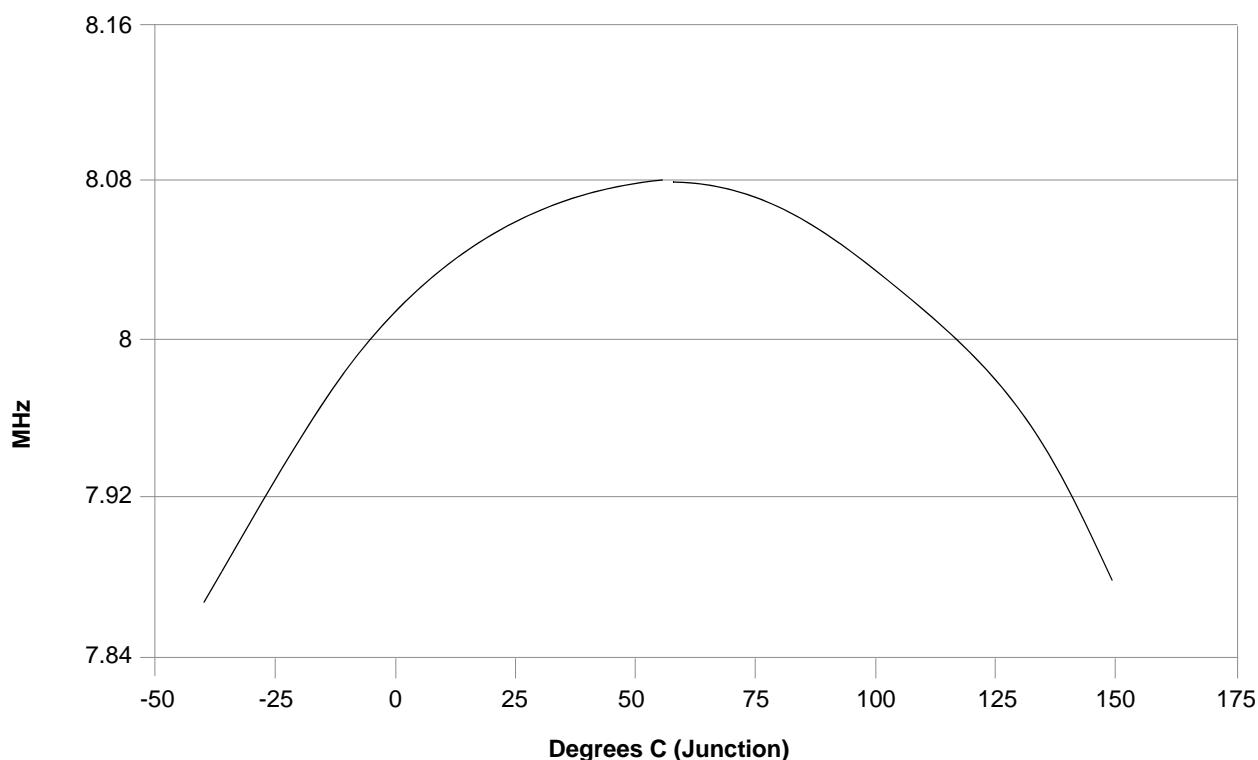

| Rev 5           | <p>Updates to <a href="#">Section 10</a><br/> <a href="#">Table 10-5</a>, corrected max values for ADC Input Current High and Low; corrected typ value for pull-up disabled Digital Input Current Low (a)<br/> <a href="#">Table 10-6</a>, corrected typ and added max values for Standby &gt; Stop and Powerdown modes<br/> <a href="#">Table 10-7</a>, corrected min value for Low-Voltage Interrupt for 3.3V<br/> <a href="#">Table 10-11</a>, corrected typ and max values and units for PLL lock time<br/> <a href="#">Table 10-12</a>, corrected typ values for Relaxation Oscillator output frequency and variation over temperature (also increased temp range to 150 degreesC) and added variation over temperature from 0—105 degreesC<br/> Updated <a href="#">Figure 10-5</a><br/> <a href="#">Table 10-19</a>, updated max values for Integral Non-Linearity full input signal range, Negative Differential Non-Linearity, ADC internal clock, Offset Voltage Internal Ref, Gain Error and Offset Voltage External Ref; updated typ values for Negative Differential Non-Linearity, Offset Voltage Internal Ref, Gain Error and Offset Voltage External Ref; added new min values and corrected typ values for Signal-to-noise ratio, Total Harmonic Distortion, Spurious Free Dynamic Range, Signal-to-noise plus distortion, Effective Number of Bits</p> |

| Rev 6           | Added details to Section 1. Clarified language in State During Reset column in <a href="#">Table 2-3</a> ; corrected flash data retention temperature in <a href="#">Table 10-4</a> ; moved input current high/low to <a href="#">Table 10-19</a> and location of footnotes in <a href="#">Table 10-5</a> ; reorganized <a href="#">Table 10-19</a> ; clarified title of <a href="#">Figure 10-1</a> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Rev. 7          | <ul style="list-style-type: none"> <li>• In <a href="#">Table 10-4</a>, added an entry for flash data retention with less than 100 program/erase cycles (minimum 20 years).</li> <li>• In <a href="#">Table 10-6</a>, changed the device clock speed in STOP mode from 8MHz to 4MHz.</li> <li>• In <a href="#">Table 10-12</a>, changed the typical relaxation oscillator output frequency in Standby mode from 400kHz to 200kHz.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Rev. 8          | In <a href="#">Table 10-19</a> , changed the maximum ADC internal clock frequency from 8MHz to 5.33MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## Document Revision History (Continued)

| Version History | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 9          | Added the following note to the description of the TMS signal in <b>Table 2-3</b> :<br><b>Note:</b> Always tie the TMS pin to V <sub>DD</sub> through a 2.2K resistor.                                                                                                                                                                                                                                                                                                                                               |

| Rev. 10         | <ul style="list-style-type: none"><li>In <b>Table 2-3</b>, changed V<sub>CAP</sub> value from 4.7 <math>\mu</math>F to 2.2 <math>\mu</math>F.</li><li>In <b>Table 2-3</b>, changed the input type for FAULT3 (was "Output", is "Input").</li><li>In <b>Table 2-3</b>, changed the input type for FAULT2 (was "Input/Output", is "Input").</li><li>Revised <b>Section 7, Security Features</b>.</li><li>Added MC56F8014MFAE to <b>Section 13, Ordering Information</b>.</li><li>Fixed miscellaneous errors.</li></ul> |

| Rev.11          | <ul style="list-style-type: none"><li>Updated temperature information in <b>Table 10-1</b> and <b>Table 10-4</b>.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                          |

Please see <http://www.freescale.com> for the most current data sheet revision.

# 56F8014 General Description

- Up to 32 MIPS at 32MHz core frequency

- DSP and MCU functionality in a unified, C-efficient architecture

- 16KB Program Flash

- 4KB Unified Data/Program RAM

- One 5-channel PWM module

- Two 4-channel 12-bit ADCs

- One Serial Communication Interface (SCI) with LIN slave functionality

- One Serial Peripheral Interface (SPI)

- One 16-bit Quad Timer

- One Inter-Integrated Circuit (I<sup>2</sup>C) Port

- Computer Operating Properly (COP)/Watchdog

- On-Chip Relaxation Oscillator

- Integrated Power-On Reset and Low-Voltage Interrupt Module

- JTAG/Enhanced On-Chip Emulation (OnCE<sup>TM</sup>) for unobtrusive, real-time debugging

- Up to 26 GPIO lines

- 32-pin LQFP Package

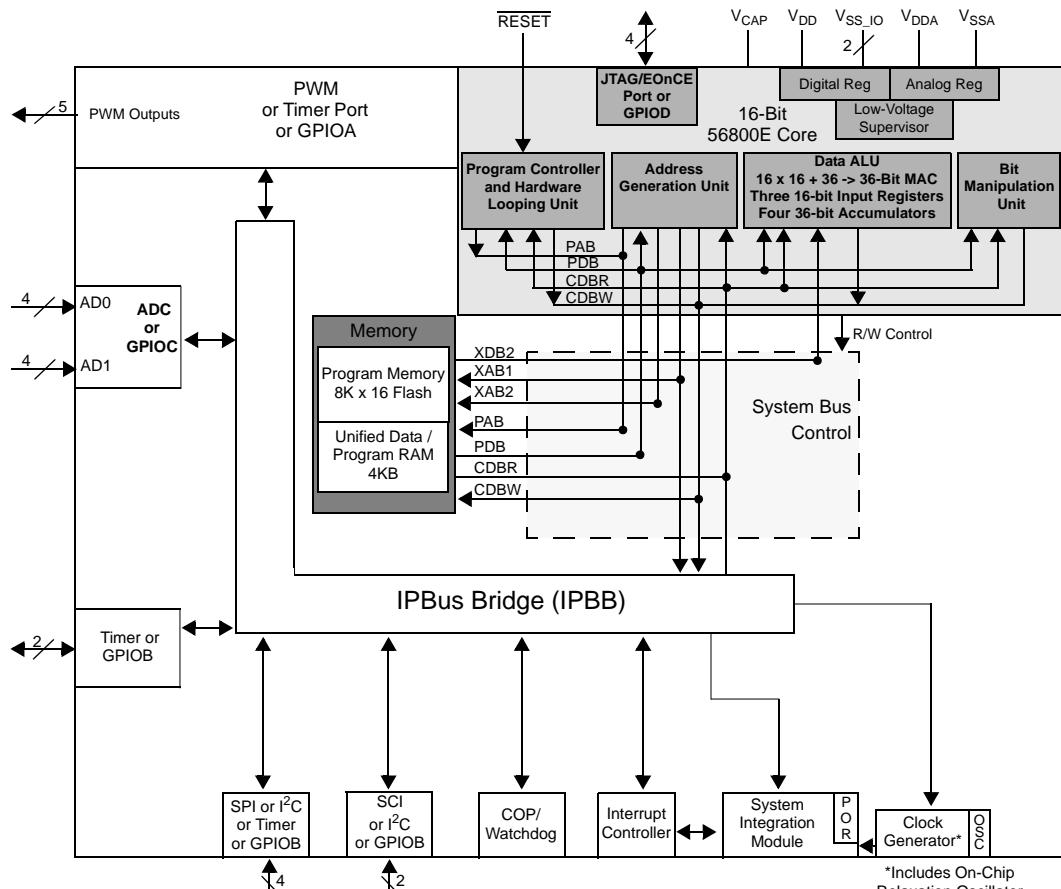

56F8014 Block Diagram

\*Includes On-Chip Relaxation Oscillator

# 56F8014 Data Sheet Table of Contents

|                                                   |           |                                                                     |            |

|---------------------------------------------------|-----------|---------------------------------------------------------------------|------------|

| <b>Part 1: Overview</b> .....                     | <b>6</b>  | <b>Part 7: Security Features</b> .....                              | <b>82</b>  |

| 1.1. 56F8014 Features .....                       | 6         | 7.1. Operation with Security Enabled .....                          | 82         |

| 1.2. 56F8014 Description .....                    | 8         | 7.2. Flash Access Lock and Unlock Mechanisms .....                  | 83         |

| 1.3. Award-Winning Development Environment .....  | 8         | 7.3. Product Analysis .....                                         | 84         |

| 1.4. Architecture Block Diagram .....             | 9         |                                                                     |            |

| 1.5. Synchronize ADC with PWM .....               | 9         |                                                                     |            |

| 1.6. Multiple Frequency PWM Output .....          | 9         |                                                                     |            |

| 1.7. Product Documentation .....                  | 13        |                                                                     |            |

| 1.8. Data Sheet Conventions .....                 | 13        |                                                                     |            |

| <b>Part 2: Signal/Connection Descriptions</b> ..  | <b>14</b> | <b>Part 8: General Purpose Input/Output (GPIO)</b> .....            | <b>84</b>  |

| 2.1. Introduction .....                           | 14        | 8.1. Introduction .....                                             | 84         |

| 2.2. 56F8014 Signal Pins .....                    | 18        | 8.2. Configuration .....                                            | 84         |

|                                                   |           | 8.3. Reset Values .....                                             | 86         |

| <b>Part 3: OCCS</b> .....                         | <b>26</b> |                                                                     |            |

| 3.1. Overview .....                               | 26        | <b>Part 9: Joint Test Action Group (JTAG)</b> ..                    | <b>91</b>  |

| 3.2. Features .....                               | 26        | 9.1. 56F8014 Information .....                                      | 91         |

| 3.3. Operating Modes .....                        | 26        |                                                                     |            |

| 3.4. Block Diagram .....                          | 28        |                                                                     |            |

| 3.5. Pin Descriptions .....                       | 29        | <b>Part 10: Specifications</b> .....                                | <b>91</b>  |

| <b>Part 4: Memory Map</b> .....                   | <b>29</b> | 10.1. General Characteristics .....                                 | 91         |

| 4.1. Introduction .....                           | 29        | 10.2. DC Electrical Characteristics .....                           | 95         |

| 4.2. Interrupt Vector Table .....                 | 29        | 10.3. AC Electrical Characteristics .....                           | 97         |

| 4.3. Program Map .....                            | 31        | 10.4. Flash Memory Characteristics .....                            | 98         |

| 4.4. Data Map .....                               | 32        | 10.5. External Clock Operation Timing .....                         | 99         |

| 4.5. EOnCE Memory Map .....                       | 32        | 10.6. Phase Locked Loop Timing .....                                | 99         |

| 4.6. Peripheral Memory Mapped Registers .....     | 33        | 10.7. Relaxation Oscillator Timing .....                            | 100        |

|                                                   |           | 10.8. Reset, Stop, Wait, Mode Select, and<br>Interrupt Timing ..... | 101        |

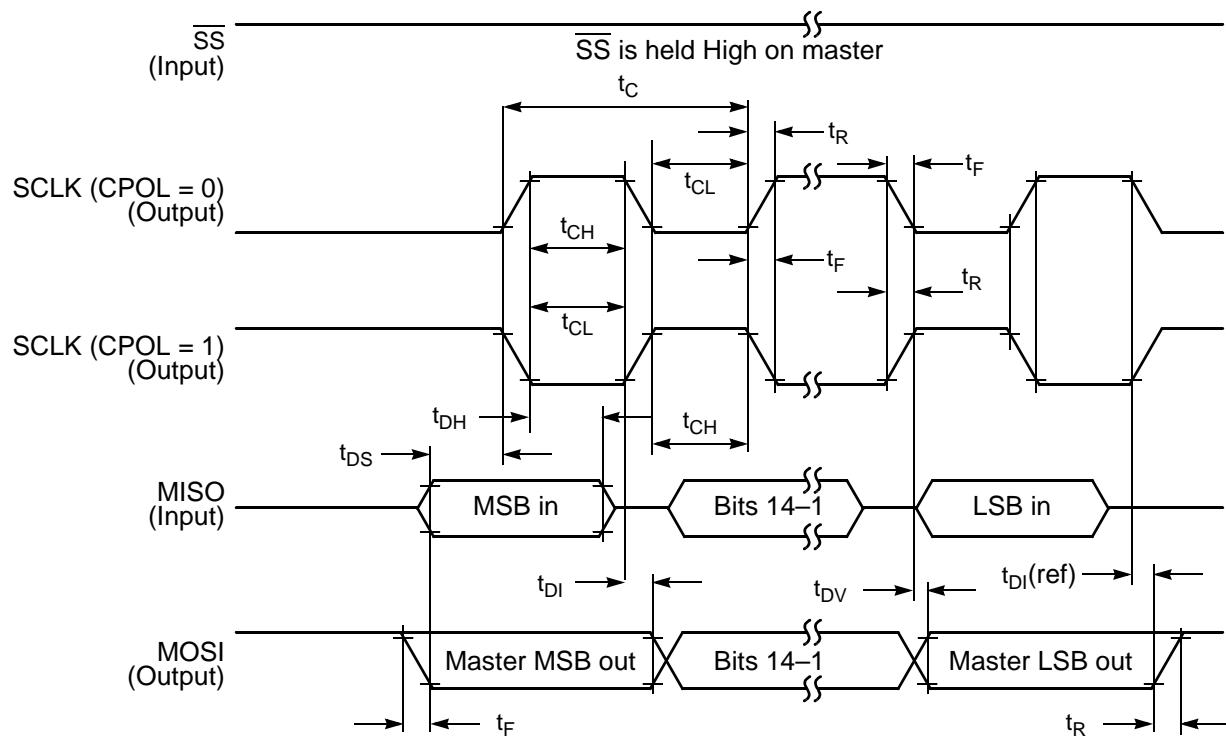

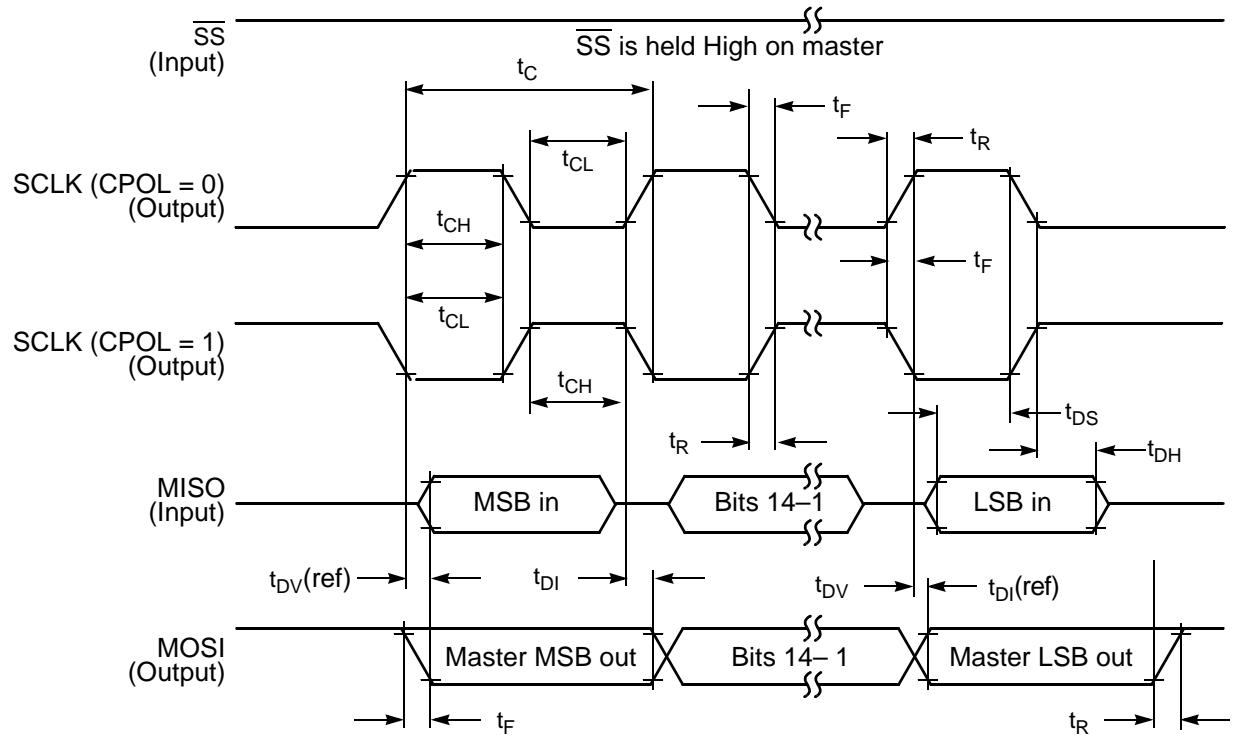

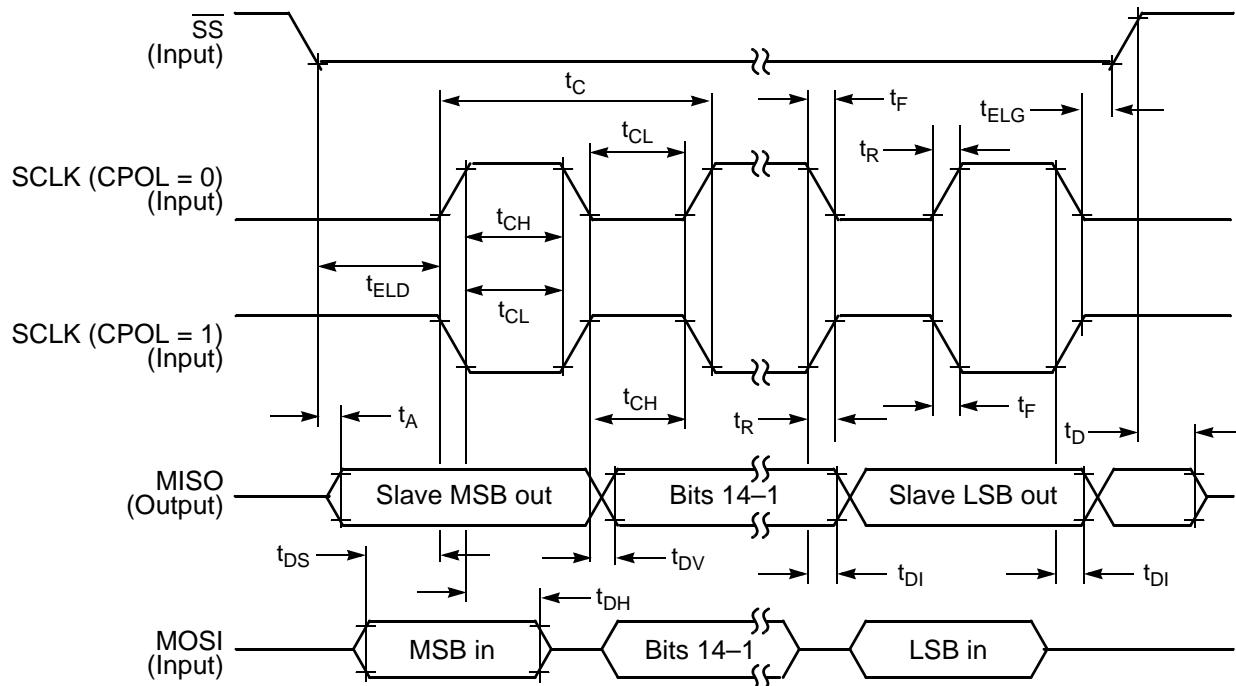

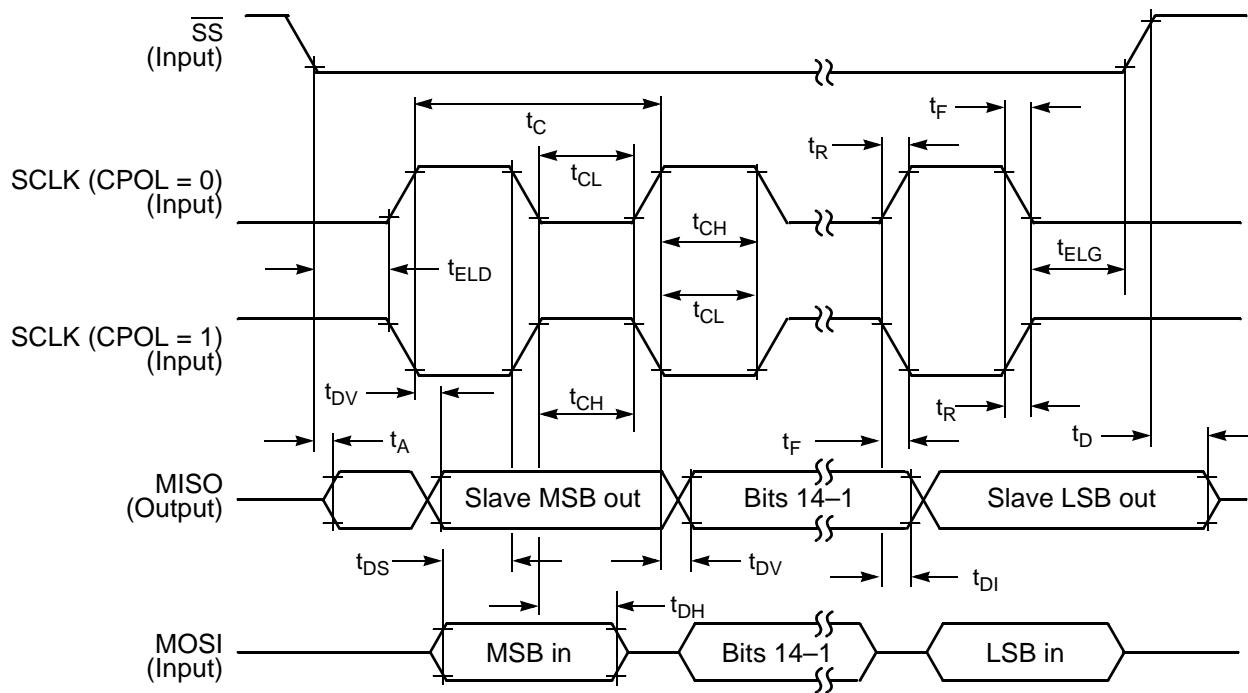

| <b>Part 5: Interrupt Controller (ITCN)</b> .....  | <b>43</b> | 10.9. Serial Peripheral Interface (SPI) Timing ..                   | 102        |

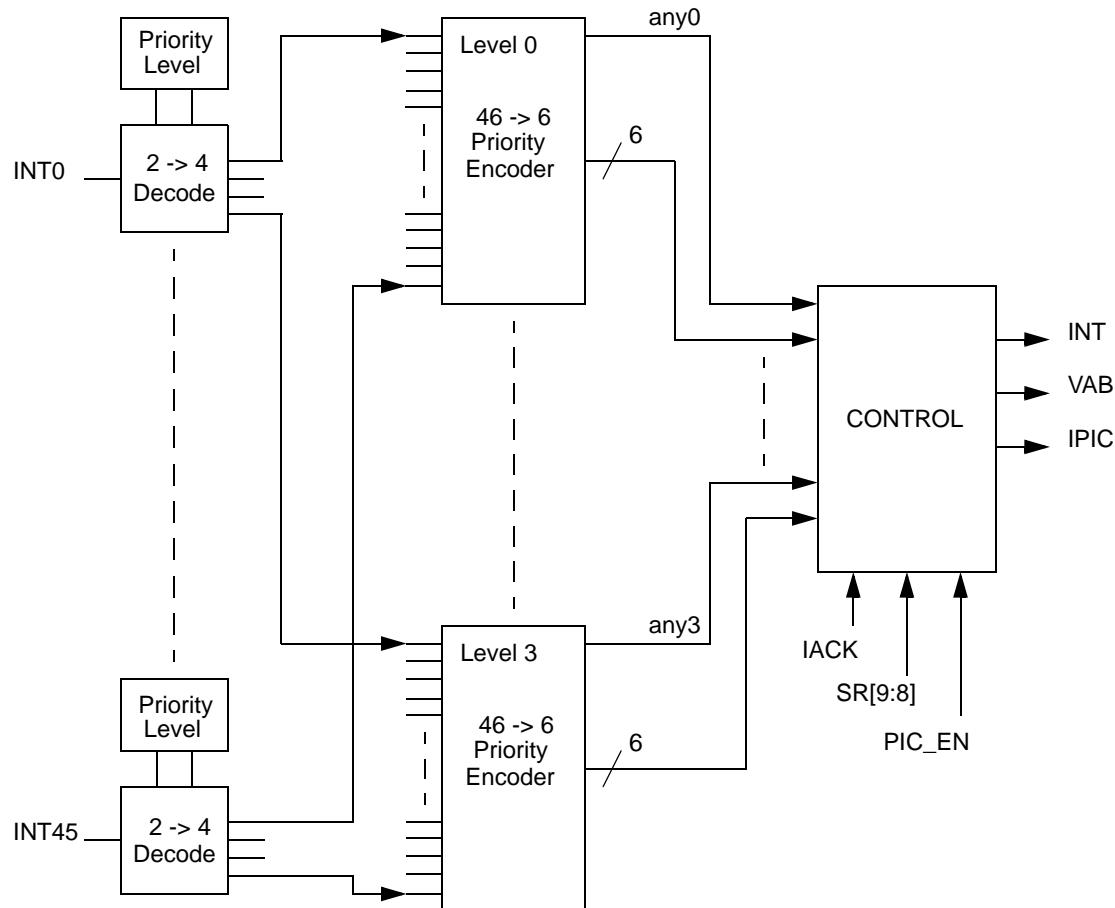

| 5.1. Introduction .....                           | 43        | 10.10. Quad Timer Timing .....                                      | 105        |

| 5.2. Features .....                               | 43        | 10.11. Serial Communication Interface (SCI)<br>Timing .....         | 107        |

| 5.3. Functional Description .....                 | 43        | 10.12. Inter-Integrated Circuit Interface (I2C)<br>Timing .....     | 108        |

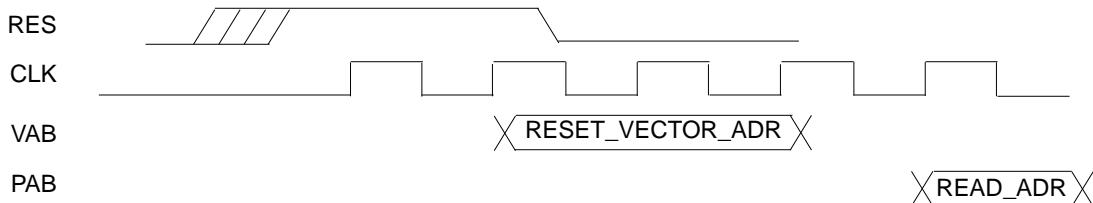

| 5.4. Block Diagram .....                          | 45        | 10.13. JTAG Timing .....                                            | 109        |

| 5.5. Register Descriptions .....                  | 45        | 10.14. Analog-to-Digital Converter (ADC)<br>Parameters .....        | 111        |

| 5.6. Resets .....                                 | 61        | 10.15. Equivalent Circuit for ADC Inputs .....                      | 112        |

|                                                   |           | 10.16. Power Consumption .....                                      | 112        |

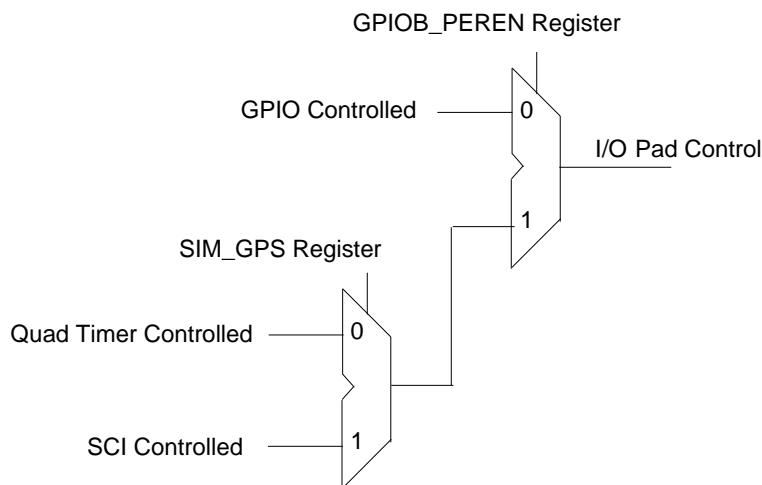

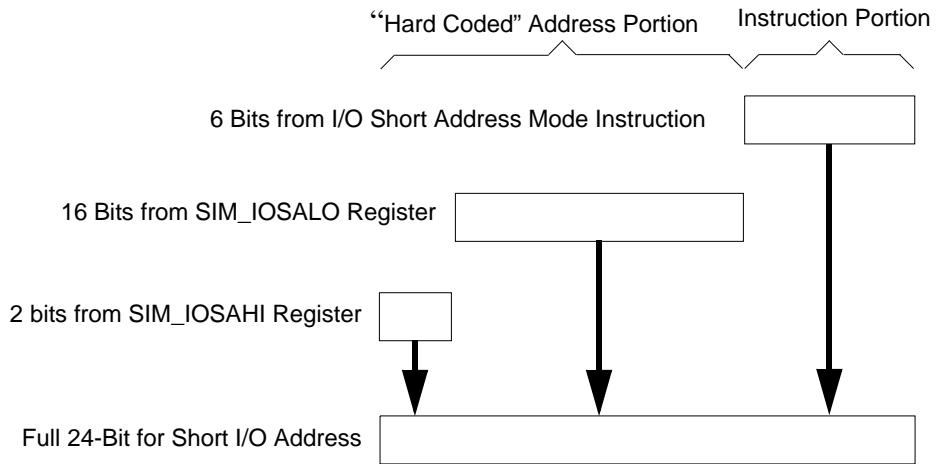

| <b>Part 6: System Integration Module (SIM)</b> .. | <b>62</b> |                                                                     |            |

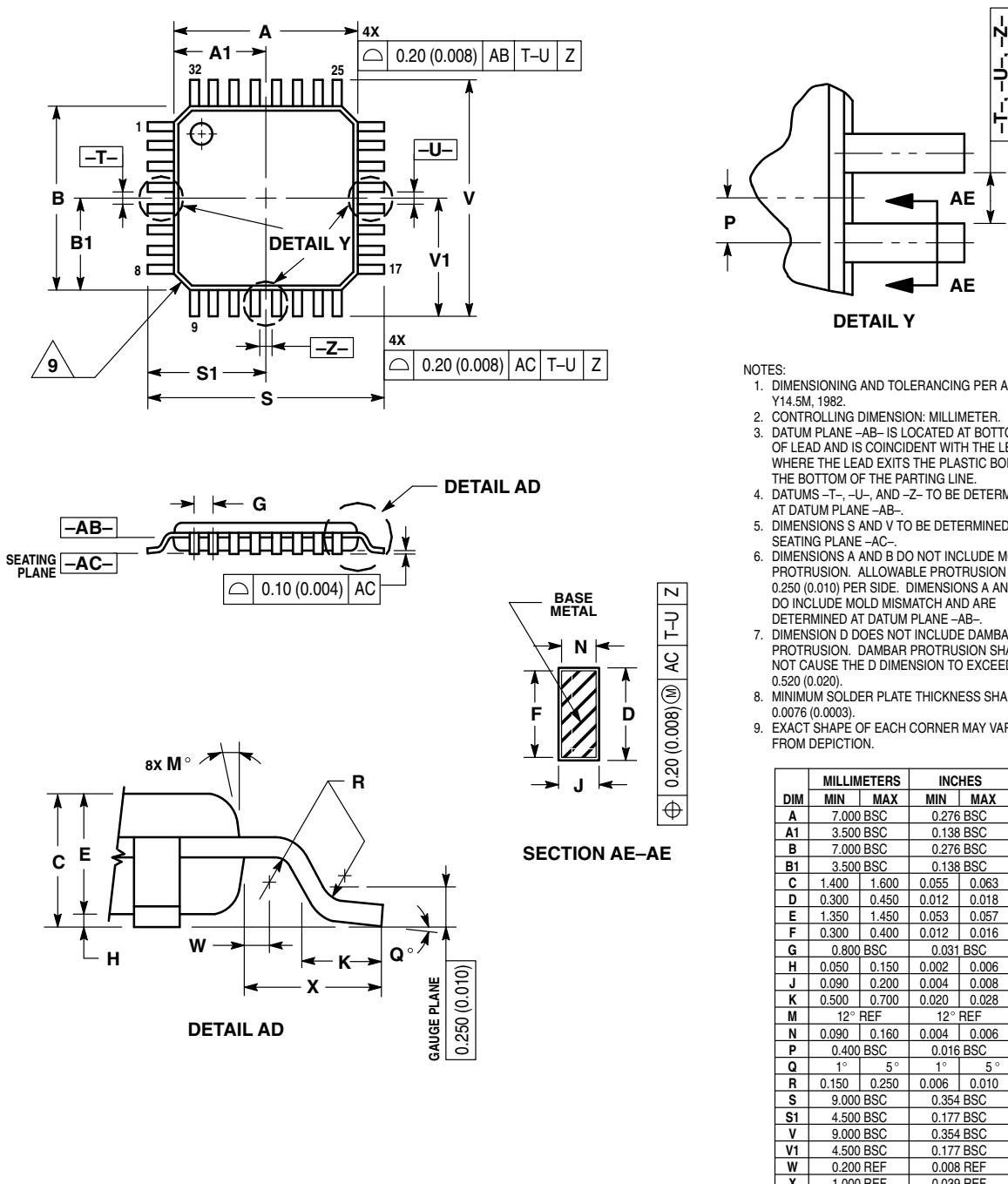

| 6.1. Introduction .....                           | 62        | <b>Part 11: Packaging</b> .....                                     | <b>115</b> |

| 6.2. Features .....                               | 62        | 11.1. 56F8014 Package and Pin-Out<br>Information .....              | 115        |

| 6.3. Register Descriptions .....                  | 64        |                                                                     |            |

| 6.4. Clock Generation Overview .....              | 77        |                                                                     |            |

| 6.5. Power-Down Modes .....                       | 77        | <b>Part 12: Design Considerations</b> .....                         | <b>118</b> |

| 6.6. Resets .....                                 | 79        | 12.1. Thermal Design Considerations .....                           | 118        |

| 6.7. Clocks .....                                 | 81        | 12.2. Electrical Design Considerations .....                        | 119        |

| 6.8. Interrupts .....                             | 82        |                                                                     |            |

|                                                   |           | <b>Part 13: Ordering Information</b> .....                          | <b>121</b> |

|                                                   |           | <b>Part 14: Appendix</b> .....                                      | <b>122</b> |

# Part 1 Overview

## 1.1 56F8014 Features

### 1.1.1 Digital Signal Controller Core

- Efficient 16-bit 56800E family Digital Signal Controller (DSC) engine with dual Harvard architecture

- As many as 32 Million Instructions Per Second (MIPS) at 32MHz core frequency

- Single-cycle  $16 \times 16$ -bit parallel Multiplier-Accumulator (MAC)

- Four 36-bit accumulators, including extension bits

- 32-bit arithmetic and logic multi-bit shifter

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Three internal address buses

- Four internal data buses

- Instruction set supports both DSP and controller functions

- Controller-style addressing modes and instructions for compact code

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, processor speed-independent, real-time debugging

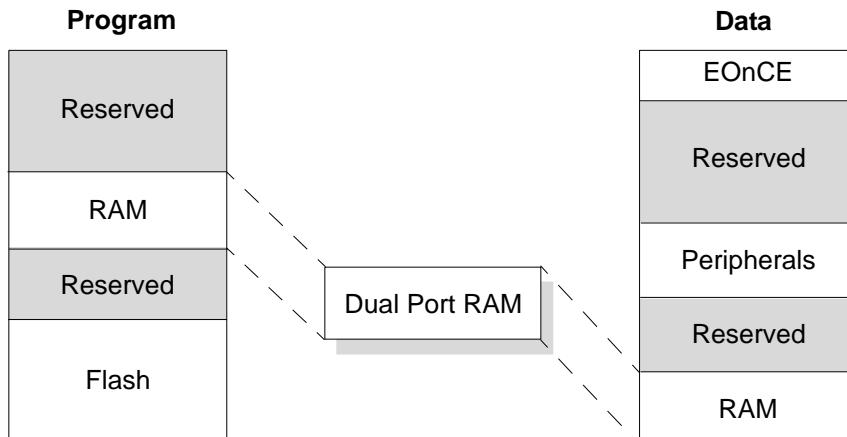

### 1.1.2 Memory

- Dual Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Flash security and protection that prevent unauthorized users from gaining access to the internal Flash

- On-chip memory

- 16KB of Program Flash

- 4KB of Unified Data/Program RAM

- EEPROM emulation capability using Flash

### 1.1.3 Peripheral Circuits for 56F8014

- One multi-function five-output Pulse Width Modulator (PWM) module

- Up to 96MHz PWM operating clock

- 15 bits of resolution

- Center-aligned and Edge-aligned PWM signal mode

- Three programmable fault inputs with programmable digital filter

- Double-buffered PWM registers

- Each complementary PWM signal pair can output a different switching frequency by selecting PWM generation sources from:

- PWM generator

- External GPIO

- Internal timers

- ADC conversion result of over/under limits:

When conversion result is greater than high limit, deactivate PWM signal

When conversion result is less than low limit, activate PWM signal

- Two independent 12-bit Analog-to-Digital Converters (ADCs)

- 2 x 4 channel inputs

- Supports both simultaneous and sequential conversions

- ADC conversions can be synchronized by both PWM and timer modules

- Sampling rate up to 2.67MSPS

- 8-word result buffer registers

- ADC Smart Power Management (Auto-standby, auto-powerdown)

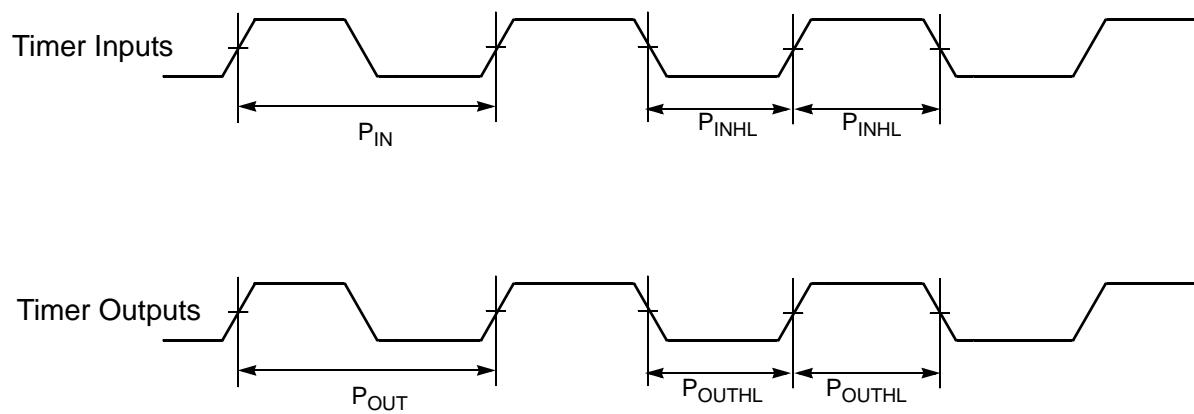

- One 16-bit multi-purpose Quad Timer module (TMR)

- Up to 96MHz operating clock

- Four independent 16-bit counter/timers with cascading capability

- Each timer has capture and compare capability

- Up to 12 operating modes

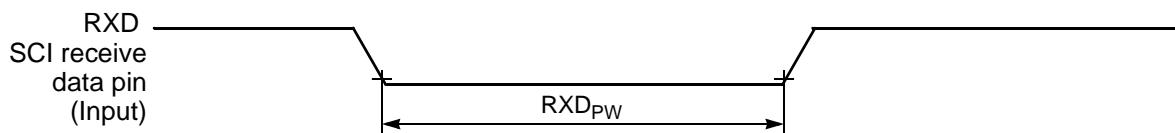

- One Serial Communication Interface (SCI) with LIN slave functionality

- Full-duplex or single-wire operation

- Two receiver wake-up methods:

- Idle line

- Address mark

- One Serial Peripheral Interface (SPI)

- Full-duplex operation

- Master and slave modes

- Programmable length transactions (two to sixteen bits)

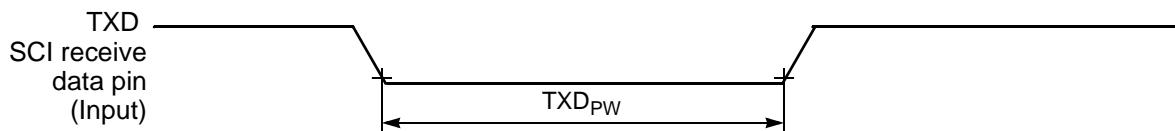

- One Inter-Integrated Circuit (I<sup>2</sup>C) port

- Operates up to 400 kbps

- Supports both master and slave operation

- Computer Operating Properly (COP)/Watchdog timer capable of selecting different clock sources

- Up to 26 General-Purpose I/O (GPIO) pins with 5V tolerance

- Integrated Power-On Reset and Low-Voltage Interrupt Module

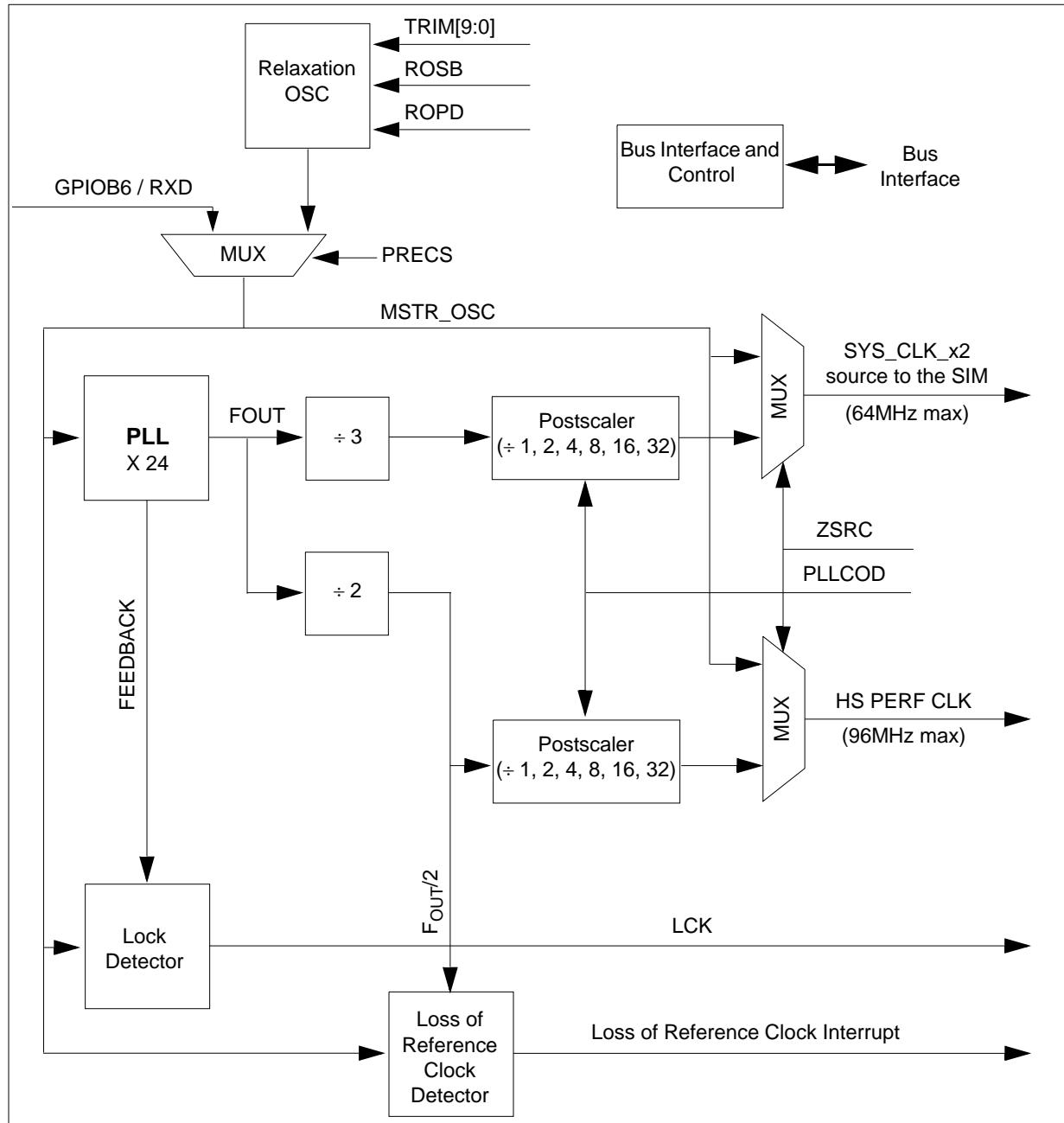

- Phase Lock Loop (PLL) provides a high-speed clock to the core and peripherals

- Clock Sources:

- On-chip relaxation oscillator

- External clock source

- On-chip regulators for digital and analog circuitry to lower cost and reduce noise

- JTAG/EOnCE debug programming interface for real-time debugging

#### 1.1.4 Energy Information

- Fabricated in high-density CMOS with 5V-tolerant, TTL-compatible digital inputs

- On-chip regulators for digital and analog circuitry to lower cost and reduce noise

- Wait and Stop modes available

- ADC smart power management

- Each peripheral can be individually disabled to save power

### 1.2 56F8014 Description

The 56F8014 is a member of the 56800E core-based family of Digital Signal Controllers (DSCs). It combines, on a single chip, the processing power of a DSP and the functionality of a microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because of its low cost, configuration flexibility, and compact program code, the 56F8014 is well-suited for many applications. The 56F8014 includes many peripherals that are especially useful for industrial control, motion control, home appliances, general purpose inverters, smart sensors, fire and security systems, switched-mode power supplies, power management, and medical monitoring applications.

The 56800E core is based on a dual Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C compilers to enable rapid development of optimized control applications.

The 56F8014 supports program execution from internal memories. Two data operands can be accessed from the on-chip data RAM per instruction cycle. The 56F8014 also offers up to 26 General Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

The 56F8014 Digital Signal Controller includes 16KB of Program Flash and 4KB of Unified Data/Program RAM. Program Flash memory can be independently bulk erased or erased in pages. Program Flash page erase size is 512 Bytes/256 Words.

A full set of programmable peripherals—PWM, ADCs, SCI, SPI, I<sup>2</sup>C, Quad Timer—support various applications. Each peripheral can be independently shut down to save power. Any pin in these peripherals can also be used as a General Purpose Input/Outputs (GPIO).

### 1.3 Award-Winning Development Environment

Processor Expert<sup>TM</sup> (PE) provides a Rapid Application Design (RAD) tool that combines easy-to-use component-based software application creation with an expert knowledge system.

The CodeWarrior Integrated Development Environment is a sophisticated tool for code navigation, compiling, and debugging. A complete set of evaluation modules (EVMs), demonstration board kit and development system cards will support concurrent engineering. Together, PE, CodeWarrior and EVMs

create a complete, scalable tools solution for easy, fast, and efficient development.

## 1.4 Architecture Block Diagram

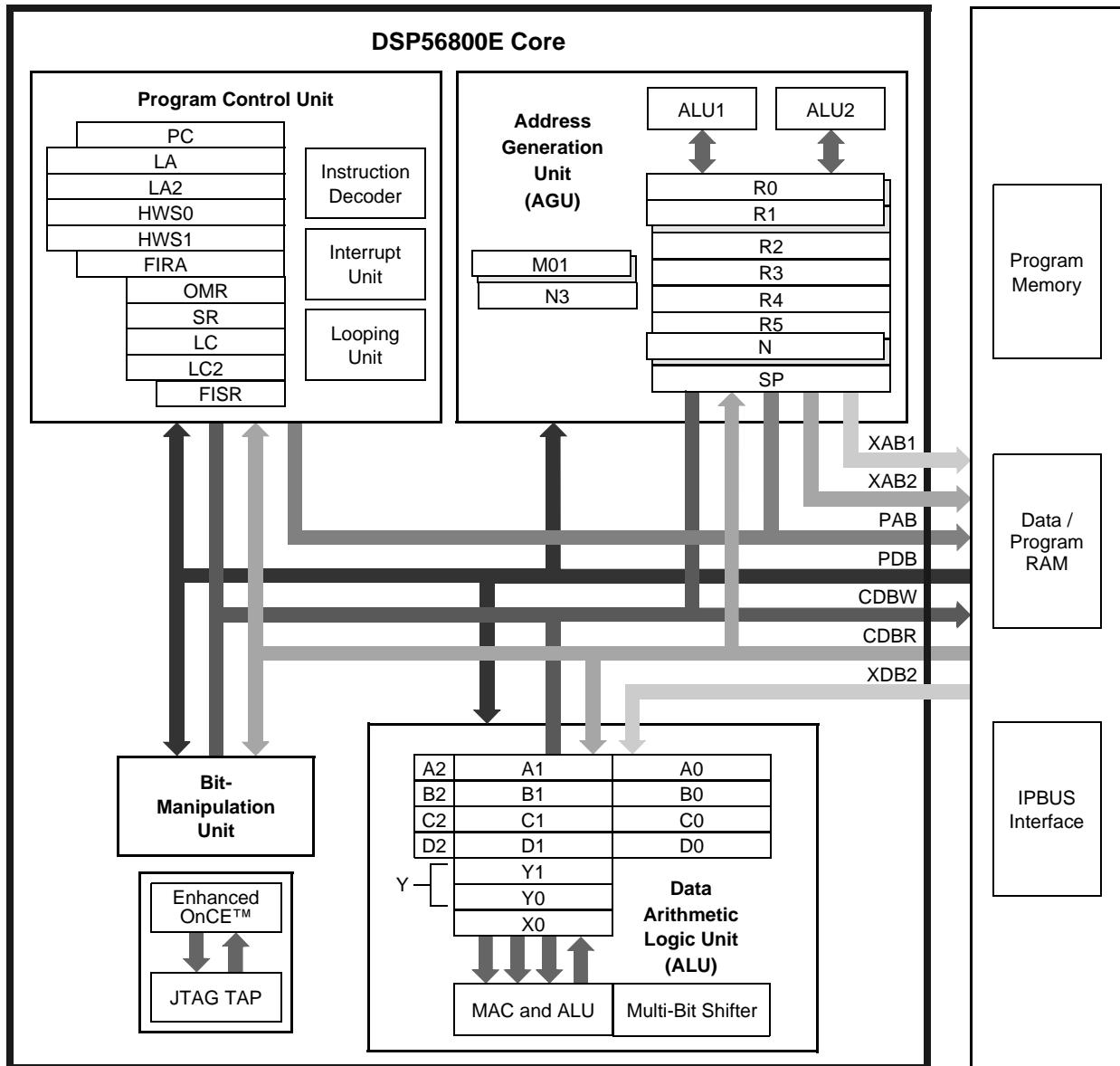

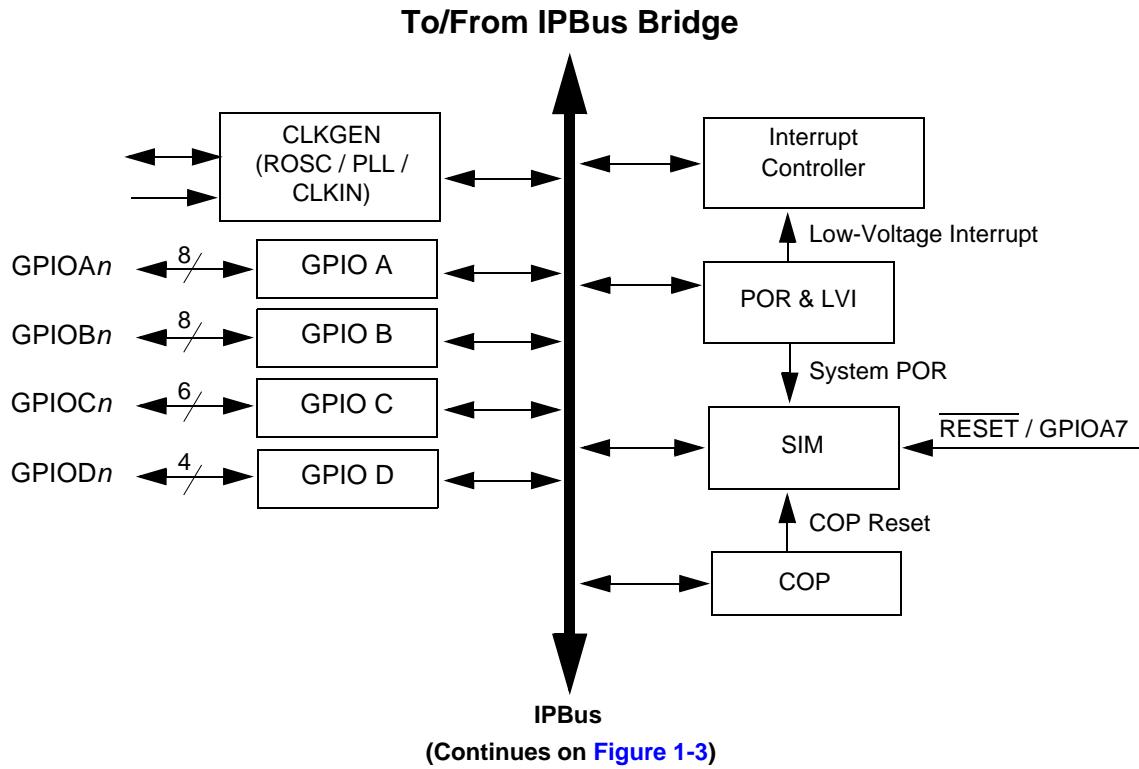

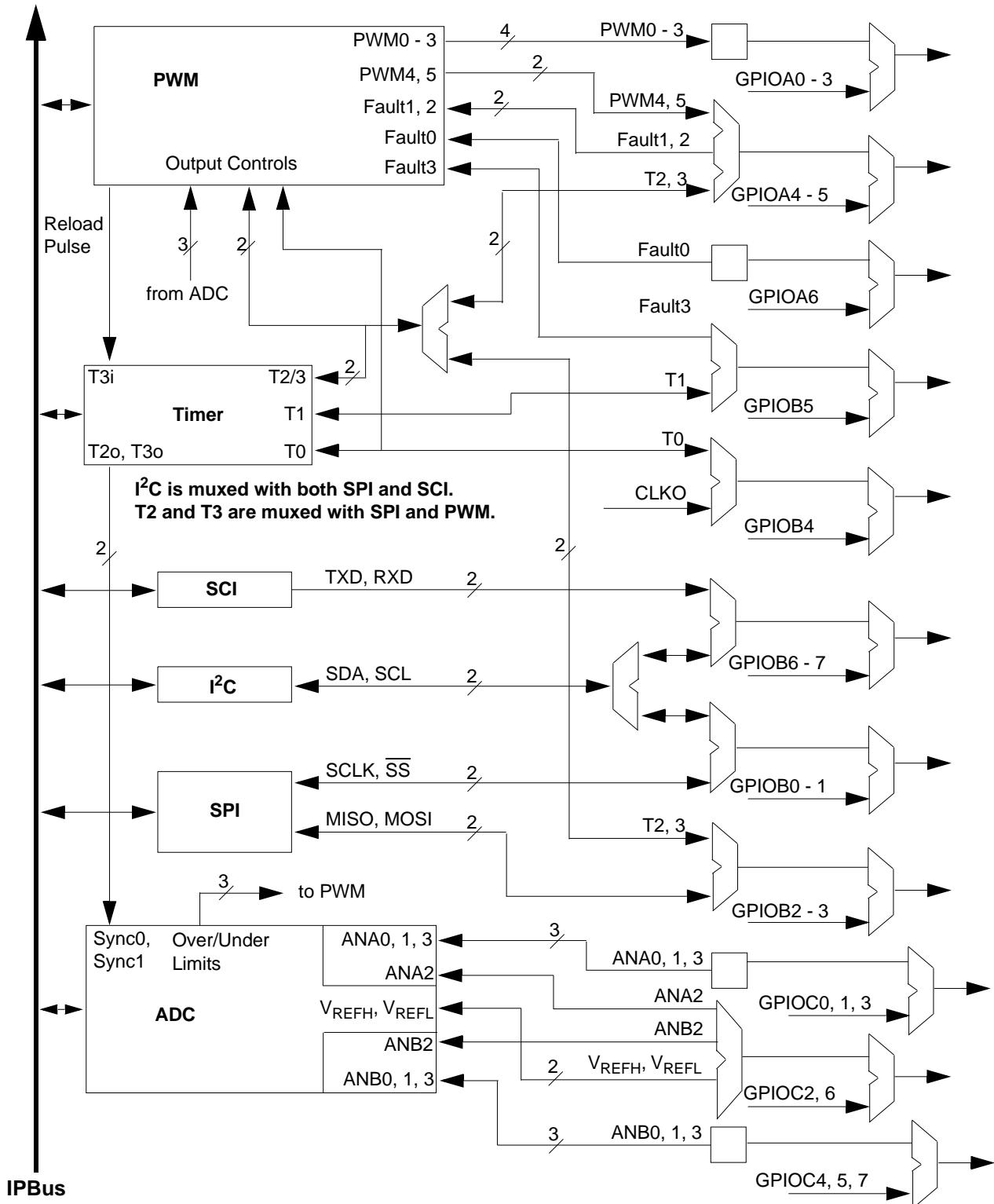

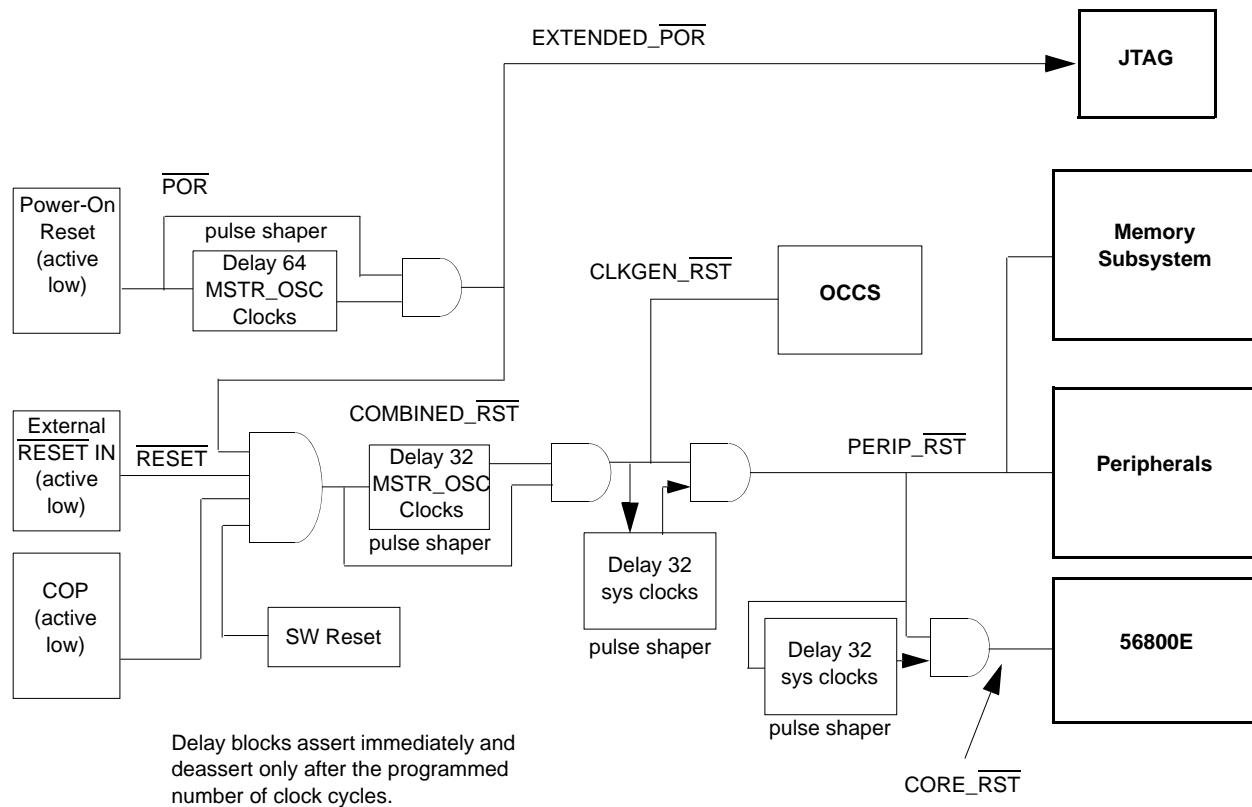

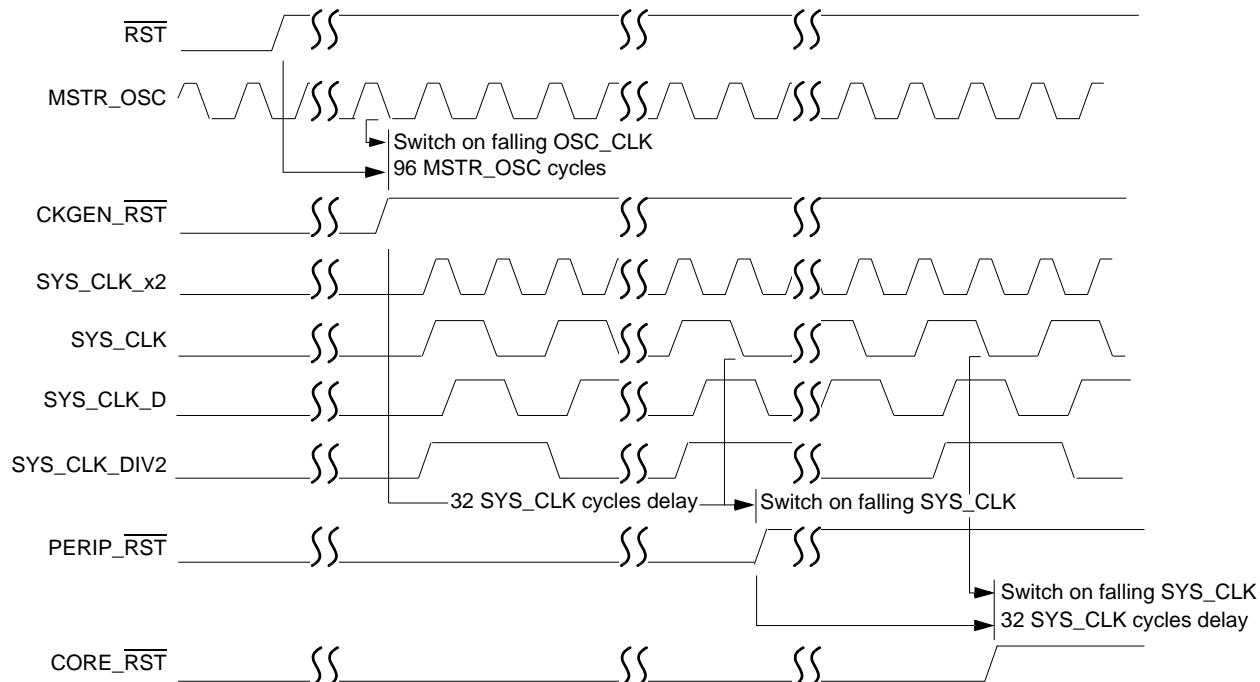

The 56F8014's architecture is shown in [Figure 1-1](#), [Figure 1-2](#), and [Figure 1-3](#). [Figure 1-1](#) illustrates how the 56800E system buses communicate with internal memories and the IPBus Bridge, as well as showing the internal connections between each unit of the 56800E core. [Figure 1-2](#) shows the peripherals and control blocks connected to the IPBus Bridge. [Figure 1-3](#) details how the device's I/O pins are muxed. The figures do not show the on-board regulator and power and ground signals. They also do not show the multiplexing between peripherals or the dedicated GPIOs. Please see [Part 2 Signal/Connection Descriptions](#) to see which signals are multiplexed with those of other peripherals.

## 1.5 Synchronize ADC with PWM

ADC conversion can be synchronized with the PWM module via Quad Timer channel 2 and 3 if needed. Internally, the PWM synch signal — which is generated at every PWM reload — can be connected to the timer channel 3 input, and the timer channel 2 and channel 3 outputs are connected to the ADC sync inputs. Timer channel 3 output is connected to SYNC0 and timer channel 2 is connected to SYNC1. The setting is controlled by the TC3\_INP bit in the SIM Control Register; see [Section 6.3.1](#).

SYNC0 is the master ADC sync input, used to trigger both ADCA and ADCB in sequence and parallel mode. SYNC1 is used to trigger ADCB in parallel independent mode, while SYNC0 is used to trigger ADCA. See *MC56F8000RM*, the 56F801X Peripheral Reference Manual, for additional information.

## 1.6 Multiple Frequency PWM Output

When both PWM channels of a complementary pair in software control mode and software control bits are set to 1, each complementary PWM signal pair — PWM 0 and 1; PWM 2 and 3; and PWM 4 and 5 — can select a PWM source from one of the following sources. This will enable each PWM pair and PWM2 to output PWM signals at different frequencies.

- External GPIO input:

- GPIOB2 input can be used to drive PWM 0 and 1

- GPIOB3 input can be used to drive PWM 2

- GPIOB4 input can be used to drive PWM 4 and 5

- Quad Timer output:

- Timer0 output can be used to drive PWM 0 and 1

- Timer2 output can be used to drive PWM 2

- Timer3 output can be used to drive PWM 4 and 5

- ADC conversion result:

- Signal of over/under limit of ADC sample 0 can be used to drive PWM 0 and 1

- Signal of over/under limit of ADC sample 1 can be used to drive PWM 2

- Signal of over/under limit of ADC sample 2 can be used to drive PWM 4 and 5

Figure 1-1 56800E Core Block Diagram

**Figure 1-2 Peripheral Subsystem**

(Continued from [Figure 1-2](#))

### To/From IPBus Bridge

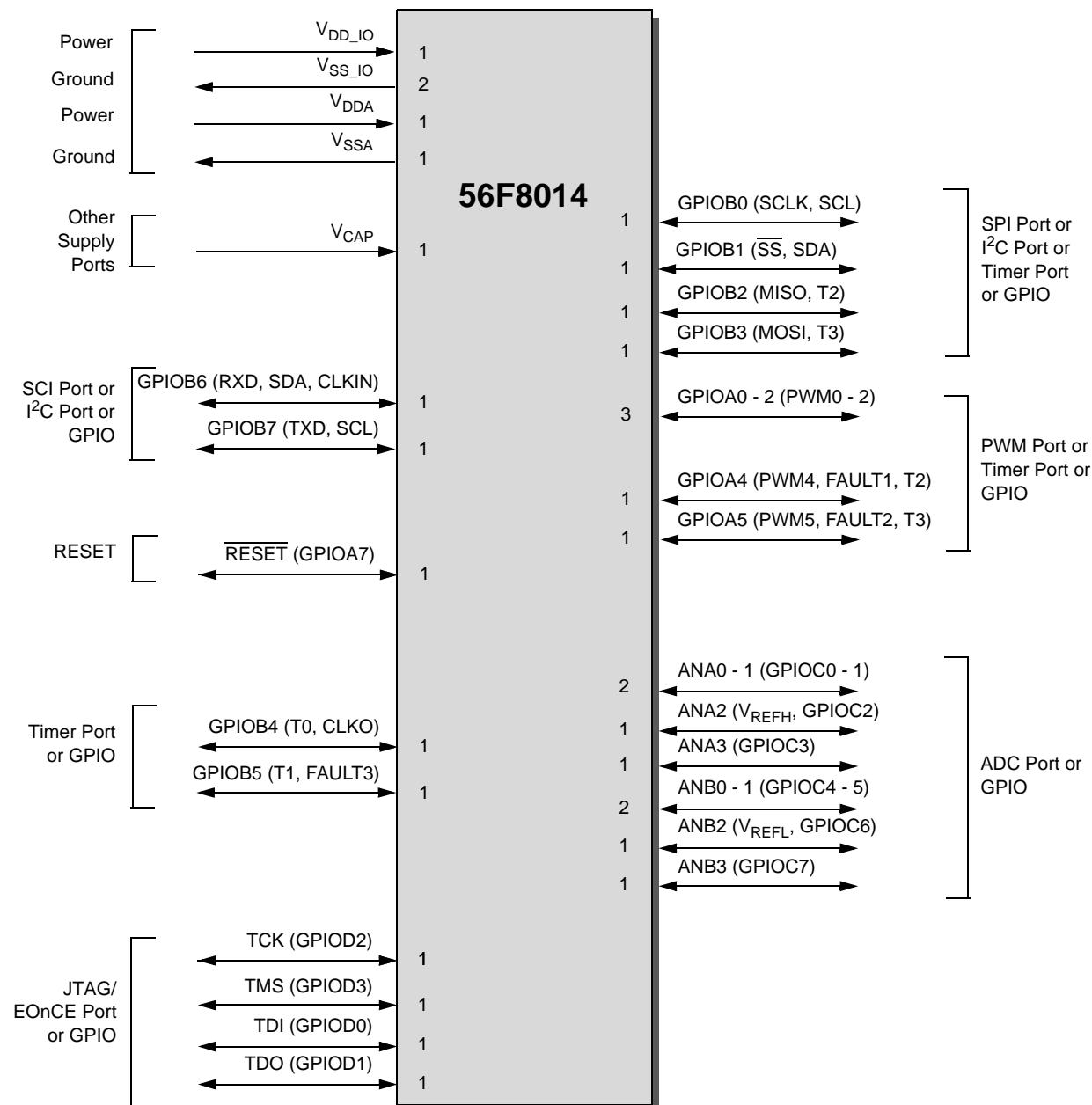

**Figure 1-3 56F8014 Peripheral I/O Pin-Out**

## 1.7 Product Documentation

The documents listed in **Table 1-1** are required for a complete description and proper design with the 56F8014. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, Freescale Literature Distribution Centers, or online at:

<http://www.freescale.com>

**Table 1-1 56F8014 Chip Documentation**

| Topic                                | Description                                                                                                                      | Order Number |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------|

| DSP56800E Reference Manual           | Detailed description of the 56800E family architecture, 16-bit Digital Signal Controller core processor, and the instruction set | DSP56800ERM  |

| 56F801X Peripheral Reference Manual  | Detailed description of peripherals of the 56F801X family of devices                                                             | MC56F8000RM  |

| 56F801x Serial Bootloader User Guide | Detailed description of the Serial Bootloader in the 56F801x family of devices                                                   | 56F801xBLUG  |

| 56F8014 Technical Data Sheet         | Electrical and timing specifications, pin descriptions, and package descriptions (this document)                                 | MC56F8014    |

| 56F8014 Errata                       | Details any chip issues that might be present                                                                                    | MC56F8014E   |

## 1.8 Data Sheet Conventions

This data sheet uses the following conventions:

**OVERBAR** This is used to indicate a signal that is active when pulled low. For example, the  $\overline{\text{RESET}}$  pin is active when low.

“asserted” A high true (active high) signal is high or a low true (active low) signal is low.

“deasserted” A high true (active high) signal is low or a low true (active low) signal is high.

| Examples: | Signal/Symbol           | Logic State | Signal State | Voltage <sup>1</sup> |

|-----------|-------------------------|-------------|--------------|----------------------|

|           | $\overline{\text{PIN}}$ | True        | Asserted     | $V_{IL}/V_{OL}$      |

|           | $\overline{\text{PIN}}$ | False       | Deasserted   | $V_{IH}/V_{OH}$      |

|           | $\text{PIN}$            | True        | Asserted     | $V_{IH}/V_{OH}$      |

|           | $\text{PIN}$            | False       | Deasserted   | $V_{IL}/V_{OL}$      |

1. Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

# Part 2 Signal/Connection Descriptions

## 2.1 Introduction

The input and output signals of the 56F8014 are organized into functional groups, as detailed in **Table 2-1**. **Table 2-2** summarizes all device pins. In **Table 2-2**, each table row describes the signal or signals present on a pin, sorted by pin number.

**Table 2-1 Functional Group Pin Allocations**

| Functional Group                                         | Number of Pins |

|----------------------------------------------------------|----------------|

| Power ( $V_{DD}$ or $V_{DDA}$ )                          | 2              |

| Ground ( $V_{SS}$ or $V_{SSA}$ )                         | 3              |

| Supply Capacitors                                        | 1              |

| Reset                                                    | 1              |

| Pulse Width Modulator (PWM) Ports <sup>1</sup>           | 5              |

| Serial Peripheral Interface (SPI) Ports <sup>2</sup>     | 4              |

| Analog-to-Digital Converter (ADC) Ports                  | 8              |

| Timer Module Ports <sup>3</sup>                          | 2              |

| Serial Communications Interface (SCI) Ports <sup>4</sup> | 2              |

| JTAG/Enhanced On-Chip Emulation (EOnCE)                  | 4              |

1. Pins in this section can function as TMR and GPIO.

2. Pins in this section can function as TMR, I<sup>2</sup>C, and GPIO.

3. Pins can function as PWM and GPIO.

4. Pins in this section can function as I<sup>2</sup>C and GPIO.

Table 2-2 56F8014 Pins

|            |                          |                                  | Peripherals: |     |     |      |                                 |     |              |                          |            |              |  |

|------------|--------------------------|----------------------------------|--------------|-----|-----|------|---------------------------------|-----|--------------|--------------------------|------------|--------------|--|

| LQFP Pin # | Pin Name                 | Signal Name                      | GPIO         | I2C | SCI | SPI  | ADC                             | PWM | Quad Timer   | Power & Ground           | JTAG       | Misc.        |  |

| 1          | <b>GPIOB1</b>            | GPIOB1, SS, SDA                  | <b>B1</b>    | SDA |     | SS   |                                 |     |              |                          |            |              |  |

| 2          | <b>GPIOB7</b>            | GPIOB7, TXD, SCL                 | <b>B7</b>    | SCL | TXD |      |                                 |     |              |                          |            |              |  |

| 3          | <b>GPIOB5</b>            | GPIOB5, T1, FAULT3               | <b>B5</b>    |     |     |      |                                 |     | FAULT3       | T1                       |            |              |  |

| 4          | <b>ANB0</b>              | ANB0, GPIOC4                     | C4           |     |     |      | <b>ANB0</b>                     |     |              |                          |            |              |  |

| 5          | <b>ANB1</b>              | ANB1, GPIOC5                     | C5           |     |     |      | <b>ANB1</b>                     |     |              |                          |            |              |  |

| 6          | <b>ANB2</b>              | ANB2, V <sub>REFL</sub> , GPIOC6 | C6           |     |     |      | <b>ANB2</b> , V <sub>REFL</sub> |     |              |                          |            |              |  |

| 7          | <b>ANB3</b>              | ANB3, GPIOC7                     | C7           |     |     |      | <b>ANB3</b>                     |     |              |                          |            |              |  |

| 8          | <b>VDDA</b>              | V <sub>DDA</sub>                 |              |     |     |      |                                 |     |              | <b>V<sub>DDA</sub></b>   |            |              |  |

| 9          | <b>VSSA</b>              | V <sub>SSA</sub>                 |              |     |     |      |                                 |     |              | <b>V<sub>SSA</sub></b>   |            |              |  |

| 10         | <b>ANA3</b>              | ANA3, GPIOC3                     | C3           |     |     |      | <b>ANA3</b>                     |     |              |                          |            |              |  |

| 11         | <b>ANA2</b>              | ANA2, V <sub>REFH</sub> , GPIOC2 | C2           |     |     |      | <b>ANA2</b> , V <sub>REFH</sub> |     |              |                          |            |              |  |

| 12         | <b>ANA1</b>              | ANA1, GPIOC1                     | C1           |     |     |      | <b>ANA1</b>                     |     |              |                          |            |              |  |

| 13         | <b>ANA0</b>              | ANA0, GPIOC0                     | C0           |     |     |      | <b>ANA0</b>                     |     |              |                          |            |              |  |

| 14         | <b>V<sub>SS_IO</sub></b> | V <sub>SS_IO</sub>               |              |     |     |      |                                 |     |              | <b>V<sub>SS_IO</sub></b> |            |              |  |

| 15         | <b>TCK</b>               | TCK, GPIOD2                      | D2           |     |     |      |                                 |     |              |                          | <b>TCK</b> |              |  |

| 16         | <b>RESET</b>             | RESET, GPIOA7                    | A7           |     |     |      |                                 |     |              |                          |            | <b>RESET</b> |  |

| 17         | <b>GPIOB3</b>            | GPIOB3, MOSI, T3                 | <b>B3</b>    |     |     | MOSI |                                 |     | T3           |                          |            |              |  |

| 18         | <b>GPIOB2</b>            | GPIOB2, MISO, T2                 | <b>B2</b>    |     |     | MISO |                                 |     | T2           |                          |            |              |  |

| 19         | <b>GPIOB4</b>            | GPIOB4, T0, CLK0                 | <b>B4</b>    |     |     |      |                                 |     | T0           |                          |            | CLK0         |  |

| 20         | <b>GPIOA5</b>            | GPIOA5, PWM5, FAULT2, T3         | <b>A5</b>    |     |     |      |                                 |     | PWM5, FAULT2 | T3                       |            |              |  |

| 21         | <b>GPIOB0</b>            | GPIOB0, SCLK, SCL                | <b>B0</b>    | SCL |     | SCLK |                                 |     |              |                          |            |              |  |

| 22         | <b>GPIOA4</b>            | GPIOA4, PWM4, FAULT1, T2         | <b>A4</b>    |     |     |      |                                 |     | PWM4, FAULT1 | T2                       |            |              |  |

| 23         | <b>GPIOA2</b>            | GPIOA2, PWM2                     | <b>A2</b>    |     |     |      |                                 |     | PWM2         |                          |            |              |  |

| 24         | <b>V<sub>CAP</sub></b>   | V <sub>CAP</sub>                 |              |     |     |      |                                 |     |              | <b>V<sub>CAP</sub></b>   |            |              |  |

**Table 2-2 56F8014 Pins (Continued)**

|            |               |                         | Peripherals: |     |     |     |     |      |            |                     |            |       |  |

|------------|---------------|-------------------------|--------------|-----|-----|-----|-----|------|------------|---------------------|------------|-------|--|

| LQFP Pin # | Pin Name      | Signal Name             | GPIO         | I2C | SCI | SPI | ADC | PWM  | Quad Timer | Power & Ground      | JTAG       | Misc. |  |

| 25         | <b>VDD_IO</b> | V <sub>DD</sub> _IO     |              |     |     |     |     |      |            | V <sub>DD</sub> _IO |            |       |  |

| 26         | <b>VSS_IO</b> | V <sub>SS</sub> _IO     |              |     |     |     |     |      |            | V <sub>SS</sub> _IO |            |       |  |

| 27         | <b>GPIOA1</b> | GPIOA1, PWM1            | <b>A1</b>    |     |     |     |     | PWM1 |            |                     |            |       |  |

| 28         | <b>GPIOA0</b> | GPIOA0, PWM0            | <b>A0</b>    |     |     |     |     | PWM0 |            |                     |            |       |  |

| 29         | <b>TDI</b>    | TDI, GPIOD0             | D0           |     |     |     |     |      |            |                     | <b>TDI</b> |       |  |

| 30         | <b>TMS</b>    | TMS, GPIOD3             | D3           |     |     |     |     |      |            |                     | <b>TMS</b> |       |  |

| 31         | <b>TDO</b>    | TDO, GPIOD1             | D1           |     |     |     |     |      |            |                     | <b>TDO</b> |       |  |

| 32         | <b>GPIOB6</b> | GPIOB6, RXD, SDA, CLKIN | <b>B6</b>    | SDA | RXD |     |     |      |            |                     |            | CLKIN |  |

Figure 2-1 56F8014 Signals Identified by Functional Group (32-Pin LQFP)

## 2.2 56F8014 Signal Pins

After reset, each pin is configured for its primary function (listed first). Any alternate functionality must be programmed.

**Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP**

| Signal Name                                                                             | LQFP Pin No. | Type                                                               | State During Reset                           | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD\_IO}$                                                                            | 25           | Supply                                                             | Supply                                       | <b>I/O Power</b> — This pin supplies 3.3V power to the chip I/O interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $V_{SS\_IO}$                                                                            | 14           | Supply                                                             | Supply                                       | $V_{SS}$ — These pins provide ground for chip logic and I/O drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $V_{SS\_IO}$                                                                            | 26           |                                                                    |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $V_{DDA}$                                                                               | 8            | Supply                                                             | Supply                                       | <b>ADC Power</b> — This pin supplies 3.3V power to the ADC modules. It must be connected to a clean analog power supply.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $V_{SSA}$                                                                               | 9            | Supply                                                             | Supply                                       | <b>ADC Analog Ground</b> — This pin supplies an analog ground to the ADC modules.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{CAP}$                                                                               | 24           | Supply                                                             | Supply                                       | $V_{CAP}$ — Connect a 2.2 $\mu$ F or greater bypass capacitor between this pin and $V_{SS\_IO}$ , which is required by the internal voltage regulator for proper chip operation. See <a href="#">Section 10.2.1</a> .                                                                                                                                                                                                                                                                                                                              |

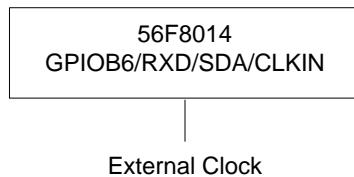

| <b>GPIOB6</b><br><br><b>(RXD)</b><br><br><b>(SDA<sup>1</sup>)</b><br><br><b>(CLKIN)</b> | 32           | Input/<br>Output<br><br>Input<br><br>Input/<br>Output<br><br>Input | Input with<br>internal<br>pull-up<br>enabled | <p><b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.</p> <p><b>Receive Data</b> — SCI receive data input.</p> <p><b>Serial Data</b> — This pin serves as the I<sup>2</sup>C serial data line.</p> <p><b>Clock Input</b> — This pin serves as an optional external clock input.</p> <p>After reset, the default state is GPIOB6. The alternative peripheral functionality is controlled via the SIM (See <a href="#">Section 6.3.8</a>) and the CLKMODE bit of the OCCS Oscillator Control Register.</p> |

| 1. This signal is also brought out on the GPIOB1 pin.                                   |              |                                                                    |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Return to [Table 2-2](#)

**Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)**

| Signal Name                                           | LQFP Pin No. | Type                    | State During Reset                  | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------|--------------|-------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOB7<br><br>(TXD)<br><br>(SCL <sup>2</sup> )        | 2            | Input/Output            | Input with internal pull-up enabled | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                                                                                             |

|                                                       |              | Input/Output            |                                     | <b>Transmit Data</b> — SCI transmit data output or transmit / receive in single wire operation.                                                                                                                                                                                                                                                                                                                                          |

|                                                       |              | Input/Output            |                                     | <b>Serial Clock</b> — This pin serves as the I <sup>2</sup> C serial clock.<br><br>After reset, the default state is GPIOB7. The alternative peripheral functionality is controlled via the SIM. See <a href="#">Section 6.3.8</a> .                                                                                                                                                                                                     |

| 2. This signal is also brought out on the GPIOB0 pin. |              |                         |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RESET<br><br>(GPIOA7)                                 | 16           | Input                   | Input with internal pull-up enabled | <b>Reset</b> — This input is a direct hardware reset on the processor. When RESET is asserted low, the chip is initialized and placed in the reset state. A Schmitt trigger input is used for noise immunity. The internal reset signal will be deasserted synchronous with the internal clocks after a fixed number of internal clocks.                                                                                                 |

|                                                       |              | Input/Open Drain Output |                                     | <b>Port A GPIO</b> — This GPIO pin can be individually programmed as an input or open drain output pin. Note that RESET functionality is disabled in this mode and the chip can only be reset via POR, COP reset, or software reset.<br><br>After reset, the default state is RESET.                                                                                                                                                     |

| GPIOB4<br><br>(T0)<br><br>(CLKO)                      | 19           | Input/Output            | Input with internal pull-up enabled | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                                                                                             |

|                                                       |              | Input/Output            |                                     | <b>T0</b> — Timer, Channel 0                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                       |              | Output                  |                                     | <b>Clock Output</b> — This is a buffered clock signal. Using the SIM_CLKO Select Register (SIM_CLKOSR), this pin can be programmed as any of the following: disabled (logic 0), CLK_MSTR (system clock), IPBus clock, or oscillator output. See <a href="#">Section 6.3.7</a> .<br><br>After reset, the default state is GPIOB4. The alternative peripheral functionality is controlled via the SIM. See <a href="#">Section 6.3.8</a> . |

Return to [Table 2-2](#)

**Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)**

| Signal Name                                             | LQFP Pin No. | Type         | State During Reset                  | Signal Description                                                                                                                                                                                                                                     |

|---------------------------------------------------------|--------------|--------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>GPIOB5</b><br><br><b>(T1)</b><br><br><b>(FAULT3)</b> | 3            | Input/Output | Input with internal pull-up enabled | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                           |

|                                                         |              | Input/Output |                                     | <b>T1</b> — Timer, Channel 1                                                                                                                                                                                                                           |

|                                                         |              | Input        |                                     | <b>FAULT3</b> — This fault input pin is used for disabling selected PWM outputs in cases where fault conditions originate off-chip.                                                                                                                    |

| <b>TCK</b><br><br><b>(GPIOD2)</b>                       | 15           | Input        | Input with internal pull-up enabled | <b>Test Clock Input</b> — This input pin provides a gated clock to synchronize the test logic and shift serial data to the JTAG/EOnCE port. The pin is connected internally to a pull-up resistor. A Schmitt trigger input is used for noise immunity. |

|                                                         |              | Input/Output |                                     | <b>Port D GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                           |

| <b>TMS</b><br><br><b>(GPIOD3)</b>                       | 30           | Input        | Input with internal pull-up enabled | <b>Test Mode Select Input</b> — This input pin is used to sequence the JTAG TAP controller's state machine. It is sampled on the rising edge of TCK and has an on-chip pull-up resistor.                                                               |

|                                                         |              | Input/Output |                                     | <b>Port D GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                           |

|                                                         |              |              |                                     | After reset, the default state is TMS.                                                                                                                                                                                                                 |

| <b>TDI</b><br><br><b>(GPIOD0)</b>                       | 29           | Input        | Input with internal pull-up enabled | <b>Test Data Input</b> — This input pin provides a serial input data stream to the JTAG/EOnCE port. It is sampled on the rising edge of TCK and has an on-chip pull-up resistor.                                                                       |

|                                                         |              | Input/Output |                                     | <b>Port D GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                           |

|                                                         |              |              |                                     | After reset, the default state is TDI.                                                                                                                                                                                                                 |

[Return to Table 2-2](#)

**Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)**

| Signal Name                                                  | LQFP Pin No. | Type                                                     | State During Reset                  | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------|--------------|----------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDO<br>(GPIOD1)                                              | 31           | Output<br>Input/<br>Output                               | Output                              | <p><b>Test Data Output</b> — This tri-stateable output pin provides a serial output data stream from the JTAG/EOnCE port. It is driven in the shift-IR and shift-DR controller states, and changes on the falling edge of TCK.</p> <p><b>Port D GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.</p> <p>After reset, the default state is TDO.</p>                                                                                                                                                                                  |

| GPIOB0<br>(SCLK)<br>(SCL <sup>3</sup> )                      | 21           | Input/<br>Output<br>Input/<br>Output<br>Input/<br>Output | Input with internal pull-up enabled | <p><b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.</p> <p><b>SPI Serial Clock</b> — In the master mode, this pin serves as an output, clocking slaved listeners. In slave mode, this pin serves as the data clock input. A Schmitt trigger input is used for noise immunity.</p> <p><b>Serial Data</b> — This pin serves as the I<sup>2</sup>C serial clock.</p> <p>After reset, the default state is GPIOB0. The alternative peripheral functionality is controlled via the SIM. See <a href="#">Section 6.3.8</a>.</p> |

| <b>3. This signal is also brought out on the GPIOB7 pin.</b> |              |                                                          |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GPIOB1<br>(SS)<br>(SDA <sup>4</sup> )                        | 1            | Input/<br>Output<br>Input<br>Input/<br>Output            | Input with internal pull-up enabled | <p><b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.</p> <p><b>SPI Slave Select</b> — SS is used in slave mode to indicate to the SPI module that the current transfer is to be received.</p> <p><b>Serial Clock</b> — This pin serves as the I<sup>2</sup>C serial data line.</p> <p>After reset, the default state is GPIOB1. The alternative peripheral functionality is controlled via the SIM. See <a href="#">Section 6.3.8</a>.</p>                                                                                 |

| <b>4. This signal is also brought out on the GPIOB6 pin.</b> |              |                                                          |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Return to [Table 2-2](#)

**Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)**

| Signal Name                                                  | LQFP Pin No. | Type                                                             | State During Reset                           | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------|--------------|------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOB2<br><br>(MISO)<br><br>(T2 <sup>5</sup> )               | 18           | Input/<br>Output<br><br>Input/<br>Output<br><br>Input/<br>Output | Input with<br>internal<br>pull-up<br>enabled | <p><b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.</p> <p><b>SPI Master In/Slave Out</b> — This serial data pin is an input to a master device and an output from a slave device. The MISO line of a slave device is placed in the high-impedance state if the slave device is not selected. The slave device places data on the MISO line a half-cycle before the clock edge the master device uses to latch the data.</p> <p><b>T2</b> — Timer, Channel 2</p> <p>After reset, the default state is GPIOB2. The alternative peripheral functionality is controlled via the SIM. See <a href="#">Section 6.3.8</a>.</p> |

| <b>5. This signal is also brought out on the GPIOA4 pin.</b> |              |                                                                  |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GPIOB3<br><br>(MOSI)<br><br>(T3 <sup>6</sup> )               | 17           | Input/<br>Output<br><br>Input/<br>Output<br><br>Input/<br>Output | Input with<br>internal<br>pull-up<br>enabled | <p><b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.</p> <p><b>SPI Master Out/Slave In</b> — This serial data pin is an output from a master device and an input to a slave device. The master device places data on the MOSI line a half-cycle before the clock edge the slave device uses to latch the data.</p> <p><b>T3</b> — Timer, Channel 3</p> <p>After reset, the default state is GPIOB3. The alternative peripheral functionality is controlled via the SIM. See <a href="#">Section 6.3.8</a>.</p>                                                                                                            |

| <b>6. This signal is also brought out on the GPIOA5 pin.</b> |              |                                                                  |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GPIOA0<br><br>(PWM0)                                         | 28           | Input/<br>Output<br><br>Output                                   | Input with<br>internal<br>pull-up<br>enabled | <p><b>Port A GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.</p> <p><b>PWM0</b> — This is one of the six PWM output pins.</p> <p>After reset, the default state is GPIOA0.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Return to [Table 2-2](#)

**Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)**