ETR0206 006

## Voltage Detector with External Delay Type Capacitor

#### **GENERAL DESCRIPTION**

The XC6109 series is highly precise, low power consumption voltage detector, manufactured using CMOS and laser trimming technologies.

With the built-in delay circuit, connecting the delay capacitance pin to the capacitor enables the IC to provide an arbitrary release delay time.

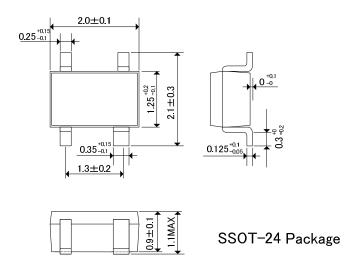

Using a small package (SSOT-24), the series is suited for high density mounting.

Both CMOS and N-channel open drain output configurations are available.

#### **APPLICATIONS**

Microprocessor reset circuitry

Charge voltage monitors

Memory battery back-up switch circuits

Power failure detection circuits

#### **FEATURES**

Highly Accurate : <u>+</u>2%

(Setting Voltage Accuracy≥1.5V)

: <u>+</u>30mV

(Setting Voltage Accuracy<1.5V)

$\textbf{Low Power Consumption} \hspace{0.3cm} : 0.8~\mu\,\text{A (detect, VDF=1.0V, VIN= 0.9V, TYP.)}$

0.9 μ A (release, VDF=1.0V, VIN= 1.1V, TYP.)

**Detect Voltage Range** : 0.8V ~ 5.0V (0.1V increments)

Operating Voltage Range : 0.7V ~ 6.0V Detect Voltage Temperature Characteristics

: ±100ppm/ °C (TYP.)

Output Configuration : CMOS or

N-channel open drain

Operating Temperature Range : -40 °C ~ +85 °C

**CMOS**

Built-In Delay Circuit, Delay Pin Available

Package : SSOT-24

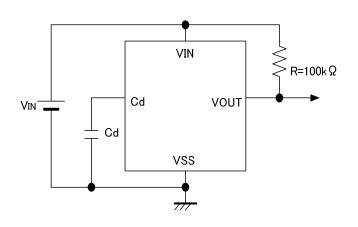

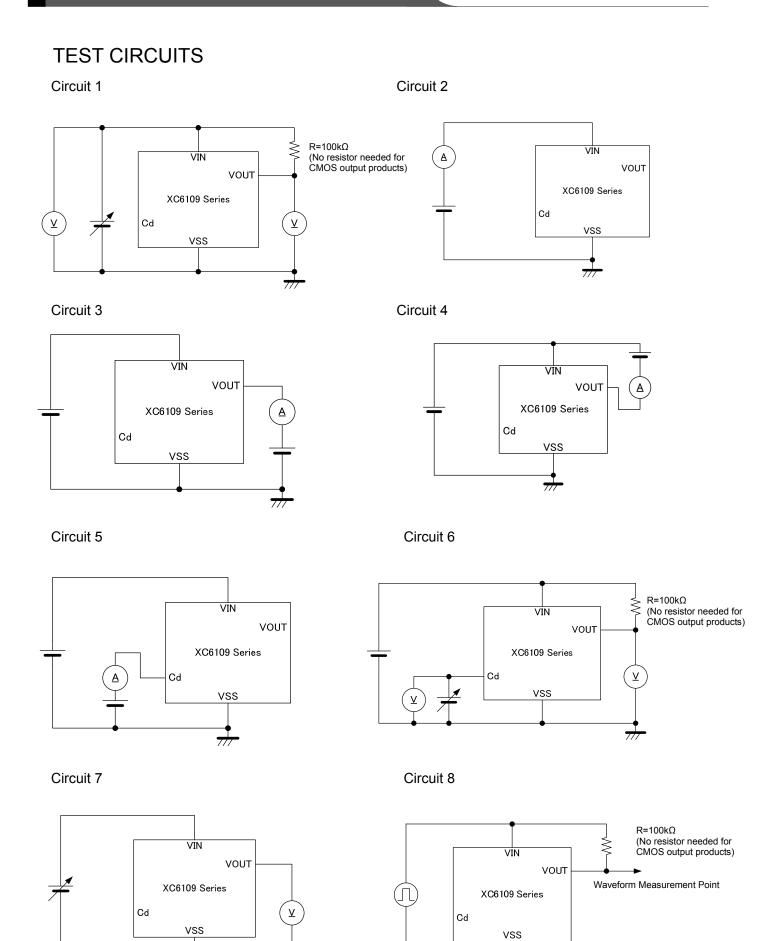

### TYPICAL APPLICATION CIRCUIT

(No pull-up resistor needed for CMOS output products)

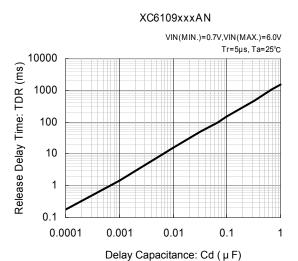

# TYPICAL PERFORMANCE CHARACTERISTICS

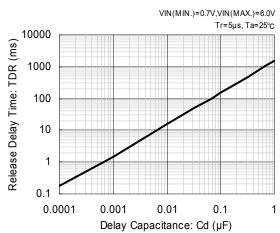

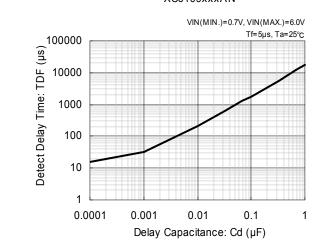

Release Delay Time vs. Delay Capacitance

## PIN CONFIGURATION

SSOT-24 (TOP VIEW)

## **PIN ASSIGNMENT**

| PIN NUMBER | PIN NAME | FUNCTION            |

|------------|----------|---------------------|

| 1          | Vin      | Input               |

| 2          | Vss      | Ground              |

| 3          | Cd       | Delay Capacitance   |

| 4          | Vout     | Output (Detect "L") |

## PRODUCT CLASSIFICATION

Ordering Information

XC6109

| DESIGNATOR | DESCRIPTION                             | SYMBOL  | DESCRIPTION                               |

|------------|-----------------------------------------|---------|-------------------------------------------|

|            | Output Configuration                    | С       | CMOS output                               |

|            | Output Configuration                    | N       | N-ch open drain output                    |

|            | Detect Voltage                          | 08 ~ 50 | e.g. 18 1.8V                              |

|            | Output Delay & Hysteresis               | А       | Built-in delay pin & hysteresis 5% (TYP.) |

|            | Packages                                | NR      | SSOT-24                                   |

| -          | Packages<br>Taping Type <sup>(*2)</sup> | NR-G    | SSOT-24 (Halogen & Antimony free)         |

<sup>(\*1)</sup> The "-G" suffix indicates that the products are Halogen and Antimony free as well as being fully RoHS compliant.

(\*2) The device orientation is fixed in its embossed tape pocket. For reverse orientation, please contact your local Torex sales office or representative. (Standard orientation: R- , Reverse orientation: L- )

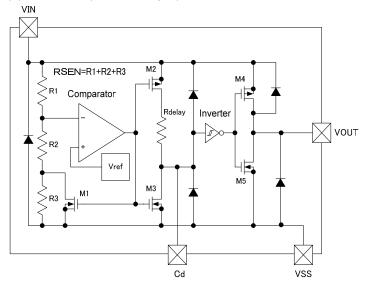

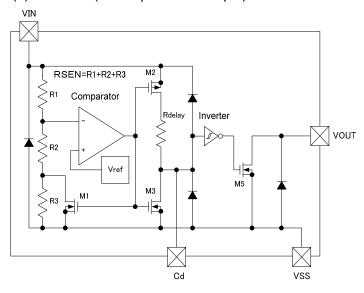

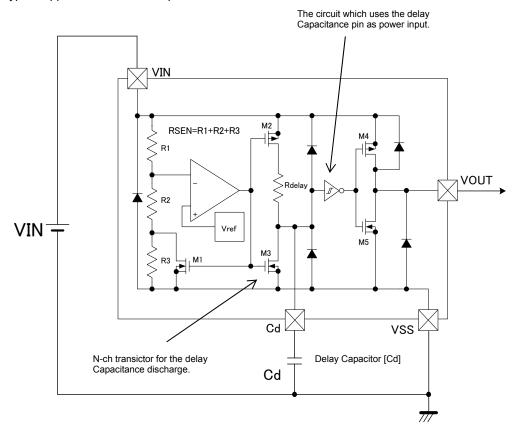

## **BLOCK DIAGRAMS**

## (1) XC6109C (CMOS Output)

#### (2) XC6109N (N-ch Open Drain Output)

## **ABSOLUTE MAXIMUM RATINGS**

Ta = 25°C

| PARAI                       | METER               | SYMBOL | RATINGS               | UNITS |  |

|-----------------------------|---------------------|--------|-----------------------|-------|--|

| Input Voltage               |                     | VIN    | Vss - 0.3 ~ 7.0       | V     |  |

| Output Current              |                     | Іоит   | 10                    | mA    |  |

| Output Voltage              | XC6109C (*1)        | Vout   | Vss - 0.3 ~ Vin + 0.3 | V     |  |

|                             | XC6109N (*2)        | VOUI   | Vss - 0.3 ~ 7.0       | V     |  |

| Delay Pin Voltage           |                     | Vcd    | Vss-0.3 ~ Vin + 0.3   | V     |  |

| Delay Pin Current           |                     | ICD    | 5.0                   | mA    |  |

| Power Dissipation           | Dissipation SSOT-24 |        | 150                   | mW    |  |

| Operating Temperature Range |                     | Та     | - 40 ~ + 85           | оС    |  |

| Storage Temp                | erature Range       | Tstg   | - 40 ~ + 125          | °С    |  |

NOTE:

\*1: CMOS output

\*2: N-ch open drain output

## **ELECTRICAL CHARACTERISTICS**

Ta = 25°C

| PAR       | RAMETER                      | SYMBOL                                          | COND                                                                                              | ITIONS          | MIN.          | TYP.          | MAX.          | UNIT      | CIRCUIT |

|-----------|------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------|---------------|---------------|---------------|-----------|---------|

| Opera     | ting Voltage                 | Vin                                             | VDF(T)=0.8~5.0V (*1)                                                                              |                 | 0.7           | -             | 6.0           | V         | -       |

| <u> </u>  | ect Voltage                  | VDF                                             | VDF(T)=0.8~5.0V                                                                                   |                 |               | E-1           |               | V         |         |

| Hyste     | resis Width                  | VHYS                                            | VIN=1.0~6.0V                                                                                      |                 | VDF<br>x 0.02 | VDF<br>x 0.05 | VDF<br>x 0.08 | V         |         |

|           |                              |                                                 |                                                                                                   | VDF(T)=0.8~1.9V | -             | 0.80          | 1.70          |           |         |

| Suppl     | ly Current 1                 | Iss1                                            | VIN=VDF x 0.9                                                                                     | VDF(T)=2.0~3.9V | -             | 0.90          | 1.90          | μA        |         |

|           | •                            |                                                 |                                                                                                   | VDF(T)=4.0~5.0V | -             | 1.00          | 2.00          |           |         |

|           |                              |                                                 |                                                                                                   | VDF(T)=0.8~1.9V | -             | 0.90          | 1.80          |           |         |

| Suppl     | ly Current 2                 | lss2                                            | VIN=VDF x 1.1                                                                                     | VDF(T)=2.0~3.9V | -             | 1.10          | 2.00          | 2.00 μ A  |         |

|           |                              |                                                 |                                                                                                   | VDF(T)=4.0~5.0V | -             | 1.20          | 2.20          |           |         |

|           |                              |                                                 | V <sub>DS</sub> =0.                                                                               | 5V(Nch)         | 0.01          | 0.36          | 2.20          |           |         |

|           |                              |                                                 |                                                                                                   |                 | 0.1           | 0.7           |               |           |         |

|           |                              | lout1                                           | V <sub>DS</sub> =0.5V(Nch)<br>V <sub>IN</sub> =2.0V <sup>(*3)</sup><br>V <sub>DS</sub> =0.5V(Nch) |                 | 0.8           | 1.6           | - mA          |           |         |

| Outp      | out Current                  | -                                               | $V_{IN}=0.5V(NCH)$ $V_{IN}=3.0V^{(*4)}$                                                           |                 | 0.0           | 1.0           |               |           |         |

|           |                              |                                                 | $V_{\rm IN}=3.6V$<br>$V_{\rm DS}=0.5V({\rm Nch})$                                                 |                 | 1.2           | 2.0           |               |           |         |

|           |                              |                                                 | V <sub>IN</sub> =4.0V (*5)                                                                        |                 |               | 2.0           |               |           |         |

|           |                              |                                                 | V <sub>DS</sub> =0.5V(Nch)                                                                        |                 | 1.6           | 2.3           |               |           |         |

|           |                              | IOUT2 <sup>(*6)</sup>                           | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                                            |                 |               |               | ^             |           |         |

|           |                              | 10012                                           | Vps=0.5V (P-ch)                                                                                   |                 | E-2           |               |               | mA        |         |

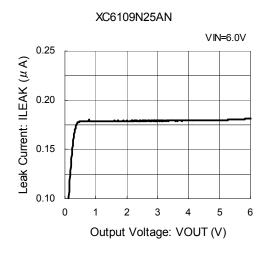

| Leak      | CMOS<br>output               |                                                 | V -C 0V V                                                                                         | -C 0)/ Od: Once | -             | 0.20          | -             | ^         |         |

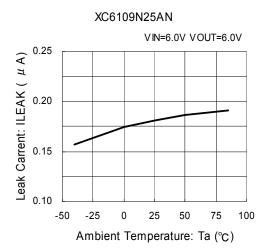

| Current   | N-ch Open<br>Drain<br>Output | I <sub>LEAK</sub>                               | V <sub>IN</sub> =6.0V, V <sub>OUT</sub>                                                           | =6.0V, Cd: Open | -             | 0.20          | 0.40          | μA        |         |

| Char      | nperature<br>racteristics    | $\triangle V$ DF/<br>( $\triangle T$ opr · VDF) | -40 °C <u>≤</u> Ta <u>≤</u> 85 °C                                                                 |                 | -             | ± 100         | -             | ppm/°C    |         |

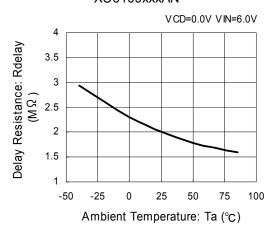

| Delay R   | Resistance <sup>(*7)</sup>   | Rdelay                                          | VIN=6.0V, Cd=0V                                                                                   |                 | 1.6           | 2.0           | 2.4           | $M\Omega$ |         |

| Delay Pir | n Sink Current               | ICD                                             | Cd=0.5V, VIN=0.7V                                                                                 |                 | 8             | 60            | ı             | μA        |         |

|           | apacitance Pin               | VTCD                                            | VIN=1.0V<br>VIN=6.0V                                                                              |                 | 0.4           | 0.5           | 0.6           | V         |         |

|           | hold Voltage                 | VICD                                            |                                                                                                   |                 | 2.9           | 3.0           | 3.1           | V         |         |

|           | fied Operating oltage (*8)   | Vuns                                            | VIN=0~0.7V                                                                                        |                 | -             | 0.3           | 0.4           | V         |         |

| Detect D  | Delay Time (*9)              | tDF0                                            | VIN=6.0 down to 0.7V<br>Cd: Open                                                                  |                 | -             | 30            | 230           | μs        |         |

| Release   | e Delay Time                 | tDR0                                            | Vin=0.7~6.0V<br>Cd: Open                                                                          |                 | -             | 30            | 200           | μs        |         |

#### NOTE:

- \*1: VDF(T): Setting Detect Voltage

- \*2: VDF(T) > 1.0V

- \*3: VDF(T) > 2.0V

- \*4: VDF(T) > 3.0V

- \*5: VDF(T) > 4.0V

- \*6: This numerical value is applied only to the XC6109C series (CMOS output).

- \*7: Calculated from the voltage value and the current value of both ends of the resistor.

- \*8: The maximum voltage of the VOUT in the range of the VIN 0 to 0.7V. This numerical value is applied only to the XC6109C series (CMOS output).

- \*9: Time which ranges from the state of VIN =VDF to the VOUT reaching 0.6V when the VIN falls without connecting to the Cd pin.

- \*10: Time which ranges from the state of VIN= VDF +VHYS to the VOUT reaching 5.4V when the VIN rises without connecting to the Cd pin.

## **VOLTAGE CHART**

| SYMBOL              |                     | E-1   |        | E                   | -2    |  |

|---------------------|---------------------|-------|--------|---------------------|-------|--|

| PARAMETER           |                     |       |        |                     |       |  |

| 17 II V IIVIL I LIV | DETECT VOLTAGE (*1) |       | (*2)   |                     |       |  |

|                     | DETE                |       | GE ''' | OUTPUT CURRENT (*2) |       |  |

| SETTING DETECT      |                     | (V)   |        | (m                  | nA)   |  |

| VOLTAGE             |                     |       |        |                     |       |  |

| ) (T)               |                     | VDF   |        | lou                 | JT2   |  |

| VDF(T)              | MIN.                | TYP.  | MAX.   | MIN.                | TYP.  |  |

| 0.8                 | 0.770               | 0.800 | 0.830  |                     |       |  |

| 0.9                 | 0.870               | 0.900 | 0.930  | -0.40               | -0.20 |  |

| 1.0                 | 0.970               | 1.000 | 1.030  |                     |       |  |

| 1.1                 | 1.070               | 1.100 | 1.130  |                     |       |  |

| 1.2                 | 1.170               | 1.200 | 1.230  | -0.60               | -0.30 |  |

| 1.3                 | 1.270               | 1.300 | 1.330  | -0.00               | -0.30 |  |

| 1.4                 | 1.370               | 1.400 | 1.430  |                     |       |  |

| 1.5                 | 1.470               | 1.500 | 1.530  |                     |       |  |

| 1.6                 | 1.568               | 1.600 | 1.632  |                     |       |  |

| 1.7                 | 1.666               | 1.700 | 1.734  | -0.80               | -0.40 |  |

| 1.8                 | 1.764               | 1.800 | 1.836  |                     |       |  |

| 1.9                 | 1.862               | 1.900 | 1.938  |                     |       |  |

| 2.0                 | 1.960               | 2.000 | 2.040  |                     |       |  |

| 2.1                 | 2.058               | 2.100 | 2.142  |                     |       |  |

| 2.2                 | 2.156               | 2.200 | 2.244  |                     |       |  |

| 2.3                 | 2.254               | 2.300 | 2.346  |                     | -0.50 |  |

| 2.4                 | 2.352               | 2.400 | 2.448  | 4.00                |       |  |

| 2.5                 | 2.450               | 2.500 | 2.550  | -1.00               |       |  |

| 2.6                 | 2.548               | 2.600 | 2.652  |                     |       |  |

| 2.7                 | 2.646               | 2.700 | 2.754  |                     |       |  |

| 2.8                 | 2.744               | 2.800 | 2.856  |                     |       |  |

| 2.9                 | 2.842               | 2.900 | 2.958  |                     |       |  |

| 3.0                 | 2.940               | 3.000 | 3.060  |                     |       |  |

| 3.1                 | 3.038               | 3.100 | 3.162  |                     |       |  |

| 3.2                 | 3.136               | 3.200 | 3.264  |                     |       |  |

| 3.3                 | 3.234               | 3.300 | 3.366  |                     |       |  |

| 3.4                 | 3.332               | 3.400 | 3.468  | 1 20                | 0.60  |  |

| 3.5                 | 3.430               | 3.500 | 3.570  | -1.20               | -0.60 |  |

| 3.6                 | 3.528               | 3.600 | 3.672  |                     |       |  |

| 3.7                 | 3.626               | 3.700 | 3.774  |                     |       |  |

| 3.8                 | 3.724               | 3.800 | 3.876  |                     |       |  |

| 3.9                 | 3.822               | 3.900 | 3.978  |                     |       |  |

| 4.0                 | 3.920               | 4.000 | 4.080  |                     |       |  |

| 4.1                 | 4.018               | 4.100 | 4.182  |                     |       |  |

| 4.2                 | 4.116               | 4.200 | 4.284  |                     |       |  |

| 4.3                 | 4.214               | 4.300 | 4.386  |                     |       |  |

| 4.4                 | 4.321               | 4.400 | 4.488  |                     |       |  |

| 4.5                 | 4.410               | 4.500 | 4.590  | -1.30               | -0.65 |  |

| 4.6                 | 4.508               | 4.600 | 4.692  |                     |       |  |

| 4.7                 | 4.606               | 4.700 | 4.794  |                     |       |  |

| 4.8                 | 4.704               | 4.800 | 4.896  |                     |       |  |

| 4.9                 | 4.802               | 4.900 | 4.998  |                     |       |  |

| 5.0                 | 4.900               | 5.000 | 5.100  |                     |       |  |

#### NOTE:

<sup>\*1:</sup> When VDF(T) 1.4V, the detection accuracy is  $\pm$  30mV. When VDF(T) 1.5V, the detection accuracy is  $\pm$  2%.

<sup>\*2:</sup> This numerical value is applied only to the XC6109C series (CMOS output).

#### OPERATIONAL EXPLANATION

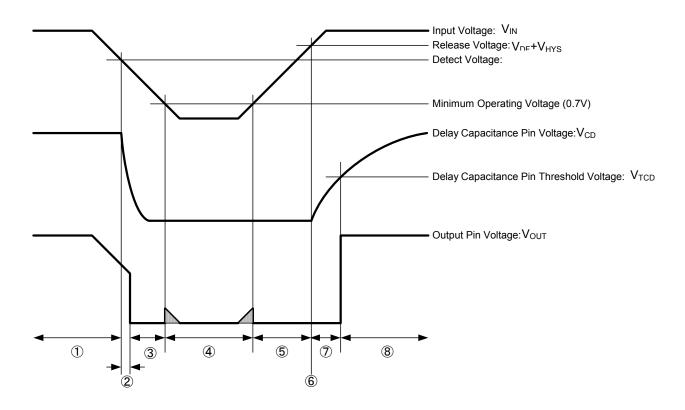

A typical circuit example is shown in Figure 1, and the timing chart of Figure 1 is shown in Figure 2 on the next page.

As an early state, the input voltage pin is applied sufficiently high voltage to the release voltage and the delay capacitance (Cd) is charged to the input pin voltage. While the input pin voltage (VIN) starts dropping to reach the detect voltage (VDF) (VIN > VDF), the output voltage (VOUT) keeps the "High" level (=VIN).

When the input pin voltage keeps dropping and becomes equal to the detect voltage (VIN = VDF), an N-ch transistor for the delay capacitance discharge is turned ON, and starts to discharge the delay capacitance. For the internal circuit, which uses the delay capacitance pin as power input, the reference voltage operates as a comparator of VIN, and the output voltage changes into the "Low" level ( $VIN \times 0.1$ ). The detect delay time (tdf) is defined as time which ranges from VIN = VDF to the VOUT of "Low" level (especially, when the Cd pin is not connected: tdf).

While the input pin voltage keeps below the detect voltage, and 0.7V or more, the delay capacitance is discharged to the ground voltage (=VSS) level. Then, the output voltage (VOUT) maintains the "Low" level.

While the input pin voltage drops to 0.7V or less and it increases again to 0.7V or more, the output voltage may not be able to maintain the "Low" level. Such an operation is called "Unspecified Operation", and voltage which occurs at the output pin voltage is defined as unstable operating voltage (VUNS).

While the input pin voltage increases more than 0.7V and it reaches to the release voltage level (VIN < VDF +VHYS), the output voltage (VOUT) maintains the "Low" level.

When the input pin voltage continues to increase more than 0.7V up to the release voltage level (= VDF + VHYS), the N-ch transistor for the delay capacitance discharge will be turned OFF, and the delay capacitance will be started discharging via a delay resistor (Rdelay). The internal circuit, which uses the delay capacitance pin as power input, will operate as a hysteresis comparator (Rise Logic Threshold: VTLH=VTCD, Fall Logic Threshold: VTHL=VSS) while the input pin voltage keeps higher than the detect voltage (VIN > VDF).

While the input pin voltage becomes equal to the release voltage or higher and keeps the detect voltage or higher, the delay capacitance (Cd) will be charged up to the input pin voltage. When the delay capacitance pin voltage (VCD) reaches to the delay capacitance pin threshold voltage (VTCD), the output voltage changes into the "High" (=VIN) level. tork is defined as time which ranges from VIN =VDF+VHYS to the VOUT of "High" level (especially when the Cd pin is not connected: tdr.).

$$t_{DR} = -Rdelay \times Cd \times In (1 - VTCD / VIN) + t_{DR0} ...(1)$$

\* In = a natural logarithm

The release delay time can also be briefly calculated with the formula (2) because the delay resistance is 2.0M (TYP.) and the delay capacitance pin threshold voltage is VIN /2 (TYP.)

$$t_{DR}$$

=  $Rdelay \times Cd \times 0.69 \dots (2)$

\* Rdelay is 2.0M (TYP.)

As an example, presuming that the delay capacitance is 0.68 µ F, toR is:

$$2.0 \times 10^6 \times 0.68 \times 10^{-6} \times 0.69 = 938 (ms)$$

While the input pin voltage is higher than the detect voltage (VIN > VDF), therefore, the output voltage maintains the "High" (=VIN) level.

#### Release Delay Time Chart

| Delay Capacitance [Cd] | Release Delay Time [tor] (TYP.) | Release Delay Time [tor] (MIN. ~ MAX.) *1 |

|------------------------|---------------------------------|-------------------------------------------|

| ( µ F)                 | (ms)                            | (ms)                                      |

| 0.01                   | 13.8                            | 11.0 ~ 16.6                               |

| 0.022                  | 30.4                            | 24.3 ~ 36.4                               |

| 0.047                  | 64.9                            | 51.9 ~ 77.8                               |

| 0.1                    | 138                             | 110 ~ 166                                 |

| 0.22                   | 304                             | 243~ 364                                  |

| 0.47                   | 649                             | 519 ~ 778                                 |

| 1                      | 1380                            | 1100 ~ 1660                               |

<sup>\*</sup> The release delay time values above are calculated by using the formula (2).

<sup>\*</sup> Note that the release delay time may remarkably be short when the delay capacitance is not discharged to the ground (=VSS) level because time described in is short.

<sup>\*1:</sup> The release delay time  $(t_{DR})$  is influenced by the delay capacitance Cd.

## **OPERATIONAL EXPLANATION (Continued)**

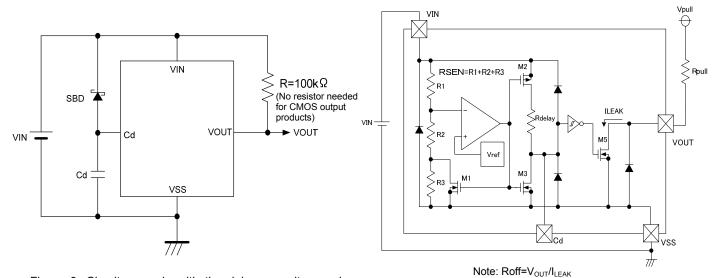

Figure 1: Typical application circuit example

Figure 2: The timing chart of Figure 1

#### NOTES ON USE

- 1. Use this IC within the stated maximum ratings. Operation beyond these limits may cause degrading or permanent damage to the device.

- 2. The input pin voltage drops by the resistance between power supply and the VIN pin, and by through current at operation of the IC. At this time, the operation may be wrong if the input pin voltage falls below the minimum operating voltage range. In CMOS output, for output current, drops in the input pin voltage similarly occur. Oscillation of the circuit may occur if the drops in voltage, which caused by through current at operation of the IC, exceed the hysteresis voltage. Note it especially when you use the IC with the VIN pin connected to a resistor.

- 3. Note that a rapid and high fluctuation of the input pin voltage may cause a wrong operation.

- 4. Power supply noise may cause operational function errors, Care must be taken to put the capacitor between V<sub>IN</sub>-GND and test on the board carefully.

- 5. When there is a possibility of which the input pin voltage falls rapidly (e.g.: 6.0V to 0V) at release operation with the delay capacitance pin (Cd) connected to a capacitor, use a schottky barrier diode connected between the VIN pin and the Cd pin as the Figure 3 shown below.

- 6. When N-ch open drain output is used, output voltages V<sub>OUT</sub> at voltage detection and release are determined by a pull-up resistor tied to the output pin. A resistance value of the pull-up resistor can be selected with referring to the followings. (Refer to Figure 4)

During detection, the formula is given as

V<sub>OUT</sub>=Vpull/(1+Rpull/R<sub>ON</sub>)

where Vpull is pull-up voltage and  $R_{ON}$  (\*1) is ON resistance of N-ch driver M5 ( $R_{ON}=V_{DS}/I_{OUT1}$  from the electrical characteristics table).

For example, when  $V_{IN}$ =2.0V (\*2),  $R_{ON}$  = 0.5/0.8 x 10<sup>-3</sup>=625 (MIN.) and if you want to get  $V_{OUT}$  less than 0.1V when Vpull=3.0V, Rpull can be calculated as follows;

Rpull=(Vpull /V<sub>OUT</sub>-1) × R<sub>ON</sub>=(3/0.1-1) × 625 18 k

Therefore, pull-up resistance should be selected 18k or higher.

- (\*1) V<sub>IN</sub> is smaller, R<sub>ON</sub> is bigger

- (\*2) For the calculation, the lowest  $V_{IN}$  should be used among of the  $V_{IN}$  range

During release, the formula is given as

V<sub>OUT</sub>=Vpull/(1+Rpull/Roff)

where Vpull is pull-up voltage Roff is OFF resistance of N-ch driver M5 (Roff= $V_{OUT}/I_{LEAK}$ =15M from the electrical characteristics table)

For examples, if you want to get  $V_{OUT}$  larger than 5.99V when Vpull is 6.0V, Rpull can be calculated as follows; Rpull= $(Vpull/V_{OUT}-1) \times Roff=(6/5.99-1) \times 15 \times 10^6$  25k

Therefore, pull-up resistance should be selected 25k or below.

Figure 3: Circuit example with the delay capacitance pin (Cd) connected to a schottky barrier diode

Figure 4: Circuit example of XC6109N Series

## TYPICAL PERFORMANCE CHARACTERISTICS

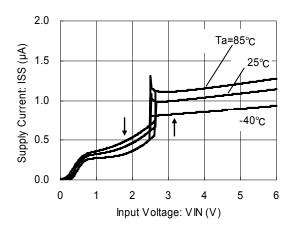

(1) Supply Current vs. Input Voltage

XC6109x25AN

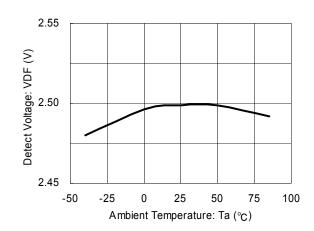

(2) Detect Voltage vs. Ambient Temperature

XC6109x25AN

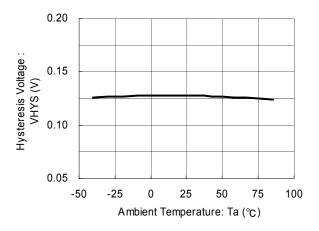

(3) Hysteresis Voltage vs. Ambient Temperature XC6109x25AN

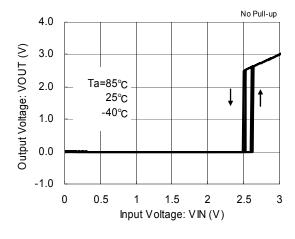

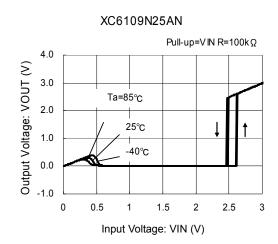

(4) Output Voltage vs. Input Voltage

XC6109C25AN

## TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

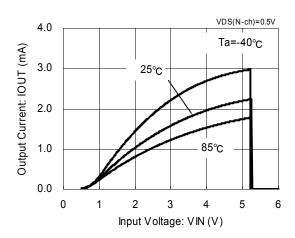

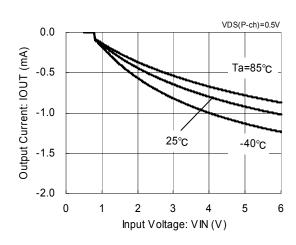

(5) Output Current vs. Input Voltage

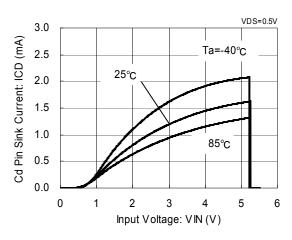

(6) Cd Pin Sink Current vs. Input Voltage

#### XC6109x50AN

(8) Release Delay Time vs. Delay Capacitance

#### XC6109xxxAN

#### XC6109C08AN

(7) Delay Resistance vs. Ambient Temperature

#### XC6109xxxAN

(9) Detect Delay Time vs. Delay Capacitance

#### XC6109xxxAN

## TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

(10) Leak Current vs. Ambient Temperature

(11) Leak Current vs. Output Voltage

## PACKAGING INFORMATION

SSOT-24 (unit : mm)

## MARKING RULE

SSOT-24

SSOT-24 (TOP VIEW) Represents output configuration and integer number of detect voltage

CMOS output (XC6109C Series)

N-ch Open Drain output (XC6109N Series)

| MARK | VOLTAGE (V) | PRODUCT SERIES | MARK | VOLTAGE (V) | PRODUCT SERIES |

|------|-------------|----------------|------|-------------|----------------|

| WARK | VOLIAGE (V) | PRODUCT SERIES | WARK | VOLIAGE (V) | PRODUCT SERIES |

| Α    | 0.x         | XC6109C0xxNx   | K    | 0.x         | XC6109N0xxNx   |

| В    | 1.x         | XC6109C1xxNx   | L    | 1.x         | XC6109N1xxNx   |

| С    | 2.x         | XC6109C2xxNx   | М    | 2.x         | XC6109N2xxNx   |

| D    | 3.x         | XC6109C3xxNx   | N    | 3.x         | XC6109N3xxNx   |

| Е    | 4.x         | XC6109C4xxNx   | Р    | 4.x         | XC6109N4xxNx   |

| F    | 5.x         | XC6109C5xxNx   | R    | 5.x         | XC6109N5xxNx   |

#### Represents decimal number of detect voltage

| MARK | VOLTAGE (V) | PRODUCT SERIES |

|------|-------------|----------------|

| N    | x.0         | XC6109xx0xNx   |

| Р    | x.1         | XC6109xx1xNx   |

| R    | x.2         | XC6109xx2xNx   |

| S    | x.3         | XC6109xx3xNx   |

| T    | x.4         | XC6109xx4xNx   |

| U    | x.5         | XC6109xx5xNx   |

| V    | x.6         | XC6109xx6xNx   |

| X    | x.7         | XC6109xx7xNx   |

| Y    | x.8         | XC6109xx8xNx   |

| Z    | x.9         | XC6109xx9xNx   |

Represents production lot number 0 to 9, A to Z or inverted characters of 0 to 9, A to Z repeated/ (G, I, J, O, Q, W excluded)

- 1. The products and product specifications contained herein are subject to change without notice to improve performance characteristics. Consult us, or our representatives before use, to confirm that the information in this datasheet is up to date.

- 2. We assume no responsibility for any infringement of patents, patent rights, or other rights arising from the use of any information and circuitry in this datasheet.

- 3. Please ensure suitable shipping controls (including fail-safe designs and aging protection) are in force for equipment employing products listed in this datasheet.

- 4. The products in this datasheet are not developed, designed, or approved for use with such equipment whose failure of malfunction can be reasonably expected to directly endanger the life of, or cause significant injury to, the user.

- (e.g. Atomic energy; aerospace; transport; combustion and associated safety equipment thereof.)

- Please use the products listed in this datasheet within the specified ranges.

Should you wish to use the products under conditions exceeding the specifications, please consult us or our representatives.

- 6. We assume no responsibility for damage or loss due to abnormal use.

- 7. All rights reserved. No part of this datasheet may be copied or reproduced without the prior permission of TOREX SEMICONDUCTOR LTD.

#### TOREX SEMICONDUCTOR LTD.