# Bidirectional 2K x 9 FIFO

### Features

- 2048 x 9 FIFO buffer memory

- Bidirectional operation

- High-speed 28.5-MHz asynchronous reads and writes

- · Simple control interface

- Registered and transparent bypass modes

- Flags indicate Empty, Full, and Half Full conditions

- 5V ± 10% supply

- Available in 300-mil DIP, PLCC, LCC, and SOJ packages

- TTL compatible

## **Functional Description**

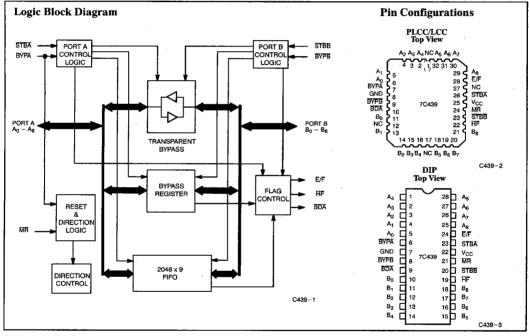

The CY7C439 is a 2048 x 9 FIFO memory capable of bidirectional operation. As the term first-in first-out (FIFO) implies, data becomes available to the output port in the same order that it was presented to the input port. There are two pins that indicate the amount of data contained within the FIFO block-E/F (Empty/Full) and HF (Half Full). These pins can be decoded to determine one of four states. Two 9-bit data ports are provided. The direction selected for the FIFO determines the input and output ports. The FIFO direction can be programmed by the user at any time through the use of the reset pin (MR) and the bypass/direction pin (BYPA). There are no control or status registers on the CY7C439, making the part simple to use while meeting the needs of the majority of bidirectional FIFO applications.

FIFO read and write operations may occur simultaneously, and each can occur at up to 28.5 MHz. The port designated as the write port drives its strobe pin (STBX, X = A or B) LOW to initiate the write operation. The port designated as the read port drives its strobe pin LOW to initiate the read operation. Output port pins go to a high-impedance state when the associated strobe pin is HIGH. All normal FIFO operations require the bypass control pin (BYPX, X = A or B) to remain HIGH.

In addition to the FIFO, two other data paths are provided; registered bypass and transparent bypass. Registered bypass can be considered as a single-word FIFO in the reverse direction to the main FIFO. The

### **Selection Guide**

|                          |                          | 7C439-25 | 7C439-30 | 7C439-40 | 7C439-65 |

|--------------------------|--------------------------|----------|----------|----------|----------|

| Frequency (MHz)          |                          | 28.5     | 25       | 20       | 12.5     |

| Maximum Access Time (ns) | Maximum Access Time (ns) |          | 30       | 40       | 65       |

| Maximum Operating        | Commercial               | 147      | 140      | 130      | 115      |

| Current (mA)             | Military                 |          | 170      | 160      | 145      |

### Functional Description (continued)

bypass register provides a means of sending a 9-bit status or control word to the FIFO-write port. The bypass data available pin  $\langle BDA \rangle$  indicates whether the bypass register is full or empty. The direction of the bypass register is always opposite to that of the main FIFO.

The port designated to write to the bypass register drives its bypass control pin (BYPX) LOW. The other port detects the presence of data by monitoring BDA and reads the data by driving its bypass control pin (BYPX) LOW. Registered bypass operations require that the associated FIFO strobe pin (STBX) remains HIGH. Registered bypass operations do not affect data residing in the FIFO, or FIFO operations at the other port.

Transparent bypass provides a means of transferring a single word (9 bits) of data immediately in either direction. This feature allows the device to act as a simple 9-bit bidirectional buffer. This is useful

for allowing the controlling circuitry to access a dumb peripheral for control/programming information.

For transparent bypass, the port wishing to send immediate data to the other side drives both its bypass and its strobe pins LOW simultaneously. This causes the buffered data to be driven out of the other port. On-chip circuitry detects conflicting use of the control pins and causes both data ports to enter a high-impedance state until the conflict is resolved.

Additionally, a Test mode is offered on the CY7C439. This mode allows the user to load data into the FIFO and then read it back out of the same port. Built-In Self Test (BIST) and diagnostic functions can take advantage of these features.

The CY7C439 is fabricated using an advanced  $0.8\mu$  N-well CMOS technology. Input ESD protection is greater than 2000V and latchup is prevented by reliable layout techniques, guard rings, and a substrate bias generator.

| Maximum Ratings (Above which the useful life may be impaired. For user guidelines, not tested.) |

|-------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                               |

| Ambient Temperature with                                                                        |

| Power Applied55°C to +125°C                                                                     |

| Supply Voltage to Ground Potential $-0.5V$ to $+7.0V$                                           |

| DC Voltage Applied to Outputs                                                                   |

| in High Z State0.5V to +7.0V                                                                    |

| DC Input Voltage3.0V to +7.0V                                                                   |

Power Dissipation . . . . . . . . . . . . . . . . . 1.0W

| Static Discharge Vo<br>(per MIL-STD-883; | Itage | > 2001V  |

|------------------------------------------|-------|----------|

| Latch-Up Current                         | ,     | > 200 mA |

### **Operating Range**

| Range                   | Ambient<br>Temperature | v <sub>cc</sub> |

|-------------------------|------------------------|-----------------|

| Commercial              | 0°C to +70°C           | 5V ± 10%        |

| Military <sup>[1]</sup> | -55°C to +125°C        | 5V ± 10%        |

### Note

1. TA is the "instant on" case temperature.

## **Pin Definitions**

| Signal<br>Name     | I/O | Description                              |

|--------------------|-----|------------------------------------------|

| A <sub>(8-0)</sub> | I/O | Data Port Associated with BYPA and STBA  |

| B <sub>(8-0)</sub> | Í/O | Data Port Associated with BYPB and STBB  |

| BYPA               | I   | Registered Bypass Mode Select for A Side |

| BYPB               | I   | Registered Bypass Mode Select for B Side |

| BDA                | 0   | Bypass Data Available Flag               |

| STBA               | I   | Data Strobe for A Side                   |

| STBB               | I   | Data Strobe for B Side                   |

| E/F                | 0   | Encoded Empty/Full Flag                  |

| HF                 | 0   | Half Full Flag                           |

| MR                 | I   | Master Reset                             |

# Electrical Characteristics Over the Operating Range<sup>[2]</sup>

|                  |                                                |                                                     |                    | 7C43 | 9-25     | 7C43 | 9-30     | 7C43 | 9-40     | 7C43 | 9-65     |      |

|------------------|------------------------------------------------|-----------------------------------------------------|--------------------|------|----------|------|----------|------|----------|------|----------|------|

| Parameter        | Description                                    | Description Test Conditions                         |                    | Min. | Max.     | Min. | Max.     | Min. | Max.     | Min. | Max.     | Unit |

| V <sub>OH</sub>  | Output HIGH<br>Voltage                         | $V_{CC} = Min.,$<br>$I_{OH} = -2.0 \text{ mA}$      |                    | 2.4  |          | 2.4  |          | 2.4  |          | 2.4  |          | V    |

| V <sub>OL</sub>  | Output LOW<br>Voltage                          | $V_{CC} = Min., I_{OL}$                             | = 8.0  mA          |      | 0.4      |      | 0.4      |      | 0.4      |      | 0.4      | V    |

| V <sub>IH</sub>  | Input HIGH                                     |                                                     | Com'l              | 2.2  | $V_{CC}$ | 2.2  | $v_{cc}$ | 2.2  | $V_{CC}$ | 2.2  | $V_{CC}$ | V    |

|                  | Voltage                                        |                                                     | Mil                |      |          | 2.2  | $v_{cc}$ | 2.2  | Vcc      | 2.2  | $v_{cc}$ | V    |

| $V_{IL}$         | Input LOW<br>Voltage                           |                                                     |                    | -3.0 | 0.8      | -3.0 | 0.8      | -3.0 | 0.8      | -3.0 | 0.8      | V    |

| I <sub>IX</sub>  | Input Leakage<br>Current                       | $GND \leq V_{I} \leq V_{CC}$                        |                    | -10  | +10      | -10  | +10      | 10   | +10      | -10  | +10      | μΑ   |

| $I_{OZ}$         | Output Leakage<br>Current                      | $\overline{STBX} \ge V_{IH},$ $GND \le V_O \le V_O$ | cc                 | -10  | +10      | -10  | +10      | -10  | +10      | -10  | +10      | μΑ   |

| $I_{CC}$         | OperatingCurrent                               | $V_{CC} = Max.,$                                    | Com'l[3]           |      | 147      |      | 140      |      | 130      |      | 115      | mA   |

|                  |                                                | $I_{OUT} = 0 \text{ mA}$                            | Mil <sup>[4]</sup> |      |          |      | 170      |      | 160      |      | 145      |      |

| I <sub>SB1</sub> | Standby Current                                | All Inputs =                                        | Com'l              |      | 40       |      | 40       |      | 40       |      | 40       | mA   |

|                  |                                                | V <sub>IH</sub> Min.                                | Mil                |      |          |      | 45       |      | 45       |      | 45       |      |

| I <sub>SB2</sub> | Power-Down                                     | All Inputs                                          | Com'l              |      | 20       |      | 20       |      | 20       |      | 20       | mA   |

|                  | Current                                        | $V_{CC} = 0.2V$                                     | Mil                |      |          |      | 25       |      | 25       |      | 25       |      |

| I <sub>OS</sub>  | Output Short<br>Circuit Current <sup>[5]</sup> | $V_{CC} = Max., V_{OU}$                             | T = GND            |      | -90      |      | -90      |      | -90      |      | -90      | mA   |

# Capacitance<sup>[6]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 8    | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 4.5V$                         | 10   | pF   |

# Notes: 2. Se

- See the last page of this specification for Group A subgroup testing information.

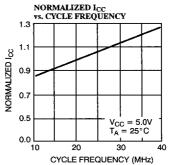

- $I_{CC}$  (commercial) = 115 mA + [( $\bar{f}$  12.5) · 2 mA/MHz] for  $\bar{f} \ge$  12.5 MHz

where  $\vec{f}$  = the larger of the write or read operating frequency.

- 4.  $I_{CC}$  (military) = 145 mA + [( $\bar{t}$  12.5) · 2 mA/MHz] for \_  $\bar{t}$  ≥ 12.5 MHz

- where  $\overline{f} = \frac{1}{1}$  the larger of the write or read operating frequency.

- For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

- Tested initially and after any design or process changes that may affect these parameters.

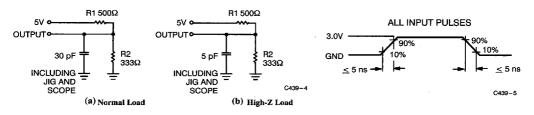

## AC Test Loads and Waveform

Equivalent to:

THÉVENIN EQUIVALENT 200Ω

OUTPUT --0 2V

Switching Characteristics Over the Operating Range [2, 7]

|                         |                               | 7C43 | 9-25      | 7C439-30 |           | 7C439-40 |           | 7C439-65 |      |      |

|-------------------------|-------------------------------|------|-----------|----------|-----------|----------|-----------|----------|------|------|

| Parameter               | Description                   | Min. | Min. Max. |          | Min. Max. |          | Min. Max. |          | Max. | Unit |

| t <sub>RC</sub>         | Read Cycle Time               | 35   |           | 40       |           | 50       |           | 80       |      | ns   |

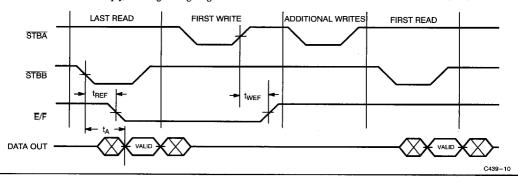

| t <sub>A</sub>          | Access Time                   | 1    | 25        |          | 30        |          | 40        |          | 65   | ns   |

| t <sub>RR</sub>         | Read Recovery Time            | 10   |           | 10       |           | 10       |           | 15       |      | ns   |

| tPR                     | Read Pulse Width              | 25   |           | 30       |           | 40       |           | 65       |      | ns   |

| t <sub>LZR</sub> [8, 9] | Read LOW to Low Z             | 3    |           | 3        |           | 3.       |           | 3        |      | ns   |

| t <sub>DVR</sub> [8, 9] | Data Valid from Read HIGH     | 3    |           | 3        |           | 3        |           | 3        |      | ns   |

| t <sub>HZR</sub> [8, 9] | Read HIGH to High Z           |      | 18        |          | 20        |          | 25        |          | 30   | ns   |

| twc                     | Write Cycle Time              | 35   |           | 40       |           | 50       | <b>—</b>  | 80       |      | ns   |

| t <sub>PW</sub>         | Write Pulse Width             | 25   |           | 30       |           | 40       |           | 65       |      | ns   |

| t <sub>HWZ</sub> [8, 9] | Write HIGH to Low Z           | 10   |           | 10       |           | 10       |           | 10       |      | ns   |

| twr                     | Write Recovery Time           | 10   |           | 10       |           | 10       |           | 15       |      | ns   |

| t <sub>SD</sub>         | Data Set-Up Time              | 15   |           | 18       |           | 20       | <u> </u>  | 30       |      | ns   |

| tHD                     | Data Hold Time                | 0    |           | 0        |           | 0        |           | 10       |      | ns   |

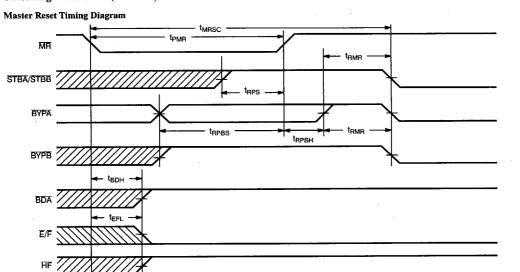

| t <sub>MRSC</sub>       | MR Cycle Time                 | 35   |           | 40       |           | 50       |           | 80       |      | ns   |

| t <sub>PMR</sub>        | MR Pulse Width                | 25   |           | 30       |           | 40       |           | 65       |      | ns   |

| t <sub>RMR</sub>        | MR Recovery Time              | 10   |           | 10       |           | 10       |           | 15       | T    | ns   |

| t <sub>RPS</sub>        | STBX HIGH to MR HIGH          | 25   |           | 30       |           | 40       |           | 65       |      | пs   |

| t <sub>RPBS</sub>       | BYPA to MR HIGH               | 10   |           | 10       |           | 15       |           | 20       |      | ns   |

| t <sub>RPBH</sub>       | BYPA Hold after MR HIGH       | 0    |           | 0        |           | 0        |           | 0        |      | ns   |

| t <sub>BDH</sub>        | MR LOW to BDA HIGH            |      | 35        |          | 40        |          | 50        |          | 80   | ns   |

| t <sub>BSR</sub>        | STBX HIGH to BYPA LOW         | 10   |           | 10       |           | 10       |           | 15       |      | ns   |

| t <sub>EFL</sub>        | MR to E/F LOW                 |      | 35        |          | 40        |          | 50        |          | 80   | ns   |

| t <sub>HFH</sub>        | MR to HF HIGH                 |      | 35        |          | 40        |          | 50        |          | 80   | ns   |

| t <sub>BRS</sub>        | BYPX HIGH to STBX LOW         | 10   | 1         | 10       |           | 10       |           | 15       |      | ns   |

| t <sub>REF</sub>        | STBX LOW to E/F LOW (Read)    |      | 25        |          | 30        |          | 35        |          | 60   | ns   |

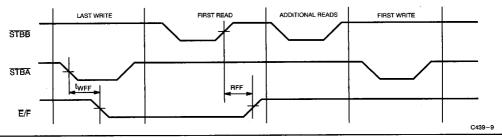

| t <sub>RFF</sub>        | STBX HIGH to E/F HIGH (Read)  |      | 25        |          | 30        |          | 35        |          | 60   | ns   |

| twer                    | STBX HIGH to E/F HIGH (Write) |      | 25        |          | 30        |          | 35        |          | 60   | ns   |

| twff                    | STBX LOW to E/F LOW (Write)   |      | 25        |          | 30        |          | 35        |          | 60   | ns   |

| t <sub>BDA</sub>        | BYPX HIGH to BDA LOW (Write)  |      | 25        |          | 30        |          | 35        | 1        | 60   | ns   |

| t <sub>BDB</sub>        | BYPX HIGH to BDA HIGH (Read)  |      | 25        |          | 30        |          | 35        |          | 60   | ns   |

| t <sub>BA</sub>         | BYPX LOW to Data Valid (Read) |      | 30        | 1        | 30        |          | 40        |          | 60   | ns   |

| t <sub>BHZ</sub> [8, 9] | BYPX HIGH to High Z (Read)    |      | 18        |          | 20        | 1        | 25        | ]        | 30   | ns   |

| t <sub>TSB</sub>        | STBX HIGH to BYPX LOW Set-Up  | 10   |           | 10       |           | 10       |           | 15       |      | ns   |

| t <sub>TBS</sub>        | STBX LOW after BYPX LOW       | 0    | 10        | 0        | 10        | 0        | 10        | 0        | 10   | ns   |

| t <sub>TSN</sub>        | STBX HIGH Recovery Time       | 10   |           | 10       |           | 10       | Ĭ         | 15       |      | ns   |

| t <sub>TSD</sub> [8, 9] | STBX HIGH to Data High Z      |      | 18        |          | 20        |          | 25        |          | 30   | ns   |

| t <sub>TBN</sub>        | BYPX HIGH Recovery Time       | 10   |           | 10       |           | 10       |           | 15       |      | ns   |

| t <sub>TBD</sub>        | BYPX HIGH to Data High Z      | 1    | 18        |          | 20        |          | 25        |          | 30   | ns   |

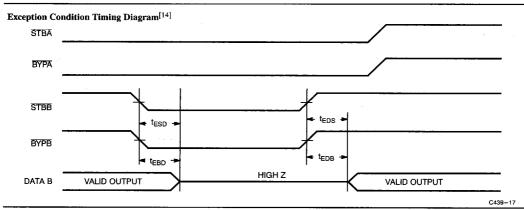

# Switching Characteristics Over the Operating Range<sup>[2, 7]</sup> (continued)

|                         | Description                                |    | 7C439-25 |      | 7C439-30 |      | 7C439-40 |      | 7C439-65 |      |

|-------------------------|--------------------------------------------|----|----------|------|----------|------|----------|------|----------|------|

| Parameter               |                                            |    | Max.     | Min. | Max.     | Min. | Max.     | Min. | Max.     | Unit |

| t <sub>TPD</sub> [8, 9] | STBX LOW to Data Valid                     |    | 20       |      | 20       |      | 30       |      | 55       | ns   |

| t <sub>DL</sub>         | Transparent Propagation Delay              |    | 20       |      | 20       |      | 25       |      | 30       | ns   |

| t <sub>ESD</sub> [8, 9] | STBX LOW to High Z                         |    | 18       |      | 20       |      | 25       |      | 30       | ns   |

| t <sub>EBD</sub> [8, 9] | BYPX LOW to High Z                         |    | 18       |      | 20       |      | 25       |      | 30       | ns   |

| t <sub>EDS</sub>        | STBX HIGH to Low Z                         |    | 18       |      | 20       |      | 25       |      | 30       | ns   |

| t <sub>EDB</sub>        | BYPX HIGH to Low Z                         |    | 18       |      | 20       |      | 25       |      | 30       | ns   |

| t <sub>BPW</sub>        | BYPX Pulse Width (Trans.)                  | 25 |          | 30   |          | 40   |          | 65   |          | ns   |

| t <sub>TSP</sub>        | STBX Pulse Width (Trans.)                  | 20 |          | 20   |          | 30   |          | 55   |          | ns   |

| t <sub>BLZ</sub> [8, 9] | BYPX LOW to Low Z (Read)                   | 10 |          | 10   |          | 10   |          | 10   |          | ns   |

| t <sub>BDV</sub>        | BYPX HIGH to Data Invalid (Read)           | 3  |          | 3    |          | 3    |          | 3    |          | ns   |

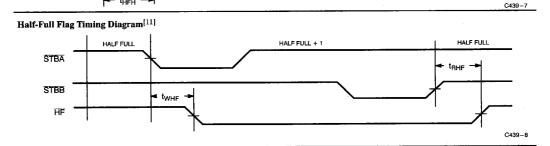

| twHF                    | STBX LOW to HF LOW (Write)                 |    | 35       |      | 40       |      | 50       |      | 80       | ns   |

| t <sub>RHF</sub>        | STBX HIGH to HF HIGH (Read)                |    | 35       |      | 40       |      | 50       |      | 80       | ns   |

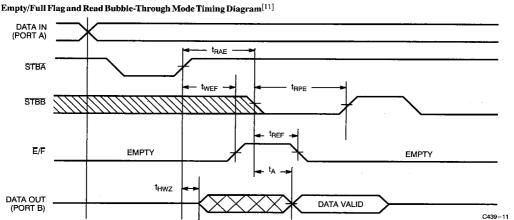

| t <sub>RAE</sub>        | Effective Read from Write HIGH             |    | 25       |      | 30       |      | 35       |      | 60       | ns   |

| t <sub>RPE</sub>        | Effective Read Pulse Width after E/F HIGH  | 25 |          | 30   |          | 40   |          | 65   |          | ns   |

| twaF                    | Effective Write from Read HIGH             |    | 25       |      | 30       |      | 35       |      | 60       | ns   |

| twpF                    | Effective Write Pulse Width after E/F HIGH | 25 |          | 30   |          | 40   |          | 65   |          | ns   |

| t <sub>BSU</sub>        | Bypass Data Set-Up Time                    | 15 |          | 18   |          | 20   |          | 30   |          | ns   |

| t <sub>BHL</sub>        | Bypass Data Hold Time                      | 0  |          | 0    |          | 0    |          | 10   |          | ns   |

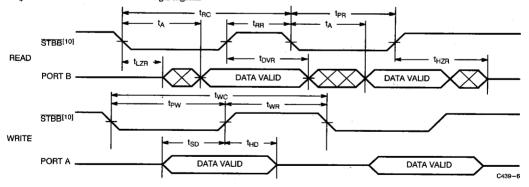

# **Switching Waveforms**

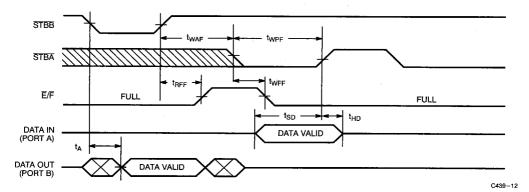

# Asynchronous Read and Write Timing Diagram

5 - 90

2589662 0015428 890 1

Notes: 7. Te Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V, and output loading of the specified Io<sub>1</sub>/I<sub>OH</sub> and 30-pF load capacitance as in part (a) of AC Test Loads, unless otherwise specified.

<sup>&</sup>lt;code>tDVR.tBDW.tHZR.tTBD.tBHZ.tEBD.tEBD.tESD.tTSD.tLZR.tHWZ.andtBLZ</code> use capacitance loading as in part (b) of AC Test Loads.

tHZR, tTBD, tBHZ, tEBD, tESD, and tTSD transition is measured at  $\pm 500$  mV from VOL and  $\pm 500$  mV from VOH. tDVR and tBDV transition is measured at the 1.5V level. tLZR, tHWZ, and tBLZ transition is measured at  $\pm 100$  mV from the steady state.

# Last Write to First Read Empty/Full Flag Timing Diagram $^{[11]}$

Notes:

10. Direction selected Port A to Port B.

11. Direction selected as A to B.

### Last Read to First Write Empty/Full Flag Timing Diagram[11]

# ${\bf Empty/Full\ Flag\ and\ Write\ Bubble-Through\ Mode\ Timing\ Diagram}^{[11]}$

5 - 92

# **2589662 0015430 449**

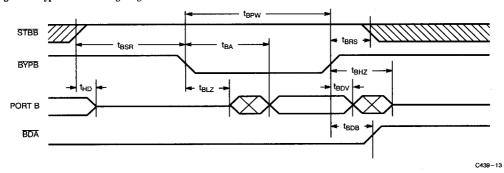

# Registered Bypass Read Timing Diagram<sup>[12]</sup>

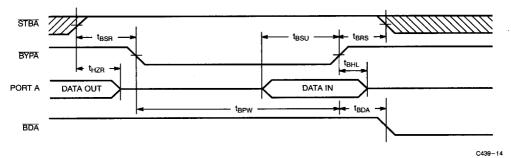

Registered Bypass Write Timing Diagram<sup>[13]</sup>

Transparent Bypass Read Timing Diagram [14]t<sub>TSB</sub> t<sub>TBS</sub> t<sub>BRS</sub> **t**RPW **BYPA** t<sub>TBD</sub> - t<sub>TPD</sub> t<sub>TSD</sub> VALID INPUT 2 PORT A VALID INPUT 1 VALID OUTPUT 1 VALID OUTPUT 2 PORT B C439-15

- Notes:

12. Port B selected to read bypass register (FIFO direction Port B to Port A).

- Port A selected to write bypass register (FIFO direction Port B to Port A.

- 14. Diagram shows transparent bypass initiated by Port A. Times are identical if initiated by Port B.

5-93

# 2589662 0015431 385 1

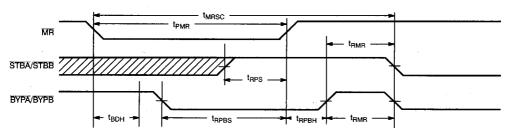

### **Test Mode Timing Diagram**

C439-16

### Architecture

The CY7C439 consists of a 2048 by 9-bit dual-ported RAM array, a read pointer, a write pointer, data switching circuitry, buffers, a bypass register, control signals ( $\overline{STBA}$ ,  $\overline{STBB}$ ,  $\overline{BYPA}$ ,  $\overline{BYPB}$ ,  $\overline{MR}$ ), and flags ( $\overline{E/F}$ ,  $\overline{HF}$ ,  $\overline{BDA}$ ).

### Operation at Power-On

Upon power-up, the FIFO must be reset with a Master Reset  $(\overline{MR})$  cycle. During an  $\overline{MR}$  cycle, the user can initialize the device by choosing the direction of FIFO operation (see Table 1). There is a minimum LOW period for  $\overline{MR}$ , but no maximum time. The state of  $\overline{BYPA}$  is latched internally by the rising edge of  $\overline{MR}$  and used to determine the direction of subsequent data operations.

### Resetting the FIFO

During the reset condition (see *Table 1*), the FIFO three-states the data ports, sets  $\overrightarrow{BDA}$  and  $\overrightarrow{HF}$  HIGH,  $\overrightarrow{E/F}$  LOW, and ignores the state of  $\overrightarrow{BYPA/B}$  and  $\overrightarrow{STBA/B}$ . The bypass registers are initialized to zero. During this time the user is expected to set the direction of the FIFO by driving  $\overrightarrow{BYPA}$  HIGH or LOW, and  $\overrightarrow{BYPB}$ ,  $\overrightarrow{STBA}$ , and  $\overrightarrow{STBB}$  HIGH. If  $\overrightarrow{BYPA}$  is LOW (selecting direction B>A), the FIFO will then remain in a reset condition until the user terminates the reset operation by driving  $\overrightarrow{BYPA}$  HIGH. If  $\overrightarrow{BYPA}$  is HIGH (selecting direction A>B), the reset condition ter-

minates after the rising edge of  $\overline{MR}$ . The entire reset phase can be accomplished in one cycle time of  $t_{RC}$ .

### **FIFO Operation**

The operation of the FIFO requires only one control pin per port  $(\overline{STBX})$ . The user determines the direction of the FIFO data flow by initiating an MR cycle (see Table 1), which clears the FIFO and bypass register and sets the data path and control signal multiplexers. The bypass register is configured in the opposite direction to the FIFO data flow. The FIFO direction can be reversed at any time by initiating another MR cycle. Data is written into the FIFO on the rising edge of the input, STBX, and read from the FIFO by a low level at the output, STBX. The two ports are asynchronous and independent. If the user attempts to read the FIFO when it is empty, no action takes place (the read pointer is not incremented) until the other port writes to the FIFO. Then a bubble-through read takes place, in which the read strobe is generated internally and the data becomes available at the read port shortly thereafter if the read strobe (STBX) is still LOW. Similarly, for an attempted write operation when the FIFO is full, no internal operation takes place until the other port performs a read operation, at which time the bubble-through write is performed if the write strobe (STBX) is still LOW.

### Registered Bypass Operation

The registered bypass feature provides a means of transferring one 9-bit word of data in the opposite direction to normal data flow without affecting either the FIFO contents or the FIFO write operations at the other port. The bypass register is configured during reset to provide a data path in the opposite direction to that of the FIFO (see Table 1). For example, if port A is writing data to the FIFO (hence port B is reading data from the FIFO) then BYPB is used to write to the bypass register at port B, and BYPA is used to read a single word from the bypass register at port A. The bypass data available flag (BDA) is generated to notify port A that bypass data is available. BDA goes true on the trailing edge of the BYPX read operation and false upon the trailing edge of the BYPX read operation.

Data is written on the rising edge of  $\overline{BYPX}$  into the bypass register for later retrieval by the other port, regardless of the state of  $\overline{BDA}$ . The bypass register is read by a low level at  $\overline{BYPX}$ , regardless of the state of  $\overline{BDA}$ .

### **Transparent Bypass Operation**

The transparent bypass feature provides a means of sending immediate data "around" the FIFO in either direction. The FIFO contents are not affected by the use of transparent bypass, but the control signals for transparent bypass are shared with those of the normal FIFO operation. Hence there are limitations on the use of transparent bypass to ensure that data integrity and ease of use are preserved. The port wishing to send immediate data must ensure that the other port will not attempt a FIFO read or write during the transparent bypass cycle. If this is not possible, registered bypass or external circuitry should be used.

Transparent bypass mode is initiated by bringing both BYPA and STBA LOW together. Care should be taken to observe the following constraints on the timing relationships. Since STBA is used for

normal FIFO operations, it must follow BYPA falling edge by t<sub>TBS</sub> to prevent erroneous FIFO read or write operations. Since BYPA is used alone to initiate registered bypass read and write, it is internally delayed before initiating registered bypass. If STBA falls during this time, delay registered bypass is averted, and transparent bypass is initiated. Identical arguments apply to BYPB and STBB.

If a transparent bypass sequence is successfully accomplished, data presented to the initiating port (port A in the above discussion) will be buffered to the other (port B) after  $t_{DL}$ . Either port can initiate a transparent bypass operation at any time, but if the control signals (STBA/B, BYPA/B) are in conflict (exception condition), internal circuitry will switch both ports to high-impedance until the conflict is resolved.

### **Test Mode Operation**

The Test mode feature provides a means of reading the FIFO contents from the same port that the data was written to the FIFO. This feature is useful for Built-In Self Test (BIST) and diagnostic functions. To utilize this capability, initialize FIFO direction A to B and load data into the FIFO using normal write timing. In order to read data back out of the same port (port A), initiate a MR cycle with both BYPA and BYPB LOW (see Test Mode Timing diagram). After completing the cycle, the data can be read out of port A in FIFO order. Data will be inverted when read out of the device. Also, flags are not valid when reading data.

### Flag Operation

There are two flags, Empty/Full ( $\overline{E/F}$ ) and Half Full ( $\overline{HF}$ ), which are used to decode four FIFO states (see *Table 4*). The states are empty, 1–1024 locations full, 1025–2047 locations full, and full. Note that two conditions cause the  $\overline{E/F}$  pin to go LOW, Empty and Full, hence both flag pins must be used to resolve the two conditions.

**Table 1. FIFO Direction Select Truth Table**

| MR      | BYPA | BYPB | STBA | STBB | Action                                                    |

|---------|------|------|------|------|-----------------------------------------------------------|

| 1       | X    | X    | X    | Х    | Normal Operation                                          |

|         | 1    | 1    | 1    | 1    | FIFO Direction A to B, Registered Bypass Direction B to A |

| <u></u> | 0    | 1    | 1    | 1    | FIFO Direction B to A, Registered Bypass Direction A to B |

| 0       | X    | Х    | Х    | X    | Reset Condition                                           |

**Table 2. Bypass Operation Truth Table**

| Direction | STBA | BYPA | STBB | BYPB | Action                                             |

|-----------|------|------|------|------|----------------------------------------------------|

| A∳B       | T    | - 1  | П    | 1    | Normal FIFO Operations, Write at A, Read at B      |

| A∳B       | 1    | T    | U    | 1    | Normal FIFO Read at B, Bypass Register Read at A   |

| A≱B       | T    | 1    | . 1  | T    | Normal FIFO Write at A, Bypass Register Write at B |

| B≱A       | J    | 1    | U    | `1   | Normal FIFO Operations, Write at B, Read at A      |

| B♦A       | 1    | U    | U    | 1    | Normal FIFO Write at B, Bypass Register Write at A |

| B∳A       | U    | 1    | 1    | TT   | Normal FIFO Read at A, Bypass Register Read at B   |

| X         | 0.   | 0    | 1    | 1    | No FIFO Operations, Transparent Data A to B        |

| X         | 1    | 1    | 0    | 0    | No FIFO Operations, Transparent Data B to A        |

| Table 3, Exception | Conditions: C | Ineration | Not Defined |

|--------------------|---------------|-----------|-------------|

|                    |               |           |             |

| Direction | STBA | BYPA | STBB | BYBP | Action                    |  |

|-----------|------|------|------|------|---------------------------|--|

| X         | 0    | 1    | 0    | 0    | Data Buses High Impedance |  |

| X         | 1    | 0    | 0    | 0    | Data Buses High Impedance |  |

| X         | 0    | 0    | 0    | 0    | Data Buses High Impedance |  |

| Х         | 0    | 0    | 1    | 0    | Data Buses High Impedance |  |

| X         | 0    | 0    | 0    | 1    | Data Buses High Impedance |  |

Table 4. Flag Truth Table

| E/F | HF | State                    |

|-----|----|--------------------------|

| 0   | 1  | Empty                    |

| 1   | 1  | 1-1024 Locations Full    |

| 1   | 0  | 1025-2047 Locations Full |

| 0   | 0  | Full                     |

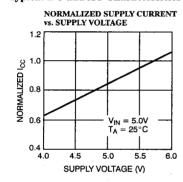

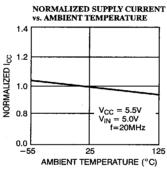

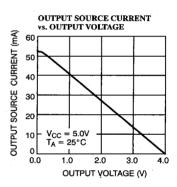

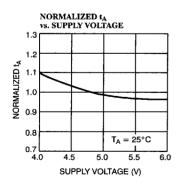

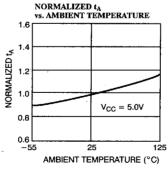

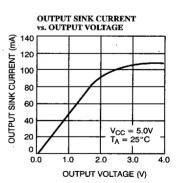

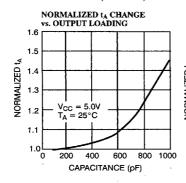

# Typical DC and AC Characteristics

# Typical DC and AC Characteristics (continued)

**Ordering Information**

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                             | Operating<br>Range |

|---------------|---------------|-----------------|------------------------------------------|--------------------|

| 25            | CY7C439-25JC  | J65             | 32-Lead Plastic Leaded Chip Carrier      | Commercial         |

|               | CY7C439-25PC  | P21             | 28-Lead (300-Mil) Molded DIP             |                    |

| 30            | CY7C439-30JC  | J65             | 32-Lead Plastic Leaded Chip Carrier      | Commercial         |

|               | CY7C439-30PC  | P21             | 28-Lead (300-Mil) Molded DIP             |                    |

|               | CY7C439-30DMB | D22             | 28-Lead (300-Mil) CerDIP                 | Military           |

|               | CY7C439-30LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier |                    |

| 40            | CY7C439-40JC  | J65             | 32-Lead Plastic Leaded Chip Carrier      | Commercial         |

|               | CY7C439-40PC  | P21             | 28-Lead (300-Mil) Molded DIP             |                    |

|               | CY7C439-40DMB | D22             | 28-Lead (300-Mil) CerDIP                 | Military           |

|               | CY7C439-40LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier | 1                  |

| 6.5           | CY7C439-65JC  | J65             | 32-Lead Plastic Leaded Chip Carrier      | Commercial         |

|               | CY7C439-65PC  | P21             | 28-Lead (300-Mil) Molded DIP             | 1                  |

|               | CY7C439-65DMB | D22             | 28-Lead (300-Mil) CerDIP                 | Military           |

|               | CY7C439-65LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier |                    |

# MILITARY SPECIFICATIONS Group A Subgroup Testing

### **DC** Characteristics

| Parameters           | Subgroups |

|----------------------|-----------|

| $V_{OH}$             | 1, 2, 3   |

| $V_{OL}$             | 1, 2, 3   |

| $V_{IH}$             | 1, 2, 3   |

| V <sub>IL</sub> Max. | 1, 2, 3   |

| $I_{IX}$             | 1, 2, 3   |

| Icc                  | 1, 2, 3   |

| I <sub>SB1</sub>     | 1, 2, 3   |

| $I_{SB2}$            | 1, 2, 3   |

| I <sub>OS</sub>      | 1, 2, 3   |

| $I_{OZ}$             | 1, 2, 3   |

**Switching Characteristics**

| Parameters        | Subgroups |

|-------------------|-----------|

| t <sub>RC</sub>   | 9, 10, 11 |

| t <sub>A</sub>    | 9, 10, 11 |

| t <sub>RR</sub>   | 9, 10, 11 |

| tpR               | 9, 10, 11 |

| t <sub>LZR</sub>  | 9, 10, 11 |

| t <sub>DVR</sub>  | 9, 10, 11 |

| tHZR              | 9, 10, 11 |

| twc               | 9, 10, 11 |

| t <sub>PW</sub>   | 9, 10, 11 |

| $t_{HWZ}$         | 9, 10, 11 |

| t <sub>WR</sub>   | 9, 10, 11 |

| t <sub>SD</sub>   | 9, 10, 11 |

| t <sub>HD</sub>   | 9, 10, 11 |

| t <sub>MRSC</sub> | 9, 10, 11 |

| t <sub>PMR</sub>  | 9, 10, 11 |

| t <sub>RMR</sub>  | 9, 10, 11 |

| t <sub>RPS</sub>  | 9, 10, 11 |

| t <sub>RPBS</sub> | 9, 10, 11 |

| t <sub>RPBH</sub> | 9, 10, 11 |

| t <sub>BDH</sub>  | 9, 10, 11 |

| t <sub>BSR</sub>  | 9, 10, 11 |

| t <sub>EFL</sub>  | 9, 10, 11 |

| t <sub>HFH</sub>  | 9, 10, 11 |

| t <sub>BRS</sub>  | 9, 10, 11 |

| t <sub>REF</sub>  | 9, 10, 11 |

| t <sub>RFF</sub>  | 9, 10, 11 |

| twef              | 9, 10, 11 |

| t <sub>WFF</sub>  | 9, 10, 11 |

| t <sub>WHF</sub>  | 9, 10, 11 |

| t <sub>RHF</sub>  | 9, 10, 11 |

| t <sub>RAE</sub>  | 9, 10, 11 |

| t <sub>RPE</sub>  | 9, 10, 11 |

| Parameters         | Subgroups |

|--------------------|-----------|

|                    |           |

| t <sub>WAF</sub>   | 9, 10, 11 |

| t <sub>WPF</sub>   | 9, 10, 11 |

| t <sub>BSU</sub>   | 9, 10, 11 |

| t <sub>BHL</sub>   | 9, 10, 11 |

| t <sub>BDA</sub>   | 9, 10, 11 |

| t <sub>BDB</sub>   | 9, 10, 11 |

| t <sub>BA</sub>    | 9, 10, 11 |

| t <sub>BHZ</sub>   | 9, 10, 11 |

| t <sub>TSB</sub>   | 9, 10, 11 |

| t <sub>TBS</sub>   | 9, 10, 11 |

| t <sub>TSN</sub>   | 9, 10, 11 |

| t <sub>TSD</sub>   | 9, 10, 11 |

| t <sub>TBN</sub>   | 9, 10, 11 |

| t <sub>TBD</sub>   | 9, 10, 11 |

| $t_{\mathrm{TPD}}$ | 9, 10, 11 |

| t <sub>DL</sub>    | 9, 10, 11 |

| t <sub>ESD</sub>   | 9, 10, 11 |

| t <sub>EBD</sub>   | 9, 10, 11 |

| t <sub>EDS</sub>   | 9, 10, 11 |

| t <sub>EDB</sub>   | 9, 10, 11 |

| t <sub>BPW</sub>   | 9, 10, 11 |

| t <sub>TSP</sub>   | 9, 10, 11 |

| t <sub>BLZ</sub>   | 9, 10, 11 |

| t <sub>BDV</sub>   | 9, 10, 11 |

Document #: 38-00126-D