# 82355 BUS MASTER INTERFACE CONTROLLER (BMIC)

- Designed for use in 32-Bit EISA Bus Master Expansion Board Designs

Integrates Three Interfaces

- (EISA, Local CPU, and Transfer Buffer)

- Supports 16- and 32-Bit Burst Transfers

33 Mbytes/Sec Maximum Data

Transfers

- Supports 32-Bit Non-Burst and Mismatched Data Size Transfers

- Supports 32-Bit EISA Addressability (4 Gigabyte)

- Two independent Data Transfer Channels with 24-Byte FIFOs

- Expansion Board Timing and EISA Timing Operate Asynchronously

- Supports Peek/Poke Operation with the Ability to Access Individual Locations in EISA Memory or I/O space

- Automatically Handles Misaligned Doubleword Data Transfers with No Performance Penalty

- Supports Automatic Handling of Complete EISA Bus Master Protocol

- EISA Arbitration/Preemption

- Cycle Timing and Execution

- Byte Alignment

- 1K Boundary Detection

- Supports Local Data Transfer Protocol Similar to Traditional DMA

- Supports a General Purpose Command and Status Interface

- Local and EISA System Interrupt Support

- General Purpose Information Transfers

- Set-and-Test-Functions in I/O Space (Semaphore Function)

- Supports the EISA Expansion Board ID Function

- Supports Decode of Slot Specific and General I/O Addresses

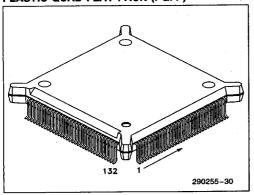

- 132-Pin JEDEC PQFP Package

(See Packaging Specification Order #240800, Package Type NG)

May 1994 Order Number: 290255-008

1-704

4826175 0160981 886 🖿

# 82355 Bus Master Interface Controller (BMIC)

| CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | \GE                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 1.0 INTRODUCTION       1-         1.1 BMIC Terminology/Definitions       1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                      |

| 2.0 BMIC INTERFACE ILLUSTRATION 1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -710                                                                                 |

| 3.0 FUNCTIONAL OVERVIEW       1-         3.1 EISA Master and EISA Slave Operations       1-         3.2 82355 Internal Architecture Description       1-         3.2.1 EISA Interface Block       1-         3.2.2 Transfer Buffer Interface Block       1-         3.2.3 FIFO/Data Aligner Block       1-         3.2.4 Local Processor Interface Block       1-         3.2.5 Data Transfer Types       1-         3.2.6 Register Accessing       1-         3.2.6.1 Register Accessing through the Local Processor Interface       1-         3.2.6.2 Register Accessing through the EISA Interface       1-         3.2.7.1 Interrupts       1-         3.2.7.2 Interrupt Handling       1- | -711<br>-711<br>-711<br>-711<br>-712<br>-712<br>-712<br>-713<br>-713<br>-713<br>-714 |

| 4.0 EISA INTERFACE 1.4.1 EISA Interface Signals 1.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -714<br>-714                                                                         |

| 4.2 Transfer Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -715<br>-716                                                                         |

| 4.3 Peek/Poke, Locked Exchange Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -717<br>-717<br>-718                                                                 |

| 4.5 EISA Address Incrementer       1         4.6 EISA Byte Decrementer       1         4.7 EISA Address Incrementer/Byte Decrementer Illustration       1         4.8 I/O Address Range Decode Support       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -720<br> -721<br> -722                                                               |

| 5.0 TRANSFER BUFFER INTERFACE 5.1 Transfer Buffer Interface Signals 5.2 External Transfer Buffer Logic 5.2.1 FIFO Implementation 5.3 Transfer Interface Start Address Generation 5.4 Transfer Buffer Interface Timing Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-723<br>1-723<br>1-724<br>1-724<br>1-724                                            |

| CONTENTS                                                   | PAGE  |

|------------------------------------------------------------|-------|

| 6.0 FIFO/DATA ALIGNER                                      | 1-727 |

| 6.1 FIFO/Data Aligner                                      | 1-727 |

| 6.2 FIFOs                                                  | 1-727 |

| 6.3 Data Aligner                                           | 1-727 |

| 6.3.1 EISA Byte Alignment                                  |       |

| 6.3.2 Data Assembly/Disassembly                            | 1-728 |

| 7.0 LOCAL PROCESSOR INTERFACE                              | 1-728 |

| 7.1 Shared Registers—Status/Command Support                | 1-728 |

| 7.1.1 Semaphore Ports                                      | 1-729 |

| 7.1.2 Mailbox Registers                                    | 1-729 |

| 7.1.3 Doorbell Registers                                   | 1-729 |

| 7.2 Local Processor Recommendations                        | 1-730 |

| 7.3 Requirements for No Local Processor                    | 1-730 |

| 7.4 EISA ID Function Support/Registers                     | 1-730 |

| 8.0 REGISTER DESCRIPTION                                   | 1-731 |

| 8.1 Shared Register Description                            | 1-731 |

| 8.1.1 Command/Status Support Registers                     | 1-732 |

| 8.1.1.1 Semaphore Ports                                    |       |

| 8.1.1.2 Mailbox Registers                                  | 1-732 |

| 8.1.1.3 Doorbell Registers                                 | 1-732 |

| 8.1.1.3.1 Local Doorbell Interrupt/Status Register         |       |

| 8.1.1.3.2 Local Doorbell Enable Register                   | 1-732 |

| 8.1.1.3.3 EISA System Doorbell Interrupt/Status Register   |       |

| 8.1.1.3.4 EISA System Doorbell Enable Register             | 1-733 |

| 8.1.1.3.5 System Interrupt Enable/Control Register         | 1-733 |

| 8.1.2 Global Configuration Register                        | 1-733 |

| 8.1.3 ID Registers                                         | 1-734 |

| 8.2 Local Processor Only Registers                         | 1-735 |

| 8.2.1 Index Registers                                      | 1-736 |

| 8.2.1.1 Local Index Register                               | 1-736 |

| 8.2.1.2 Local Data Register                                | 1-736 |

| 8.2.2 Local Status/Control Register                        | 1-736 |

| 8.2.3 Data Channel Transfer Registers                      | 1-736 |

| 8.2.3.1 Channel 0 and 1 Transfer Base Address Registers    | 1-737 |

| 8.2.3.2 Channel 0 and 1 Transfer Current Address Registers | 1-737 |

| 8.2.3.3 Channel 0 and 1 Transfer Base Count Registers      |       |

| 8.2.3.4 Channel 0 and 1 Transfer Current Count Registers   | 1-737 |

| CONTENTS                                                               |   |

|------------------------------------------------------------------------|---|

| 8.2.4 Data Transfer Status/Control Registers                           |   |

| 8.2.4.1 Channel 0 and 1 Transfer Strobe Registers 1-738                |   |

| 8.2.4.2 Channel 0 and 1 Transfer Channel Configuration Registers 1-738 |   |

| 8.2.4.3 Channel 0 and 1 Transfer Channel Status Registers              |   |

| 8.2.5 Peek/Poke Registers1-740                                         |   |

| 8.2.5.1 Peek/Poke Address Registers 1-741                              |   |

| 8.2.5.2 Peek/Poke Data Registers1-741                                  |   |

| 8.2.5.3 Peek/Poke Control Register1-741                                | I |

| 8.2.6 I/O Range Decode Registers1-741                                  | I |

| 8.2.6.1 Range 0 and 1 I/O Decode Base Address Registers                |   |

| 8.2.6.2 Range 0 and 1 I/O Decode Control Registers                     |   |

| 8.2.7 Transfer Buffer Interface (TBI) Registers1-742                   |   |

| 8.2.7.1 Channel 0 and 1 TBI Base Address Registers1-742                |   |

| 8.2.7.2 Channel 0 and 1 TBI Current Address Registers                  |   |

| 9.0 DETAILED PIN DESCRIPTION1-743                                      |   |

| 9.1 EISA Interface Signals1-743                                        |   |

| 9.2 EISA Buffer Control Signals 1-746                                  |   |

| 9.3 Address Decode Signals 1-746                                       |   |

| 9.4 Transfer Buffer Interface Signals 1-747                            |   |

| 9.5 Local Processor Interface Signals 1-748                            |   |

| 9.6 Power Supplies1-748                                                |   |

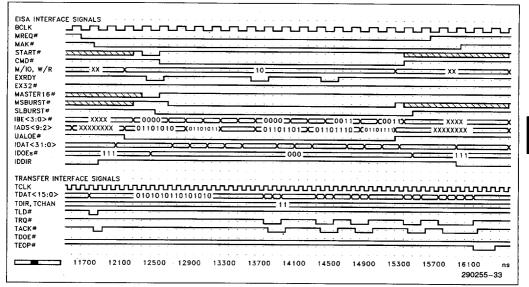

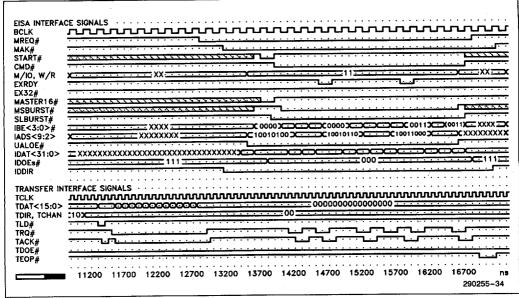

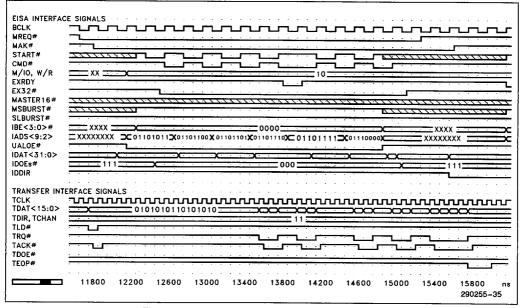

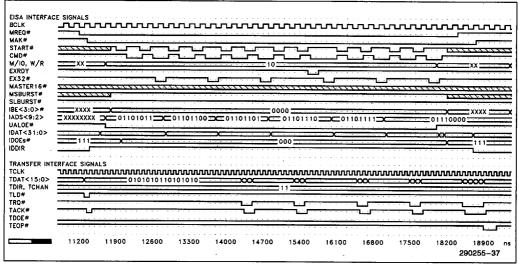

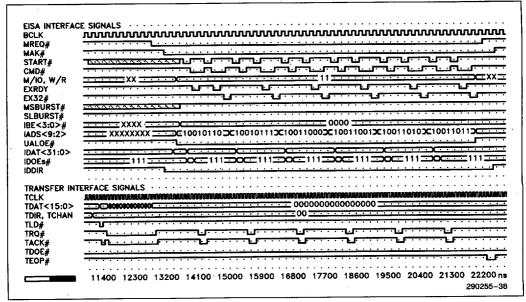

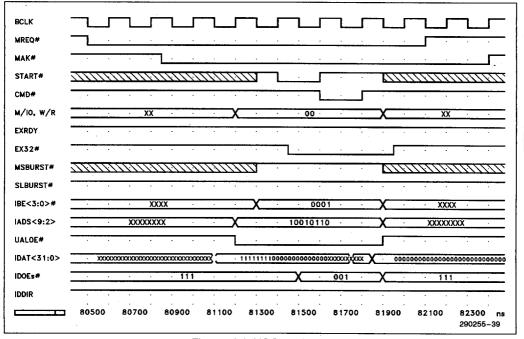

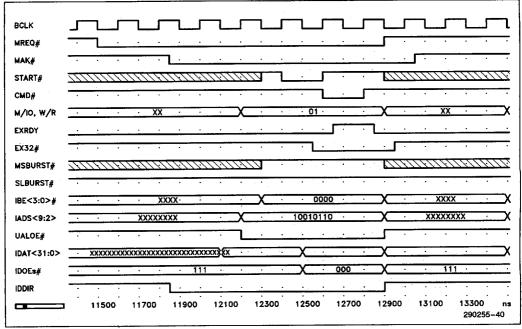

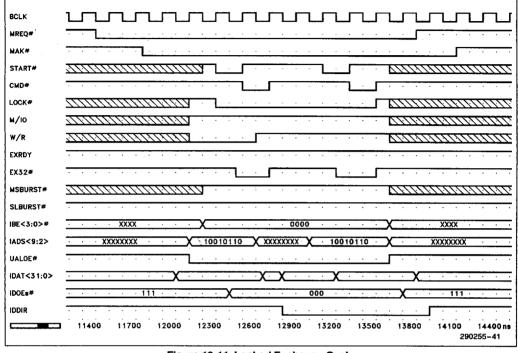

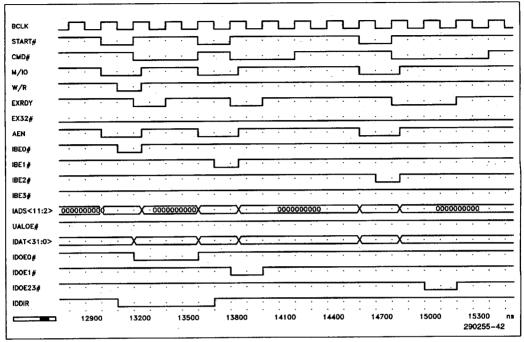

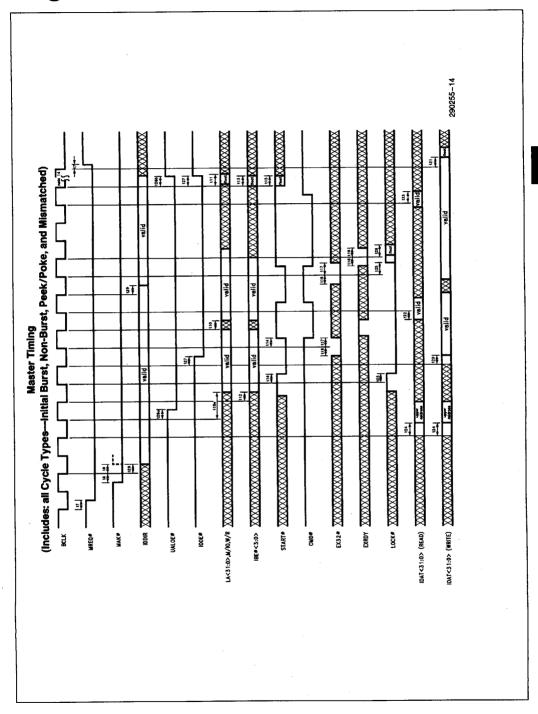

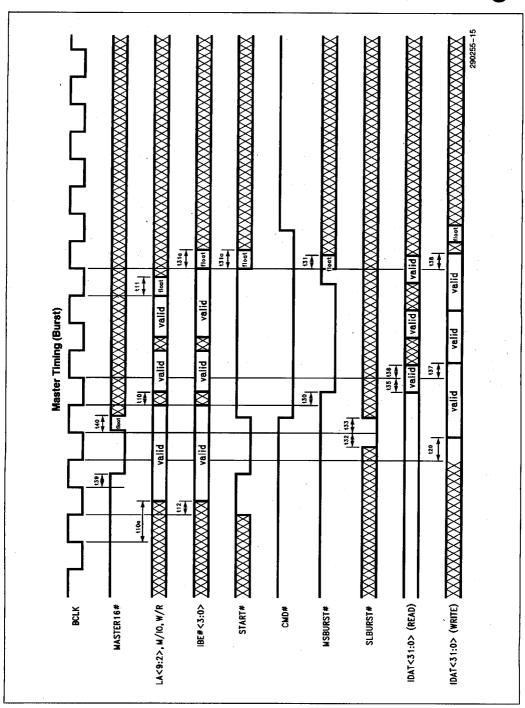

| 10.0 BASIC FUNCTION TIMING DIAGRAMS 1-749                              |   |

| 11.0 D.C. SPECIFICATIONS                                               |   |

| 11.1 Maximum Ratings 1-761                                             |   |

| 11.2 D.C. Characteristics Table                                        |   |

| 12.0 A.C. SPECIFICATIONS                                               |   |

| 12.1 A.C. Characteristics Tables                                       |   |

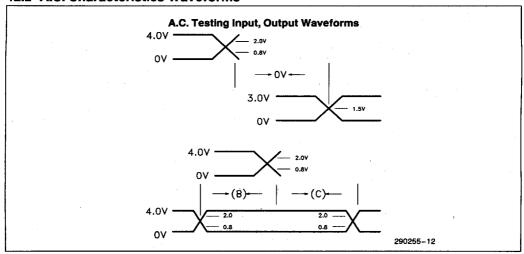

| 12.2 A.C. Characteristics Vaveforms                                    |   |

|                                                                        |   |

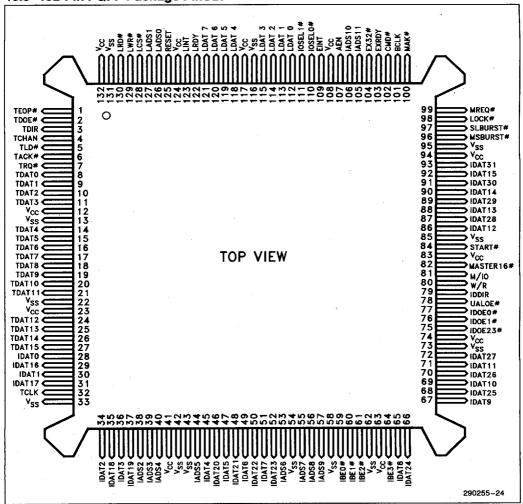

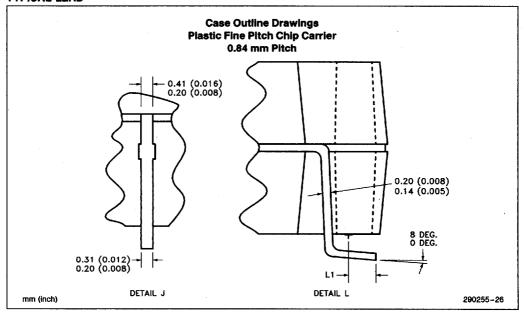

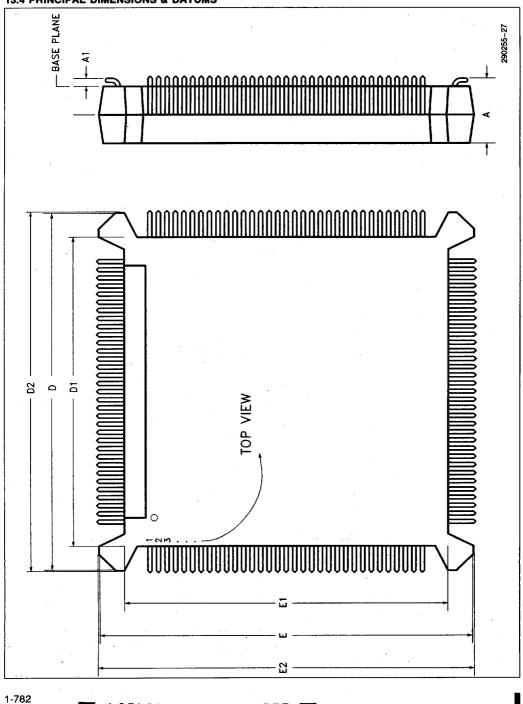

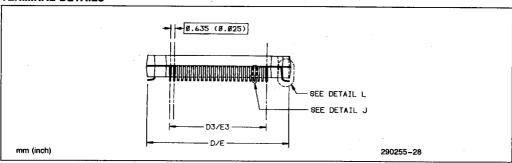

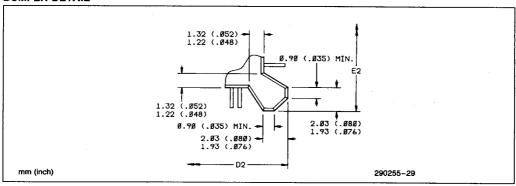

| 13.0 BMIC PIN AND PACKAGE INFORMATION1-777                             |   |

| 13.1 Signal Overview1-777                                              |   |

| 13.2 Device Pinout                                                     |   |

| 13.3 132-Pin PQFP Package Pinout                                       | , |

| 13.4 Package Dimensions and Datums                                     |   |

| 13.5 Package Thermal Specification1-784                                |   |

| 14.0 BMIC REGISTER ADDRESS MAP 1-784                                   | ŀ |

| 14.1 Index Register Set 1-784                                          |   |

| 14.2 Shared Register Set 1-785                                         |   |

| 14.3 Processor Only Register Set1-786                                  | j |

|                                                                        |   |

### 1.0 INTRODUCTION

The 82355 Bus Master Interface Controller (BMIC) is a highly integrated Bus Master designed for use in 32-Bit EISA Bus Master expansion board designs and supports all of the enhancements defined in the EISA specifications required for EISA bus master applications. The BMIC provides a simple, yet, powerful and flexible interface between the functions on the expansion board and the EISA bus. With the help of external buffer devices, the BMIC provides all EISA control, address, and data signals necessary to interface to the EISA bus.

The primary function of the 82355 is to support 16and 32-bit burst data transfers between functions on the EISA expansion board and the EISA bus. Data transfer rates of up to 33 Mbytes/sec are supported (the fastest transfer rate available on an EISA bus). The following logic on the BMIC supports efficient burst transfers:

- Arbitration logic, for gaining control of the EISA bus

- · Two transfer-address and byte counters

- Two data FIFOs, which allow expansion board and EISA bus timing to operate asynchronously

- Data shifters, which align data to specific byte boundaries

- A transfer buffer interface, for the data transfers on the expansion board

- General-purpose command and status interface logic

- Local processor interface, to allow programming by an on-board processor

- EISA slave interface, to allow communication with the EISA system

The BMIC greatly simplifies the design of EISA expansion boards. With the 82355, a board can be implemented with simple logic similar to that used in traditional ISA DMA designs. The EISA standard allows designs with 32-bit data and address buses, burst transfers, and automatic handling of the full EISA bus master protocol.

To maximize system throughput, the 82355 BMIC incorporates three fully concurrent interfaces: EISA interface, Transfer Buffer interface, and Local Processor interface. The EISA interface incorporates two 24-byte FIFOs, and implements the full EISA protocol. The Transfer Buffer interface is optimized for high speed static RAM buffers, and can operate at a maximum frequency of 20 MHz. The Local Processor interface supports a generic slave interface, and allows the local processor to fully program the BMIC for operation. Local processors are supported with the ability to access individual locations in system memory or I/O space; this peek-and-poke feature allows the expansion board to communicate easily with other devices in the system. All three interfaces can operate simultaneously, thus maximizing overall system performance.

Address-generation support for the data transfer buffer logic on the expansion board is provided onchip. The transfer logic on the expansion board can use a high-speed asynchronous transfer clock. The BMIC handles all synchronization with the EISA bus. A FIFO within the BMIC eliminates performance degradation on burst transfers caused by synchronization delays. The BMIC also provides a set of programmable address comparators that drive external chip selects on the expansion board to assist local devices in decoding I/O address ranges.

# 1.1 BMIC Terminology/Definitions

EISA BUS MASTER—A 32- or 16-bit device that uses the extended part of the EISA bus to generate memory or I/O cycles.

**Downshifting Bus Master**—A "downshifting" master is a 32-bit master which can convert to a 16-bit master "on the fly". The BMIC will only downshift from a 32-bit master to a 16-bit master if programmed for burst mode (refer to Section 4.2.1).

EISA READ—A data transfer (burst, non-burst (two BCLK), or mismatched) from system to the expansion board across transfer channel 1.

EISA WRITE—A data transfer (burst, non-burst (two BCLK), or mismatched) from the expansion board to system memory across one of the two transfer channels.

I/O ADDRESS DECODE SUPPORT—Refers to slot specific or general I/O address decoding.

Slot Specific Address Decoding—Refers to the decoding of unique addresses allocated to EISA slot specific expansion boards. These addresses are: X000h—X0FFh, X400h—X4FFh, X800h—X8FFh, and XC00h—XCFFh, where X represents the EISA slot number. EISA slot number "0" is reserved for the EISA system board.

**General I/O Address Decoding**—Refers to the decoding of addresses allocated to ISA expansion boards. These addresses are: 0100h-03FFh.

LOCAL PROCESSOR—A processor located on the expansion board.

**SYSTEM CPU—**Processor located on the mother-board.

**SYSTEM MEMORY**—Memory located on the EISA bus or motherboard.

**TRANSFER INTERRUPTION**—A transfer interruption is defined as an occurrence resulting in a break in a transfer caused by one of the following conditions: A FIFO pause, a FIFO stall, a channel preemption, a channel clear or suspension, a 1K page break, or a transfer complete (EOP).

FIFO Pause—This is a condition where the EISA bus does not provide or take data at a rate fast enough to keep up with the expansion board transfer buffer logic. During an EISA read, this condition is defined as an empty FIFO. During an EISA write, this condition is defined as a full FIFO. A FIFO pause is considered a preferred condition and under normal operations should occur frequently. A FIFO pause will result in the BMIC negating TRQ # until the FIFO becomes not full during an EISA write or not empty during an EISA read.

FIFO Stall—This is a condition where the transfer buffer logic on the expansion board does not provide or take data at a rate fast enough to keep up with the EISA bus. During an EISA read, this condition is defined as a full FIFO. During an EISA write, this condition is defined as an empty FIFO. Under normal operations, a FIFO stall is expected to be a rare and exceptional event. For additional information regarding a FIFO stall, refer to Section 6.2.

Channel Clear—A channel clear results in the immediate termination of the current transfer and the flushing of the channel's corresponding FIFO. A channel clear is initiated by setting the CFGCL bit in the corresponding channel's Configuration register to a 1. For additional information regarding channel clear, refer to Section 8.2.4.2.

Channel Suspension—This temporarily prevents a channel from proceeding with a transfer. A transfer can be temporarily suspended by setting the CFGSU bit in the corresponding channel's Configuration register to a 1.

Channel Preemption—The BMIC can be preempted from the EISA bus by the 82357 (ISP). The 82357 negates MAK# indicating to the BMIC that it must finish the current bus cycle and relinquish control of the EISA bus by negating MREQ# within 64 BCLK periods. The BMIC is programmable to relinquish the bus within 0, 32, or 64 BCLKs from the negation of MAK# (refer to Section 4.4.2).

**1K Page Break**—The temporary termination of a burst, non-burst (two BCLK), or mismatched data transfer due to a 1K page address boundary crossing (refer to Section 4.2.2).

**Transfer Complete (EOP)**—End of process due to the transfer byte count being exhausted or a channel being cleared (channel clear). A transfer complete (EOP) will result in the BMIC asserting TEOP # with the last cycle (refer to Section 5.4).

TRANSFER BUFFER LOGIC—Logic located on the expansion board used to support the transfer and storage of data during BMIC EISA master mode transfers between the expansion board and system memory.

The transfer buffer logic interfaces to the Transfer Buffer Interface of the BMIC. Refer to Section 5.2 for additional information regarding transfer buffer logic.

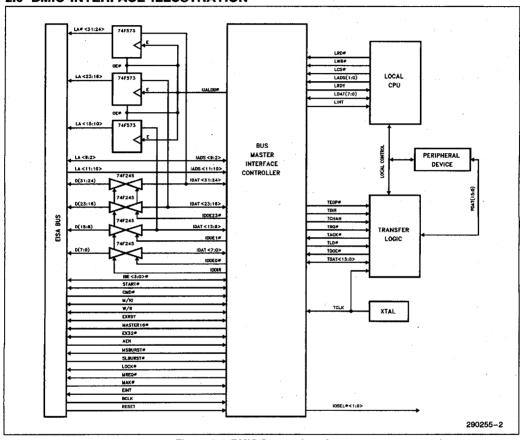

## 2.0 BMIC INTERFACE ILLUSTRATION

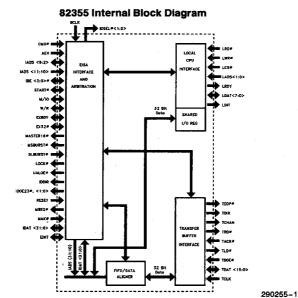

Figure 2-1. BMIC System Interface

### 3.0 FUNCTIONAL OVERVIEW

The following is a brief discussion of the functional blocks and features of the 82355. The EISA interface, Transfer Buffer interface, FIFO/Data Aligner, and Local interface each have a corresponding detailed section later in this data sheet.

# 3.1 EISA Master and EISA Slave Operations

In EISA slave mode, the 82355 monitors the EISA address lines <11:2> for general I/O address decoding, slot-specific address decoding, and Shared register accessing. During slave mode operations, all internal registers are accessible through the Local Processor interface, and all Shared registers are accessible through either the Local Processor interface or the EISA interface of the BMIC.

In EISA master mode, the 82355 becomes the master of the EISA bus. It may perform burst, non-burst (two BCLK), mismatched, or Peek/Poke data transfers at this time. During master mode operations, all internal registers are accessible through the Local Processor interface of the BMIC.

The arbiter portion of the BMIC determines which mode the device is in, performs the EISA arbitration, and provides the control signals necessary to regulate the slave and master activities internal to the chip. In slave mode, the arbiter also mediates between the EISA side and the local side during Shared register accesses.

The following is a table of the functions that can be performed during master and slave operations:

|                                   | Shared Reg.<br>Accessing |     | Address | Data<br>Transfers |

|-----------------------------------|--------------------------|-----|---------|-------------------|

| EISA                              | YES (1, 2)               | YES | YES     | NO                |

| Slave Mode<br>EISA<br>Master Mode | YES (2)                  | YES | NO      | YES               |

#### NOTE:

Shared Reg. Accessing refers to the registers that are accessible through either the EISA interface or Local Processor interface.

Local Processor Only Reg. Accessing refers to the registers that are accessible through the Local Processor interface only

EISA I/O Address Decoding refers to either general or slot specific I/O decoding support for the expansion board. Data Transfers refer to either burst, non-burst (two BCLK), mismatched, or peek/poke data transfers.

YES = Can Be Performed NO = Can Not Be Performed

1 = EISA interface 2 = Local interface

# 3.2 82355 Internal Architecture Description

The 82355 contains four blocks of control logic. The EISA interface block, Transfer Buffer interface block, FIFO/Data Aligner block, and the Local Processor interface block.

#### 3.2.1 EISA INTERFACE BLOCK

The EISA interface block provides the following functions:

- generates the 32-bit EISA address for burst, nonburst (two BCLK), and peek/poke data transfers

- generates the EISA control signals necessary to implement an EISA 16-bit or 32-bit bus master, and a 32-bit EISA slave

- generates the control signals necessary to enable and disable the external buffer devices

- performs the EISA arbitration and provides the internal control signals required to regulate the slave and master activities of the BMIC

- integrates the registers necessary for the above operations as well as the registers required to provide the configuration and status of the data transfers between the EISA bus and the memory buffer on the expansion board

The EISA memory address range of the 82355 covers the 4 Gigabytes and supports the detection of 1K page address boundaries during burst, non-burst (two BCLK), and mismatched data cycles to and from system memory.

During slave mode, the EISA interface also supports slot specific and general I/O address decode necessary for Shared Register accesses and general decode as required by the expansion board. The shared register addresses are mapped into the slot specific I/O range (C80h-C9Fh).

The EISA interface block contains 43 registers necessary to execute the above functions. A detailed description of the registers and their functions can be found under Register Description (Sections 8.1 and 8.2).

## 3.2.2 TRANSFER BUFFER INTERFACE BLOCK

The Transfer Buffer interface block provides the group of signals that are required to perform 16-bit data transfers to and from the memory buffer on the expansion board. The protocol used is similar to that found in standard DMA designs. The interface includes a 16-bit data bus (TDAT), seven control signals and a transfer clock (TCLK). The transfer clock can run completely asynchronous to the EISA BCLK signal.

The Transfer Buffer interface block also provides a 16-bit transfer start address which is generated at the beginning of all new data transfers to and from the memory buffer on the expansion board. The 16 TDAT data lines are used to transfer the address.

The Transfer Buffer interface block contains eight registers. A detailed description of the registers and their functions can be found under Register Description (Section 8.2).

#### 3.2.3 FIFO/DATA ALIGNER BLOCK

The FIFO/Data Aligner block is used to isolate and simplify the timing relationships between the EISA bus and the bus master expansion board. This allows the transfer buffer logic and EISA bus timing to operate asynchronously. The FIFO provides the data channel between the EISA bus and the expansion board during BMIC master data transfers and the Data Aligner provides the byte alignment and assembly necessary for the EISA bus.

There are two dual-port, six doubleword wide (24 byte) FIFOs on-board, one per transfer channel. The data is written into the FIFO from either the EISA bus side or the expansion board side, depending on the direction of the transfer. The transfer direction is controlled by a bit in the Transfer Base Count register set.

#### 3.2.4 LOCAL PROCESSOR INTERFACE BLOCK

The Local Processor interface block provides the interface between the BMIC and the local processor. If a local processor is not present, the processor interface can be connected to the ISA bus. The Local Processor interface block is based on an 8086 style slave mode and provides an 8-bit data path for BMIC programming. All of the BMICs internal registers are accessible through this interface.

The Local Processor interface block contains a group of Shared registers used to support general-purpose command and status interactions between the system CPU or EISA bus master and the local processor. In addition to the command/status registers, the CPU interface includes a set of ID registers for EISA expansion board ID support, and a set of Peek/Poke data registers used to hold the data during peek/poke operations.

The local interface portion of the BMIC also contains three 8-bit registers which are used by the local processor to access all of the BMICs internal registers. These registers are mapped into the local processor interface and include a local status register, local data register, and a local index register (refer to Section 3.2.6.1).

The Local Processor block contains 31 registers. A detailed description of the registers and their functions can be found under Register Description (Sections 8.1 and 8.2).

#### 3.2.5 DATA TRANSFER TYPES

The BMIC supports four types of data transfers on the EISA bus: Burst, non-burst (two BCLK), peek/poke or locked exchange, and mismatched. For all of the above transfer types, the addressed slave device can negate EXRDY if wait state timing is required (each wait state is one BCLK).

The primary function of the BMIC is to support 16and 32-bit burst data transfers between functions on the expansion board and the EISA memory. If the addressed memory is not capable of supporting burst transfers, the BMIC will run either 32-bit nonburst (two BCLK) cycles or, with the support of the 82358 EISA Bus Controller, run mismatched data cycles.

The burst cycle type provides a continuous sequence of one BCLK read or write cycles to and from 16- or 32-bit EISA memory. Burst cycles can not be used with I/O devices or ISA devices (slaves or masters).

The non-burst cycle type provides a continuous sequence of two BCLK read or write transfers to and from 32-bit EISA memory. The BMIC will only respond as a 32-bit master when configured for two BCLK transfers (refer to Section 4.2.1).

The peek/poke and locked exchange feature allows local processor accesses to and from individual I/O space or system memory locations on the EISA bus. The BMIC responds as a 32-bit master and generates two BCLK cycles when configured for peek/poke transfers (refer to Section 4.3). A locked exchange transfer consists of six BCLKs (peek followed by a poke). A peek/poke data transfer has the same timings as a non-burst (two BCLK) data transfer

The mismatched cycle type provides a means of communicating with 8- or 16-bit EISA or ISA devices. In the event the I/O or memory slave device that has been addressed requires a data size translation, the BMIC will back-off the bus and allow the 82358 EISA Bus Controller to perform the necessary data size translations (refer to Section 4.2.1). The BMIC will generate mismatched cycles as required for all data transfers (burst, non-burst, peek, poke, or locked-exchange).

The following table identifies the BMIC cycle types, master sizes, slave types accessible (memory-I/O), and BCLKs per cycle.

1-712

4826175 0160989 077

| Transfer        |        | BMIC<br>laster Size |     | ve Type<br>cessible | BCLKs<br>per |  |

|-----------------|--------|---------------------|-----|---------------------|--------------|--|

| Туре            | 16-Bit | 32-Bit              | 1/0 | Memory              | Cycle        |  |

| Burst           | Х      | Х                   |     | х                   | 1            |  |

| Mismatched      |        | Х                   |     | x                   |              |  |

| Non-Burst       |        | х                   |     | ×                   | 2            |  |

| Mismatched      |        | x                   |     | х                   |              |  |

| Peek/Poke       |        | x                   | Х   | х                   | 2            |  |

| Mismatched      |        | x                   | х   | x                   | *            |  |

| Locked Exchange |        | X                   | X   | ıх                  | 6            |  |

| Mismatched      |        | ×                   | x   | X                   |              |  |

<sup>\*</sup>Depends on slave type/size (EISA/ISA, I/O/Memory, 8-bit/16-bit)

For all of the above transfer types, the addressed slave device can negate EXRDY if wait-state timing is required (each wait-state is one BCLK).

#### 3.2.6 REGISTER ACCESSING

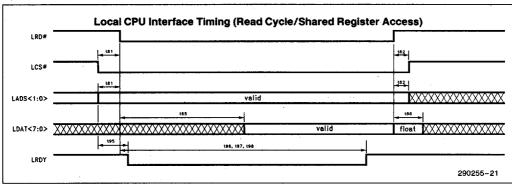

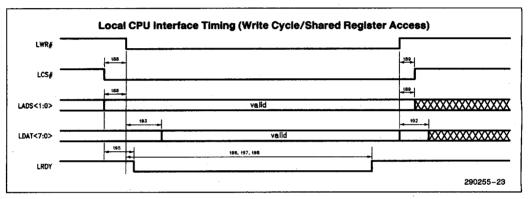

The BMIC provides three distinct groups of registers; the Shared register set, the Local Processor Only register set, and the Index register set. The Shared register set is used by the system CPU or EISA bus master and the local processor for general-purpose command and status interactions and expansion board ID support. The Local Processor only registers are used by the local processor to program the BMIC and provide status for data transfers across the EISA bus and Transfer Buffer interface. The Local Processor Only register set also provides address range decode support for slot specific and general I/O address ranges of interest to the expansion board. The Index register set is used by the local processor as a means of accessing all of the above registers through an indexing scheme.

The Shared register set is accessible through either the EISA interface or the Local Processor interface, the remaining two register sets are accessible through the Local Processor interface only. In the case of contention between the EISA bus and the local processor accessing a Shared register simultaneously, the local processor on the expansion board will have initial priority. Consecutive multiple accesses to the BMIC's shared registers result in a rotational arbitration between the EISA bus and the local processor.

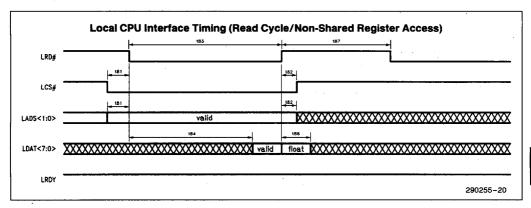

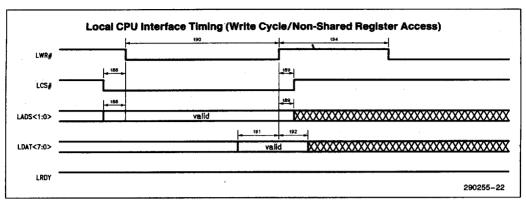

### 3.2.6.1 Register Accessing through the Local Processor Interface

Register accessing on the local side of the BMIC is accomplished using an indexing procedure. The local interface portion of the BMIC contains two 8-bit registers which are used by the local processor to access all of the BMIC's internal registers. These registers are mapped into the Local Processor inter-

face and include a local data register and a local index register. The registers are selected using the two local address lines (LADS<1:0>). The BMIC's internal register set is read by writing the address of the register to be accessed into the local index register. The register contents are then read through the Local Data registers. To write to one of the BMIC's internal registers, the local processor must first write the address of the register to be accessed into the local index register, same as a read, then write the new data value to the Local Data register.

An optional auto-increment mode is supported by the BMIC, which automatically increments the index register after each register read or write. This allows for efficient programming of the register set by using byte string moves. If the Local Index register is given a local index address with bit (7) set high, the local index address will automatically increment each time the Local Data register is read or written.

The Local Status/Control register is directly mapped into the Local Processor interface and is also accessible using the two address lines (LADS<1:0>).

# 3.2.6.2 Register Accessing through the EISA Interface

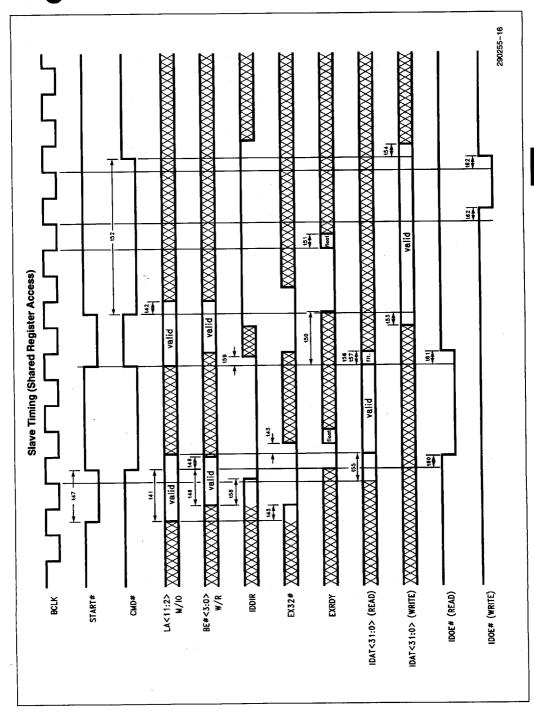

The shared registers are mapped directly into the EISA slot-specific I/O space XC80-XC9F. The EISA address lines <11:2> and the byte enables <3:0> are used for decode during shared register accesses.

A standard slave read or write access to the BMIC consists of two BCLKs + one wait-state (one wait-state = one BCLK period). During a slave cycle where the EISA access loses the internal register access through arbitration to the local processor, the cycle will consist of two BCLKs + two wait-states. The BMIC will negate EXRDY for one BCLK for each wait-state required.

## 3.2.7 INTERRUPTS

The BMIC provides two interrupt request lines, one for the EISA side (EINT), and one for the local side (LINT). The EISA interrupt (EINT) can be programmed for either edge or level-triggered operations. During edge-triggered operations the EINT signal will transition from a low level to a high level. In level-triggered mode, the EISA interrupt signal is an active low open collector output. The local interrupt signal (LINT) can be programmed for either active low or active high level operations and will default to active low operation upon reset. The LINT signal is not an open collector output during active low operations and will require external logic if interrupts need to be tied together on the local side. The EINT and LINT modes of operation are programmed through the Global Configuration register.

1-713

4826175 0160990 899

#### 3.2.7.1 Interrupt Sources

Several events can trigger each of the two interrupt request signals, and the events can be enabled or disabled on an individual or global basis (refer to Sections 8.1.1.3 and 8.2.2). The system CPU or EISA bus master can only be interrupted by an I/O write from the local processor to the BMIC EISA System Doorbell register. However, the local processor can be interrupted by several sources which are listed below:

- An I/O write from the system CPU or EISA bus master to the BMIC Local Doorbell register.

- The completion of a data transfer on one of the transfer channels.

### 3.2.7.2 Interrupt Handling

To prevent the BMIC from allowing undetected interrupts from occurring, when servicing an interrupt initiated by the BMIC, all additional interrupts must be disabled prior to reading the Local or EISA System Doorbell Status registers. The interrupts are disabled by writing to the Local or EISA System Doorbell Enable registers, depending on the source of the interrupt.

This is required due to the nature of the interrupt mechanism of the BMIC. All interrupt sources have an edge triggered nature internal to the BMIC, with each event being 'OR'ed together. Additional interrupt sources occurring after the first interrupt will set their appropriate bit in the Status register, but they will not generate an external interrupt until the initial event has been cleared. Thus if the Status register was read first, and another interrupt occurred after this read, the second interrupt would remain undetected in the status register until another event occurred. Disabling of the interrupts prior to reading the status register will prevent this from occurring.

### 4.0 EISA INTERFACE

### 4.1 EISA Interface Signals

The BMIC provides a complete interface to the EISA bus and supplies all of the control signals, data lines, and address lines necessary to implement a 16- or 32-bit EISA bus master and a 32-bit EISA slave. This includes a 32-bit data path, a 32-bit address path, and 20 EISA control signals. The BMIC also provides five control signals used to enable and disable the external data buffers and address latches, as shown in Figure 2-1.

The BMIC uses four 74F245 external bidirectional buffers to drive and receive the 32 EISA data and three 74F573 external latches to latch and drive the upper 22 EISA address lines. The external data buffers and address latches should be comprised of "F" or "AS" type logic to meet EISA speed requirements.

The upper 22 EISA addresses are multiplexed through the 22 upper EISA data lines of the BMIC. They are latched externally by the 74F573's. EISA address lines <11:2> and byte enable lines <3:0> are tied directly to the EISA bus. Address lines 10 and 11 are input directly to the BMIC for slave mode address decode. During EISA master operation, lines 10 and 11 are driven indirectly through the external latches.

As a slave, the BMIC receives address lines IADS<11:2> and byte enable lines IBE<3:0> # for I/O address decode. Address lines <11:2> are used for slot specific decode and address lines <9:2> are used for general I/O address decode. Address lines <11:2> along with IBE<3:0> # are used by the BMIC during Shared register accesses. Address lines <31:12> are not used by the BMIC in slave mode.

The following address lines are used during I/O decoding as shown:

Slot specific I/O address decoding (expansion board)—IADS<11:2>

Slot specific I/O address decoding (shared registers)—IADS<11:2>/IBE<3:0>#

General I/O address decoding (expansion board)—IADS<9:2>

All of the BMIC EISA control signals function as defined in the EISA bus specification. The signals are used to support the following cycles:

#### **BMIC** as a Master

| (Cycle Type Performed) |       |           |            |                              |  |  |

|------------------------|-------|-----------|------------|------------------------------|--|--|

| Master<br>Type         | Burst | Non-Burst | Mismatched | Peek/Poke/Locked<br>Exchange |  |  |

| 32-Bit<br>16-Bit       | X     | ×         | X          | x                            |  |  |

#### **BMIC** as a Slave

- Responds to EISA shared register accesses as 32-bit slave.

- Responds to slot specific and general I/O accesses (refer to Section 4.8).

1-714

4826175 0160991 725

# 4.2 Transfer Channels

The BMIC contains two identical independent transfer channels which are configurable to run either burst or non-burst (two BCLK) cycles to and from system memory. The BMIC will automatically run non-burst (two BCLK) or mismatched cycles if the memory the BMIC has addressed cannot run burst cycles. Mismatched cycles will be run if data size translation is required.

Channel 0 must be used for EISA READ operation only. Channel 1 can be used for both EISA READ and EISA WRITE operations.

Each channel has three sets of registers to regulate data transfers. These are the Base register group, the Current register group, and the Data Status/Control register group. This implementation of a triple register set allows a processor to begin programming the next transfer on the channel while the current transfer is being executed.

The Base register set contains seven 8-bit registers. These registers are programmed by the local processor when a transfer is required across one of the channels. Four Transfer Channel Base Address registers are combined to form the starting 32-bit EISA address to be used during the transfer. The remaining three registers are the Transfer Channel Base Count Registers. The Base Count registers are combined to determine the number of transfers (in bytes) to be performed. The number of bytes which can be transferred ranges from 1 byte to 4 Mbytes. The most significant bit of the Transfer Channel Base Count register group is used to control the start of the transfer and the second most significant bit is used to control the direction of the transfer (refer to Section 8.2.3.3).

The Current register set contains seven registers each of which corresponds to a Base register. These registers are loaded from the Base registers. The Transfer Channel Current Address registers contain the 32-bit real-time EISA memory address. The Transfer Channel Current Count registers contain the number of bytes remaining to be transferred on the channel. The current register set is readable by the local processor. However, there are possible coherency problems involved with reading multiple bytes while the current registers are being updated during a transfer. To avoid these problems, a channel's transfer should be temporarily suspended (using the channel's Configuration Register) before trying to read the channel's current register set.

The Status/Control register set contains three registers: the Transfer Channel Strobe register, Transfer Channel Configuration register, and the Transfer Channel Status register. The Transfer Channel Strobe register is used to initiate the transfer of data

from the Base register set to the associated Current register set. A transfer request for that channel will be generated following the Current register load. The Transfer Channel Configuration register is used to program the mode of the transfer. The Transfer Channel Status register provides current FIFO and transfer channel status.

To initialize a transfer over either of the two transfer channels, the following steps must be completed:

1. Verify that the Base registers for the desired transfer channel are available.

The Transfer Channel Base Address and Base Count registers must be available before they can be programmed. This is determined by the status of bits 0 and 1 in the Local Status/Control register. A "1" in either of the two bits indicates that the corresponding channel is currently running a transfer and the Base registers are busy. A "0" indicates that the Base registers are free and available for programming. In the event that the Base registers are not available, the local processor must wait until the data transfer executing on the requested channel has completed, at which time bits "0" or "1" (depending on which channel was programmed) in the Local Status/Control registers will be reset to 0. Programming the Base registers during a Base register Busy state. is illegal and will corrupt the Base register data of the pending transfer. Programming the Transfer Configuration register during a cycle in progress may cause the termination of the transfer, depending on which bit in the register was changed.

- Program the transfer channel's associated Transfer Base register set with the desired transfer information (Base registers must be available).

- Initiate the Base register to Current register load and schedule a transfer request by writing to the channel's Transfer Strobe register.

If a transfer is in progress on the requested channel and a write to the associated channel's Strobe register is done, the Base to Current register load will take place immediately after the data transfer on the requested channel has completed.

# 4.2.1 BURST AND NON-BURST MODES OF OPERATION

The BMIC can be programmed for burst or non-burst (two BCLK) data transfers to and from EISA memory. This is determined by a write to the Channel Configuration Register.

If burst mode is enabled, the BMIC will look for the SLBURST# signal at the beginning of the transfer to determine if the slave device that was addressed is

capable of running burst cycles. If the slave device does not respond with an active SLBURST# signal, the BMIC will not activate the MSBURST# signal and will proceed with either non-burst (two BCLK) bus cycles or mismatched cycles.

In burst mode, the BMIC can respond as a 16- or 32-bit master. The BMIC informs the system of this capability by driving MASTER16# low from the same BCLK rising edge that START# is asserted. MASTER16# will remain low for one BCLK. The BMIC will automatically "downshift" from a 32- to a 16-bit master if the EX32# signal is sampled inactive and the SLBURST# signal is sampled active at the beginning of a transfer. If EX32# and SLBURST# are sampled active at the beginning of the transfer, the BMIC will proceed with a 32-bit burst transfer.

In non-burst mode, the BMIC will respond as a 32bit master. The BMIC will look for the EX32# signal at the beginning of the transfer to determine if the system memory it has addressed has the same bus width. If the EX32# signal is not returned (mismatched cycle indicated), the BMIC will "back-off" the bus by floating START#, IBE#<3:0>, and IDAT <31:0> to allow the 82358 EISA Bus Controller to take control of the transfer. The EISA Bus Controller will then proceed to assemble or disassemble the data as needed. The EISA Bus Controller will return the EX32# signal after the mismatched cycle is complete, indicating to the BMIC that a new address can be placed on the bus. If the EX32# signal is sampled active at the beginning of the transfer, the BMIC will proceed with a 32-bit nonburst (two BCLK) transfer.

# 4.2.2 1K PAGE ADDRESS BOUNDARY DETECTION

During burst, non-burst (two BCLK), and mismatched data cycles, the BMIC provides the support to detect 1K page address boundary crossings. If the BMIC detects that the current cycle is about to cross a 1K page boundary, the transfer will be temporarily terminated on the next cycle. The BMIC will then arbitrate between restarting the transfer on the current channel, selecting the second channel, doing a peek/poke cycle, or preempting the channel (refer to Section 4.4 for information regarding BMIC arbitration).

Example: Transfer = 32-bit transfer and page address boundary is at location 400h = 1024

- The BMIC detects that the current cycle is about to cross a 1K page address boundary—current address (3FCh = 1020).

- Address after BMIC has executed the current cycle (400h = 1024).

- 3. Transfer is temporarily terminated (interrupted).

- BMIC will now arbitrate between restarting the transfer on a new page, selecting the second channel, doing a peek/poke cycle, or preempting the channel.

## 4.3 Peek/Poke, Locked Exchange Transfers

To allow the local processor to communicate with other devices in the main system, the BMIC allows the local processor to execute individual I/O or memory cycles over the EISA bus. These cycles can be thought of as being similar to "peek" and "poke" statements in the Basic programming language. These cycles may be reads, writes, or locked exchanges in 8-, 16-, 24-, or 32-bit values. All cycles must be contained within a single doubleword.

The Peek/Poke operation requires the following set of registers: Four 8-bit Peek/Poke Address registers which are combined to provide the 32-bit Peek/Poke address; One 8-bit Peek/Poke Control register which contains the bits defining whether the cycle is I/O or memory, peek (read)/poke (write) or locked exchange, and which byte enables are to be active during the cycle; and four 8-bit Peek/Poke Data reqisters which are used to hold the data for the Peek/ Poke cycle. During all peek/poke or locked exchange cycles, byte enables IBE < 3:0 > # are derived from bits 0-3 in the Peek/Poke Control register set. The lower two bits of the Peek/Poke Address register are ignored. Peek, poke, or locked exchange cycles will not be generated for illegal combinations of byte enables (i.e., 1111, 1010, 0110, 0101, 0100, 0010).

To do an individual write cycle (poke), the local processor must first write to the Peek/Poke Address register set to specify the 32-bit memory address or the 16-bit I/O address. It must then write the data to be transferred into the Peek/Poke Data register set. The data must be placed in the appropriate byte positions in the Data register set so that it goes out on the correct byte lanes during a 32-bit bus master transfer.

Once the appropriate data and address have been programmed, the local processor must write to the Peek/Poke Control register to specify the cycle type and initiate the cycle. After this write to the Peek/Poke Control register, bit 2 in the Local Status/Control register will be set to a 1 by the BMIC to indicate that a peek/poke request is pending and that the peek/poke registers are busy. When the poke cycle has finished executing on the EISA bus, the Peek/Poke status bit 2 in the Local Status/Control register will return to normal (0).

To do an individual read cycle (peek), the local processor must write to the Peek/Poke Address registers, then to the Peek/Poke control register to initiate the read cycle. The Peek/Poke status bit 2 in the Local Status/Control register will be set high by the BMIC and remain active until the peek cycle finishes on the EISA bus. The local processor can then read the data from the Peek/Poke data registers.

### NOTE:

When running consecutive peek transfers, the data must be read from the Peek/Poke data registers before each new peek transfer is generated. The BMIC will read the data off the EISA bus from all four byte lanes regardless of which Byte enables (IBE<3:0>#) are active. (Although all bytes are read, the value of the byte enables are important to the system and must be programmed for the peek transfer).

When a locked exchange cycle is requested by the local processor, a peek cycle is scheduled first and then immediately followed by a poke cycle. The LOCK# signal is active during the locked exchange cycle to indicate to the system that no other accesses to the addressed location can be made.

Whenever the BMIC is commanded to do an EISA POKE cycle, the BMIC will assert the MREQ# signal low normally, transfer up to four bytes of data, and release the bus by de-asserting MREQ# high. A potential problem exists, however, when the slave device extends the cycle by de-asserting EXRDY low. If the slave holds this signal low past the time that the BMIC is forced to release MREQ# high (it has been preempted while waiting for the slave to assert EXRDY high), then the BMIC will drive MREQ# back low again immediately after this cycle ends if there is another transfer pending (TBI, PEEK, POKE or LOCKED-EXCHANGE). Note that according to the EISA spec, MREQ\* signal description "A bus master must wait at least two BCLKs after releasing the bus before reasserting its MREQx\*". To adhere to EISA specifications, it is required that LOCKED-EXCHANGE cycles be used in lieu of POKE cycles.

Any consecutive Peek/Poke or Locked exchange transfers must be initiated only after the previous Peek/Poke or Locked exchange has been completed. This can be accomplished by making sure that bit 2 of the local status/control register is set to a zero before initiating the transfer.

### 4.4 Arbitration

### 4.4.1 EISA/BMIC ARBITRATION

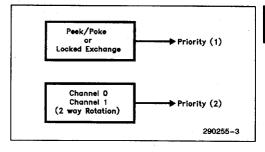

The BMIC will begin master mode operation any time a transfer request is pending. If more than one transfer request is pending, the BMIC will service them in the following order. Peek/Poke cycles have

the highest priority access to the EISA bus followed by the two data channels. Once the BMIC has gained control of the EISA bus, the BMIC will first perform any peek, poke, or locked exchange transfers that may be pending. If there are no peek, poke, or locked exchange transfers pending, the BMIC will run data transfers initiated by either of the two transfer channels. The two transfer channels have equal priority with respect to each other and are serviced in an alternating fashion. The priorities and assignments are as follows:

The BMIC will maintain ownership of the EISA bus until it has serviced all outstanding data transfer requests or it is preempted from the bus by the removal of the MAK# signal. The BMIC can be configured to relinquish the EISA bus immediately, 4 µs, or 8 µs after a preempt is received. If the BMIC has completed all outstanding data transfer requests prior to the time-out of the preempt timer, it will give up the bus. If the BMIC finishes one task prior to the timeout of the preempt timer, it will start on the next pending transfer request unless the request is a peek, poke, or locked exchange cycle. The BMIC will not start a set of peek, poke, or locked exchange cycles after the MAK# signal has been removed. If a transfer is cut-off due to a preempt timer time-out. the BMIC, upon regaining access to the EISA bus and following its internal arbitration priority scheme, will continue the transfer that was preempted at the point the transfer was cut-off.

When a channel is interrupted for any reason, 1K page break, FIFO stall, channel clear, channel suspend, or transfer complete, the BMIC may immediately relinquish the EISA bus depending on the state of the CFGFF bit in the Channel Configuration register set.

#### NOTE:

During a FIFO pause, the CFGFF bit in the associated Channel's Configuration register is ignored. The function of the CFGFF bit, as related to the above channel interruptions, is as follows:

If the CFGFF bit = 1, the BMIC will immediately relinquish control of the EISA bus upon the detection of any of the above interruptions. This will occur

regardless if there are additional data transfer requests pending. If there are additional data transfer requests pending, the BMIC will reassert MREQ# a minimum of two BCLKs later to reacquire the EISA bus. The BMIC will follow the arbitration priority scheme outlined above when servicing a data transfer request after a transfer interruption has occurred.

If the CFGFF bit = 0, the BMIC retains ownership of the EISA bus upon detection of a FIFO stall or 1K page break as long as a preempt timer timeout has not occurred. If there are additional data requests pending, the BMIC will immediately perform the pending transfer and then rearbitrate for the EISA bus to complete the interrupted transfer. If there are no additional data requests pending, the BMIC will relinquish ownership of the EISA bus only after the current transfer interruption has been serviced and completed.

## 4.4.2 BMIC PREEMPT TIMER

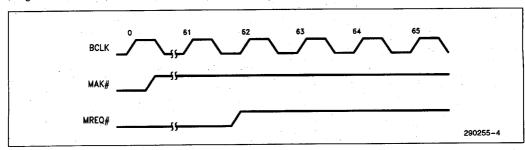

The BMIC can be preempted from the EISA bus by the 82357 (ISP). The 82357 negates MAK#, indicating to the BMIC that it must finish the current bus cycle and relinquish control of the EISA bus by negating MREQ# within 64 BCLK periods (8  $\mu$ s).

The BMIC provides a programmable preempt timer which can be programmed to relinquish the bus within 3, 32, or 64 BCLKs. The preempt timer is programmable through the Global Configuration register.

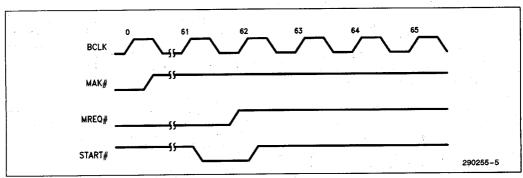

The following diagrams illustrate the latest the BMIC will start a new transfer after MAK# has been negated.

Depending on the type of transfer started, the BMIC will respond as follows:

### Assumptions:

- The 82357 has negated the MAK# signal at BCLK zero.

- The preempt timer is programmed to relinquish the EISA bus within 64 BCLKs after the negation of MAK#.

- Let X = programmed value of preempt delay (in BCLKs).

## **BMIC Response:**

For all transfers, the BMIC will negate MREQ# within (X-2.5) BCLK periods following the MAK# transition to an inactive state (BCLK 61.5).

For all transfers, the BMIC may assert START# on any of the first X-3 rising edges of BCLK following the MAK# transition to an inactive state (BCLK 61).

1-718

**4** 4426175 0160995 370 **•**

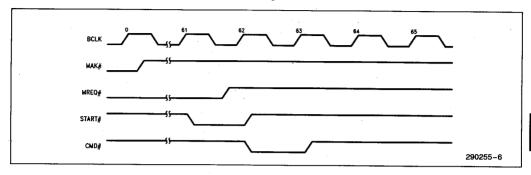

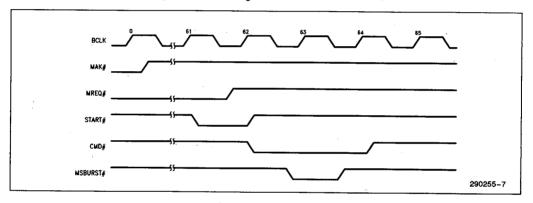

If the last cycle is a non-burst two BCLK cycle, CMD# will become inactive within (X-1) BCLK periods from the inactive transition of MAK# (BCLK 63), this is assuming that EXRDY is active.

If the last cycle is a burst EISA cycle, the BMIC will negate MSBURST# within (X-0.5) BCLK periods from the inactive transition of MAK# (BCLK 63.5). The last CMD# will go inactive within X BCLK periods from the deassertion of MAK# (BCLK 64). This is assuming EXRDY is active.

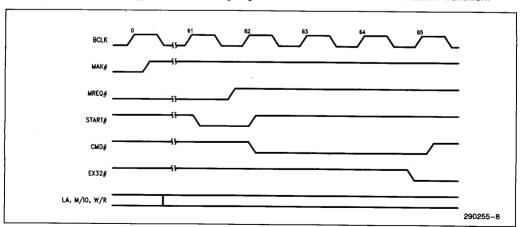

If the last cycle is mismatched, cycle completion will be controlled by the system. The BMIC will drive the LA address, M/IO, and W/R signals until the falling edge of BCLK after the last CMD# inactive transition.

### 4.5 EISA Address incrementer

The Transfer Channel Current Address register set for each channel functions as an address incrementer and is used to generate and track the address of the data during transfers. The register set increments the address according to the number of bytes being transferred during that cycle. The transfer is automatically aligned on doubleword boundaries. The two least significant bits of the starting 32-bit address (A0 and A1) are used to determine the initial address increment value.

For 32-bit transfers, the BMIC provides an initial address increment of 1, 2, 3 or 4 depending on the value of address lines A < 1:0 > . After the initial increment, the BMIC increments the address by 4 until the last cycle is detected.

The following example illustrates the BMIC address incrementer during a 32-bit master mode transfer.

|                          |           | EISA Address |    |    |    |

|--------------------------|-----------|--------------|----|----|----|

|                          | .·        | A3           | A2 | A1 | A0 |

| Start Address            | FFFFF001h | 0            | 0  | 0  | 1  |

| Initial Increment        | FFFFF004h | 0            | 1  | 0  | 0  |

| (Incremented by 3)       |           |              |    |    |    |

| All Increments Following | FFFFF008h | 1            | 0  | 0  | 0  |

| (Incremented by 4)       | FFFFF00Ch | 1            | 1  | 0  | 0  |

The starting address A<1:0> is 01, this means that the initial increment must be 3 in order to align the next increments on doubleword boundaries. The subsequent increments will be by 4 until the last cycle is detected.

For 16-bit transfers, the BMIC provides an initial address increment of 1 or 2 depending on the status of address lines A<1:0>. After the initial increment, the BMIC increments the address by two until the last cycle is detected.

The following example illustrates the BMIC address incrementer during a 16-bit master mode transfer.

|                                         |           | EISA Address |    |    |    |

|-----------------------------------------|-----------|--------------|----|----|----|

|                                         |           | A3           | A2 | A1 | A0 |

| Start Address                           | FFFFF001h | 0            | 0  | 0  | 1  |

| Initial Increment<br>(Incremented by 1) | FFFFF002h | 0            | 0  | 1  | 0  |

| All Increments Following                | FFFFF004h | 0            | 1  | 0  | 0  |

| (Incremented by 2)                      | FFFFF006h | 0            | 1  | 1  | 0  |

The starting address A<1:0> is 01, this means that the initial increment must be 1 in order to align the next increments on singleword boundaries. The subsequent increments will be by 2 until the last cycle is detected.

## NOTE:

The BMIC internally assembles 32-bit dwords. When a 16-bit burst transfer is preempted, the transfer will stop on a doubleword boundary.

# 4.6 EISA Byte Decrementer

The Transfer Channel Current Count register set for each channel contains the intermediate value of the byte count during the transfer and is used as the byte decrementer. The decrementer's function is partially based upon the address incrementer. In the above 32-bit incrementer example, the byte count would be decremented by 3 on the first cycle. After the initial decrement, the channel's Current Count register set is decremented by 4 until the last cycle is detected. In the above 16-bit incrementer example, the byte count would be decremented by 1 on the first cycle. After the initial decrement, the channel's Current Count register set is decremented by 2 until the last cycle is detected. Note that the Current Count register does not decrement entirely to zero. Instead, it retains the value of the number of bytes transferred during the last cycle.

# 4.7 EISA Address Incrementer/Byte Decrementer Illustration

The following table illustrates the various states of (A0, A1) vs the transfer byte-count and the initial address during a 32-bit transfer.

| Byte<br>Count | Starting<br>Address | Next<br>Address | Initial<br>Increment | Number of<br>Bytes Left | Last<br>Cycle | Number of<br>Cycles Left |

|---------------|---------------------|-----------------|----------------------|-------------------------|---------------|--------------------------|

| 1             | XXX 0000            | NA              | NA                   | 0                       | Yes           | 0                        |

|               | XXX 0001            | NA              | NA.                  | 0                       | Yes           | ŏ                        |

|               | XXX 0010            | NA .            | NA NA                | 0                       | Yes           | ŏ                        |

|               | XXX 0011            | NA NA           | NA                   | o                       | Yes           | Ö                        |

| 2             | XXX 0000            | , NA            | NA                   | 0                       | Yes           | ō                        |

|               | XXX 0001            | NA.             | NA                   | l o                     | Yes           | Ö                        |

|               | XXX 0010            | NA NA           | NA                   | 0                       | Yes           | ő                        |

|               | XXX 0011            | XXX 0100        | 1                    | 1                       | No            | 1                        |

| 3             | XXX 0000            | NA NA           | NA.                  | 0                       | Yes           | Ó                        |

|               | XXX 0001            | NA NA           | NA                   | o                       | Yes           | ő                        |

|               | XXX 0010            | XXX 0100        | 2                    | 1                       | No            | 1                        |

|               | XXX 0011            | XXX 0100        | 1                    | 2                       | No            | 1                        |

| 4             | XXX 0000            | NA              | NA                   | Ō                       | Yes           | Ó                        |

|               | XXX 0001            | XXX 0100        | 3                    | 1                       | No            | Ĭ                        |

|               | XXX 0010            | XXX 0100        | 2                    | 2                       | No            | i i                      |

|               | XXX 0011            | XXX 0100        | 1                    | 3                       | No            | 1                        |

| 5             | XXX 0000            | XXX 0100        | 4                    | 1                       | No            | 1                        |

|               | XXX 0001            | XXX 0100        | 3                    | 2                       | No            | 1                        |

|               | XXX 0010            | XXX 0100        | 2                    | 3                       | No            | 1                        |

|               | XXX 0011            | XXX 0100        | 1.                   | 4                       | No            | 1                        |

| 6             | XXX 0000            | XXX 0100        | 4                    | 2                       | No            | 1                        |

|               | XXX 0001            | XXX 0100        | 3                    | 3                       | No            | i                        |

|               | XXX 0010            | XXX 0100        | 2                    | 4                       | No            | 1                        |

|               | XXX 0011            | XXX 0100        | 1                    | 5                       | No            | 2                        |

| 7             | XXX 0000            | XXX 0100        | 4                    | 3                       | No            | 1                        |

|               | XXX 0001            | XXX 0100        | 3                    | 4                       | No            | 1                        |

|               | XXX 0010            | XXX 0100        | 2                    | 5                       | No            | 2                        |

|               | XXX 0011            | XXX 0100        | 1                    | 6                       | No            | 2                        |

| 8             | XXX 0000            | XXX 0100        | 4                    | 4                       | No            | 1                        |

|               | XXX 0001            | XXX 0100        | 3                    | 5                       | No            | 2                        |

|               | XXX 0010            | XXX 0100        | 2                    | 6                       | No            | 2                        |

|               | XXX 0011            | XXX 0100        | 1                    | 7                       | No            | 2                        |

| 9             | XXX 0000            | XXX 0100        | 4                    | 5                       | No            | 2                        |

|               | XXX 0001            | XXX 0100        | 3                    | 6                       | No            | 2                        |

|               | XXX 0010            | XXX 0100        | 2                    | 7                       | No            | 2                        |

|               | XXX 0011            | XXX 0100        | 1                    | 8                       | No            | 2                        |

| 10            | XXX 0000            | XXX 0100        | 4                    | 6                       | No            | 2                        |

|               | XXX 0001            | XXX 0100        | 3                    | 7                       | No            | 2                        |

|               | XXX 0010            | XXX 0100        | 2                    | 8                       | No            | 2                        |

|               | XXX 0011            | XXX 0100        | 1                    | 9                       | No            | 3                        |

## NOTES:

<sup>1. &</sup>quot;X" = Don't Care

<sup>2.</sup> If the "byte count" is less than or equal to the "initial increment", then the current cycle = the first cycle = the last cycle.

<sup>3.</sup> If the number of bytes left is less than or equal to 4, then the next cycle = the last cycle.

<sup>4.</sup> For information regarding byte alignment, refer to Section 6.3.1.

# 4.8 I/O Address Range Decode Support

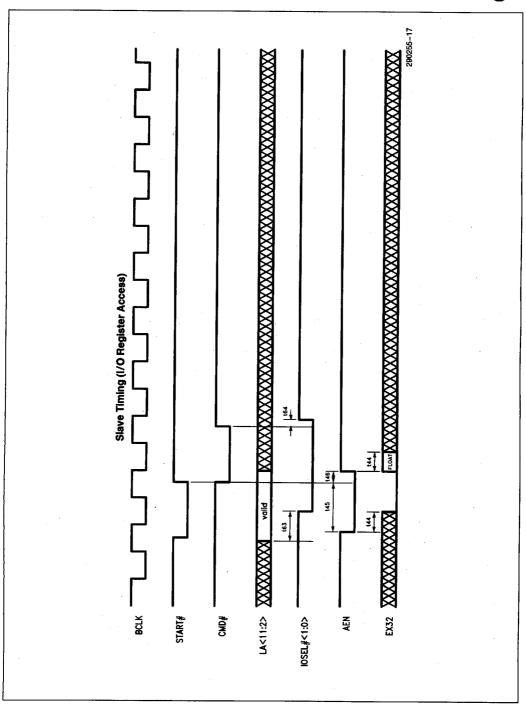

The BMIC provides on-board decoder logic, two I/O select pins (IOSEL<1:0>#), and a set of 8-bit I/O Decode Range registers to support both general I/O decode and expansion board slot specific I/O decode. The BMIC also uses the AEN signal when decoding I/O locations.

The set of I/O Decode registers include two I/O Decode Range Base Address registers and two I/O Decode Range Control registers (refer to Section 8.2.6). The I/O Decode registers are used to define the address ranges of interest to the bus master expansion board. Each IOSEL#<1:0> pin has an associated Control and Base register along with an associated address range as defined by the I/O Decode register set.

Through the I/O Decode Range Control register set, the BMIC can be programmed to respond to a select I/O address range as either an 8-bit or 32-bit EISA device. The only control signal provided by the BMIC to the EISA bus during an I/O decode is the EX32\* signal. The output state of the EX32\* pin on the BMIC will indicate the elected response (low = 32-bit EISA, high = 8-bit EISA). The Control register set controls the size of the I/O decode range, the I/O decode type (slot specific or general I/O), and the I/O decode address latching. The I/O address can be latched by the CMD\* signal (de-pipelined) or merely decoded. By latching the I/O address, the associated IOSEL\* line will remain active a minimum of 5 ns from the rising edge of CMD\*.

The IDOEs do not go active during an IOSEL cycle outside the shared register access space.

The I/O decode range size depends on the value of bits <4:0> in the Control register. Each of these bits masks a corresponding address comparison bit in the Base register. If no bits are masked in the Control register, the BMIC will decode a doubleword address. The bits are masked as follows:

| I/O Control<br>Register | I/O Base Register<br>Bit Masked | EISA Address<br>Bit Masked |

|-------------------------|---------------------------------|----------------------------|

| Bit 0                   | Bit 0                           | IADS2                      |

| Bit 1                   | Bit 1                           | IADS3                      |

| Bit 2                   | Bit 2                           | IADS4                      |

| Bit 3                   | Bit 3                           | IADS5                      |

| Bit 4                   | Bit 4, 5                        | IADS<7:6>                  |

The I/O Decode Range Base Address register contains the address range that is used during the I/O decode address comparison. The following table gives the bits in the I/O Base Address Register and the EISA Address that are used during the comparison:

| I/O Base         | (EISA Add     | ress Bits)  |

|------------------|---------------|-------------|

| Address Register | Slot Specific | General I/O |

| Bit 0            | IADS2         | IADS2       |

| Bit 1            | IADS3         | IADS3       |

| Bit 2            | IADS4         | IADS4       |

| Bit 3            | IADS5         | IADS5       |

| Bit 4            | IADS6         | IADS6       |

| Bit 5            | IADS7         | IADS7       |

| Bit 6            | IADS10        | IADS8       |

| Bit 7            | IADS11        | IADS9       |

If bit 6 in the I/O Decode Range Control register is programmed for General I/O decode, and the two most significant bits in the I/O Decode Range Base Address register are programmed to 0 (IADS<9:8>), I/O decoding for that range will be disabled. This is done to ensure that the I/O address does not conflict with the slot specific address range or the EISA system board address range. The following table summarizes the EISA system I/O address mapping:

| I/Q     |  |

|---------|--|

| Address |  |

| Range   |  |

# (HEX) I/O Range Reserved for

0000-00FF EISA/ISA System Board

0100-03FF General I/O (ISA Expansion Board)

0400-04FF ISP (82357)

0500-07FF General I/O (Alias of 0100h-03FFh)

0800-08FF EISA System Board

0900-0BFF General I/O (Alias of 0100h-03FFh)

0C00-0CFF EISA System Board

0D00-0FFF General I/O (Alias of 0100h-03FFh)

# Slot Specific Range where X = Slot Number

X000-X0FF Slot (X)

X100-X3FF General I/O (Alias of 0100h-03FFh)

X400-X4FF Slot (X)

X500-X7FF General I/O (Alias of 0100h-03FFh)

X800-X8FF Slot (X)

X900-XBFF General I/O (Alias of 0100h-03FFh)

XC00-XCFF Slot (X) (BMIC Registers 0C80h-0CAFh)

XD00-XFFF General I/O (Alias of 0100h-03FFh)

The following is an example of the BMIC programmed for slot specific decode:

I/O Decode Range 0 Control register programmed for (EFh)

|       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| (EFh) | 1     | 1     | 1     | 0     | 1     | 1     | 1     | 1     |

- Bit 7-Respond as a 32-bit EISA slave

- Bit 6-Slot specific decode enabled

- Bit 5—Slot specific address latched by CMD#

- Bit 4—Compare I/O Decode Range 0 Base Address Bits (5) and (4) with EISA address signals IADS7 and IADS6 respectively

- Bit 3—Mask I/O Decode Range 0 Base Address Bit (3)

- Bit 2—Mask I/O Decode Range 0 Base Address Bit (2)

- Bit 1—Mask I/O Decode Range 0 Base Address Bit (1)

- Bit 0—Mask I/O Decode Range 0 Base Address Bit (0)

I/O Decode Range 0 Base Address register programmed for (2-h)

|       |       |       |       |       | IADS5 |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| (2-h) | 0     | 0     | 1     | 0     | _     | _     |       |       |

EISA slot specific address range decoded—X080h through X0BFh where X represents the expansion board slot number

Byte enables IBE<3:0> # and EISA address lines IADS<1:0> are not used during either slot specific or general I/O decode. During slot specific I/O decode, EISA address lines IADS<9:8> must be 0 to ensure that the I/O address does not conflict with the ISA general I/O address range (0100h-03FFh).

IOSEL0# and EX32# will be driven low by the BMIC if addresses X080h through X0BFh are present on the EISA bus.

AEN is used as part of the decode and must be negated low when a response from the BMIC is required.

# 5.0 TRANSFER BUFFER INTERFACE

## 5.1 Transfer Buffer Interface Signals

The Transfer Buffer Interface portion of the BMIC provides the signals essential for interfacing to the expansion board as required for EISA-to-expansion

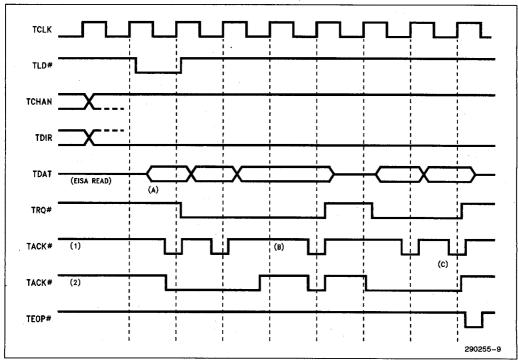

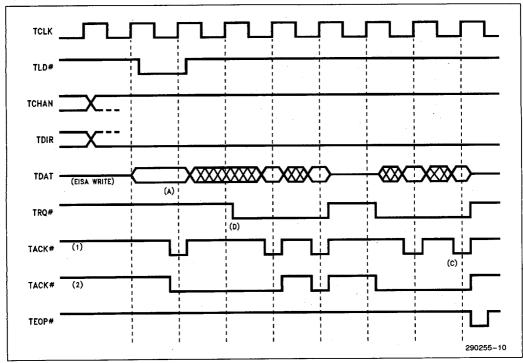

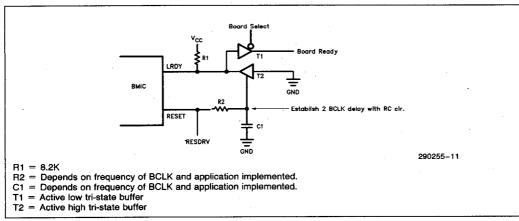

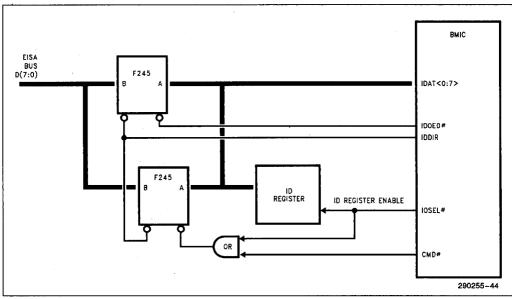

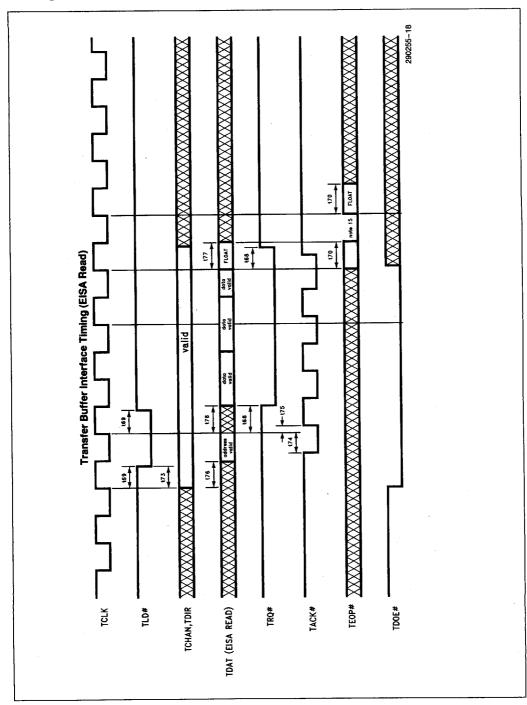

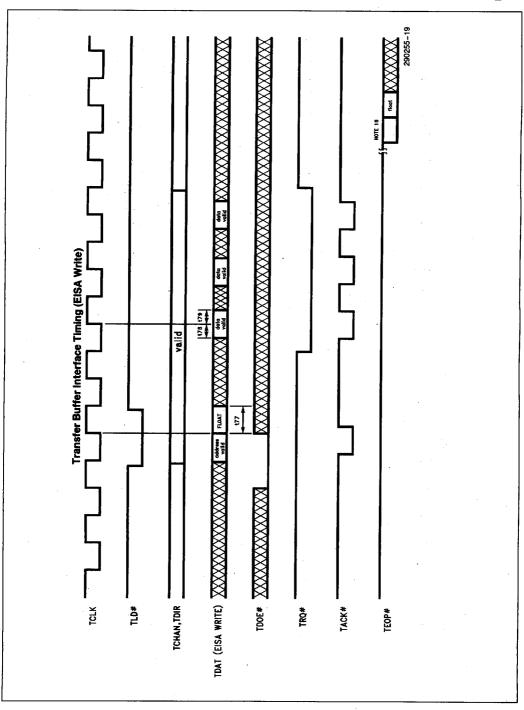

board and expansion board-to-EISA burst data transfers. The Transfer Buffer Interface is designed to interface to a high speed transfer buffer and simple logic similar to that used in traditional DMA designs. This interface includes a 16-bit data bus, one clock input, and seven control signals.