(Column Driver)

# **HITACHI**

ADE-207-279(Z) '99.9 Rev. 0.0

## **Description**

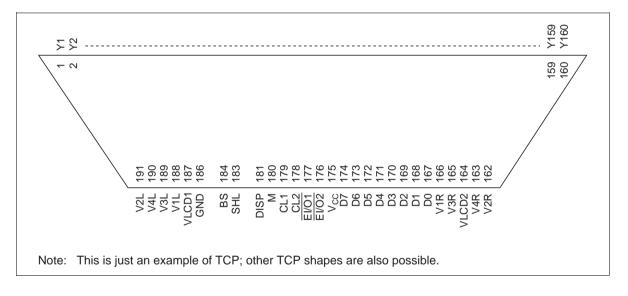

The HD66110ST, the column driver for a large liquid crystal display (LCD) panel, features as many as 160 LCD outputs powered by 160 internal LCD drive circuits, and a high duty cycle. This device can interface to various LCD controllers by using an internal automatic chip enable signal generator. Its strip shape enables a slim tape carrier package (TCP).

#### **Features**

- 191-pin TCP

- CMOS fabrication process

- High voltage

- LCD drive: 14 to 40V

- · High speed

- Maximum clock speed:

- 12 MHz ( $V_{CC} = 4.5 \text{ to } 5.5V$ )

- 10 MHz ( $V_{CC} = 2.7 \text{ to } 5.5 \text{V}$ )

- 4- and 8-bit data bus interface

- Display off function

- Standby function

## **Ordering Information**

| Type No.    | Outer lead pitch (μm) |  |

|-------------|-----------------------|--|

| HD66110STB2 | 92                    |  |

| HD66110STB4 | 80                    |  |

| HD66110STB5 | 180                   |  |

| HD66110STB8 | 200                   |  |

| HD66110STC0 | 220                   |  |

| HD66110STC1 | 240                   |  |

| HD66110STC2 | 260                   |  |

| HD66110STC3 | 280                   |  |

Note: The details of TCP pattern are shown in "The Information of TCP."

## **Pin Arrangement**

# **Pin Description**

| Symbol          | Pin No. Pin Name Input/Output |                        | Input/Output | Classification   |

|-----------------|-------------------------------|------------------------|--------------|------------------|

| V <sub>cc</sub> | 175                           | V <sub>cc</sub>        | _            | Power supply     |

| GND             | 186                           | GND                    | _            | Power supply     |

| VLCD1           | 187                           | VLCD1                  | <del></del>  | Power supply     |

| VLCD2           | 164                           | VLCD2                  | <del>_</del> | Power supply     |

| V1R             | 166                           | V1R                    | Input        | Power supply     |

| V2R             | 162                           | V2R                    | Input        | Power supply     |

| V3R             | 165                           | V3R                    | Input        | Power supply     |

| V4R             | 163                           | V4R                    | Input        | Power supply     |

| V1L             | 188                           | V1L                    | Input        | Power supply     |

| V2L             | 191                           | V2L                    | Input        | Power supply     |

| V3L             | 189                           | V3L                    | Input        | Power supply     |

| V4L             | 190                           | V4L                    | Input        | Power supply     |

| CL1             | 179                           | Clock 1                | Input        | Control signal   |

| CL2             | 178                           | Clock 2                | Input        | Control signal   |

| М               | 180                           | M                      | Input        | Control signal   |

| D0-D7           | 167–174                       | Data 0-data 7          | Input        | Control signal   |

| SHL             | 183                           | Shift left             | Input        | Control signal   |

| EI/O1, EI/O2    | 177, 176                      | Enable IO1, enable IO2 | Input/output | Control signal   |

| DISP            | 181                           | Display off            | Input        | Control signal   |

| BS              | 184                           | Bus select             | Input        | Control signal   |

| Y1-Y160         | 1–160                         | Y1-Y160                | Output       | LCD drive output |

**HITACHI**

#### Pin Functions

#### **Power Supply**

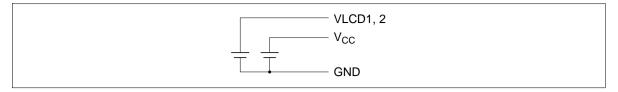

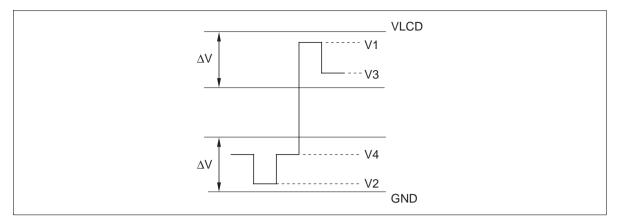

$V_{CC}$ , VLCD1, VLCD2, GND:  $V_{CC}$ -GND supplies power to the internal logic circuits. VLCD-GND supplies power to the LCD drive circuits. See Figure 1.

V1R, V1L, V2R, V2L, V3R, V3L, V4R, V4L: Supply different levels of power to drive the LCD. V1 and V2 are selected levels. and V3 and V4 are non-selected levels.

#### **Control Signals**

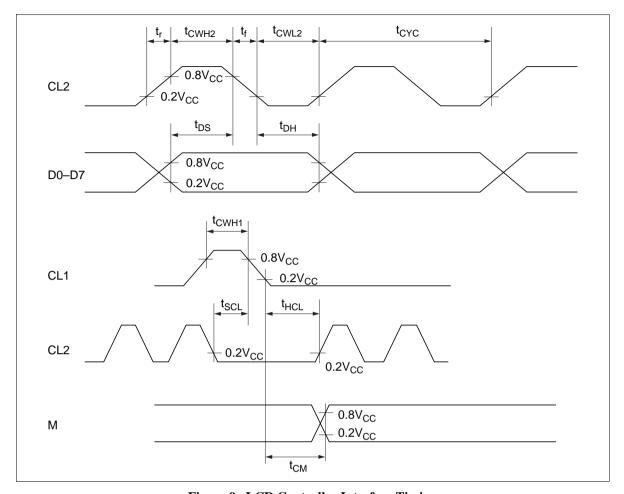

**CL1:** Inputs display data latch pulses for latch circuit 2. Latch circuit 2 latches display data input from latch circuit 1, and outputs LCD drive signals corresponding to the latched data, both at the falling edge of each CL1 pulse.

**CL2:** Inputs display data latch pulses for latch circuit 1. Latch circuit 1 latches display data input via D0–D7 at the falling edge of each CL2 pulse.

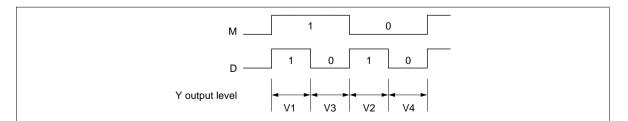

M: Changes LCD drive outputs to AC.

**D0–D7:** Input display data. High-voltage level ( $V_{CC}$  level) of data corresponds to a selected level and turns an LCD pixel on, and low-voltage level (GND level) data corresponds to a non-selected level and turns an LCD pixel off.

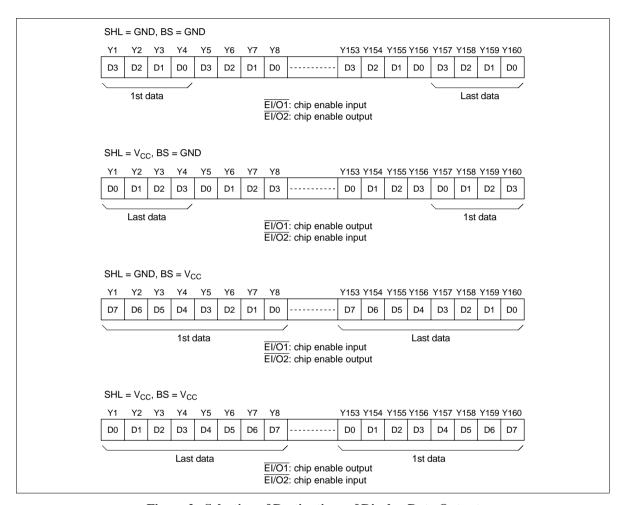

**SHL:** Shifts the destinations of display data output, and determines which chip enable pin ( $\overline{\text{EI/O1}}$ ) or  $\overline{\text{EI/O2}}$ ) is an input and which is an output. See Figure 2.

$\overline{\text{EI/O1}}$ ,  $\overline{\text{EI/O2}}$ : If SHL is GND level,  $\overline{\text{EI/O1}}$  inputs the chip enable signal, and  $\overline{\text{EI/O2}}$  outputs the signal. If SHL is  $V_{CC}$  level,  $\overline{\text{EI/O1}}$  outputs the chip enable signal, and  $\overline{\text{EI/O2}}$  inputs the signal. The chip enable input pin of the first HD66110RT must be grounded, and those of the other HD6611STs must be connected to the chip enable output pin of the previous HD66110RT. The chip enable output pin of the last HD66110RT must be open.

**DISP:** A low DISP sets LCD drive outputs Y1–Y160 to V2 level.

**BS:** Selects either the 4-bit or 8-bit display data bus interface. If BS is  $V_{CC}$  level, the 8-bit bus is selected, and if BS is GND level, the 4-bit bus is selected. In 4-bit bus mode, data is latched via D0–D3; D4–D7 must be grounded.

#### **LCD Drive Output**

**Y1–Y160:** Each Y outputs one of the four voltage levels V1, V2, V3, or V4, depending on a combination of the M signal and display data levels. See Figure 3.

Figure 1 Power Supply for Logic and LCD Drive Circuits

Figure 2 Selection of Destinations of Display Data Output

Figure 3 Selection of LCD Drive Output Level

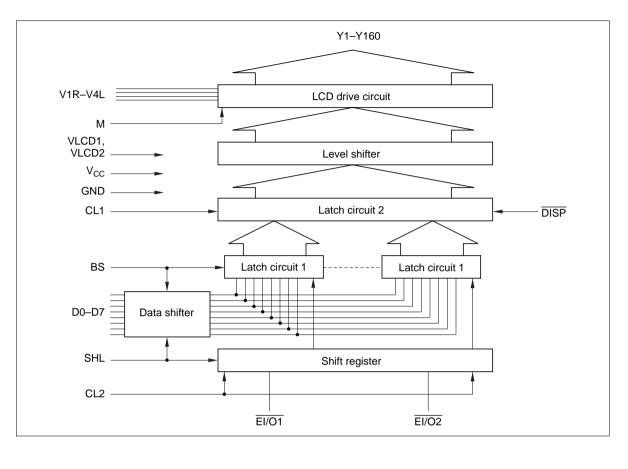

#### **Block Functions**

#### **LCD Drive Circuit**

The 160-bit LCD drive circuit generates four voltage levels V1, V2, V3, and V4, for driving an LCD panel. One of the four levels is output to the corresponding Y pin, depending on a combination of the M signal and the data in the latch circuit 2.

#### **Level Shifter**

The level shifter changes 5-V signals into high-voltage signals for the LCD drive circuit.

#### Latch Circuit 2

160-bit latch circuit 2 latches data input from latch circuit 1, and outputs the latched data to the level shifter, both at the falling edge of each clock 1 (CL1) pulse.

#### Latch Circuit 1

160-bit latch circuit 1 latches 4-bit or 8-bit parallel data input via the D0 to D7 pins at the timing generated by the shift register.

### **Shift Register**

The 40-bit shift register generates and outputs data latch signals for latch circuit 1 at the falling edge of each clock 2 (CL2) pulse.

#### **Data Shifter**

The data shifter shifts the destination of display data output, when necessary.

## **Block Diagram**

## Comparison of HD66110RT with the HD66110ST

| Item         |                                         | HD66110RT   | HD66110ST |  |

|--------------|-----------------------------------------|-------------|-----------|--|

| LCD drive vo | Itage range                             | 28 to 40V   | 14 to 40V |  |

| Speed        | $V_{cc} = 4.5 \text{ to } 5.5 \text{V}$ | 12 MHz      | 12 MHz    |  |

|              | $V_{cc} = 2.7 \text{ to } 4.5 \text{V}$ | _           | 10 MHz    |  |

| Number of p  | oins (power supply)                     | 26 (7)      | 31 (12)   |  |

| Voltage supp | ly pin format                           | Single side | Dual side |  |

Figure 4  $\,t_{HCL}$  Definitions of the HD66110RT and HD66110ST

### **Operation Timing**

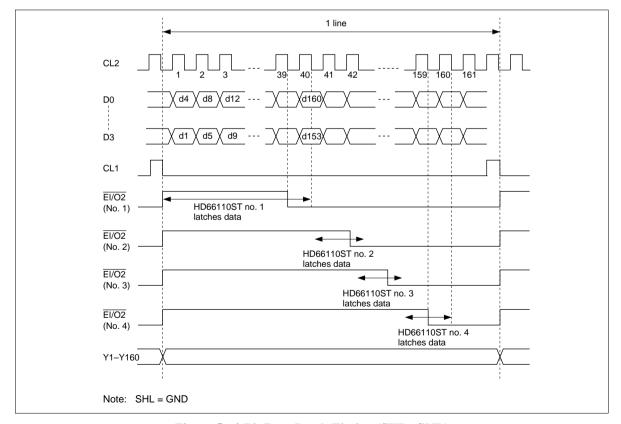

#### 4-Bit Bus Mode (BS = GND)

Figure 5 shows 4-bit data latch timing when SHL = GND, that is, the  $\overline{EI/O1}$  pin is a chip enable input and  $\overline{EI/O2}$  pin is a chip enable output. When SHL =  $V_{CC}$ , the  $\overline{EI/O1}$  pin is a chip enable output and  $\overline{EI/O2}$  pin is a chip enable input.

When a low chip enable signal is input via the  $\overline{EI/O1}$  pin, the HD66110RT is first released from data standby state, and, at the falling edge of the following CL2 pulse, it is released entirely from standby state and starts latching data.

It simultaneously latches 4 bits of data at the falling edge of each CL2 pulse. When it has latched 156 bits of data, it sets the  $\overline{\text{EI/O2}}$  signal low. When it has latched 160 bits of data, it automatically stops and enters standby state, initiating the next HD66110RT, as long as its  $\overline{\text{EI/O2}}$  pin is connected to the  $\overline{\text{EI/O1}}$  pin of the next HD66110RT.

The HD66110RTs output one line of data from the Y1–Y160 pins at the falling edge of each CL1 pulse. Data d1 is output from Y1, and d160 from Y160 when SHL = GND, and d1 is output from Y160, and d160 from Y1 when SHL =  $V_{CC}$ .

Figure 5 4-Bit Data Latch Timing (SHL=GND)

HITACHI

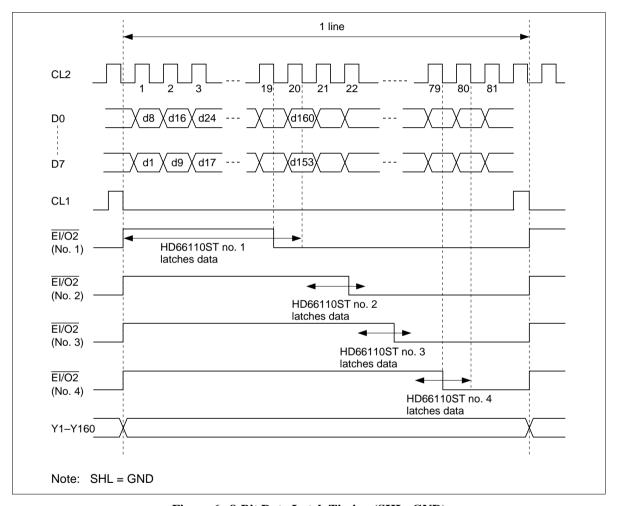

#### 8-Bit Bus Mode (BS = $V_{CC}$ )

Figure 6 shows 8-bit data latch timing when SHL = GND, that is, the  $\overline{EI/O1}$  pin is a chip enable input and  $\overline{EI/O2}$  pin is a chip enable output.

When SHL =  $V_{CC}$ , the  $\overline{EI/O1}$  pin is a chip enable output and  $\overline{EI/O2}$  pin is a chip enable input.

The operation is the same as that in 4-bit bus mode except that 8 bits of data are latched simultaneously.

Figure 6 8-Bit Data Latch Timing (SHL=GND)

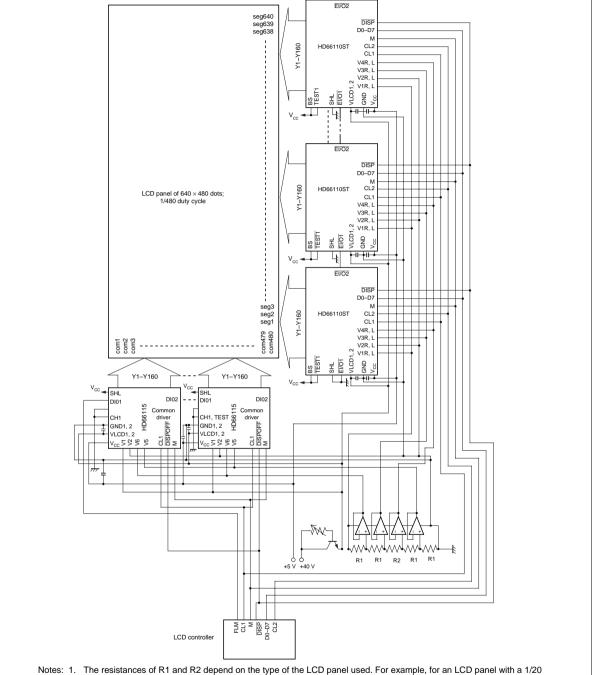

## **Application Example**

- 2. To stabilize the power supply, place two 0.1- $\mu$ F capacitors near each LCD driver: one between the V $_{CC}$  and GND pins, and the other between the VLCD and GND pins.

- 3. The load must be less than 30 pF between the  $\overline{\text{EI/O2}}$  and  $\overline{\text{EI/O1}}$  connections of HD66110STs.

## **Absolute Maximum Ratings**

| Item                                        | Symbol           | Rating                   | Unit | Notes   |

|---------------------------------------------|------------------|--------------------------|------|---------|

| Power supply voltage for logic circuits     | $V_{cc}$         | -0.3 to +7.0             | V    | 1, 5    |

| Power supply voltage for LCD drive circuits | VLCD             | -0.3 to +42              | V    | 1, 2, 5 |

| Input voltage 1                             | VT1              | $-0.3$ to $V_{cc}$ + 0.3 | V    | 1, 3    |

| Input voltage 2                             | VT2              | -0.3 to VLCD + 0.3       | V    | 1, 4    |

| Operating temperature                       | T <sub>opr</sub> | -30 to +75               | °C   |         |

| Storage temperature                         | T <sub>stg</sub> | –55 to +110              | °C   |         |

Notes: 1. The reference point is GND (0V).

- 2. Indicates the voltage between GND and VLCD.

- 3. Applies to input pins for logic circuits, that is, control signal pins.

- 4. Applies to input pins for LCD drive level voltages, that is, V1–V4 pins.

- 5. Power should be applied to  $V_{cc}$ –GND first, and then VLCD–GND. It should be disconnected in the reverse order.

- 6. If the LSI is used beyond the absolute maximum ratings, it may be permanently damaged. It should always be used within its electrical characteristics in order to prevent malfunctioning or degradation of reliability.

## **Electrical Characteristics**

DC Characteristics 1 ( $V_{CC}$  = 2.7 to 4.5V, VLCD–GND = 14 to 40V, and  $T_a$  = -30 to +75°C, unless otherwise noted)

| Item                    | Symbol           | Pins | Min                  | Max                 | Unit | Condition                                                                                                                         | Notes |

|-------------------------|------------------|------|----------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|-------|

| Input high voltage      | VIH              | 1    | $0.8 \times V_{cc}$  | V <sub>cc</sub>     | V    |                                                                                                                                   |       |

| Input low voltage       | VIL              | 1    | 0                    | $0.2 \times V_{CC}$ | V    |                                                                                                                                   |       |

| Output high voltage     | VOH              | 2    | V <sub>cc</sub> -0.4 | _                   | V    | $I_{OH} = -0.4 \text{ mA}$                                                                                                        |       |

| Output low voltage      | VOL              | 2    | _                    | 0.4                 | V    | I <sub>OL</sub> = 0.4 mA                                                                                                          |       |

| Vi-Yj on resistance     | $R_{ON}$         | 3    | _                    | 3.0                 | kΩ   | $I_{ON} = 150 \mu A$                                                                                                              | 1     |

| Input leakage current 1 | I <sub>IL1</sub> | 1    | -5.0                 | 5.0                 | μΑ   | $VIN = V_{CC}$ to GND                                                                                                             |       |

| Input leakage current 2 | I <sub>IL2</sub> | 4    | -100                 | 100                 | μΑ   | VIN = VLCD to GND                                                                                                                 |       |

| Current consumption 1   | I <sub>cc</sub>  | _    | _                    | 2.2                 | mA   | $\begin{split} f_{\text{CL2}} &= 10 \text{ MHz} \\ f_{\text{CL1}} &= 28 \text{ kHz} \\ V_{\text{CC}} &= 3.0 \text{V} \end{split}$ | 2     |

| Current consumption 2   | I <sub>LCD</sub> | _    | _                    | 3.0                 | mA   | Same as above                                                                                                                     | 2     |

| Current consumption 3   | I <sub>ST</sub>  | _    | _                    | 0.3                 | mA   | Same as above                                                                                                                     | 2, 3  |

Pins and notes on next page.

# DC Characteristics 2 ( $V_{CC}$ = 5V $\pm$ 10%, VLCD–GND = 14 to 40V, and $T_a$ = -30 to +75°C, unless otherwise noted)

| Item                    | Symbol           | Pins | Min                  | Max                  | Unit | Condition                                              | Notes |

|-------------------------|------------------|------|----------------------|----------------------|------|--------------------------------------------------------|-------|

| Input high voltage      | VIH              | 1    | $0.8 \times V_{cc}$  | V <sub>cc</sub>      | V    |                                                        |       |

| Input low voltage       | VIL              | 1    | 0                    | 0.2 ×V <sub>cc</sub> | V    |                                                        |       |

| Output high voltage     | VOH              | 2    | V <sub>cc</sub> -0.4 | _                    | V    | $I_{OH} = -0.4 \text{ mA}$                             |       |

| Output low voltage      | VOL              | 2    | _                    | 0.4                  | V    | I <sub>OL</sub> = 0.4 mA                               |       |

| Vi–Yj on resistance     | R <sub>on</sub>  | 3    | _                    | 3.0                  | kΩ   | I <sub>ON</sub> = 150 μA                               | 1     |

| Input leakage current 1 | I <sub>IL1</sub> | 1    | -5.0                 | 5.0                  | μΑ   | VIN = V <sub>CC</sub> to GND                           |       |

| Input leakage current 2 | I <sub>IL2</sub> | 4    | -100                 | 100                  | μΑ   | VIN = VLCD to GND                                      |       |

| Current consumption 1   | I <sub>cc</sub>  | _    | _                    | 5.0                  | mA   | f <sub>CL2</sub> = 12 MHz<br>f <sub>CL1</sub> = 28 kHz | 2     |

| Current consumption 2   | I <sub>LCD</sub> | _    | _                    | 3.0                  | mA   | Same as above                                          | 2     |

| Current consumption 3   | I <sub>ST</sub>  | _    | _                    | 0.7                  | mA   | Same as above                                          | 2, 3  |

Pins:

- 1. CL1, CL2, M, SHL, BS, EI/O1, EI/O2, DISP, D0-D7

- 2. EI/O1, EI/O2

- 3. Y1-Y160, V1-4

- 4. V1-V4

Notes: 1. Indicates the resistance between one pin from Y1–Y160 and another pin from V1–V4 when load current is applied to the Y pin; defined under the following conditions.

VLCD-GND = 40V

$V1, V3 = VLCD - \{1/20 (VLCD-GND)\}$

$V2, V4 = GND + \{1/20 (VLCD-GND)\}$

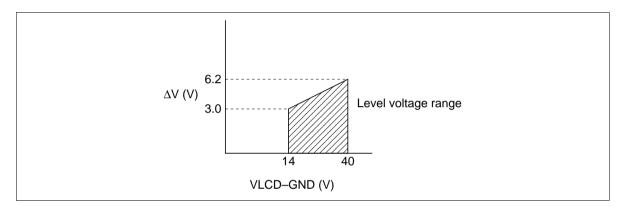

V1 and V3 should be near VLCD level, and V2 and V4 should be near GND level (Figure 7). All voltage must be within  $\Delta V$ .  $\Delta V$  is the range within which RON, the LCD drive circuits' output impedance, is stable. Note that  $\Delta V$  depends on power supply voltage VLCD–GND (Figure 8).

- 2. Input and output current is excluded. When a CMOS input is floating, excess current flows from the power supply through the input circuit. To avoid this, VIH and VIL must be held to  $V_{cc}$  and GND levels, respectively.

- 3. Applies to standby mode.

Figure 7 Relation between Driver Output Waveform and Level Voltages

Figure 8 Relation between VLCD–GND and  $\Delta V$

# AC Characteristics 1 ( $V_{CC}$ = 2.7 to 4.5V, VCD–GND = 14 to 40V, and $T_a$ = -30 to +75°C, unless otherwise noted)

| Item                     | Symbol            | Pins       | Min | Max | Unit | Notes |

|--------------------------|-------------------|------------|-----|-----|------|-------|

| Clock cycle time         | t <sub>CYC</sub>  | CL2        | 100 | _   | ns   |       |

| Clock high-level width 1 | t <sub>CWH2</sub> | CL2        | 37  | _   | ns   |       |

| Clock low-level width    | t <sub>CWL2</sub> | CL2        | 37  | _   | ns   |       |

| Clock high-level width 2 | t <sub>CWH1</sub> | CL1        | 50  | _   | ns   |       |

| Clock setup time         | t <sub>SCL</sub>  | CL1, CL2   | 100 | _   | ns   |       |

| Clock hold time          | t <sub>HCL</sub>  | CL1, CL2   | 100 | _   | ns   |       |

| Clock rise time          | t <sub>r</sub>    | CL1, CL2   | _   | 50  | ns   | 2     |

| Clock fall time          | t <sub>f</sub>    | CL1, CL2   | _   | 50  | ns   | 2     |

| Data setup time          | t <sub>DS</sub>   | D0-D7, CL2 | 35  | _   | ns   |       |

| Data hold time           | t <sub>DH</sub>   | D0-D7, CL2 | 35  | _   | ns   |       |

| M phase difference time  | t <sub>CM</sub>   | M, CL1     | _   | 300 | ns   |       |

Notes: 1. The load must be less than 30 pF between  $\overline{\text{EI/O2}}$  and  $\overline{\text{EI/O1}}$  connections of HD66110STs.

# AC Characteristics 2 ( $V_{CC}$ = 5 ± 10%, VLCD–GND = 14 to 40V, and $T_a$ = -30 to +75°C, unless otherwise noted)

| Item                     | Symbol            | Pins       | Min | Max | Unit | Notes |

|--------------------------|-------------------|------------|-----|-----|------|-------|

| Clock cycle time         | t <sub>cvc</sub>  | CL2        | 83  | _   | ns   |       |

| Clock high-level width 1 | t <sub>CWH2</sub> | CL2        | 20  | _   | ns   |       |

| Clock low-level width    | t <sub>CWL2</sub> | CL2        | 20  | _   | ns   |       |

| Clock high-level width 2 | t <sub>CWH1</sub> | CL1        | 50  | _   | ns   |       |

| Clock setup time         | t <sub>SCL</sub>  | CL1, CL2   | 100 | _   | ns   |       |

| Clock hold time          | t <sub>HCL</sub>  | CL1, CL2   | 100 | _   | ns   |       |

| Clock rise time          | t <sub>r</sub>    | CL1, CL2   | _   | 50  | ns   | 2     |

| Clock fall time          | t <sub>f</sub>    | CL1, CL2   | _   | 50  | ns   | 2     |

| Data setup time          | t <sub>DS</sub>   | D0-D7, CL2 | 10  | _   | ns   |       |

| Data hold time           | t <sub>DH</sub>   | D0-D7, CL2 | 10  | _   | ns   |       |

| M phase difference time  | t <sub>CM</sub>   | M, CL1     | _   | 300 | ns   |       |

Notes: 1. The load must be less than 30 pF between  $\overline{\text{El/O2}}$  and  $\overline{\text{El/O1}}$  connections of HD66110STs.

<sup>2.</sup>  $t_r$ ,  $t_f < (t_{cyc} - t_{CWH2} - t_{CWL2})/2$  and  $t_r$ ,  $t_f \le 50$  ns

<sup>2.</sup>  $t_r$ ,  $t_f$  <  $(t_{cyc}$ - $t_{CWH2}$ - $t_{CWL2}$ )/2 and  $t_r$ ,  $t_f \le 50$  ns

Figure 9 LCD Controller Interface Timing

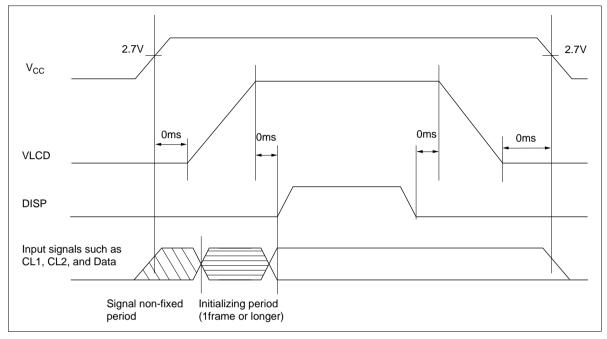

#### Notes on Power-On/Off of the LCD Driver

To prevent an LCD driver display error at power on/off, the sequence for power-on signal activation must be as follows (see Figure 10):

Figure 10 Sequence of Power-On/Off

#### At Power On

- (1) Power on  $V_{CC}$ . At this time, input 0 to the  $\overline{DISP}$  pin.

- (2) Display-off function forces the LCD driver to output a V2 level (lowest level).

- (3) Display-off function takes priority even if the input signal status becomes irregular immediately after  $V_{\rm CC}$  power-on.

- (4) Input the specified signals to initialize registers of the LCD driver. Its period must be 1 frame or longer.

- (5) Set the  $\overline{\text{DISP}}$  level to 1 to cancel display-off function after steps (1) to (4). At this time, VLCD and each V pin input must be at the specified levels.

#### At Power Off

Basically, the power-off procedure is the reverse of the power-on procedure.

- (1) Set the  $\overline{\text{DISP}}$  level to 0.

- (2) Lower LCD driver power supply to 0V

- (3) Lower  $V_{\text{CC}}$  and each input signals to 0V

At this time, each V pin input must be at 0V. Display-off function stops when  $V_{\rm CC}$  falls to 0V, and therefore, the LCD driver may output a level other than V2 (lowest level). As a result, a display error may be caused at power-off or power-on.

HITACHI

### LCD Driver LSI Power Supply Pin Connection

A feature of the LCD driver is the LCD drive power supply. As the number of pixel drives per LSI increases, so does the voltage and number of outputs.

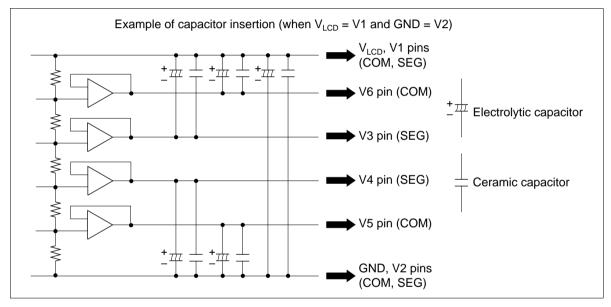

Consequently, if multi-output CMOS circuits are switched simultaneously, a wiring voltage drop may occurs due to transient currents, and the potential between the LCD drive circuit power supply  $(V_{LCD})$  and LCD drive level power supplies (V1, V6, and V3) or GND and the LCD level power supplies  $(V2, \overline{V5}, \text{ and } V4)$  may be inverted, resulting in latchup breakdown. To prevent this, it is recommended that, when designing the LCD drive power supply and board power supply wiring, the power supply wiring be designed as low-impedance and capacitors be inserted in the wiring between  $V_{LCD}$  and V1, V3, V6, and V2, V4, V5 and GND. In set evaluation, it is recommended that a check  $\overline{be}$  carried out to confirm that there is no inversion of the LCD drive power supply and level power supplies in the period between when the LCD drive power supply is turned on and turned off.

Figure 11 Example of Capacitor Insertion

#### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# HITACHI

#### Hitachi. Ltd.

Semiconductor & Integrated Circuits. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

URL NorthAmerica : http:semiconductor.hitachi.com/ Europe : http://www.hitachi-eu.com/hel/ecg

Asia (Singapore)

Asia (Taiwan)

Asia (HongKong)

: http://www.has.hitachi.com.sg/grp3/sicd/index.htm

Asia (HongKong)

: http://www.hitachi.com.tw/E/Product/SICD\_Frame.htm

Japan : http://www.hitachi.co.jp/Sicd/indx.htm

#### For further information write to:

Hitachi Semiconductor (America) Inc. 179 East Tasman Drive, San Jose,CA 95134 Tel: <1> (408) 433-1990 Fax: <1>(408) 433-0223 Hitachi Europe GmbH Electronic components Group Dornacher Straße 3 D-85622 Feldkirchen, Munich Germany

Tel: <49> (89) 9 9180-0 Fax: <49> (89) 9 29 30 00

Hitachi Europe Ltd. Electronic Components Group. Whitebrook Park Lower Cookham Road Maidenhead Berkshire SL6 8YA, United Kingdom

Tel: <44> (1628) 585000 Fax: <44> (1628) 778322 Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 049318 Tel: 535-2100 Fax: 535-1533

Hitachi Asia Ltd. Taipei Branch Office 3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (10

Tun-Hwa North Road, Taipei (105) Tel: <886> (2) 2718-3666 Fax: <886> (2) 2718-8180 Hitachi Asia (Hong Kong) Ltd. Group III (Electronic Components) 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Tsim Sha Tsui, Kowloon, Hong Kong

Tel: <852> (2) 735 9218 Fax: <852> (2) 730 0281 Telex: 40815 HITEC HX

Copyright © Hitachi, Ltd., 1998. All rights reserved. Printed in Japan.