# HN28F101 Series

131072-word × 8-bit CMOS Flash Memory

**HITACHI**

ADE-203-122J (Z)

Rev. 10.0

Nov. 15, 1996

## Description

The Hitachi HN28F101 is a 131072-word × 8-bit CMOS flash Memory, realizing on-board programming. It programs or erases data with only on-board power supply (12 V  $V_{PP}$  supply/5 V  $V_{CC}$  supply). It programs data with fast programming algorithm by command inputs. It has two types of erase algorithm : automatic erase and fast erase by command inputs. Automatic erase function can erase data automatically without external control only by inputting trigger pulse and inform erase completion to CPU by status polling. The HN28F101 can control programming/erase algorithm externally.

## Features

- On-board power supply ( $V_{CC}/V_{PP}$ )

- $V_{CC} = 5 \text{ V} \pm 10\%$

- $V_{PP} = V_{SS}$  to  $V_{CC}$  (Read)

- $V_{PP} = 12.0 \text{ V} \pm 0.6 \text{ V}$  (Erase/Program)

- Fast access time

- 120 ns/150 ns/200 ns (max)

- Programming function

- Byte programming

- Programming time: 25  $\mu\text{s}$  typ/byte

- Address, data, control latch function

- On-board automatic erase function

- Chip erase

- Erase time: 1 s typ

- Address, data, control latch function

- Status polling function

- Low power dissipation

- $I_{CC} = 10 \text{ mA}$  typ (Read)

- $I_{CC} = 20 \mu\text{A}$  max (Standby)

- $I_{PP} = 30 \text{ mA}$  typ (Auto erase/Program)

- $I_{PP} = 20 \mu\text{A}$  max (Read/Standby)

# HN28F101 Series

- Erasing endurance: 10,000 times

- Pin arrangement: 32-pin JEDEC standard

- Package

- 32-pin SOP

- 32-pin TSOP

## Ordering Information

| Type No.      | Access Time | Package                         |

|---------------|-------------|---------------------------------|

| HN28F101FP-12 | 120 ns      | 32-pin plastic SOP (FP-32D)     |

| HN28F101FP-15 | 150 ns      |                                 |

| HN28F101FP-20 | 200 ns      |                                 |

| HN28F101T-12  | 120 ns      | 32-pin plastic TSOP (TFP-32DA)  |

| HN28F101T-15  | 150 ns      |                                 |

| HN28F101T-20  | 200 ns      |                                 |

| HN28F101R-12  | 120 ns      | 32-pin plastic TSOP (TFP-32DAR) |

| HN28F101R-15  | 150 ns      |                                 |

| HN28F101R-20  | 200 ns      |                                 |

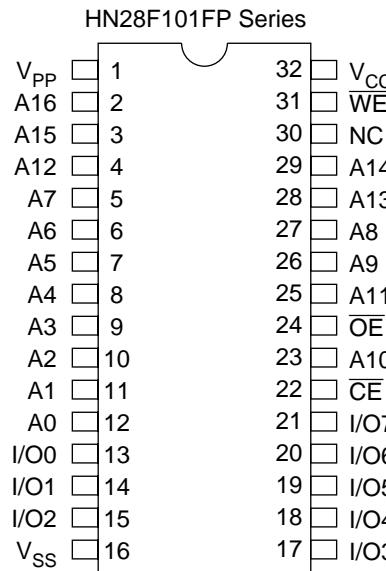

## Pin Arrangement

(Top view)

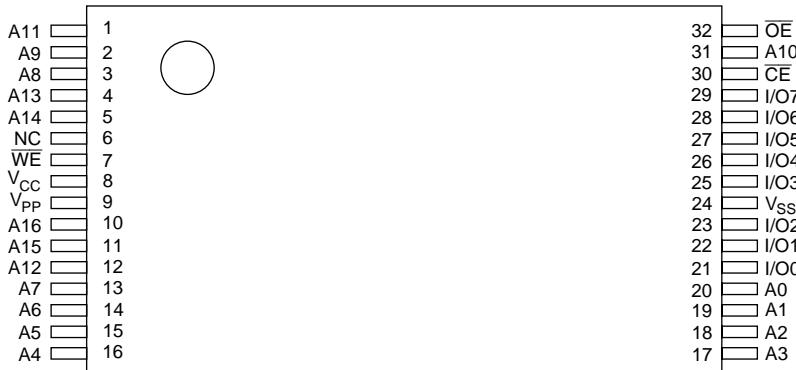

## Pin Arrangement (cont)

## HN28F101T Series

(Top view)

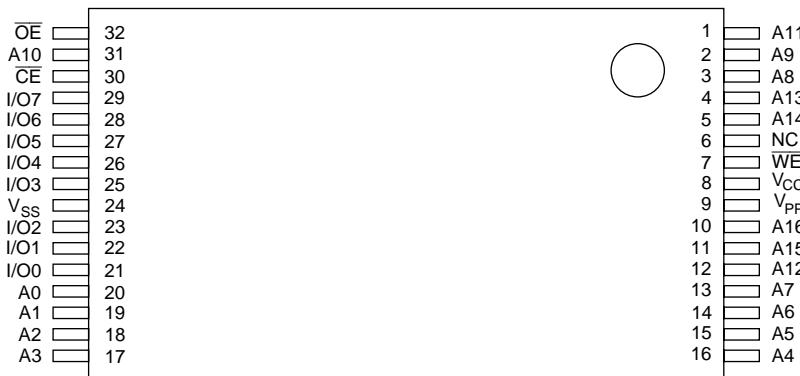

## HN28F101R Series

(Top view)

## Pin Description

| Pin Name        | Function                 |

|-----------------|--------------------------|

| A0-A16          | Address                  |

| I/O0-I/O7       | Input/output             |

| CE              | Chip enable              |

| OE              | Output enable            |

| WE              | Write enable             |

| V <sub>CC</sub> | Power supply             |

| V <sub>PP</sub> | Programming power supply |

| V <sub>SS</sub> | Ground                   |

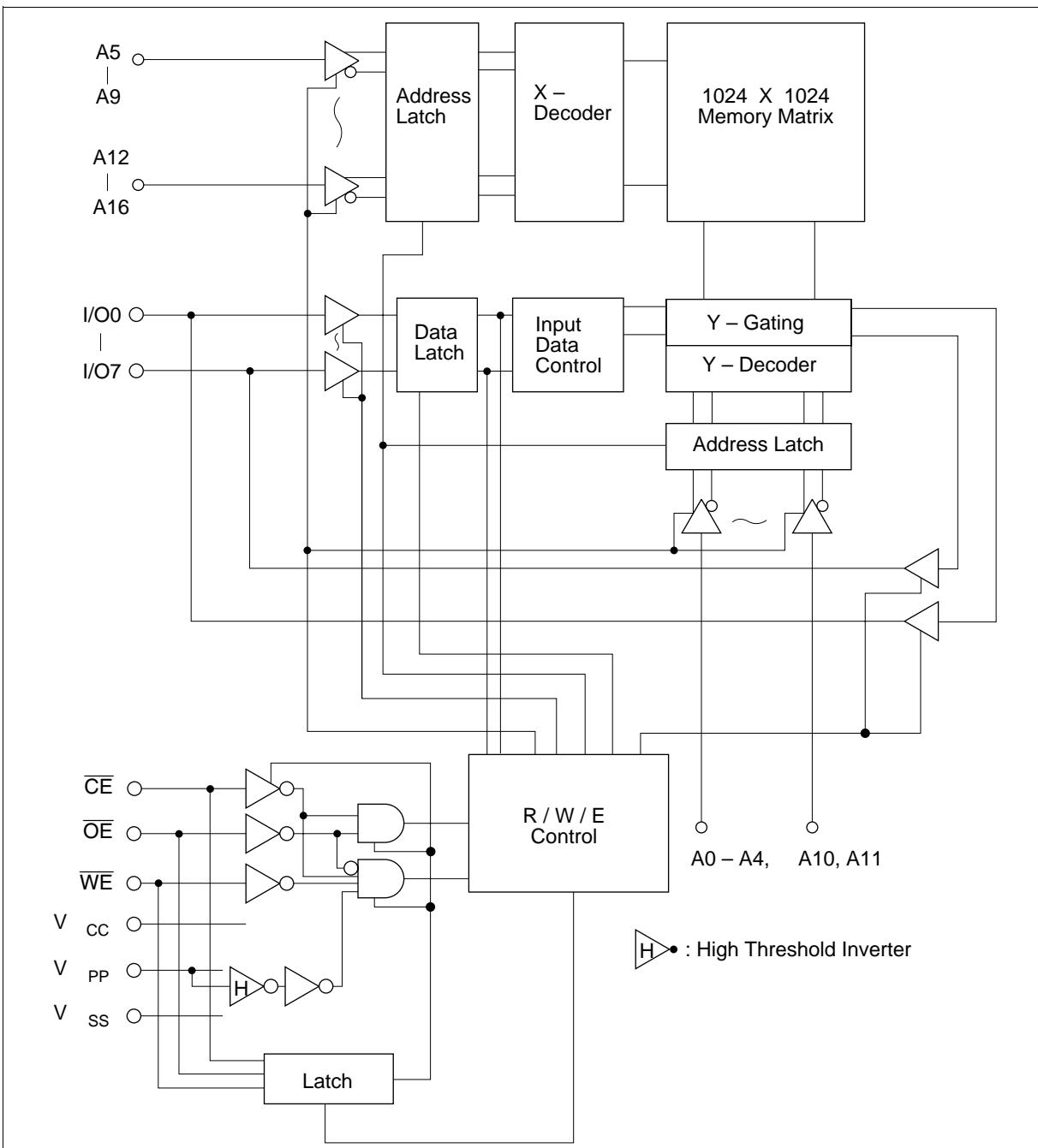

## Block Diagram

## Mode Selection

| Mode            | SOP, TSOP                | Pin           |                 |                 |                 |             |                                          |

|-----------------|--------------------------|---------------|-----------------|-----------------|-----------------|-------------|------------------------------------------|

|                 |                          | $V_{PP}$      | $\overline{CE}$ | $\overline{OE}$ | $\overline{WE}$ | A9          | I/O0 – I/O7                              |

|                 |                          | (1)<br>(9)    | (22)<br>(30)    | (24)<br>(32)    | (31)<br>(7)     | (26)<br>(2) | (13 – 15, 17 – 21)<br>(21 – 23, 25 – 29) |

| Read            | Read                     | $V_{CC}^{*6}$ | $V_{IL}$        | $V_{IL}$        | $V_{IH}$        | A9          | Dout                                     |

|                 | Output disable           | $V_{CC}$      | $V_{IL}$        | $V_{IH}$        | $V_{IH}$        | X           | High-Z                                   |

|                 | Standby                  | $V_{CC}$      | $V_{IH}$        | X               | X               | X           | High-Z                                   |

|                 | Identifier <sup>*1</sup> | $V_{CC}$      | $V_{IL}$        | $V_{IL}$        | $V_{IH}$        | $V_H^{*2}$  | ID                                       |

| Command program | Read <sup>*3,*5</sup>    | $V_{PP}$      | $V_{IL}$        | $V_{IL}$        | $V_{IH}$        | A9          | Dout                                     |

|                 | Output disable           | $V_{PP}$      | $V_{IL}$        | $V_{IH}$        | $V_{IH}$        | X           | High-Z                                   |

|                 | Standby                  | $V_{PP}$      | $V_{IH}$        | X               | X               | X           | High-Z                                   |

|                 | Write <sup>*4</sup>      | $V_{PP}$      | $V_{IL}$        | $V_{IH}$        | $V_{IL}$        | A9          | Din                                      |

Notes:

1. Device identifier code can be output in command programming mode. Refer to the table of command address and data input.

2.  $V_H: 11.5 \leq V_H \leq 12.5V$ .

3. Data can be read when 12 V is applied to  $V_{PP}$ . Device identifier code can be output by command inputs.

4. Refer to the table of command address and data input. Data is programmed, erased, or verified after mode setting by command inputs.

5. Status of automatic erase can be verified in this mode. Status outputs on I/O7, I/O0 to I/O6 are in high impedance state.

6. X :  $V_{IH}$  or  $V_{IL}$ .  $V_{PP} = 0$  V to  $V_{CC}$

## Command Address and Data Input

| Command                                    | The number of cycle | First cycle                  |                       |                    | Second cycle                 |                       |                    |

|--------------------------------------------|---------------------|------------------------------|-----------------------|--------------------|------------------------------|-----------------------|--------------------|

|                                            |                     | Operation mode <sup>*1</sup> | Address <sup>*2</sup> | Data <sup>*3</sup> | Operation mode <sup>*1</sup> | Address <sup>*2</sup> | Data <sup>*3</sup> |

| Read (memory) <sup>*4</sup>                | 1                   | Write                        | ×                     | 00H                | Read                         | RA                    | Dout               |

| Read identified codes                      | 2                   | Write                        | ×                     | 90H                | Read                         | IA                    | ID                 |

| Setup erase/erase <sup>*5</sup>            | 2                   | Write                        | ×                     | 20H                | Write                        | ×                     | 20H                |

| Erase verify <sup>*5</sup>                 | 2                   | Write                        | EA                    | A0H                | Read                         | ×                     | EVD                |

| Setup auto erase/ auto erase <sup>*6</sup> | 2                   | Write                        | ×                     | 30H                | Write                        | ×                     | 30H                |

| Setup program/ program <sup>*7</sup>       | 2                   | Write                        | ×                     | 40H                | Write                        | PA                    | PD                 |

| Program verify <sup>*7</sup>               | 2                   | Write                        | ×                     | C0H                | Read                         | ×                     | PVD                |

| Reset                                      | 2                   | Write                        | ×                     | FFH                | Write                        | ×                     | FFH                |

Notes:

1. Refer to command program mode in mode selection about operation mode.

2. Refer to device identifier mode. IA = Identifier address, PA = Programming address, EA = Erase verify address, RA = Read address

3. Refer to device identifier mode. PA are latched by programming command. ID = Identifier output code, PD = Programming data, PVD = Programming verify output data, EVD = Erase verify output data

4. Command latch default value when applying 12 V to  $V_{PP}$  is “00H”. Device is in read mode after  $V_{PP}$  is set 12 V (before other command is input).

5. All data in chip are erased. Erase data according to fast high-reliability erase flowchart.

6. All data in chip are erased. Data are erased automatically by internal logic circuit. External erase verify is not required. Erasure completion must be verified by status polling after automatic erase starts.

7. Program data according to fast high-reliability programming flowchart.

## Absolute Maximum Ratings

| Parameter                                  | Symbol               | Value                      | Unit |

|--------------------------------------------|----------------------|----------------------------|------|

| All input and output voltage <sup>*1</sup> | $V_{in}$ , $V_{out}$ | −0.6 <sup>*2</sup> to +7.0 | V    |

| $V_{PP}$ voltage <sup>*1</sup>             | $V_{PP}$             | −0.6 to +14.0              | V    |

| $V_{CC}$ voltage <sup>*1</sup>             | $V_{CC}$             | −0.6 to +7.0               | V    |

| Operating temperature range                | $T_{opr}$            | 0 to +70                   | °C   |

| Storage temperature range <sup>*3</sup>    | $T_{stg}$            | −55 to +125                | °C   |

| Storage temperature under bias             | $T_{bias}$           | −10 to +80                 | °C   |

Notes:

1. Relative to  $V_{SS}$ .

2.  $V_{in}$ ,  $V_{out}$ ,  $V_{ID}$  min = −2.0 V for pulse width  $\leq 20$  ns.

3. Device storage temperature range before programming.

**Capacitance (Ta = 25°C, f = 1 MHz)**

| Parameter          | Symbol | Min | Typ | Max | Unit | Test conditions |

|--------------------|--------|-----|-----|-----|------|-----------------|

| Input capacitance  | Cin    | —   | —   | 6   | pF   | Vin = 0 V       |

| Output capacitance | Cout   | —   | —   | 12  | pF   | Vout = 0 V      |

**Read Operation****DC Characteristics (V<sub>CC</sub> = 5 V ± 10%, V<sub>PP</sub> = V<sub>CC</sub>~V<sub>SS</sub>, Ta = 0 to +70°C)**

| Parameter                         | Symbol           | Min                | Typ | Max                                 | Unit | Test conditions             |

|-----------------------------------|------------------|--------------------|-----|-------------------------------------|------|-----------------------------|

| Input leakage current             | I <sub>IL</sub>  | —                  | —   | 2                                   | µA   | Vin = 0 to V <sub>CC</sub>  |

| Output leakage current            | I <sub>LO</sub>  | —                  | —   | 2                                   | µA   | Vout = 0 to V <sub>CC</sub> |

| V <sub>PP</sub> current           | I <sub>PP1</sub> | —                  | —   | 20                                  | µA   | V <sub>PP</sub> = 5.5 V     |

| Standby V <sub>CC</sub> current   | I <sub>SB1</sub> | —                  | —   | 1                                   | mA   | CE = V <sub>IH</sub>        |

|                                   | I <sub>SB2</sub> | —                  | —   | 20                                  | µA   | CE = V <sub>CC</sub>        |

| Operating V <sub>CC</sub> current | I <sub>CC1</sub> | —                  | 6   | 15                                  | mA   | Iout = 0 mA, f = 1 MHz      |

|                                   | I <sub>CC2</sub> | —                  | 10  | 30                                  | mA   | Iout = 0 mA, f = 8 MHz      |

| Input voltage <sup>*3</sup>       | V <sub>IL</sub>  | -0.3 <sup>*1</sup> | —   | 0.8                                 | V    |                             |

|                                   | V <sub>IH</sub>  | 2.2                | —   | V <sub>CC</sub> + 0.3 <sup>*2</sup> | V    |                             |

| Output voltage                    | V <sub>OL</sub>  | —                  | —   | 0.45                                | V    | I <sub>OL</sub> = 2.1 mA    |

|                                   | V <sub>OH</sub>  | 2.4                | —   | —                                   | V    | I <sub>OH</sub> = -400 µA   |

Notes: 1. V<sub>IL</sub> min = -2.0 V for pulse width ≤ 20 ns.

2. V<sub>IH</sub> max = V<sub>CC</sub> + 1.5 V for pulse width ≤ 20 ns.

If V<sub>IH</sub> is over the specified maximum value, read operation cannot be guaranteed.

3. Only defined for DC and long cycle function test.

V<sub>IL</sub> max = 0.45 V, V<sub>IH</sub> min = 2.4 V for AC function test.

## AC Characteristics ( $V_{CC} = 5 \text{ V} \pm 10\%$ , $V_{PP} = V_{SS}$ to $V_{CC}$ , $Ta = 0$ to $+70^\circ\text{C}$ )

### Test Conditions

- Input pulse levels: 0.45 V/2.4 V

- Input rise and fall time: 10 ns

- Output load: 1TTL Gate + 100 pF (Including scope and jig.)

- Reference levels for measuring timing: 0.8 V, 2.0 V

HN28F101-12 HN28F101-15 HN28F101-20

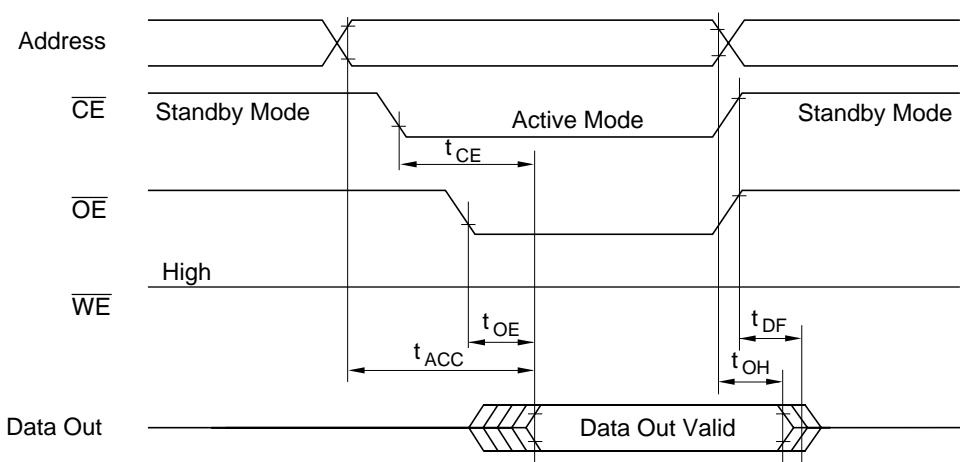

| Parameter                                          | Symbol    | Min | Max | Min | Max | Min | Max | Unit | Test conditions                          |

|----------------------------------------------------|-----------|-----|-----|-----|-----|-----|-----|------|------------------------------------------|

| Address to output delay                            | $t_{ACC}$ | —   | 120 | —   | 150 | —   | 200 | ns   | $\overline{CE} = \overline{OE} = V_{IL}$ |

| $\overline{CE}$ to output delay                    | $t_{CE}$  | —   | 120 | —   | 150 | —   | 200 | ns   | $\overline{OE} = V_{IL}$                 |

| $\overline{OE}$ to output delay                    | $t_{OE}$  | —   | 60  | —   | 70  | —   | 80  | ns   | $\overline{CE} = V_{IL}$                 |

| $\overline{OE}$ high to output float <sup>*1</sup> | $t_{DF}$  | 0   | 40  | 0   | 50  | 0   | 60  | ns   | $\overline{CE} = V_{IL}$                 |

| Address to output hold                             | $t_{OH}$  | 5   | —   | 5   | —   | 5   | —   | ns   | $CE = OE = V_{IL}$                       |

Note: 1.  $t_{DF}$  is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

### Read Timing Waveform

## Command Programming/Data Programming/Erase Operation

DC Characteristics ( $V_{CC} = 5 \text{ V} \pm 10\%$ ,  $V_{PP} = 12.0 \text{ V} \pm 0.6 \text{ V}$ ,  $T_a = 0 \text{ to } +70^\circ\text{C}$ )

| Parameter                  | Symbol    | Min       | Typ                | Max                 | Unit          | Test conditions                                |

|----------------------------|-----------|-----------|--------------------|---------------------|---------------|------------------------------------------------|

| Input leakage current      | $I_{LI}$  | —         | —                  | 2                   | $\mu\text{A}$ | $V_{in} = 0 \text{ V}$ to $V_{CC}$             |

| Output leakage current     | $I_{LO}$  | —         | —                  | 2                   | $\mu\text{A}$ | $V_{out} = 0 \text{ V}$ to $V_{CC}$            |

| Standby $V_{CC}$ current   | $I_{SB1}$ | —         | —                  | 1                   | mA            | $\overline{CE} = V_{IH}$                       |

|                            | $I_{SB2}$ | —         | —                  | 200                 | $\mu\text{A}$ | $\overline{CE} = V_{CC}$                       |

| Operating $V_{CC}$ current | Read      | $I_{CC1}$ | —                  | 6                   | mA            | $I_{out} = 0 \text{ mA}$ , $f = 1 \text{ MHz}$ |

|                            |           | $I_{CC2}$ | —                  | 10                  | mA            | $I_{out} = 0 \text{ mA}$ , $f = 8 \text{ MHz}$ |

|                            | Program   | $I_{CC3}$ | —                  | 2                   | mA            |                                                |

|                            | Erase     | $I_{CC4}$ | —                  | 10                  | mA            | In automatic erase                             |

|                            |           | $I_{CC5}$ | —                  | 5                   | mA            | In high-reliability erase                      |

| $V_{PP}$ current           | Read      | $I_{PP1}$ | —                  | 1                   | mA            | $V_{PP} = 12.6 \text{ V}$                      |

|                            | Program   | $I_{PP2}$ | —                  | 5                   | mA            | In programming                                 |

|                            | Erase     | $I_{PP3}$ | —                  | 35                  | mA            | In automatic erase                             |

|                            |           | $I_{PP4}$ | —                  | 10                  | mA            | In high-reliability erase                      |

| Input voltage              | $V_{IL}$  | —         | —0.3 <sup>*4</sup> | —                   | V             |                                                |

|                            | $V_{IH}$  | 2.2       | —                  | $V_{CC} + 0.3^{*5}$ | V             |                                                |

| Output voltage             | $V_{OL}$  | —         | —                  | 0.45                | V             | $I_{OL} = 2.1 \text{ mA}$                      |

|                            | $V_{OH}$  | 2.4       | —                  | —                   | V             | $I_{OH} = -400 \mu\text{A}$                    |

# HN28F101 Series

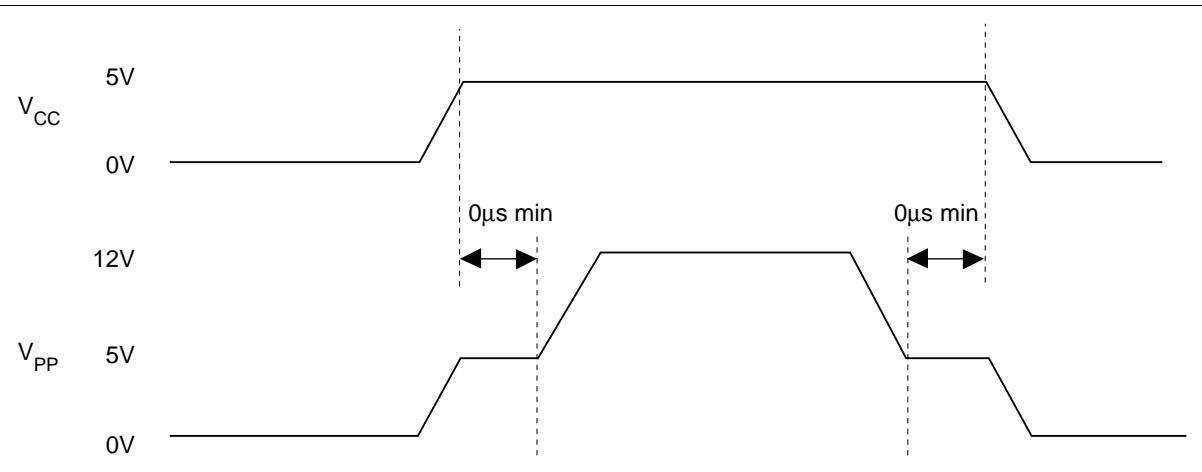

Notes: 1.  $V_{CC}/V_{PP}$  power on/off timing

$V_{CC}$  must be applied before or simultaneously  $V_{PP}$ , and removed after or simultaneously  $V_{PP}$ .

This  $V_{CC}/V_{PP}$  power on/off timing must be satisfied at  $V_{CC}/V_{PP}$  on/off caused by power failure.

2.  $V_{PP}$  must not exceed 14 V including overshoot.

3. An influence may be had upon device reliability if the device is installed or removed while  $V_{PP} = 12$  V.

4.  $V_{IL}$  min = -1.0 V for pulse width  $\leq 20$  ns.

5. If  $V_{IH}$  is over the specified maximum value, programming operation cannot be guaranteed.

AC Characteristics ( $V_{CC} = 5 \text{ V} \pm 10\%$ ,  $V_{PP} = 12.0 \text{ V} \pm 0.6 \text{ V}$ ,  $Ta = 0 \text{ to } +70^\circ\text{C}$ )

## Test Conditions

- Input pulse levels: 0.45 V/2.4 V

- Input rise and fall time: 10 ns

- Output load: 1TTL Gate + 100 pF (Including scope and jig.)

- Reference levels for measuring timing: 0.8 V, 2.0 V

| Parameter                                             | Symbol     | HN28F101-12 |     | HN28F101-15 |     | HN28F101-20 |     | Unit          | Test conditions |

|-------------------------------------------------------|------------|-------------|-----|-------------|-----|-------------|-----|---------------|-----------------|

|                                                       |            | Min         | Max | Min         | Max | Min         | Max |               |                 |

| Command programming cycle time                        | $t_{CWC}$  | 120         | —   | 150         | —   | 200         | —   | ns            |                 |

| Address setup time                                    | $t_{AS}$   | 0           | —   | 0           | —   | 0           | —   | ns            |                 |

| Address hold time                                     | $t_{AH}$   | 60          | —   | 60          | —   | 60          | —   | ns            |                 |

| Data setup time                                       | $t_{DS}$   | 50          | —   | 50          | —   | 50          | —   | ns            |                 |

| Data hold time                                        | $t_{DH}$   | 10          | —   | 10          | —   | 10          | —   | ns            |                 |

| $\overline{CE}$ setup time                            | $t_{CES}$  | 0           | —   | 0           | —   | 0           | —   | ns            |                 |

| $\overline{CE}$ hold time                             | $t_{CEH}$  | 50          | —   | 50          | —   | 50          | —   | ns            |                 |

| $V_{PP}$ setup time                                   | $t_{VPS}$  | 100         | —   | 100         | —   | 100         | —   | ns            |                 |

| $V_{PP}$ hold time                                    | $t_{VPH}$  | 100         | —   | 100         | —   | 100         | —   | ns            |                 |

| $\overline{WE}$ programming pulse width               | $t_{WEP}$  | 70          | —   | 70          | —   | 80          | —   | ns            |                 |

| $\overline{WE}$ programming pulse high time           | $t_{WEH}$  | 40          | —   | 40          | —   | 40          | —   | ns            |                 |

| $\overline{OE}$ setup time before command programming | $t_{OEWS}$ | 0           | —   | 0           | —   | 0           | —   | ns            |                 |

| $\overline{OE}$ setup time before verify              | $t_{OERS}$ | 6           | —   | 6           | —   | 6           | —   | $\mu\text{s}$ |                 |

| Verify access time                                    | $t_{VA}$   | —           | 120 | —           | 150 | —           | 200 | ns            |                 |

| Verify access time in erase                           | $t_{VAE}$  | —           | 300 | —           | 300 | —           | 300 | ns            |                 |

| $\overline{OE}$ setup time before status polling      | $t_{OEPS}$ | 120         | —   | 120         | —   | 120         | —   | ns            |                 |

| Status polling access time                            | $t_{SPA}$  | —           | 120 | —           | 150 | —           | 200 | ns            |                 |

| Standby time before programming                       | $t_{PPW}$  | 25          | —   | 25          | —   | 25          | —   | $\mu\text{s}$ |                 |

| Standby time in erase                                 | $t_{ET}$   | 9           | 11  | 9           | 11  | 9           | 11  | ms            |                 |

| Output disable time <sup>*3</sup>                     | $t_{DF}$   | 0           | 40  | 0           | 50  | 0           | 60  | ns            |                 |

| Total erase time in automatic erase <sup>*3</sup>     | $t_{AET}$  | —           | 30  | —           | 30  | —           | 30  | s             |                 |

Notes:

1.  $\overline{CE}$ ,  $\overline{OE}$ , and  $\overline{WE}$  must be fixed high during  $V_{PP}$  transition from 5 V to 12 V or from 12 V to 5 V.

2. Refer to read operation when  $V_{PP} = V_{CC}$  about read operation while  $V_{PP} = 12$  V.

3.  $t_{DF}$  is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

4. Address are taken into on the falling edge of write-enable pulse and addresses are latched on the rising edge of write-enable pulse during chip-enable is low. Data is latched on the rising edge of write-enable pulse during chip-enable is low.

## Erase and Program Time

|                            | Erase and program mode                            | Min | Typ <sup>*4</sup> | Max              | Unit   |

|----------------------------|---------------------------------------------------|-----|-------------------|------------------|--------|

| Chip (128 kB) erase time   | Auto erase mode                                   | —   | 1                 | 30               | second |

|                            | Fast high-reliability erase mode <sup>*2, 3</sup> | —   | 0.6               | 30               | second |

| Chip (128 kB) program time | Fast high-reliability program mode <sup>*3</sup>  | —   | 5                 | 81 <sup>*5</sup> | second |

Notes:

1. Each values are same for all read access version.

2. Excludes pre-write process before erasure and verify process (6  $\mu$ s x 128 kB).

3. Excludes system overhead.

4.  $T_a = 25^\circ C$ ,  $V_{PP} = 12$  V,  $V_{CC} = 5$  V

5. Theoretical value calculated from fast high-reliability programming flowchart.

(25  $\mu$ s program + 6  $\mu$ s verify) x 20 times x 128 kB = 81 second.

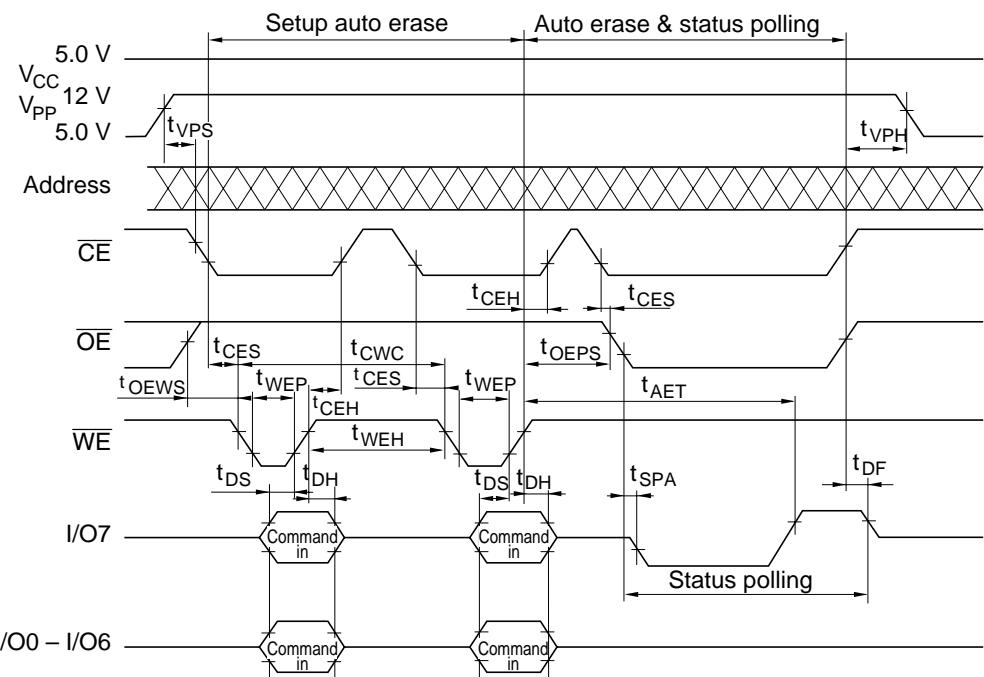

## Automatic Erase Timing Waveform

### Status Polling

Status polling allows the status of the flash memory to be determined. If the flash memory is set to the status polling mode during erase cycle,  $I/O7$  pin is lowered to  $V_{OL}$  level to indicate that the flash memory is performing erase operation.  $I/O7$  pin is set to the  $V_{OH}$  level when erase operation has finished.

Notes: In automatic erase mode, the device automatically processes to pre-write all “0” before erasing. Therefore, it is not required to pre-write by fast high-reliability programming.

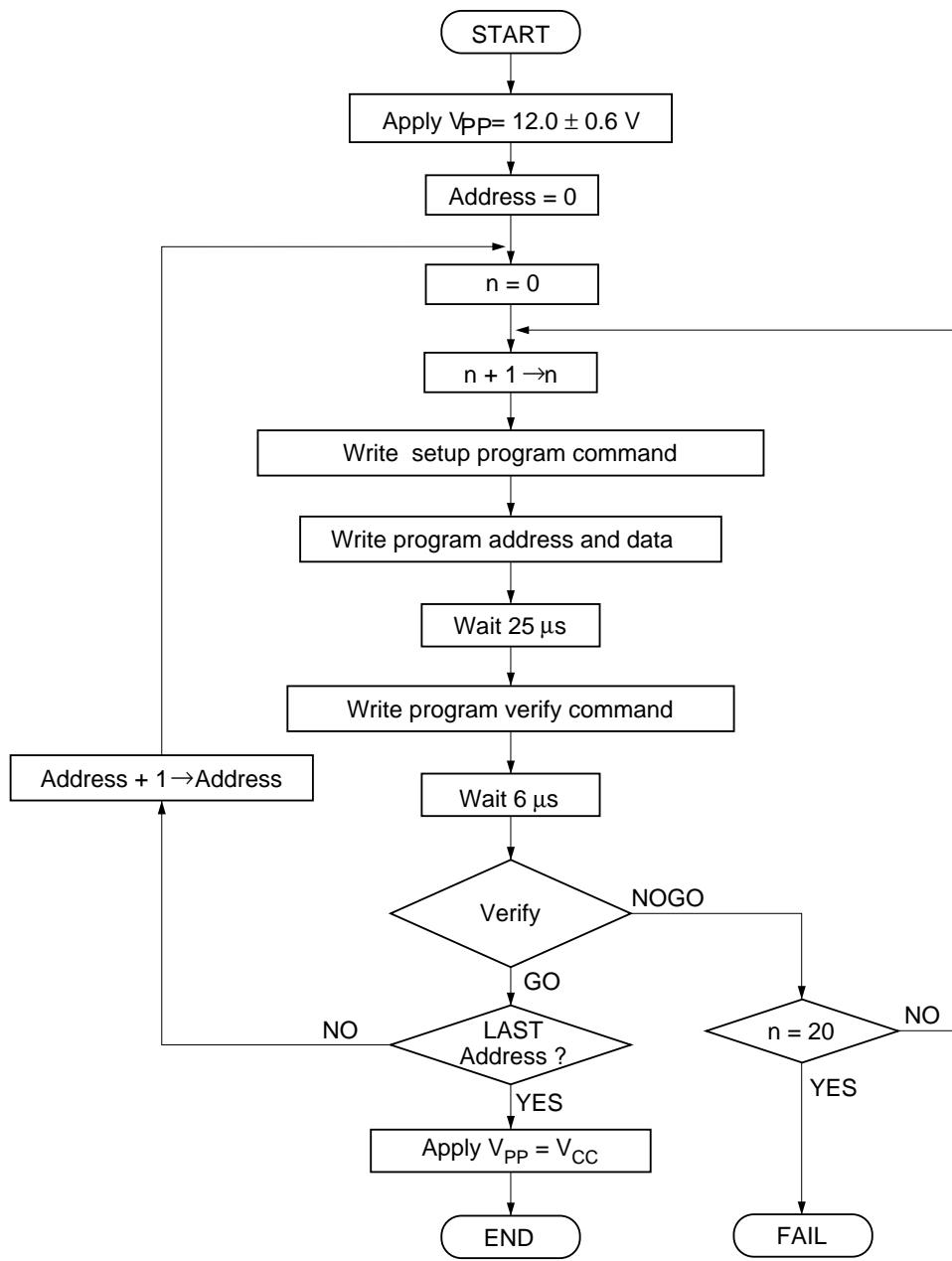

## Fast High-Reliability Programming

This device can be applied the fast high-reliability programming algorithm shown in following flowchart. This algorithm allows to obtain faster programming time without any voltage stress to the device nor deterioration in reliability of programmed data.

Fast High-Reliability Programming Flowchart

Notes: In case of two or more devices are programmed simultaneously, following steps should be applied to avoid over programming for the verified device.

- (1) Write set up program command to FFH,

- (2) Write program command to FFH,

- (3) Write program verify command to 00H and program verify address to read address.

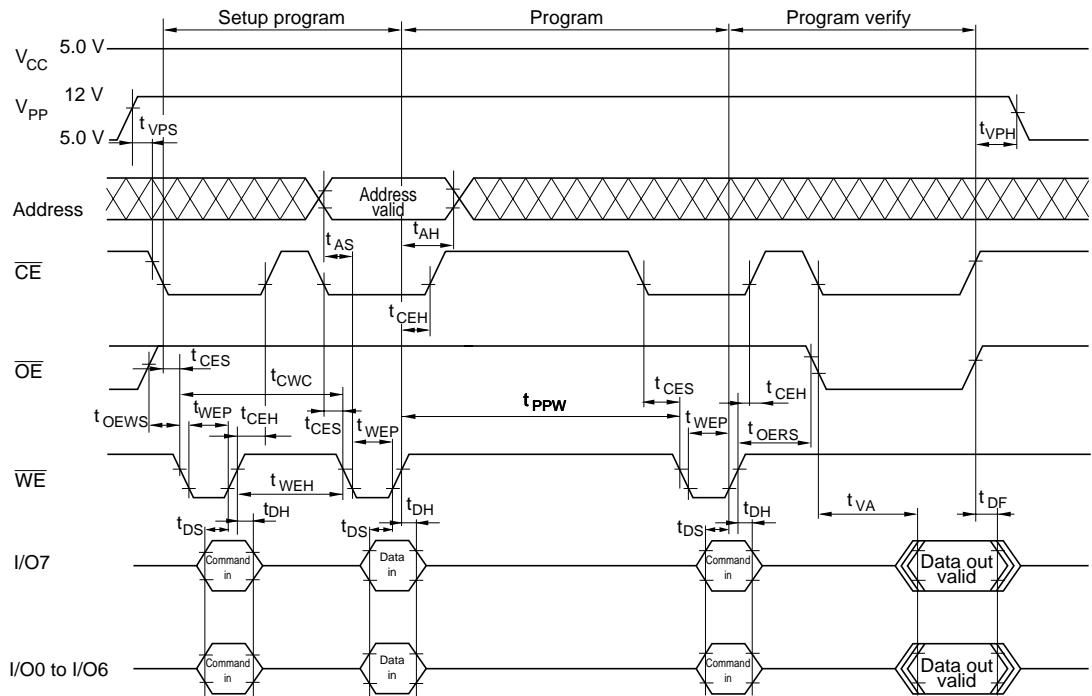

## Fast High-Reliability Programming Timing Waveform

Notes: The data output level during program verification may result in an intermediate level between V0H and V<sub>OL</sub> due to an insufficiently programmed.

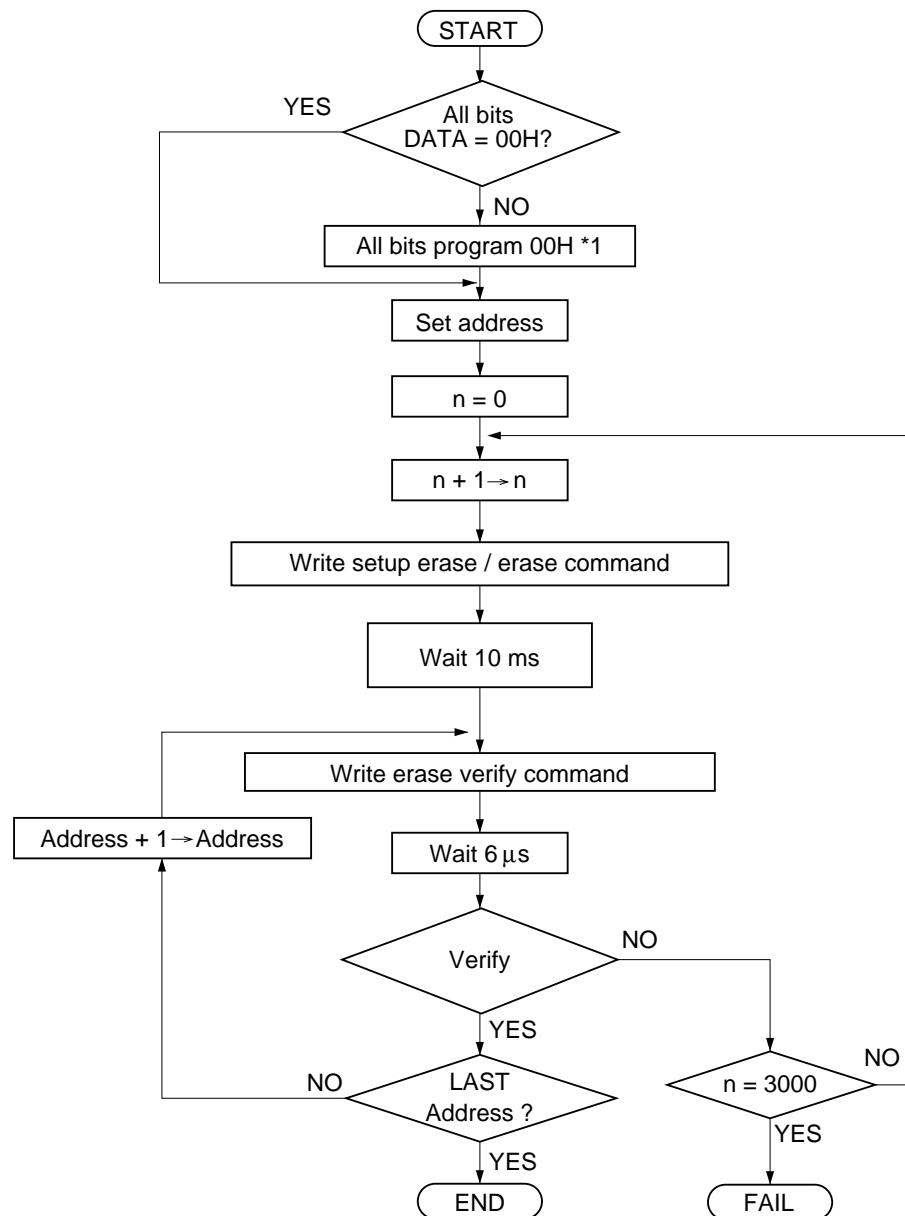

## Fast High-Reliability Erase

This device can be applied the fast high-reliability erase algorithm shown in following flowchart. This algorithm allows to obtain faster erase time without any voltage any voltage stress to the device nor deterioration in reliability of data.

\*1. Program data to all bits according to fast high-reliability erasing flowchart.

**Fast High-Reliability Erasing Flowchart**

Notes: In case of two or more devices are erased simultaneously, following steps should be applied to avoid over erase for verified device.

- (1) Write set up erase command to A0H and set erase verify address to verify address.

- (2) Write erase command to A0H.

- (3) Write erase verify command to A0H.

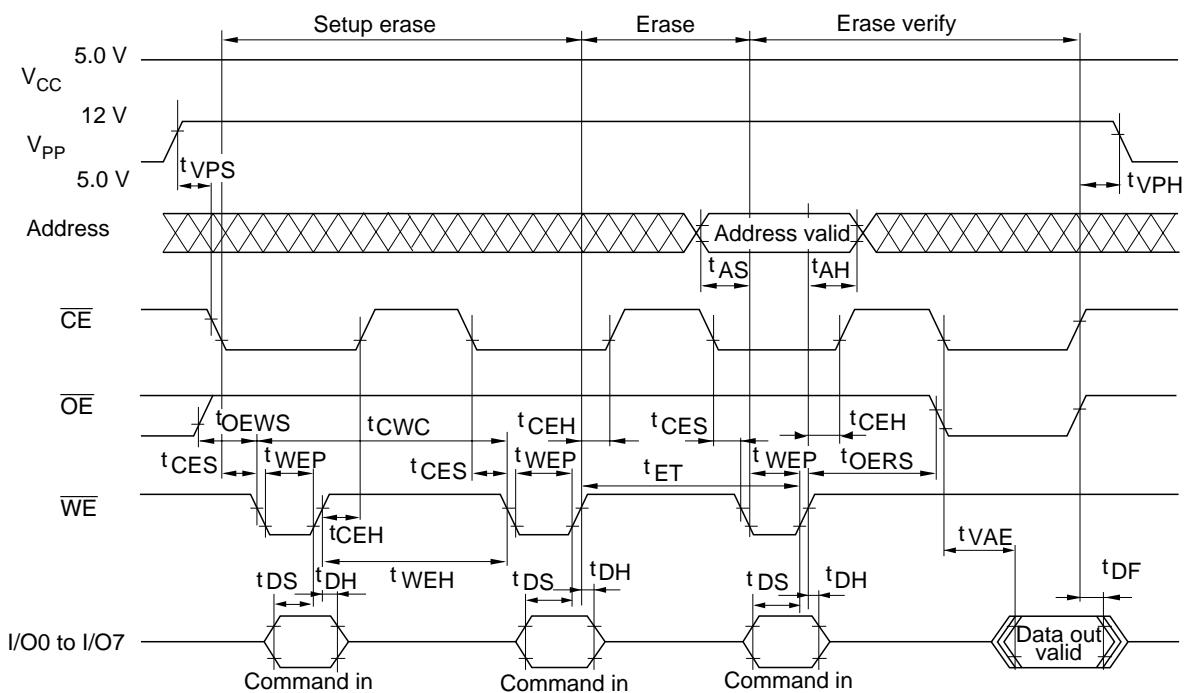

## Erase Timing Waveforms

Notes: The data output level during erasure verification may result in an intermediate level between  $V_{OH}$  and  $V_{OL}$  due to an insufficiently erased.

## Mode Description

### Device Identifier Mode

The device identifier mode allows the reading out of binary codes that identify manufacturer and type of device, from outputs of flash memory. By this mode, the device will be automatically matched its own corresponding erase and programming algorithm, using programming equipment.

### HN28F101 Series Identifier Code

| Identifier        | Pins<br>SOP,<br>TSOP | A0<br>(12)<br>(20) | I/O7<br>(21)<br>(29) | I/O6<br>(20)<br>(28) | I/O5<br>(19)<br>(27) | I/O4<br>(18)<br>(26) | I/O3<br>(17)<br>(25) | I/O2<br>(15)<br>(23) | I/O1<br>(14)<br>(22) | I/O0<br>(13)<br>(21) | Hex<br>Data |

|-------------------|----------------------|--------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-------------|

| Manufacturer code |                      | $V_{IL}$           | 0                    | 0                    | 0                    | 0                    | 0                    | 1                    | 1                    | 1                    | 07          |

| Device code       |                      | $V_{IH}$           | 0                    | 0                    | 0                    | 1                    | 1                    | 0                    | 0                    | 1                    | 19          |

Notes: 1. Device identifier code can be read out by applying  $12.0\text{ V} \pm 0.5\text{ V}$  to A9 when  $V_{PP} = V_{CC}$ , or inputting command while  $V_{PP}$  is 12 V.

2. A1 to A8, A10 to A16, and  $\overline{CE} = \overline{OE} = V_{IL}$ ,  $\overline{WE} = V_{IH}$

3.  $V_{CC} = V_{PP} = 5\text{ V} \pm 10\%$

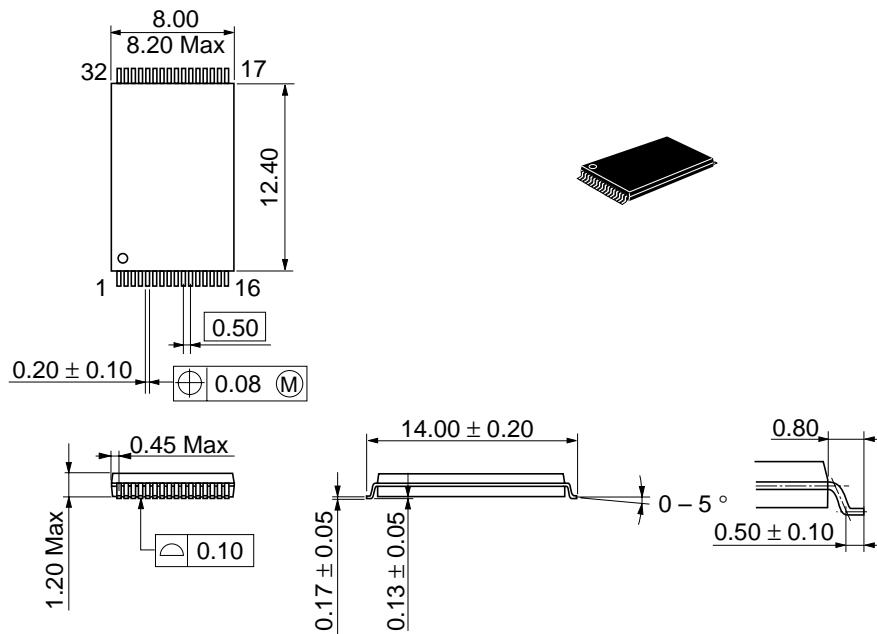

**Package Dimensions****HN28F101FP Series (FP-32D)**

Unit: mm

## HN28F101 Series

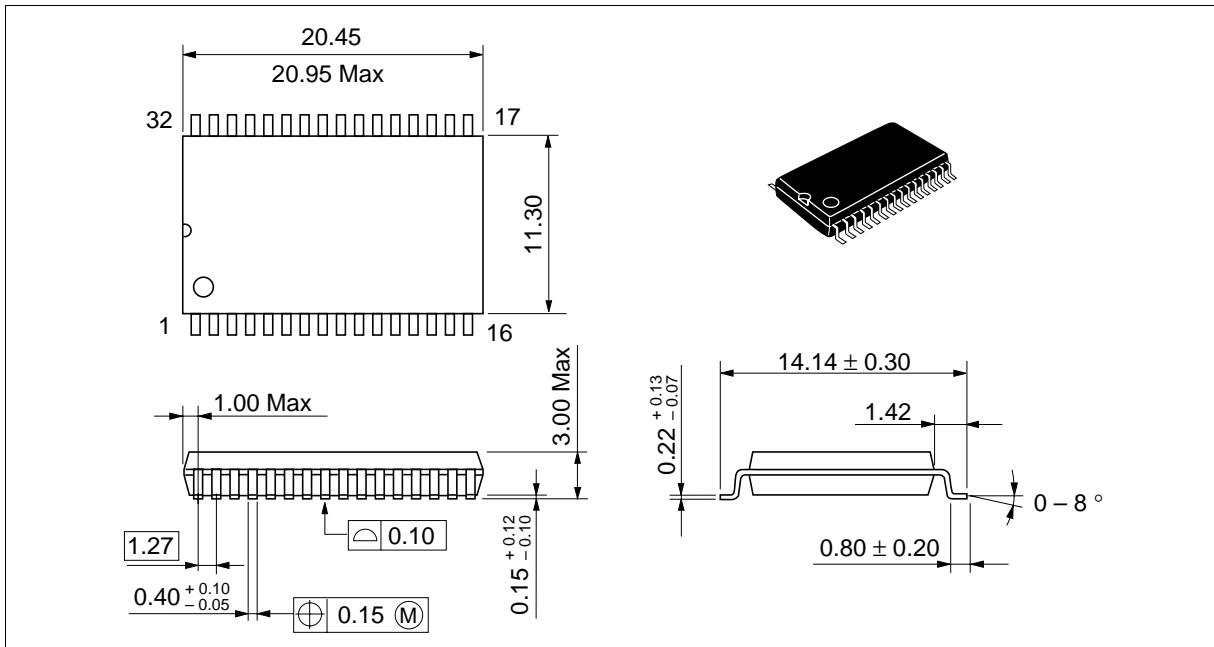

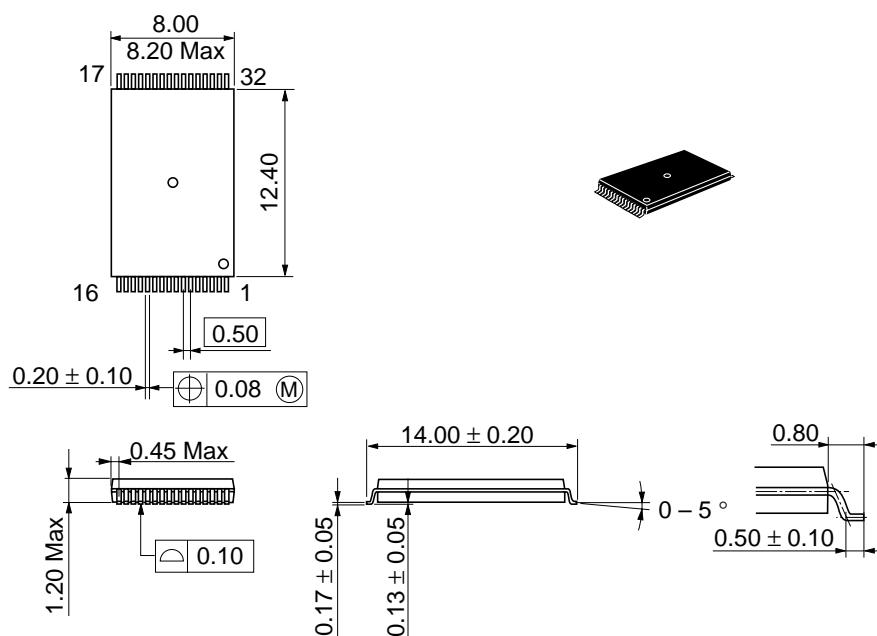

## **HN28F101T Series (TFP-32DA)**

Unit: mm

## HN28F101R Series (TFP-32DAR)

Unit: mm

When using this document, keep the following in mind:

1. This document may, wholly or partially, be subject to change without notice.

2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

---

# **HITACHI**

## **Hitachi, Ltd.**

Semiconductor & IC Div.

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100, Japan

Tel: Tokyo (03) 3270-2111

Fax: (03) 3270-5109

### **For further information write to:**

Hitachi America, Ltd.

Semiconductor & IC Div.

2000 Sierra Point Parkway

Brisbane, CA. 94005-1835

U S A

Tel: 415-589-8300

Fax: 415-583-4207

Hitachi Europe GmbH

Electronic Components Group

Continental Europe

Dornacher Straße 3

D-85622 Feldkirchen

München

Tel: 089-9 91 80-0

Fax: 089-9 29 30 00

Hitachi Europe Ltd.

Electronic Components Div.

Northern Europe Headquarters

Whitebrook Park

Lower Cookham Road

Maidenhead

Berkshire SL6 8YA

United Kingdom

Tel: 0628-585000

Fax: 0628-778322

Hitachi Asia Pte. Ltd.

16 Collyer Quay #20-00

Hitachi Tower

Singapore 0104

Tel: 535-2100

Fax: 535-1533

Hitachi Asia (Hong Kong) Ltd.

Unit 706, North Tower,

World Finance Centre,

Harbour City, Canton Road

Tsim Sha Tsui, Kowloon

Hong Kong

Tel: 27359218

Fax: 27306071

## Revision Record

| Rev. | Date          | Contents of Modification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Drawn by    | Approved by |

|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| 1.0  | Sep. 20, 1990 | Initial issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | K. Furusawa | T. Wada     |

| 2.0  | Dec. 24, 1990 | P1 Erasing endurance: 10000 times<br>P3, 4, 17 Addition of 32-pin PLCC package (CP-32)<br>P9 $t_{OE_{RS}}$ min: 5/5/5 $\mu$ s to 6/6/6 $\mu$ s<br>$t_{PPW}$ min: 15/15/15 $\mu$ s to 25/25/25 $\mu$ s<br>max: 25/25/25 $\mu$ s to not specified<br>P11 Change of fast high reliability programming flowchart<br>P13 Change of fast high reliability erase flowchart                                                                                                                                                                                                    | K. Furusawa | T. Wada     |

| 3.0  | Feb. 19, 1991 | P1, 8, 9, 11 $V_{PP}$ : 12V $\pm$ 0.4 V to 12 V $\pm$ 0.6 V<br>P6 $V_{PP}$ : -0.6 to 13 V to -0.6 to 14 V<br>P10, 12, 14 Change of timing waveforms<br>Addition of $t_{WEH}$                                                                                                                                                                                                                                                                                                                                                                                           | K. Furusawa | T. Wada     |

| 4.0  | Jun. 20, 1991 | Change of type no.<br>HN29C1001B to HN28F101<br>Change of fast high reliability programing timing waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                             | K. Furusawa | T. Wada     |

| 5.0  | Oct. 20, 1991 | Change of Low power dissipation<br>$I_{CC}$ typ (Read): 30 mA to 10 mA<br>P8, 10 DC Characteristics<br>Change of $I_{CC2}$ typ: 25 mA to 10 mA<br>$I_{CC2}$ max: 50 mA to 30 mA<br>$V_{IH}$ max: $V_{CC} + 1$ V to $V_{CC} + 0.3$ V<br>AC Characteristics<br>$t_{WEH}$ min: 20 ns to 40 ns<br>$t_{OEPS}$ min: 20 ns to 120 ns                                                                                                                                                                                                                                          | K. Furusawa | T. Wada     |

| 6.0  | Nov. 25, 1991 | P1,3,19 Addition of 32-pin plastic TSOP (TFP-32D)<br>P1,3,19 Addition of 32-pin plastic TSOP (TFP-32DR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                | K. Furusawa | T. Wada     |

| 7.0  | Nov. 11, 1992 | Deletion of 32-pin plastic TSOP (TFP-32D)<br>Deletion of 32-pin plastic TSOP (TFP-32DR)<br>Mode selection<br>Addition of pin number (DIP, SOP, PLCC)<br>Addition of pin number (TSOP)<br>Change of notes 5<br>DC Characteristics<br>Change of $I_{SB}$ , $I_{CC3}$ , $I_{PP1}$<br>Change of automatic erase timing waveform<br>Addition of notes from P12, P16<br>AC Characteristics<br>Change of $t_{CEH}$<br>Change of fast high reliability programming timing waveform<br>Change of fast high reliability programming flowchart<br>Change of erase timing waveform | K. Furusawa | T. Wada     |

**Revision Record (cont.)**

| Rev. | Date          | Contents of Modification                                                                                                                                                                                                                                                                                             | Drawn by    | Approved by |

|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| 7.0  | Nov. 11, 1992 | Mode Description<br>Addition of pin number (DIP, SOP, PLCC)<br>Addition of pin number (TSOP)<br>Change of notes 1                                                                                                                                                                                                    | K. Furusawa | T. Wada     |

| 8.0  | Aug. 20, 1993 | Addition of HN28F101TD Series (TFP-32D)<br>Addition of HN28F101RD Series (TFP-32DR)<br>Change of Read Timing Waveform                                                                                                                                                                                                | K. Izawa    | O. Sakai    |

| 9.0  | Apr. 20, 1994 | Deletion of old type name (HN29c101B)<br>DC Characteristics<br>I <sub>CC3</sub> typ: 9 mA to 2 mA<br>Change of note1<br>AC Characteristics<br>Addiditon of t <sub>VAE</sub> max: 300/300/300 ns<br>t <sub>AET</sub> min: 0.5/0.5/0.5 s to —/—/— s<br>Addition of Erase and program Time<br>Change of Timing Waveform | Y. Mori     | K. Furusawa |

| 10.0 | Nov. 15, 1996 | Change of format<br>Deletion of HN28F101P/CP/TD/DR Series                                                                                                                                                                                                                                                            |             |             |