# National Semiconductor

## DAC1266A/DAC1266 Hi-Speed 12-Bit D/A Converter

### General Description

The DAC1266A and DAC1266 are fast 12-bit digital to analog converters. These DACs use 12 precision high speed bipolar current steering switches, control amplifier, and a thin film resistor network to obtain a high accuracy, very fast analog output current. The DAC1266A and DAC1266 have 10%-90% full-scale transition time under 30 ns and settle to less than 1/2 LSB in 200 ns.

These digital to analog converters are recommended for applications in CRT displays, precision instruments and data acquisition systems requiring throughput rates as high as 5 MHz for full range transitions.

#### **Features**

- Bipolar current output DAC

- Fully differential, non-saturating precision current switch - ROUT and COUT do not change with digital input

- Precision thin film resistors for use with external op amp for voltage out or as input resistors for a successive approximate A/D converter

- Superior replacement for 12-bit D/A converters of this

### **Key Specifications**

■ Resolution and Monotonicity

12 Bits

■ Linearity

12 Bits

(Guaranteed over temperature)

400 ns max to 0.01%

■ Output Current Settling Time Full-Scale Transition Time (10%-90%)

TL/H/5068-7

Power Supply Sensitivity ±15 ppm of FS/% VSUPPLY

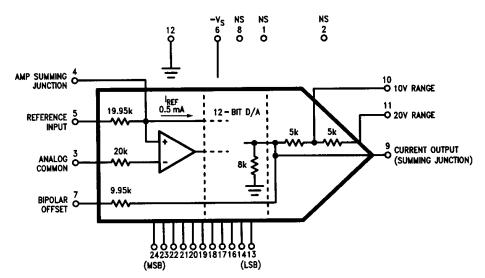

### **Block and Connection Diagrams**

#### **Dual-In-Line Package**

Absolute Maximum Ratings (Note 11)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sup>-</sup>)

Current Output (Pin 9) Voltage

Logic Input Voltage

-1V, 7V

Reference Input Voltage (Pin 5)

Analog GND to Power GND

±1V

Bipolar Offset

10V Range

±12V

$V^{-}$  to +24V 20V Range 1000 mW Power Dissipation (Note 1) Operating Temperature Range  $T_{MIN} \le T_A \le T_{MAX}$ -55°C to +125°C **DAC1266AJ, DAC1266LJ** DAC1266ACJ, DAC1266LCJ 0°C to +70°C -65°C to +150°C Storage Temperature Range 150°C **Maximum Junction Temperature** 300°C Lead Temp. (Soldering, 10 sec.) **TBD** ESD Susceptibility (Note 12)

**Electrical Characteristics**  $V_{SUPPLY} = -15V \pm 5\%$  and  $V_{REF} = 10.000V$  unless otherwise noted. **Boldface limits apply over temperature,**  $T_{MIN} \le T_A \le T_{MAX}$ . For all other limits  $T_A = 25^{\circ}C$ .

|                                                      | Conditions                                                                     | See<br>Note | DAC1266A |                             |                             | DAC1266 |                             |                             |                  |

|------------------------------------------------------|--------------------------------------------------------------------------------|-------------|----------|-----------------------------|-----------------------------|---------|-----------------------------|-----------------------------|------------------|

| Parameter                                            |                                                                                |             | Тур      | Tested<br>Limit<br>(Note 2) | Design<br>Limit<br>(Note 3) | Тур     | Tested<br>Limit<br>(Note 2) | Design<br>Limit<br>(Note 3) | Units            |

| CONVERTER CH                                         | ARACTERISTICS                                                                  |             |          |                             |                             |         |                             |                             |                  |

| Resolution                                           |                                                                                |             |          | 12                          |                             |         | 12                          |                             | Bits             |

| Linearity Error<br>Max                               | Zero and Full-Scale Adjusted  AJ and LJ Suffix Parts  ACJ and LCJ Suffix Parts | 4           | ± 1/8    | ± 1/4<br>± 1/2              | ± 1/2                       | ±1/4    | ±½<br>±¾                    | ± <b>¾</b>                  | LSB              |

| Differential<br>Non-Linearity<br>Max                 | Zero and Full-Scale Adjusted                                                   |             | ±1/4     | ±1/2                        |                             | ± 1/2   | ± 3/4                       |                             |                  |

| Monotonicity                                         | AJ and LJ Suffix Parts<br>ACJ and LCJ Suffix Parts                             |             |          | <b>12</b><br>12             | 12                          |         | <b>12</b><br>12             | 12                          | Bits             |

| Full-Scale<br>(Gain) Error<br>Max                    | R2=50 $\Omega$ in <i>Figure 1</i>                                              | 5           | ±0.1     | ±0.20                       |                             | ±0.1    |                             |                             | % Full-<br>Scale |

| Offset Error Max                                     | Unipolar (Figure 1 Pin 7 Open)                                                 | 6           | ±0.01    | ±0.05                       |                             | ±0.01   | ±0.05                       |                             |                  |

| All Bits OFF,<br>Logic "0"                           | Bipolar (R1 and R2 = $50\Omega$ in Figure 2)                                   | 7           | ±0.05    | ±0.1                        |                             | ±0.05   | ±0.15                       |                             |                  |

| Zero Error Max<br>MSB ON                             | Bipolar (R1 and R2 = $50\Omega$ in Figure 2)                                   | 8           | ±0.05    | ±0.1                        |                             | ±0.05   | ±0.15                       |                             |                  |

| Gain<br>Adjustment<br>Range Min                      | R2 = $50\Omega \pm 50\Omega$ in <i>Figure 1</i>                                |             |          | ±0.2                        |                             |         | ±0.2                        |                             | :                |

| Bipolar Offset<br>Adjustment<br>Range Min            | R1 = $50\Omega \pm 50\Omega$ and R2 = $50\Omega$ in Figure 2                   |             |          | ±0.15                       |                             |         | ±0.15                       |                             |                  |

| Full-Scale (Gain)<br>Temperature<br>Coefficients Max | AJ and LJ Suffix<br>ACJ and LCJ Suffix                                         | 9           | 1        | 3                           | 3                           | 5<br>5  | 10                          | 10                          | ppm/°C           |

| Unipolar Offset<br>Temperature<br>Coefficients Max   | AJ and LJ Suffix<br>ACJ and LCJ Suffix                                         |             | 1        | 2                           | 2                           | 1       | 2                           | 2                           |                  |

| Bipolar Zero<br>Temperature<br>Coefficients Max      | AJ and LJ Suffix<br>ACJ and LCJ Suffix                                         |             | 5<br>5   | 10                          | 10                          | 5<br>5  | 10                          | 10                          |                  |

| Output<br>Resistance                                 | Exclusive of Offset and Range R <sub>S</sub>                                   |             | 7.5      | 6 to 10                     |                             | 7.5     | 6 to 10                     |                             | kΩ               |

| Current Output                                       | Unipolar                                                                       |             | -2       | -1.6 to<br>-2.4             |                             | -2      | -1.6 to<br>-2.4             |                             | mA               |

|                                                      | Bipolar                                                                        |             | ±1.0     | ±0.8 to ±1.2                | :                           | ±1.0    | ±0.8 to ±1.2                |                             |                  |

**Electrical Characteristics** (Continued)  $V_{SUPPLY} = -15V \pm 5\%$  and  $V_{REF} = 10.000V$  unless otherwise noted. Boldface limits apply over temperature,  $T_{MIN} \le T_A \le T_{MAX}$ . For all other limits  $T_A = 25^{\circ}C$ .

| Parameter                       |      |                                 | See<br>Note                            | DAC1266A |                                |                             | DAC1266        |                             |                             |                |                     |

|---------------------------------|------|---------------------------------|----------------------------------------|----------|--------------------------------|-----------------------------|----------------|-----------------------------|-----------------------------|----------------|---------------------|

|                                 |      | Conditions                      |                                        | Тур      | Tested<br>Limit<br>(Note 2)    | Design<br>Limit<br>(Note 3) | Тур            | Tested<br>Limit<br>(Note 2) | Design<br>Limit<br>(Note 3) | Units          |                     |

| Output<br>Capacitance           |      |                                 |                                        |          | 25                             |                             |                | 25                          |                             |                | pF                  |

| Typ Output<br>Voltage Ranges    |      | Using Interr                    | nal Offset and Range R <sub>S</sub>    |          | ±2.5, ±5, ±10, 0 to 5, 0 to 10 |                             |                | V                           |                             |                |                     |

| Reference Input<br>Resistance   |      |                                 | -                                      |          | 20.8                           | 15 to 25                    |                | 20.8                        | 15 to 25                    |                | kΩ                  |

| Output<br>Compliance<br>Voltage |      |                                 |                                        |          |                                |                             | - 1.5 to<br>10 |                             |                             | - 1.5 to<br>10 | ٧                   |

| DIGITAL AND D                   | C CH | ARACTERI                        | ISTICS                                 |          |                                |                             |                |                             |                             |                |                     |

| Logic Input<br>Voltage          |      | Logic High<br>Bit ON            | AJ and LJ Suffix                       |          |                                | <b>2 to 5.5</b> 1.9 to 5.5  | 2 to 5.5       |                             | <b>2 to 5.5</b> 1.9 to 5.5  | 2 to 5.5       | ٧                   |

|                                 | Max  | Logic Low<br>Bit OFF            | AJ and LJ Suffix<br>ACJ and LCJ Suffix |          |                                | <b>0.8</b><br>1.0           | 0.8            |                             | <b>0.8</b><br>1.0           | 0.8            |                     |

| Logic Input<br>Current Max      |      | Logic High                      | AJ and LJ Suffix<br>ACJ and LCJ Sufix  |          | 150<br>150                     | <b>300</b><br>280           | 300            | 150<br>150                  | <b>300</b><br>280           | 300            | μΑ                  |

|                                 |      | Logic Low                       | AJ and LJ Suffix<br>ACJ and LCJ Suffix |          | 45<br>45                       | <b>100</b><br>90            | 100            | 45<br>45                    | <b>100</b><br>90            | 100            |                     |

| Power Supply<br>Current Max     | •    | V - Supply                      | = -15V±10%                             |          | -12                            | -18                         |                | -12                         | -18                         |                | mA                  |

| Power Dissipation Max           |      | V - Supply                      | = -15V                                 |          | 180                            | 270                         |                | 180                         | 270                         |                | mW                  |

| Power Supply<br>Sensitivity Max |      | V - Supply                      | =-12V±5%                               | 10       | ±15                            | ±25                         |                | ± 15                        | ±25                         | <u> </u>       | ppm of F            |

|                                 |      | V <sup>-</sup> Supply= −15V±10% |                                        | 10       | ± 15                           | ±25                         |                | ± 15                        | ± 25                        | J              | % V <sub>SUPP</sub> |

| AC CHARACTE                     | RIST | ICS                             |                                        |          |                                |                             |                |                             | _                           |                |                     |

| Settling<br>Time Max            |      | FSR Chang                       | је                                     |          | 200                            |                             | 400            | 200                         |                             | 400            | ns                  |

| Full-scale                      |      | Delay Plus                      | 10% to 90% Rise Time                   |          | 15                             |                             | 30             | 15                          |                             | 30             |                     |

| Transition Max                  |      | Delay Plus 90% to 10% Fall Time |                                        |          | 30                             |                             | 50             | 30                          |                             | 50             | ns                  |

Note 1: The typical  $\theta_{\rm JA}$  of the 24-pin package is 80° C/W.

- Note 2: Tested and guaranteed to National's AOQL (Average Outgoing Quality Level).

- Note 3: Guaranteed, but not 100% production tested. These limits are not used to calculate outgoing quality levels.

Note 4: Linearity error =

$$\frac{V_{OUT} - V_{OFFSET} - (D \times V_{LSB})}{V_{LSB}}$$

where  $V_{LSB} = \frac{V_{FS} - V_{OFFSET}}{4095}$  and D is the digital input (0 to 4095) which produced  $V_{OUT}$ .

Note 5: Percent gain error for 10V range =  $\frac{(V_{FS} - V_{OFFSET}) - (4095/4096)V_{REF}}{V_{OFF}} \times 100.$

Note 6: Unipolar offset error for 10V range =  $(V_{OUT}/V_{REF}) \times 100$  in percent of full-scale.

Note 7: Bipolar offset error for 10V range =  $\frac{V_{OUT} - (-V_{REF}/2)}{V_{REF}} \times$  100 in percent of full-scale.

Note 8: Bipolar zero error for 10V range =  $(V_{OUT}/V_{REF}) \times 100$  in percent of full-scale.

Note 9: Gain error tempco =  $\frac{(V_{FS} - V_{OFFSET}) \text{ at } (T_{MAX} \text{ or } T_{MIN}) - (V_{FS} - V_{OFFSET}) \text{ at } 25^{\circ}\text{C}}{10V \text{ range} \times (T_{MAX} \text{ or } T_{MIN} - 25^{\circ}\text{C})} \times 10^{6} \text{ in ppm/}^{\circ}\text{C}.$

Note 10: Power supply sensitivity for 10V range =  $10^6 \times \frac{(V_{FS} - V_{OFFSET}) \text{ at } (-13.5\text{V}) - (V_{FS} - V_{OFFSET}) \text{ at } (-16.5\text{V})}{V_{REF} \times 20\%}$  in ppm of FS/% V<sub>S</sub>.

Note 11: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

Note 12: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

## Functional Description and Applications

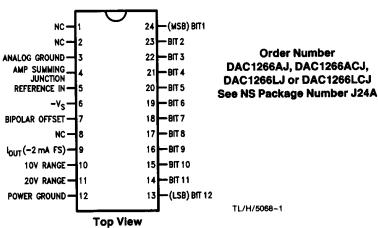

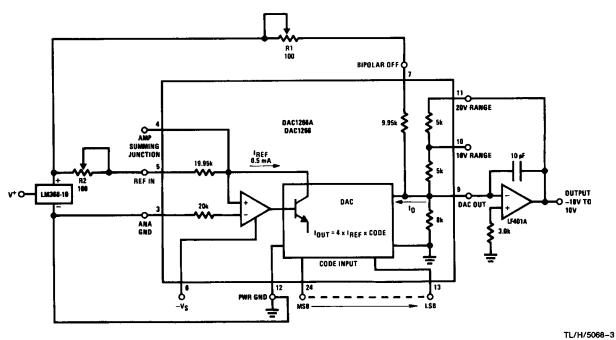

#### 1.0 BUFFERED VOLTAGE OUTPUT CONNECTION

The standard current-to-voltage conversion connections using an operational amplifier are shown here with the preferred trimming techniques. If a low offset operational amplifier (LF401A) is used, excellent performance can be obtained in many situations without trimming (an op amp with less than 0.5 mV maximum offset voltage should be used to keep offset errors below ½ LSB). Unipolar zero will typically be within  $\pm \frac{1}{2}$  LSB (plus op amp offset), and if a 50 $\Omega$  fixed resistor is substituted for the 100 $\Omega$  trimmer (R2, Figure 1), full-scale accuracy will be within 0.1% (0.20% maximum). Substituting a 50 $\Omega$  resistor for the 100 $\Omega$  bipolar offset trimmer (R1, Figure 2) will give a bipolar zero error typically within  $\pm 2$  LSB (0.05%).

#### 1.1 Unipolar Configuration (Figure 1)

This configuration will provide a unipolar 0V to 9.9976V output range.

#### Step 1—Offset Adjust (Zero)

Turn all bits OFF and adjust zero trimmer, R1, until the output reads 0.000V (1 LSB = 2.44 mV). In most cases this trim is not needed.

#### Step 2-Gain Adjust

Turn all bits ON and adjust  $100\Omega$  gain trimmer, R2, until the output is 9.9976V (full-scale adjusted to 1 LSB less than nominal full-scale of 10.000V). If a 10.2375V full-scale is desired (exactly 2.5 mV/bit), insert a  $120\Omega$  resistor in series with the gain resistor at pin 10 to the op amp output or use the LH0071 voltage reference.

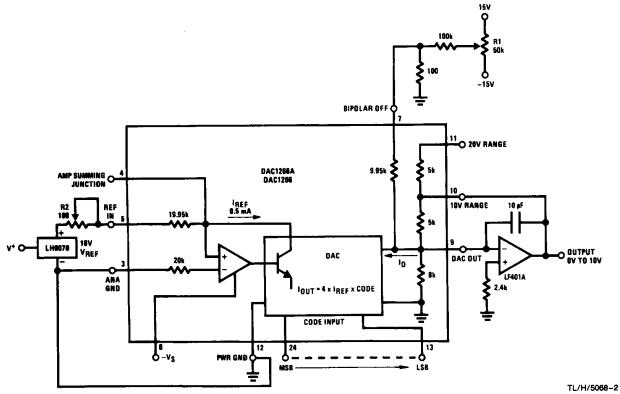

#### 1.2 Bipolar Configuration (Figure 2)

This configuration will provide a bipolar output voltage from -5.000V to 4.9976V, with positive full-scale occurring with all bits ON (all 1s).

#### Step 1-Offset Adjust

Turn OFF all bits. Adjust 100 $\Omega$  offset trimmer, R1, to give -5.000V output.

#### Step 2-Gain Adjust

Turn ON all bits. Adjust  $100\Omega$  gain trimmer, R2, to give a reading of 4.9976V.

Please note that it is not necessary to trim the op amp to obtain full accuracy at room temperature. In most bipolar situations, an op amp trim is unnecessary unless the untrimmed offset drift of the op amp is excessive. Bipolar zero error (MSB bit ON) is not adjusted separately and is typically  $<\pm 0.05\%$  of FS after offset and gain adjust.

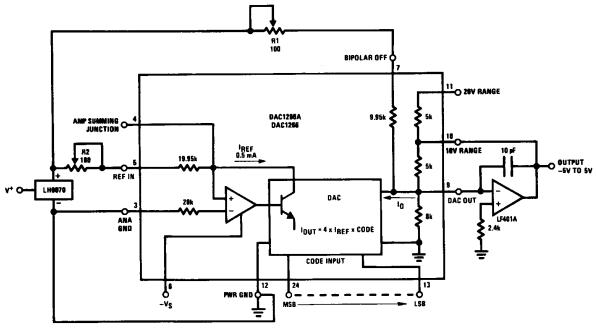

#### 1.3 Other Voltage Ranges (Figure 3)

The DAC1266A and DAC1266 can also be easily configured for a unipolar 0V to 5V range or  $\pm 2.5 V$  and  $\pm 10 V$  bipolar ranges by using the additional 5k application resistor provided at the 20V range R terminal, pin 11. For a 5V span (0V to 5V or  $\pm 2.5 V$ ), the two 5k resistors are used in parallel by shorting pin 11 to pin 9 and connecting pin 10 to the op amp output and the bipolar offset either left open for unipolar or connected through a  $100\Omega$  pot to the external

FIGURE 1. 0V to 10V Unipolar Voltage Output

\*Power and analog ground must have a common current return path. See section 3.0 for proper connections.

## Functional Description and Applications (Continued)

TL/H/5068~6

\*Power and analog ground must have a common current return path. See section 3.0 for proper connections.

FIGURE 2. ±5V Bipolar Voltage Output

FIGURE 3.  $\pm$  10V Voltage Output

12/11/5000-3

\*Power and analog ground must have a common current return path. See section 3.0 for proper connections.

## Functional Description and Applications (Continued)

reference for the bipolar range. For the  $\pm 10V$  range use the 5k resistors in series by connecting only pin 11 to the op amp output and connecting the bipolar offset as shown. The  $\pm 10V$  option is shown in *Figure 3*.

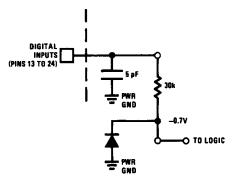

#### 2.0 DIGITAL INPUT

The DAC1266A and DAC1266 use a standard positive true straight binary code for unipolar outputs (all 1s give full-scale output), and an offset binary code for bipolar output ranges. In the bipolar mode, with all 0s on the inputs, the output will go to negative full-scale; with 100...00 (only the MSB on), the output will be 0.00V; with all 1s, the output will go to positive full-scale.

The threshold of the digital input circuitry is set at 1.4V and does not vary with supply voltage. The input lines can interface with any type of 5V logic, TTL/DTL or CMOS, and have sufficiently low input currents to interface easily with unbuffered CMOS logic. The configuration of the input circuit is shown in *Figure 4*. The input line can be modelled as a 30 k $\Omega$  resistance connected to a -0.7V rail.

TL/H/5068-4

FIGURE 4. Equivalent Digital Input Circuit

#### 3.0 APPLICATION OF ANALOG AND POWER GROUND

The DAC1266A and DAC1266 have separate analog and power ground pins to allow optimum connections for low noise and high speed performance. The two ground lines can be separated by up to 200 mV without any loss in performance. There may be some loss in linearity beyond that level. If these DACs are to be used in a system in which the two grounds will be ultimately connected at some distance from the device, it is recommended that parallel back-to-back diodes be connected between the ground lines near the device to prevent a fault condition.

The analog ground at pin 3 is the ground reference point for the internal reference and is thus the "high quality" ground; it should be connected directly to the analog reference point of the system. The power ground at pin 12 can be connected to the most convenient ground reference point; analog power return is preferred, but digital ground is acceptable. If power ground contains high frequency noise beyond 200 mV, this noise may feed through the converter, so that some caution will be required in applying these grounds.

#### **4.0 OUTPUT VOLTAGE COMPLIANCE**

The DAC1266A and DAC1266 have a typical output compliance range from -2V to 10V. The current-steering output stages will be unaffected by changes in the output terminal voltage over that range. However, there is an equivalent output impedance of 8k in parallel with 25 pF at the output terminal which produces an equivalent error current if the voltage deviates from power ground. This is a linear effect that does not change with input code. Operation beyond the compliance limits may cause either output stage saturation or breakdown which results in non-linear performance. Compliance limits are a function of output current and negative supply.

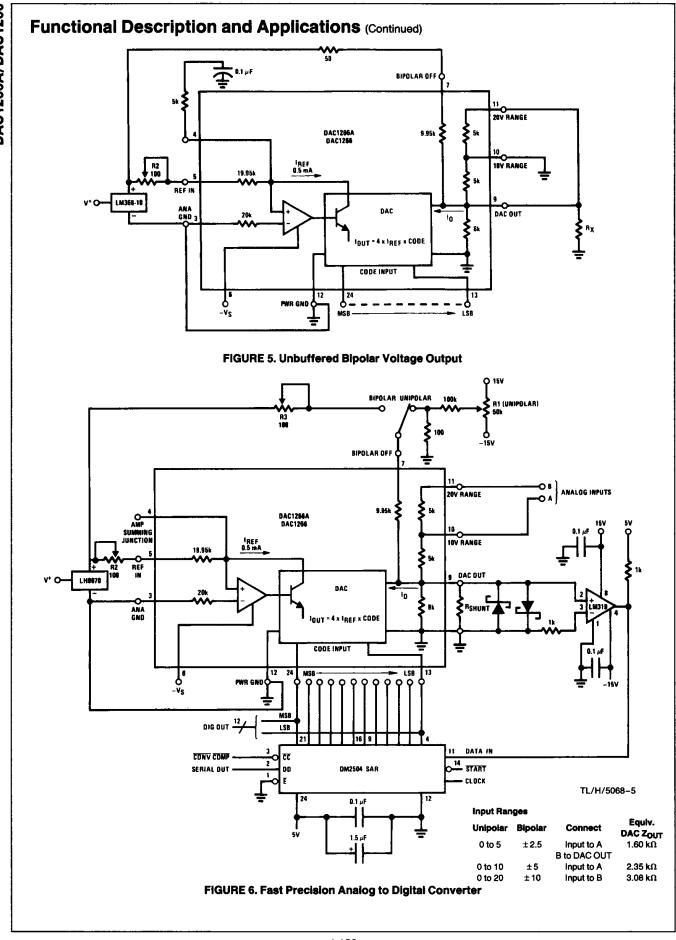

## 5.0 DIRECT UNBUFFERED VOLTAGE OUTPUT FOR CABLE DRIVING

The wide compliance range allows direct current-to-voltage conversion with just an output resistor. Figure 5 shows a connection using the gain and bipolar output resistors to give a  $\pm 1.60 \text{V}$  bipolar swing. In this situation, the digital code is complementary binary. Other combinations of internal and external output resistors (R\_X) can be used to scale to alternate voltage ranges, simply by appropriately scaling the 0 mA to -2 mA unipolar output current and using the 10.0V reference voltage for bipolar offset. For example, setting  $R_{\rm X}\!=\!2.67~{\rm k}\Omega$  gives a  $\pm\,1{\rm V}$  range with a 1 k $\Omega$  equivalent output impedance.

This connection is especially useful for directly driving a long cable at high speed. Using a  $50\Omega$  resistor for  $R_X$  would allow interface to a  $50\Omega$  cable with a  $\pm\,50$  mV full-scale swing.

#### 6.0 HIGH SPEED 12-BIT A/D CONVERTERS

The fast settling characteristics of the DAC1266A and DAC1266 make them ideal for high speed successive approximation A/D converters. Shown in *Figure 6* is a configuration using standard components; this system completes a full 12-bit conversion in 10  $\mu$ s unipolar or bipolar. This converter will be accurate to  $\pm \frac{1}{2}$  LSB of 12 bits and have a typical gain TC of 10 ppm/°C.

## Functional Description and Applications (Continued)

In the unipolar mode, the system range is 0V to 9.9976V, with each bit having a value of 2.44 mV. For true conversion accuracy, an A/D converter should be trimmed so that a given output code results from input levels from ½ LSB below to ½ LSB above the exact voltage represented by that code. Therefore, the converter zero point should be trimmed with an input voltage of 1.22 mV; trim R1 until the LSB just begins to appear in the output code (all other bits "0"). For full-scale, use an input voltage of 9.9963V (10V-1 LSB-½ LSB); then trim R2 until the LSB just begins to appear (all other bits "1").

The bipolar signal range is -5.0V to 4.9976V. Bipolar offset trimming is done by applying a -4.9988V input signal and trimming R3 for the LSB transition (all other bits "0").

Full-scale is set by applying a 4.9963V and trimming R2 for the LSB transition (all other bits "1"). In many applications, the pretrimmed internal resistors are sufficiently accurate that external trimmers will be unnecessary, especially in situations requiring less than full 12-bit  $\pm \frac{1}{2}$  LSB accuracy.

For fastest operation, the impedance at the comparator summing node must be minimized. However, lowering the impedance will reduce the voltage signal to the comparator (at an equivalent impedance at the summing node of 1 k $\Omega$ , 1 LSB = 0.5 mV), to the point that comparator performance will be sacrificed. The contribution to this impedance from the DAC will vary with the input configuration (*Figure 6*, Input Ranges Table).

To prevent dynamic errors, the input signal should have a low dynamic source impedance, such as that of the LF411A op amp.

#### **Definition of Terms**

**Digital Inputs:** The DAC1266A and DAC1266 accept digital input codes in binary format and may be user connected for any one of three binary codes: straight binary, two's complement, or offset binary.

|                             | Analog Output      |                  |                      |  |  |  |  |

|-----------------------------|--------------------|------------------|----------------------|--|--|--|--|

| Digital<br>Input<br>MSB LSB | Straight<br>Binary | Offset<br>Binary | Two's<br>Complement* |  |  |  |  |

| 000000                      | zero               | -FS (Full-Scale) | zero                 |  |  |  |  |

| 011111                      | 1/2 FS-1 LSB       | zero-1 LSB       | +FS-1 LSB            |  |  |  |  |

| 100000                      | 1/ <sub>2</sub> FS | zero             | −FS                  |  |  |  |  |

| 111111                      | +FS-1 LSE          | + FS-1 LSB       | zero-1 LSB           |  |  |  |  |

<sup>\*</sup>Invert MSB with external inverter to obtain Two's Complement coding

Linearity Error: Linearity Error of a D/A converter is an important measure of its accuracy. It describes the deviation from an ideal straight line transfer curve drawn between zero (all bits OFF) and full-scale (all bits ON).

**Differential Non-Linearity:** For a D/A converter, it is the difference between the actual output voltage change and the ideal (1 LSB) voltage change for a one-bit change in code. A differential non-linearity of  $\pm 1$  LSB or less guarantees monotonicity; i.e., the output always increases and never decreases for an increasing input. It is guaranteed by testing the major carry transitions; i.e., 100...000 to 011...111 etc.

**Settling Time:** Settling time is the time required for the output to settle to within the specified error band for any input code transition. It is usually specified for a full-scale or major carry transition.

**Gain Tempco:** The change in full-scale analog output over the specified temperature range expressed in parts per million of full-scale per °C (ppm of FS/°C). Gain error is measured with respect to 25°C at high ( $T_{MAX}$ ) and low ( $T_{MIN}$ ) temperatures. Gain tempco is calculated for both high ( $T_{MAX}$ -25°C) and low (25°C- $T_{MIN}$ ) ranges by dividing the gain error by the respective change in temperature. The specification is the larger of the two representing worst-case drift.

**Offset Tempco:** The change in analog output with all bits OFF over the specified temperature expressed in parts per million of full-scale per °C (ppm of FS/°C). Offset error is measured with respect to 25°C at high ( $T_{MAX}$ ) and low ( $T_{MIN}$ ) temperatures. Offset tempco is calculated for both high ( $T_{MAX}-25$ °C) and low (25°C  $-T_{MIN}$ ) ranges by dividing the offset error by the respective change in temperature. The specification given is the larger of the two, representing worst-case drift.

**Power Supply Sensitivity:** Power supply sensitivity is a measure of the change in gain and offset of the D/A converter resulting from a change in -15V supply. It is specified under DC conditions and expressed as parts per million of full-scale per percent of change in power supply (ppm of FS/%).

## **Ordering Information**

| Temperature R    | ange     | 0°C to 70°C | -55°C to +125°C |  |  |

|------------------|----------|-------------|-----------------|--|--|

| Linearity Error  | ±1/2 Bit | DAC1266ACJ  | DAC1266AJ       |  |  |

| Over Temperature | ±3/4 Bit | DAC1266LCJ  | DAC1266LJ       |  |  |