TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# **TC9240F**

#### Audio LCD Driver IC

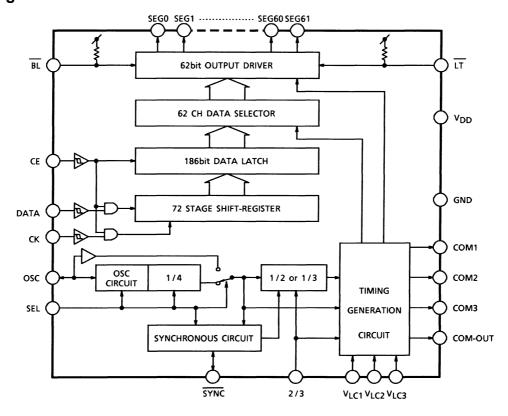

The TC9240F is a driver IC designed for exclusive use for output expansion LCD which is controlled by serial data.

#### **Features**

- 1/2 or 1/3 duty and 1/2 or 1/3 bias can be switched.

- Max 124 segments can be displayed in the 1/2 duty mode and 186 segments in the 1/3 duty mode.

- Built-in display synchronizing circuit enables display in multi-chip configuration.

- Built-in oscillation circuit with externally connected capacitor and resistor.

- Connected to the controller using the tree-wire system.

- Display data split in 3 segment blocks enables efficient data transfer.

Weight: 1.57 g (typ.)

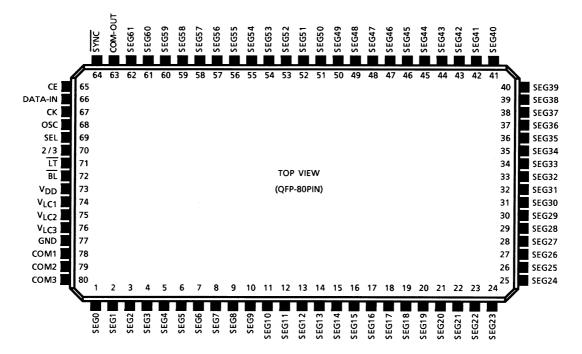

### Pin Assignment (top view)

1

# **Block Diagram**

# **Pin Description**

| Pin No. | Symbol         | Pin Name           | Description                                                                       | Remarks                                                 |  |  |

|---------|----------------|--------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------|--|--|

| 73      | $V_{DD}$       | Power Supply Pin   | Power Supply Pin (5 V ± 0.5 V)                                                    | _                                                       |  |  |

| 77      | GND            | GND Pin            | Fower Supply Fill (5 V ± 0.5 V)                                                   |                                                         |  |  |

| 1~62    | SEG0~<br>SEG61 | Segment Output Pin | LCD segment drive output pins  1/2 or 1/3 duty  1/2 or 1/3 bias  can be switched. | V <sub>DD</sub><br>V <sub>LC3</sub><br>V <sub>LC2</sub> |  |  |

| 72      | BL             | Blanking Input Pin | All segments are put in the blanking state when "L" level signal is input.        | V <sub>DD</sub> ←                                       |  |  |

| 71      | 71 LT Lamp Te  |                    | All segments light when "L" level signal is input.                                |                                                         |  |  |

| 65      | CE             | Chip Select Input  | Display data input pins                                                           |                                                         |  |  |

|         |                | Pin                | Input data becomes valid only when CE = "H".                                      |                                                         |  |  |

| 66      | DATA           | Data Input Pin     | Display data is input synchronizing with rise of CK clock.                        | O                                                       |  |  |

| 67      | СК             | Clock Input Pin    | When CE = "H" changes to CE = "L", data is latched and display is updated.        |                                                         |  |  |

| Pin No. | Symbol           | Pin Name                      | Description                                                                                                                                                            | Remarks                           |

|---------|------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 68      | osc              | Oscillation Pin               | This pin serves as an oscillator when a capacitor and a resistor are connected externally.  In the slave mode, COM-OUT output from the master IC is input to this pin. | VDD Master Input Slave Input      |

| 69      | SEL              | Master/Slave<br>Switching Pin | Master/slave switching input when more than 2 pieces of this IC are used simultaneously.  "H" = Master Mode  "L" = Slave Mode                                          | VDD X                             |

| 64      | SYNC             | Synchronous Pin               | Synchronizing input/output pin when more than 2 pieces of this IC are used simultaneously.  Master Mode: Synchronous output  Slave Mode: Synchronous input             | V <sub>DD</sub> ,                 |

| 70      | 2/3              | Duty Switching Pin            | 1/2 or 1/3 duty switching input  "H" = 1/2 duty mode  "L" = 1/3 duty mode                                                                                              | VDD <b>1</b>                      |

| 74      | V <sub>LC1</sub> |                               | LCD drive voltage input pins                                                                                                                                           |                                   |

| 75      | V <sub>LC2</sub> | Bias Input Pin                | Set input voltage to                                                                                                                                                   | _                                 |

| 76      | V <sub>LC3</sub> |                               | $V_{DD} \ge V_{LC1} \ge V_{LC2} \ge V_{LC3} \ge GND$                                                                                                                   |                                   |

| 78      | COM1             |                               |                                                                                                                                                                        | V <sub>DD</sub> ,                 |

| 79      | COM2             | Common Output Pin             | Common pin drive output  In the 1/2 duty mode, COM3 pin is used in the open state.                                                                                     | V <sub>L</sub> C1                 |

| 80      | СОМЗ             |                               |                                                                                                                                                                        | V <sub>LC3</sub> V <sub>LC2</sub> |

| 63      | COM-OUT          | Common Clock<br>Output Pin    | Synchronizing clock output pin Supplies clock to the OSC pin of the slave IC. $f_{COM} = f_{OSC}/4 \ [Hz]$                                                             | V <sub>DD</sub>                   |

## **Description of Operation**

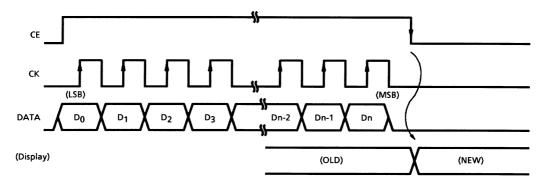

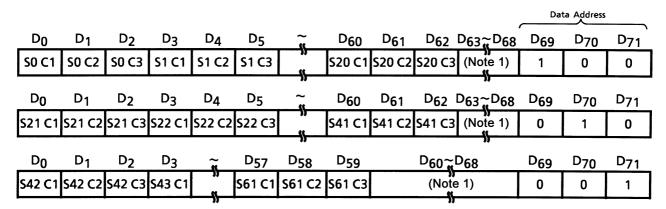

### 1. Data Input Format

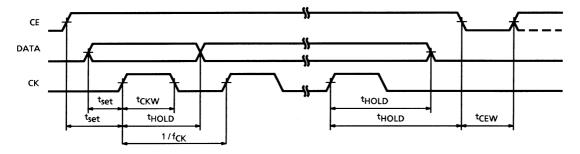

• Display data are input at the following timings:

### (display)

• For data length, 48 bits (D0~D47) are transferred 3 times in the 1/2 duty mode and 72 bits (D0~D71) 3 times in the 1/3 duty mode

4

- 3 bits (last 3 bits) from MSB side of data are address data. (D45 $\sim$ D47 in the 1/2 duty mode, while D69 $\sim$ D71 in the 1/3 duty mode.)

- Data in the 1/2 duty mode (2/3 = "H")

COM1 system data:

$$D_0$$

,  $D_2$ ,  $D_4$ .......  $(D_0 + 2n)$   $COM2$  system data:  $D_1$ ,  $D_3$ ,  $D_5$ .......  $(D_1 + 2n)$   $COM2$  system data: "100" = SEG0~SEG20 "010" = SEG21~SEG41 "001" = SEG42~SEG61

• Data in the 1/3 duty mode (2/3 = "L")

COM1 system data: D<sub>0</sub>, D<sub>3</sub>, D<sub>6</sub>....... (D<sub>0</sub> + 3n)

COM2 system data: D<sub>1</sub>, D<sub>4</sub>, D<sub>7</sub>...... (D<sub>1</sub> + 3n)

COM3 system data: D<sub>2</sub>, D<sub>5</sub>, D<sub>8</sub>...... (D<sub>2</sub> + 3n)

Address data: "100" = SEG0

$$\sim$$

SEG20

"010" = SEG21 $\sim$ SEG41

"001" = SEG42~SEG61

(1) Data format at 1/3 duty (186 segment)

Note 1: 1 or 0

(2) Data format at 1/2 duty (124 segment)

|                |                |                |                |                |                 |                 |                 |                 |                   |                                 | Dat               |                 |                   |

|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-------------------|---------------------------------|-------------------|-----------------|-------------------|

| D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub>  | ~               | D39             | D <sub>40</sub> | D <sub>41</sub>   | D42~D2                          | , D <sub>45</sub> | D <sub>46</sub> | D <sub>47</sub> ` |

| S0 C1          | S0 C2          | S1 C1          | S1 C2          | S2 C1          | S2 C2           | "               | S19 C1          | S20 C1          | S20 C2            | (Note 1                         | ) 1               | 0               | 0                 |

| D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub>  | ~               | D <sub>39</sub> | D <sub>40</sub> | D <sub>41</sub>   | D <sub>42</sub> ~D <sub>4</sub> | 4 D <sub>45</sub> | D <sub>46</sub> | D <sub>47</sub>   |

| S21 C1         | S21 C2         | S22 C1         | S22 C2         | S23 C1         | S23 C2          | "               | S40 C2          | S41 C1          | S41 C2            | (Note 1                         | ) 0               | 1               | 0                 |

| D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | ~              | D <sub>37</sub> | D <sub>38</sub> | D <sub>39</sub> |                 | D <sub>40</sub> ~ | <b>»</b><br>D44                 | D <sub>45</sub>   | D <sub>46</sub> | D <sub>47</sub>   |

| S42 C1         | S42 C2         | S43 C1         | S43 C2         | "              | S60 C2          | S61 C1          | S61 C2          |                 | (Note             | e 1)                            | 0                 | 0               | 1                 |

Note 1: 1 or 0

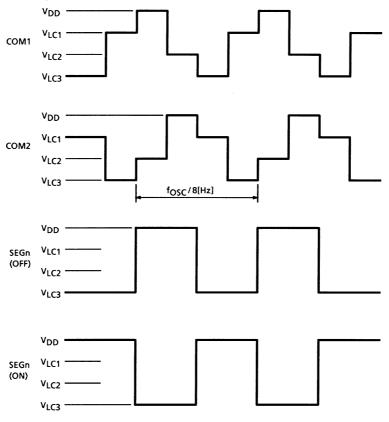

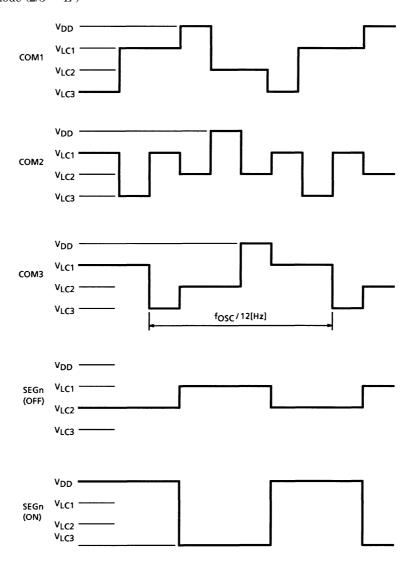

# 2. LCD Display Timings

(1) 1/2 duty mode (2/3 = "H")

Note 2: When used in the 1/2 bias, supply bias by connecting  $V_{LC2}$  pin and  $V_{LC3}$  pin. (this also applies to the 1/3 duty mode.)

6

• 1/3 bias operation

• 1/2 bias operation

### (2) 1/3 duty mode (2/3 = ``L'')

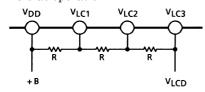

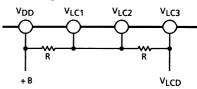

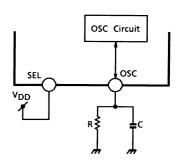

### 3. Oscillation Circuit

When a resistor and a capacitor are connected to the OSC pin and oscillation circuit is composed and common signal is generated.

1/4 division of oscillation frequency becomes common frequency.

Capacitor (C) and resistor (R) are connected as shown in the right-side figure and the oscillation frequency is expressed by the following expression:

$$\mathrm{fOSC} \approx 1.44/\mathrm{C} \cdot \mathrm{R} \; (\mathrm{Ta} = 25^{\circ}\mathrm{C}, \, \mathrm{VDD} = 5 \; \mathrm{V})$$

For instance, when C = 0.012  $\mu F,$  and R = 150  $k\Omega,$  fOSC will be about 800 Hz and common frequency will be 200 Hz. Use the external resistor at 12~220  $k\Omega.$

However, there is no restriction for the external capacitor C.

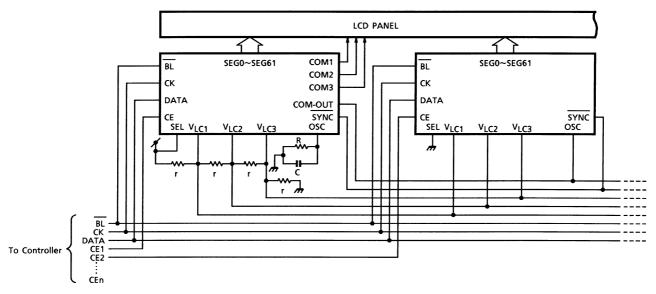

### 4. In Case of Using More than 2

When more than 2 TC9240F are used simultaneously, common frequency is generated using one IC in the master mode.

As a result, the slave mode IC performs the simultaneous operation.

### (1) Processing of pins at simultaneous operation

| Pin Name | PIN No. | Master Mode IN               | Slave Mode IC                 |

|----------|---------|------------------------------|-------------------------------|

| SEL      | 68      | "H" (V <sub>DD</sub> ) Level | "L" (GND) Level               |

| osc      | 75      | Connect External C&R         | Connect to Master IC: COM-OUT |

| SYNC     | 64      | Generate SYNC Output         | Connect to Master IC: SYNC    |

| COM-OUT  | 63      | Connect to Slave IC: OSC     | Open (unused)                 |

| COM1     | 78      |                              |                               |

| COM2     | 79      | Connect to COM Pin of LCD    | Open (unused)                 |

| COM3     | 80      |                              |                               |

### (2) Example of application circuit synchronizing operation

# **Maximum Ratings (Ta = 25°C)**

| Characteristics       | Symbol           | Rating                     | Unit |

|-----------------------|------------------|----------------------------|------|

| Supply voltage        | $V_{DD}$         | -0.3~7.0                   | V    |

| Input voltage         | V <sub>IN</sub>  | -0.3~V <sub>DD</sub> + 0.3 | V    |

| Power dissipation     | PD               | 300                        | mW   |

| Operating temperature | T <sub>opr</sub> | -40~85                     | °C   |

| Storage temperature   | T <sub>stg</sub> | -65~150                    | °C   |

# Electrical Characteristics (unless otherwise specified, $V_{DD} = 4.5 \sim 5.5 \text{ V}$ , $Ta = -40 \sim 85 ^{\circ}\text{C}$ )

| Characteristics          |                       | Symbol            | Test<br>Circuit | Test Condition                                                                             |                                                                  | Min                   | Тур. | Max                   | Unit |

|--------------------------|-----------------------|-------------------|-----------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| Operating supply voltage |                       | $V_{DD}$          | _               | _                                                                                          |                                                                  | 4.5                   | 5.0  | 5.5                   | V    |

| Operating supply current |                       | I <sub>DD</sub>   | _               | $f_{OSC} = 1.2 \text{ kHz}, \text{ No load}, $<br>$V_{DD} = 5 \text{ V}$                   |                                                                  |                       | 0.3  | 1.0                   | mA   |

| la serie de la serie     | "H" level             | V <sub>IH</sub>   |                 | All input pins                                                                             |                                                                  | V <sub>DD</sub> × 0.7 | ~    | V <sub>DD</sub>       | V    |

| Input voltage            | "L" level             | V <sub>IL</sub>   |                 |                                                                                            |                                                                  | GND                   | ~    | V <sub>DD</sub> × 0.3 |      |

| Input ourrent            | "H" level             | I <sub>IH</sub>   |                 | CMOS input                                                                                 | $V_{IH} = V_{DD}$                                                | -2                    | _    | 2                     |      |

| Input current            | "L" level             | I <sub>IL</sub>   |                 | pins, $V_{DD} = 5 \text{ V}$                                                               | V <sub>IL</sub> = GND                                            | -2                    | _    | 2                     | μΑ   |

| Pull-up resistance       |                       | R <sub>UP</sub>   | _               | $\overline{BL}$ , $\overline{LT}$ pins, $V_{DD} = 5 \text{ V}$ , $Ta = 25^{\circ}\text{C}$ |                                                                  | 50                    | 100  | 200                   | kΩ   |

| Output resistance        | Segment               | R <sub>seg</sub>  |                 | SEG0~SEG61 Output pins                                                                     | $V_{LC1} = V_{LC2}$ $= 1/2V_{DD}$ $V_{LC3} = GND$ $V_{DD} = 5 V$ | _                     | 0.6  | 3.0                   | kΩ   |

| Output resistance        | Common                | R <sub>COM</sub>  |                 | COM1~COM3 Output pins                                                                      |                                                                  | _                     | 0.5  | 3.0                   | K22  |

| Output current           | "H" level             | ІОН               |                 | SYNC ,<br>COM-OUT                                                                          | V <sub>OH</sub> = 4.5 V                                          | -0.2                  | -0.8 | _                     | mA   |

| Output current           | "L" level             | l <sub>OL</sub>   |                 | Output pins,<br>V <sub>DD</sub> = 5 V                                                      | V <sub>OL</sub> = 0.5 V                                          | 0.2                   | 1.0  | _                     | IIIA |

| Oscillation frequen      | Oscillation frequency |                   | _               | OSC Pin Operation Frequency                                                                |                                                                  | _                     | 1.2  | 50                    | kHz  |

| Max clock frequency      |                       | f <sub>CK</sub>   |                 | Refer to the timing chart as below.                                                        |                                                                  | 0                     | ~    | 2.0                   | MHz  |

| Clock pulse width        |                       | t <sub>CKW</sub>  |                 |                                                                                            |                                                                  | 250                   | _    | _                     | ns   |

| Data set time            |                       | t <sub>set</sub>  | _               |                                                                                            |                                                                  | 250                   | _    | _                     | ns   |

| Data hold time           |                       | t <sub>HOLD</sub> |                 |                                                                                            |                                                                  | 250                   | _    | _                     | ns   |

| CE pulse width           |                       | tcew              |                 |                                                                                            |                                                                  | 250                   | _    | _                     | ns   |

# **CE, CK, DATA Timing**

TC9240F

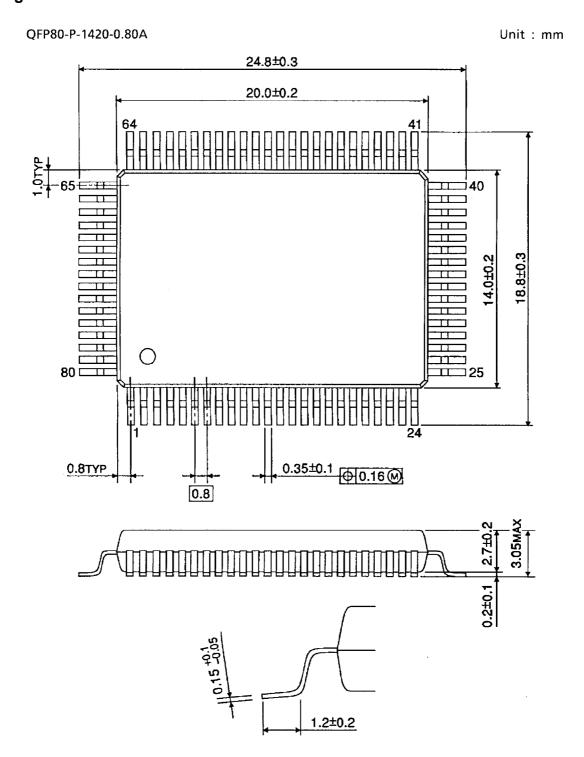

# **Package Dimensions**

Weight: 1.57 g (typ.)

#### **RESTRICTIONS ON PRODUCT USE**

030519EBA

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other

rights of the third parties which may result from its use. No license is granted by implication or otherwise under

any intellectual property or other rights of TOSHIBA CORPORATION or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.