TLCS-90 Series TMP90CM36

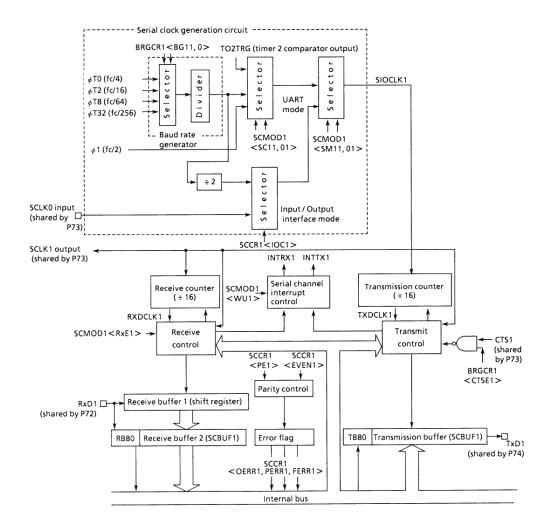

### **CMOS 8–Bit Microcontroller**

### TMP90CM36F/TMP90CM36T

#### 1. Outline and Characteristics

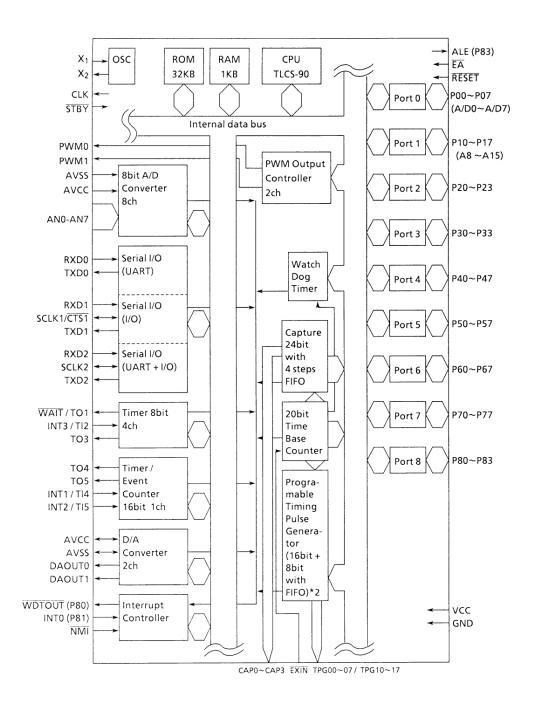

The TMP90CM36 is a high-speed, high performance 8-bit microcontroller developed for application in the control of various devices.

The TMP90CM36, CMOS 8-bit microcontroller, integrates an 8-bit CPU, ROM, RAM, A/D converter, D/A converter, multi-function timer/event counter, general-purpose serial interface, signal measure circuit, timing pulse generation circuit and PWM output in a single chip, and with which external program memory and data memory can be extended up to 31KB.

The TMP90CM36F is a device with an 80-pin flat package.

The TMP90CM36T is a device with an 84-pin QF (PLCC) package.

The following are the features of the TMP90CM36:

- (1) Highly efficient instruction set: 167 basic instructions Division and multiplication instructions, 16-bit operation instructions and bit operation instructions

- (2) Minimum instruction executing time: 250ns (at 16MHz oscillation frequency)

- (3) Built-in ROM: 32K bytes(4) Built-in RAM: 1K bytes

- (5) Memory extension capabilityExternal program memory: 31K bytesExternal data memory: 31K bytes

- (6) Interrupt functions: 18 internal, 5 external

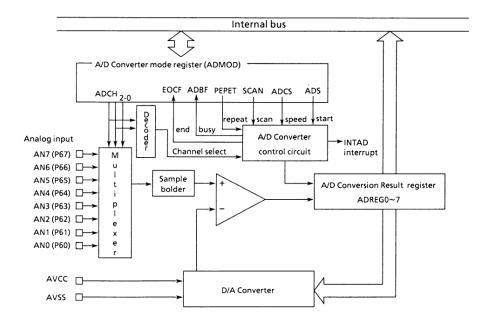

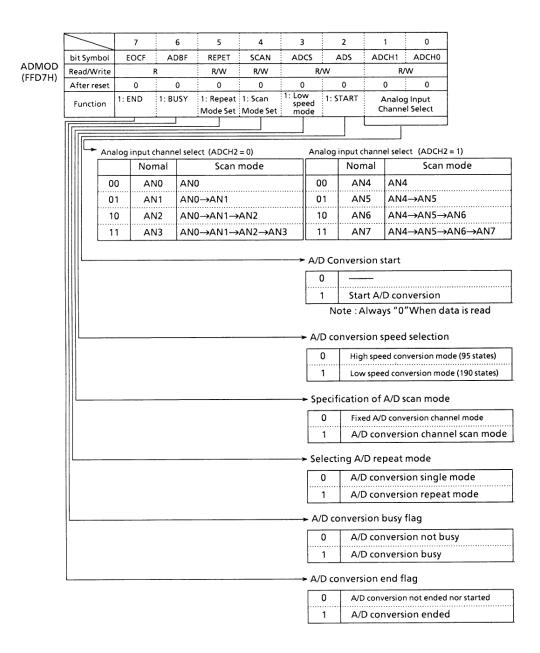

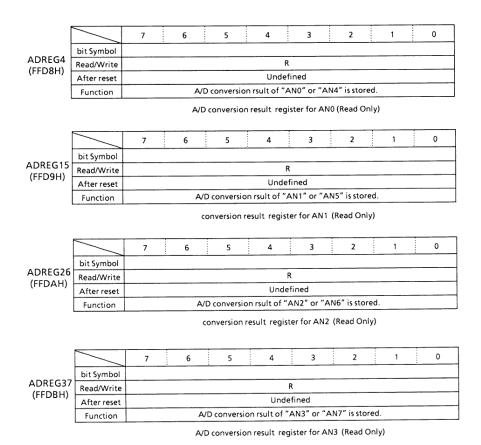

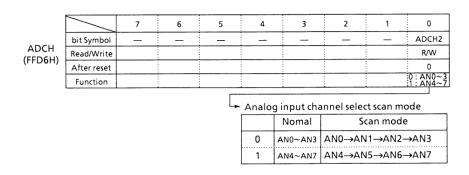

- (7) 8-bit A/D converter (8 channels)

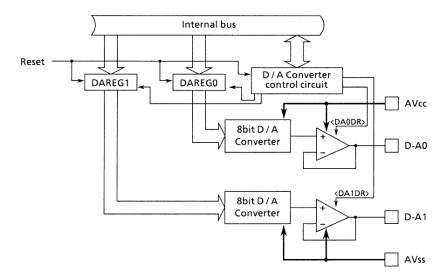

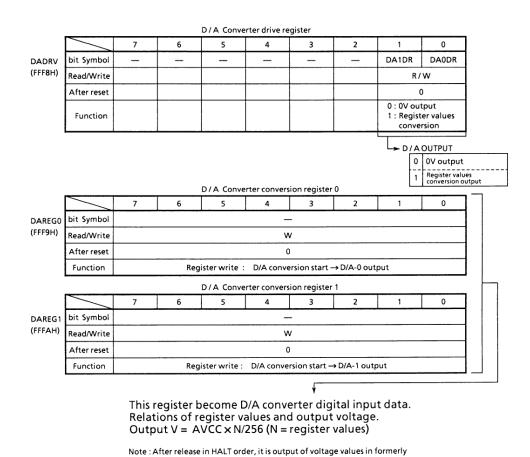

- (8) 8-bit D/A converter (2 channels)

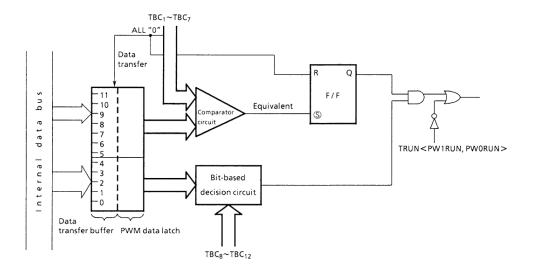

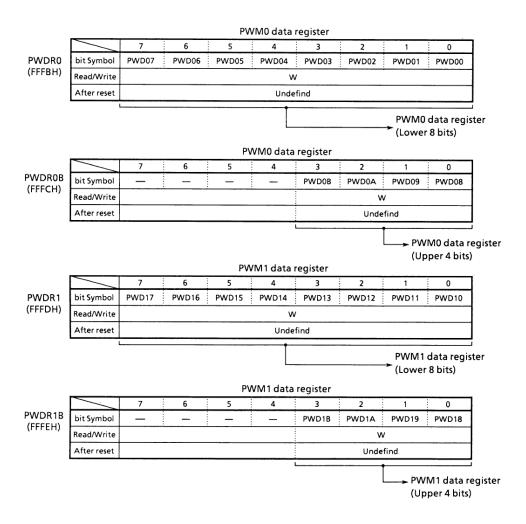

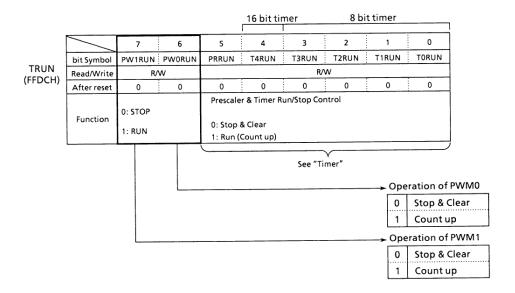

- (9) 12-bit D/A conversion (pulse width change of tone) output (2 channels)

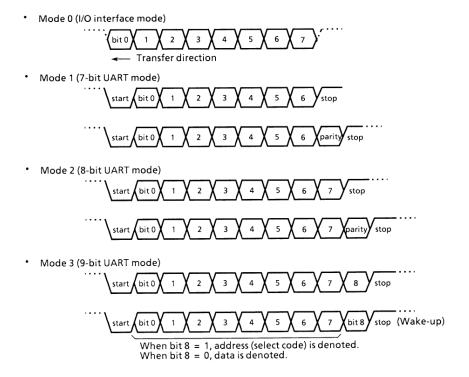

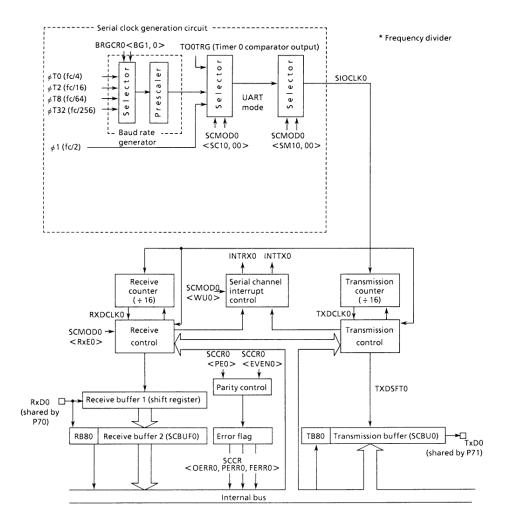

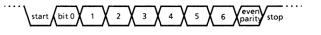

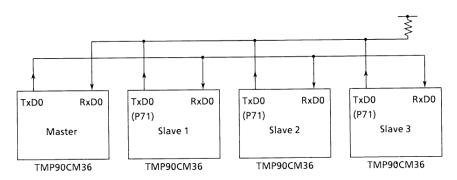

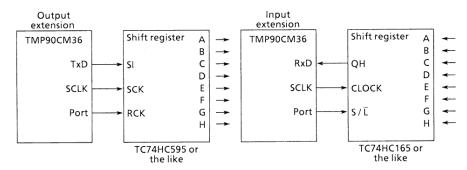

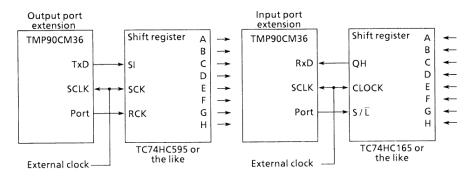

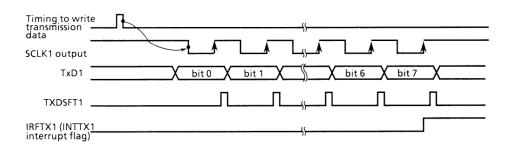

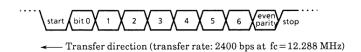

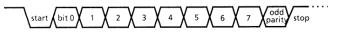

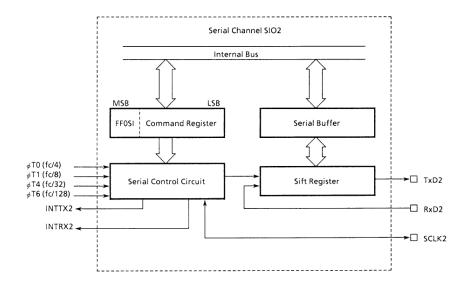

- (10) General-purpose serial interface mode (3 channels)

- With asynchronous mode and I/O interface mode (1 channel)

- With synchronous mode (1 channel)

- I/O interface mode (1 channels)

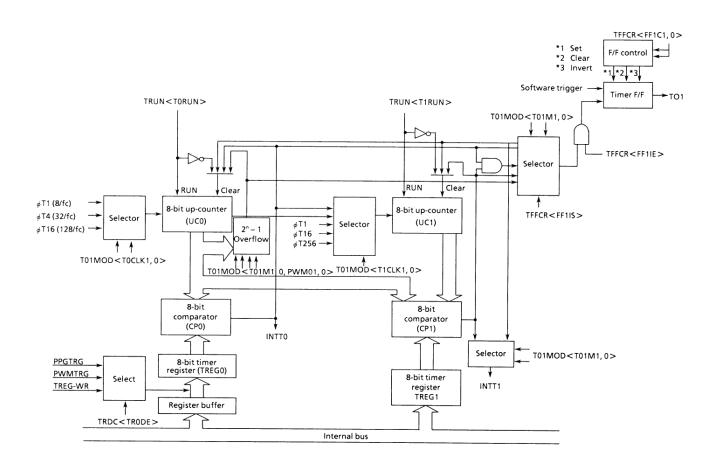

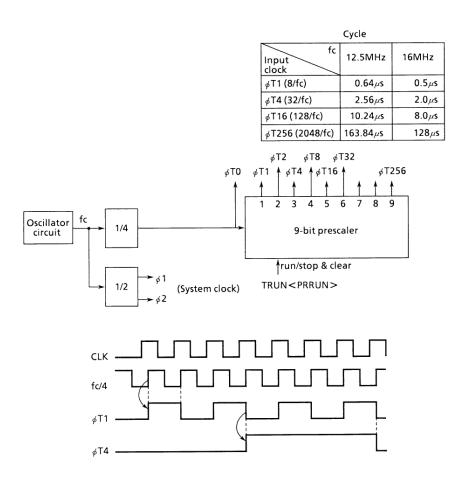

- (11) Timer function

- (1) 20-bit time base counter

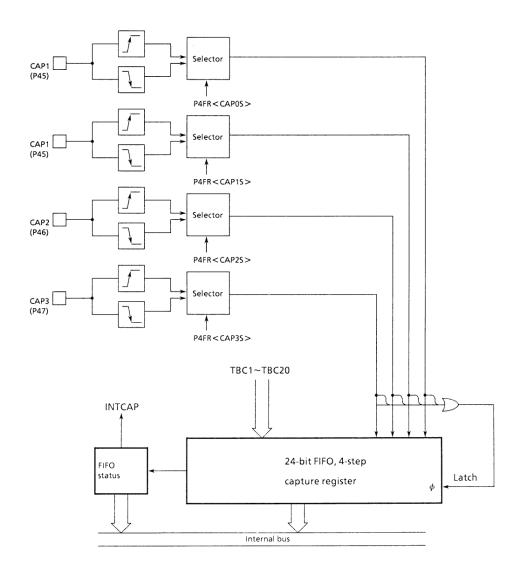

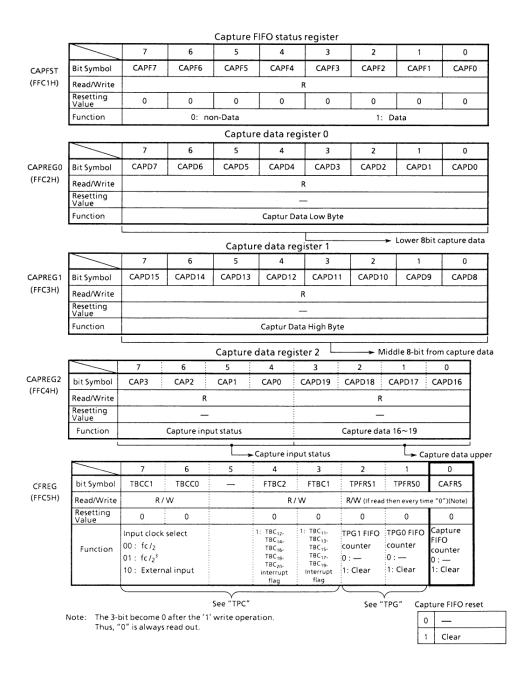

- (2) 24-bit capture with 4 step FIFO

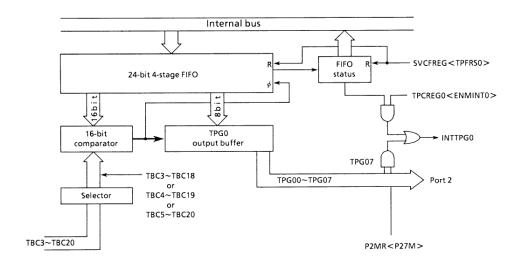

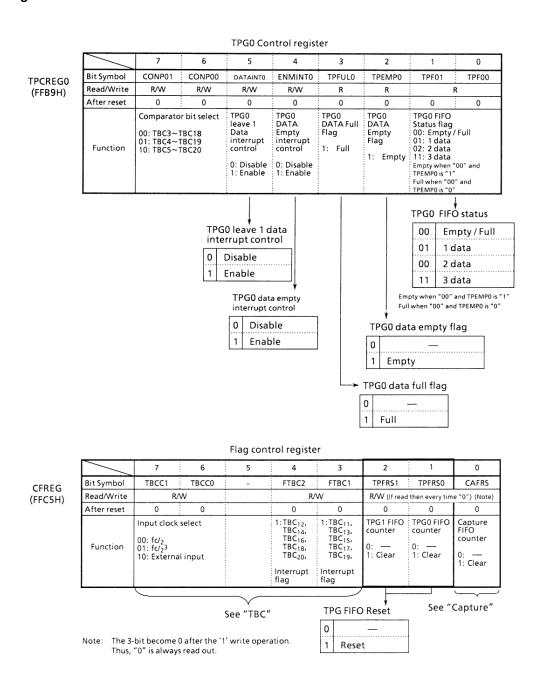

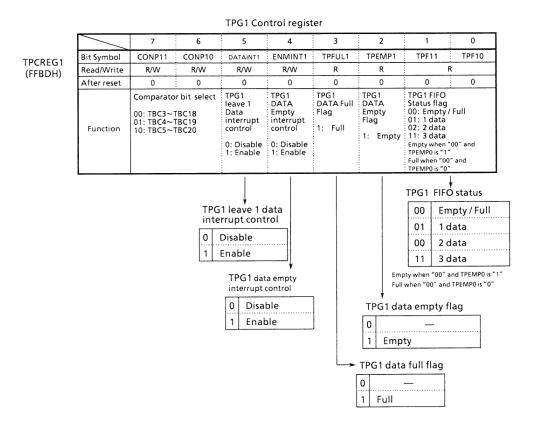

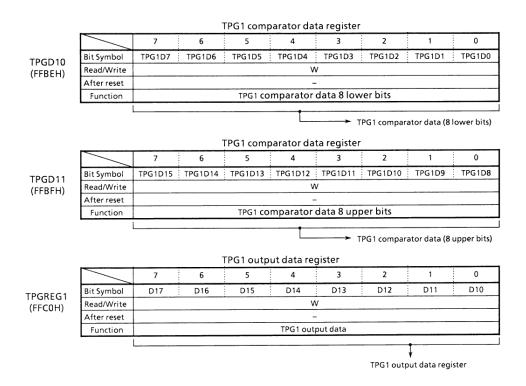

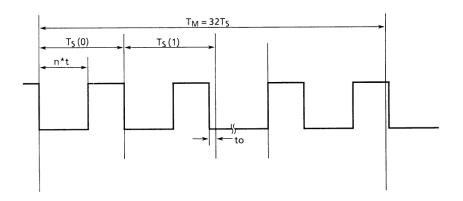

- (3) 24-bit timing pulse generation circuit (2 channels) (Comparator data 16-bit + timing output 8-bit) x 4 step FIFO

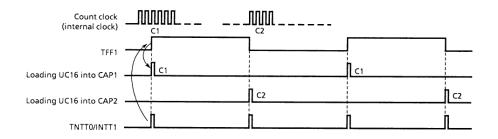

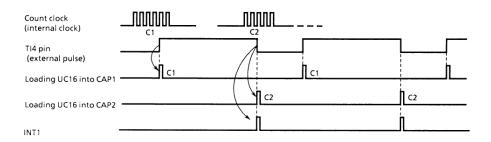

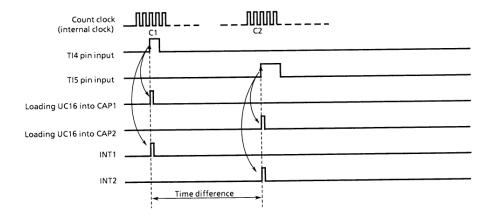

- (4) 16-bit timer/event counter (1 channel)

- ----- Built-in 2 capture register and 2 comparator

- (5) 8-bit timer (4 channels)

- ----- Built-in 1 comparator in each channel

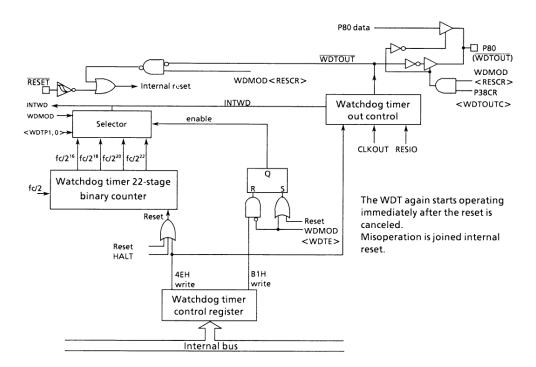

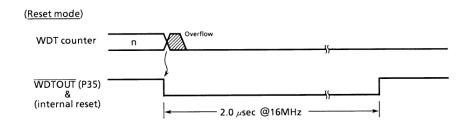

- (6) Watchdog timer function (WDTOUT pin having)

- (12) I/O ports: MAX64 pins

- (13) HDMA function (2 channels) ----- 1 byte transmission: 1.75µs (@16.0MHz)

- (14) Software standby function ----- RUN, STOP, IDLE modes

Hardware standby function ----- STOP mode

The information contained here is subject to change without notice

The information contained herein is presented only as guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. These TOSHIBA products are intended for usage in general electronic equipments, communication equipment, measuring equipment, domestic electrification, etc.) Please make sure that you consult with us before you use these TOSHIBA products in equipments which require high quality and/or reliability, and in equipments which could have major impact to the welfare of human life (atomic energy control, spaceship, traffic signal, combustion control, all types of safety devices, etc.). TOSHIBA cannot accept liability to any damage which may occur in case these TOSHIBA products were used in the mentioned equipments without prior consultation with TOSHIBA.

Figure 1. TMP90CM36 Block Diagram

# 2. Pin Assignment and Functions

### 2.1 Pin Layout Diagram

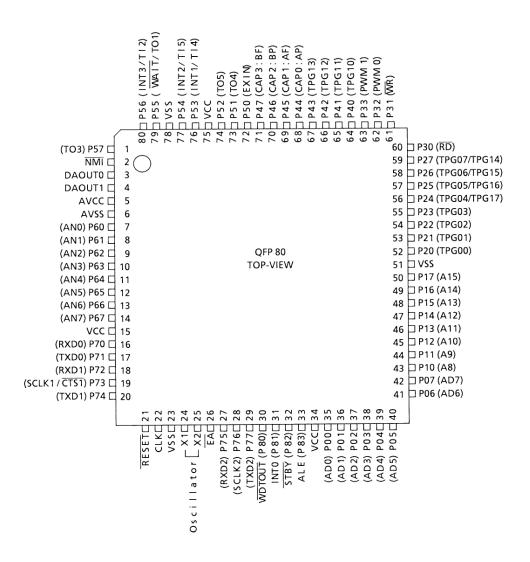

The assignment of input/output pins for TMP90CM36, their name and outline functions are described below.

Figure 2.1 (1) shows the pin assignment of TMP90CM36F.

Figure 2.1 (1). Pin Assignments (Flat Package)

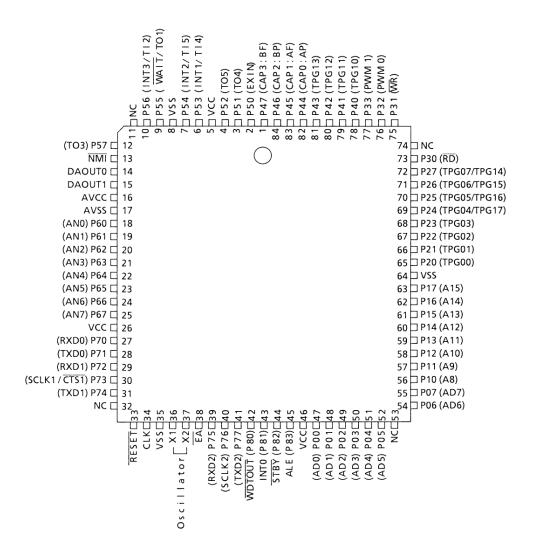

Figure 2.1 (2) shows the pin assignment of TMP90CM36T.

Figure 2.1 (2). Pin Assignments (QFJ (PLCC) Package)

# 2.2 Pin Names and Functions

The names of input/output pins and their functions are

described below. Table 2.2 Shows the input/output Pin Names and Functions.

Table 2.2. Pin Names and Functions (1/4)

| Pin name                   | No. of pins | I/O or<br>tristate | Function                                                                                                                                                                                                                           |

|----------------------------|-------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00~P07                    | 8           | I/O                | Port 0 : An 8-bit I/O port. Each bit can be set for input or output.                                                                                                                                                               |

| /AD0~AD7                   |             | Tristate           | Address/data bas: Operates as an 8-bit bi-directional address bus or data bus when using external memory. Operates port when built-in memory used.                                                                                 |

| P10~P17                    | 8           | I/O                | Port1: An 8-bit I/O port. Each bit can be set for input or output.                                                                                                                                                                 |

| /A8~A15                    |             | Output             | Address bus: Operates as the 8 upper bits of the address bus when using external memory.  Operates port when built-in memory used.                                                                                                 |

| P20~P27<br>/TPG00~         | 8           | I/O                | Port2: An 8-bit I/O port. Each bit can be set for input or output.                                                                                                                                                                 |

| TPG07<br>(TPG14~<br>TPG17) |             | Output<br>Tristate | TPG0 output: Operates of the TPG00~TPG07 output pin. 4 upper bits are shared in TPG14~TPG17. Operates as Reset at once of the 3 state condition. Operates output condition of agreement for output data write and comparator data. |

| P30                        | 1           | Output             | Port30: A 1-bit output port.                                                                                                                                                                                                       |

| /RD                        |             |                    | Read: Strobe signal output for reading external memory.                                                                                                                                                                            |

| P31                        | 1           | Output             | Port31: A 1-bit output port.                                                                                                                                                                                                       |

| ∕WR                        |             |                    | Write: Strobe signal output for writing external memory.                                                                                                                                                                           |

| P32, P33                   | 2           | I/O                | Port32, Port33: A 2-bit I/O port. Each bit can be set for input or output.                                                                                                                                                         |

| /PWM0,<br>PWM1             |             | Output<br>Tristate | Motor control output : PWM0/1 motor control output pin.                                                                                                                                                                            |

| P40~P43                    | 4           | I/O                | Port40~43: A 4-bit I/O port. Each bit can be set for input or output.                                                                                                                                                              |

| /TPG10~<br>TPG13           |             | Output<br>Tristate | TPG1output: Operates of the TPG10~TPG13 output pin. TPG14~TPG17 are shared in TPG04~07. Operates as Reset at once of the 3 state condition. Operates output condition of agreement for output data write and comparator data.      |

Table 2.2. Pin Names and Functions (2/4)

| Pin name           | No. of pins | I/O or<br>tristate | Function                                                                                                                           |

|--------------------|-------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|

| P44~P47<br>/CAP0~  | 4           | I/O                | Port44~47: A 4-bit I/O port. Each bit can be set for input or output.                                                              |

| CAP3               |             | Input              | Capture input : CAP0~CAP3 input pin.                                                                                               |

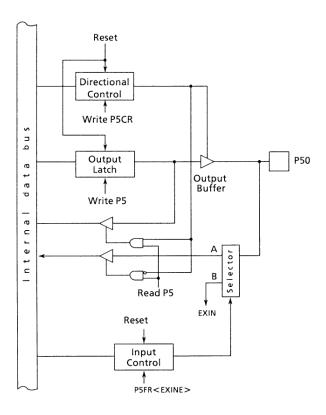

| P50                | 1           | I/O                | Port50: A 1-bit I/O port.                                                                                                          |

| /EXIN              |             | Input              | Time base counter to external clock input pin.                                                                                     |

| P51                | 1           | I/O                | Port51: A 1-bit I/O port.                                                                                                          |

| /ТО4               |             | Output             | Timer Output4: Timer 4 output pin.                                                                                                 |

| P52                | 1           | 1/0                | Port52: A 1-bit I/O port.                                                                                                          |

| /ТО5               |             | Output             | Timer Output5: Timer 5 output pin.                                                                                                 |

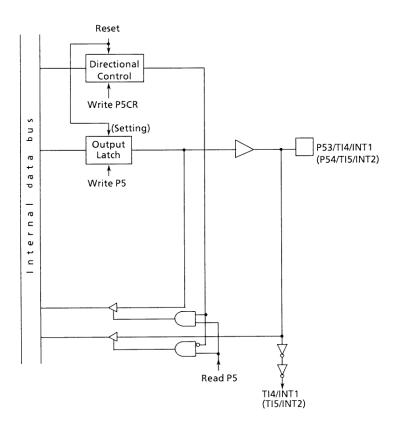

| P53                | 1           | I/O                | Port53: A 1-bit I/O port.                                                                                                          |

| /INT1              |             | Input              | Interrupt request pin1: A rising/falling edge programmable interrupt request pin.                                                  |

| /TI4               |             | Input              | Timer input4: Timer 4 counter input pin.                                                                                           |

| P54                | 1           | I/O                | Port54: A 1-bit I/O port.                                                                                                          |

| /INT2              |             | Input              | Interrupt request pin2: A rising edge interrupt request input pin.                                                                 |

| /TI5               |             | Input              | Timer input5: Timer 5 counter input pin.                                                                                           |

| P55                | 1           | 1/0                | Port55: A 1-bit I/O port.                                                                                                          |

| /TO1/WAIT          |             | Output /           | Timer output0/1: Timer 0 or timer 1 output.  / Wait: Input pin for connecting a memory or peripheral LSI with delayed access time. |

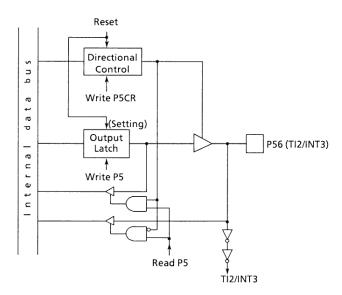

| P56                | 1           | I/O                | Port56: A 1-bit I/O port.                                                                                                          |

| /TI2               |             | Input              | Timer input2/3: Timer 2 or Timer 3 counter input pin.                                                                              |

| /INT3              |             | Input              | Interrupt request pin3: A rirising edge interrupt request input pin.                                                               |

| P57                | 1           | I/O                | Port57: A 1-bit I/O port.                                                                                                          |

| /ТОЗ               |             | Output             | Timer Output2/3: Timer 2 or Timer 3 output.                                                                                        |

| NMI                | 1           | Input              | Non-maskable Interrupt request pin: A falling edge interrupt request pin (Sctimitt input).                                         |

| /DAOUT0,<br>DAOUT1 | 2           | Output             | D/A Output: D/A converter 0/1 analog current output pin.                                                                           |

Table 2.2. Pin Names and Functions (3/4)

| Pin name | No. of pins | I/O or<br>tristate | Function                                                                                                                                           |

|----------|-------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| AVCC     | 1           | Input              | Reference Voltage to A/D converter.                                                                                                                |

| AVSS     | 1           | Input              | GND pin for A/D converter (0V).                                                                                                                    |

| P60~P67  | 8           | Input              | Port60~67: An 8-bit input ports.                                                                                                                   |

| /AN0~AN7 |             |                    | Analog input: 8 analog inputs to A/D converter.                                                                                                    |

| vcc      | 2           | Input              | Power supply pin ( + 5V).                                                                                                                          |

| VSS      | 3           | Input              | GND pin (0V).                                                                                                                                      |

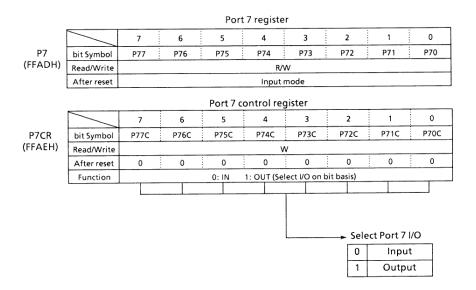

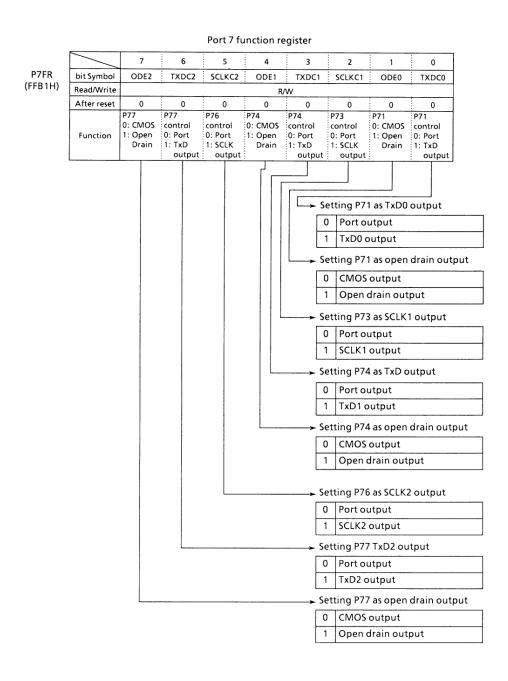

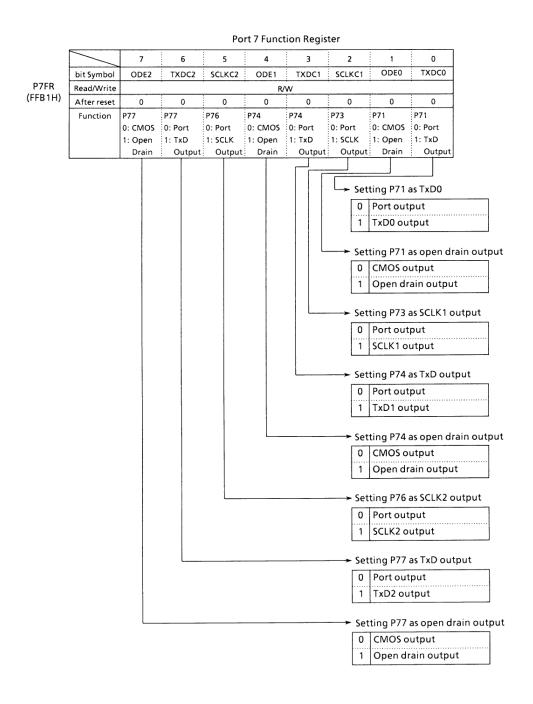

| P70      | 1           | I/O                | Port70: A 1-bit I/O port.                                                                                                                          |

| /RXD0    |             | Input              | Serial channel 0 receive data input pin.                                                                                                           |

| P71      | 1           | I/O                | Port71: A 1-bit I/O port.                                                                                                                          |

| /TXD0    |             | Output             | Serial channel 0 send data output pin.                                                                                                             |

| P72      | 1           | I/O                | Port72: A 1-bit I/O port.                                                                                                                          |

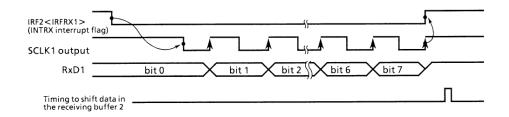

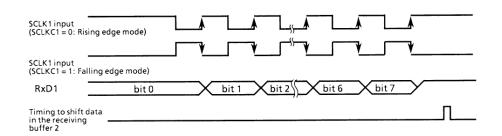

| /RXD1    |             | Input              | Serial channel 1 receive data input pin.                                                                                                           |

| P73      | 1           | I/O                | Port73: A 1-bit I/O port.                                                                                                                          |

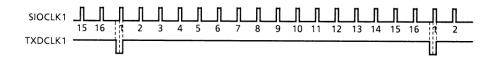

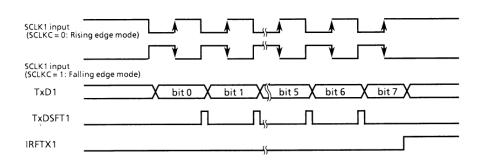

| /SCLK1   |             | I/O                | Serial clock I/O : External clock for SCLK1 do input or send clock for internal boudrate generator do output when I/O interface mode is condition. |

| /CTS1    |             | Input              | CTS1 input pin: Serial data send possible signal (Clear To Send).                                                                                  |

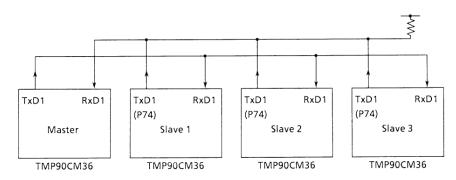

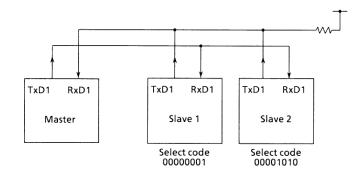

| P74      | 1           | I/O                | Port74: A 1-bit I/O port.                                                                                                                          |

| /TXD1    |             | Output             | Serial channel 1 send data output pin.                                                                                                             |

| P75      | 1           | I/O                | Port75: A 1-bit I/O port.                                                                                                                          |

| /RXD2    |             | Input              | Serial channel 2 receive data input pin.                                                                                                           |

| P76      | 1           | 1/O                | Port76: A 1-bit I/O port.                                                                                                                          |

| /SCLK2   |             | I/O                | Serial clock I/O: External clock for SCLK2 do input or send clock for internal boudrate generator do output when I/O interface mode is condition.  |

| P77      | 1           | 1/0                | Port77: A 1-bit I/O port.                                                                                                                          |

| /TXD2    |             | Output             | Serial channel 2 send data output pin.                                                                                                             |

| RESET    | 1           | Input              | Reset: Reset input pin to initialize the TMP90CM36.                                                                                                |

Table 2.2. Pin Names and Functions (4/4)

| Pin name | No. of pins | I/O or<br>Tristate | Function                                                                                                                         |  |  |  |  |  |  |

|----------|-------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| CLK      | 1           | Output             | Clock output: Output 1/4 frequency of the clock oscillation. Pulled up during reset.                                             |  |  |  |  |  |  |

| X1, X2   | 2           | I/O                | The crystal oscillator connectopn pin.                                                                                           |  |  |  |  |  |  |

| ĒĀ       | 1           | Input              | External access: Connects to the Vcc pin when the TMP90CM36 built-in ROM is used.                                                |  |  |  |  |  |  |

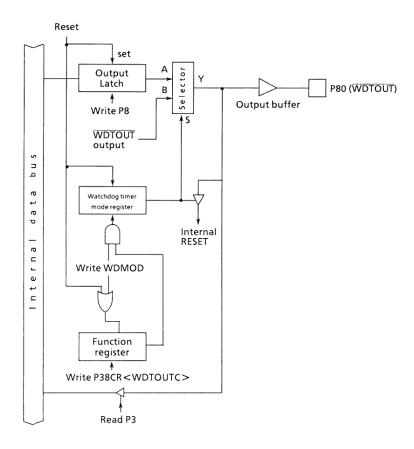

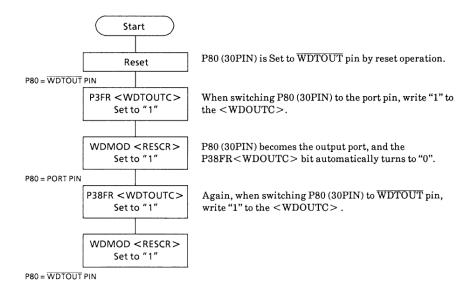

| P80      | 1           | Output             | Port80: A 1-bit output port.                                                                                                     |  |  |  |  |  |  |

| /WDTOUT  |             | Output             | Wachdog out: Operates WDTOUT output pin when watchdog timer register is D1 = 1                                                   |  |  |  |  |  |  |

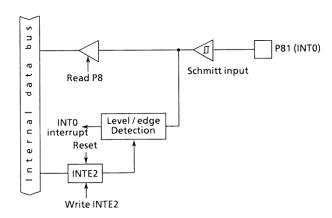

| P81      | 1           | Input              | Port81: A 1-bit input port.                                                                                                      |  |  |  |  |  |  |

| /INT0    |             | Input              | Interrupt request pin0: A level/rising edge programmable interrupt request pin.                                                  |  |  |  |  |  |  |

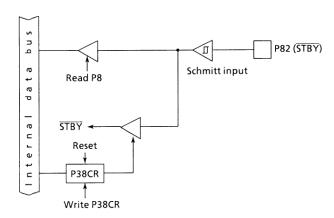

| P82      | 1           | Input              | Port82: A 1-bit input port.                                                                                                      |  |  |  |  |  |  |

| /STBY    |             | Input              | Hardware standby input pin (schmitt input).                                                                                      |  |  |  |  |  |  |

| P83      | 1           | Output             | Port83: A 1-bit output port.                                                                                                     |  |  |  |  |  |  |

| /ALE     |             | Output             | Address latch enable : The falling edge of this signal is used for latching addresses on AD0-AD7 when accessing external memory. |  |  |  |  |  |  |

# 3. Operation

This section explains the functions and basic operations of the TMP90CM36 in blocks.

#### 3.1 CPU

The TMP90CM36 has a built-in high performance 8 bit CPU. For the operation of the CPU, see the book TLCS 90 Series CPU Core Architecture.

This section explains the CPU functions unique to the TMP90CM36 that are not explained in that book.

#### 3.1.1 Reset

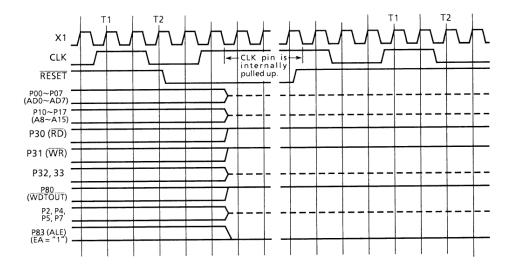

Figure 3.1 (1) shows the basic timing of reset.

To reset the TMP90CM36, it is required that the power supply voltage is within operating range, the internal oscillator is stably functioning, and RESET input be kept at "0" for at least 10 system clocks (10 states: 2 microseconds with 10MHz system clock)

When a reset is accepted, among I/O common ports, port 0 (address data bus A0 - A7), port 1 (address data bus A8 - A15) and port 2 are set to input status (with high impedance). Output ports P30 (RD) and P31 (WR) and CLK are set to "1" and ALE (P83) is cleared to "0".

CPU registers and external memory are not changed. However, program counter PC and interrupt enable/disable flag IFF are cleared to "0". The A register becomes undefined.

When the reset is released, instruction execution starts from address 0000H.

Figure 3.1 (1). Reset Timing of TMP90CM36

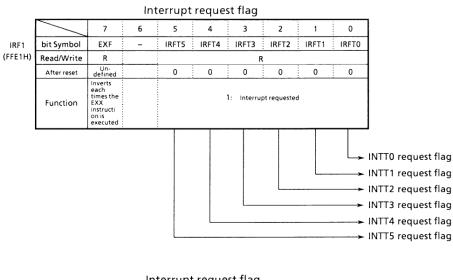

# 3.1.2 EXF (Exchange Flag)

The exchange flag EXF is inverted when the EXX instruction is executed to exchange data between the TMP90CM36 main

registers and auxiliary registers. This flag is assigned to bit 7 at memory address FFE1H.

IRF1 (FFE1H)

|             | 7                                                   | 6 | 5     | 4     | 3     | 2                            | 1     | 0     |

|-------------|-----------------------------------------------------|---|-------|-------|-------|------------------------------|-------|-------|

| bit Symbol  | EXF                                                 | _ | IRFT5 | IRFT4 | IRFT3 | IRFT2                        | IRFT1 | IRFT0 |

| Read/Write  | R                                                   |   |       |       |       | R                            |       |       |

| After reset | Un-deFined                                          |   | 0     | 0     | 0     | 0                            | 0     | 0     |

| Function    | Inverts each times the EXX instructio n is executed |   |       |       | •     | Request Flag<br>rrently requ | -     |       |

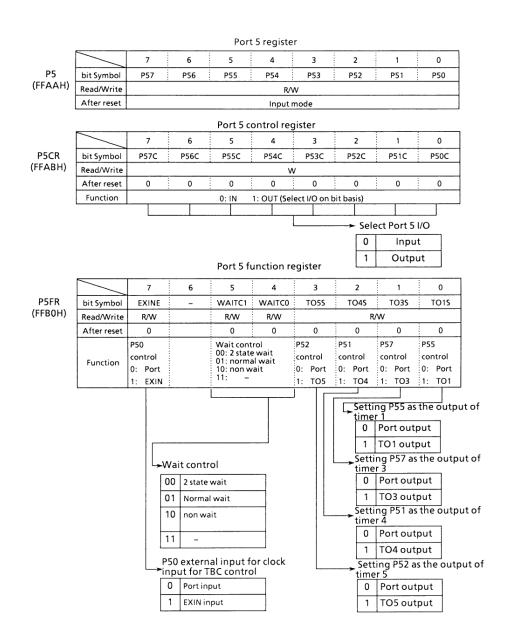

# 3.1.3 Wait Control

to bits 4 and 5 at memory address FFB4H.

For the TMP90CM36, a wait control register (WAITC) is assigned

P5FR (FFB4H)

|             | 7                                    | 6 | 5                                                      | 4                    | 3    | 2    | 1                                   | 0                                   |

|-------------|--------------------------------------|---|--------------------------------------------------------|----------------------|------|------|-------------------------------------|-------------------------------------|

| bit Symbol  | EXINE                                | - | WAITC1                                                 | WAITC0               | TO5S | T04S | T03S                                | TO15                                |

| Read/Write  | R/W                                  |   | R/W                                                    | R/W                  |      | R/   | w                                   |                                     |

| After reset | 0                                    |   | 0                                                      | 0                    | 0    | 0    | 0                                   | 0                                   |

| Function    | P50<br>Control<br>0: Port<br>1: EXIN |   | WAIT Cont<br>00: 2 sta<br>01: norn<br>10: non<br>11: - | ite wait<br>nal Wait |      |      | P57<br>Control<br>0: Port<br>1: TO3 | P55<br>Control<br>0: Port<br>1: TO1 |

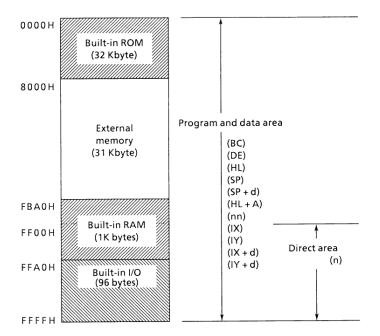

### 3.2 Memory Map

The TMP90CM36 can provide a maximum 64K byte program memory and data memory.

The program and data memories may be allocated to the addresses 0000H ~ FFFFH.

#### (1) Built-in ROM

The TMP90CM36 has an internal 32K byte ROM. This ROM is located at addresses 0000H ~ 7FFFH. Program execution starts from address 000H after a reset operation.

Addresses  $0008H \sim 0078H$  in the internal ROM area are used as the interrupt processing entry area.

### (2) Built-in RAM

The TMP90CM36 contains a 1K byte built-in RAM which is allocated to the addresses FBA0H ~ FF9FH.

The CPU can also access some portions of the RAM (160 byte area FF00H ~ FF9FH) using short instruction codes in the direct addressing mode.

## (3) Built-in I/O

The TMP90CM36 uses 96 bytes of the address space as a built-in I/O area. The area is allocated to the addresses FFA0H ~ FFFFH. The CPU can access the built-in I/O using short instruction codes in the direct addressing mode.

Figure 3.2 shows the memory map and the access ranges of the CPU for each addressing mode.

Figure 3.2. Memory Map

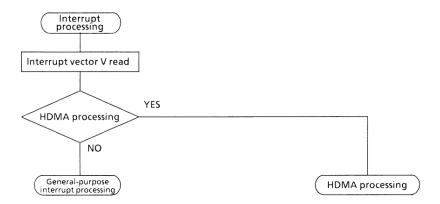

#### 3.3 Interrupt Functions

The TMP90CM36 has a general-purpose interrupt processing routine for responding to both internal and external interrupt request, and a high-speed micro DMA (HDMA) processing mode in which the CPU automatically transfers data.

Immediately after a reset is released, all responses to

interrupt requests are set to the general-purpose interrupt processing mode.

The high-speed DMA processing mode can be set by loading a vector value to the DMAV 0/1 register.

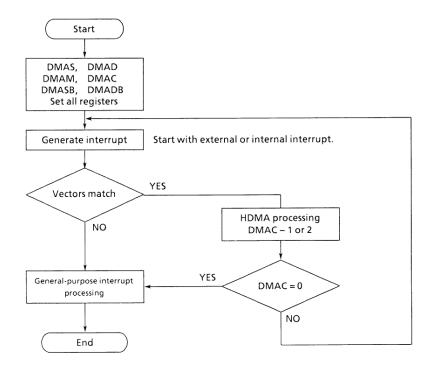

Figure 3.3 (1) shows the interrupt response flow.

Figure 3.3 (1). Interrupt Response Flow

When an interrupt request is generated, this is reported to the CPU via the built-in interrupt controller. If the request is for a non-maskable interrupt or an enabled maskable interrupt, the CPU starts interrupt processing. If for a disabled maskable interrupt, the request is ignored and not received.

If the interrupt is received, the CPU first reads the interrupt vector from the built-in interrupt controller to determine the source of the interrupt request.

Next, a check is made as to whether this request is for general-purpose interrupt processing, micro DMA processing or high-speed DMA (HDMA) processing, and then the corresponding processing is performed.

The interrupt vector is read in an internal operation cycle so the bus cycle becomes a dummy cycle.

#### 3.3.1 General-Purpose Interrupt Processing

Figure 3.3 (2) shows the general-purpose interrupt processing flow.

The CPU first saves the contents of the program counter PC and register AF (including the interrupt enable/disable flag IFF immediately before an interrupt) to the stack and then

resets the interrupt enable/disable flag IFF to "0" (interrupt disable). Finally, the interrupt vector contents [V] are transferred to the program counter and a jump is made to the interrupt processing program.

There is a 20-state overhead from the time when the interrupt is received until the jump is made to the interrupt processing program.

Figure 3.3 (2). General-Purpose Interrupt Processing Flow

Interrupt processing program is ended with the RETI instruction for both maskable and non-maskable interrupts.

Executing this instruction restores the program counter PC and register AF contents from the stack. (Resets the interrupt enable/disable flag immediately before an interrupt.)

When the CPU reads the interrupt vector, the interrupt request source confirms that the interrupt has been received and then clears the interrupt request. Non-maskable interrupts cannot be disabled by program. Maskable interrupts, however, can be enabled and disabled by program. Bit 5 of CPU reg-

ister F is an interrupt enable/disable flipflop (IFF). Interrupts are enabled by setting this bit to "1" with the EI (interrupt enable) instruction and disabled by resetting this bit to "0" with the DI (interrupt disable) instruction. IFF is reset to "0" by resetting and when an interrupt is received (including non-maskable interrupts).

The El instruction is actually executed after the next instruction is executed.

Table 3.3 (1) shows the interrupt sources.

Table 3.3 (1) Interrupt Sources

| Prio-<br>rity<br>sea- | Туре     | Interrupt          | Interrupt<br>vector | General<br>purpose<br>interrupt | Interrupt so       | ources   | Comments   |

|-----------------------|----------|--------------------|---------------------|---------------------------------|--------------------|----------|------------|

| uence                 | .,,,,,   | name               | value               | processing start<br>address     | Internal           | External | Comments   |

| 1                     | Non      | SWI<br>instruction | 10H                 | 0010H                           | 0                  | _        | -          |

| 2                     | maskable | NMI                | 18H                 | 0018H                           | -                  | NMI pin  | -          |

| 3                     |          | INTWD              | 20H                 | 0020H                           | WDT                | _        | -          |

| 4                     |          | INT0               | 28H                 | 0028H                           | -                  | INT0 pin | External 0 |

| 5                     |          | INTCAP             | 30H                 | 0030H                           | Capture Input      | _        | Capture    |

| 6                     |          | INTTPG0            | 38H                 | 0038H                           | TPG0               | _        | TPG        |

| 7                     |          | INTTPG1            | 40H                 | 0040H                           | TPG1               | _        | TPG        |

| 8                     |          | INTRX0             | 48H                 | 0048H                           | Serial receive and | _        | SIO        |

| 9                     |          | INTTX0             | 50H                 | 0050H                           | Serial send end    | _        | SIO        |

| 10                    | maskable | INTT0              | 58H                 | 0058H                           | Timer 0            | _        | Timer      |

| 11                    |          | INTT1              | 60H                 | 0060H                           | Timer 1            | _        | Timer      |

| 12                    |          | INTT2              | 68H                 | 0068H                           | Timer 2            | _        | Timer      |

| 13                    |          | INTAD              | 70H                 | 0070H                           | AD                 | _        | AD         |

| 14                    |          | INTT3              | 78H                 | 0078H                           | Timer 3            | _        | Timer      |

| 15                    |          | INTT4              | 80H                 | 0080H                           | Timer 4            | _        | Timer      |

| 16                    |          | INT1               | 88H                 | 0088H                           | -                  | INT1 pin | External 1 |

| 17                    |          | INTT5              | 90H                 | 0090H                           | Timer 5            | _        | Timer      |

| 18                    |          | INT2               | 98H                 | 0098H                           | -                  | INT2 pin | External 2 |

| 19                    |          | INTRX1             | A0H                 | 00A0H                           | Serial receive and | _        | SIO        |

| 20                    |          | INTTX1             | A8H                 | H8A00                           | Serial send end    | _        | SIO        |

| 21                    |          | INT3               | вон                 | 00B0H                           | -                  | INT3 pin | External 3 |

| 22                    |          | INTRX2             | ввн                 | 00B8H                           | Serial receive and | -        | SIO        |

| 23                    |          | INTTX2             | СОН                 | 00C0H                           | Serial send end    | _        | SIO        |

The "priority sequence" shown in Table 3.3 (1) indicates the sequence in which interrupt sources are received by the CPU when multiple interrupt requests are generated simultaneously.

For example, if interrupt requests with the priority sequences 4 and 5 are generated simultaneously, the CPU will receive the interrupt request with priority sequence 4 first. When processing of the interrupt with priority sequence 4 is ended with the RETI instruction, the CPU will then receive the interrupt with priority sequence 5.

If the interrupt processing program for the priority

sequence 4 interrupt is interrupted by executing the El instruction, the CPU will receive the priority sequence 5 interrupt request. When multiple interrupt requests are generated simultaneously, the built-in interrupt controller only determines the priority sequence of the interrupt sources received by the CPU. There is no function to compare the priority sequence of the interrupt currently being processed and the interrupt currently being requested.

Another interrupt can be enabled while another interrupt is being processed by resetting the interrupt enable/disable flag IFF to enable.

## 3.3.2 High-Speed Micro DMA Processing

The TMP90CM36 has two built-in DMA channels called HDMA.

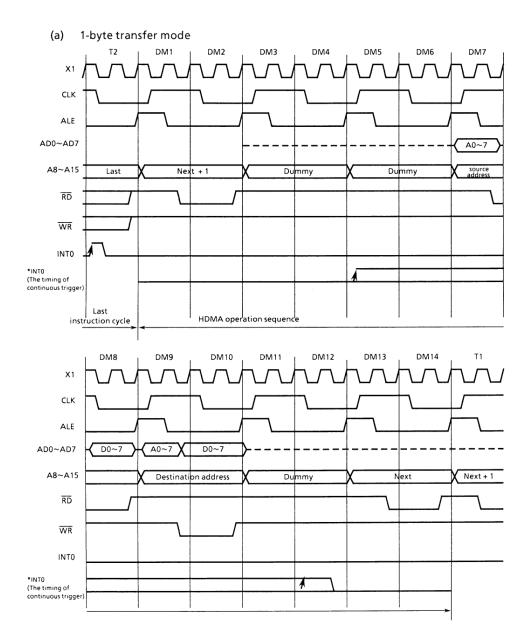

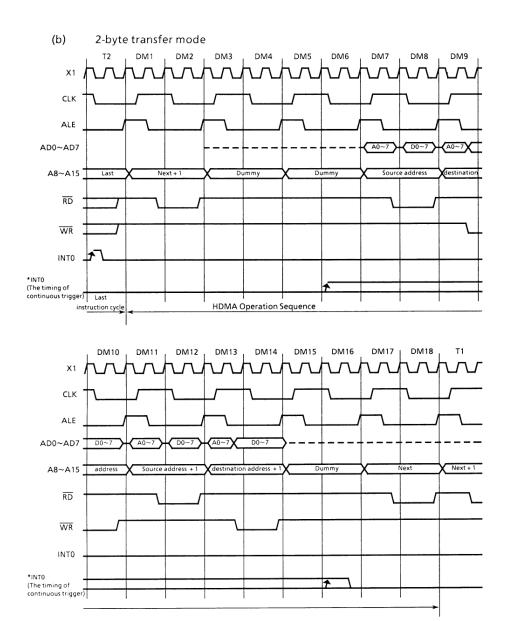

HDMA has three times the processing capacity of  $\mu$ DMA and is used for high-speed data transfers. HDMA execution time (decrease the value of transfer number and the value is

not "0" data) is 14 states, regardless of whether the 1-byte transfer mode or 2-byte transfer mode is used. HDMA and micro DMA (the TMP90CM36 has not the micro DMA) transfer speeds.

Table 3.3 (3) shows the high-speed micro.

Table 3.3 (3) Transfer Speeds

| fxtal (MHz) | HDMA    | Micro DMA |                      |

|-------------|---------|-----------|----------------------|

| 10          | 2.8 μs  | 9.2 μs    | * At 1 byte transfer |

| 12.5        | 2.24 μs | 7.36 μs   | mode.                |

| 16          | 1.75 μs | 5.75 μs   |                      |

Table 3.3 (4) Shows the DHMA Functions

| Number of channels    | 2                                                          |

|-----------------------|------------------------------------------------------------|

| Transfer speed        | 14 states (for 1 byte) or 18 states (for 2 bytes)          |

| Start method          | By interrupt (all external and internal interrupt sources) |

| Transfer mode         | 1-byte transfer or 2-byte transfer                         |

| Address output method | Dual address (source/destination)                          |

| Access area           | 0~8M-byte memory area (64k-byte units)                     |

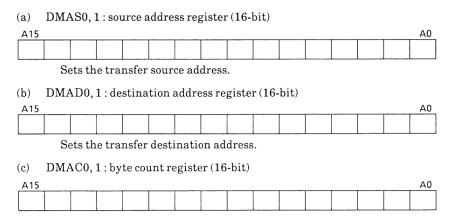

## (1) HDMA Setting Registers

HDMA operation.

The following describes the registers required for

Sets the number of bytes to be transferred.

The set value is decremented (-1) for each HDMA started. A generation purpose interrupt is when the value reaches "0".

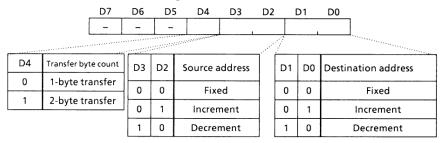

(d) DMAM0, 1: transfer mode register (8-bit)

This register determines the HDMA transfer mode.

The bits of this register are as shown in the table above.

The source and destination addresses shown here are the addresses loaded to DMAS0, 1 and DMAD0, 1 above.

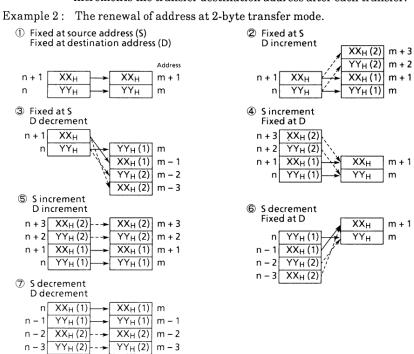

#### Example 1: $\times \times \times 00001$

Transfers 1 byte, fixes transfer source address (DMASO, 1), and increments the transfer destination address after each transfer.

Note: It is ineffective to set decrement for a destination address when a source address being increment; and to set increment for a destination address when a source address being decrement.

#### (e) DMAV0, 1: DMA vector register

| DMAV0   |                    | 7    | - | 6    | : | 5    | : | 4    |   | 3    | 2    | 1    | 0    |

|---------|--------------------|------|---|------|---|------|---|------|---|------|------|------|------|

|         | bit Symbol         | DV07 |   | DVO6 |   | DV05 |   | DV04 |   | DV03 | DV02 | DV01 | DV00 |

| (FFE8H) | Read/Write         |      |   |      |   |      |   |      | w |      |      |      |      |

|         | Resetting<br>Value | 0    |   | 0    |   | 0    |   | 0    |   | 0    | 0    | 0    | 0    |

|         |                    | 7    | 6    | 5   |   | 4    | 3    | 2    | 1    | 0    |  |

|---------|--------------------|------|------|-----|---|------|------|------|------|------|--|

|         | bit Symbol         | DV17 | DV16 | DV1 | 5 | DV14 | DV13 | DV12 | DV11 | DV10 |  |

| (FFEBH) | Read/Write         | W    |      |     |   |      |      |      |      |      |  |

|         | Resetting<br>Value | 0    | 0    | 0   |   | 0    | 0    | 0    | 0    | 0    |  |

HDMA is started by interrupts. Consequently, the vector address of the interrupt that assigns HDMA start is loaded to the DMA vector register (DMAV0/1).

HDMA compares the interrupt vector and the contents of this register. If they match, HDMA operation starts.

It is necessary to set the vector address before generating the interrupt that starts HDMA.

### (2) Register Loading

- (a) DMASO, 1

DMADO, 1

Loaded with the LDC instruction.

DMACO, 1

DMAMO, 1

(\* The LDC instruction is a new TLCS-90 instruction.)

- (b) DMAV0, 1 Load the input / output address with the LD instruction. (See the separate address map concerning input / output addresses.)

# (3) HDMA Start

HDMA can be started by any of the following TMP90CM36 maskable interrupt sources

- (a) Internal start factors

- SWI (software)

- All internal I/O interrupts

Assign starting of HDMA channel 0 or channel 1 to the INT0 - INT3 external interrupts, connect any of the bits of ports 0 - 8 (output mode) externally to INT0 - INT3 to generate a start interrupt.

- (b) External start factors

- $\overline{\text{NMI}}$  pin

- INT0 ~ 3 pin

(4) HDMA Channel 0 and Channel 1 Priority Sequence

The channel where an interrupt is generated first has priority.

Note: HDMA, regardless of an interrupt enable flag, compares the vector and the values of the DMA V0/1 register. If they match in El mode, the HDMA starts.

Do not write the vector value of the non-maskable interrupt to the DMA V0/1 register. If doing so, the HDMA does not operate normally. To stop the HDMA from being started, set DI mode before generating the interrupt to start the HDMA, or set the DMA V0/1 register to 00H.

## (5) HDMA Operation Flow

Figure 3.3 (6). HDMA Operation Flow

18

# (6) HDMA Operation Timing

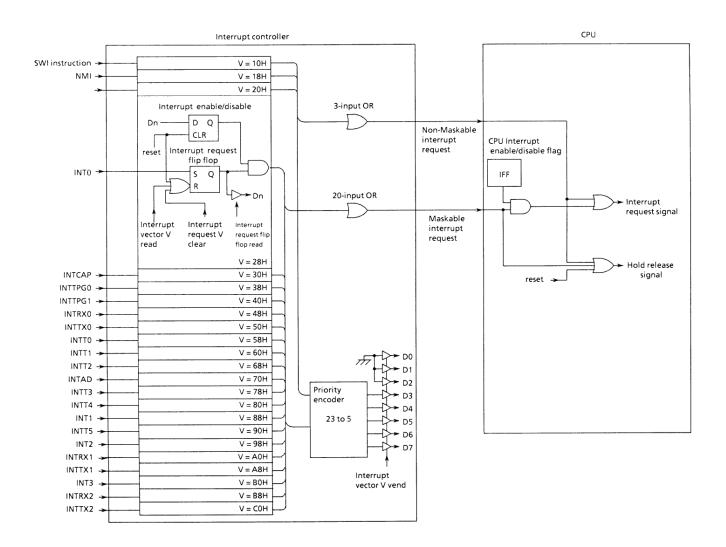

#### 3.3.3 Interrupt Controller

Figure 3.3 (9) shows an abbreviated interrupt circuit diagram. The left half of this diagram shows the interrupt controller and the right half shows the CPU interrupt request signal circuit and hold release circuit.

The interrupt controller has an interrupt request flipflop and interrupt enable/disable flag for each interrupt channel (total: 23 channels), and a micro DMA enable/disable flag. The interrupt request flipflop latches interrupt requests that arrive from the periphery. This flipflop is reset to "0" when there is a reset, when the CPU receives an interrupt and reads the vector of that interrupt channel, and when an instruction that clears the interrupt request (writes "vector value/8" to memory address FFEOH) for that channel is executed.

LD (0FFE0H), 60H/8

For example, when LD (0FFE0H), 60H/8 is executed, the interrupt request flipflop for the interrupt channel [INTT1] with the vector value 38H is reset to "0" (to clear the flipflop, also write to address FFC9H when the interrupt request flag is assigned to FFE1H and FFE2H).

Table 3.3 (5) shows the "interrupt vector value/8" values. The status of the interrupt request flipflop can be determined by reading memory address FFC9H, FFCAH or FFCBH. "0" means no interrupt request and "1" means an interrupt request. Figure 3.3 (8) shows the bit layout when the interrupt request flipflop is read.

Table 3.3 (4) Interrupt Vector Value/8 Values

|                 | Priori<br>seque |      | Туре     |            | Interrup<br>function na |             | Interrupt vect<br>value     | or Vec                               | tor value ÷ 8                                       |  |  |  |

|-----------------|-----------------|------|----------|------------|-------------------------|-------------|-----------------------------|--------------------------------------|-----------------------------------------------------|--|--|--|

|                 | 1               |      |          |            | SWI Instruc             | tion        | 10H                         |                                      |                                                     |  |  |  |

|                 | 2               |      | Non Mask | able       | NMI                     |             | 18H                         |                                      |                                                     |  |  |  |

|                 | 3               |      |          |            | INTWD                   |             | 20H                         |                                      |                                                     |  |  |  |

|                 | 4               |      |          |            | INT0                    |             | 28H                         |                                      | 05H                                                 |  |  |  |

|                 | 5               |      |          |            | INTCAP                  | •           | 30H                         |                                      | 06H                                                 |  |  |  |

|                 | 6               |      |          |            | INTTPG                  | )           | 38H                         |                                      | 07H                                                 |  |  |  |

|                 | 7               |      |          |            | INTTPG                  | 1           | 40H                         |                                      | 08H                                                 |  |  |  |

|                 | 8               |      |          |            | INTRX0                  | ŀ           | 48H                         |                                      | 09H                                                 |  |  |  |

|                 | 9               |      |          |            | INTTX0                  | 1           | 50H                         |                                      | 0AH                                                 |  |  |  |

|                 | 10              |      |          |            | INTT0                   |             | 58H                         |                                      | овн                                                 |  |  |  |

|                 | 11              |      |          |            | INTT1                   |             | 60H                         |                                      | 0СН                                                 |  |  |  |

|                 | 12              |      |          |            | INTT2                   |             | 68H                         |                                      | 0DH                                                 |  |  |  |

|                 | 13              |      |          |            | INTAD                   |             | 70H                         |                                      | 0EH                                                 |  |  |  |

|                 | 14              |      | Maskat   | ole        | INTT3                   |             | 78H                         |                                      | 0FH                                                 |  |  |  |

|                 | 15              |      |          |            | INTT4                   |             | 80H                         |                                      | 10H                                                 |  |  |  |

|                 | 16              |      |          |            | INT1                    |             | 88H                         |                                      | 11H                                                 |  |  |  |

|                 | 17              |      |          |            | INTT5                   |             | 90H                         |                                      | 12H                                                 |  |  |  |

|                 | 18              |      |          |            | INT2                    |             | 98H                         |                                      | 13H                                                 |  |  |  |

|                 | 19              |      |          |            | INTRX1                  |             | A0H                         |                                      | 14H                                                 |  |  |  |

|                 | 20              |      |          |            | INTTX1                  |             | A8H                         |                                      | 15H                                                 |  |  |  |

|                 | 21              |      |          |            | INT3                    |             | вон                         |                                      | 16H                                                 |  |  |  |

|                 | 22              |      |          |            | INTRX2                  |             | B8H                         |                                      | 17H                                                 |  |  |  |

|                 | 23              |      |          |            | INTTX2                  |             | СОН                         |                                      | 18H                                                 |  |  |  |

|                 |                 | 7    | 6        | 5          | 4                       |             | 3 2                         | 1                                    | 0                                                   |  |  |  |

|                 | bit Symbol      | IRF3 | IRF2     | IRF        | 1 IRFAD                 | IRFT        | PG1 IRFTPG0                 | IRFCAP                               | IRF0                                                |  |  |  |

| IRFO<br>(FFEOH) | Read/Write      |      |          | R (O       | nly IRF Clear Co        | ode ca      | n be written)               |                                      |                                                     |  |  |  |

| (11 LO11)       | After reset     | 0    | 0        | 0          | 0                       | <del></del> | 0 0                         | 0                                    | 0                                                   |  |  |  |

|                 |                 |      |          |            | Interrupt R             |             | -                           |                                      |                                                     |  |  |  |

|                 | Function        |      | (        | IRF is cla | 1: Interrup             |             | esteu<br>ng IRF clear code) |                                      |                                                     |  |  |  |

|                 |                 |      |          | 11.13 CI   |                         |             |                             |                                      |                                                     |  |  |  |

|                 |                 |      |          |            |                         |             |                             | → INTO → INTC → INTT! → INTT! → INTT | PG0 request fla<br>PG1 request fla<br>D request fla |  |  |  |

|                 |                 |      |          |            |                         |             |                             | → INT1                               | request fla                                         |  |  |  |

|                 |                 |      |          |            |                         |             |                             | → INT2<br>→ INT3                     | request fla<br>request fla                          |  |  |  |

|                 |                 |      |          |            |                         |             |                             | - 11413                              | requestria                                          |  |  |  |

Note: The specified interrupt request flipflop is cleared by writing  $\lceil$  vector value/8  $\rfloor$  to memory address FFE0H.

Figure 3.3 (5). Interrupt Request Flipflop Read (1/2)

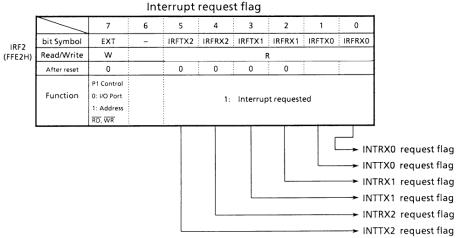

Figure 3.3 (6). Interrupt Request Flipflop Read (2/2)

Figure 3.3 (7). Interrupt Controller Block

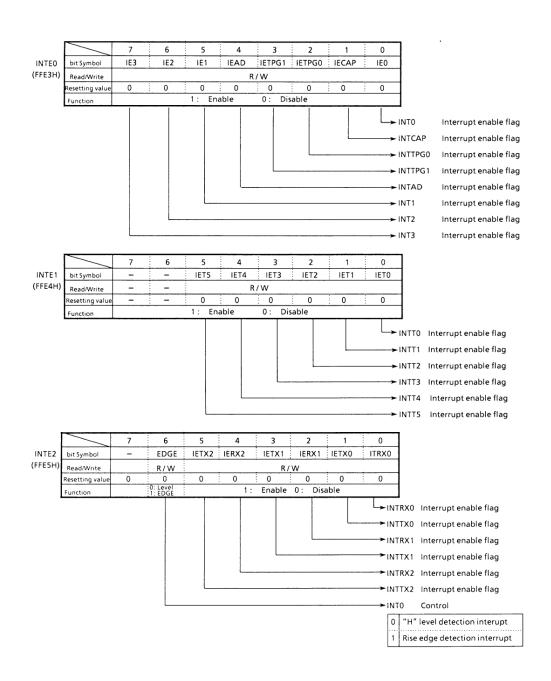

The interrupt enable/disable flags for each interrupt request channel are assigned to memory addresses FFE3H - FFE5H.

Interrupts are enabled for a channel by setting the flag to "1". The flags are reset to "0" by reseting.

| Interrupt | Common Terminal | Mode      | How to set                                          |

|-----------|-----------------|-----------|-----------------------------------------------------|

| INTO      | P81             | Level     | INTE2 <edge> = 0</edge>                             |

|           |                 | Rise edge | INTE2 <edge> = 1</edge>                             |

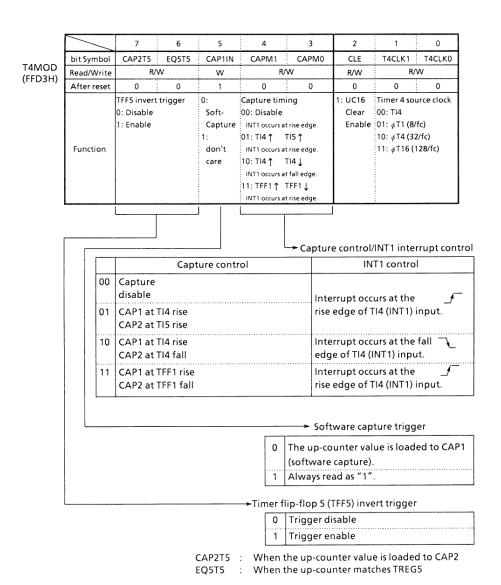

| INT1      | P53             | Rise edge | T4MOD <capm1, 0=""> = 0, 0 or 0, 1 or 1, 1</capm1,> |

|           |                 | Fall edge | T4M0D <capm1, 0=""> = 1, 0</capm1,>                 |

| INT2      | P54             | Rise edge | -                                                   |

| INT2      | P56             | Rise edge | -                                                   |

For the pulse width for external interrupt, refer to "4.7 Interrupt Operation".

Be careful that the following five are exceptional circuits.

| INTO Level mode | As the INTO is not an edge type interrupt, the interrupt request flipflop is cancelled, and thus an interrupt request from peripheral devices passes through S input of the flipflop to become Q output. When the mode is changed over (from edge type to level type), the previous interrupt request flag will be cleared automatically. |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | When the mode is changed from level to edge, the interrupt request flag set in the level mode is not cleared. Thus, use the following sequence to clear the interrupt request flag.                                                                                                                                                       |

|                 | DI SET 6, (0FFE5H): Switch the mode from level to edge LD (0FFE0H), FEH: Clear interrupt request flag EI                                                                                                                                                                                                                                  |

| INTRX1, INTRX2  | The interrupt request flipflop cannot be cleared only by reset operation or reading the serial channel receiving buffer, and cannot be cleared by an instruction.                                                                                                                                                                         |

Figure 3.3 (8). Interrupt Enable Flags

Figure 3.3 (9). Interrupt Processing Flow Chart

## 3.4 Standby Functions

When a HALT instruction is executed, TMP90CM36 enters the RUN, IDLE1 or STOP mode according to the contents of the halt mode setting register. The features are shown below.

- (1) Run: Only the CPU halts, power consumption remains unchanged.

- (2) IDLE: Only the internal oscillators operate, while all other internal circuits halt. Power consumption is 1/10 or less than that during normal operation.

- (3) STOP: All internal circuits halt, including the internal oscillator. Power consumption is extremely reduced.

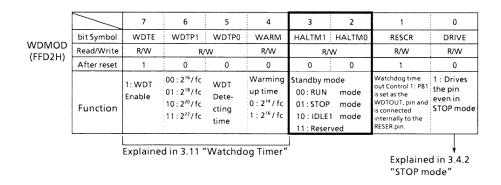

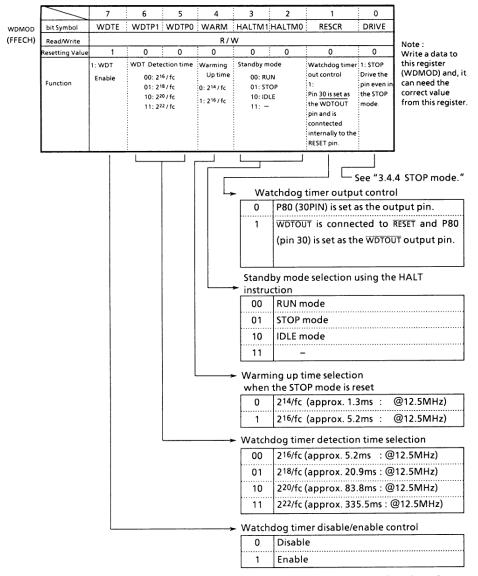

The HALT mode setting register WDMOD <HALTM1, 0> is assigned to bits 2 and 3 memory address FFECH in the built-in I/O register area (all other bits are used to control other block functions). The RUN mode ("00") is entered by reseting.

These HALT states can be released by requesting an interrupt or resetting. Table 3.4 (2) shows how to release the HALT state. If the CPU is in the EI state for non-maskable or maskable interrupt, the interrupt will be acknowledged by the CPU and the CPU starts interrupt processing. If the CPU is in the DI state fro maskable interrupt, the CPU starts the execution from the instruction following HALT instruction, but the interrupt request flag remains at "1".

Even when HALT state is released by reset operation, the state (including the built-in RAM) just before entering the HALT can be retained. However, if HALT instruction has already been executed in the built-in RAM, the RAM contents may not be retained.

Figure 3.4 (1). HALT Mode Setting Register

## **3.4.1 RUN Mode**

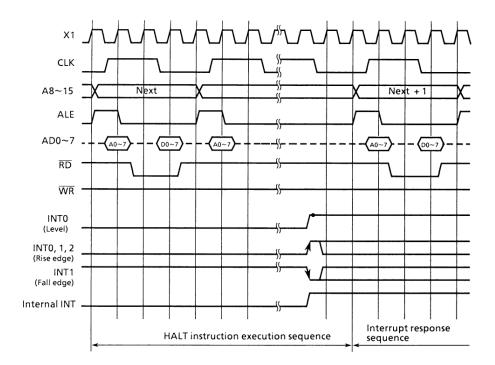

Figure 3.4 (2) shows the timing for releasing the HALT state by an interrupt during RUN mode. In the RUN mode, the system clock inside MCU does not stop even after HALT instruction

has been executed; the CPU merely stops executing instructions. Accordingly, the CPU repeats dummy cycle until HALT state, interrupt requests are sampled at the fall edge of CLK signal.

Figure 3.4 (2). HALT Release Timing Using Interrupts in RUN Mode

## 3.4.2 IDLE1 Mode

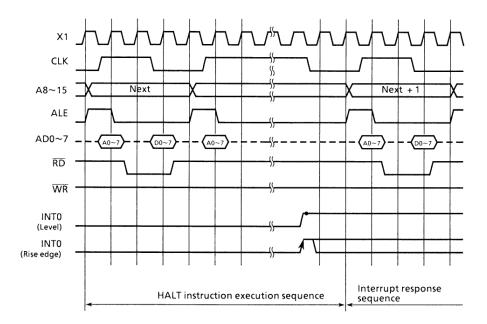

Figure 3.4 (3) shows the timing used for releasing the HALT mode by interrupts in the IDLE1 mode.

In the IDLE1 mode, only the internal oscillator operates, the system clock inside MCU stops and CLK signal is fixed to "1".

In the HALT state, interrupt requests are sampled asynchronously with the system clock but sampling is performed synchronously with the system clock, whereas the HALT release (restart of operation) is performed synchronously with it

Figure 3.4 (3). HALT Release Timing Using Interrupts in the IDLE1 Mode

### 3.4.3 STOP Mode

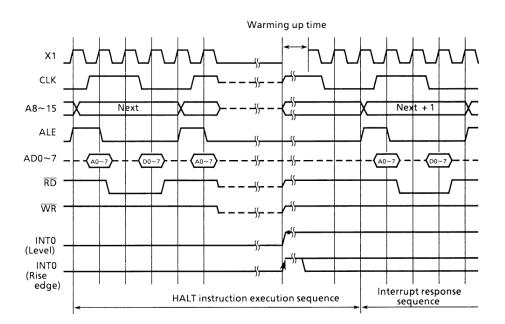

Figure 3.4 (4) shows the timing of HALT release caused by interrupts in STOP mode.

In the STOP mode, all interval circuits stop, including internal oscillator. When the STOP mode is activated, all pins except special ones are put in the high-impedance state, isolated from the internal operation of MCU. Table 3.4 (1) shows the state of each pin in the STOP mode. However, if WDMOD <DRVE> (drive enable: bit 0 of memory address FFECH) of th built-in I/O register is set to "1", the pre-halt state of the pins can be retained. The register is cleared to "0" by reset operation.

When the CPU accepts an interrupt request, the internal oscillator first restarts. However, to get the stabilized oscillation, the system clock starts its output after the time set by warming up counter has passed. WDMOD <WARM> (warming up: bit 4 at memory address FFECH) is used to set up the warming up time. Warming up is executed for  $2^{14}$  clock oscillation time when this bit is set to "0", while  $2^{16}$  clock oscillation time when set to "1". This bit is cleared to "0" by reset operation.

Figure 3.4 (4). HALT Release Timing Using Interrupts in STOP Mode

The internal oscillator can also be restarted by inputting the RESET signal "0" to the CPU.

However, the warming up counter remains inactive in order to make the CPU rapidly operate when the power is turned on. Accordingly, wrong operation may occur due to

unstable clocks immediately after the internal oscillator has restarted. To release the HALT state by resetting in the STOP mode, RESET signal must be kept at "0" for a sufficient period of time.

Table 3.4 (1) State of Pins in STOP Mode

|                                              | 1                                                                                                                 |                             |                                    |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------|

|                                              | I/O                                                                                                               | DRVE = 0                    | DRVE = 1                           |

| P00 ~ P07                                    | Input Mode<br>Output Mode                                                                                         |                             | Input<br>Output                    |

| P10 ~ P17                                    | Input Mode<br>Output Mode                                                                                         | -                           | Input<br>Output                    |

| P20 ~ P27                                    | Input Mode<br>Output Mode                                                                                         | -                           | Input<br>Output                    |

| P30 ~ P31                                    | Input Mode<br>Output Mode                                                                                         | -                           | Input<br>Output                    |

| P32 ~ P33                                    | Input Mode<br>Output Mode                                                                                         | -                           | Input<br>Output                    |

| P40 ~ P47                                    | Input Mode<br>Output Mode                                                                                         | -                           | Input<br>Output                    |

| P56 ~ P57                                    | Input Mode<br>Output Mode                                                                                         | -                           | Input<br>Output                    |

| P60 ~ P67                                    | Input Mode                                                                                                        | -                           | -                                  |

| P70 ~ P77                                    | Input Mode<br>Output Mode                                                                                         | –<br>Output                 | Input<br>Output                    |

| NMI DAOUTO DAOUT1 NMI CLK X1 X2 EA           | Input Mode Output Mode Output Mode Input Mode Output Mode Input Mode Input Mode Input Mode Output Mode Input Mode | Input 0V 0V Input "1" Input | Input OV OV Input "1" Input        |

| P80 (WDTOUT) P81 (INT0) P82 (STBY) P83 (ALE) | Output Mode<br>Input Mode<br>Input Mode<br>Output Mode                                                            | Input Input —               | Output<br>Input<br>Input<br>Output |

Indicates that input mode/input pin cannot be used for input and that the output mode/ output pin have been set to high impedance.

Input: Input is enabled.

Input: The input gate is operating. Fix the input voltage at either "0" or "1" to prevent the pin floating. Output: Output status.

Table 3.4 (2) I/O Operation Release in HALT Mode

| HALT mode                   |                       | RUN                   | IDLE1                                                | STOP         |                   |  |

|-----------------------------|-----------------------|-----------------------|------------------------------------------------------|--------------|-------------------|--|

| WDMOD <haltm1,0></haltm1,0> |                       | 00                    | 10                                                   | 01           |                   |  |

|                             | CPL                   | J                     |                                                      | Halt         |                   |  |

| 0                           | 1/0                   | port                  | Retains the state when HALT instruction is executed. |              | See Table 3.4 (1) |  |

| p                           | 8-bi                  | it timer              |                                                      |              |                   |  |

|                             | 16-1                  | oit timer             |                                                      |              |                   |  |

| a                           | Tim                   | e Base Counter        |                                                      |              |                   |  |

| l t                         | Capture circuit       |                       |                                                      |              |                   |  |

| n                           | Tim                   | ming pulse generation |                                                      | Halt         |                   |  |

| g                           | Wat                   | tchdog timer          | Operation                                            |              |                   |  |

| b                           | PW                    | M Output              |                                                      |              |                   |  |

| 0                           | Seri                  | al interface          |                                                      |              |                   |  |

| c                           | A/D                   | converter             |                                                      |              |                   |  |

| k                           | D/A                   | converter             |                                                      |              |                   |  |

|                             | Inte                  | errupt controller     |                                                      |              |                   |  |

|                             |                       | NMI                   | 0                                                    | 0            | 0                 |  |

|                             |                       | INTWD                 | 0                                                    | _            |                   |  |

|                             |                       | INT0                  | 0                                                    | 0            | 0                 |  |

|                             | i<br>n<br>t<br>e<br>r | INTCAP                | 0                                                    | <del>_</del> | _                 |  |

| ١.,.                        |                       | INTTPG0               | 0                                                    |              |                   |  |

| H                           |                       | INTTPG1               | 0                                                    | _            |                   |  |

| L                           |                       | INTRX0                | O                                                    | _            |                   |  |

| '                           |                       | INTTX0                | 0                                                    |              |                   |  |

| r                           |                       | INTT0                 | 0                                                    | _            |                   |  |

| e                           |                       | INTT1                 | 0                                                    |              | <del>-</del>      |  |

| e                           |                       | INTT2                 | 0                                                    | <del>-</del> |                   |  |

| a<br>s                      |                       | INTAD                 | 0                                                    | _            | <del>-</del>      |  |

| i<br>n                      |                       | INTT3                 | 0                                                    |              |                   |  |

| g                           |                       | INTT4                 | 0                                                    |              | _                 |  |

| s                           |                       | INT1                  | 0                                                    |              | _                 |  |

| 0                           |                       | INTT5                 | 0                                                    |              |                   |  |

| u<br>r                      | р                     | INT2                  | 0                                                    | _            |                   |  |

| c                           | t                     | INTRX1                | 0                                                    |              | _                 |  |

| е                           |                       | INTTX1                | 0                                                    | _            |                   |  |

|                             |                       | INT3                  | 0                                                    |              | _                 |  |

|                             |                       | INTRX2                | 0                                                    |              |                   |  |

|                             |                       | INTTX2                | - 0                                                  |              |                   |  |

|                             |                       | INTTX2                | 0                                                    |              |                   |  |

|                             | INTTBC                |                       | 0                                                    |              |                   |  |

| L                           | Reset                 |                       | 0                                                    | 0            | 0                 |  |

Can be used for HALT release

Cannot be used for HALT release

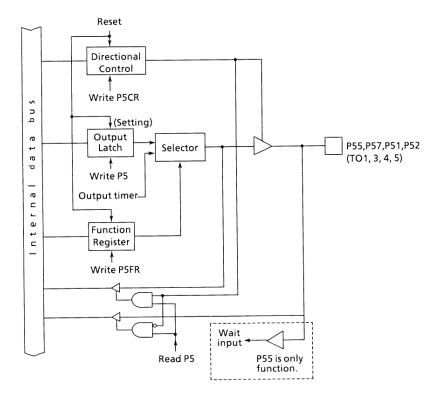

# 3.5 Function of Ports

The TMP90CM36 contains total of 64 I/O port pins. These port pins function not only as the general-purpose I/O ports

but also as the I/O ports for the internal CPU and built-in I/O. Table 3.5 shows the functions of these port pins.

**Table 3.5 Functions of Ports**

| name   | Pin name | NO. of pins | Direction | Direction<br>Setting unit | Direction setting unit | Pin mane for internal function |

|--------|----------|-------------|-----------|---------------------------|------------------------|--------------------------------|

| Port 0 | P00~P07  | 8           | I/O       | Bit                       | Input                  | AD0~AD7                        |

| Port 1 | P10~P17  | 8           | I/O       | Bit                       | Input                  | A8~A15                         |

| Port 2 | P20~P23  | 4           | I/O       | Bit                       | Input                  | TPG00~07<br>(TPG14~17)         |

| Port 3 | P30      | 1           | Output    |                           | Output                 | RD                             |

|        | P31      | 1           | Output    |                           | Output                 | WR                             |

|        | P32, P33 | 2           | 1/0       |                           | Input                  | PWM0, PWM1                     |

| Port 4 | P40~P43  | 4           | I/O       | Bit                       | Input                  | TPG10~13                       |

|        | P44~P47  | 4           | I/O       | Bit                       | Input                  | CAP0~CAP3                      |

| Port 5 | P50      | 1           | I/O       |                           | Input                  | EXIN                           |

|        | P51      | 1           | I/O       |                           | Input                  | TO4                            |

|        | P52      | 1           | I/O       |                           | Input                  | TO5                            |

|        | P53      | 1           | I/O       |                           | Input                  | INT1/TI4                       |

|        | P54      | 1           | I/O       |                           | Input                  | INT2/TI5                       |

|        | P55      | 1           | I/O       |                           | Input                  | TO1                            |

|        | P56      | 1           | I/O       |                           | Input                  | INT3/TI2                       |

|        | P57      | 1           | I/O       |                           | Input                  | ТОЗ                            |

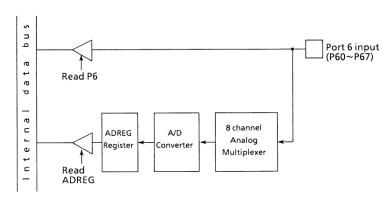

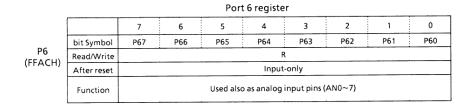

| Port 6 | P60~P67  | 8           | Input     | Bit                       | Input                  | AN0~AN7                        |

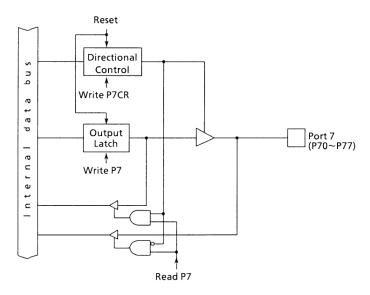

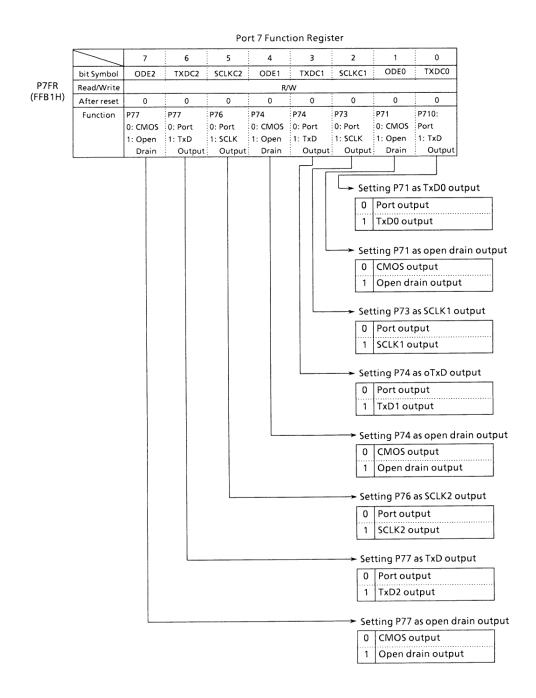

| Port 7 | P70      | 1           | I/O       |                           | Input                  | RXD0                           |

|        | P71      | 1           | 1/0       |                           | Input                  | TXD0                           |

|        | P72      | 1           | 1/0       |                           | Input                  | RXD1                           |

|        | P73      | 1           | 1/0       |                           | Input                  | SCLK1/CTS1                     |

|        | P74      | 1           | I/O       |                           | Input                  | TXD1                           |

|        | P75      | 1           | 1/0       |                           | Input                  | RXD2                           |

|        | P76      | 1           | 1/0       |                           | Input                  | SCLK2                          |

|        | P77      | 1           | 1/0       |                           | Input                  | TXD2                           |

| Port 8 | P80      | 1           | Output    |                           | Output                 | WDTOUT                         |

|        | P81      | 1           | Input     |                           | Input                  | INT0                           |

|        | P82      | 1           | Input     |                           | Input                  | STBY                           |

|        | P83      | 1           | Output    |                           | Output                 | ALE                            |

These port pins function as the general-purpose I/O port pins by resetting. The port pins, for which input or output is programmably selectable, function as input ports by resetting. A

separate program is required to use them for an internal function.

36

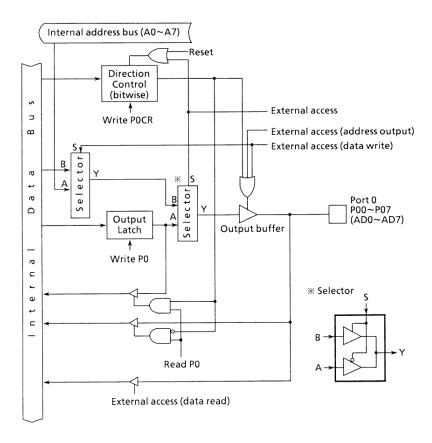

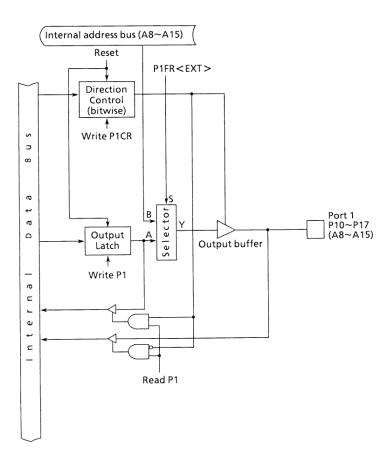

# 3.5.1 Port 0 (P00 ~ P07)

Port 0 is the 8-bit general-purpose I/O port P0, each bit of which can be set independently for input or output. The control register P0CR is used to set input or output. Reset operations clear all output latch and control register bits to "0" and

set port 0 to the input mode.

In addition to the general-purpose I/O port function, port 0 also functions as an address/data bus (AD0  $\sim$  AD7). When the external memory is accessed, port 0 automatically functions as the address/data bus.

Figure 3.5 (1). Port 0 (P00 ~ P07)

Figure 3.5 (2). Registers for Port 0

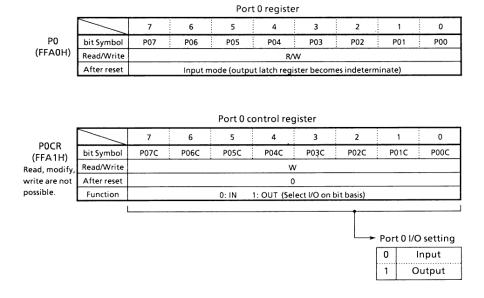

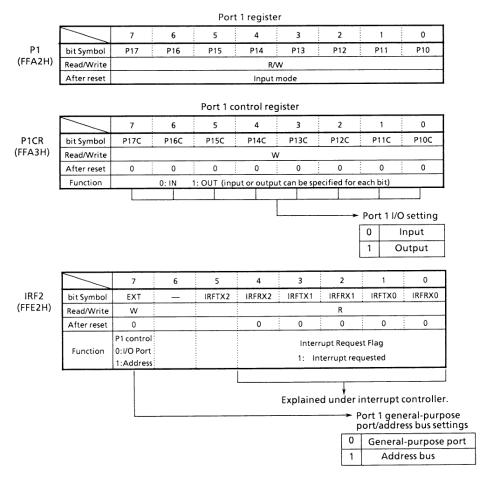

## 3.5.2 Port 1 (P10 ~ P17)

Port 1 is the 8-bit general-purpose I/O port P1, each bit of which can be set to input or output. The port 1 control register P1CR is used to set input or output. Reset operations clear all output latch and the control register bits to "0" and sets all port 1 bits to the input mode.

In addition to the general-purpose I/O port function, port 1

also functions as an address bus (A8 ~ A15). This is specified by setting the external extended specification register IRFL<EXT> to "1" and setting P1CR to the output mode. When the P1CR cleared to "0", port 1 is set to the input mode, regardless of the external extended specification register value.

Figure 3.5 (3). Port 1 (P10 ~ P17)

P1CR and IRFL <EXT > settings

| P1CR EXT> | 0           | 1           |

|-----------|-------------|-------------|

| 0         | Input port  | Input port  |

| 1         | Output port | Address bus |

Note: Each bit can be set independently. P1CR < P1XC > is the X bit of P1CR.

Figure 3.5 (4). Registers for Port 1

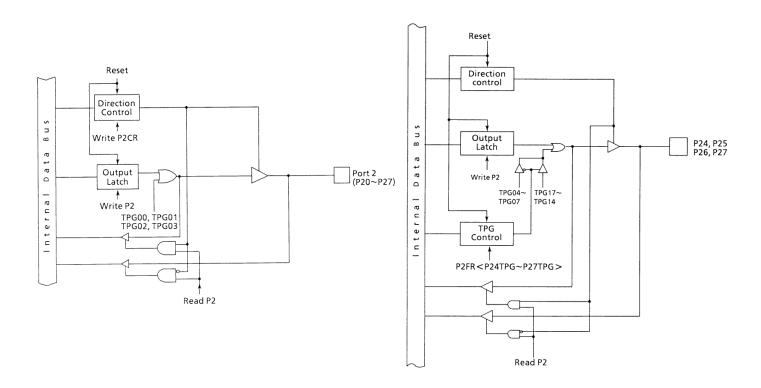

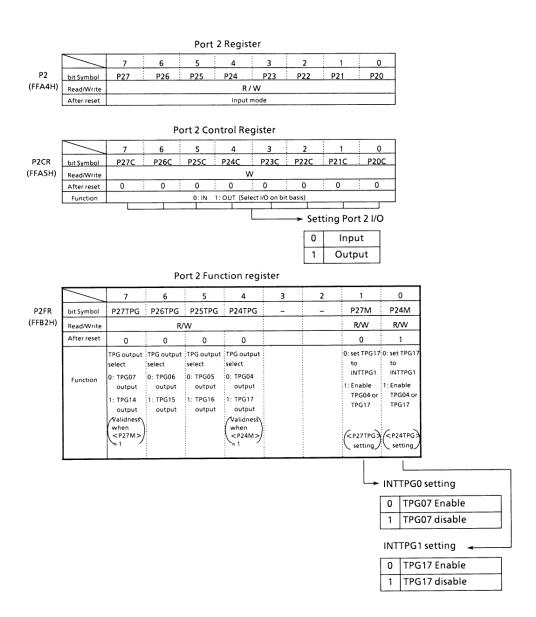

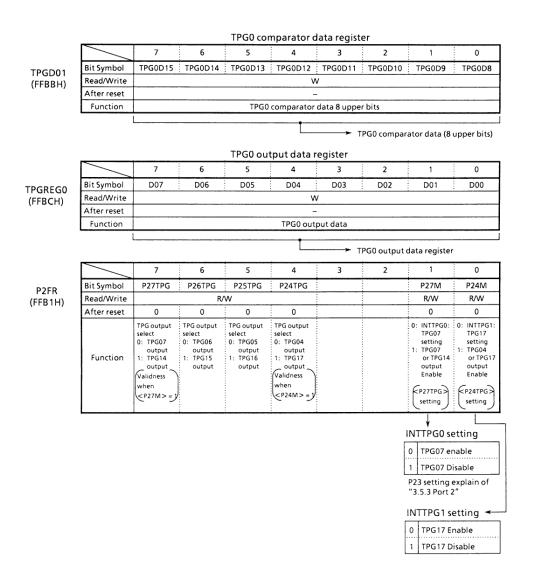

## 3.5.3 Port 2 (P20 ~ P27)

Port 2 is the 8-bit general-purpose I/O port P2, each bit of which can be set to input or output. The port 2 control register P2CR is used to set input or output. Reset operations clear all output latch and the control register bits to "0" and set port 2 to the input mode.

In addition to the general-purpose I/O port function, port 2 also has a timing pulse generator (TPG) output (TPG00  $\sim$  07, TPG14  $\sim$  TPG17). To use TPG as the output port function,

port should be set to output mode, and and port output latch set to "0". (After reset "0") P24 ~ P27 is also used as TPG04 and TPG17 (P24), TPG05 and TPG16 (P25), TPG06 and TPG15 (P26), TPG07 and TPG14 (P27), it selects by the port 2 function register P2FR <P24TPG ~ P27TPG>. P27 is TPG07 output by setting P2 FR <P27M> "1". TPG07 is <P27M> = "1" by resetting, and the port turns to output mode.

Figure 3.5 (5). Port 2 (P20 ~ P27)

Figure 3.5 (6) Port 2 (P24, P25, P26, P27)

Figure 3.5 (7). Registers for Port 2

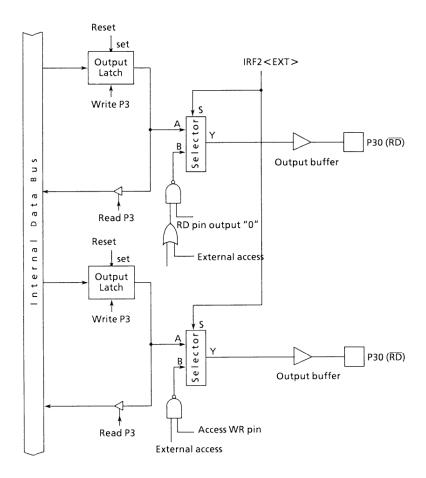

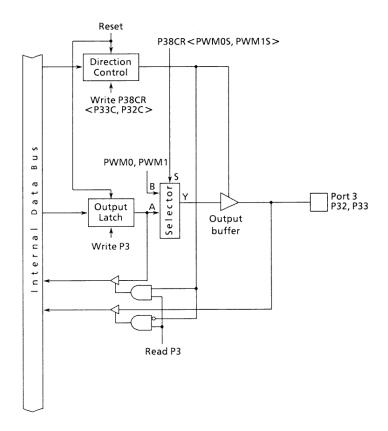

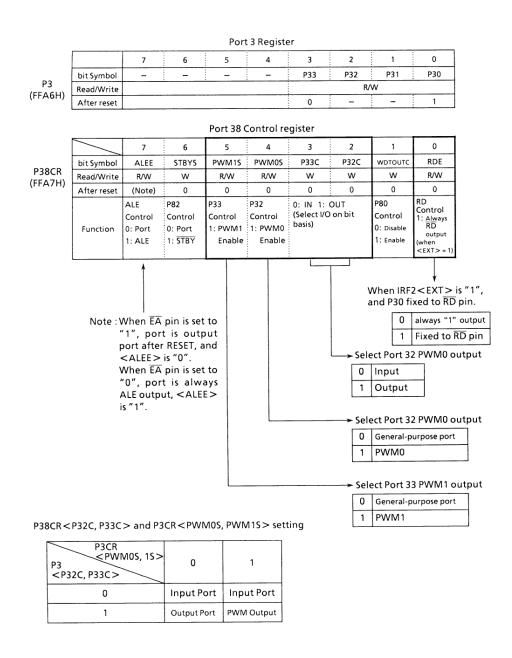

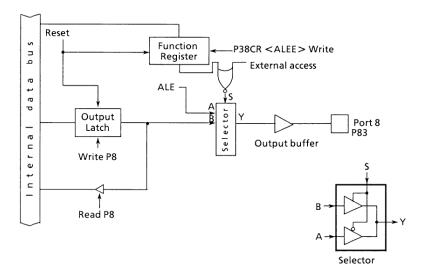

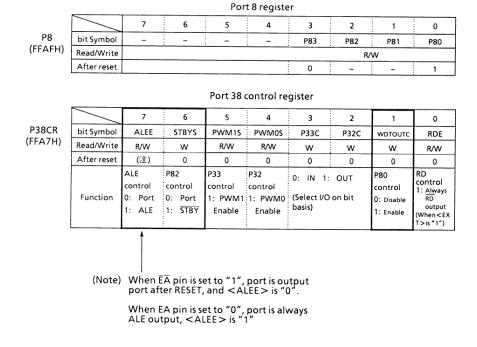

## 3.5.4 Port 3 (P30 ~ P33)

P32, P33 are a 4-bit general-purpose I/O port. The control register P38CR <P33C, P32C> is used for input or output.

P30, P31 are output ports. All bits of the output latch are set to "1" by resetting, and "1" is generated to the output port. Access of external memory makes P30, P31 function as the memory control pins ( $\overline{RD}$  and  $\overline{WR}$ ), when set IRF2 <EXT> to

"1". When access of an internal memory makes them function, "1" is generated always.

Also function register P38CR <RDE> is intended for a pseudostatic RAM. When set IRF2 <EXT> to "1", and set P38CR <RDE> to "1", it always functions as  $\overline{\text{RD}}$  pin. Therefore, the  $\overline{\text{RD}}$  pin outputs "0" (Enable) when it is an internal memory read and internal I/O read cycle.

Figure 3.5 (8). Port 3 (P30, 31)

Figure 3.5 (9). Port 3

Figure 3.5 (10). Register for Port 3

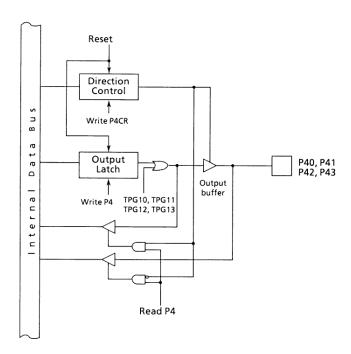

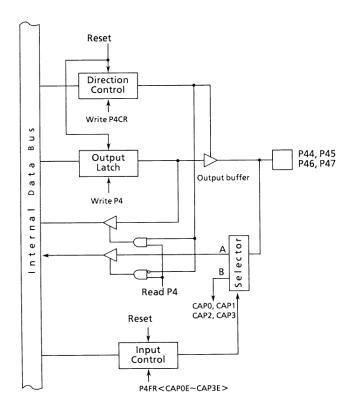

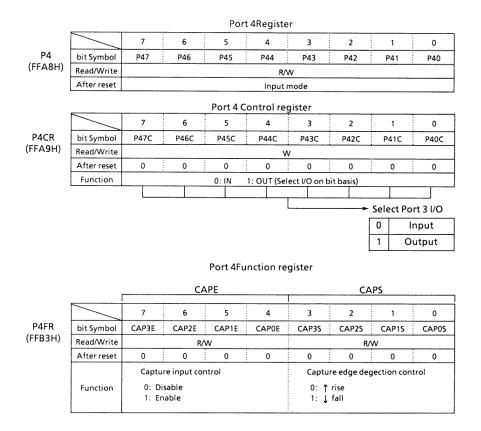

# 3.5.5 Port 4 (P40 - P47)

Port 4 is the 8-bit general-purpose I/O port, each bit of which can be set for input or output. The control register P4CR is used to set input or output.

All bits of the function register are cleared to "0" by reset-

ting, and the port turns of general-purpose I/O port mode. In addition to the general-purpose I/O port function, P40 ~ 43 have an input/output function for the Timing Pulse Generators output (TPG10 ~ TPG13) function, and P44 ~ P47 have the capture input (CAP0 ~ CAP3) function.

Figure 3.5 (11). Port 4 (P40, P41, P42, P43)

Figure 3.5 (12). Port 4 (P44, P45, P46, P47)

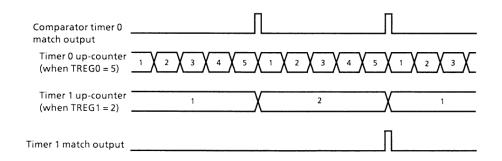

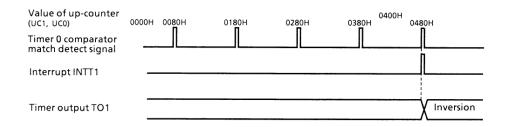

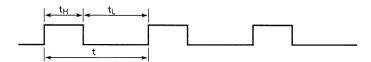

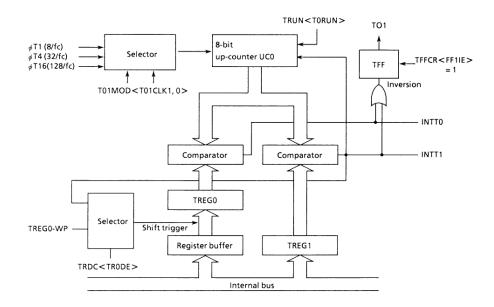

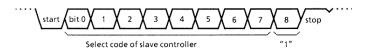

Figure 3.5 (13). Register for Port 4