# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

## General Description

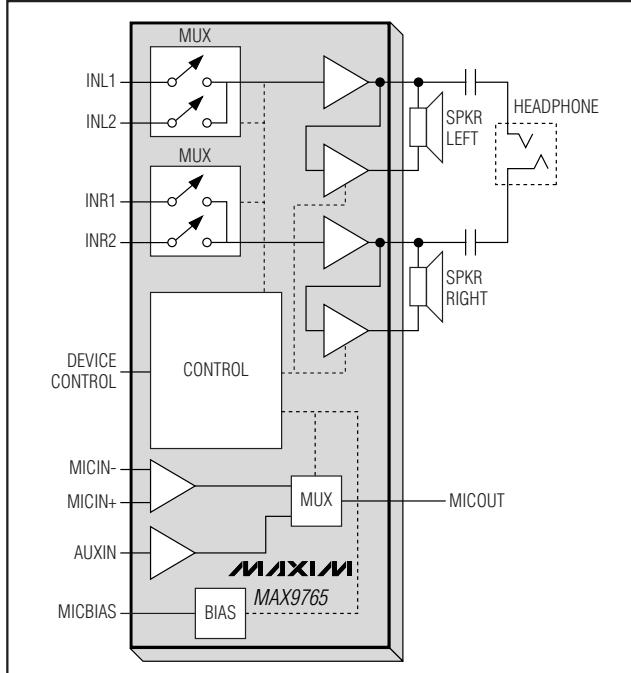

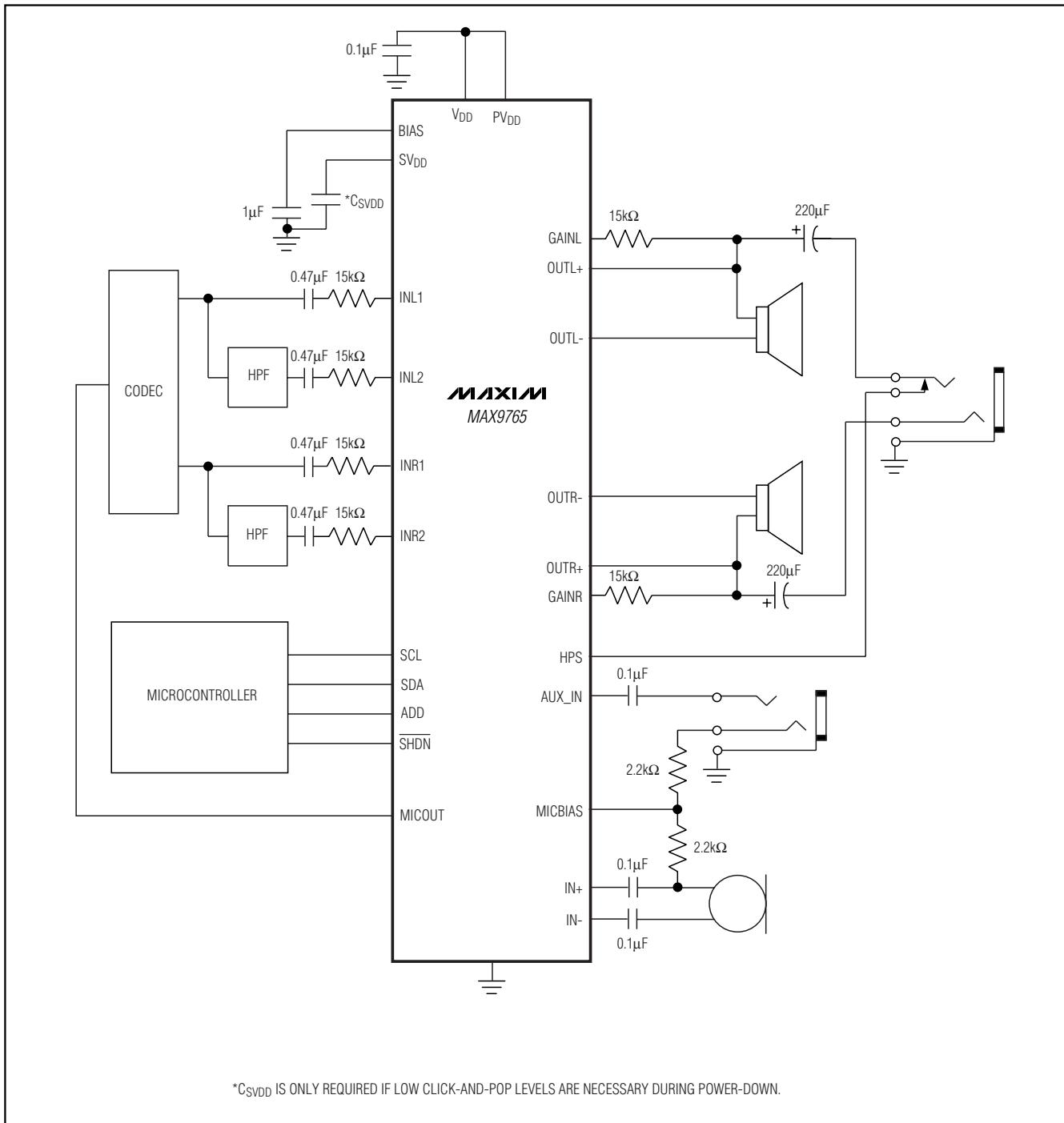

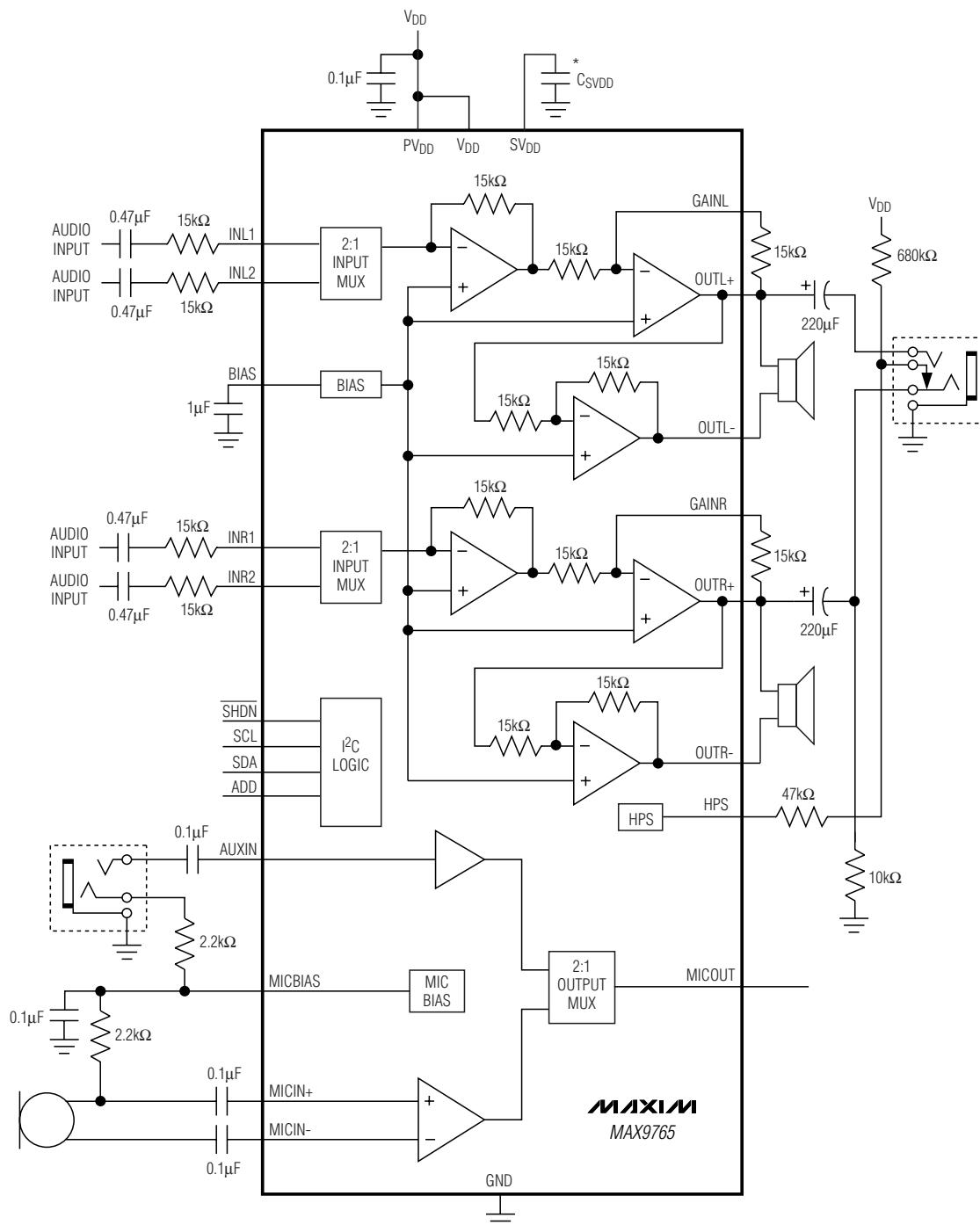

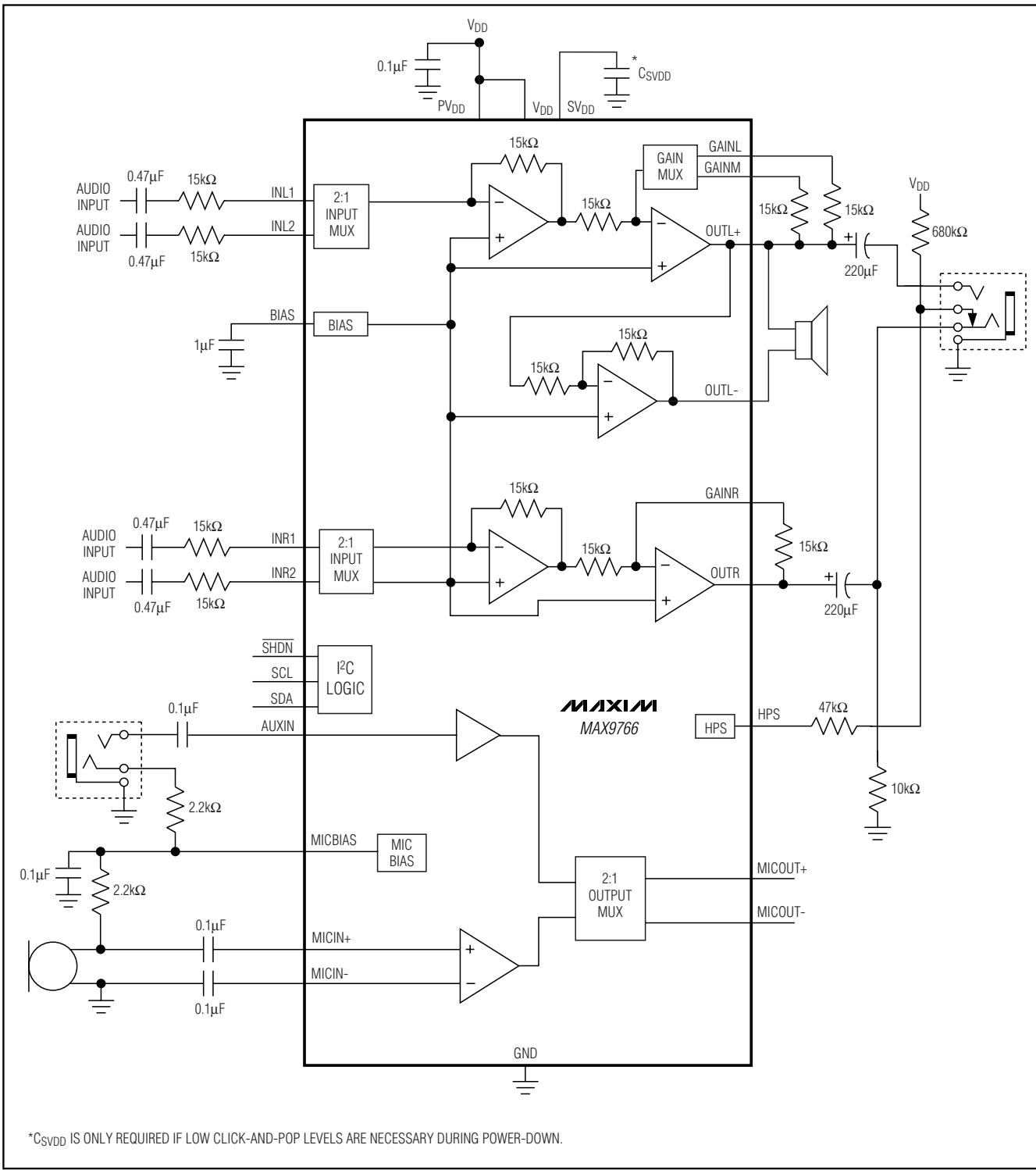

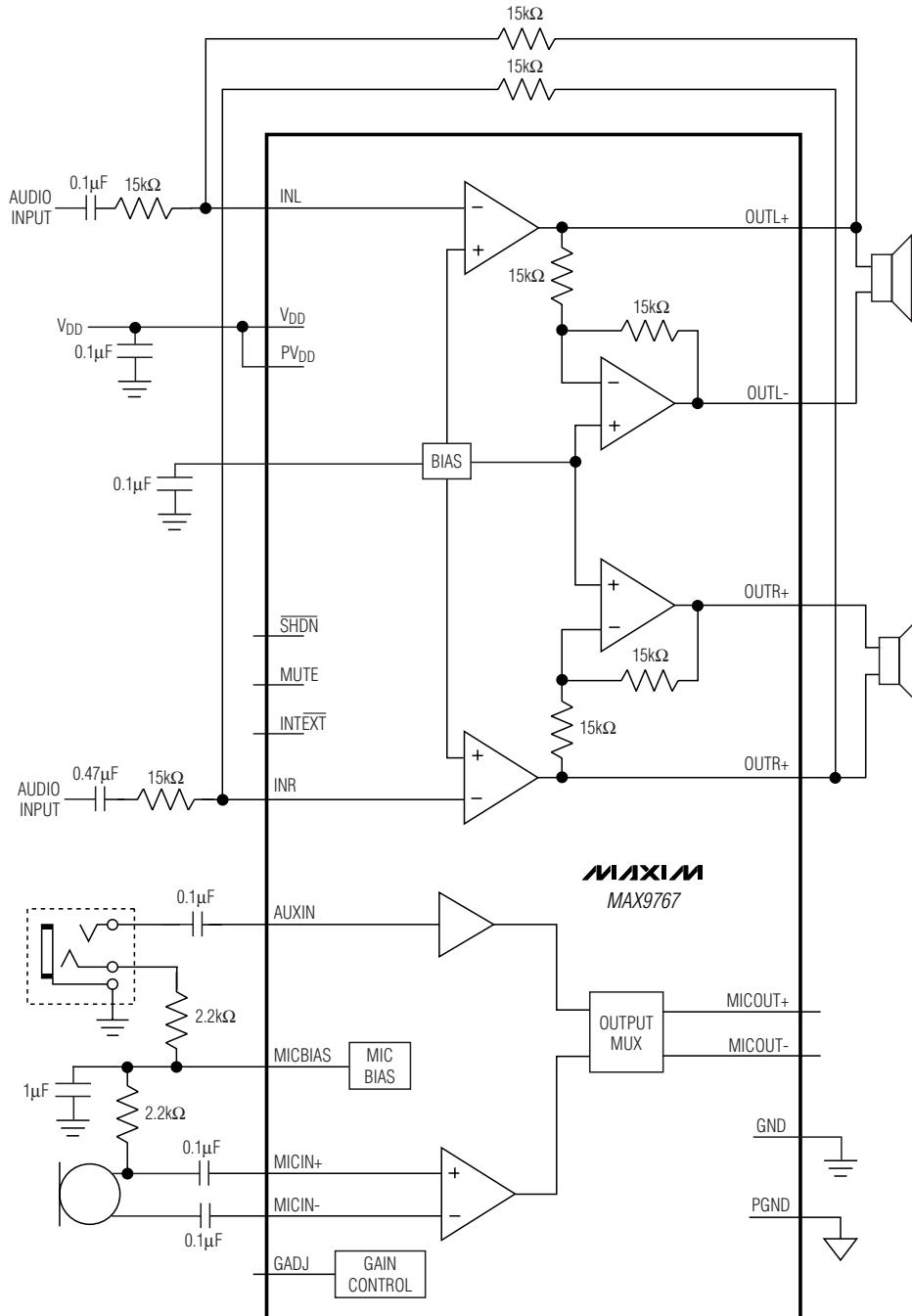

The MAX9765/MAX9766/MAX9767 family combines speaker, headphone, and microphone amplifiers, all in a small thin QFN package. The MAX9765 is targeted at stereo speaker playback applications and includes a stereo bridge-tied load (BTL) speaker amp, stereo headphone amp, single-ended output mic amp, input MUX, and I<sup>2</sup>C control. The MAX9766 is targeted at mono speaker playback applications and includes a mono BTL speaker amp, stereo headphone amp, differential output mic amp, input MUX, and I<sup>2</sup>C control. The MAX9767 is targeted at applications that do not require a headphone amp and includes a stereo BTL speaker amp, differential output mic amp, and parallel control.

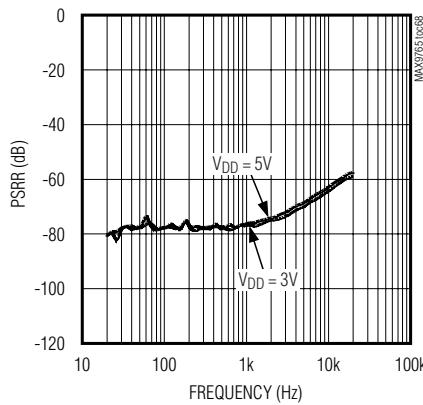

These devices operate from a single 2.7V to 5.5V supply. A high 95dB PSRR allows these devices to operate from noisy supplies without additional power conditioning. An ultra-low 0.003% THD+N ensures clean, low distortion amplification of the audio signal. Patented click-and-pop suppression eliminates audible transients on power and shutdown cycles.

In speaker mode, the amplifiers can deliver up to 750mW of continuous average power into a 4Ω load. In headphone mode, the amplifier can deliver up to 65mW of continuous average power into a 16Ω load. The gain of the amplifiers is externally set, allowing maximum flexibility in optimizing output levels for a given load. The MAX9765/MAX9766 also feature a 2:1 input multiplexer, allowing multiple audio sources to be selected. The various functions are controlled by either an I<sup>2</sup>C-compatible (MAX9765/MAX9766) or simple parallel control interface (MAX9767).

All devices include two low-noise microphone preamps, a differential amp for internal microphones, and a single-ended amplifier for additional external microphones. A microphone bias output is provided, reducing external component count.

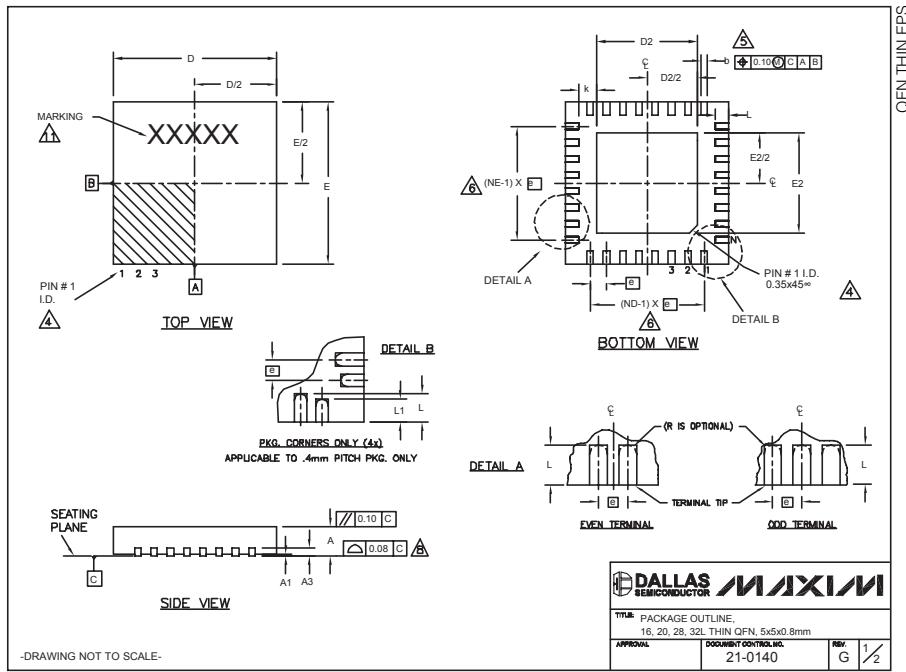

The MAX9765/MAX9766/MAX9767 are available in a thermally efficient 32-pin thin QFN package (5mm × 5mm × 0.8mm). All devices have short-circuit and thermal-overload protection (OVP) and are specified over the extended -40°C to +85°C temperature range.

## Applications

PDA Audio Systems

Notebooks

Tablet PCs

Digital Cameras

Cell Phones

Purchase of I<sup>2</sup>C components from Maxim Integrated Products, Inc., or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification defined by Philips.

## Features

- ◆ 750mW BTL Stereo Speaker Amplifier

- ◆ 65mW Stereo Headphone Amplifier

- ◆ 2.7V to 5.5V Single-Supply Operation

- ◆ Patented Click-and-Pop Suppression

- ◆ Low 0.003% THD+N

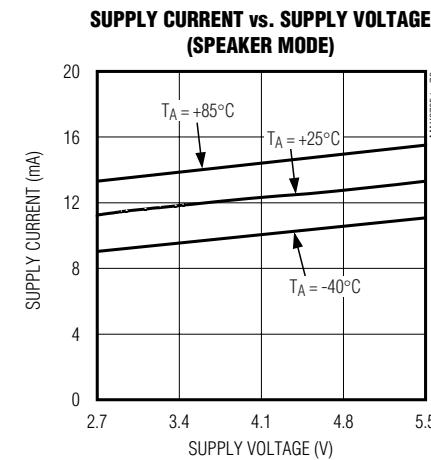

- ◆ Low Quiescent Current: 13mA

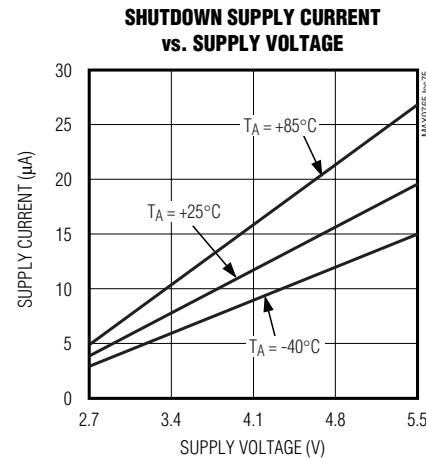

- ◆ Low-Power Shutdown Mode: 5µA

- ◆ MUTE Function

- ◆ Headphone Sense Input

- ◆ Stereo 2:1 Input Multiplexer

- ◆ Optional 2-Wire, I<sup>2</sup>C-Compatible, or Parallel Interface

- ◆ Small 32-Pin Thin QFN (5mm × 5mm × 0.8mm) Package

## Ordering Information

| PART              | TEMP RANGE     | PIN-PACKAGE     |

|-------------------|----------------|-----------------|

| <b>MAX9765ETJ</b> | -40°C to +85°C | 32 Thin QFN-EP* |

| <b>MAX9766ETJ</b> | -40°C to +85°C | 32 Thin QFN-EP* |

| <b>MAX9767ETJ</b> | -40°C to +85°C | 32 Thin QFN-EP* |

\*EP = Exposed paddle.

*Pin Configurations and Functional Diagrams appear at end of data sheet.*

## Simplified Diagram

**MAX9765/MAX9766/MAX9767**

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at [www.maxim-ic.com](http://www.maxim-ic.com).

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

## ABSOLUTE MAXIMUM RATINGS

|                                                                             |       |                                   |

|-----------------------------------------------------------------------------|-------|-----------------------------------|

| V <sub>DD</sub> to GND                                                      | ..... | +6V                               |

| S <sub>VDD</sub> to GND                                                     | ..... | +6V                               |

| S <sub>VDD</sub> to V <sub>DD</sub>                                         | ..... | -0.3V                             |

| P <sub>VDD</sub> to V <sub>DD</sub>                                         | ..... | ±0.3V                             |

| P <sub>GND</sub> to GND                                                     | ..... | ±0.3V                             |

| All Other Pins to GND                                                       | ..... | -0.3V to (V <sub>DD</sub> + 0.3V) |

| Output Short-Circuit Duration (to V <sub>DD</sub> or GND)                   | ..... | Continuous                        |

| Continuous Input Current (into any pin except power-supply and output pins) | ..... | ±20mA                             |

|                                                       |       |                 |

|-------------------------------------------------------|-------|-----------------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) | ..... |                 |

| 32-Pin Thin QFN (derate 26.3mW/°C above +70°C)        | ..... | 2105.3mW        |

| Operating Temperature Range                           | ..... | -40°C to +85°C  |

| Storage Temperature Range                             | ..... | -65°C to +150°C |

| Junction Temperature                                  | ..... | +150°C          |

| Lead Temperature (soldering, 10s)                     | ..... | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>DD</sub> = P<sub>VDD</sub> = 3.0V, GND = 0, HPS = MUTE = GND, S<sub>HNDN</sub> = 3V, C<sub>BIAS</sub> = 1μF, R<sub>IN</sub> = R<sub>F</sub> = 15kΩ, R<sub>L</sub> = ∞, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                        | SYMBOL                            | CONDITIONS                                                           | MIN                                           | TYP   | MAX | UNITS |

|------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------|-----------------------------------------------|-------|-----|-------|

| Supply Voltage Range                                             | V <sub>DD</sub> /P <sub>VDD</sub> | Inferred from PSRR test                                              | 2.7                                           | 5.5   |     | V     |

| Quiescent Supply Current (I <sub>VDD</sub> + I <sub>PVDD</sub> ) | I <sub>DD</sub>                   | Speaker mode                                                         | MAX9765/MAX9767                               | 12    | 28  | mA    |

|                                                                  |                                   |                                                                      | MAX9766                                       | 7     | 17  |       |

|                                                                  |                                   | Headphone mode, HPS = V <sub>DD</sub>                                |                                               | 7     | 17  |       |

| Shutdown Current                                                 | I <sub>SHDN</sub>                 | S <sub>HNDN</sub> = GND                                              |                                               | 5     | 18  | μA    |

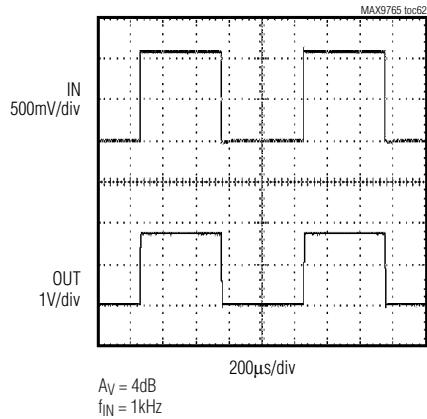

| Switching Time                                                   | t <sub>SW</sub>                   | Gain or input switching (MAX9765/MAX9766)                            |                                               | 10    |     | μs    |

| Turn-On/Turn-Off Time                                            | t <sub>ON/OFF</sub>               | C <sub>BIAS</sub> = 1μF, settled to 90%                              |                                               | 250   |     | ms    |

|                                                                  |                                   | C <sub>BIAS</sub> = 0.1μF, settled to 90%                            |                                               | 25    |     |       |

| Input Bias Current                                               | I <sub>BIAS</sub>                 |                                                                      |                                               | 50    |     | nA    |

| Thermal Shutdown Threshold                                       |                                   |                                                                      |                                               | 150   |     | °C    |

| Thermal Shutdown Hysteresis                                      |                                   |                                                                      |                                               | 8     |     | °C    |

| Output Short-Circuit Current                                     |                                   | To V <sub>DD</sub> or GND                                            |                                               | 1.2   |     | A     |

| <b>STANDBY SUPPLY (S<sub>VDD</sub>)</b>                          |                                   |                                                                      |                                               |       |     |       |

| Standby Current                                                  | I <sub>SVDD</sub>                 | V <sub>BIAS</sub> = 1.25V, V <sub>DD</sub> = 0V                      | 230                                           | 400   |     | μA    |

|                                                                  |                                   | V <sub>BIAS</sub> = 1.5V, V <sub>DD</sub> = 3V                       |                                               | 5     |     |       |

| <b>OUTPUT AMPLIFIERS (SPEAKER MODE)</b>                          |                                   |                                                                      |                                               |       |     |       |

| Output Offset Voltage                                            | V <sub>OS</sub>                   | V <sub>OUT+</sub> - V <sub>OUT-</sub> , A <sub>V</sub> = 1V/V        | 10                                            | 45    |     | mV    |

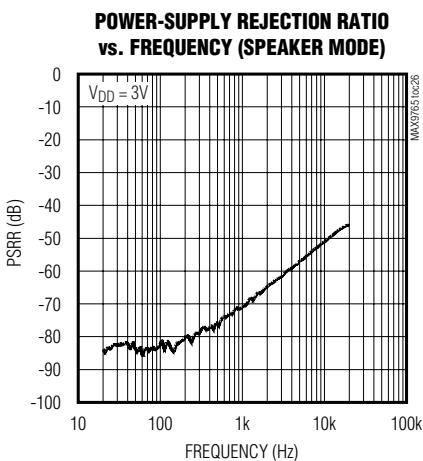

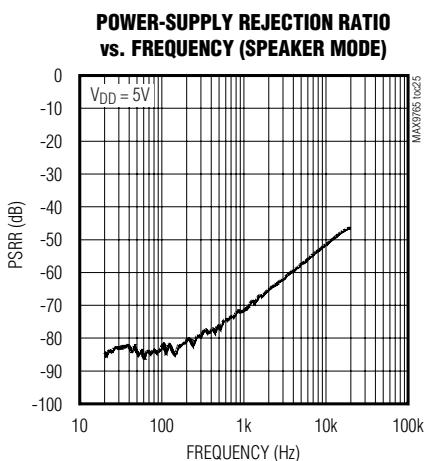

| Power-Supply Rejection Ratio                                     | PSRR                              | V <sub>DD</sub> = 2.7V to 5.5V                                       | 72                                            | 85    |     | dB    |

|                                                                  |                                   | f = 1kHz, V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub>                 |                                               | 72    |     |       |

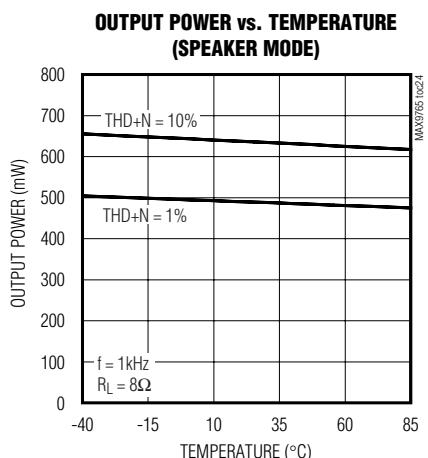

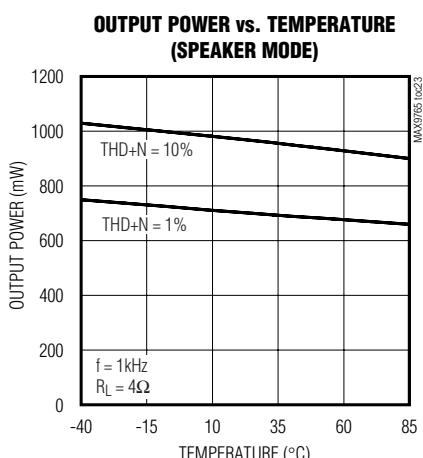

| Output Power                                                     | P <sub>OUT</sub>                  | f <sub>IN</sub> = 1kHz, THD+N = 1%, T <sub>A</sub> = +25°C (Note 2)  | R <sub>L</sub> = 8Ω                           | 450   |     | mW    |

|                                                                  |                                   |                                                                      | R <sub>L</sub> = 4Ω                           | 400   | 750 |       |

| Total Harmonic Distortion Plus Noise                             | THD+N                             | f <sub>IN</sub> = 1kHz, BW = 22Hz to 22kHz                           | P <sub>OUT</sub> = 200mW, R <sub>L</sub> = 8Ω | 0.033 |     | %     |

|                                                                  |                                   |                                                                      | P <sub>OUT</sub> = 400mW, R <sub>L</sub> = 4Ω | 0.065 |     |       |

| Signal-to-Noise Ratio                                            | SNR                               | R <sub>L</sub> = 8Ω, V <sub>OUT-</sub> = 1.4VRMS, BW = 22Hz to 22kHz |                                               | 89    |     | dB    |

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = PV_{DD} = 3.0V$ ,  $GND = 0$ ,  $HPS = GND$ ,  $\bar{SHDN} = 3V$ ,  $C_{BIAS} = 1\mu F$ ,  $R_{IN} = R_F = 15k\Omega$ ,  $R_L = \infty$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                            | SYMBOL     | CONDITIONS                                                                                           | MIN                                           | TYP   | MAX | UNITS           |

|------------------------------------------------------|------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------|-----|-----------------|

| Maximum Capacitive Load Drive                        | $C_L$      | No sustained oscillations                                                                            | 400                                           |       |     | pF              |

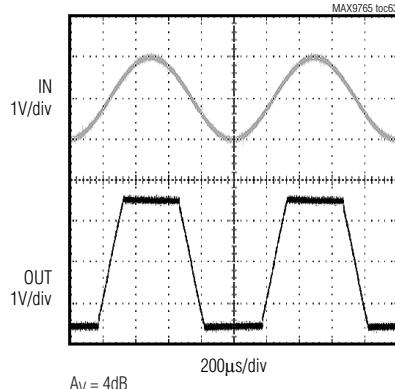

| Slew Rate                                            | SR         |                                                                                                      | 1.4                                           |       |     | V/ $\mu$ s      |

| Crosstalk                                            |            | $f_{IN} = 10kHz$                                                                                     | 73                                            |       |     | dB              |

| <b>OUTPUT AMPLIFIERS (HEADPHONE MODE)</b>            |            |                                                                                                      |                                               |       |     |                 |

| Power-Supply Rejection Ratio                         | PSRR       | $V_{DD} = 2.7V$ to $5.5V$                                                                            | 95                                            |       |     | dB              |

|                                                      |            | $f = 1kHz$ , $V_{RIPPLE} = 200mV_{P-P}$                                                              | 75                                            |       |     |                 |

|                                                      |            | $f = 20kHz$ , $V_{RIPPLE} = 200mV_{P-P}$                                                             | 50                                            |       |     |                 |

| Output Power                                         | POUT       | $f_{IN} = 1kHz$ , $THD+N = 1\%$ ,<br>$T_A = +25^\circ C$ (Note 2)                                    | $R_L = 32\Omega$                              | 40    |     | mW              |

|                                                      |            |                                                                                                      | $R_L = 16\Omega$                              | 35    | 65  |                 |

| Total Harmonic Distortion Plus Noise                 | THD+N      | $f_{IN} = 1kHz$ , $BW = 22Hz$ to $22kHz$                                                             | $V_{OUT} = 0.7V_{RMS}$ ,<br>$R_L = 10k\Omega$ | 0.002 |     | %               |

|                                                      |            |                                                                                                      | $POUT = 15mW$ ,<br>$R_L = 32\Omega$           | 0.005 |     |                 |

|                                                      |            |                                                                                                      | $POUT = 30mW$ ,<br>$R_L = 16\Omega$           | 0.004 |     |                 |

| Signal-to-Noise Ratio                                | SNR        | $R_L = 8\Omega$ , $V_{OUT\_} = 1.4V_{RMS}$ ,<br>$BW = 20Hz$ to $22kHz$                               |                                               | 89    |     | dB              |

| Slew Rate                                            | SR         |                                                                                                      |                                               | 0.7   |     | V/ $\mu$ s      |

| Maximum Capacitive Load Drive                        | $C_L$      | No sustained oscillations                                                                            | 200                                           |       |     | pF              |

| Crosstalk                                            |            | $f_{IN} = 10kHz$                                                                                     | 79                                            |       |     | dB              |

| <b>BIAS VOLTAGE (BIAS)</b>                           |            |                                                                                                      |                                               |       |     |                 |

| BIAS Voltage                                         | $V_{BIAS}$ |                                                                                                      | 1.4                                           | 1.5   | 1.6 | V               |

| Output Resistance                                    | $R_{BIAS}$ |                                                                                                      | 50                                            |       |     | k $\Omega$      |

| <b>MICROPHONE AMPLIFIER GENERAL</b>                  |            |                                                                                                      |                                               |       |     |                 |

| Output Voltage Swing                                 | VOUT       | $R_L = 100k\Omega$                                                                                   | $V_{DD} - V_{OH}$                             | 35    | 70  | mV              |

|                                                      |            |                                                                                                      | $V_{OL} - GND$                                | 50    | 400 |                 |

|                                                      |            | $R_L = 2k\Omega$                                                                                     | $V_{DD} - V_{OH}$                             | 80    | 150 |                 |

|                                                      |            |                                                                                                      | $V_{OL} - GND$                                | 70    | 400 |                 |

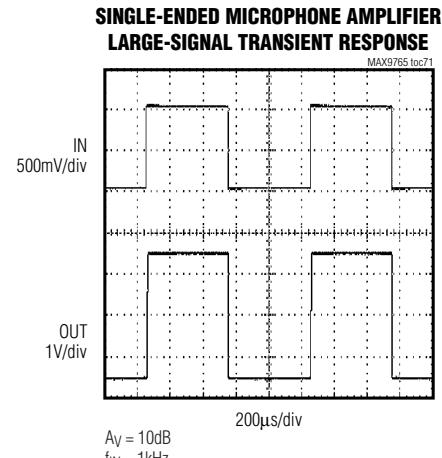

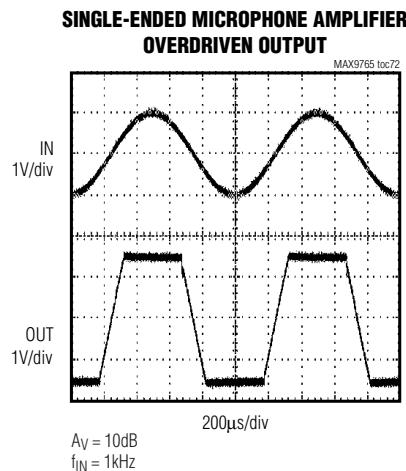

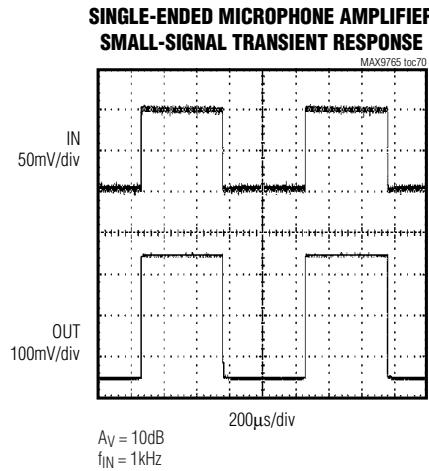

| Slew Rate                                            | SR         | $A_V = 10dB$                                                                                         |                                               | 0.6   |     | V/ $\mu$ s      |

| Output Short-Circuit Current                         |            | To $V_{DD}$ or GND                                                                                   |                                               | 10    |     | mA              |

| Maximum Capacitive Load Drive                        | $C_L$      | No sustained oscillations                                                                            | 50                                            |       |     | pF              |

| <b>DIFFERENTIAL INPUT AMPLIFIER (MICIN+, MICIN-)</b> |            |                                                                                                      |                                               |       |     |                 |

| Input Offset Voltage                                 | $V_{OS}$   |                                                                                                      | 2                                             | 5     |     | mV              |

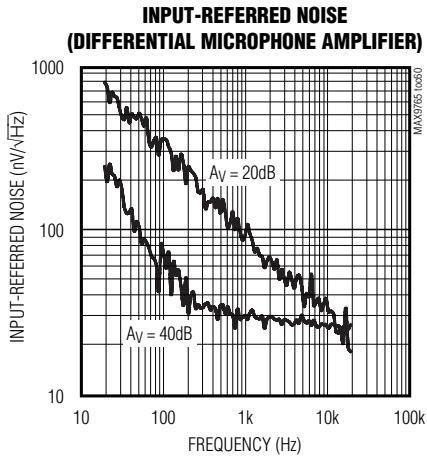

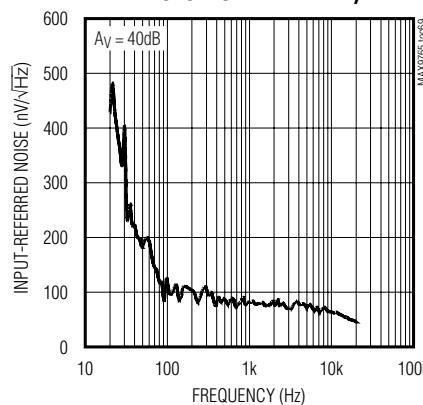

| Input Noise-Voltage Density                          | en         | $f_{IN} = 1kHz$                                                                                      | $A_V = 20dB$                                  | 31    |     | nV/ $\sqrt{Hz}$ |

|                                                      |            |                                                                                                      | $A_V = 40dB$                                  | 11.6  |     |                 |

| Total Harmonic Distortion Plus Noise                 | THD+N      | $V_{DD} = 3V$ , $V_{OUT} = 0.35V_{RMS}$ , $A_V = 10dB$ ,<br>$f_{IN} = 1kHz$ , $BW = 22Hz$ to $22kHz$ |                                               | 0.01  |     | %               |

| Small-Signal Bandwidth                               | BW-3dB     | $A_V = 40dB$ , $V_{OUT} = 100mV_{P-P}$                                                               |                                               | 300   |     | kHz             |

| Input Resistance                                     | $R_{IN}$   | MICIN_ to GND                                                                                        | 100                                           |       |     | k $\Omega$      |

MAX9765/MAX9766/MAX9767

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = PV_{DD} = 3.0V$ ,  $GND = 0$ ,  $HPS = GND$ ,  $SHDN = 3V$ ,  $C_{BIAS} = 1\mu F$ ,  $R_{IN} = R_F = 15k\Omega$ ,  $R_L = \infty$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                    | SYMBOL               | CONDITIONS                                                                                  | MIN                                      | TYP             | MAX | UNITS           |

|----------------------------------------------|----------------------|---------------------------------------------------------------------------------------------|------------------------------------------|-----------------|-----|-----------------|

| Input Resistance Matching                    | R <sub>MATCH</sub>   |                                                                                             |                                          | 1               |     | %               |

| Differential Gain Accuracy                   | A <sub>VDIFF</sub>   | MAX9765, $A_V = 4dB$ to $39dB$                                                              |                                          | 2               | 4   | %               |

|                                              |                      | MAX9766, $A_V = 10dB$ to $45dB$                                                             |                                          | 2               | 4   |                 |

|                                              |                      | MAX9767, $A_V = 10dB$ , $20dB$ , $30dB$                                                     |                                          | 2               | 4   |                 |

| Common-Mode Rejection Ratio                  | C <sub>MRR</sub>     | $A_V = 10dB$ , $f_{IN} = 1kHz$ , $V_{CM} = 200mV_{P-P}$ , $R_S = 2k\Omega$                  |                                          | 60              |     | dB              |

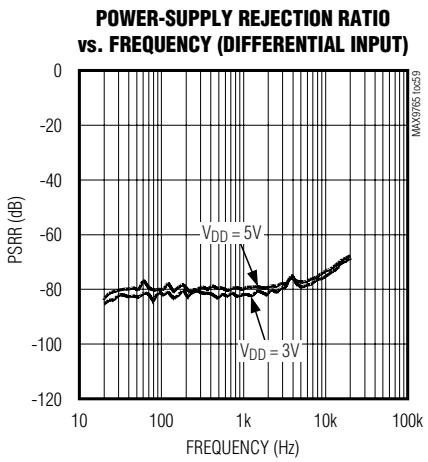

| Power-Supply Rejection Ratio                 | PSRR                 | A <sub>V</sub> = $10dB$ , output referred                                                   | V <sub>DD</sub> = $2.7V$ to $5.5V$       | 62              | 80  | dB              |

|                                              |                      |                                                                                             | f = $1kHz$ , $V_{RIPPLE} = 200mV_{P-P}$  |                 | 80  |                 |

|                                              |                      |                                                                                             | f = $20kHz$ , $V_{RIPPLE} = 200mV_{P-P}$ |                 | 68  |                 |

| Common-Mode Input Voltage Range              | V <sub>CM</sub>      |                                                                                             |                                          | 1               |     | V               |

| <b>SINGLE-ENDED INPUT AMPLIFIER (AUXIN)</b>  |                      |                                                                                             |                                          |                 |     |                 |

| Input Offset Voltage                         | V <sub>OS</sub>      |                                                                                             |                                          | 4               | 10  | mV              |

| Input Noise-Voltage Density                  | e <sub>N</sub>       | A <sub>V</sub> = $20dB$ , $f_{IN} = 1kHz$                                                   |                                          | 73              |     | nV/ $\sqrt{Hz}$ |

| Total Harmonic Distortion Plus Noise         | THD+N                | A <sub>V</sub> = $10dB$ , $f_{IN} = 1kHz$ , BW = $22Hz$ to $22kHz$ , $V_{OUT} = 0.7V_{RMS}$ |                                          | 0.01            |     | %               |

| Small-Signal Bandwidth                       | BW. <sub>3dB</sub>   | A <sub>V</sub> = $20dB$ , $V_{OUT} = 100mV_{P-P}$                                           |                                          | 200             |     | kHz             |

| Input Resistance                             | R <sub>IN</sub>      |                                                                                             |                                          | 100             |     | k $\Omega$      |

| Voltage Gain Accuracy                        | A <sub>V</sub>       |                                                                                             |                                          | 4               |     | %               |

| Power-Supply Rejection Ratio                 | PSRR                 | A <sub>V</sub> = $10dB$ , output referred                                                   | V <sub>DD</sub> = $2.7V$ to $5.5V$       | 65              | 80  | dB              |

|                                              |                      |                                                                                             | f = $1kHz$ , $V_{RIPPLE} = 200mV_{P-P}$  |                 | 76  |                 |

|                                              |                      |                                                                                             | f = $20kHz$ , $V_{RIPPLE} = 200mV_{P-P}$ |                 | 58  |                 |

| <b>MICROPHONE BIAS OUTPUT (MICBIAS)</b>      |                      |                                                                                             |                                          |                 |     |                 |

| Microphone Bias Output Voltage               | V <sub>MICBIAS</sub> | V <sub>DD</sub> = $2.7V$ to $5.5V$ , $I_{LOAD} = 500\mu A$                                  | 2.4                                      | 2.5             | 2.6 | V               |

| Output Noise-Voltage Density                 | e <sub>N</sub>       | f = $1kHz$                                                                                  |                                          | 52              |     | nV/ $\sqrt{Hz}$ |

| Power-Supply Rejection Ratio                 | PSRR                 | V <sub>DD</sub> = $2.7V$ to $5.5V$                                                          | 63                                       | 72              |     | dB              |

|                                              |                      | f <sub>IN</sub> = $1kHz$ , $V_{RIPPLE} = 200mV_{P-P}$                                       |                                          | 70              |     |                 |

| <b>DIGITAL INPUTS (MUTE, SHDN, INT/EXT)</b>  |                      |                                                                                             |                                          |                 |     |                 |

| Input Voltage High                           | V <sub>IH</sub>      |                                                                                             | 2                                        |                 |     | V               |

| Input Voltage Low                            | V <sub>IL</sub>      |                                                                                             |                                          | 0.8             |     | V               |

| Input Leakage Current                        | I <sub>IN</sub>      |                                                                                             |                                          | $\pm 1$         |     | $\mu A$         |

| <b>MAX9767 MICGAIN INPUT (TRI-STATE PIN)</b> |                      |                                                                                             |                                          |                 |     |                 |

| Input Voltage High                           | V <sub>IH</sub>      |                                                                                             |                                          | V <sub>DD</sub> |     | V               |

| Input Voltage Low                            | V <sub>IL</sub>      |                                                                                             |                                          | GND             |     | V               |

| Input Voltage Mid                            | V <sub>IZ</sub>      |                                                                                             |                                          | FLOAT           |     | V               |

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = PV_{DD} = 3.0V$ ,  $GND = 0$ ,  $HPS = MUTE = GND$ ,  $\bar{SHDN} = 3V$ ,  $C_{BIAS} = 1\mu F$ ,  $R_{IN} = R_F = 15k\Omega$ ,  $R_L = \infty$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                                        | SYMBOL       | CONDITIONS         | MIN                 | TYP     | MAX | UNITS   |

|------------------------------------------------------------------|--------------|--------------------|---------------------|---------|-----|---------|

| <b>HEADPHONE SENSE INPUT (HPS)</b>                               |              |                    |                     |         |     |         |

| Input Voltage High                                               | $V_{IH}$     |                    | $0.9 \times V_{DD}$ |         |     | V       |

| Input Voltage Low                                                | $V_{IL}$     |                    | $0.7 \times V_{DD}$ |         |     | V       |

| Input Leakage Current                                            | $I_{IN}$     |                    |                     | $\pm 1$ |     | $\mu A$ |

| <b>2-WIRE SERIAL INTERFACE (SCL, SDA, ADD) (MAX9765/MAX9766)</b> |              |                    |                     |         |     |         |

| Input Voltage High                                               | $V_{IH}$     | $V_{DD} > 3.6V$    | 3                   |         |     | V       |

|                                                                  |              | $V_{DD} \leq 3.6V$ | 2                   |         |     |         |

| Input Voltage Low                                                | $V_{IL}$     |                    |                     | 0.8     |     | V       |

| Input Hysteresis                                                 |              |                    |                     | 0.2     |     | V       |

| Input High Leakage Current                                       | $I_{IH}$     | $V_{IN} = 3V$      |                     | $\pm 1$ |     | $\mu A$ |

| Input Low Leakage Current                                        | $I_{IL}$     | $V_{IN} = 0V$      |                     | $\pm 1$ |     | $\mu A$ |

| Input Capacitance                                                | $C_{IN}$     |                    |                     | 10      |     | $pF$    |

| Output Voltage Low                                               | $V_{OL}$     | $I_{OL} = 3mA$     |                     | 0.4     |     | V       |

| Output Current High                                              | $I_{OH}$     | $V_{OH} = 3V$      |                     | 1       |     | $\mu A$ |

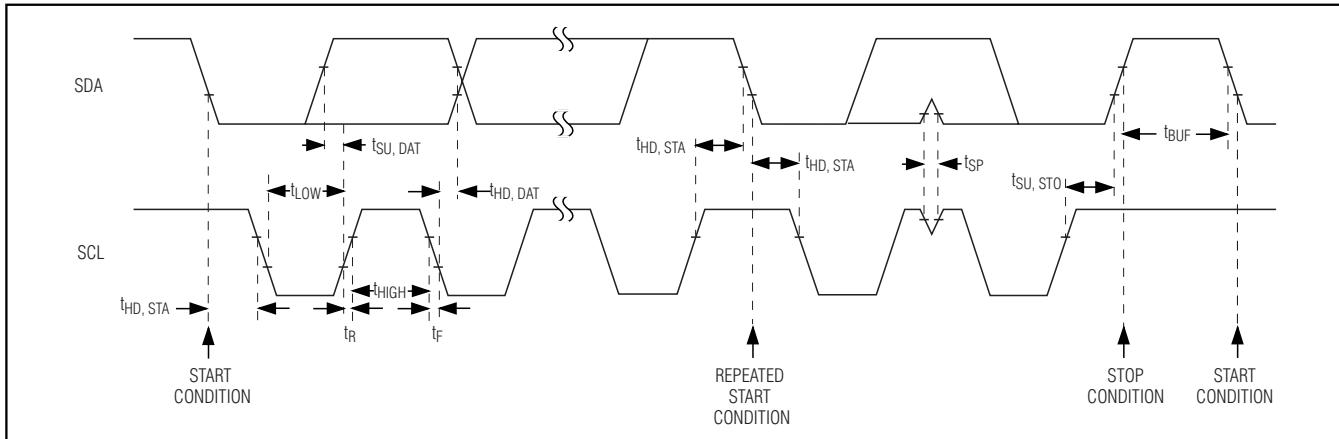

| <b>TIMING CHARACTERISTICS (MAX9765/MAX9766)</b>                  |              |                    |                     |         |     |         |

| Serial Clock Frequency                                           | $f_{SCL}$    |                    |                     | 400     |     | kHz     |

| Bus Free Time Between STOP and START Conditions                  | $t_{BUF}$    |                    |                     | 1.3     |     | $\mu s$ |

| START Condition Hold Time                                        | $t_{HD:STA}$ |                    |                     | 0.6     |     | $\mu s$ |

| START Condition Setup Time                                       | $t_{SU:STA}$ |                    |                     | 0.6     |     | $\mu s$ |

| Clock Period Low                                                 | $t_{LOW}$    |                    |                     | 1.3     |     | $\mu s$ |

| Clock Period High                                                | $t_{HIGH}$   |                    |                     | 0.6     |     | $\mu s$ |

| Data Setup Time                                                  | $t_{SU:DAT}$ |                    |                     | 100     |     | ns      |

| Data Hold Time                                                   | $t_{HD:DAT}$ | (Note 3)           |                     | 0       | 0.9 | $\mu s$ |

| Receive SCL/SDA Rise Time                                        | $t_R$        | (Note 4)           | $20 + 0.1C_B$       | 300     |     | ns      |

| Receive SCL/SDA Fall Time                                        | $t_F$        | (Note 4)           | $20 + 0.1C_B$       | 300     |     | ns      |

| Transmit SDA Fall Time                                           | $t_F$        | (Note 4)           | $20 + 0.1C_B$       | 250     |     | ns      |

| Pulse Width of Suppressed Spike                                  | $t_{SP}$     | (Note 5)           |                     | 50      |     | ns      |

**Note 1:** All devices are 100% production tested at  $+25^\circ C$ . All temperature limits are guaranteed by design.

**Note 2:**  $P_{OUT}$  limits are tested by a combination of electrical and guaranteed by design.

**Note 3:** A device must provide a hold time of at least 300ns for the SDA signal to bridge the undefined region of SCL's falling edge.

**Note 4:**  $C_B$  = total capacitance of one of the bus lines in picofarads. Device tested with  $C_B = 400pF$ . 1k $\Omega$  pullup resistors connected from SDA/SCL to  $V_{DD}$ .

**Note 5:** Input filters on SDA, SCL, and ADD suppress noise spikes less than 50ns.

MAX9765/MAX9766/MAX9767

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

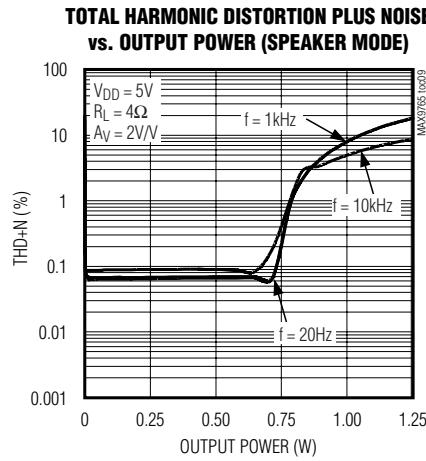

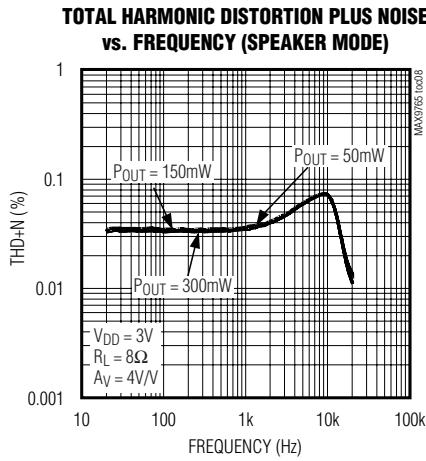

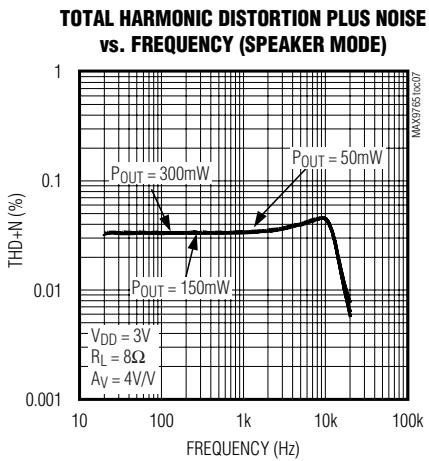

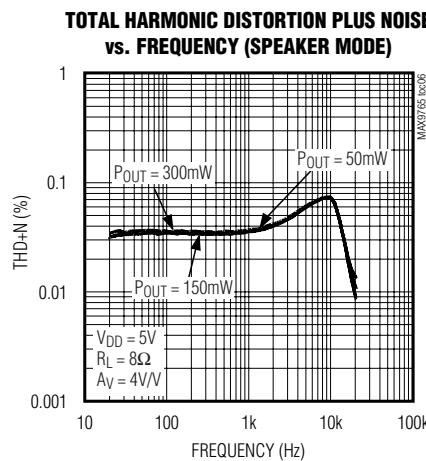

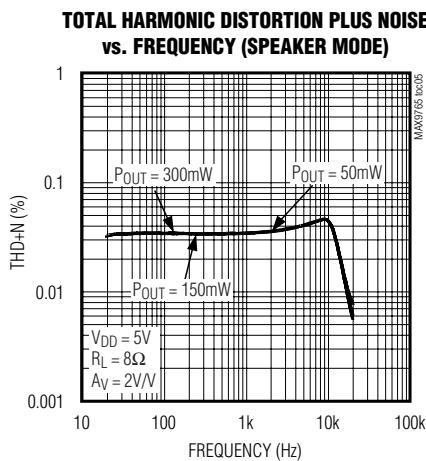

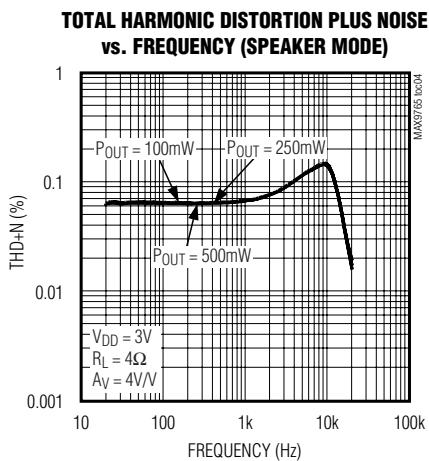

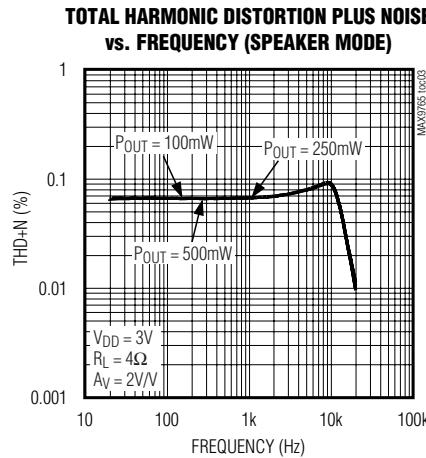

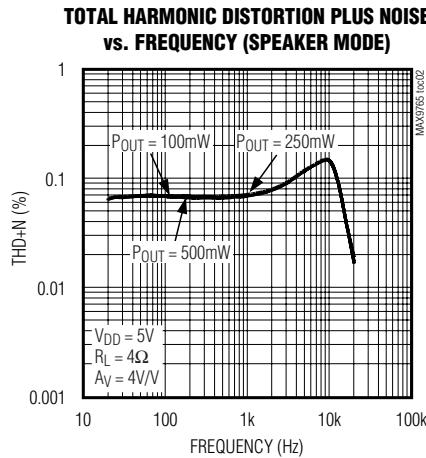

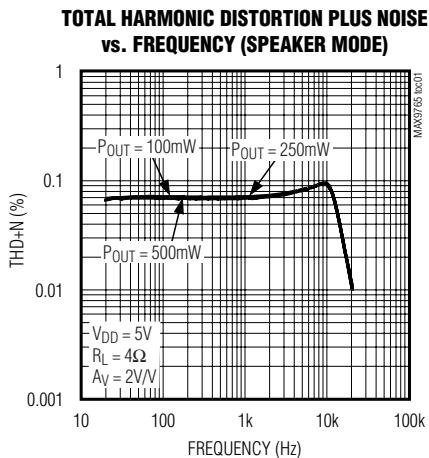

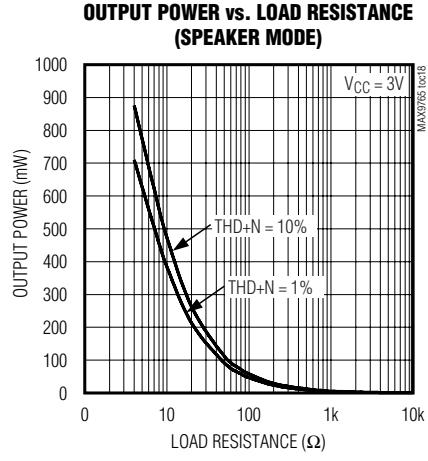

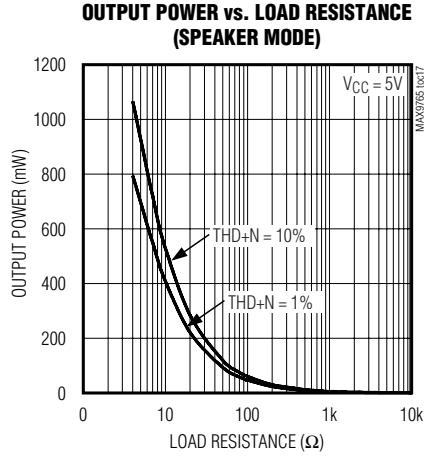

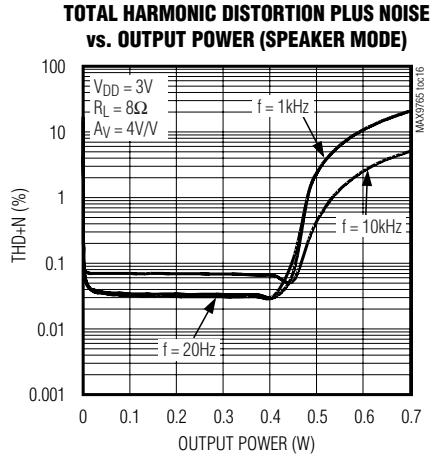

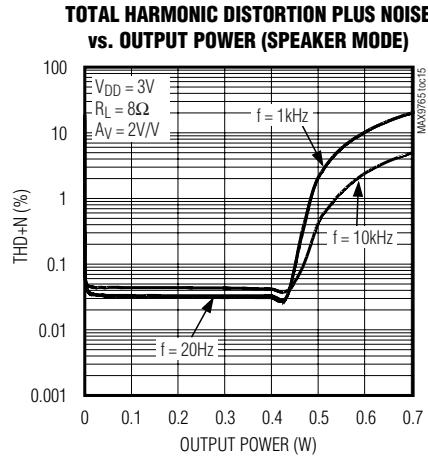

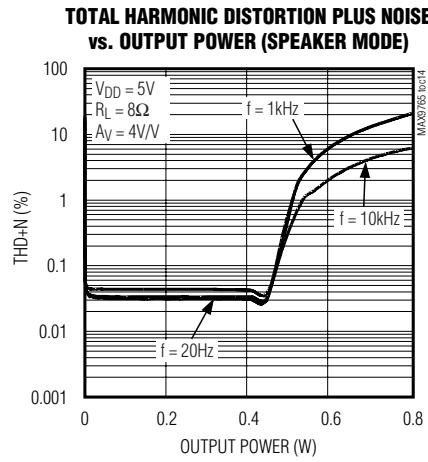

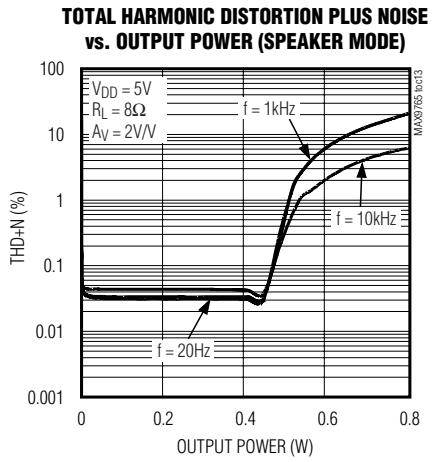

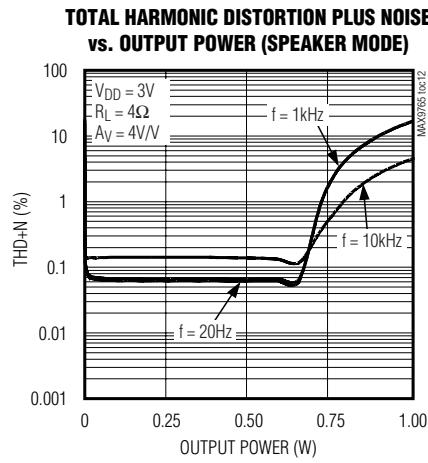

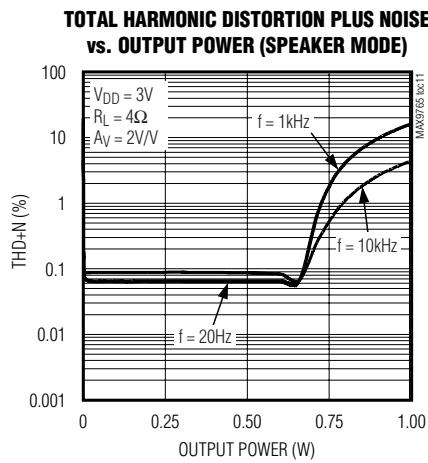

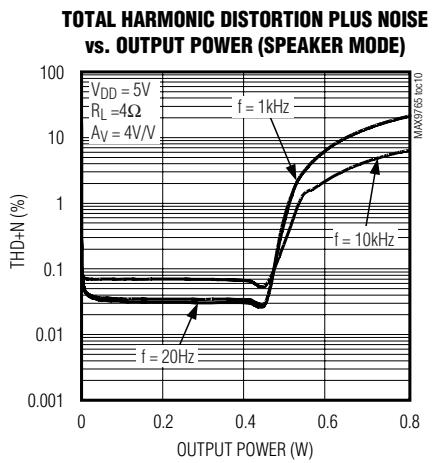

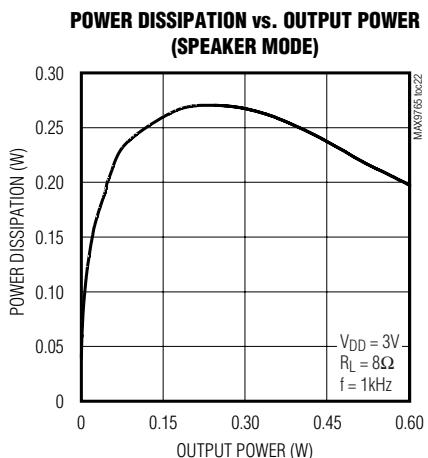

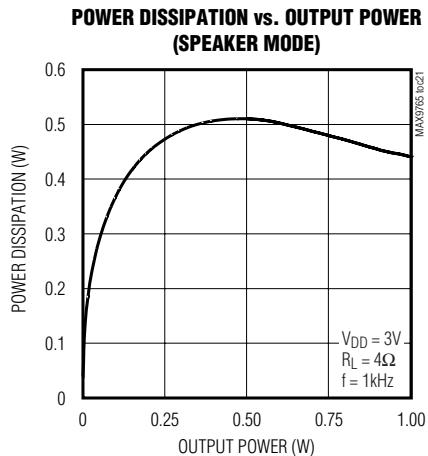

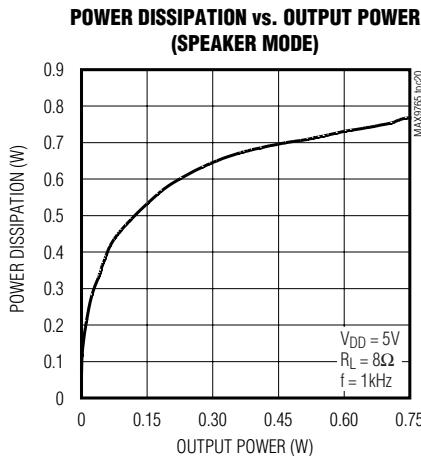

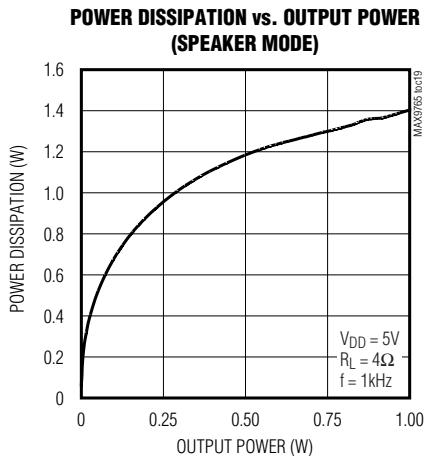

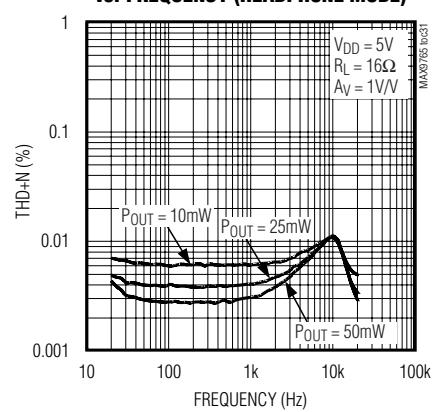

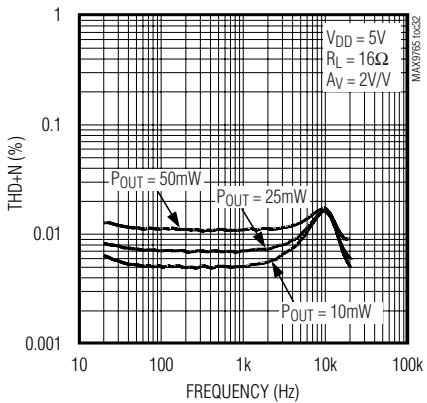

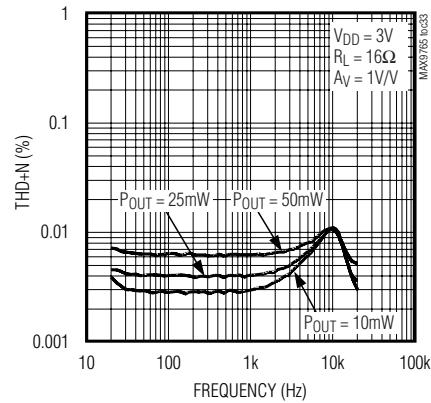

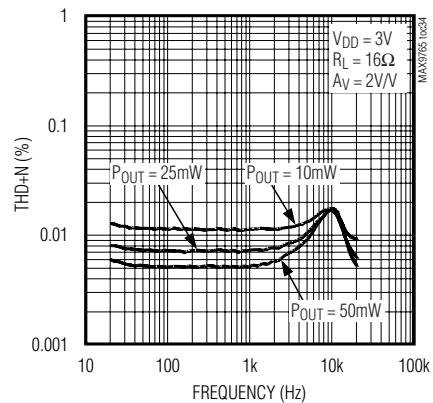

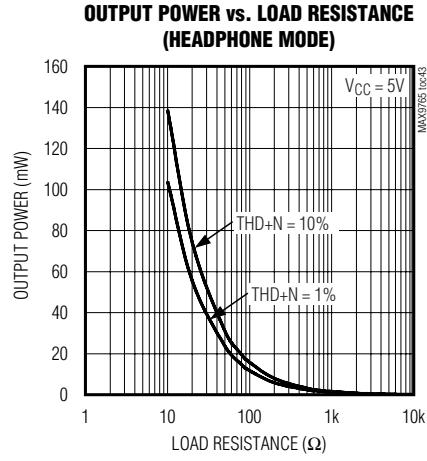

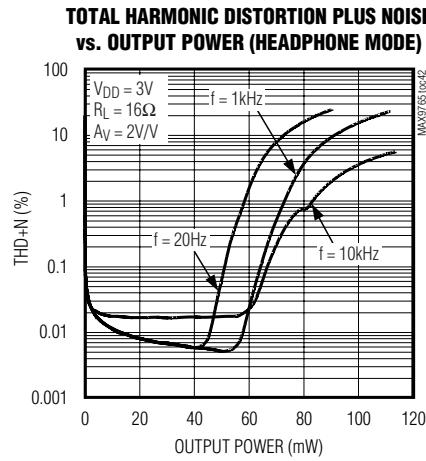

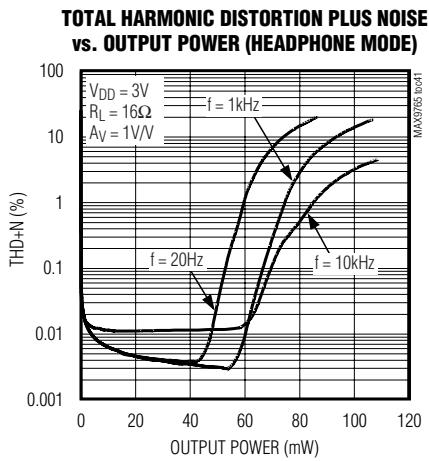

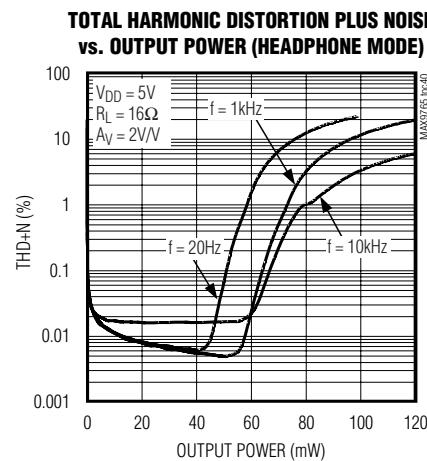

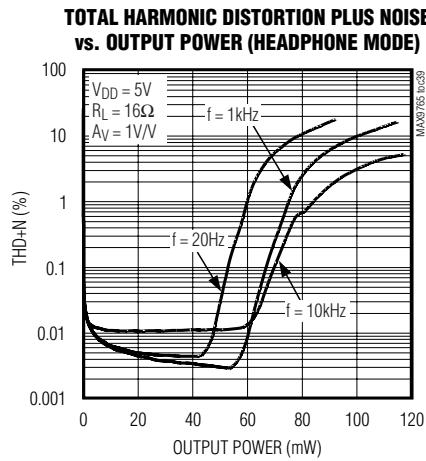

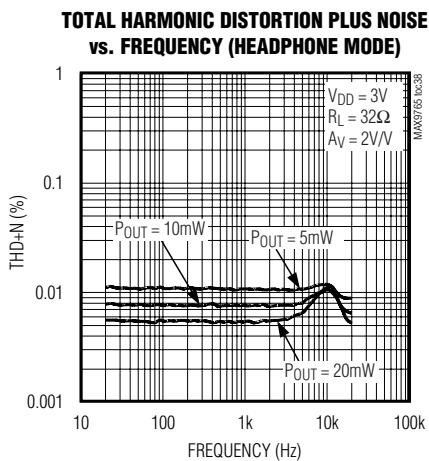

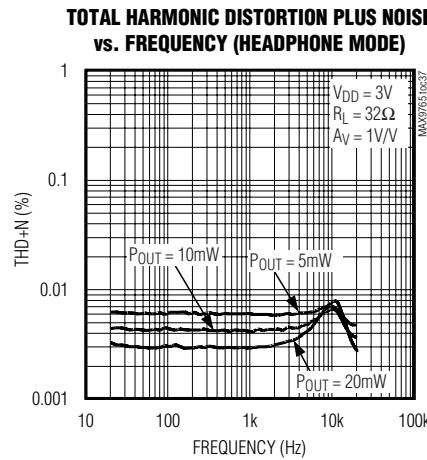

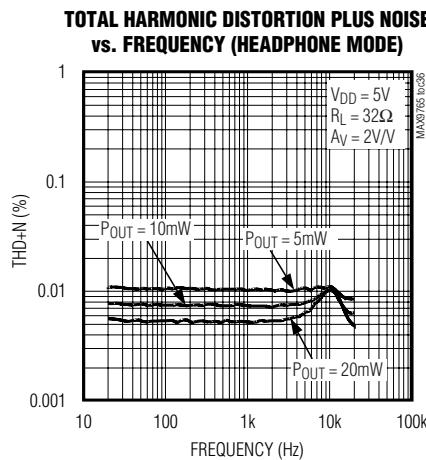

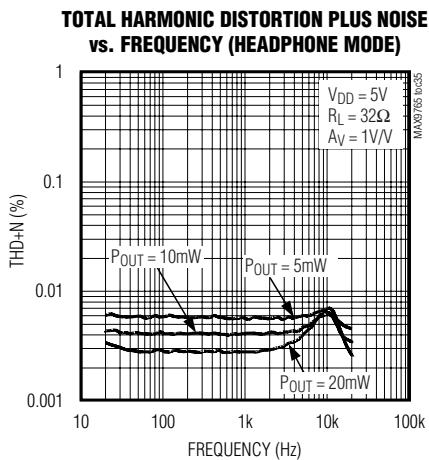

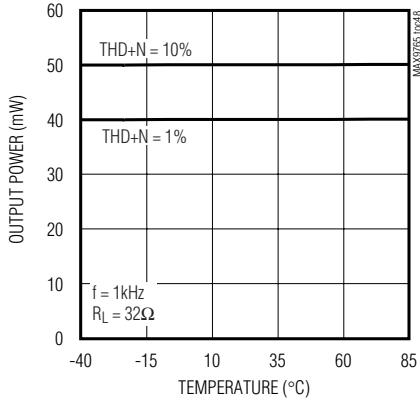

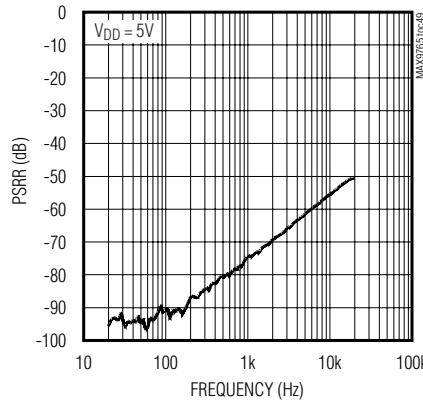

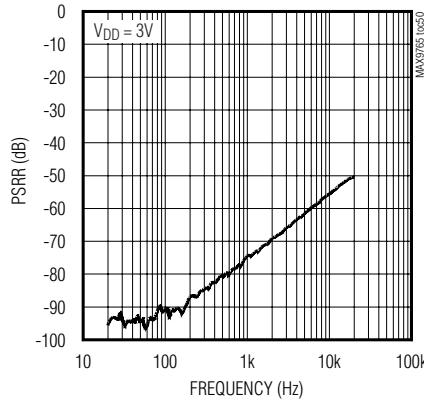

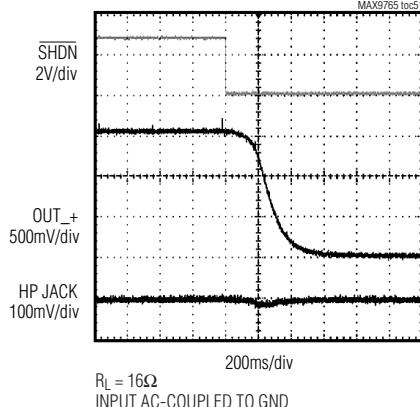

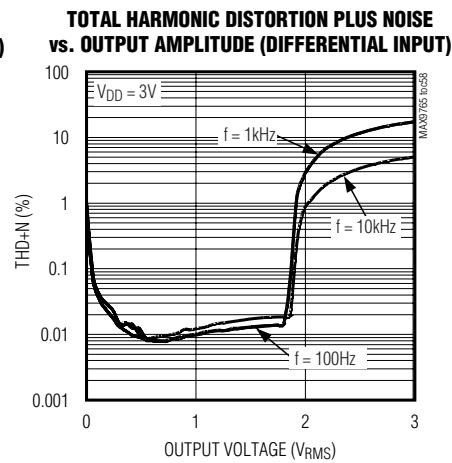

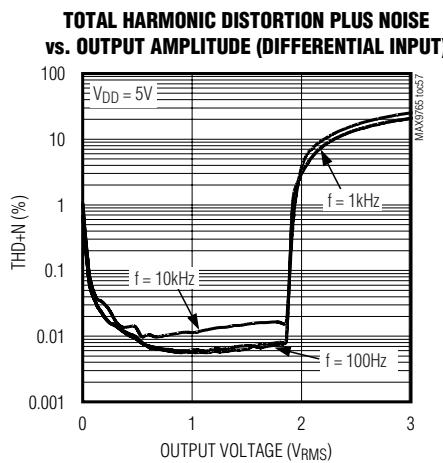

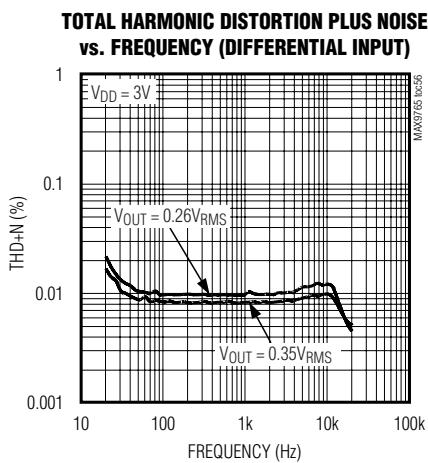

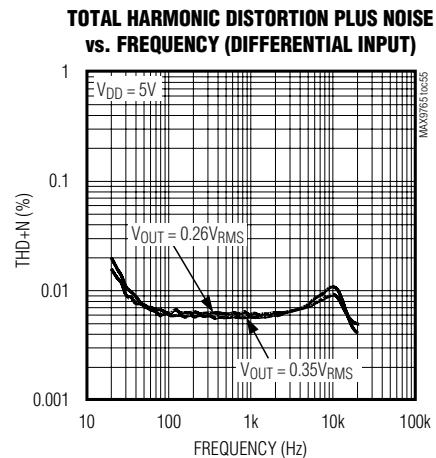

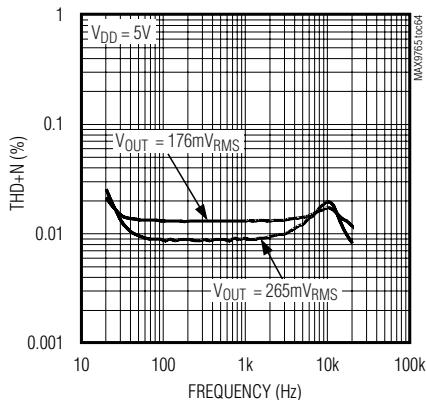

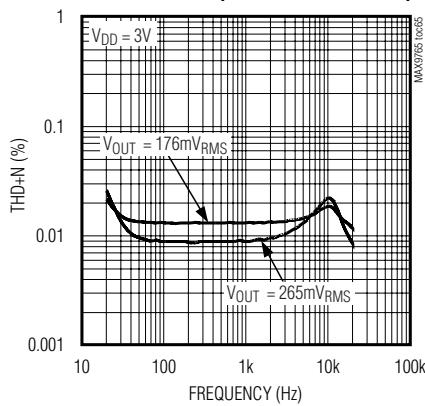

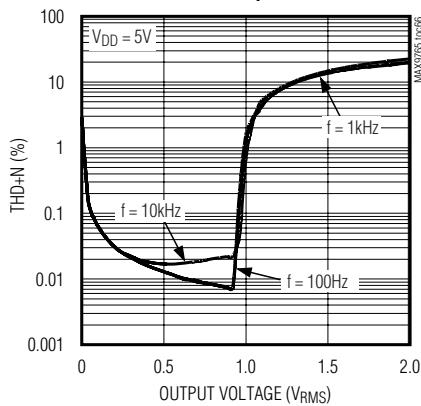

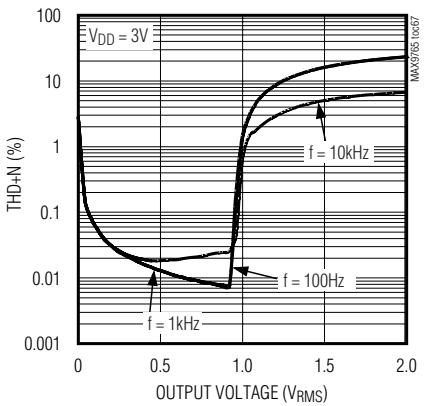

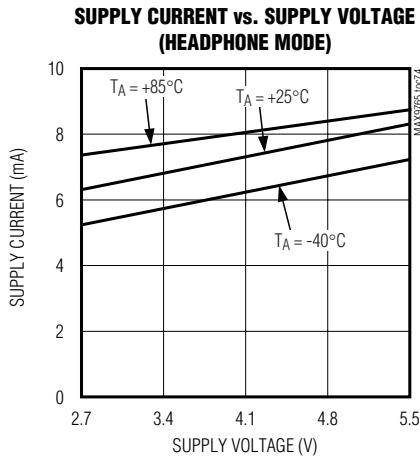

## Typical Operating Characteristics

( $V_{DD} = PV_{DD} = 5V$ ,  $BW = 22\text{Hz}$  to  $22\text{kHz}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

MAX9765/MAX9766/MAX9767

## Typical Operating Characteristics (continued)

( $V_{DD} = PV_{DD} = 5V$ ,  $BW = 22\text{Hz}$  to  $22\text{kHz}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

## Typical Operating Characteristics (continued)

( $V_{DD} = PV_{DD} = 5V$ ,  $BW = 22\text{Hz}$  to  $22\text{kHz}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

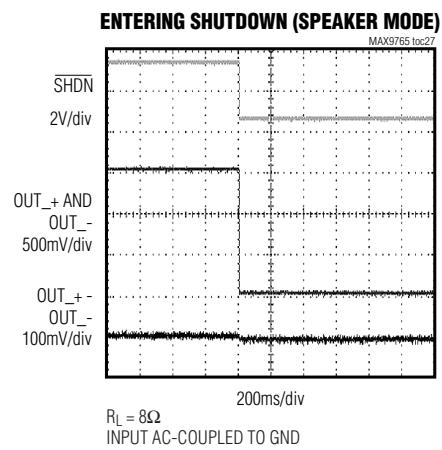

## Typical Operating Characteristics (continued)

( $V_{DD} = PV_{DD} = 5V$ ,  $BW = 22\text{Hz}$  to  $22\text{kHz}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

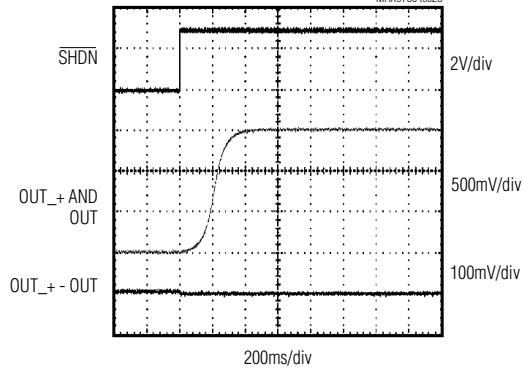

### EXITING SHUTDOWN (SPEAKER MODE)

MAX9765 Ic28

$R_L = 8\Omega$

INPUT AC-COUPLED TO GND

$C_{BIAS} = 1\mu\text{F}$

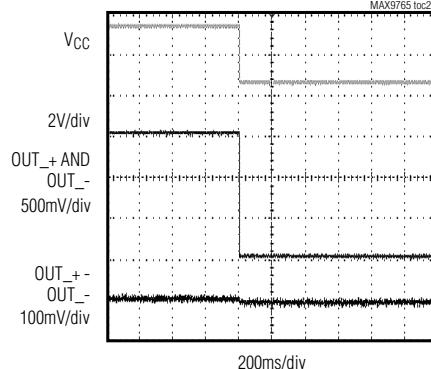

### ENTERING POWER-DOWN (SPEAKER MODE)

MAX9765 Ic29

$R_L = 8\Omega$

INPUT AC-COUPLED TO GND

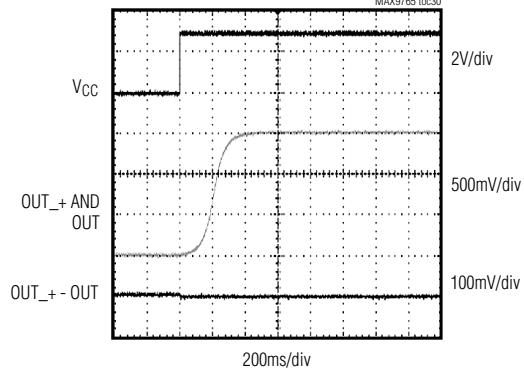

### POWER-UP (SPEAKER MODE)

MAX9765 Ic30

$R_L = 8\Omega$

INPUT AC-COUPLED TO GND

$C_{BIAS} = 1\mu\text{F}$

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY (HEADPHONE MODE)

MAX9765 Ic31

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY (HEADPHONE MODE)

MAX9765 Ic32

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY (HEADPHONE MODE)

MAX9765 Ic33

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY (HEADPHONE MODE)

MAX9765 Ic34

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

## Typical Operating Characteristics (continued)

( $V_{DD} = PV_{DD} = 5V$ ,  $BW = 22\text{Hz}$  to  $22\text{kHz}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

## Typical Operating Characteristics (continued)

( $V_{DD} = PV_{DD} = 5V$ ,  $BW = 22\text{Hz}$  to  $22\text{kHz}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

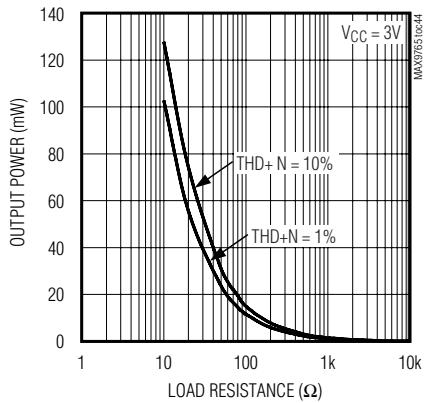

**OUTPUT POWER vs. LOAD RESISTANCE (HEADPHONE MODE)**

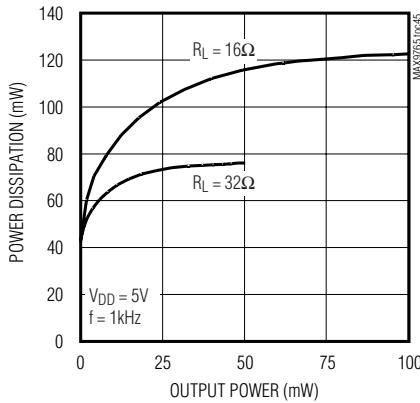

**POWER DISSIPATION vs. OUTPUT POWER (HEADPHONE MODE)**

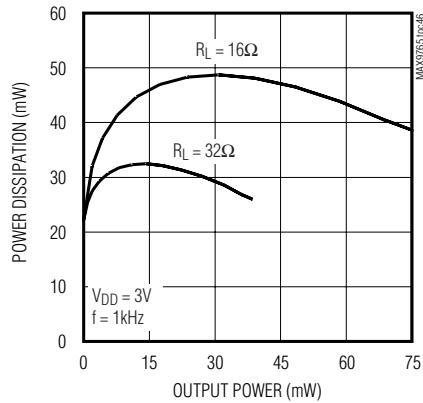

**POWER DISSIPATION vs. OUTPUT POWER (HEADPHONE MODE)**

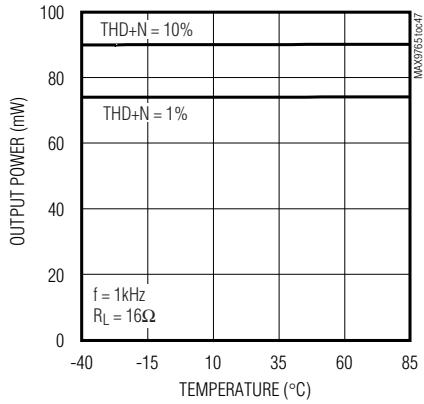

**OUTPUT POWER vs. TEMPERATURE (HEADPHONE MODE)**

**OUTPUT POWER vs. TEMPERATURE (HEADPHONE MODE)**

**POWER-SUPPLY REJECTION RATIO vs. FREQUENCY (HEADPHONE MODE)**

**POWER-SUPPLY REJECTION RATIO vs. FREQUENCY (HEADPHONE MODE)**

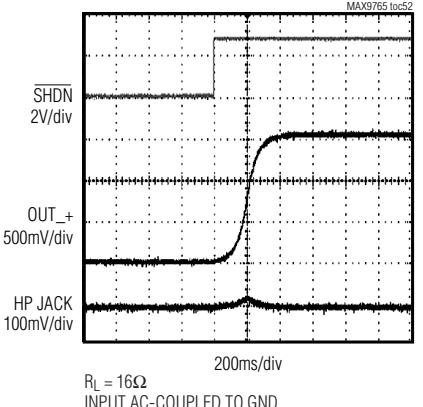

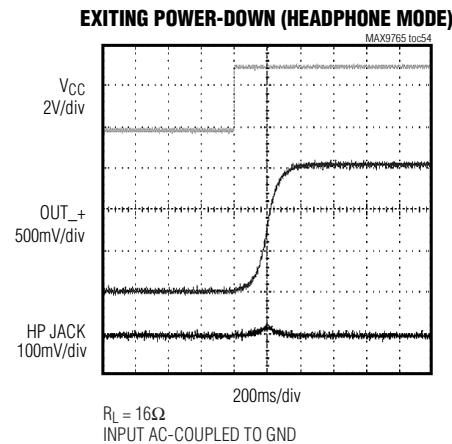

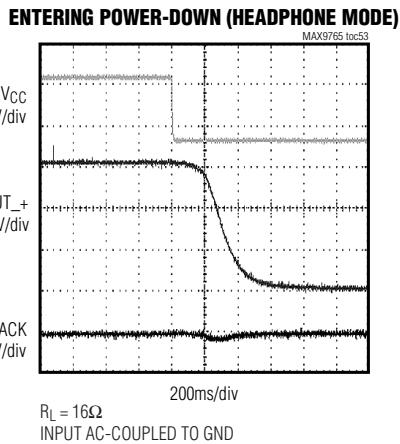

**ENTERING SHUTDOWN (HEADPHONE MODE)**

**EXITING SHUTDOWN (HEADPHONE MODE)**

MAX9765/MAX9766/MAX9767

## 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

### Typical Operating Characteristics (continued)

( $V_{DD} = PV_{DD} = 5V$ ,  $BW = 22\text{Hz}$  to  $22\text{kHz}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

MAX9765/MAX9766/MAX9767

## Typical Operating Characteristics (continued)

( $V_{DD} = PV_{DD} = 5V$ ,  $BW = 22\text{Hz}$  to  $22\text{kHz}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

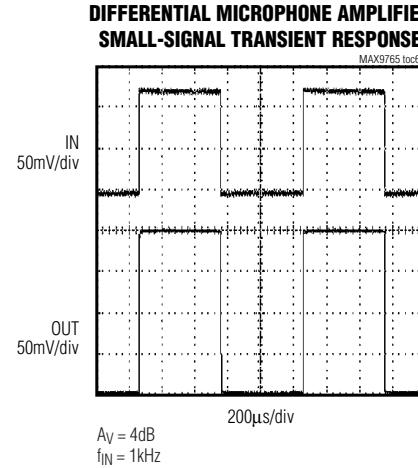

### DIFFERENTIAL MICROPHONE AMPLIFIER LARGE-SIGNAL TRANSIENT RESPONSE

### DIFFERENTIAL MICROPHONE AMPLIFIER OVERDRIVEN OUTPUT

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY (SINGLE-ENDED INPUT)

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY (SINGLE-ENDED INPUT)

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT AMPLITUDE (SINGLE-ENDED INPUT)

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT AMPLITUDE (SINGLE-ENDED INPUT)

### POWER-SUPPLY REJECTION RATIO vs. FREQUENCY (SINGLE-ENDED INPUT)

### INPUT-REFERRED NOISE (SINGLE-ENDED INPUT MICROPHONE AMPLIFIER)

## **750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux**

### **Typical Operating Characteristics (continued)**

( $V_{DD} = PV_{DD} = 5V$ ,  $BW = 22\text{Hz}$  to  $22\text{kHz}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

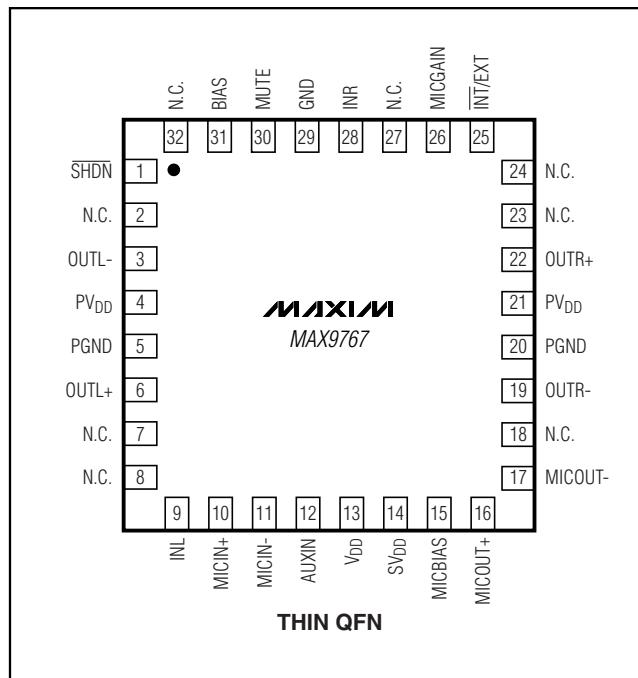

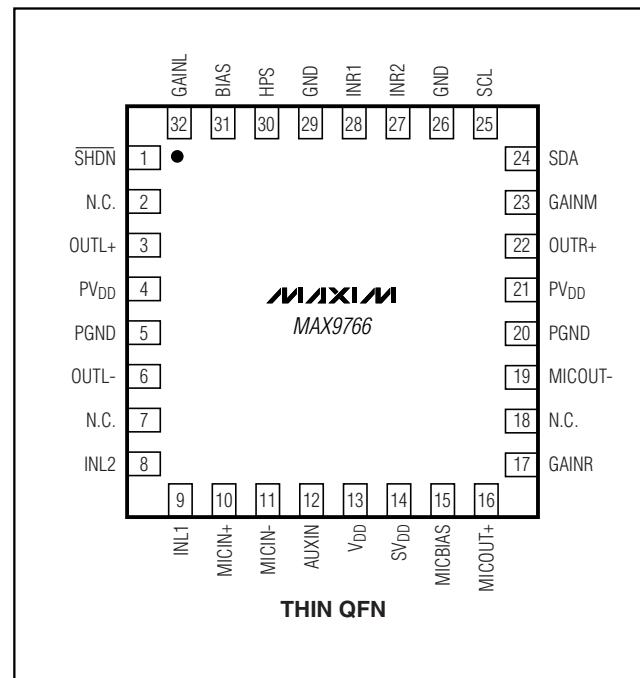

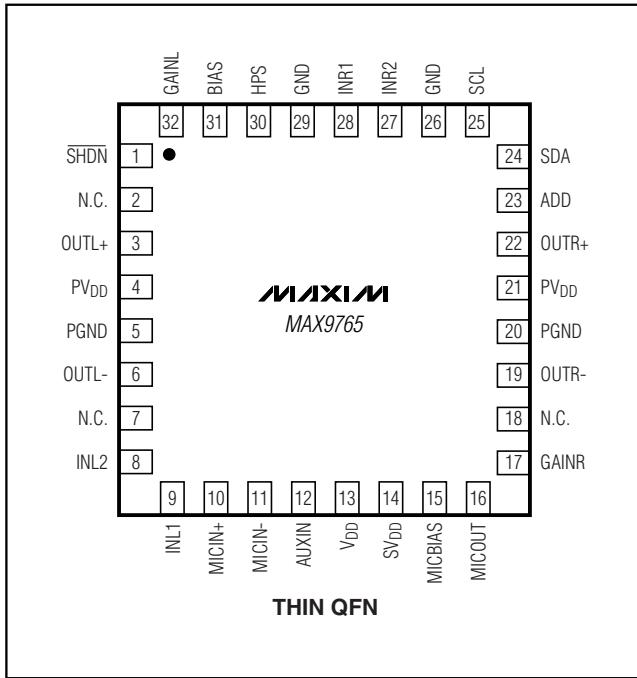

## Pin Description

| PIN      |          |                                   | NAME            | FUNCTION                                                                                                                                                                                                                                            |

|----------|----------|-----------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX9765  | MAX9766  | MAX9767                           |                 |                                                                                                                                                                                                                                                     |

| 1        | 1        | 1                                 | SHDN            | Active-Low Shutdown. Connect SHDN to V <sub>DD</sub> for normal operation.                                                                                                                                                                          |

| 2, 7, 18 | 2, 7, 18 | 2, 7, 8,<br>18, 23,<br>24, 27, 32 | N.C.            | No Connection. Not internally connected.                                                                                                                                                                                                            |

| 3        | 3        | 6                                 | OUTL+           | Left-Channel Bridged Amplifier Positive Output. OUTL+ also serves as the left-channel headphone amplifier output.                                                                                                                                   |

| 4, 21    | 4, 21    | 4, 21                             | PVDD            | Output Amplifier Power Supply. Connect PVDD to V <sub>DD</sub> .                                                                                                                                                                                    |

| 5, 20    | 5, 20    | 5, 20                             | PGND            | Power Ground. Connect PGND to GND.                                                                                                                                                                                                                  |

| 6        | 6        | 3                                 | OUTL-           | Left-Channel Bridged Amplifier Negative Output                                                                                                                                                                                                      |

| 8        | 8        | —                                 | INL2            | Left-Channel Input 2                                                                                                                                                                                                                                |

| 9        | 9        | —                                 | INL1            | Left-Channel Input 1                                                                                                                                                                                                                                |

| 10       | 10       | 10                                | MICIN+          | Differential Microphone Amplifier Noninverting Input                                                                                                                                                                                                |

| 11       | 11       | 11                                | MICIN-          | Differential Microphone Amplifier Inverting Input                                                                                                                                                                                                   |

| 12       | 12       | 12                                | AUXIN           | Single-Ended Microphone Amplifier Input                                                                                                                                                                                                             |

| 13       | 13       | 13                                | V <sub>DD</sub> | Power Supply                                                                                                                                                                                                                                        |

| 14       | 14       | 14                                | SVDD            | Standby Power Supply. Connect to a standby power supply that is always on, or connect to V <sub>DD</sub> through a Schottky diode and bypass with a 220 $\mu$ F capacitor to GND. Short to V <sub>DD</sub> if clickless operation is not essential. |

| 15       | 15       | 15                                | MICBIAS         | Microphone Bias Output. Bypass MICBIAS with a 1 $\mu$ F capacitor to GND.                                                                                                                                                                           |

| 16       | —        | —                                 | MICOUT          | Microphone Amplifier Output                                                                                                                                                                                                                         |

| 17       | 17       | —                                 | GAINR           | Right-Channel Gain Set                                                                                                                                                                                                                              |

| 19       | —        | 19                                | OUTR-           | Right-Channel Bridged Amplifier Negative Output                                                                                                                                                                                                     |

| 22       | 22       | 22                                | OUTR+           | Right-Channel Bridged Amplifier Positive Output. OUTR+ also serves as the right-channel headphone amplifier output.                                                                                                                                 |

| 23       | —        | —                                 | ADD             | Address Select. A logic high sets the address LSB to 1, a logic low sets the address LSB to 0.                                                                                                                                                      |

| 24       | 24       | —                                 | SDA             | Bidirectional Serial Data I/O                                                                                                                                                                                                                       |

| 25       | 25       | —                                 | SCL             | Serial Clock Line                                                                                                                                                                                                                                   |

| 26, 29   | 26, 29   | 29                                | GND             | Ground                                                                                                                                                                                                                                              |

| 27       | 27       | —                                 | INR2            | Right-Channel Input 2                                                                                                                                                                                                                               |

| 28       | 28       | —                                 | INR1            | Right-Channel Input 1                                                                                                                                                                                                                               |

| 30       | 30       | —                                 | HPS             | Headphone Sense Input                                                                                                                                                                                                                               |

| 31       | 31       | 31                                | BIAS            | DC Bias Bypass. See <i>BIAS Capacitor</i> section for capacitor selection. Connect CBIAS capacitor from BIAS to GND.                                                                                                                                |

| 32       | 32       | —                                 | GAINL           | Left-Channel Gain Set                                                                                                                                                                                                                               |

| —        | 16       | 16                                | MICOUT+         | Microphone Amplifier Positive Output                                                                                                                                                                                                                |

MAX9765/MAX9766/MAX9767

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

## Pin Description (continued)

| PIN     |         |         | NAME    | FUNCTION                                                                                                                                               |

|---------|---------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX9765 | MAX9766 | MAX9767 |         |                                                                                                                                                        |

| —       | 19      | 17      | MICOUT- | Microphone Amplifier Negative Output                                                                                                                   |

| —       | 23      | —       | GAINM   | Mono Mode Gain Set                                                                                                                                     |

| —       | —       | 9       | INL     | Left-Channel Input                                                                                                                                     |

| —       | —       | 25      | INT/EXT | Internal (Differential) or External (Single-Ended) Input Select. Drive INT/EXT low to select internal or high to select external microphone amplifier. |

| —       | —       | 26      | MICGAIN | Microphone Amplifier Gain Set. Tri-State Pin. Connect to VDD for gain = 10dB, float for gain = 20dB, and to GND for gain = 30dB.                       |

| —       | —       | 28      | INR     | Right-Channel Input                                                                                                                                    |

| —       | —       | 30      | MUTE    | Mute Input                                                                                                                                             |

| —       | —       | —       | EP      | Exposed Pad. Connect to ground plane of PC board to optimize heatsinking.                                                                              |

### Detailed Description

The MAX9765/MAX9766/MAX9767 feature 750mW BTL speaker amplifiers, 65mW headphone amplifiers, input multiplexers, headphone sensing, differential and single-ended input microphone amplifiers, and comprehensive click-and-pop suppression. The MAX9765/MAX9766 are controlled through an I<sup>2</sup>C-compatible, 2-wire serial interface. The MAX9767 is controlled through three logic inputs: MUTE, SHDN, INT (see the *Selector Guide*). The MAX9765 family features exceptional PSRR (95dB at 1kHz), allowing these devices to operate from noisy digital supplies without the need for a linear regulator.

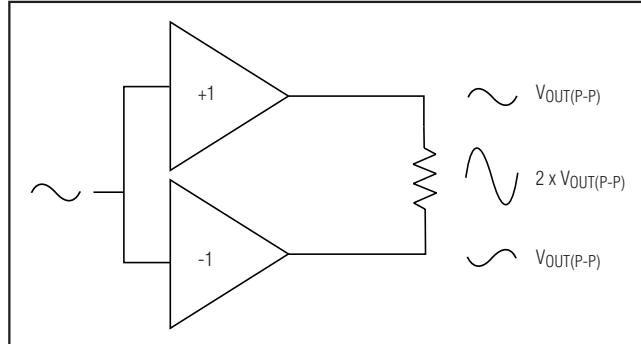

The speaker amplifiers use a BTL configuration. The MAX9765/MAX9766 main amplifiers are composed of an input amplifier and an output amplifier. Resistor R<sub>IN</sub> sets the input amplifier's gain, and resistor R<sub>F</sub> sets the output amplifier's gain. The output of these two amplifiers serves as the input to a slave amplifier configured as an inverting unity-gain follower. This results in two outputs, identical in magnitude, but 180° out of phase. The overall gain of the speaker amplifiers is twice the product of the two amplifier gains (see the *Gain-Setting Resistor* section). A unique feature of this architecture is that there is no phase inversion from input to output. The MAX9767 does not use a two-stage input amplifier and therefore has phase inversion from input to output.

When configured as a headphone (single-ended) amplifier, the slave amplifier is disabled, muting the speaker and the main amplifier drives the headphone. The MAX9765/MAX9766/MAX9767 can deliver 700mW of

continuous average power into a 4Ω load with less than 1% THD+N in speaker mode. The MAX9765/MAX9766 can deliver 70mW of continuous average power into a 16Ω load with less than 1% THD+N in headphone mode. The speaker amplifiers also feature thermal-overload and short-circuit current protection.

All devices feature microphone amplifiers with both differential and single-ended inputs. Differential input is intended for use with internal microphones. Single-ended input is intended for use with external (auxiliary) microphones. The differential input configuration is particularly effective when layout constraints force the microphone amplifier to be physically remote from the ECM microphone and/or the rest of the audio circuitry. The MAX9766/MAX9767 feature a complementary output, creating an ideal interface with CODECs and other devices with differential inputs. All devices also feature an internal microphone bias generator.

### Amplifier Common-Mode Bias

These devices feature an internally generated common-mode bias voltage of 1.5V referenced to GND. BIAS provides both click-and-pop suppression and sets the DC bias level for the audio signal. BIAS is internally connected to the noninverting input of each speaker amplifier (see the *Typical Application Circuit*). Choose the value of the bypass capacitor as described in the *BIAS Capacitor* section.

### Input Multiplexer

The MAX9765/MAX9766 feature a 2:1 input multiplexer on the front end of each amplifier. The multiplexer is controlled by bit 1 in the control register. A logic low

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

MAX9765/MAX9766/MAX9767

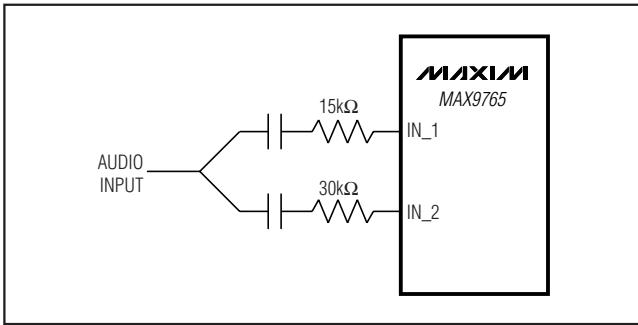

Figure 1. Using the Input Multiplexer for Gain Setting

selects input IN\_1 and a logic high selects input IN\_2. Both right- and left-channel multiplexers are controlled by the same input.

The input multiplexer can also be used to further expand the number of gain options available from the MAX9765/MAX9766. Connect the audio source to the device through two different input resistors for multiple gain configurations (Figure 1). Additionally, the input multiplexer allows a speaker equalization network to be switched into the speaker signal path. This is typically useful in optimizing acoustic response from speakers with small physical dimensions.

## Mono Mode

The mono MAX9766 incorporates a mixer/attenuator (see the *Functional Diagram*). In speaker (mono) mode, the mixer/attenuator combines the two stereo inputs (INL\_ and INR\_) and attenuates the resultant signal by a factor of 2. This allows for full reproduction of a stereo signal through a single speaker while maintaining optimum headroom. The resistor connected between GAINM and OUTL+ sets the device gain in speaker mode. This allows the speaker amplifier to have a different gain and feedback network from the headphone amplifier.

## Headphone Sense Disable Input

The headphone sensing function can be disabled by the HPS\_D bit (MAX9765/MAX9766). HPS\_D bit determines whether the device is in automatic-detection mode, or fixed-mode operation.

## Headphone Sense Input (HPS)

When the MAX9765/MAX9766 are in automatic headphone-detection mode, the state of the headphone sense input (HPS) determines the operating mode of the device. A voltage on HPS less than  $0.7 \times VDD$  sets the device to speaker mode. A voltage greater than  $0.9 \times VDD$  disables the inverting bridge amplifier (OUT\_-),

which mutes the speaker amplifier and sets the device into headphone mode.

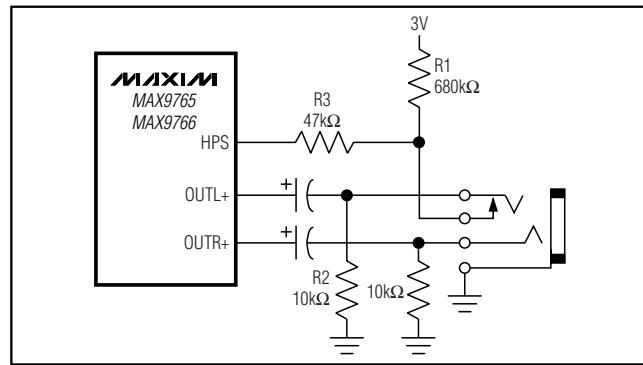

Connect HPS to the control pin of a 3-wire headphone jack as shown in Figure 2. With no headphone present, the resistive voltage-divider created by R1 and R2 sets the voltage on HPS to 44mV, setting the device to speaker mode. When a headphone plug is inserted into the jack, the control pin is disconnected from the tip contact, and HPS is pulled to VDD through R1, setting the device into headphone mode. Place a resistor in series with the control pin and HPS (R3) to prevent any audio signal from coupling into HPS when the device is in speaker mode.

## Shutdown

The MAX9765/MAX9766/MAX9767 feature a 5µA, low-power shutdown mode that reduces quiescent current consumption and extends battery life. The drive and microphone amplifiers and the bias circuitry are disabled, the amplifier outputs (OUT\_-/MIC\_) go high impedance, and BIAS and MICBIAS are driven to GND. The digital section of the MAX9765/MAX9766 remains active when the device is shut down through the interface. A logic high on bit 0 of the SHDN register places the MAX9765/MAX9766 in shutdown. A logic low enables the device. A logic low on the SHDN input places the devices into shutdown mode, disables the interface, and resets the I<sup>2</sup>C registers to a default state. A logic high on SHDN enables the device. A logic high on SHDN enables the devices.

## MUTE

All devices feature a mute mode. When the device is muted, the input is disconnected from the amplifiers. MUTE only affects the power amplifiers, and does not shut down the device. The MAX9765/MAX9766 MUTE mode is selected by writing to the MUTE register (see Command Byte Definitions). The left and right channels can be independently muted. The MAX9767 features an active-high MUTE input that mutes both channels.

## INT/EXT

The MAX9767 microphone amplifier input configuration is controlled by the INT/EXT input. A logic low In INT/EXT selects internal (differential) microphone mode. A logic high selects external (single-ended) mode.

## Click-and-Pop Suppression

The MAX9765/MAX9766/MAX9767 feature Maxim's patented comprehensive click-and-pop suppression. During startup and shutdown, the common-mode bias voltage of the amplifiers is slowly ramped to and from the DC bias point using an S-shaped waveform. In

## 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

headphone mode, this waveform shapes the frequency spectrum, minimizing the amount of audible components present at the headphone. In speaker mode, the BTL amplifiers start up in the same fashion as in headphone mode. When entering shutdown, both amplifier outputs ramp to GND quickly and simultaneously. The devices can also be connected to a standby power source that ensures that the device undergoes its full shutdown cycle even after power has been removed. The value of the capacitor on the BIAS pin affects the click-and-pop energy. For optimum click/pop performance, use a 1 $\mu$ F capacitor.

### Standby Power Supply (SVDD)

The MAX9765/MAX9766/MAX9767 feature a patented system that provides clickless power-down when power is removed from the device. SVDD is an **optional** secondary supply that powers the device through its shutdown cycle when VDD is removed. During this cycle, the amplifier output DC level slowly ramps to GND, ensuring clickless power-down. If clickless power-down is required, connect SVDD to either a secondary power supply that is always on, or connect a reservoir capacitor from SVDD to GND. SVDD does not need to be connected to either a secondary power supply or reservoir capacitor for normal device operation. If click-and-pop suppression during power-down is not required, connect SVDD to VDD directly.

The clickless power-down cycle only occurs when the device is in headphone mode. The speaker mode is inherently clickless, the differential architecture cancels the DC shift across the speaker. The MAX9765/MAX9766/MAX9767 BTL outputs are pulled to GND quickly and simultaneously, resulting in no audible components. If the MAX9765/MAX9766/MAX9767 are only used as speaker amplifiers, then reservoir capacitors or secondary supplies are not necessary.

When using a reservoir capacitor, a 220 $\mu$ F capacitor provides optimum charge storage for the shutdown cycle for all conditions. If a smaller reservoir capacitor is desired, decrease the size of CBIAS. A smaller CBIAS causes the output DC level to decay at a faster rate, increasing the audible content at the speaker, but reducing the duration of the shutdown cycle.

### Digital Interface

The MAX9765/MAX9766 feature an I<sup>2</sup>C/SMBus-compatible 2-wire serial interface consisting of a serial data line (SDA) and a serial clock line (SCL). SDA and SCL facilitate bidirectional communication between the MAX9765/MAX9766 and the master at clock rates up to 400kHz. Figure 3 shows the 2-wire interface timing diagram. The MAX9765/MAX9766 are transmit/receive

Figure 2. HPS Configuration Circuit

slave-only devices, relying upon a master to generate a clock signal. The master (typically a microcontroller) initiates data transfer on the bus and generates SCL to permit that transfer.

A master device communicates to the MAX9765/MAX9766 by transmitting the proper address followed by a command and/or data words. Each transmit sequence is framed by a START (S) or REPEATED START (Sr) condition and a STOP (P) condition. Each word transmitted over the bus is 8 bits long and is always followed by an acknowledge clock pulse.

The MAX9765/MAX9766 SDA and SCL amplifiers are open-drain outputs requiring a pullup resistor to generate a logic-high voltage. Series resistors in line with SDA and SCL are optional. These series resistors protect the input stages of the devices from high-voltage spikes on the bus lines, and minimize crosstalk and undershoot of the bus signals.

### Bit Transfer

One data bit is transferred during each SCL clock cycle. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high are control signals (see the *START and STOP Conditions* section). SDA and SCL idle high when the I<sup>2</sup>C bus is not busy.

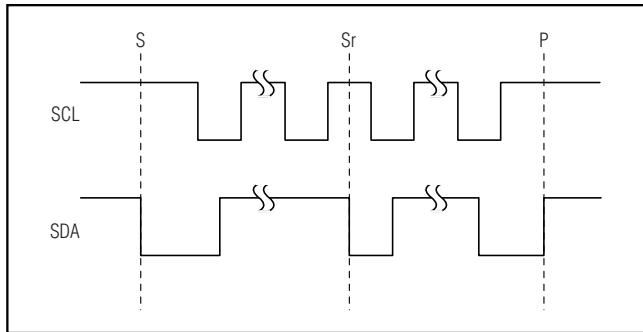

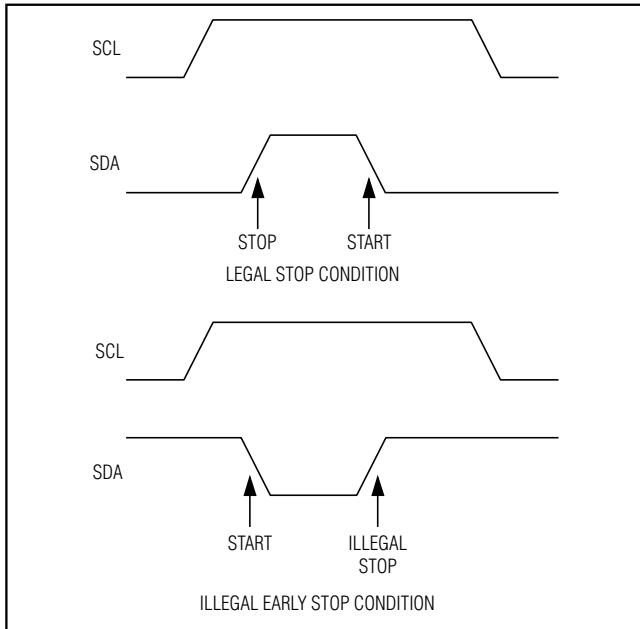

### START and STOP Conditions

When the serial interface is inactive, SDA and SCL idle high. A master device initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 4). A START condition from the master signals the beginning of a transmission to the MAX9765/MAX9766. The master terminates transmission by issuing the STOP condition; this frees the bus. If a REPEATED START condition is generated instead of a STOP

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

MAX9765/MAX9766/MAX9767

Figure 3. 2-Wire Serial Interface Timing Diagram

condition, the bus remains active. When a STOP condition or incorrect address is detected, the MAX9765/MAX9766 internally disconnects SCL from the serial interface until the next START condition, minimizing digital noise and feedthrough.

### Early STOP Conditions

The MAX9765/MAX9766 recognize a STOP condition at any point during the transmission except if a STOP condition occurs in the same high pulse as a START condition (Figure 5). This condition is not a legal I<sup>2</sup>C format; at least one clock pulse must separate any START and STOP conditions.

### REPEATED START Conditions

A REPEATED START (Sr) condition may indicate a change of data direction on the bus. Such a change occurs when a command word is required to initiate a read operation. Sr may also be used when the bus master is writing to several I<sup>2</sup>C devices and does not want to relinquish control of the bus. The MAX9765/MAX9766 serial interface supports continuous write operations with or without an Sr condition separating them. Continuous read operations require Sr conditions because of the change in direction of data flow.

### Acknowledge Bit (ACK)

The acknowledge bit (ACK) is the ninth bit attached to any 8-bit data word. The receiving device always generates ACK. The MAX9765/MAX9766 generate an ACK when receiving an address or data by pulling SDA low during the ninth clock period. When transmitting data, the MAX9765/MAX9766 wait for the receiving device to generate an ACK. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a sys-

Figure 4. START/STOP Conditions

tem fault has occurred. In the event of an unsuccessful data transfer, the bus master should reattempt communication at a later time.

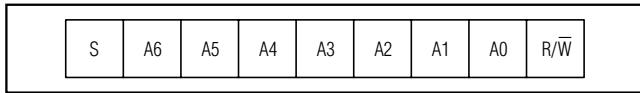

### Slave Address

The bus master initiates communication with a slave device by issuing a START condition followed by a 7-bit slave address (Figure 6). When idle, the MAX9765/MAX9766 wait for a START condition followed by its slave address. The serial interface compares each address value bit-by-bit, allowing the interface to power down immediately if an incorrect address is detected. The LSB of the address word is the Read/Write (R/W) bit. R/W indicates whether the master is writing to or reading from the MAX9765/MAX9766 (R/W = 0 selects the write condition, R/W = 1 selects the read condition). After receiving the proper address, the MAX9765/MAX9766 issue an ACK by pulling SDA low for one clock cycle.

The MAX9765 has a factory/user-programmed address (Table 2). The MAX9766 has a factory-programmed address: 1001011.

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

Figure 5. Early STOP Condition

Figure 6. Slave Address Byte Definition

### Write Data Format

There are three registers that configure the MAX9765/MAX9766: the MUTE register, SHDN register, and control register. In write data mode ( $R/\bar{W} = 0$ ), the register address and data byte follow the device address (Figure 7).

### MUTE Register

The MUTE register (01hex) is a read/write register that sets the MUTE status of the device. Bit 3 (MUTEL) of the MUTE register controls the left channel, bit 4 (MUTER) controls the right channel. A logic high mutes the respective channel, a logic low brings the channel out of mute.

### SHDN Register

The SHDN register (02hex) is a read/write register that controls the power-up state of the device. A logic high in bit 0 of the SHDN register shuts down the device; a logic low turns on the device. A logic high is required in bits 2 to 7 to reset all registers to their default register settings.

Table 1. HPS Setting (MAX9765/MAX9766)

| HPS_D BIT | HPS | SPKR/HP BIT | MODE |

|-----------|-----|-------------|------|

| 0         | 0   | X           | BTL  |

| 0         | 1   | X           | SE   |

| 1         | X   | 0           | BTL  |

| 1         | X   | 1           | SE   |

Table 2. I<sup>2</sup>C Slave Addresses

| ADD CONNECTION  | I <sup>2</sup> C ADDRESS |

|-----------------|--------------------------|

| GND             | 100 1000                 |

| V <sub>DD</sub> | 100 1001                 |

| SDA             | 100 1010                 |

| SCL             | 100 1011                 |

Table 3. MUTE Register Format

| REGISTER ADDRESS |       | 0000 0001  |                      |

|------------------|-------|------------|----------------------|

| BIT              | NAME  | VALUE      | DESCRIPTION          |

| 7                | X     | Don't Care | —                    |

| 6                | X     | Don't Care | —                    |

| 5                | X     | Don't Care | —                    |

| 4                | MUTER | 0*         | Unmute right channel |

|                  |       | 1          | Mute right channel   |

| 3                | MUTEL | 0*         | Unmute left channel  |

|                  |       | 1          | Mute left channel    |

| 2                | X     | Don't Care | —                    |

| 1                | X     | Don't Care | —                    |

| 0                | X     | Don't Care | —                    |

\*Default state.

### Control Register

The control register (03hex) is a read/write register that determines the device configuration. Bit 1 (IN1/IN2) controls the input multiplexer, a logic high selects input 1, a logic low selects input 2. Bit 2 (HPS\_EN) controls the headphone sensing. A logic low configures the device in automatic headphone detection mode. A logic high disables the HPS input. Bit 3 (INT/EXT) controls the microphone amplifier inputs. A logic low selects differential (internal) input mode. A logic high selects single-ended (external) input mode. Bit 4 (SPKR/HP) selects the amplifier operating mode when

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

MAX9765/MAX9766/MAX9767

Table 4. SHDN Register Format

| REGISTER ADDRESS |       | 0000 0010  |                  |

|------------------|-------|------------|------------------|

| BIT              | NAME  | VALUE      | DESCRIPTION      |

| 7                | RESET | 0*         | —                |

|                  |       | 1          | Reset device     |

| 6                | RESET | 0*         | —                |

|                  |       | 1          | Reset device     |

| 5                | RESET | 0*         | —                |

|                  |       | 1          | Reset device     |

| 4                | RESET | 0*         | —                |

|                  |       | 1          | Reset device     |

| 3                | RESET | 0*         | —                |

|                  |       | 1          | Reset device     |

| 2                | RESET | 0*         | —                |

|                  |       | 1          | Reset device     |

| 1                | X     | Don't Care | —                |

| 0                | SHDN  | 0*         | Normal operation |

|                  |       | 1          | Shutdown         |

\*Default state.

Table 5. Control Register Format

| REGISTER ADDRESS |          | 0000 0011  |                                                                                                |

|------------------|----------|------------|------------------------------------------------------------------------------------------------|

| BIT              | NAME     | VALUE      | DESCRIPTION                                                                                    |

| 7                | MG2      | MG0        | Microphone amplifier gain set; 3-bit code sets the gain of the microphone amplifiers (Table 6) |

| 6                | MG1      |            |                                                                                                |

| 5                |          |            |                                                                                                |

| 4                | SPKR/HP  | 0*         | Speaker mode selected                                                                          |

|                  |          | 1          | Headphone mode selected                                                                        |

| 3                | INT/EXT  | 0*         | Differential input selected                                                                    |

|                  |          | 1          | Single-ended input selected                                                                    |

| 2                | HPS_D    | 0*         | Automatic headphone detection enabled                                                          |

|                  |          | 1          | Automatic headphone detection disabled (HPS ignored)                                           |

| 1                | INT1/IN2 | 0*         | Input 1 selected                                                                               |

|                  |          | 1          | Input 2 selected                                                                               |

| 0                | X        | Don't Care | —                                                                                              |

|   |                                                 |    |     |                                                      |     |                                                 |         |                              |

|---|-------------------------------------------------|----|-----|------------------------------------------------------|-----|-------------------------------------------------|---------|------------------------------|

| S | ADDRESS                                         | WR | ACK | COMMAND                                              | ACK | DATA                                            | ACK     | P                            |

|   | 7 BITS                                          |    |     | 8 BITS                                               |     | 8 BITS                                          |         | 1                            |

|   | I <sup>2</sup> C SLAVE ADDRESS. SELECTS DEVICE. |    |     | REGISTER ADDRESS. SELECTS REGISTER TO BE WRITTEN TO. |     | REGISTER DATA.                                  |         |                              |

| S | ADDRESS                                         | WR | ACK | COMMAND                                              | ACK | S                                               | ADDRESS | WR                           |

|   | 7 BITS                                          |    |     | 8 BITS                                               |     |                                                 | 7 BITS  |                              |

|   | I <sup>2</sup> C SLAVE ADDRESS. SELECTS DEVICE. |    |     | REGISTER ADDRESS. SELECTS REGISTER TO BE READ.       |     | I <sup>2</sup> C SLAVE ADDRESS. SELECTS DEVICE. |         | DATA FROM SELECTED REGISTER. |

Figure 7. Write/Read Data Format Example

HPS\_EN = 1. A logic high selects speaker mode, a logic low selects headphone mode. Bits 5 to 7 (MG0-2) control the gain of the microphone amplifiers (Table 5).

## Read Data Format

In read mode (R/W = 1), the MAX9765/MAX9766 write the contents of the selected register to the bus. The

direction of the data flow reverses following the address acknowledge by the MAX9765/MAX9766. The master device reads the contents of all registers, including the read-only status register. Table 7 shows the status register format. Figure 7 shows an example read data sequence.

# 750mW Audio Amplifiers with Headphone Amp, Microphone Preamp, and Input Mux

Table 6. Microphone Gain Setting

| MG2 | MG1 | MG0 | MAX9765<br>DIFF GAIN (dB) | MAX9766<br>DIFF GAIN (dB) | SINGLE-ENDED GAIN<br>(dB) |

|-----|-----|-----|---------------------------|---------------------------|---------------------------|

| 0*  | 0*  | 0*  | 4                         | 10                        | 10                        |

| 0   | 0   | 1   | 9                         | 15                        | 15                        |