December 1996

# **Fast CMOS 16-Bit Registered Transceiver**

#### **Features**

- Advanced 0.6 micron CMOS Technology

- These Devices Are High-speed, Low Power Devices with High Current Drive

- V<sub>CC</sub> = 5V ±10%

- · Hysteresis on All Inputs

- CD74FCT16952T

- High Output Drive: I<sub>OH</sub> = -32mA; I<sub>OL</sub> = 64mA

- Power Off Disable Outputs Permit "Live Insertion"

- Typical  $V_{OLP}$  (Output Ground Bounce) < 1.0V at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$

- CD74FCT162952T

- Balanced Output Drivers: ±24mA

- Reduced System Switching Noise

- Typical V<sub>OLP</sub> (Output Ground Bounce) < 0.6V at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C

### Description

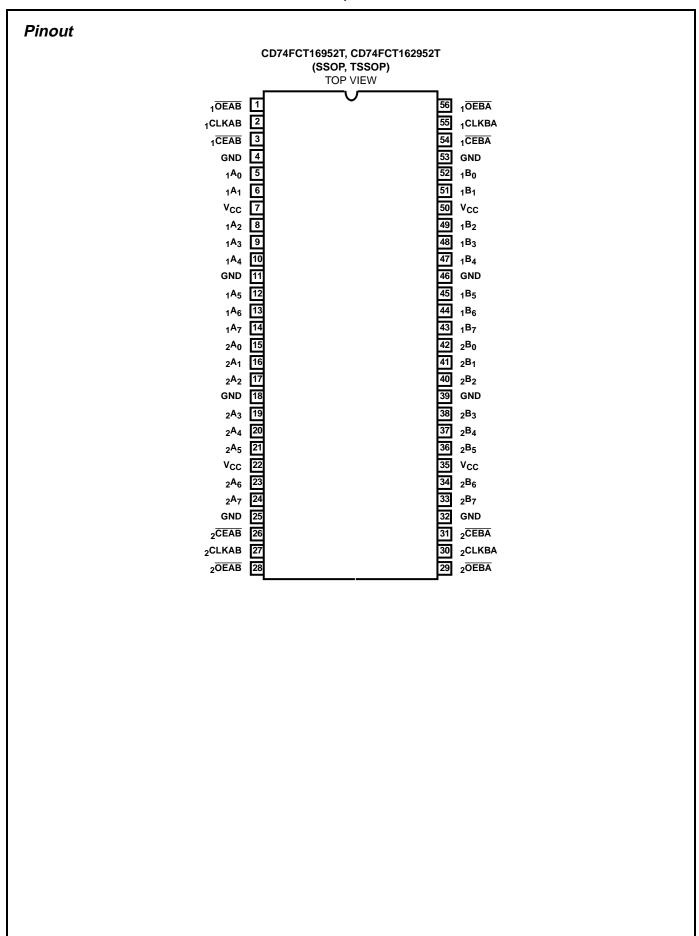

These devices are 16-bit registered transceivers organized with two sets of eight D-type latches with separate input and output controls for each set. For data flow from A-to-B, for example, the A-to-B Enable ( $\chi \overline{CEAB}$ ) input must be LOW in order to enter data from  $\chi A_X$ . The data present on the A port will be clocked on the B register when  $\chi CLKAB$  toggles from LOW-to-HIGH. The  $\chi \overline{OEAB}$  control performs the output enable function on the B port. Control of data from B-to-A is similar, but uses the  $\chi \overline{CEBA}$ ,  $\chi CLKBA$ , and  $\chi \overline{OEBA}$  inputs. By connecting the control pins of the two independent transceivers together, a full 16-bit operation can be achieved. The output buffers are designed with a Power-Off disable allowing "live insertion" of boards when used as backplane drivers.

The CD74FCT16952T output buffers are designed with a Power-Off disable allowing "live insertion" of boards when used as backplane drivers.

The CD74FCT162952T has  $\pm 24$ mA balanced output drivers. It is designed with current limiting resistors at its outputs to control the output edge rate resulting in lower ground bounce and undershoot. This eliminates the need for external terminating resistors for most interface applications.

# Ordering Information

|                   |                        | г           | T           |

|-------------------|------------------------|-------------|-------------|

| PART NUMBER       | TEMP.<br>RANGE<br>(°C) | PACKAGE     | PKG.<br>NO. |

| CD74FCT16952ATMT  | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT16952ATSM  | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT16952TMT   | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT16952TSM   | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT16952CTMT  | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT16952CTSM  | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT16952DTMT  | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT16952DTSM  | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT16952ETMT  | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT16952ETSM  | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT162952ATMT | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT162952ATSM | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT162952TMT  | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT162952TSM  | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT162952CTMT | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT162952CTSM | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT162952DTMT | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT162952DTSM | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT162952ETMT | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT162952ETSM | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

NOTE: When ordering, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

# Functional Block Diagram 20EBA 1CEBA 1CEBA 1CEAB 1CEA

# TRUTH TABLE (NOTES 1, 2)

**TO 7 OTHER CHANNELS**

|                  | OUTPUTS            |     |   |            |

|------------------|--------------------|-----|---|------------|

| <sub>X</sub> ŒAB | <sub>X</sub> CLKAB | χΒχ |   |            |

| Н                | X                  | L   | X | B (Note 3) |

| Х                | L                  | L   | X | B (Note 3) |

| L                | 1                  | L   | L | L          |

| L                | 1                  | L   | Н | Н          |

| Х                | Х                  | Н   | X | High Z     |

#### NOTES:

- 1. H = High Voltage Level

- L = Low Voltage Level

- X = Don't Care or Irrelevant

TO 7 OTHER CHANNELS

- ↑ = LOW-to-HIGH Transition

- Z = High Impedance

- 2. A-to-B data flow shown. B-to-A flow control is the same, except using  $\chi \overline{\text{CEBA}}$ ,  $\chi \text{CLKBA}$ , and  $\chi \overline{\text{OEBA}}$ .

- 3. Level of B before the indicated steady-state input conditions were established.

# Pin Descriptions

| PIN NAME            | DESCRIPTION                                                  |

|---------------------|--------------------------------------------------------------|

| XOEAB               | A-to-B Output Enable Input<br>(Active LOW)                   |

| χ <mark>ΌΕΒΑ</mark> | B-to-A Output Enable Input<br>(Active LOW)                   |

| <sub>X</sub> CEAB   | A-to-B Clock Enable Input (Active LOW)                       |

| <sub>X</sub> CEBA   | B-to-A Clock Enable Input (Active LOW)                       |

| XCLKAB              | A-to-B Clock Input                                           |

| XCLKBA              | B-to-A Clock Input                                           |

| хАх                 | A-to-B Data Inputs or B-to-A<br>Three-State Outputs (Note 4) |

| χΒχ                 | B-to-A Data Inputs or A-to-B<br>Three-State Outputs (Note 4) |

| GND                 | Ground                                                       |

| V <sub>CC</sub>     | Power                                                        |

#### **Absolute Maximum Ratings Thermal Information** $\theta_{JA}$ (°C/W) DC Input Voltage .....-0.5V to 7.0V Thermal Resistance (Typical, Note 4) 85 **Operating Conditions** Maximum Storage Temperature Range $\,\ldots\ldots\,$ .-65°C to 150°C Supply Voltage to Ground Potential Maximum Lead Temperature (Soldering 10s).....300°C Inputs and V<sub>CC</sub> Only.....-0.5V to 7.0V (Lead Tips Only) Supply Voltage to Ground Potential Outputs and D/O Only.....-0.5V to 7.0V

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

4.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

# **Electrical Specifications**

| PARAMETERS                              | SYMBOL           | (NOTE 5<br>TEST CONDIT                                 | MIN                               | (NOTE 6)<br>TYP | MAX  | UNITS |    |

|-----------------------------------------|------------------|--------------------------------------------------------|-----------------------------------|-----------------|------|-------|----|

| DC ELECTRICAL SPE                       | CIFICATION       | IS Over the Operating Range, T                         | $T_A = -40^{\circ}$ C to 85°C, V  | CC = 5.0V ±1    | 0%   |       |    |

| Input HIGH Voltage                      | $V_{IH}$         | Guaranteed Logic HIGH Level                            |                                   | 2.0             | -    | -     | V  |

| Input LOW Voltage                       | V <sub>IL</sub>  | Guaranteed Logic LOW Level                             |                                   | -               | -    | 0.8   | V  |

| Input HIGH Current                      | I <sub>IH</sub>  | Standard Input, V <sub>CC</sub> = Max                  | $V_{IN} = V_{CC}$                 | -               | -    | 1     | μА |

| Input HIGH Current                      | I <sub>IH</sub>  | Standard I/O, V <sub>CC</sub> = Max                    | V <sub>IN</sub> = V <sub>CC</sub> | -               | -    | 1     | μА |

| Input HIGH Current                      | lіН              | Bus Hold Input (Note 8)<br>V <sub>CC</sub> = Max       | $V_{IN} = V_{CC}$                 | -               | -    | ±100  | μА |

| Input HIGH Current                      | lіН              | Bus Hold I/O (Note 8) $V_{IN} = V_{CC}$ $V_{CC} = Max$ |                                   | -               | -    | ±100  | μА |

| Input LOW Current                       | I <sub>IL</sub>  | Standard Input, $V_{CC} = Min$ $V_{IN} = GND$          |                                   | -               | -    | -1    | μА |

| Input LOW Current                       | I <sub>IL</sub>  | Standard I/O, $V_{CC} = Min$ $V_{IN} = GND$            |                                   | -               | -    | -1    | μА |

| Input LOW Current                       | I <sub>IL</sub>  | Bus Hold Input (Note 8) $V_{IN} = GND$ $V_{CC} = Min$  |                                   | -               | -    | ±100  | μА |

| Input LOW Current                       | I <sub>IL</sub>  | Bus Hold I/O (Note 8)<br>V <sub>CC</sub> = Min         | V <sub>IN</sub> = GND             | -               | -    | ±100  | μА |

| Bus Hold                                | Івнн             | Bus Hold Input (Note 8)                                | V <sub>IN</sub> = 2.0V            | -50             | -    | i     | μА |

| Sustain Current                         | I <sub>BHL</sub> | V <sub>CC</sub> = Min                                  | V <sub>IN</sub> = 0.8V            | 50              | -    | -     | μА |

| High Impedance Out-                     | I <sub>OZH</sub> | V <sub>CC</sub> = Max                                  | V <sub>OUT</sub> = 2.7V           | -               | -    | 1     | μА |

| put Current (Three-<br>State) (Note 10) | I <sub>OZL</sub> | V <sub>CC</sub> = Max                                  | V <sub>OUT</sub> = 0.5V           | -               | -    | -1    | μА |

| Clamp Diode Voltage                     | V <sub>IK</sub>  | V <sub>CC</sub> = Min, I <sub>IN</sub> = -18mA         | -                                 | -0.7            | -1.2 | V     |    |

| Short Circuit Current                   | los              | V <sub>CC</sub> = Max (Note 7), V <sub>OUT</sub> = 0   | -80                               | -140            | -200 | mA    |    |

| Output Drive Current                    | Io               | V <sub>CC</sub> = Max (Note 7), V <sub>OUT</sub> = 2   | -50                               | -               | -180 | mA    |    |

| Input Hysteresis                        | V <sub>H</sub>   |                                                        | -                                 | 100             | -    | mV    |    |

# **Electrical Specifications (Continued)**

| PARAMETERS                                       | SYMBOL                     | (NOTE 5)<br>TEST CONDITI                                                                                                                                      | MIN                                                        | (NOTE 6)<br>TYP | MAX  | UNITS             |            |

|--------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|------|-------------------|------------|

| CD74FCT16952T OUT                                | PUT DRIVE                  | SPECIFICATIONS Over the Ope                                                                                                                                   | erating Range                                              | •               |      |                   |            |

| Output HIGH Voltage                              | V <sub>OH</sub>            | $V_{CC} = Min, V_{IN} = V_{IH} \text{ or } V_{IL}$                                                                                                            | I <sub>OH</sub> = -3.0mA                                   | 2.5             | 3.5  | -                 | V          |

|                                                  |                            |                                                                                                                                                               | I <sub>OH</sub> = -15.0mA                                  | 2.4             | 3.5  | -                 | V          |

|                                                  |                            |                                                                                                                                                               | I <sub>OH</sub> = -32.0mA                                  | 2.0             | 3.0  | -                 | V          |

| Output LOW Voltage                               | V <sub>OL</sub>            | $V_{CC} = Min, V_{IN} = V_{IH} \text{ or } V_{IL}$                                                                                                            | I <sub>OL</sub> = 64mA                                     | -               | 0.2  | 0.55              | V          |

| Power Down Disable                               | l <sub>OFF</sub>           | $V_{CC} = 0V$ , $V_{IN}$ or $V_{OUT} \le 4.5V$                                                                                                                |                                                            | =               | -    | ±100              | μΑ         |

| CD74FCT162952T OU                                | TPUT DRIVI                 | E SPECIFICATIONS Over the Op                                                                                                                                  | perating Range                                             |                 |      |                   |            |

| Output HIGH Voltage                              | V <sub>OH</sub>            | $V_{CC} = Min, V_{IN} = V_{IH} \text{ or } V_{IL}$                                                                                                            | I <sub>OH</sub> = -24.0mA                                  | 2.4             | 3.3  | -                 | V          |

| Output LOW Voltage                               | V <sub>OL</sub>            | $V_{CC} = Min, V_{IN} = V_{IH} \text{ or } V_{IL}$                                                                                                            | I <sub>OL</sub> = 24mA                                     | =               | 0.3  | 0.55              | V          |

| Output LOW Current                               | l <sub>ODL</sub>           | $V_{CC} = 5V$ , $V_{IN} = V_{IH}$ or $V_{IL}$ , $V_{O}$                                                                                                       | UT = 1.5V (Note 7)                                         | 60              | 115  | 150               | mA         |

| Output HIGH Current                              | I <sub>ODH</sub>           | $V_{CC} = 5V$ , $V_{IN} = V_{IH}$ or $V_{IL}$ , $V_{O}$                                                                                                       | <sub>UT</sub> = 1.5V (Note 7)                              | -60             | -115 | -150              | mA         |

| CAPACITANCE T <sub>A</sub> = 2                   | 25 <sup>0</sup> C, f = 1Ml |                                                                                                                                                               |                                                            |                 |      |                   |            |

| Input Capacitance<br>(Note 10)                   | C <sub>IN</sub>            | V <sub>IN</sub> = 0V                                                                                                                                          |                                                            | -               | 4.5  | 6                 | pF         |

| Output Capacitance (Note 10)                     | C <sub>OUT</sub>           | V <sub>OUT</sub> = 0V                                                                                                                                         |                                                            | -               | 5.5  | 8                 | pF         |

| POWER SUPPLY SPE                                 | CIFICATION                 | IS                                                                                                                                                            |                                                            |                 | •    |                   |            |

| Quiescent Power<br>Supply Current                | Icc                        | V <sub>CC</sub> = Max                                                                                                                                         | V <sub>IN</sub> = GND<br>or V <sub>CC</sub>                | -               | 0.1  | 500               | μА         |

| Supply Current per<br>Input at TTL HIGH          | Δl <sub>CC</sub>           | V <sub>CC</sub> = Max                                                                                                                                         | V <sub>IN</sub> = 3.4V<br>(Note 11)                        | -               | 0.5  | 1.5               | mA         |

| Supply Current per<br>Input per MHz<br>(Note 12) | ICCD                       | $V_{CC}$ = Max, Outputs Open $_{\chi}\overline{\text{OEAB}}$ or $_{\chi}\overline{\text{OEBA}}$ = GND One Input Toggling 50% Duty Cycle                       | V <sub>IN</sub> = V <sub>CC</sub><br>V <sub>IN</sub> = GND | -               | 75   | 120               | μΑ/<br>MHz |

| Total Power Supply<br>Current (Note 14)          | Ic                         | V <sub>CC</sub> = Max, Outputs Open<br>f <sub>CP</sub> = 10MHz (xCLKAB)                                                                                       | $V_{IN} = V_{CC}$<br>$V_{IN} = GND$                        | -               | 0.8  | 1.7<br>(Note 13)  | mA         |

|                                                  |                            | 50% Duty Cycle<br>$\chi \overline{OEAB} = \chi \overline{CEAB} = GND$<br>$\chi \overline{CEBA} = V_{CC}$<br>One Bit Toggling, $f_I = 5MHz$                    | V <sub>IN</sub> = 3.4V<br>V <sub>IN</sub> = GND            | -               | 1.3  | 3.2<br>(Note 13)  | mA         |

|                                                  |                            | V <sub>CC</sub> = Max, Outputs Open<br>f <sub>CP</sub> = 10MHz ( <sub>X</sub> CLKAB)                                                                          | $V_{IN} = V_{CC}$<br>$V_{IN} = GND$                        | -               | 3.8  | 6.5<br>(Note 13)  | mA         |

|                                                  |                            | 50% Duty Cycle<br>$\chi\overline{OEAB} = \chi\overline{CEAB} = GND$<br>$\chi\overline{CEBA} = V_{CC}$<br>16 Bits Toggling, $f_{I} = 2.5MHz$<br>50% Duty Cycle | V <sub>IN</sub> = 3.4V<br>V <sub>IN</sub> = GND            | -               | 8.3  | 20.5<br>(Note 13) | mA         |

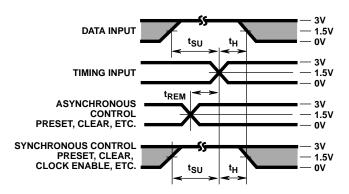

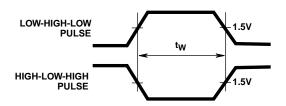

#### **Switching Specifications Over Operating Range**

|                                                                                                                                  |                                       |                                   | АТ                         | -    | СТ                         | -   | DT                         | •   | ET                         | •   |       |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------|----------------------------|------|----------------------------|-----|----------------------------|-----|----------------------------|-----|-------|

| PARAMETER                                                                                                                        | SYMBOL                                | (NOTE 16) TEST CONDITIONS         | (NOTE<br>17)<br><b>MIN</b> | MAX  | (NOTE<br>17)<br><b>MIN</b> | MAX | (NOTE<br>17)<br><b>MIN</b> | MAX | (NOTE<br>17)<br><b>MIN</b> | MAX | UNITS |

| Propagation Delay $_{\chi}$ CLKAB, $_{\chi}$ CLKBA to $_{\chi}$ B $_{\chi}$ , $_{\chi}$ A $_{\chi}$                              | t <sub>PLH,</sub><br>t <sub>PHL</sub> | $C_L = 50pF$<br>$R_L = 500\Omega$ | 2.0                        | 10.0 | 2.0                        | 6.3 | 2.0                        | 4.4 | 1.5                        | 3.7 | ns    |

| Output Enable Time $\chi$ OEBA, $\chi$ OEAB to $\chi$ A $\chi$ , $\chi$ B $\chi$                                                 | <sup>t</sup> PZH,<br><sup>t</sup> PZL |                                   | 1.5                        | 10.5 | 1.5                        | 7.0 | 1.5                        | 4.8 | 1.5                        | 4.4 | ns    |

| Output Disable Time<br>(Note 18)<br>$\chi$ OEBA, $\chi$ OEAB<br>to $\chi$ A $\chi$ , $\chi$ B $\chi$                             | t <sub>PHZ,</sub><br>t <sub>PLZ</sub> |                                   | 1.5                        | 10.0 | 1.5                        | 6.5 | 1.5                        | 4.0 | 1.5                        | 4.0 | ns    |

| Setup Time HIGH or LOW, $\chi A_{X}$ , $\chi B_{X}$ to $\chi CLKAB$ , $\chi CLKBA$                                               | t <sub>SU</sub>                       |                                   | 2.5                        | -    | 2.5                        | -   | 2.0                        | -   | 1.5                        | -   | ns    |

| Hold Time HIGH or LOW, $\chi A_{\chi}$ , $\chi B_{\chi}$ to $\chi CLKAB$ , $\chi CLKBA$                                          | t <sub>H</sub>                        |                                   | 2.0                        | -    | 1.5                        | -   | 1.0                        | -   | 0.0                        | -   | ns    |

| Setup Time HIGH or LOW, $\chi$ CEAB, $\chi$ CEBA to $\chi$ CLK-AB, $\chi$ CLKBA                                                  | t <sub>SU</sub>                       |                                   | 3.0                        | -    | 3.0                        | -   | 2.0                        | -   | 2.0                        | -   | ns    |

| Hold Time HIGH or LOW, $_\chi \overline{\text{CEAB}}, _\chi \overline{\text{CEBA}}$ to $_\chi \text{CLK-AB}, _\chi \text{CLKBA}$ | t <sub>H</sub>                        |                                   | 2.0                        | -    | 2.0                        | -   | 1.5                        | -   | 0.0                        | -   | ns    |

| Pulse Width HIGH<br>(Note 18) or<br>LOW, <sub>X</sub> CLKAB or <sub>X</sub> CLKBA                                                | t <sub>W</sub>                        |                                   | 3.0                        | -    | 3.0                        | -   | 3.0                        | -   | 3.0                        | -   | ns    |

| Output Skew (Note 19)                                                                                                            | t <sub>SK(O)</sub>                    |                                   | -                          | 0.5  | -                          | 0.5 | -                          | 0.5 | -                          | 0.5 | ns    |

#### NOTES:

- 5. For conditions shown as Max or Min, use appropriate value specified under Electrical Characteristics for the applicable device type.

- 6. Typical values are at  $V_{CC} = 5.0V$ ,  $25^{\circ}$ C ambient and maximum loading, except as noted.

- 7. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.

- 8. Pins with Bus Hold are identified in the pin description.

- 9. This specification does not apply to bi-directional functionalities with Bus Hold.

- 10. This parameter is determined by device characterization but is not production tested.

- 11. Per TTL driven input ( $V_{IN} = 3.4V$ ); all other inputs at  $V_{CC}$  or GND.

- 12. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

- 13. Values for these conditions are examples of the  $I_{CC}$  formula. These limits are guaranteed but not tested.

- 14. IC = IQUIESCENT + INPUTS + IDYNAMIC

- $I_{C} = I_{CC} + \Delta I_{CC} D_{H} N_{T} + I_{CCD} (f_{CP}/2 + f_{I} N_{I})$

I<sub>CC</sub> = Quiescent Current

$\Delta I_{CC}$  = Power Supply Current for a TTL High Input (V<sub>IN</sub> = 3.4V)

D<sub>H</sub> = Duty Cycle for TTL Inputs High

$N_T$  = Number of TTL Inputs at  $D_H$

I<sub>CCD</sub> = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

f<sub>CP</sub> = Clock Frequency for Register Devices (Zero for Non-Register Devices)

f<sub>I</sub> = Input Frequency

$N_I = Number of Inputs at f_I$

All currents are in milliamps and all frequencies are in megahertz.

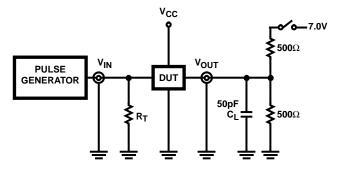

- 15. See test circuit and wave forms.

- 16. Minimum limits are guaranteed but not tested on Propagation Delays.

- 17. This parameter is guaranteed but not production tested.

- 18. Skew between any two outputs, of the same package, switching in the same direction. This parameter is guaranteed by design.

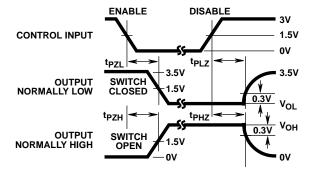

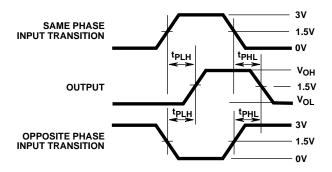

# Test Circuits and Waveforms

#### **SWITCH POSITION**

| TEST                                                                      | SWITCH |

|---------------------------------------------------------------------------|--------|

| t <sub>PLZ</sub> , t <sub>PZL</sub>                                       | Closed |

| t <sub>PHZ</sub> , t <sub>PZH</sub> , t <sub>PLH</sub> , t <sub>PHL</sub> | Open   |

#### **DEFINITIONS:**

$C_L$  = Load capacitance, includes jig and probe capacitance.

$R_T^-$  = Termination resistance, should be equal to  $Z_{OUT}^-$  of the Pulse Generator.

#### NOTE:

1. Pulse Generator for All Pulses: Rate  $\leq$  1.0MHz; Z\_{OUT}  $\leq$  500;  $t_{\rm f},\,t_{\rm f} \leq$  2.5ns.

FIGURE 1. TEST CIRCUIT

FIGURE 2. SETUP, HOLD, AND RELEASE TIMING

FIGURE 3. PULSE WIDTH

FIGURE 4. ENABLE AND DISABLE TIMING

FIGURE 5. PROPAGATION DELAY

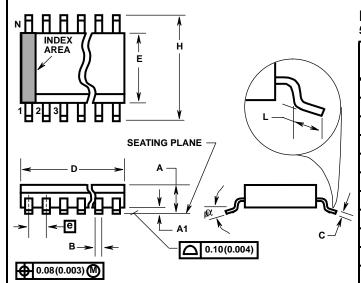

# Thin Shrink Small Outline Plastic Packages (TSSOP)

#### M56.240-P 56 LEAD THIN SHRINK SMALL OUTLINE PLASTIC PACKAGE

|        | INC   | HES            | MILLIM |       |       |

|--------|-------|----------------|--------|-------|-------|

| SYMBOL | MIN   | MAX            | MIN    | MAX   | NOTES |

| Α      | 0.041 | 0.047          | 1.05   | 1.20  | -     |

| A1     | 0.002 | 0.006          | 0.05   | 0.15  | -     |

| В      | 0.007 | 0.010          | 0.178  | 0.254 | -     |

| С      | 0.004 | 0.008          | 0.102  | 0.203 | -     |

| D      | 0.547 | 0.555          | 13.90  | 14.09 | 1     |

| Е      | 0.236 | 0.244          | 6.00   | 6.19  | 2     |

| е      | 0.019 | 7 BSC          | 0.50   | BSC   | -     |

| Н      | 0.307 | 0.330          | 7.80   | 8.38  | -     |

| L      | 0.020 | 0.030          | 0.51   | 0.76  | 3     |

| N      | 56    |                | 56     |       | 4     |

| α      | 0°    | 8 <sup>0</sup> | 0°     | 0° 8° |       |

Rev. 0 6/96

#### NOTES:

- Dimension "D" does not include mold flash, protrusions or gate burrs.

- 2. Dimension "E" does not include interlead flash or protrusions.

- 3. "L" is the length of terminal for soldering to a substrate.

- 4. "N" is the number of terminal positions.

- 5. Terminal numbers are shown for reference only.

- Controlling dimension: INCHES. Converted millimeter dimensions are not necessarily exact.

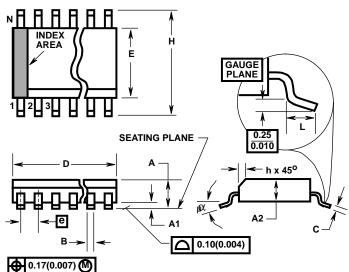

# Shrink Small Outline Plastic Packages (SSOP)

#### NOTES:

- 1. These package dimensions are within allowable dimensions of JECEC MO-118-AB, Issue B.

- 2. Dimension "D" does not include mold flash, protrusions or gate

- 3. Dimension "E" does not include interlead flash or protrusions.

- 4. "L" is the length of terminal for soldering to a substrate.

- 5. "N" is the number of terminal positions.

- 6. Terminal numbers are shown for reference only.

- 7. Controlling dimension: INCHES. Converted millimeter dimensions are not necessarily exact.

# M56.300-P

56 LEAD SHRINK SMALL OUTLINE PLASTIC PACKAGE

|        | INC   | HES            | MILLIM                        |       |       |

|--------|-------|----------------|-------------------------------|-------|-------|

| SYMBOL | MIN   | MAX            | MIN                           | MAX   | NOTES |

| Α      | 0.096 | 0.108          | 2.44                          | 2.74  | -     |

| A1     | 0.008 | 0.016          | 0.20                          | 0.41  | -     |

| A2     | 0.088 | 0.092          | 2.24                          | 2.34  | -     |

| В      | 0.008 | 0.0135         | 0.20                          | 0.34  | -     |

| С      | 0.005 | 0.010          | 0.13                          | 0.25  | -     |

| D      | 0.720 | 0.730          | 18.29                         | 18.54 | 2     |

| Е      | 0.291 | 0.299          | 7.39                          | 7.59  | 3     |

| е      | 0.025 | BSC            | 0.635 BSC                     |       | -     |

| Н      | 0.395 | 0.415          | 10.03                         | 10.54 | -     |

| h      | 0.015 | 0.025          | 0.381                         | 0.635 | -     |

| L      | 0.020 | 0.040          | 0.51                          | 1.01  | 4     |

| N      | 56    |                | 56                            |       | 5     |

| α      | 0°    | 8 <sup>0</sup> | 0 <sub>0</sub> 8 <sub>0</sub> |       | -     |

Rev. 0 5/96

All Harris Semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Harris Semiconductor products are sold by description only. Harris Semiconductor reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Harris is believed to be accurate and reliable. However, no responsibility is assumed by Harris or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Harris or its subsidiaries.

# Sales Office Headquarters

For general information regarding Harris Semiconductor and its products, call 1-800-4-HARRIS

#### **NORTH AMERICA**

Harris Semiconductor P. O. Box 883, Mail Stop 53-210 Melbourne, FL 32902 TEL: 1-800-442-7747

(407) 729-4984 FAX: (407) 729-5321

#### **EUROPE**

Harris Semiconductor Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

Harris Semiconductor PTE Ltd. No. 1 Tannery Road Cencon 1, #09-01 Singapore 1334 TEL: (65) 748-4200 FAX: (65) 748-0400