# **ADC1001**

ADC1001 10-Bit µP Compatible A/D Converter

Literature Number: SNAS536

June 1999

# ADC1001 10-Bit µP Compatible A/D Converter

### **General Description**

The ADC1001 is a CMOS, 10-bit successive approximation A/D converter. The 20-pin ADC1001 is pin compatible with the ADC0801 8-bit A/D family. The 10-bit data word is read in two 8-bit bytes, formatted left justified and high byte first. The six least significant bits of the second byte are set to zero, as is proper for a 16-bit word.

Differential inputs provide low frequency input common mode rejection and allow offsetting the analog range of the converter. In addition, the reference input can be adjusted enabling the conversion of reduced analog ranges with 10-bit resolution.

### **Key Specifications**

| ■ Resolution      | 10 bits |

|-------------------|---------|

| ■ Linearity error | ±1 LSB  |

| ■ Conversion time | 200µS   |

### **Features**

- ADC1001 is pin compatible with ADC0801 series 8-bit A/D converters

- Compatible with NSC800 and 8080 µP derivatives—no interfacing logic needed

- Easily interfaced to 6800 µP derivatives

- Differential analog voltage inputs

- Logic inputs and outputs meet both MOS and TTL voltage level specifications

- Works with 2.5V (LM336) voltage reference

- On-chip clock generator

- 0V to 5V analog input voltage range with single 5V supply

- Operates ratiometrically or with 5 V<sub>DC</sub>, 2.5 V<sub>DC</sub>, or analog span adjusted voltage reference

- 0.3" standard width 20-pin DIP package

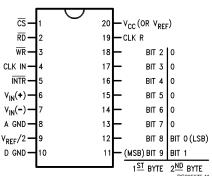

## **Connection Diagram**

### ADC1001 Dual-In-Line Package

Top View

## **Ordering Information**

| Temperature<br>Range | 0°C to +70°C | -40°C to +85°C |

|----------------------|--------------|----------------|

| Order Number         | ADC1001CCJ-1 | ADC1001CCJ     |

| Package Outline      | J20A         | J20A           |

TRI-STATE® is a registered trademark of National Semiconductor Corp

### **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>) (Note 3) 6.5V -0.3V to +18V Logic Control Inputs Voltage at Other Inputs and Outputs -0.3V to  $(V_{CC}+0.3V)$ -65°C to +150°C

Storage Temperature Range

Package Dissipation at T<sub>A</sub>=25°C 875 mW

Lead Temp. (Soldering, 10 seconds) ESD Susceptibility (Note 10)

300°C 800V

### **Operating Conditions** (Notes 1, 2)

Temperature Range  $T_{MIN} \leq T_{A} \leq T_{MAX}$ ADC1001CCJ  $-40^{\circ}C \le T_A \le +85^{\circ}C$ ADC1001CCJ-1  $0^{\circ}C \le T_A \le +70^{\circ}C$ 4.5  $V_{DC}$  to 6.3  $V_{DC}$ Range of  $V_{\rm CC}$

### **Converter Characteristics**

$\textbf{Converter Specifications:} \ \ V_{\text{CC}} = 5 \ \ V_{\text{DC}}, \ \ V_{\text{REF}} / 2 = 2.500 \ \ V_{\text{DC}}, \ \ T_{\text{MIN}} \leq T_{\text{A}} \leq T_{\text{MAX}} \ \ \text{and} \ \ f_{\text{CLK}} = 410 \ \ \text{kHz} \ \ \text{unless otherwise specified.}$

| Parameter Conditions             |                                                     | MIn      | Тур  | Max                   | Units           |

|----------------------------------|-----------------------------------------------------|----------|------|-----------------------|-----------------|

| Linearity Error                  |                                                     |          |      | ±1                    | LSB             |

| Zero Error                       |                                                     |          |      | ±2                    | LSB             |

| Full-Scale Error                 |                                                     |          |      | ±2                    | LSB             |

| Total Ladder Resistance (Note 9) | Input Resistance at Pin 9                           | 2.2      | 4.8  |                       | ΚΩ              |

| Analog Input Voltage Range       | (Note 4) V(+) or V(-)                               | GND-0.05 |      | V <sub>CC</sub> +0.05 | V <sub>DC</sub> |

| DC Common-Mode Error             | Over Analog Input Voltage Range                     |          | ±1/8 |                       | LSB             |

| Power Supply Sensitivity         | V <sub>CC</sub> =5 V <sub>DC</sub> ±5% Over         |          | ±1/8 |                       | LSB             |

|                                  | Allowed V <sub>IN</sub> (+) and V <sub>IN</sub> (-) |          |      |                       |                 |

|                                  | Voltage Range (Note 4)                              |          |      |                       |                 |

### **AC Electrical Characteristics**

Timing Specifications:  $V_{CC}$ =5  $V_{DC}$ and  $T_A$ =25 $^{\circ}$ C unless otherwise specified.

| Symbol Parameter                  |                                 | Conditions                                        | MIn | Тур | Max  | Units              |  |

|-----------------------------------|---------------------------------|---------------------------------------------------|-----|-----|------|--------------------|--|

| T <sub>c</sub>                    | Conversion Time                 | (Note 5)                                          | 80  |     | 90   | 1/f <sub>CLK</sub> |  |

|                                   |                                 | f <sub>CLK</sub> =410 kHz                         | 195 |     | 220  | μs                 |  |

| f <sub>CLK</sub>                  | Clock Frequency                 | (Note 8)                                          | 100 |     | 1260 | kHz                |  |

|                                   | Clock Duty Cycle                |                                                   | 40  |     | 60   | %                  |  |

| CR                                | Conversion Rate In Free-Running | INTR tied to WR with                              |     |     | 4600 | conv/s             |  |

|                                   | Mode                            | CS =0 V <sub>DC</sub> , f <sub>CLK</sub> =410 kHz |     |     |      |                    |  |

| t <sub>W(WR)L</sub>               | Width of WR Input (Start Pulse  | CS =0 V <sub>DC</sub> (Note 6)                    | 150 |     |      | ns                 |  |

|                                   | Width)                          |                                                   |     |     |      |                    |  |

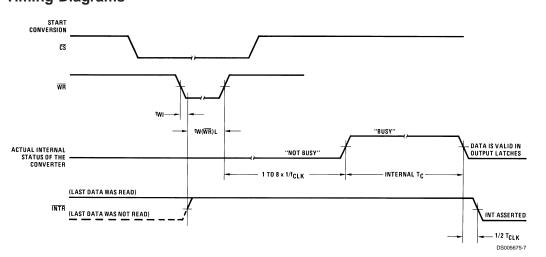

| t <sub>ACC</sub>                  | Access Time (Delay from         | C <sub>L</sub> =100 pF                            |     | 170 | 300  | ns                 |  |

|                                   | Falling Edge of RD to Output    |                                                   |     |     |      |                    |  |

|                                   | Data Valid)                     |                                                   |     |     |      |                    |  |

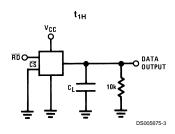

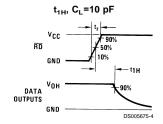

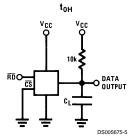

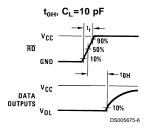

| t <sub>1H</sub> , t <sub>OH</sub> | TRI-STATE® Control (Delay       | C <sub>L</sub> =10 pF, R <sub>L</sub> =10k        |     | 125 | 200  | ns                 |  |

|                                   | from Rising Edge of RD to       | (See TRI-STATE Test                               |     |     |      |                    |  |

|                                   | Hi-Z State)                     | Circuits)                                         |     |     |      |                    |  |

| t <sub>WI</sub> , t <sub>RI</sub> | Delay from Falling Edge         |                                                   |     | 300 | 450  | ns                 |  |

|                                   | of WR or RD to Reset of INTR    |                                                   |     |     |      |                    |  |

| t <sub>1rs</sub>                  | INTR to 1st Read Set-Up Time    |                                                   | 550 | 400 |      | ns                 |  |

| C <sub>IN</sub>                   | Input Capacitance of Logic      |                                                   |     | 5   | 7.5  | pF                 |  |

|                                   | Control Inputs                  |                                                   |     |     |      |                    |  |

| C <sub>OUT</sub>                  | TRI-STATE Output                |                                                   |     | 5   | 7.5  | pF                 |  |

|                                   | Capacitance (Data Buffers)      |                                                   |     |     |      |                    |  |

www.national.com

### **DC Electrical Characteristics**

The following specifications apply for  $V_{CC}$ =5  $V_{DC}$  and  $T_{MIN}$  $\le$   $T_{A}$  $\le$   $T_{MAX}$ , unless otherwise specified.

| Symbol               | Parameter                         | Conditions                                                       | MIn         | Тур             | Max  | Units            |

|----------------------|-----------------------------------|------------------------------------------------------------------|-------------|-----------------|------|------------------|

| CONTROL              | INPUTS [Note: CLK IN is the input | of a Schmitt trigger circuit and is the                          | refore spec | cified separate | ely] |                  |

| V <sub>IN</sub> (1)  | Logical "1" Input Voltage         | V <sub>CC</sub> =5.25 V <sub>DC</sub>                            | 2.0         |                 | 15   | V <sub>DC</sub>  |

|                      | (Except CLK IN)                   |                                                                  |             |                 |      |                  |

| V <sub>IN</sub> (0)  | Logical "0" Input Voltage         | V <sub>CC</sub> =4.75 V <sub>DC</sub>                            |             |                 | 0.8  | V <sub>DC</sub>  |

|                      | (Except CLK IN)                   |                                                                  |             |                 |      |                  |

| I <sub>IN</sub> (1)  | Logical "1" Input Current         | V <sub>IN</sub> =5 V <sub>DC</sub>                               |             | 0.005           | 1    | μA <sub>DC</sub> |

|                      | (All Inputs)                      |                                                                  |             |                 |      |                  |

| I <sub>IN</sub> (0)  | Logical "0" input Current         | V <sub>IN</sub> =0 V <sub>DC</sub>                               | -1          | -0.005          |      | μA <sub>DC</sub> |

|                      | (All Inputs)                      |                                                                  |             |                 |      |                  |

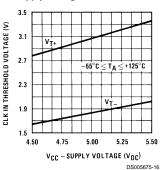

| CLOCK IN             |                                   |                                                                  |             |                 |      |                  |

| V <sub>T</sub> +     | CLK IN Positive Going             |                                                                  | 2.7         | 3.1             | 3.5  | V <sub>DC</sub>  |

|                      | Threshold Voltage                 |                                                                  |             |                 |      |                  |

| V <sub>T</sub> -     | CLK IN Negative Going             |                                                                  | 1.5         | 1.8             | 2.1  | V <sub>DC</sub>  |

|                      | Threshold Voltage                 |                                                                  |             |                 |      |                  |

| V <sub>H</sub>       | CLK IN Hysteresis                 |                                                                  | 0.6         | 1.3             | 2.0  | V <sub>DC</sub>  |

|                      | $(V_T+)-(V_T-)$                   |                                                                  |             |                 |      |                  |

| OUTPUTS              | AND INTR                          |                                                                  |             | •               |      | •                |

| V <sub>OUT</sub> (0) | Logical "0" Output Voltage        | $I_{OUT}$ =1.6 mA, $V_{CC}$ =4.75 $V_{DC}$                       |             |                 | 0.4  | V <sub>DC</sub>  |

| V <sub>OUT</sub> (1) | Logical "1" Output Voltage        | I <sub>O</sub> =-360 μA, V <sub>CC</sub> =4.75 V <sub>DC</sub>   | 2.4         |                 |      | V <sub>DC</sub>  |

|                      |                                   | $I_{O}$ =-10 $\mu$ A, $V_{CC}$ =4.75 $V_{DC}$                    | 4.5         |                 |      | V <sub>DC</sub>  |

| l <sub>out</sub>     | TRI-STATE Disabled Output         | V <sub>OUT</sub> =0.4 V <sub>DC</sub>                            |             | 0.1             | -100 | μA <sub>DC</sub> |

|                      | Leakage (All Data Buffers)        | V <sub>OUT</sub> =5 V <sub>DC</sub>                              |             | 0.1             | 3    | μA <sub>DC</sub> |

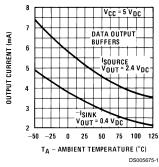

| I <sub>SOURCE</sub>  |                                   | V <sub>OUT</sub> Short to GND, T <sub>A</sub> =25°C              | 4.5         | 6               |      | mA <sub>DC</sub> |

| I <sub>SINK</sub>    |                                   | V <sub>OUT</sub> Short to V <sub>CC</sub> , T <sub>A</sub> =25°C | 9.0         | 16              |      | mA <sub>DC</sub> |

| POWER SU             | JPPLY                             | •                                                                |             |                 | •    |                  |

| I <sub>cc</sub>      | Supply Current (Includes          | f <sub>CLK</sub> =410 kHz,                                       |             |                 |      |                  |

|                      | Ladder Current)                   | V <sub>REF</sub> /2=NC, T <sub>A</sub> =25°C                     |             |                 |      |                  |

|                      |                                   | and $\overline{CS}$ =1                                           |             | 2.5             | 5.0  | mA               |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified. The separate A GND point should always be wired to the D GND.

Note 3: A zener diode exists, internally, from  $V_{CC}$  to GND and has a typical breakdown voltage of 7  $V_{DC}$ .

Note 4: For  $V_{IN}(-) \ge V_{IN}(+)$  the digital output code will be all zeros. Two on-chip diodes are tied to each analog input (see Block Diagram) which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater than the  $V_{CC}$  supply. Be careful, during testing at low  $V_{CC}$  levels (4.5V), as high level analog inputs (5V) can cause this input diode to conduct — especially at elevated temperatures, and cause errors for analog inputs near fullscale. The spec allows 50 mV forward bias of either diode. This means that as long as the analog  $V_{IN}$  does not exceed the supply voltage by more than 50 mV, the output code will be correct. To achieve an absolute 0  $V_{DC}$  to 5  $V_{DC}$  input voltage range will therefore require a minimum supply voltage of 4.950  $V_{DC}$  over temperature variations, initial tolerance and loading.

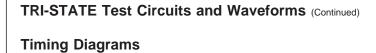

Note 5: With an asynchronous start pulse, up to 8 clock periods may be required before the internal clock phases are proper to start the conversion process. The start request is internally latched, see Figure 3.

Note 6: The  $\overline{\text{CS}}$  input is assumed to bracket the  $\overline{\text{WR}}$  strobe input and therefore timing is dependent on the  $\overline{\text{WR}}$  pulse width. An arbitrarily wide pulse width will hold the converter in a reset mode and the start of conversion is initiated by the low to high transition of the  $\overline{\text{WR}}$  pulse (see Timing Diagrams).

Note 7: All typical values are for  $T_A=25^{\circ}C$ .

$\textbf{Note 8:} \ \, \textbf{Accuracy is guaranteed at } f_{\text{CLK}} \text{=} 410 \text{ kHz. At higher clock frequencies accuracy can degrade.}$

Note 9: The  $V_{REF/2}$  pin is the center point of a two resistor divider (each resistor is  $2.4k\Omega$ ) connected from  $V_{CC}$  to ground. Total ladder input resistance is the sum of these two equal resistors.

Note 10: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

# **Typical Performance Characteristics**

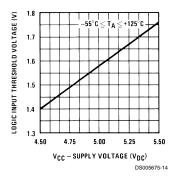

### Logic Input Threshold Voltage vs Supply Voltage

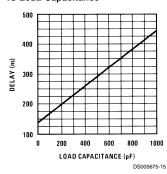

# <u>Del</u>ay From Falling Edge of RD to Output Data Valid vs Load Capacitance

**CLK IN Schmitt Trip Levels** vs Supply Voltage

### **Output Current vs** Temperature

# **TRI-STATE Test Circuits and Waveforms**

t<sub>r</sub>=20 ns

t<sub>r</sub>=20 ns

\*All timing is measured from the 50% voltage points.

### Timing Diagrams (Continued)

## Byte Sequencing For The 20-Pin ADC1001

| Byte  | 8-Bit Data Bus Connection |       |       |       |       |       |       |       |

|-------|---------------------------|-------|-------|-------|-------|-------|-------|-------|

| Order | DB7                       | DB6   | DB5   | DB4   | DB3   | DB2   | DB1   | DB0   |

|       | MSB                       |       |       |       |       |       |       |       |

| 1st   | Bit 9                     | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 |

|       |                           | LSB   |       |       |       |       |       |       |

| 2nd   | Bit 1                     | Bit 0 | 0     | 0     | 0     | 0     | 0     | 0     |

### **Functional Description**

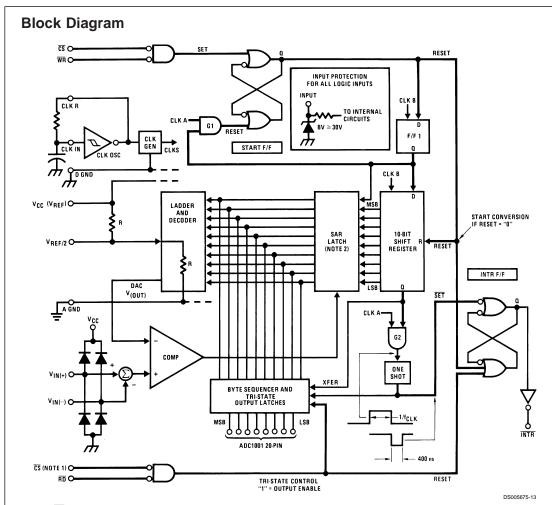

The ADC1001 uses an advanced potentiometric resistive ladder network. The analog inputs, as well as the taps of this ladder network, are switched into a weighted capacitor array. The output of this capacitor array is the input to a sampled data comparator. This comparator allows the successive approximation logic to match the analog difference input voltage  $[V_{IN}(+)-V_{IN}(-)]$  to taps on the R network. The most significant bit is tested first and after 10 comparisons (80 clock cycles) a digital 10-bit binary code (all "1"s=full-scale) is transferred to an output latch and then an interrupt is asserted (INTR makes a high-to-low transition). The device may be operated in the free-running mode by connecting  $\overline{\text{INTR}}$  to the  $\overline{\text{WR}}$  input with  $\overline{\text{CS}}$  =0. To ensure start-up under all possible conditions, an external WR pulse is required during the first power-up cycle. A conversion in process can be interrupted by issuing a second start command.

On the high-to-low transition of the  $\overline{WR}$  input the internal SAR latches and the shift register stages are reset. As long as the  $\overline{CS}$  input and  $\overline{WR}$  input remain low, the A/D will remain in a reset state. Conversion will start from 1 to 8 clock periods after at least one of these inputs makes a low-to-high transition

A functional diagram of the A/D converter is shown in *Figure 3*. All of the inputs and outputs are shown and the major logic control paths are drawn in heavier weight lines.

The conversion is initialized by taking  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  simultaneously low. This sets the start flip-flop (F/F) and the resulting "1" level resets the 8-bit shift register, resets the Interrupt (INTR) F/F and inputs a "1" to the D flop, F/F1, which is at the input end of the 10-bit shift register. Internal clock signals then transfer this "1" to the Q output of F/F1. The AND gate, G1, combines this "1" output with a clock signal to provide a reset signal to the start F/F. If the set signal is no longer present (either WR or CS is a "1") the start F/F is reset and the 10-bit shift register then can have the "1" clocked in, which allows the conversion process to continue. If the set signal were to still be present, this reset pulse would have no effect and the 10-bit shift register would continue to be held in the reset mode. This logic therefore allows for wide  $\overline{\text{CS}}$ and WR signals and the converter will start after at least one of these signals returns high and the internal clocks again provide a reset signal for the start F/F.

After the "1" is clocked through the 10-bit shift register (which completes the SAR search) it causes the new digital word to transfer to the TRI-STATE output latches. When this XFER signal makes a high-to-low transition the one shot fires, setting the INTR F/F. An inverting buffer then supplies the INTR output signal.

Note that this  $\overline{\text{SET}}$  control of the INTR F/F remains low for approximately 400 ns. If the data output is continuously enabled ( $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  both held low), the  $\overline{\text{INTR}}$  output will still signal the end of the conversion (by a high-to-low transition),

because the  $\overline{\text{SET}}$  input can control the Q output of the INTR F/F even though the RESET input is constantly at a "1" level. This  $\overline{\text{INTR}}$  output will therefore stay low for the duration of the  $\overline{\text{SET}}$  signal.

When data is to be read, the combination of both  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  being low will cause the INTR F/F to be reset and the TRI-STATE output latches will be enabled.

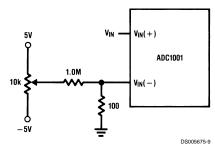

#### Zero and Full-Scale Adjustment

Zero error can be adjusted as shown in Figure 1.  $V_{\rm IN}(+)$  is forced to +2.5 mV (+½ LSB) and the potentiometer is adjusted until the digital output code changes from 00 0000 0000 to 00 0000 0001.

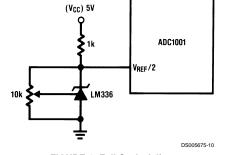

Full-scale is adjusted as shown in Figure 2, with the  $V_{REF}/2$  input. With  $V_{IN}$  (+) forced to the desired full-scale voltage less  $1\frac{1}{2}$  LSBs ( $V_{FS}-1\frac{1}{2}$  LSBs),  $V_{REF}/2$  is adjusted until the digital output code changes from 11 1111 1110 to 11 1111 1111

www.national.com

# Functional Description (Continued)

Note 11:  $V_{IN}(-)$  should be biased so that  $V_{IN}(-) \ge -0.05V$  when potentiometer wiper is set at most negative voltage position.

FIGURE 2. Full-Scale Adjust

### FIGURE 1. Zero Adjust Circuit

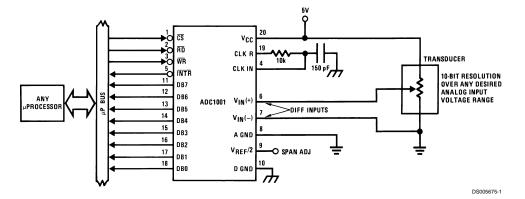

# **Typical Application**

Note 12:  $\overline{\text{CS}}$  shown twice for clarity.

Note 13: SAR= Successive Approximation Register.

FIGURE 3.

www.national.com

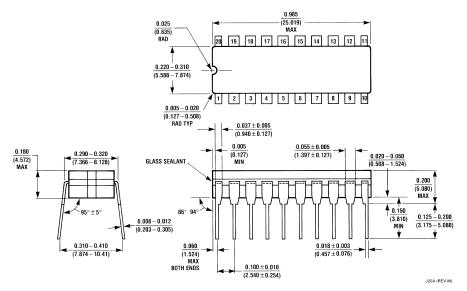

### Physical Dimensions inches (millimeters) unless otherwise noted

Cavity Dual-In-Line Package (J) (Side Brazed)

Order Number ADC1001CCJ or ADC1001CCJ-1

NS Package Number J20A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

National Semiconductor

Fax: 449 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: 449 (0) 1 80-530 85 85

English Tel: 449 (0) 1 80-532 78 32

Français Tel: 449 (0) 1 80-532 93 58

Italiano Tel: 449 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products | Applications |

|----------|--------------|

|----------|--------------|

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface interface.ti.com Security www.ti.com/security

Logic logic.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors <u>www.ti.com/omap</u>

Wireless Connectivity www.ti.com/wirelessconnectivity

TI E2E Community Home Page e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated