## LC<sup>2</sup>MOS Complete, High Speed 12-Bit ADC

AD7572

FEATURES

12-Bit Resolution and Accuracy

Fast Conversion Time AD7572XX05: 5µs AD7572XX12: 12.5µs

Complete with On-Chip Reference Fast Bus Access Time: 90ns

Fast Bus Access Time: 90ns Low Power: 135mW Small, 0.3", 24-Pin Package

and 28-Terminal Surface Mount Packages

#### GENERAL DESCRIPTION

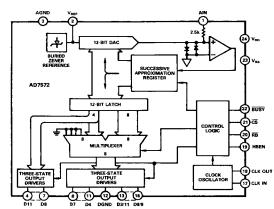

The AD7572 is a complete, 12-bit ADC that offers high speed performance combined with low, CMOS power levels. The AD7572 uses an accurate, high speed DAC and comparator in a successive-approximation loop to achieve a fast conversion time. An on-chip, buried Zener diode provides a stable reference voltage to give low drift performance over the full temperature range and the specified accuracy is achieved without any user trims. An on-chip clock circuit is provided, which may be used with a crystal for stand-alone operation, or the clock input may be driven from an external clock source such as a divided-down microprocessor clock. The only other external components required for basic operation of the AD7572 are decoupling capacitors for the supply voltages and reference output.

The AD7572 has a high speed digital interface with three-state data outputs and can operate under the control of standard microprocessor Read  $(\overline{RD})$  and decoded address  $(\overline{CS})$  signals. Interface timing is sufficiently fast to allow the AD7572 to operate with most popular microprocessors, with three-state enable times of only 90ns and bus relinquish times of 75ns.

The AD7572 is fabricated in Analog Devices Linear Compatible CMOS process (LC<sup>2</sup>MOS), an advanced, all ion-implanted process that combines fast CMOS logic and linear, bipolar circuits on a single chip, thus achieving excellent linear performance while still retaining low CMOS power levels.

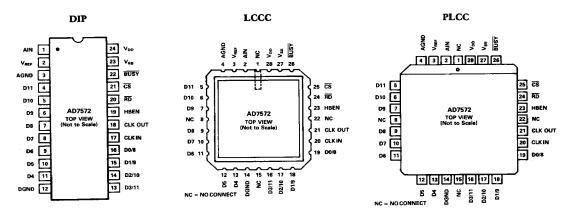

The AD7572 is available in both 0.3" wide, 24-pin DIPs and in a 28-terminal plastic leaded chip carrier (PLCC) and leadless ceramic chip carrier (LCCC).

#### FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT HIGHLIGHTS

- Fast, 5μs and 12.5μs conversion times make the AD7572 ideal for a wide range of applications in telecommunications, sonar and radar signal processing or any wideband data acquisition system.

- On-chip buried-Zener reference has temperature coefficient as low as 25ppm/°C, giving low full-scale drift over the operating temperature range.

- Stable DAC and comparator give excellent linearity and low zero error over the full temperature range.

- Fast, easy-to-use digital interface has three-state bus access times of 90ns and bus relinquish times of 75ns, allowing the AD7572 to interface to most popular microprocessors.

- LC<sup>2</sup>MOS circuitry gives low power drain (135mW) from +5, -15 volt supplies.

- 24-pin 0.3" package offers space saving over parts in 28-pin 0.6" DIP.

#

| Parameter                                      | J, A, S<br>Versions <sup>1</sup> | K, B, T<br>Versions | L Version | C, U<br>Versions | Units         | Test Conditions/Comments                                                                                                         |

|------------------------------------------------|----------------------------------|---------------------|-----------|------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------|

| ACCURACY                                       |                                  |                     |           |                  |               |                                                                                                                                  |

|                                                | 12                               | 12                  | 12        | 12               | Bits          |                                                                                                                                  |

| Resolution                                     | ±1                               | ±1                  | ± 1/2     | ± 1/2            | LSB max       |                                                                                                                                  |

| Integral Nonlinearity @ +25℃                   | ±1<br>±1                         | ±1<br>±1            | ± 1/2     | ± 3/4            | LSB max       |                                                                                                                                  |

| T <sub>min</sub> to T <sub>max</sub>           |                                  |                     | ±1/2      | ±1               | LSB max       |                                                                                                                                  |

| Differential Nonlinearity                      | ±1                               | ±1                  | Ξ,        | ± 1              | LSDillex      |                                                                                                                                  |

| Minimum Resolution for which no                |                                  |                     | 1         | 12               | Bits          |                                                                                                                                  |

| Missing Codes are Guaranteed                   | 12                               | 12                  | 12        |                  |               |                                                                                                                                  |

| Offset Error @ +25°C                           | ±4                               | ±3                  | ± 3       | ±3               | LSB max       | Typical Change over Temp Is ± 1LS                                                                                                |

| T <sub>min</sub> to T <sub>max</sub>           | ±6                               | ± 5                 | ± 4       | ±4_              | LSB max       |                                                                                                                                  |

| Full Scale (FS) Error <sup>2</sup> @ + 25°C    | ± 15                             | ± 10                | ± 10      | ± 10             | LSB max       | $V_{DD} = 5V; V_{SS} = -15V; FS = 5V$                                                                                            |

| Full Scale TC <sup>3,4</sup>                   | 45                               | 25                  | 25        | 25               | ppm/°C max    | Ideal Last Code Transition =<br>FS - 3/2LSBs                                                                                     |

| ANALOG INPUT                                   |                                  | -                   |           |                  |               |                                                                                                                                  |

| Input Voltage Range                            | 0 to + 5                         | 0 to +5             | 0 to +5   | 0 to +5          | Volts         | For Bipolar Operation See                                                                                                        |

| Input Current                                  | 3.5                              | 3.5                 | 3.5       | 3.5              | mA max        | Figures 10 & 12                                                                                                                  |

| INTERNAL REFERENCE VOLTAGE                     | 2.5                              |                     |           |                  |               |                                                                                                                                  |

| V <sub>REF</sub> Output @ +25°C                | -5.2/-5.3                        | - 5.2/ - 5.3        | -5.2/-5.3 | -5.2/-5.3        | V min/V max   | $-5.25V \pm 1\%$                                                                                                                 |

| V <sub>REF</sub> Output TC                     | 40                               | 20                  | 20        | 20               | ppm/°C typ    |                                                                                                                                  |

| Output Current Sink Capability                 | 550                              | 550                 | 550       | 550              | μ.A max       | External Load Should Not Change                                                                                                  |

| Output Current Sink Capability                 | 550                              | 330                 |           |                  |               | During Conversion                                                                                                                |

| POWER SUPPLY REJECTION                         |                                  | _                   |           |                  | 1 on .        | FS Change, V <sub>SS</sub> = -15V                                                                                                |

| V <sub>DD</sub> Only                           | ± 1/2                            | ± 1/2               | ± 1/2     | ± 1/2            | LSB typ       | $V_{DD} = +4.75V \text{ to } +5.25V$                                                                                             |

|                                                |                                  | l                   |           |                  |               |                                                                                                                                  |

| V <sub>SS</sub> Only                           | ± 1/2                            | ± 1/2               | ± 1/2     | ± 1/2            | LSB typ       | FS Change, $V_{DD} = 5V$<br>$V_{SS} = -14.25V \text{ to } -15.75V$                                                               |

| LOGICINPUTS                                    |                                  |                     |           | <del> </del>     |               | V <sub>SS</sub> = 14.25 v to 15.75 v                                                                                             |

| CS, RD, HBEN, CLK IN                           |                                  | ļ                   | 1         | ł                |               |                                                                                                                                  |

| V <sub>INI.</sub> , Input Low Voltage          | +0.8                             | +0.8                | +0.8      | + 0.8            | V max         | $V_{DD} = 5V \pm 5\%$                                                                                                            |

|                                                | + 2.4                            | + 2.4               | +2.4      | + 2.4            | V min         |                                                                                                                                  |

| V <sub>INH</sub> , Input High Voltage          | 10                               | 10                  | 10        | 10               | pF max        |                                                                                                                                  |

| C <sub>IN</sub> , 5 Input Capacitance          | 10                               | 10                  |           | 1 ""             | F             |                                                                                                                                  |

| CS, RD, HBEN                                   | ± 10                             | ± 10                | ± 10      | ± 10             | μA max        | $V_{IN} = 0 \text{ to } V_{DD}$                                                                                                  |

| IIN, Input Current                             | ± 10                             | = 10                | 1 - 10    |                  | F.1.1         | 114                                                                                                                              |

| CLKIN                                          |                                  | ± 20                | ± 20      | ± 20             | μA max        | $V_{tN} = 0 \text{ to } V_{DD}$                                                                                                  |

| I <sub>IN</sub> , Input Current                | ± 20                             | ± 20                | = 20      | - 20             | pars intex    | TIN TO IDD                                                                                                                       |

| LOGICOUTPUTS                                   |                                  | 1                   | Į.        | 1                |               | <b>I</b>                                                                                                                         |

| D11-D0/8, BUSY, CLK OUT                        |                                  |                     | 1         | +0.4             | V max         | I <sub>SINK</sub> = 1.6mA                                                                                                        |

| Vol., Output Low Voltage                       | +0.4                             | +0.4                | +0.4      |                  | V min         | I <sub>SOURCE</sub> = 200μA                                                                                                      |

| V <sub>OH</sub> , Output High Voltage          | +4.0                             | +4.0                | +4.0      | +4.0             | V min         | ISOURCE - 200µII                                                                                                                 |

| D11-D0/8                                       |                                  |                     |           |                  | 1 .           |                                                                                                                                  |

| Floating State Leakage Current                 | ± 10                             | ± 10                | ± 10      | ± 10             | μA max        |                                                                                                                                  |

| Floating State Output Capacitance <sup>5</sup> | 15                               | 15                  | 15        | 15               | pF max        |                                                                                                                                  |

| CONVERSION TIME                                | ľ                                |                     | 1         |                  | 1             | l                                                                                                                                |

| AD7572XX05                                     | l .                              | l .                 | 1.        | 1 .              | l             | f <sub>CLK</sub> = 2.5MHz. See Under                                                                                             |

| Synchronous Clock                              | 5                                | 5                   | 5         | 3                | µs max        | Control Inputs Synchronization                                                                                                   |

| Asynchronous Clock                             | 4.8/5.2                          | 4.8/5.2             | 4.8/5.2   | 4.8/5.2          | μs min/max    | Control Inputs Sylicinoinzation                                                                                                  |

| AD7572XX12                                     |                                  | Į.                  |           |                  | ł.            | C 11477-                                                                                                                         |

| Synchronous Clock                              | 12.5                             | 12.5                | 12.5      | 12.5             | μs max        | $f_{CLK} = 1MHz$                                                                                                                 |

| Asynchronous Clock                             | 12/13                            | 12/13               | 12/13     | 12/13            | με min/με max |                                                                                                                                  |

| POWER REQUIREMENTS                             |                                  |                     |           | +5               | VNOM          | ± 5% for Specified Performance                                                                                                   |

| $V_{DD}$                                       | +5                               | +5                  | +5        |                  |               | ± 5% for Specified Performance                                                                                                   |

| V <sub>ss</sub>                                | - 15                             | - 15                | - 15      | - 15             | VNOM          | $\frac{\pm 5\% \text{ for Specified Performance}}{\overline{\text{CS}} = \overline{\text{RD}} = V_{\text{DD}}, \text{AIN} = 5V}$ |

| I <sub>DD</sub> <sup>6</sup>                   | 7                                | 7                   | 7         | 7                | mA max        |                                                                                                                                  |

| I <sub>SS</sub> <sup>6</sup>                   | 12                               | 12                  | 12        | 12               | mA max        | $\overline{CS} = \overline{RD} = V_{DD}$ , AIN = 5V                                                                              |

| Power Dissipation                              | 135                              | 135                 | 135       | 135              | m₩ typ        | 1                                                                                                                                |

|                                                | 215                              | 215                 | 215       | 215              | mW max        | •                                                                                                                                |

NOTES

Temperature range as follows: J, K, L Versions; 0 to + 70°C.

A, B, C Versions; - 25°C to + 85°C.

S, T, U Versions; - 55°C to + 125°C.

Includes internal voltage reference error. Pull-Scale change from  $T_A=+25^\circ\text{C}$  to  $T_{max}$  or  $T_{max}$ . The change from  $T_A=+25^\circ\text{C}$  to  $T_{max}$  or  $T_{max}$ .

Sample tested to ensure compliance.

Power supply current is measured when AD7572 is inactive, i.e.,  $\overline{CS} = \overline{RD} = \overline{BUSY} = HIGH$ .

Specifications subject to change without notice.

### TIMING CHARACTERISTICS<sup>1</sup> $(v_{00} = 5V, V_{SS} - 15V)$

| Parameter                   | Limit at +25°C<br>(All Grades) | Limit at T <sub>min</sub> , T <sub>max</sub> (J, K, L, A, B, C Grades) | Limit at T <sub>min</sub> , T <sub>max</sub> (S, T, U Grades) | Units  | Conditions/Comments                                    |

|-----------------------------|--------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------|--------|--------------------------------------------------------|

| t <sub>1</sub>              | 0                              | 0                                                                      | 0                                                             | ns min | CS to RD Setup Time                                    |

| t <sub>2</sub>              | 190                            | 230                                                                    | 270                                                           | ns max | RD to BUSY Propagation Delay                           |

| t <sub>3</sub> <sup>2</sup> | 90                             | 110                                                                    | 120                                                           | ns max | Data Access Time after $\overline{RD}$ , $C_L = 20pF$  |

|                             | 125                            | 150                                                                    | 170                                                           | ns max | Data Access Time after $\overline{RD}$ , $C_L = 100pI$ |

| t <sub>4</sub>              | t <sub>3</sub>                 | t <sub>3</sub>                                                         | t <sub>3</sub>                                                | ns min | RD Pulse Width                                         |

| t <sub>5</sub>              | 0                              | 0                                                                      | 0                                                             | ns min | CS to RD Hold Time                                     |

| t <sub>6</sub> <sup>2</sup> | 70                             | 90                                                                     | 100                                                           | ns max | Data Setup Time after BUSY                             |

| t <sub>7</sub> 3            | 20                             | 20                                                                     | 20                                                            | ns min | Bus Relinquish Time                                    |

|                             | 75                             | 85                                                                     | 90                                                            | ns max | •                                                      |

| t <sub>8</sub>              | 0                              | 0                                                                      | 0                                                             | ns min | HBEN to RD Setup Time                                  |

| t <sub>9</sub>              | 0                              | 0                                                                      | 0                                                             | ns min | HBEN to RD Hold Time                                   |

| t <sub>10</sub>             | 200                            | 200                                                                    | 200                                                           | ns min | Delay Between Successive<br>Read Operations            |

#### NOTES

Specifications subject to change without notice.

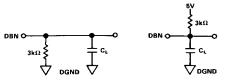

a. High-Z to  $V_{OH}$  ( $t_3$ ) and  $V_{OL}$  to  $V_{OH}$  ( $t_6$ )

b. High-Z to  $V_{OL}$  ( $t_3$ ) and  $V_{OH}$  to  $V_{OL}$  ( $t_6$ )

Figure 1. Load Circuits for Access Time

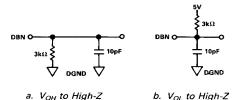

Figure 2. Load Circuits for Output Float Delay

#### ABSOLUTE MAXIMUM RATINGS\*

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$  $V_{DD}$  to DGND  $\ \ldots \ \ldots \ \ldots \ -0.3V$  to +7V $V_{SS}$  to DGND . . . . . . . . . . . . . . . . +0.3V to -17V AGND to DGND . . . . . . . . . . -0.3V,  $V_{DD}$  + 0.3VAIN to AGND . . . . . . . . . . . . -15V to +15V Digital Input Voltage to DGND (CLK IN, HBEN,  $\overline{RD}$ ,  $\overline{CS}$ ) . . . . . -0.3V,  $V_{DD}$  + 0.3VDigital Output Voltage to DGND (D11-D0/8, CLK OUT,  $\overline{BUSY}$ ) . . . -0.3V,  $V_{DD} + 0.3V$ Operating Temperature Range Commercial (J, K, L Versions) . . . . . . . . 0 to +70°C Industrial (A, B, C Versions) . . . . . . -25°C to +85°C Extended (S, T, U Versions) . . . . . . -55°C to +125°C Storage Temperature . . . . . . . . . . . -65°C to +150°C Lead Temperature (Soldering, 10secs) . . . . . . + 300°C Power Dissipation (Any Package) to +75°C . . . . 1,000mW Derates above +75°C by . . . . . . . . . . . . . 10mW/°C

\*Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### CAUTION

ESD (electrostatic discharge) sensitive device. The digital control inputs are diode protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.

<sup>&</sup>lt;sup>1</sup>Timing Specifications are sample tested at +25°C to ensure compliance. All input control signals are specified with

tr = tf = 5ns(10% to 90% of + 5V) and timed from a voltage level of 1.6V.

$<sup>^2</sup>t_3$  and  $t_6$  are measured with the load circuits of Figure 1 and defined as the time required for an

output to cross 0.8V or 2.4V.  $^3t_7$  is defined as the time required for the data lines to change 0.5V when loaded with the circuits of Figure 2.

#### ORDERING GUIDE<sup>1</sup>

| Model <sup>2</sup> | Conversion<br>Time | Temperature<br>Range | Full-Scale<br>TC | Accuracy<br>Grade | Package<br>Option <sup>3</sup> |

|--------------------|--------------------|----------------------|------------------|-------------------|--------------------------------|

| AD7572JN05         | 5μs                | 0 to +70°C           | 45ppm/°C         | ±1LSB             | N-24                           |

| AD7572KN05         | 5μs                | 0 to +70°C           | 25ppm/°C         | ±1LSB             | N-24                           |

| AD7572LN05         | 5μs                | 0 to +70°C           | 25ppm/°C         | ±1/2LSB           | N-24                           |

| AD7572JP05         | 5μs                | 0 to +70°C           | 45ppm/°C         | ±1LSB             | P-28A                          |

| AD7572KP05         | 5μs                | 0 to +70°C           | 25ppm/°C         | ±1LSB             | P-28A                          |

| AD7572LP05         | 5μs                | 0 to +70°C           | 25ppm/°C         | ±1/2LSB           | P-28A                          |

| AD7572AQ05         | 5μs                | −25°C to +85°C       | 45ppm/°C         | ±1LSB             | Q-24                           |

| AD7572BQ05         | 5μs                | −25°C to +85°C       | 25ppm/°C         | ±1LSB             | Q-24                           |

| AD7572CQ05         | 5μs                | −25°C to +85°C       | 25ppm/°C         | ±1/2LSB           | Q-24                           |

| AD7572SQ05         | 5μs                | −55°C to +125°C      | 45ppm/°C         | ±1LSB             | Q-24                           |

| AD7572TQ05         | 5μs                | -55°C to +125°C      | 25ppm/°C         | ±1LSB             | Q-24                           |

| AD7572UQ05         | 5μs                | -55°C to +125°C      | 25ppm/°C         | ±1/2LSB           | Q-24                           |

| AD7572SE05         | 5μs                | −55°C to +125°C      | 45ppm/°C         | ±1LSB             | E-28A                          |

| AD7572TE05         | 5μs                | −55°C to +125°C      | 25ppm/°C         | ±1LSB             | E-28A                          |

| AD7572UE05         | 5μs                | −55°C to +125°C      | 25ppm/°C         | ±1/2LSB           | E-28A                          |

| AD7572JN12         | 12.5μs             | 0 to +70°C           | 45ppm/°C         | ±1LSB             | N-24                           |

| AD7572KN12         | 12.5µs             | 0 to +70°C           | 25ppm/°C         | ±1LSB             | N-24                           |

| AD7572LN12         | 12.5µs             | 0 to +70°C           | 25ppm/°C         | ±1/2LSB           | N-24                           |

| AD7572JP12         | 12.5µs             | 0 to +70°C           | 45ppm/°C         | ±1LSB             | P-28A                          |

| AD7572KP12         | 12.5µs             | 0 to +70°C           | 25ppm/°C         | ±1LSB             | P-28A                          |

| AD7572LP12         | 12.5µs             | 0 to +70°C           | 25ppm/°C         | ±1/2LSB           | P-28A                          |

| AD7572AQ12         | 12.5μs             | −25°C to +85°C       | 45ppm/°C         | ±1LSB             | Q-24                           |

| AD7572BQ12         | 12.5µs             | −25°C to +85°C       | 25ppm/°C         | ±1LSB             | Q-24                           |

| AD7572CQ12         | 12.5µs             | -25°C to +85°C       | 25ppm/°C         | ±1/2LSB           | Q-24                           |

| AD7572SQ12         | 12.5µs             | -55°C to +125°C      | 45ppm/°C         | ±1LSB             | Q-24                           |

| AD7572TQ12         | 12.5μs             | -55°C to +125°C      | 25ppm/°C         | ±1LSB             | Q-24                           |

| AD7572UQ12         | 12.5µs             | −55°C to +125°C      | 25ppm/°C         | ±1/2LSB           | Q-24                           |

| AD7572SE12         | 12.5µs             | −55°C to +125°C      | 45ppm/°C         | ±1LSB             | E-28A                          |

| AD7572TE12         | 12.5µs             | −55°C to +125°C      | 25ppm/°C         | ±1LSB             | E-28A                          |

| AD7572UE12         | 12.5µs             | −55°C to +125°C      | 25ppm/°C         | ±1/2LSB           | E-28A                          |

#### NOTES

<sup>1</sup>Analog Devices Reserves the right to ship ceramic (D-24A) in lieu cerdip (Q-24) hermetic package.

<sup>2</sup>To order MIL-STD-883, Class B processed parts, add /883B to part number. Contact your local sales office for military data sheet. For U.S. Standard Military Drawing (SMD) see DESC Drawing #5962-87591.

<sup>3</sup>D = Ceramic DIP; E = Leadless Ceramic Chip Carrier (LCCC); N = Plastic DIP; P = Plastic Leaded Chip Carrier (PLCC); Q = Cerdip. For outline information see Package Information ssection.

#### PIN CONFIGURATIONS

2-302 ANALOG-TO-DIGITAL CONVERTERS

REV. A