**CMOS 8-Bit Microcontroller**

**TMP88CS34NG/FG, TMP88CP34NG/FG**

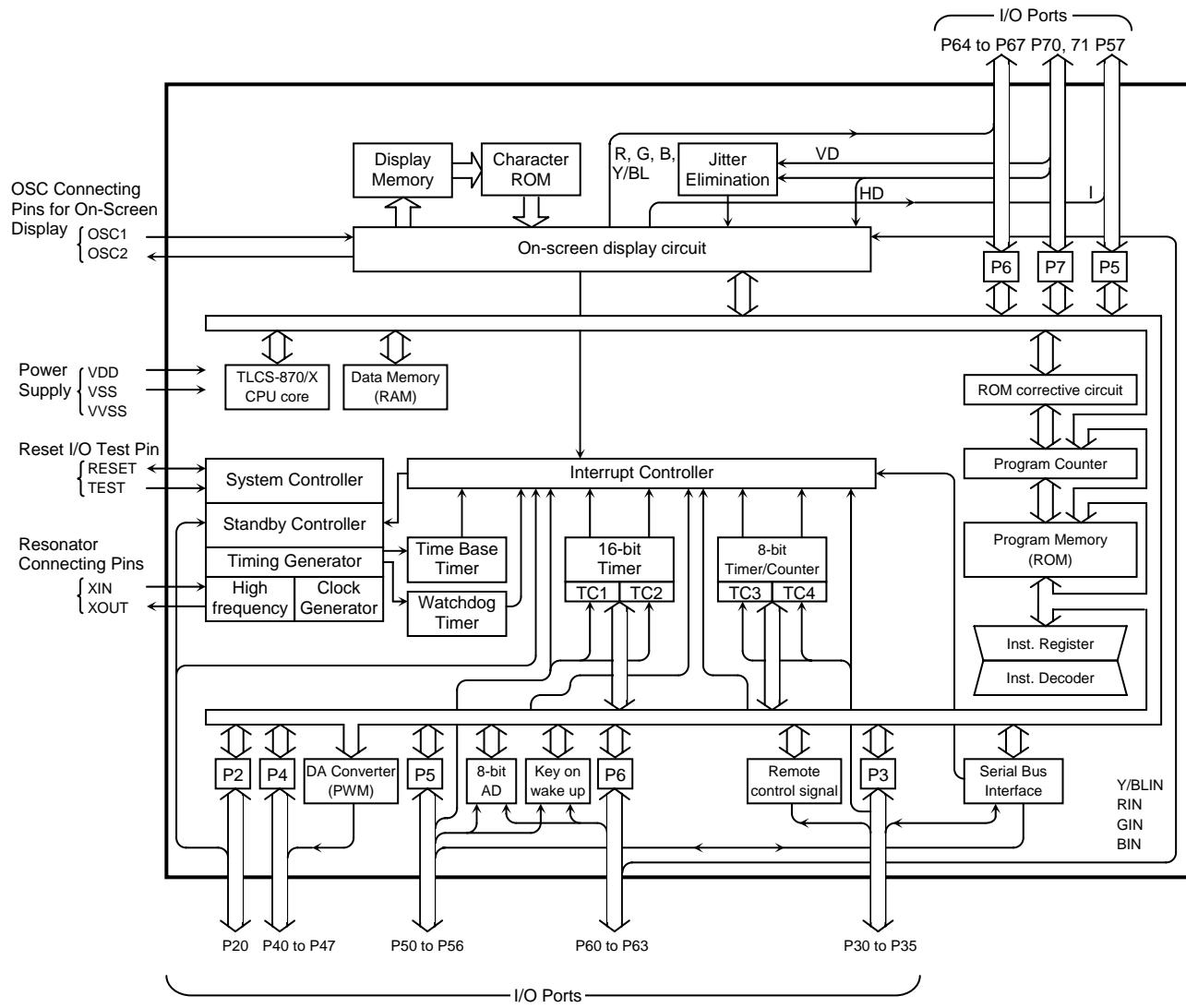

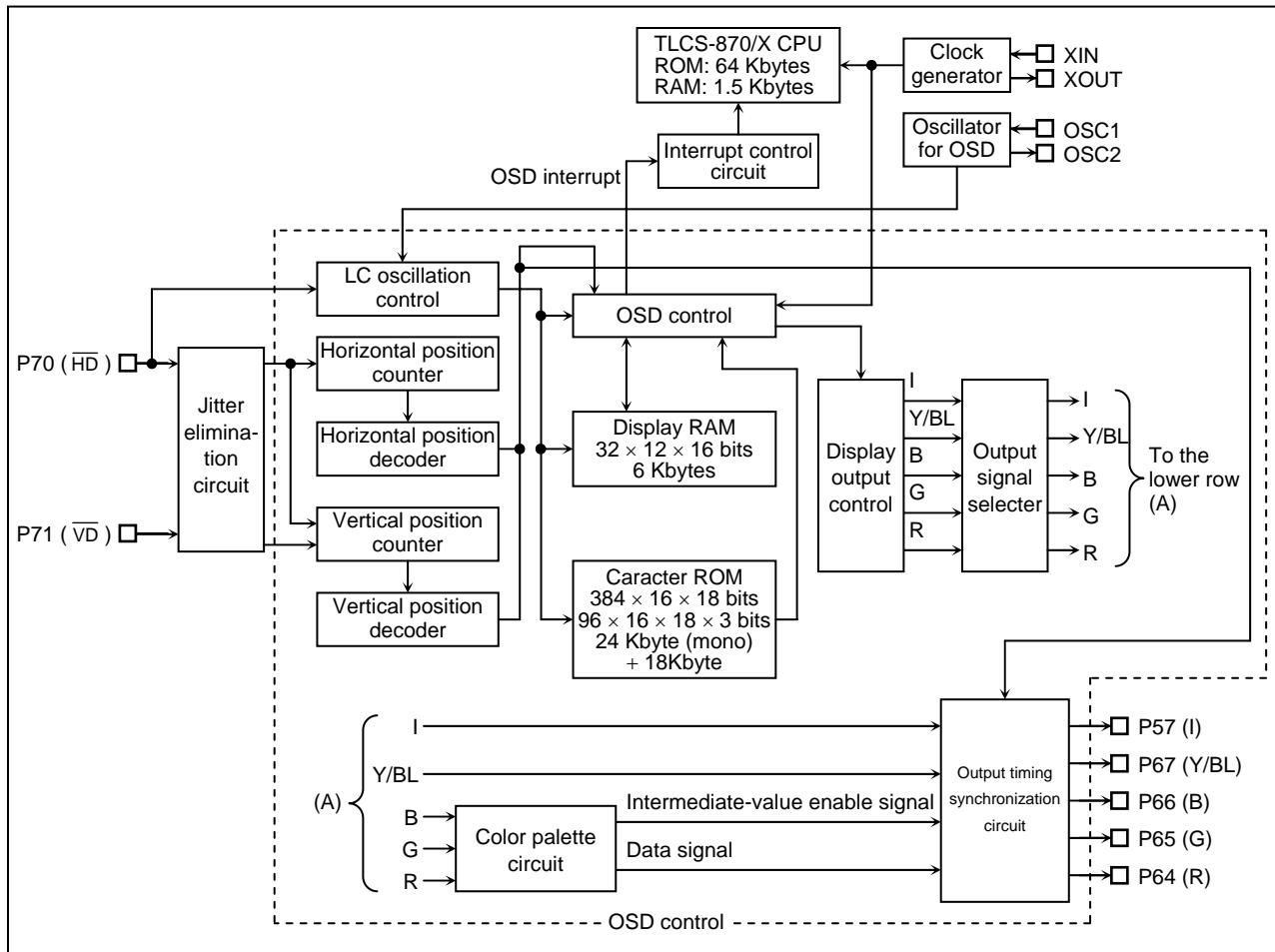

The TMP88CS34/CP34 is the high speed and high performance 8-bit single chip microcomputers. This MCU contain CPU core, ROM, RAM, input/output ports, four Multi-function timer/counters, serial bus interface, on-screen display, PWM output, 8-bit AD converter, and remote control signal preprocessor on chip.

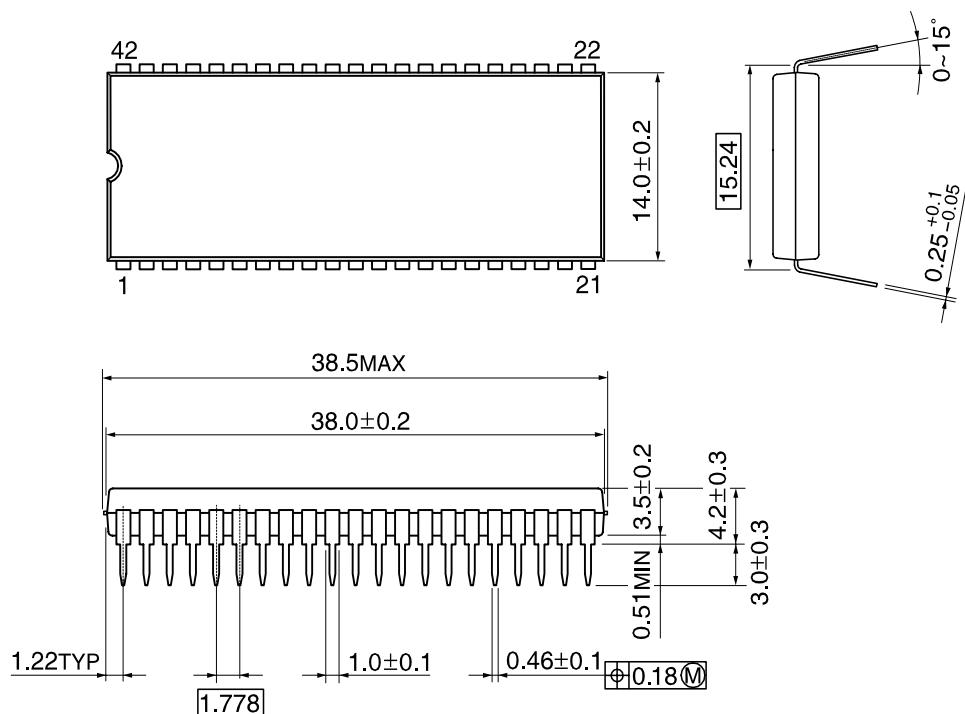

| Product No.    | ROM          | RAM           | Package            | OTP MCU        |

|----------------|--------------|---------------|--------------------|----------------|

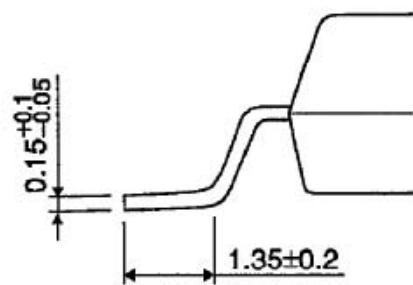

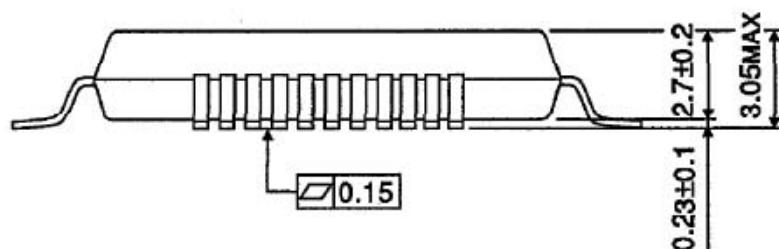

| TMP88CS34NG/FG | 64 K × 8-bit | 1.5 K × 8-bit | P-SDIP42-600-1.78  | TMP88PS34NG/FG |

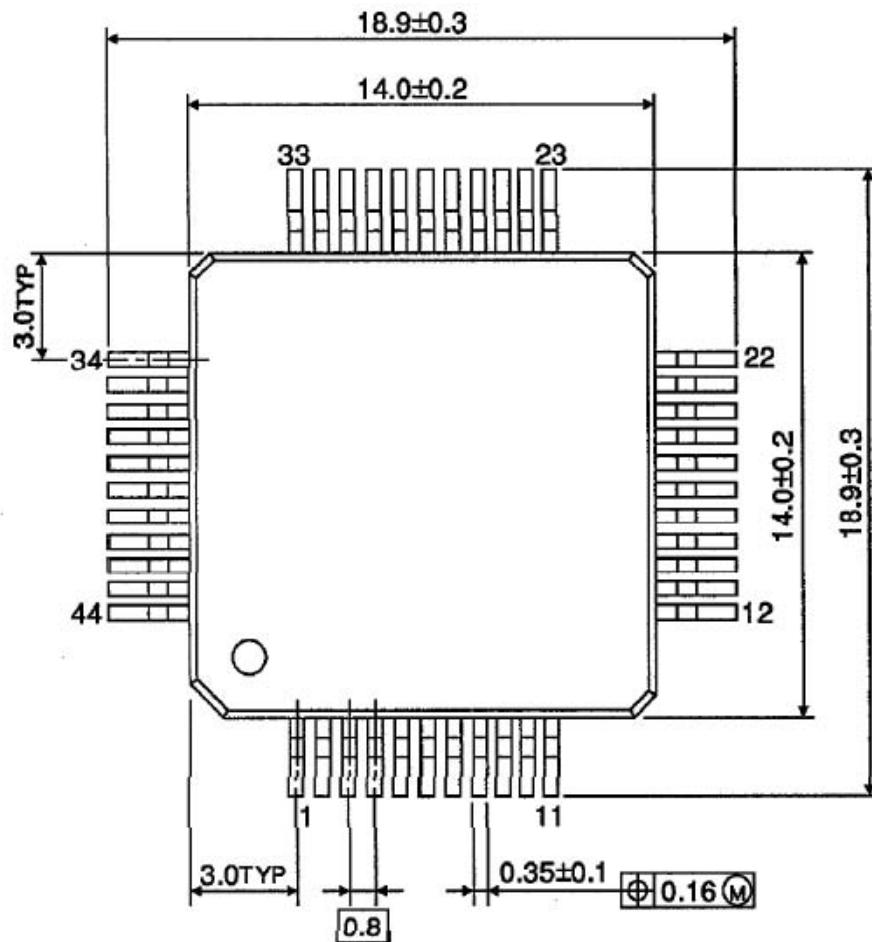

| TMP88CP34NG/FG | 48 K × 8-bit |               | P-QFP44-1414-0.80D |                |

## Features

- ◆ 8-bit single chip microcomputer TLCS-870/X Series

- ◆ Instruction execution time: 0.25  $\mu$ s (at 16 MHz)

- ◆ 842 basic instructions

- Multiplication and Division (8 bits × 8 bits, 16 bits × 8 bits, 16 bits/8 bits)

- Bit manipulations (Set/Clear/Complement/Move/Test/Exclusive or)

- 16-bit data and 20-bit data operations

- 1-byte jump/subroutine-call (Short relative jump/Vector call)

## RESTRICTIONS ON PRODUCT USE

20070701-EN

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.

- ◆ I/O ports: Maximum 33 (High current output: 4)

- ◆ 15 interrupt sources: External 6, Internal 10

- All sources have independent latches each, and nested interrupt control is available.

- Edge-selectable external interrupts with noise reject

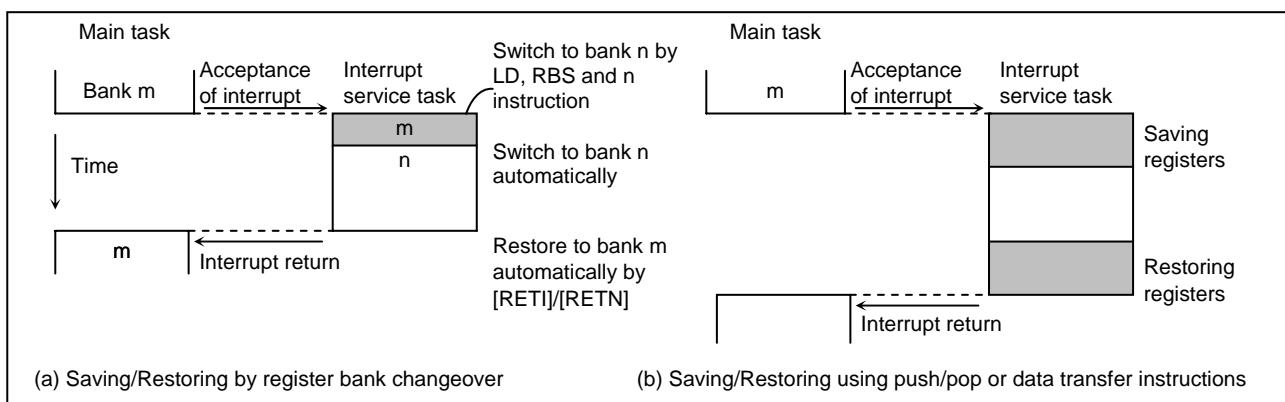

- High-speed task switching by register bank changeover

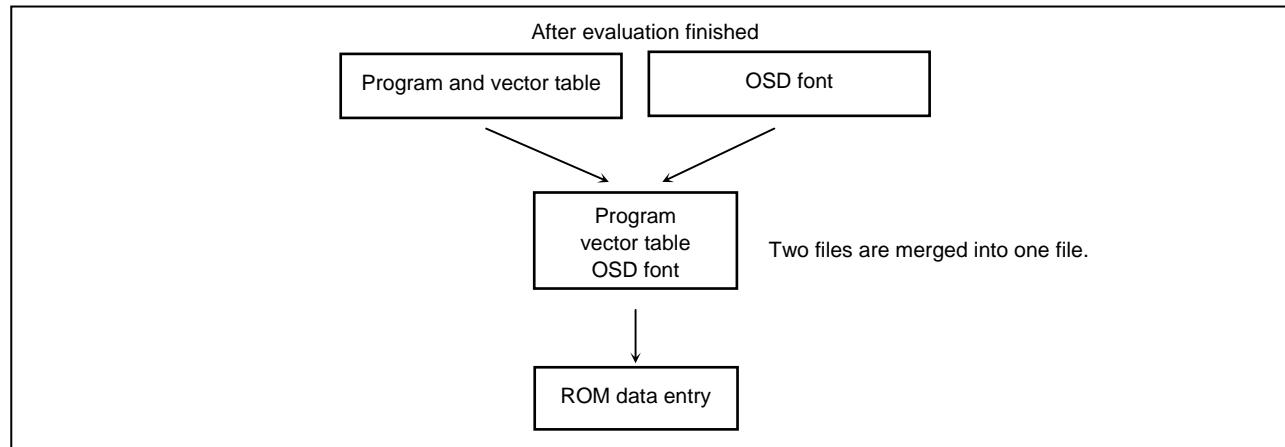

- ◆ ROM corrective function

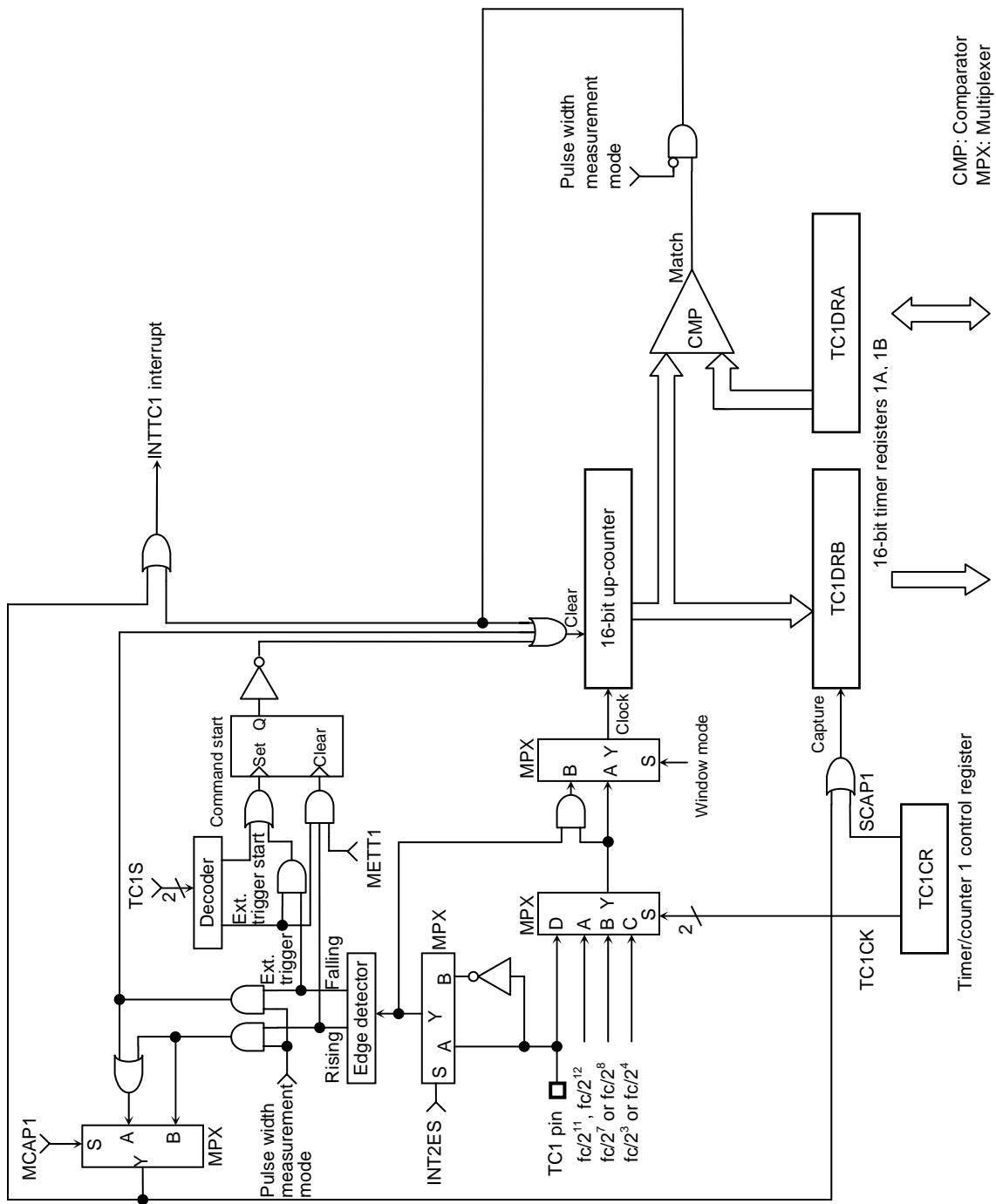

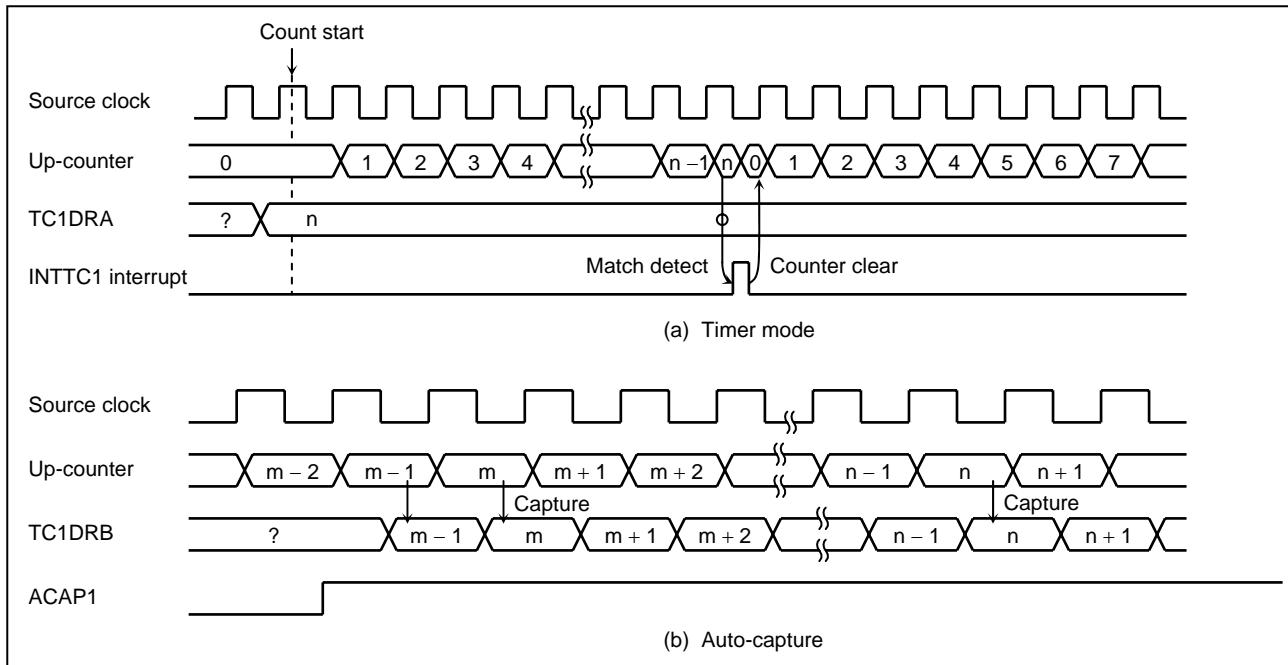

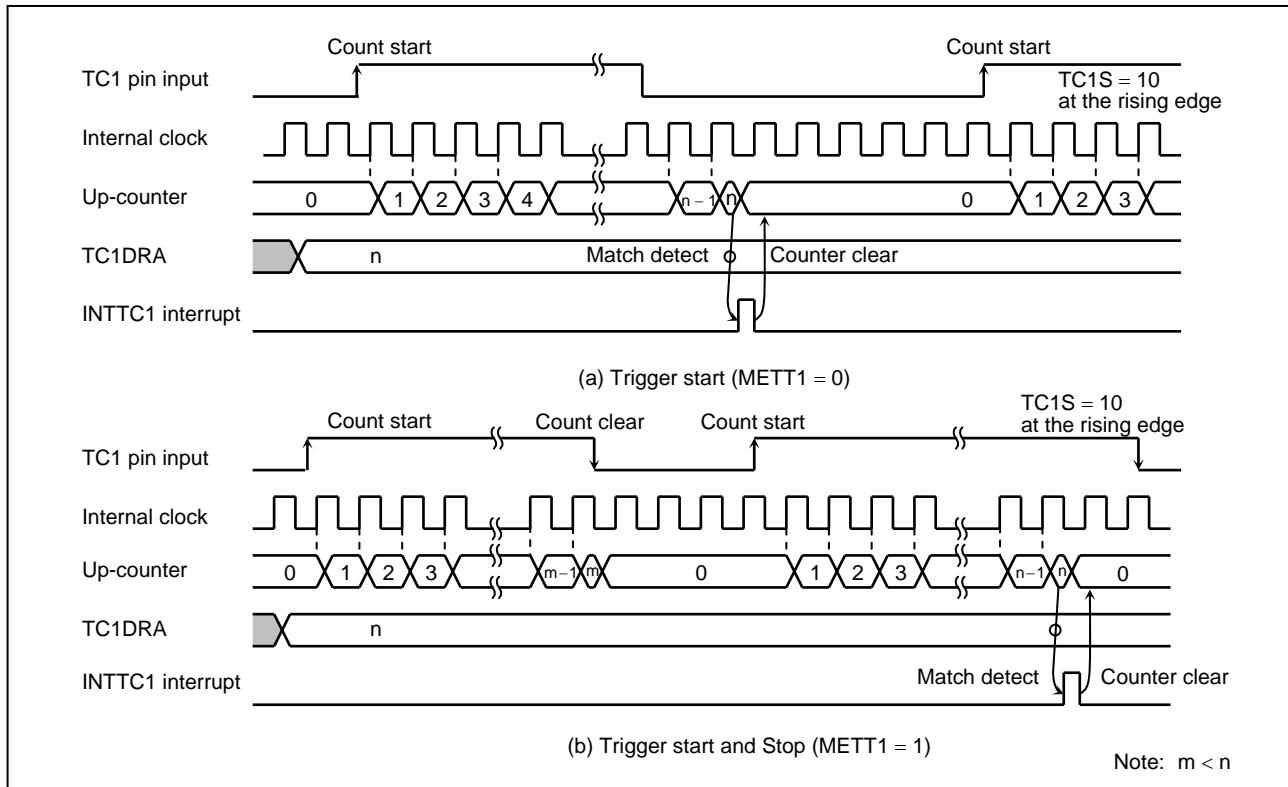

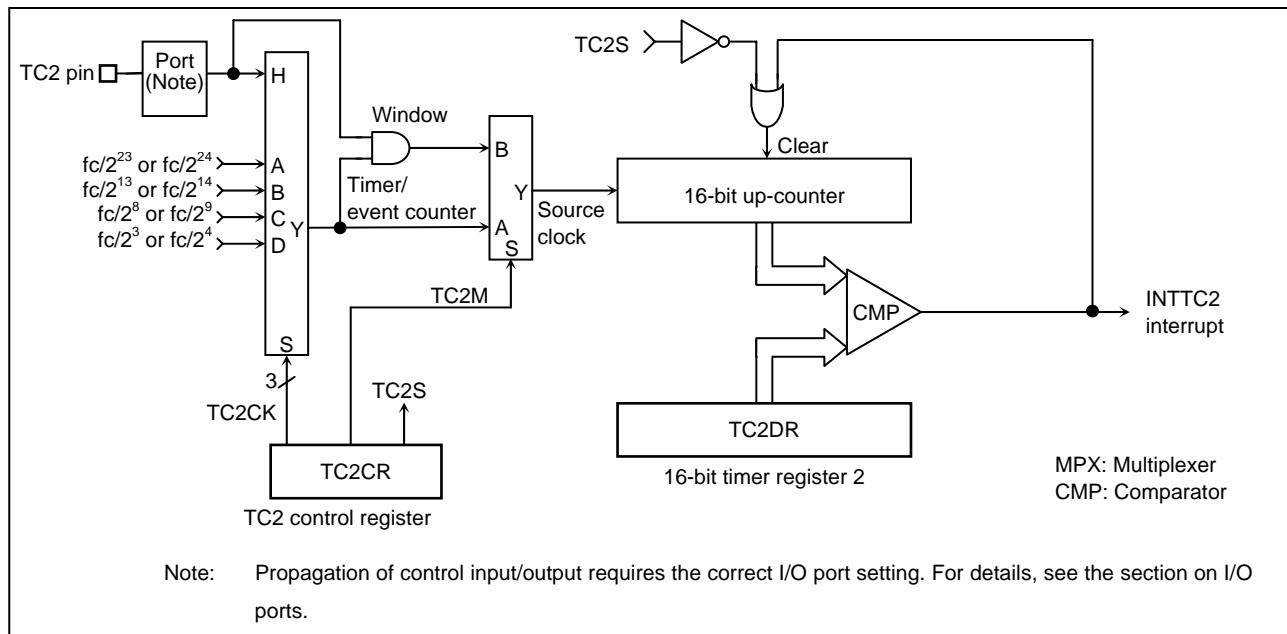

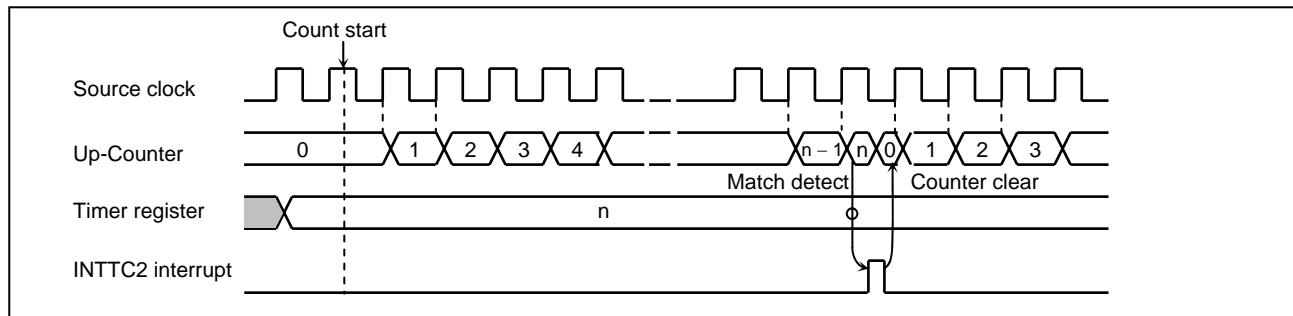

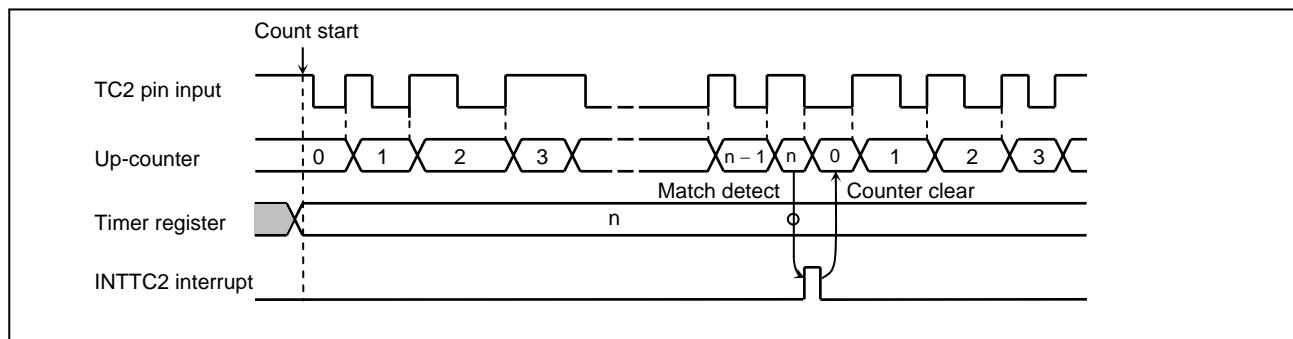

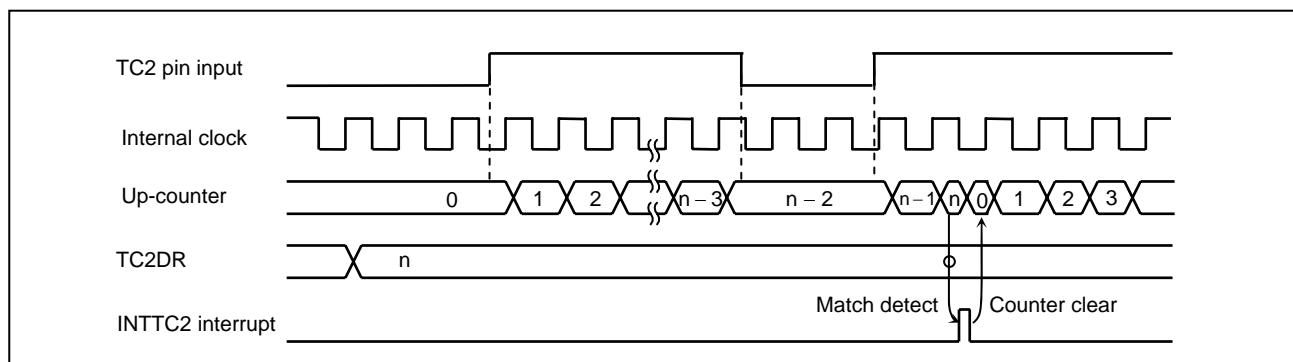

- ◆ Two 16-bit timer/counters: TC1, TC2

- Timer, Event-counter, Pulse width measurement, External trigger timer, Window modes

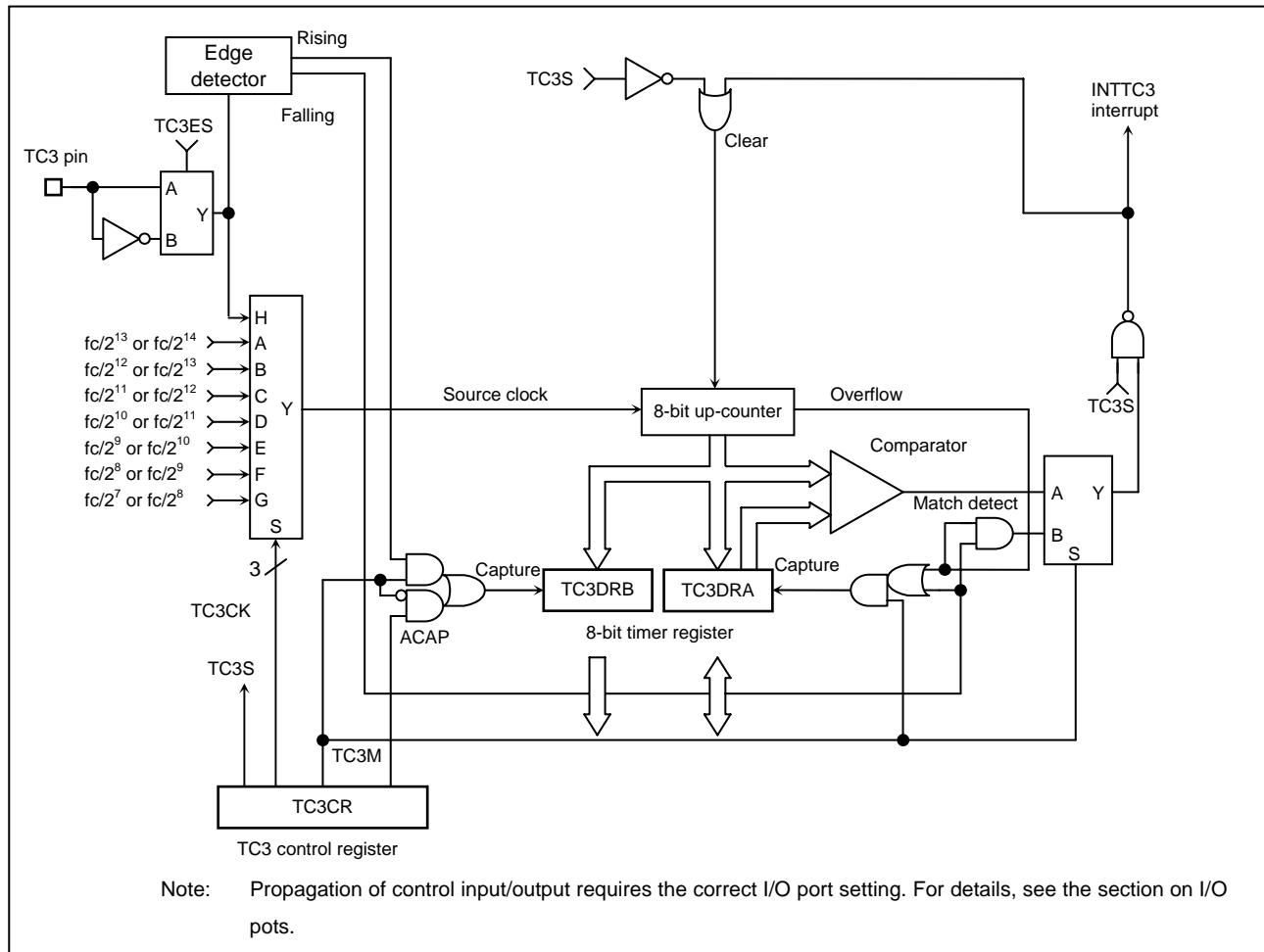

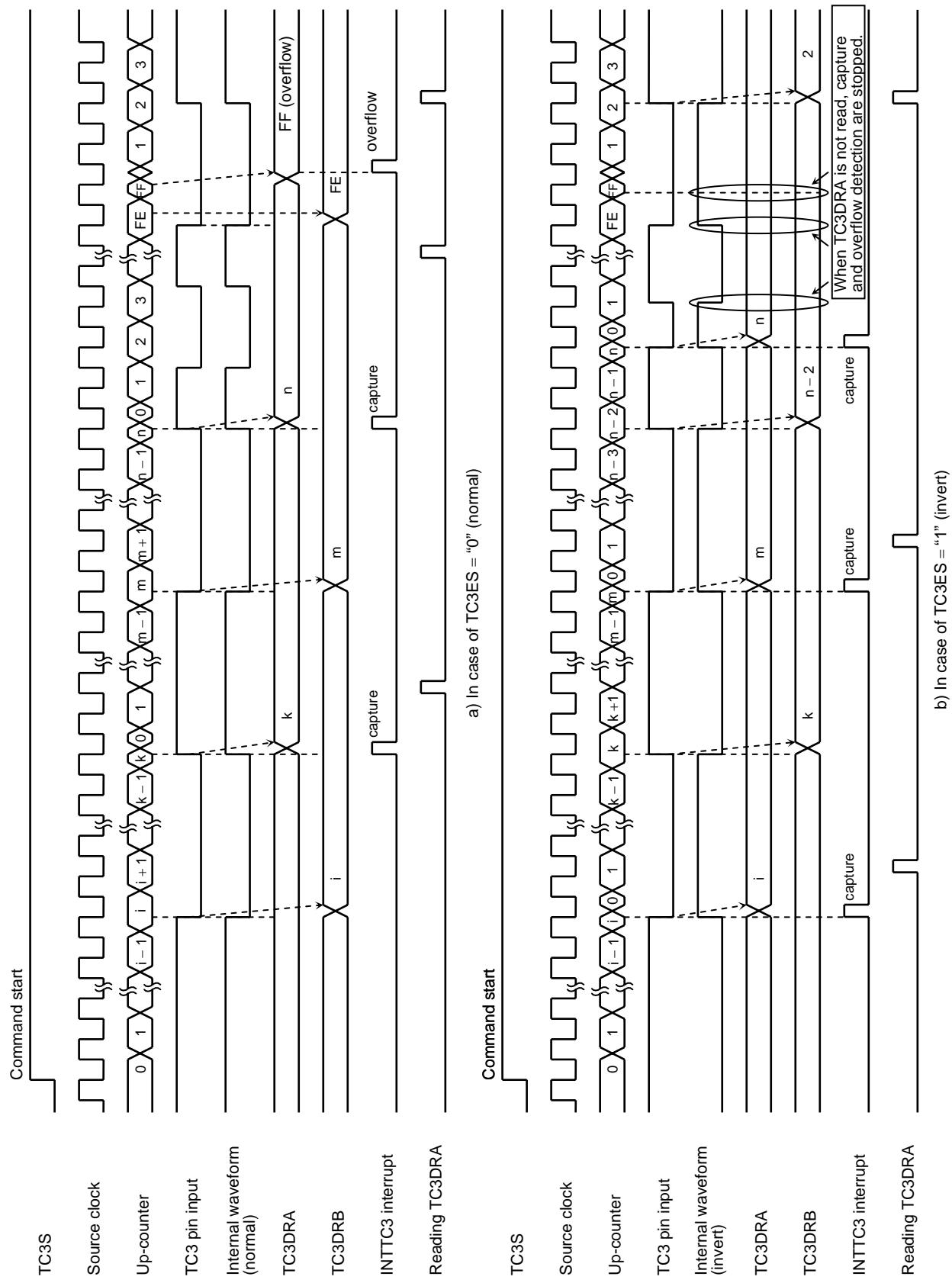

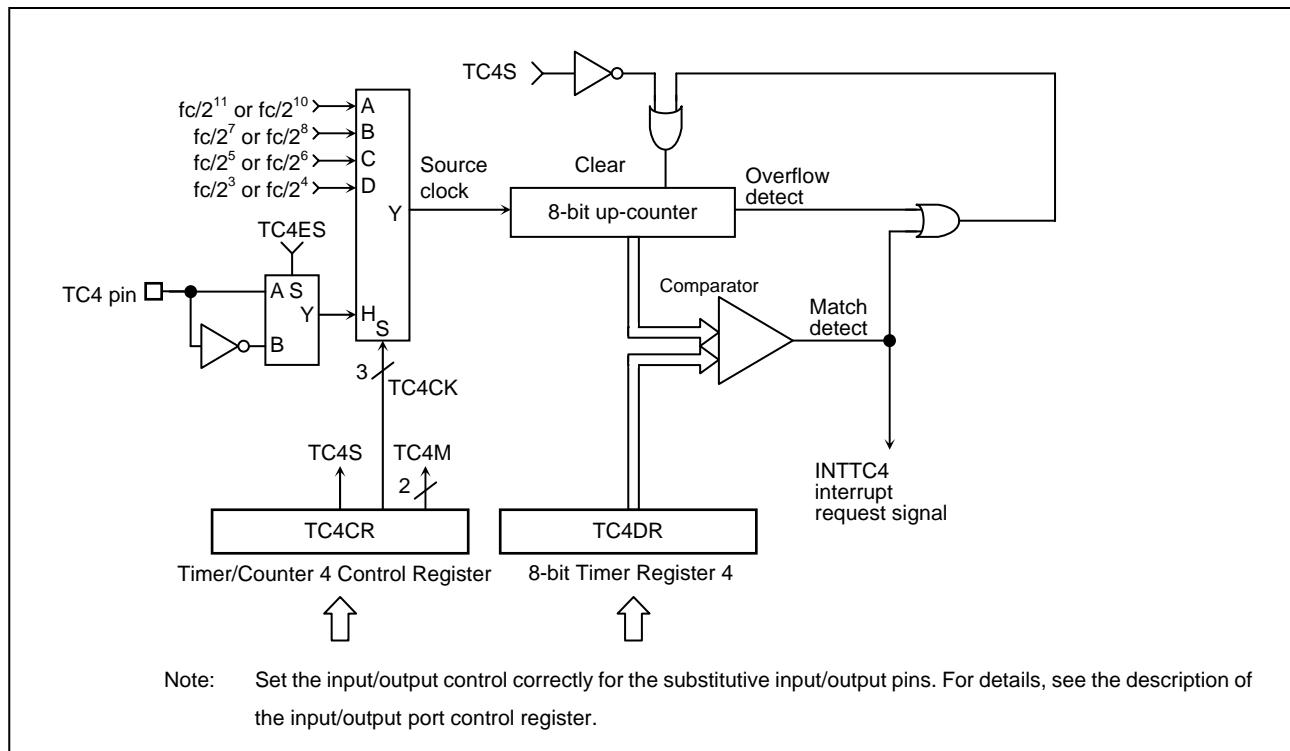

- ◆ Two 8-bit timer/counters: TC3, TC4

- Timer, Event counter, Capture (Pulse width/duty measurement) mode

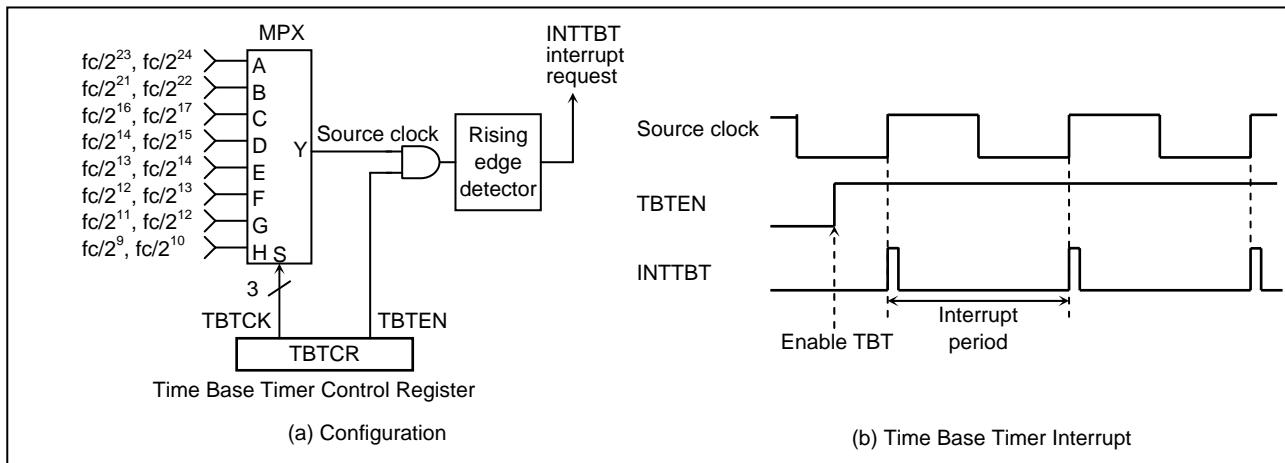

- ◆ Time base timer (Interrupt frequency: 0.95 Hz to 31250 Hz)

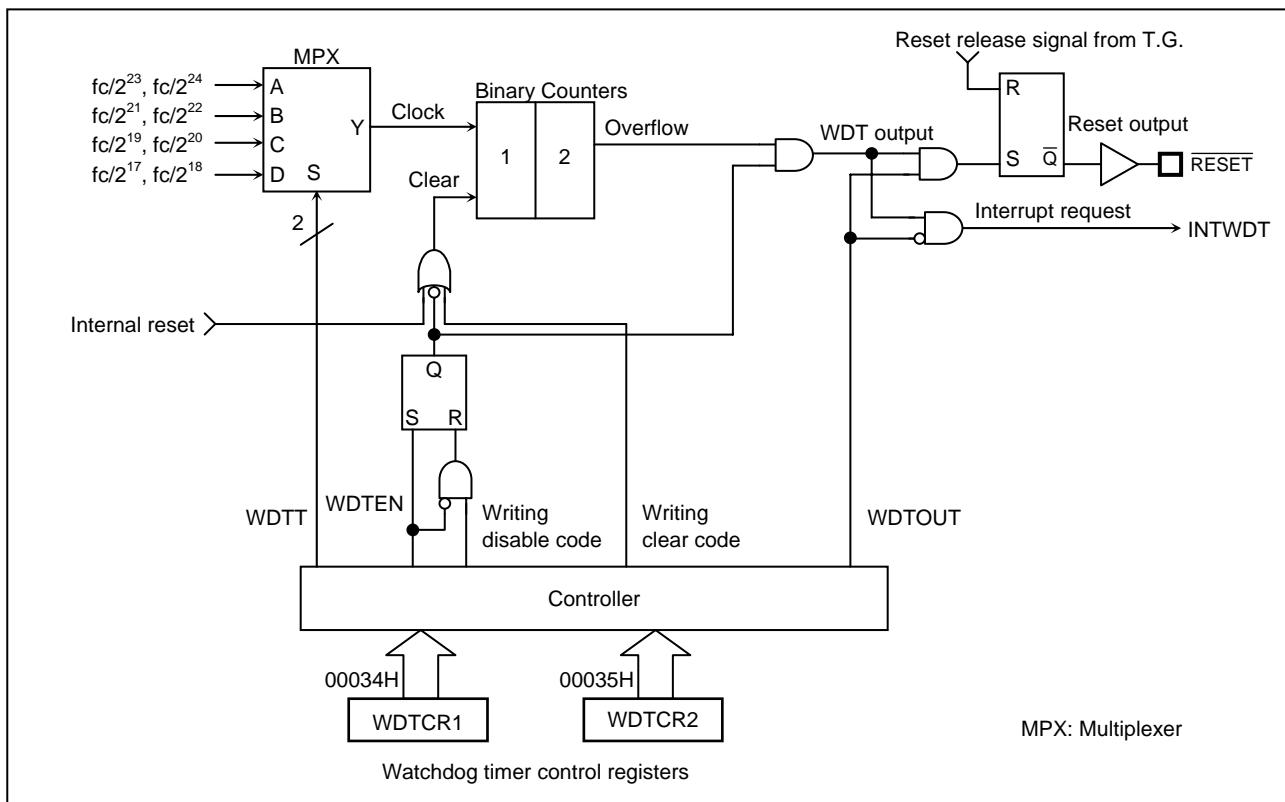

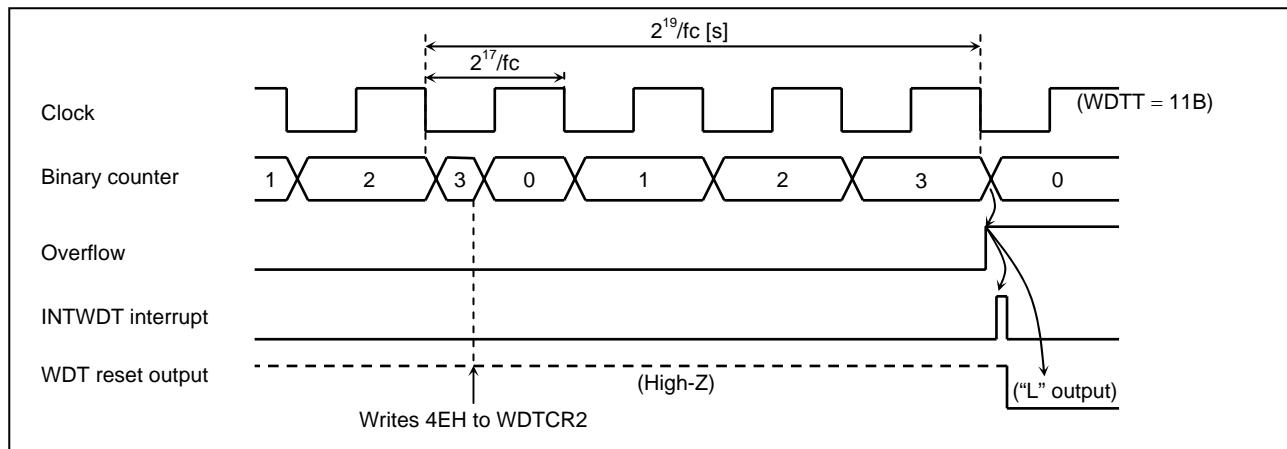

- ◆ Watchdog timer

- Interrupt source/reset output

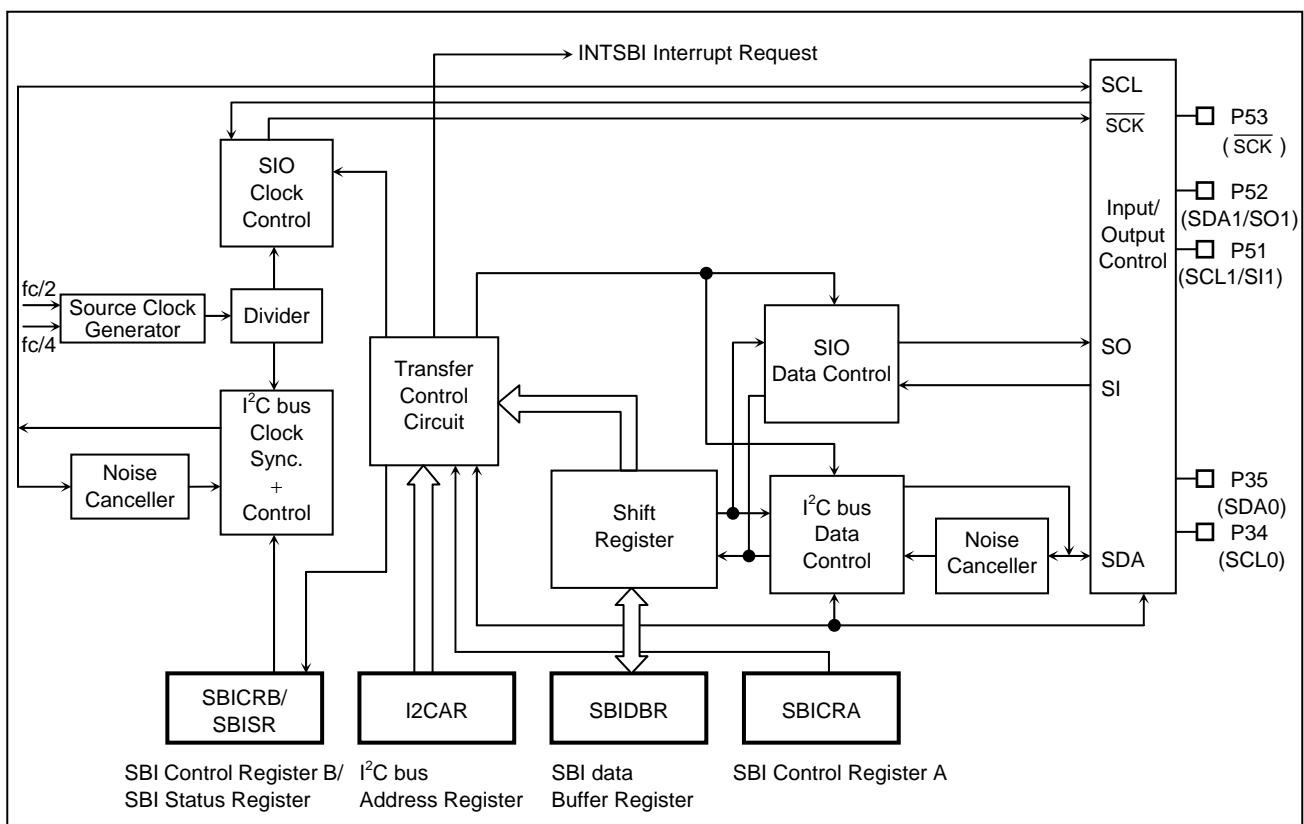

- ◆ Serial bus interface

- I<sup>2</sup>C bus, 8-bit SIO mode (Selectable two I/O channels)

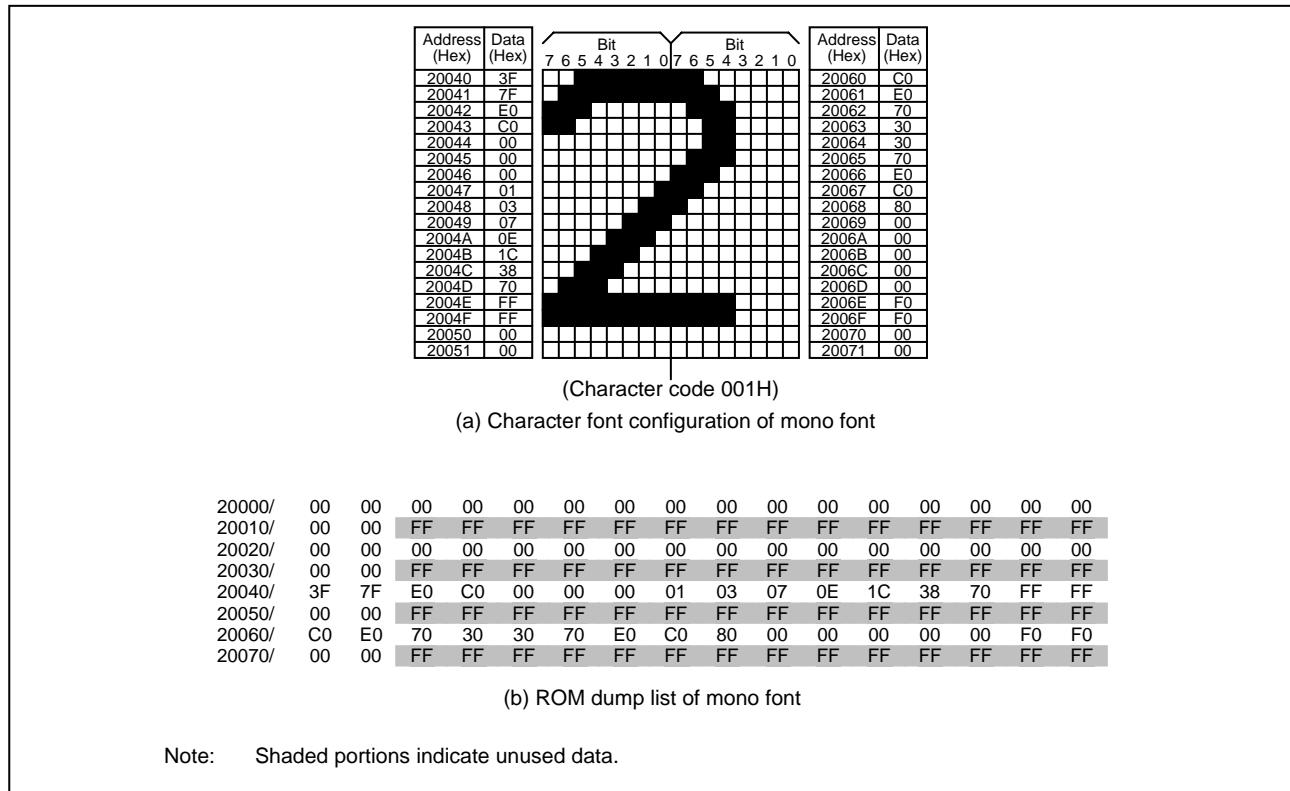

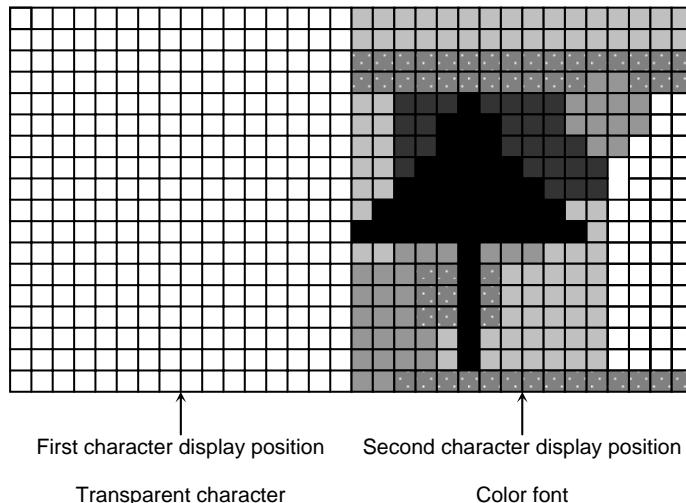

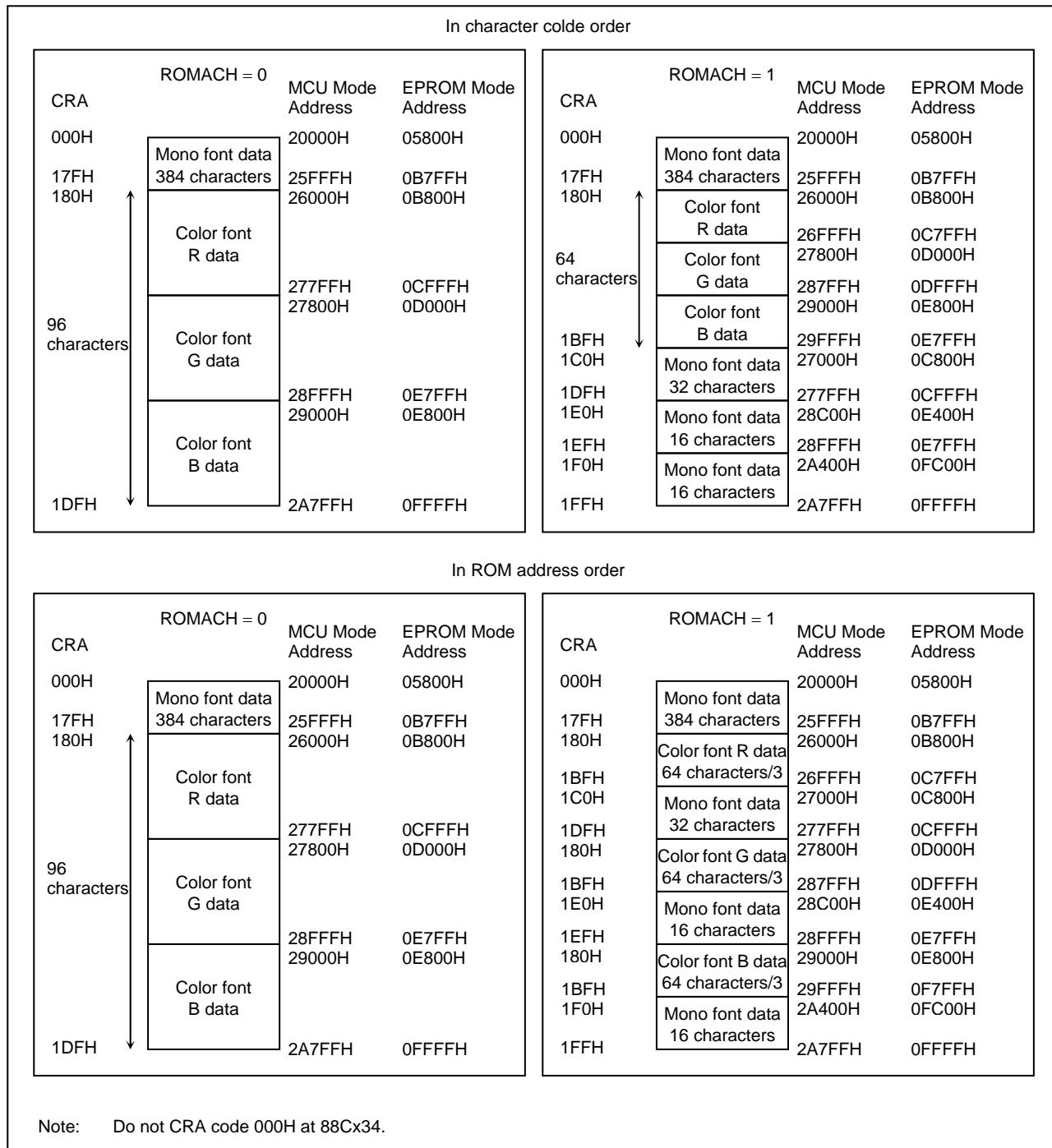

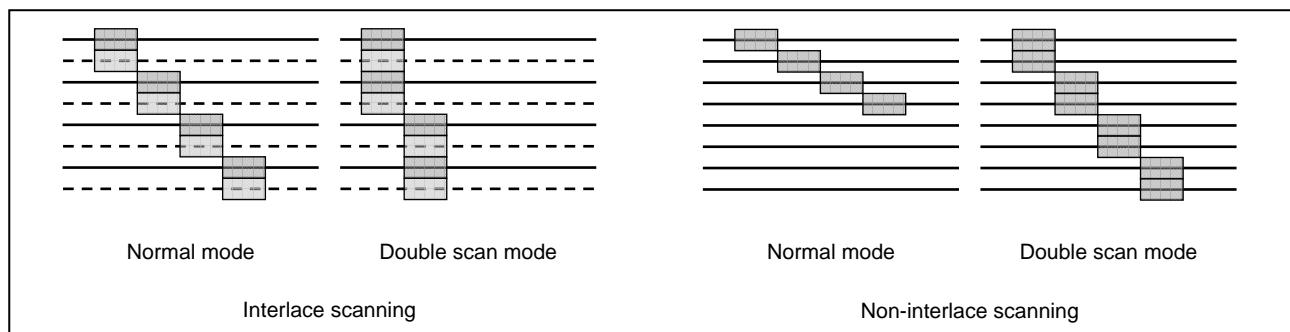

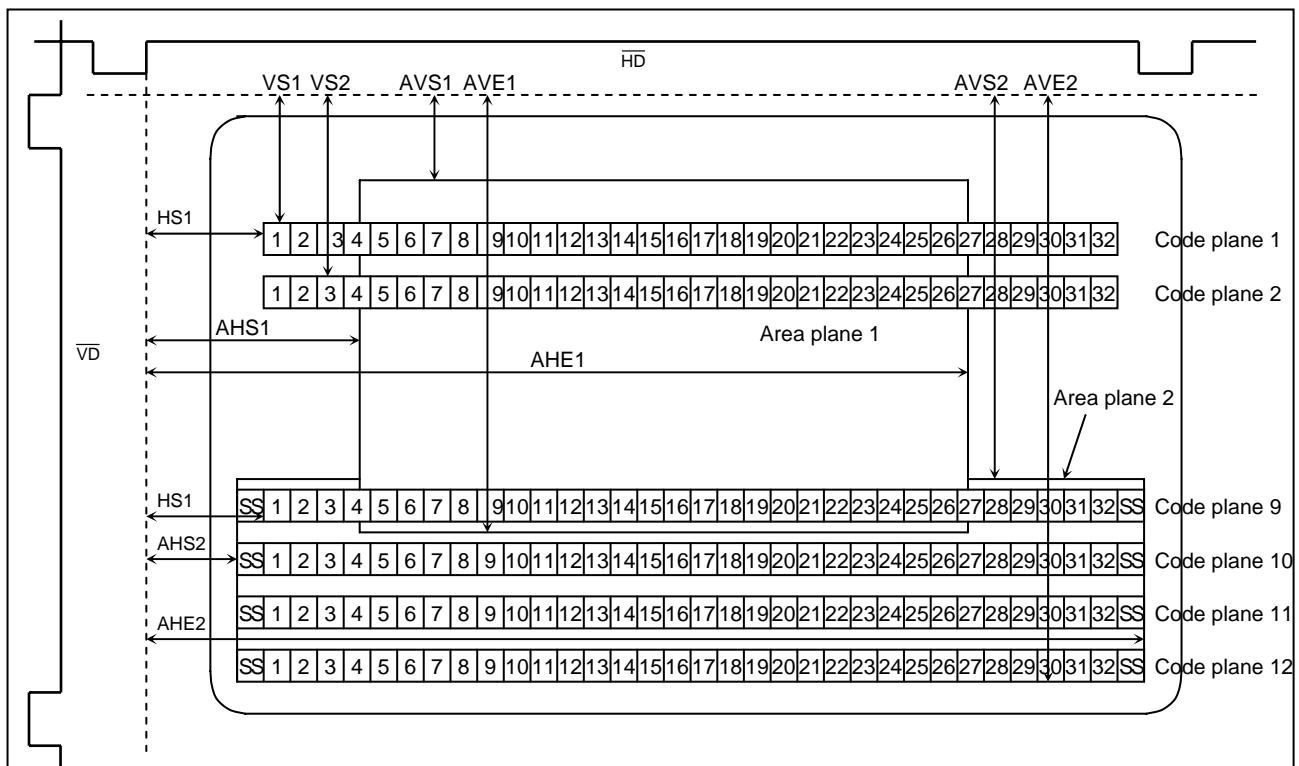

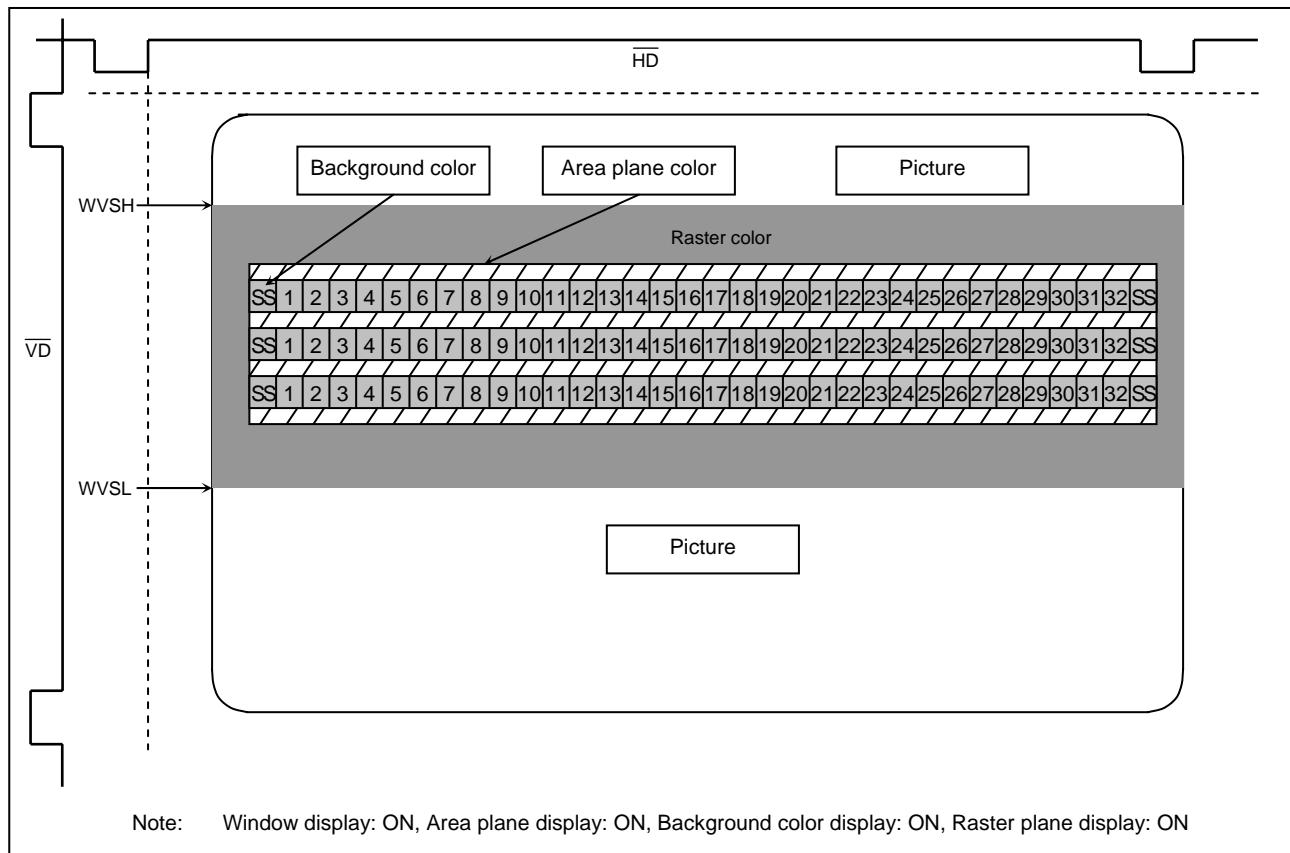

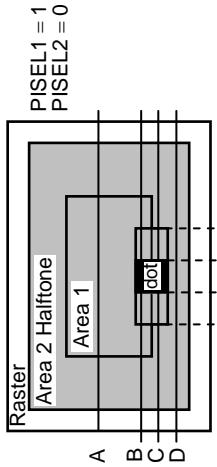

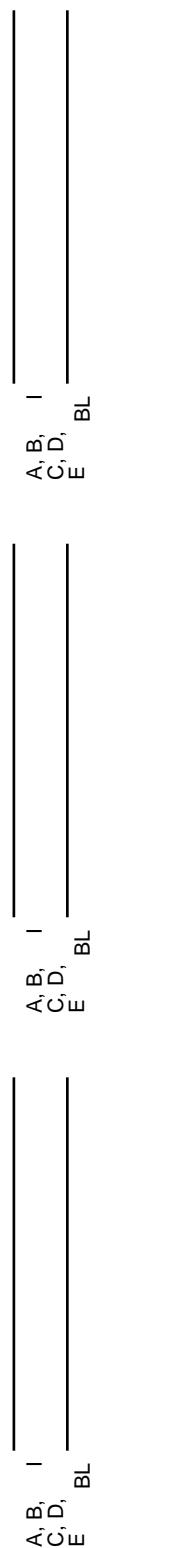

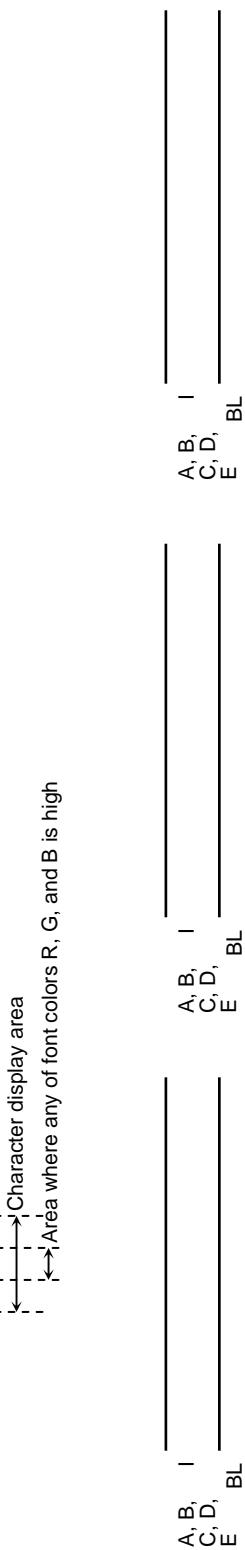

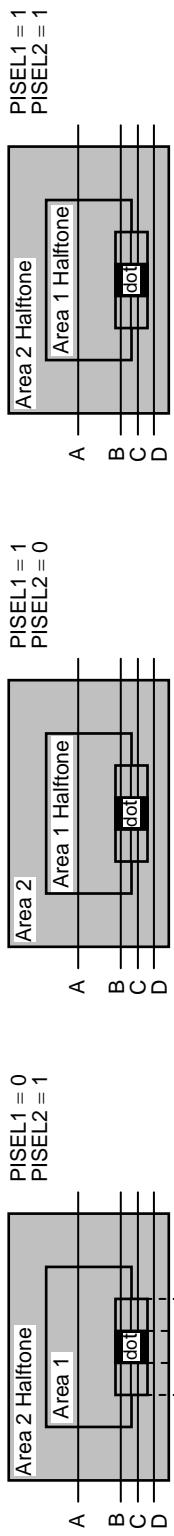

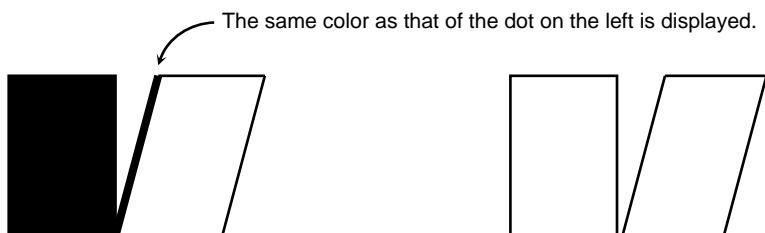

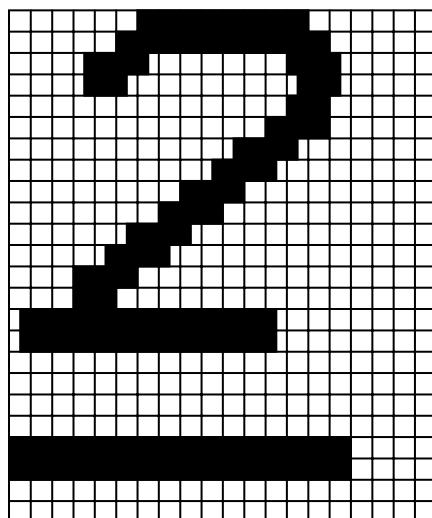

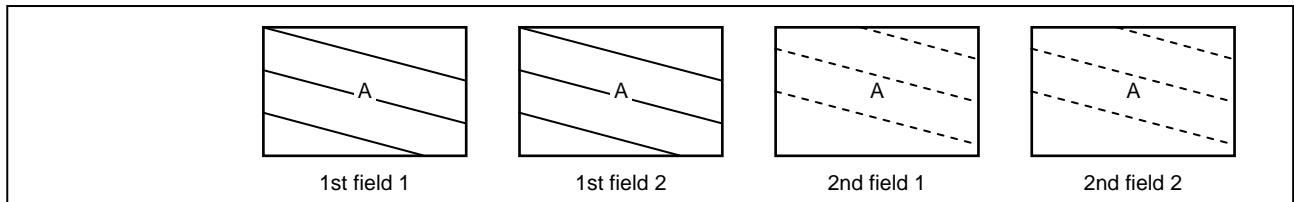

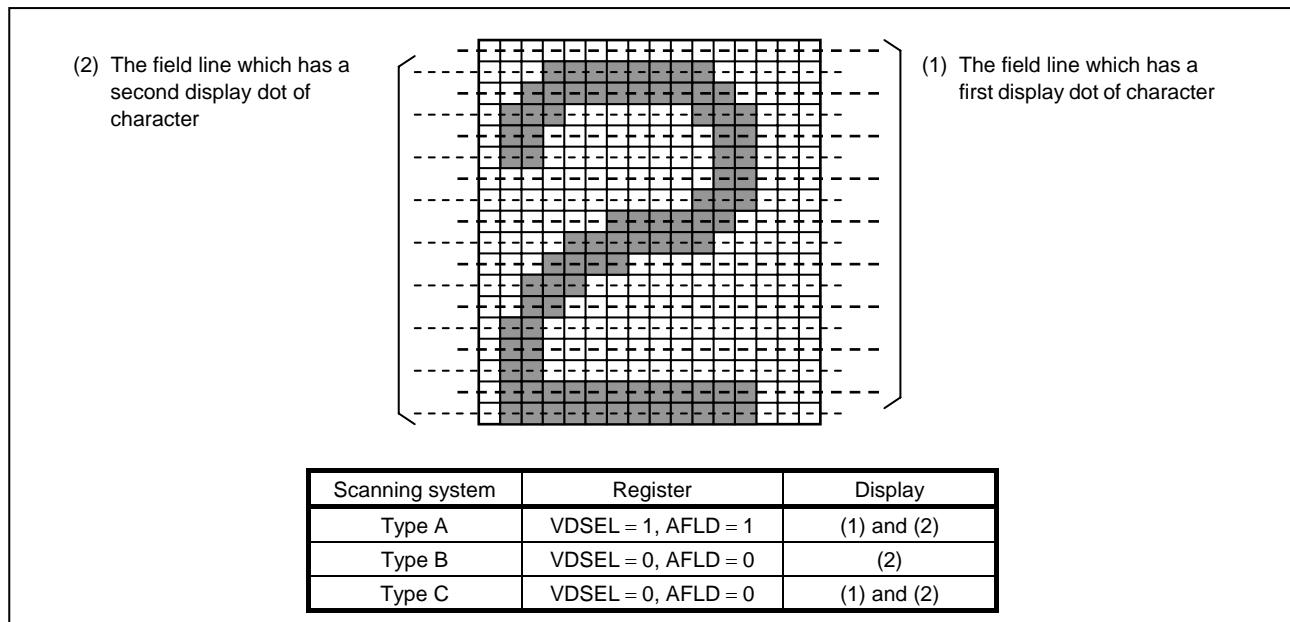

- ◆ On-screen display circuit

- Font ROM characters: Mono font 383 characters, color font 96 characters or mono font 447 characters, color font 64 characters

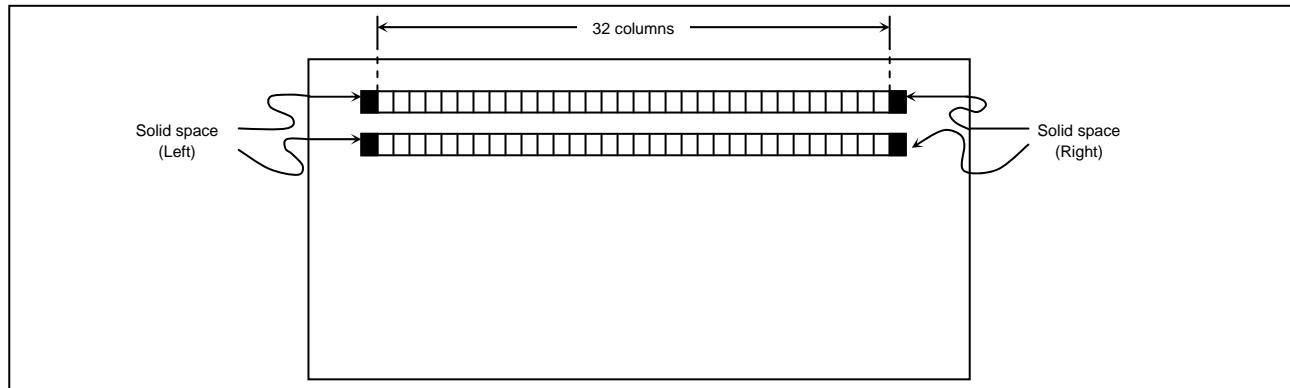

- Characters display: 32 columns × 12 lines

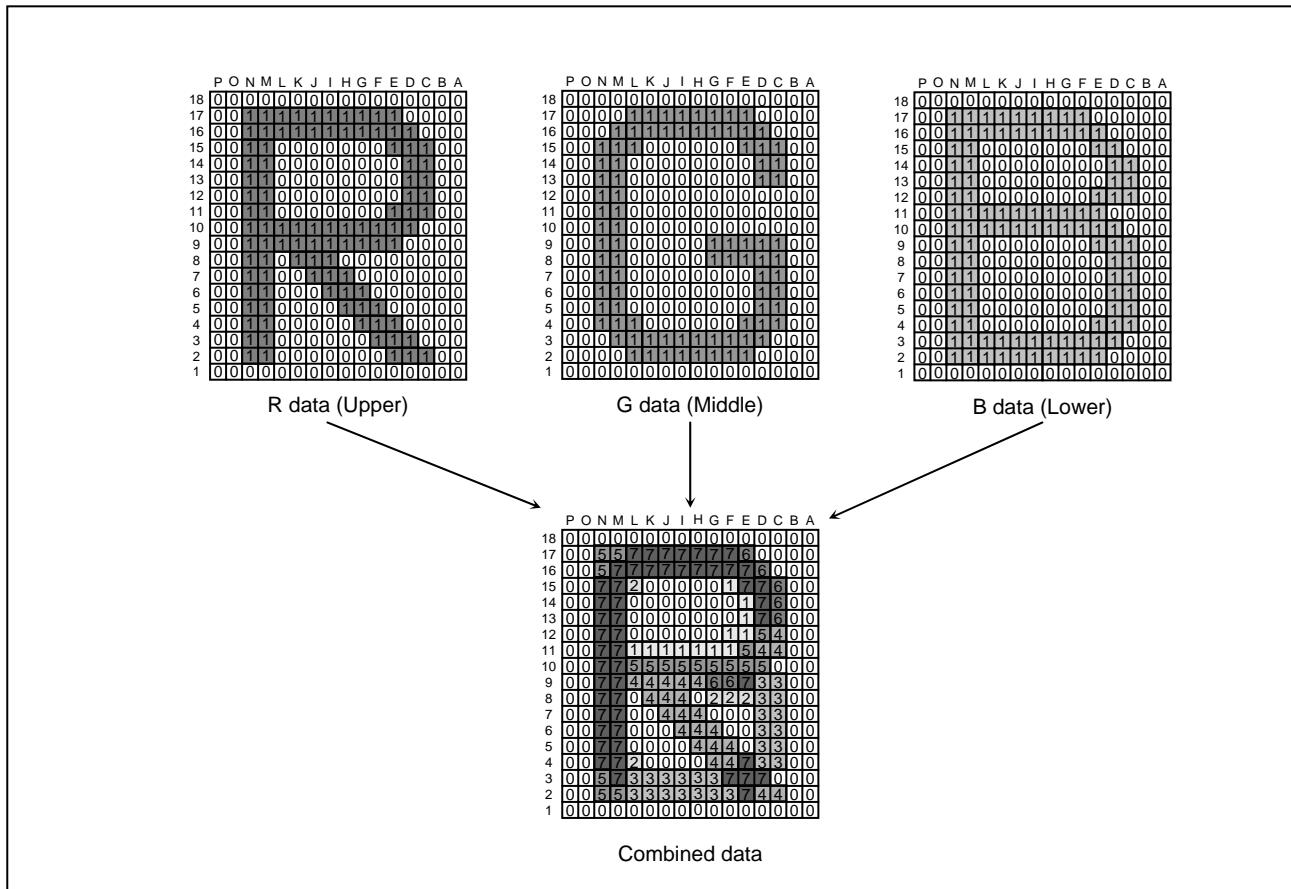

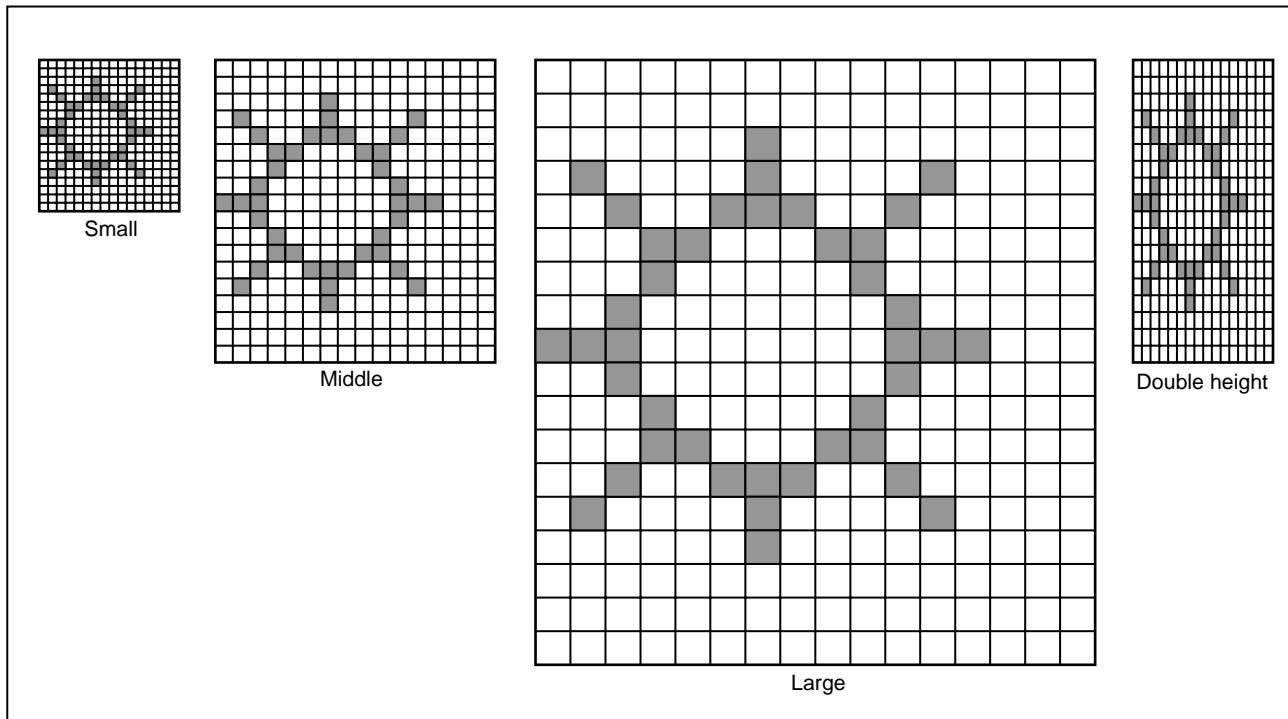

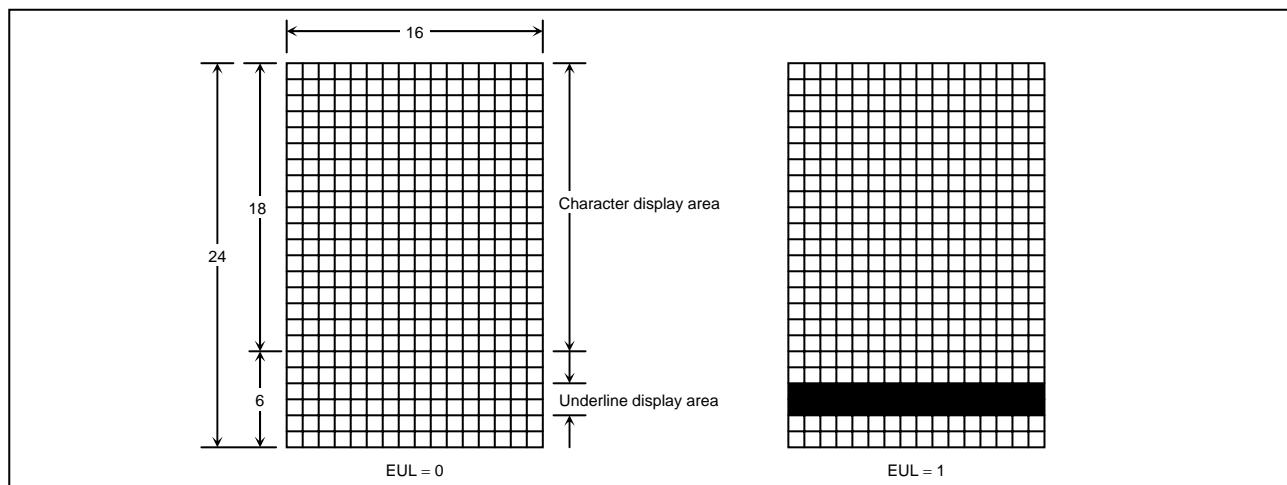

- Composition: 16 × 18 dots

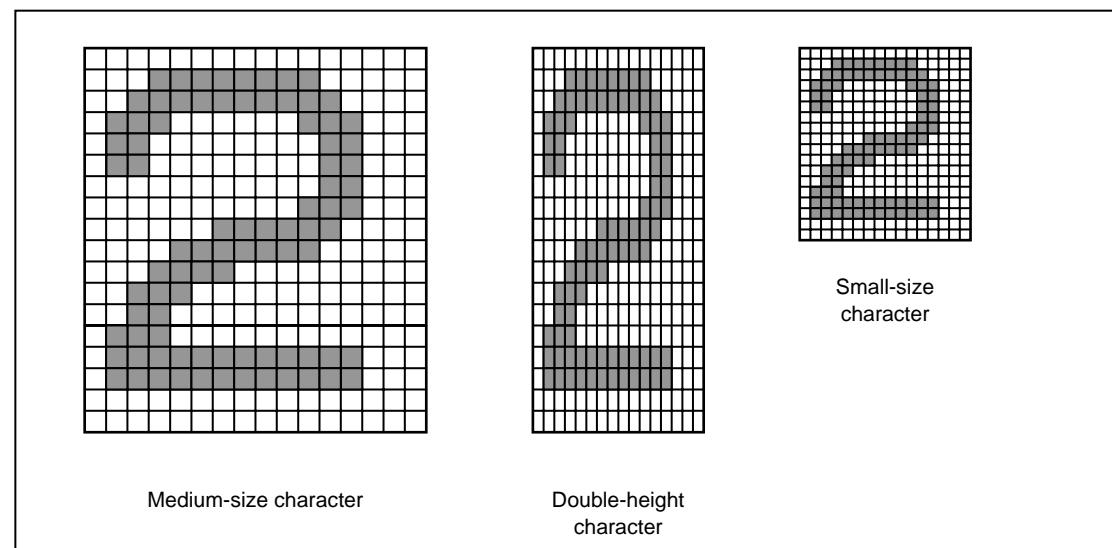

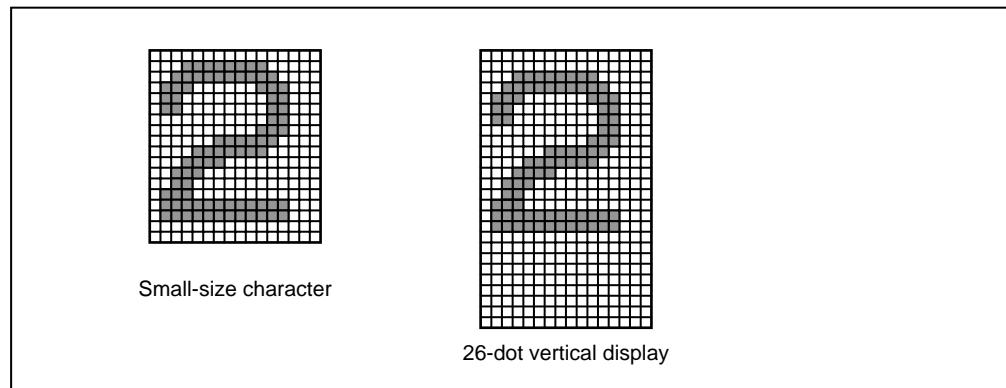

- Size of character: 4 kinds (line by line)

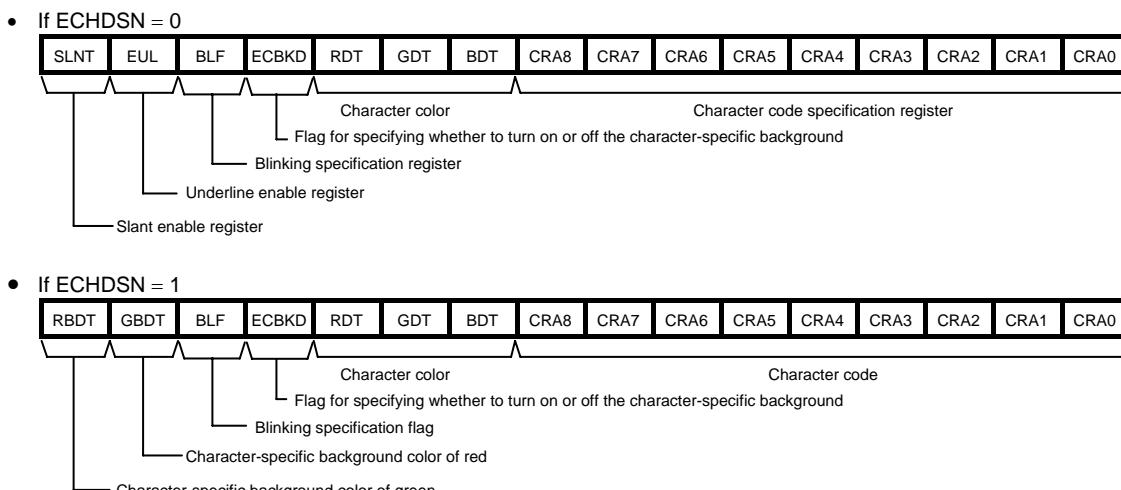

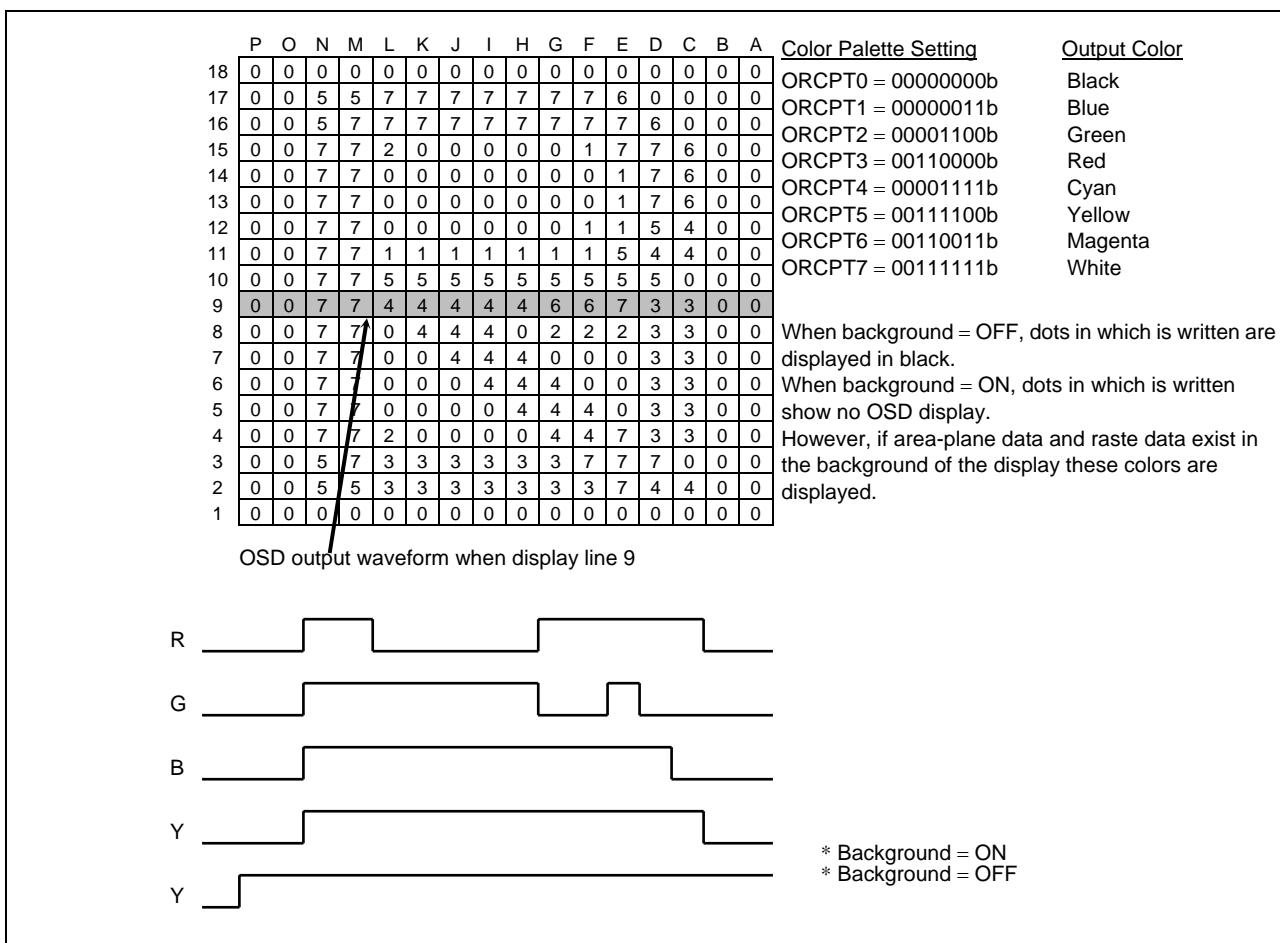

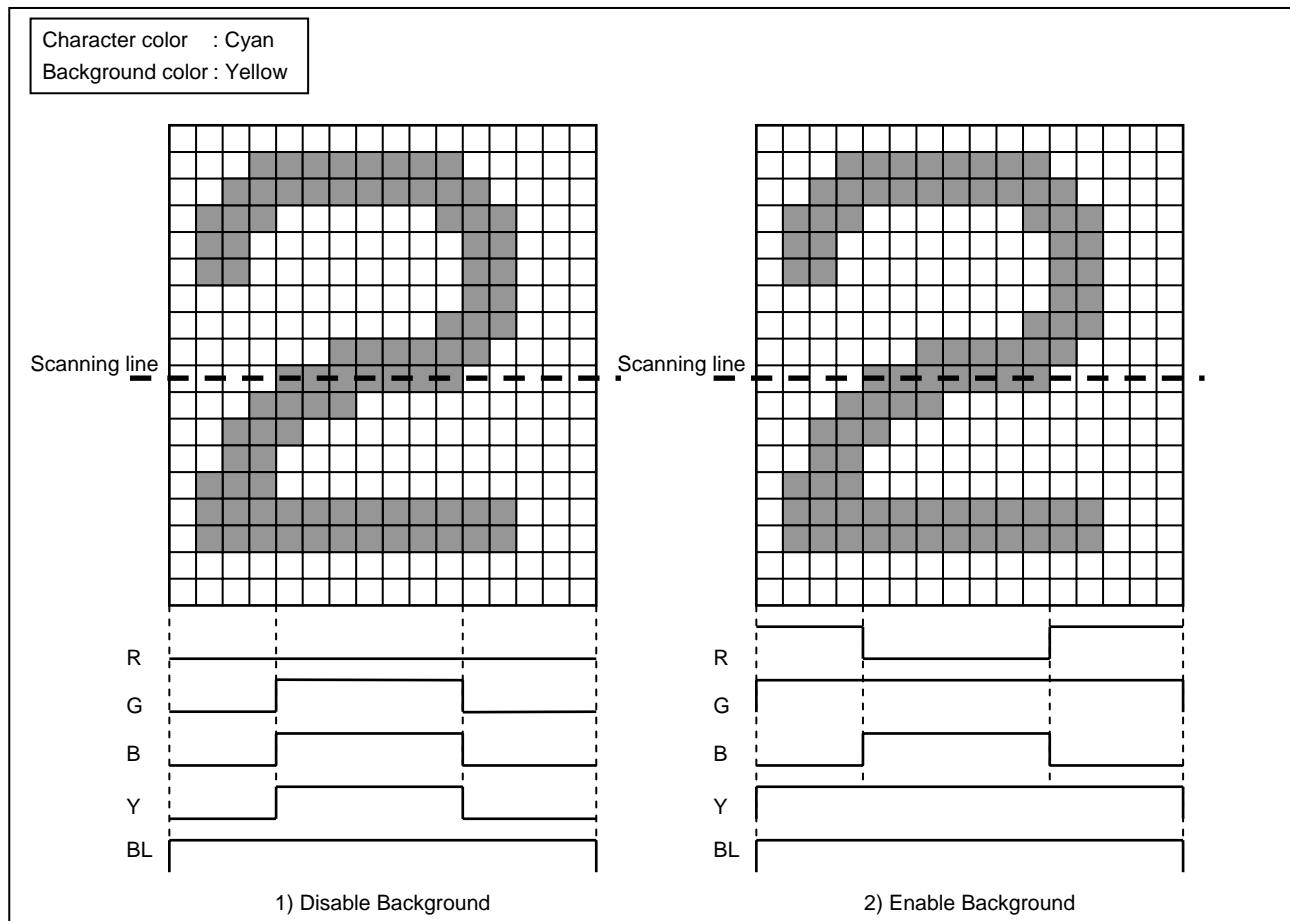

- Color of character: 8 or 27 kinds (character by character)

- Variable display position: Horizontal 256 steps, Vertical 625 steps

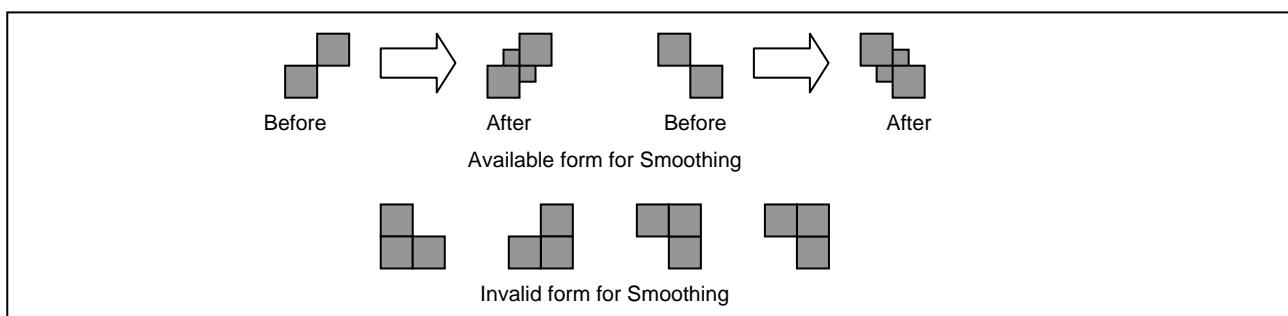

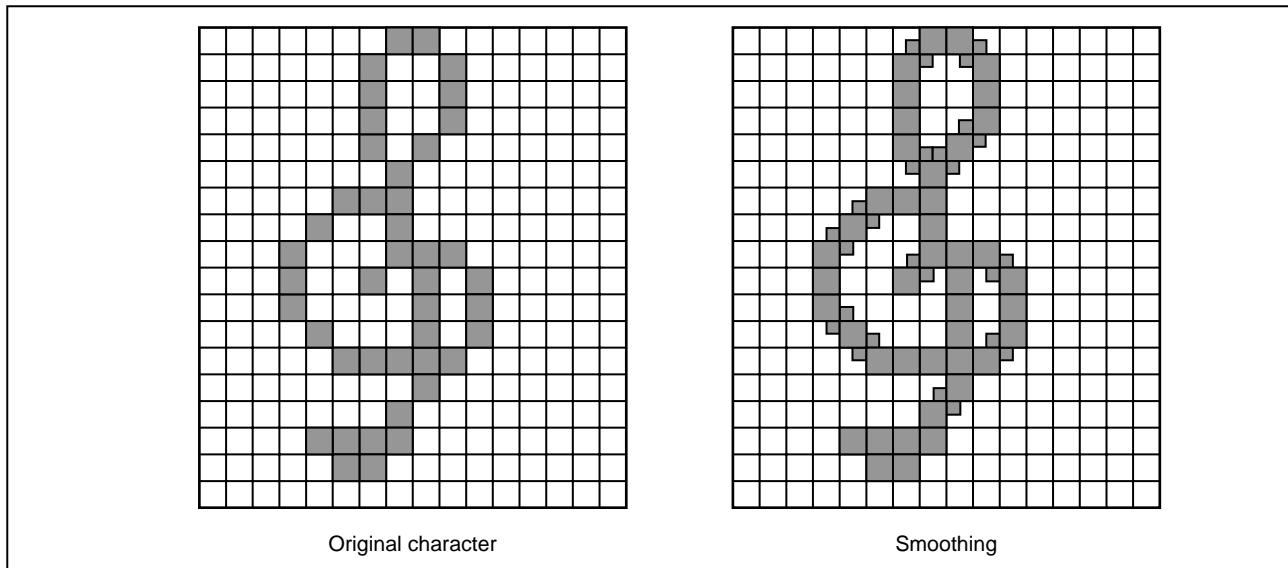

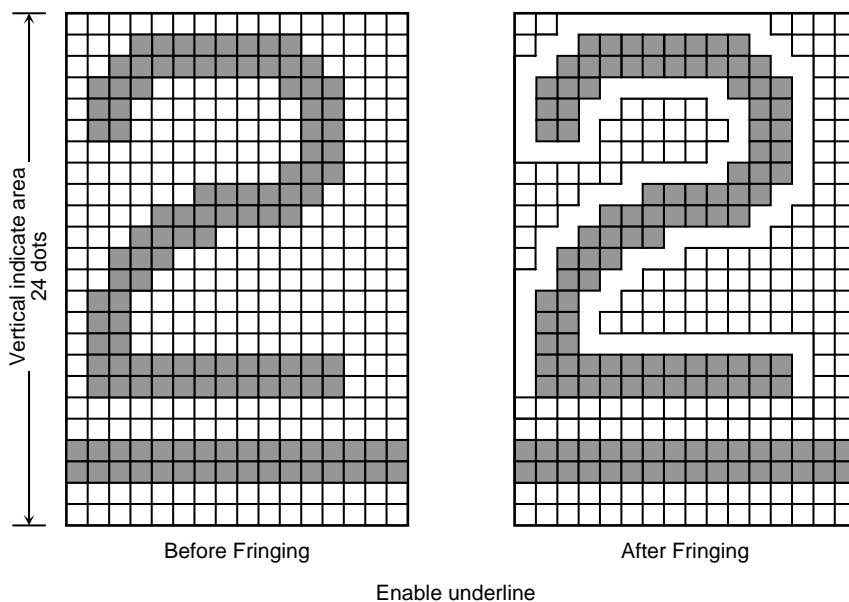

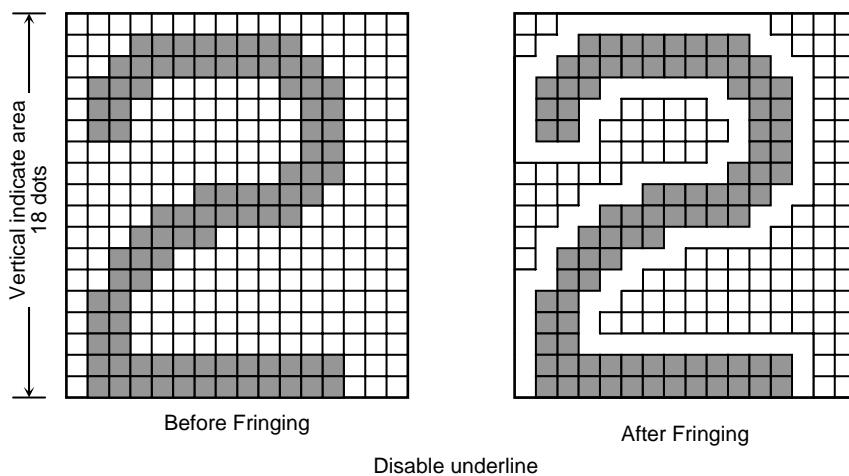

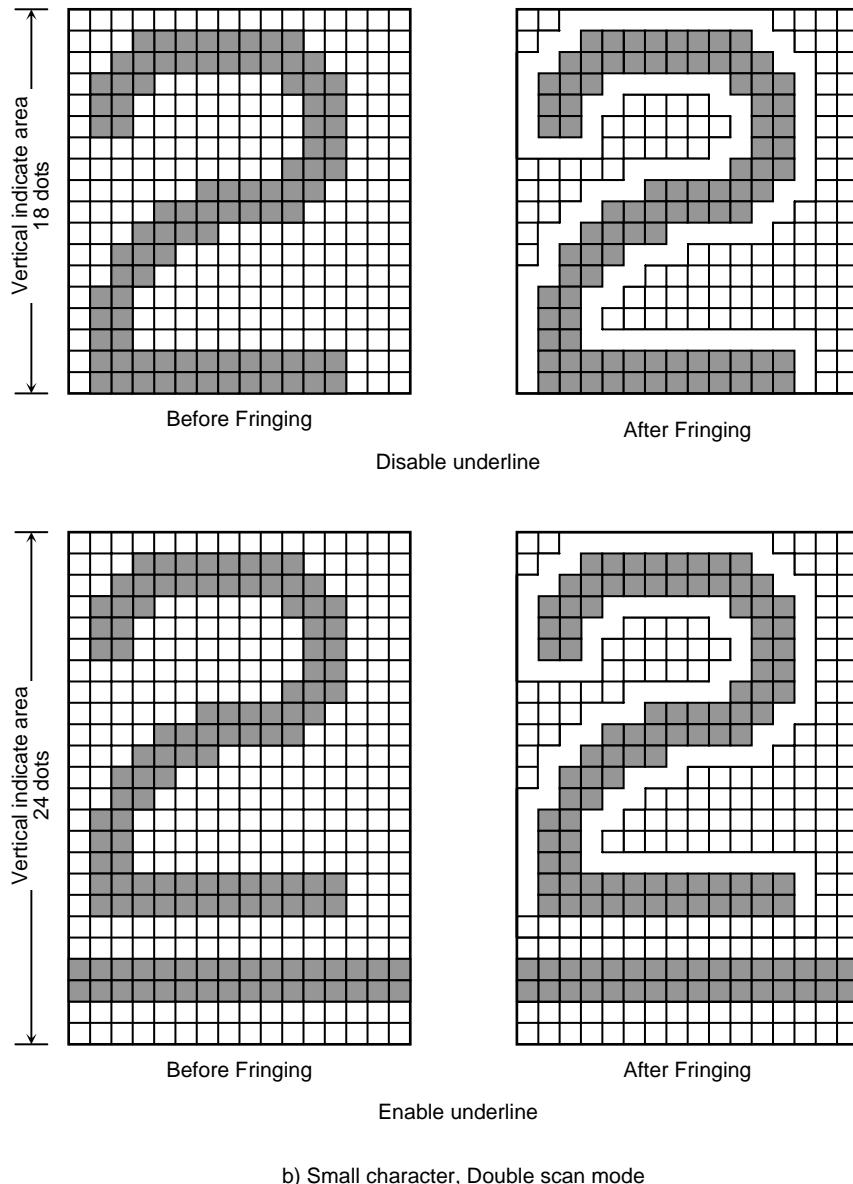

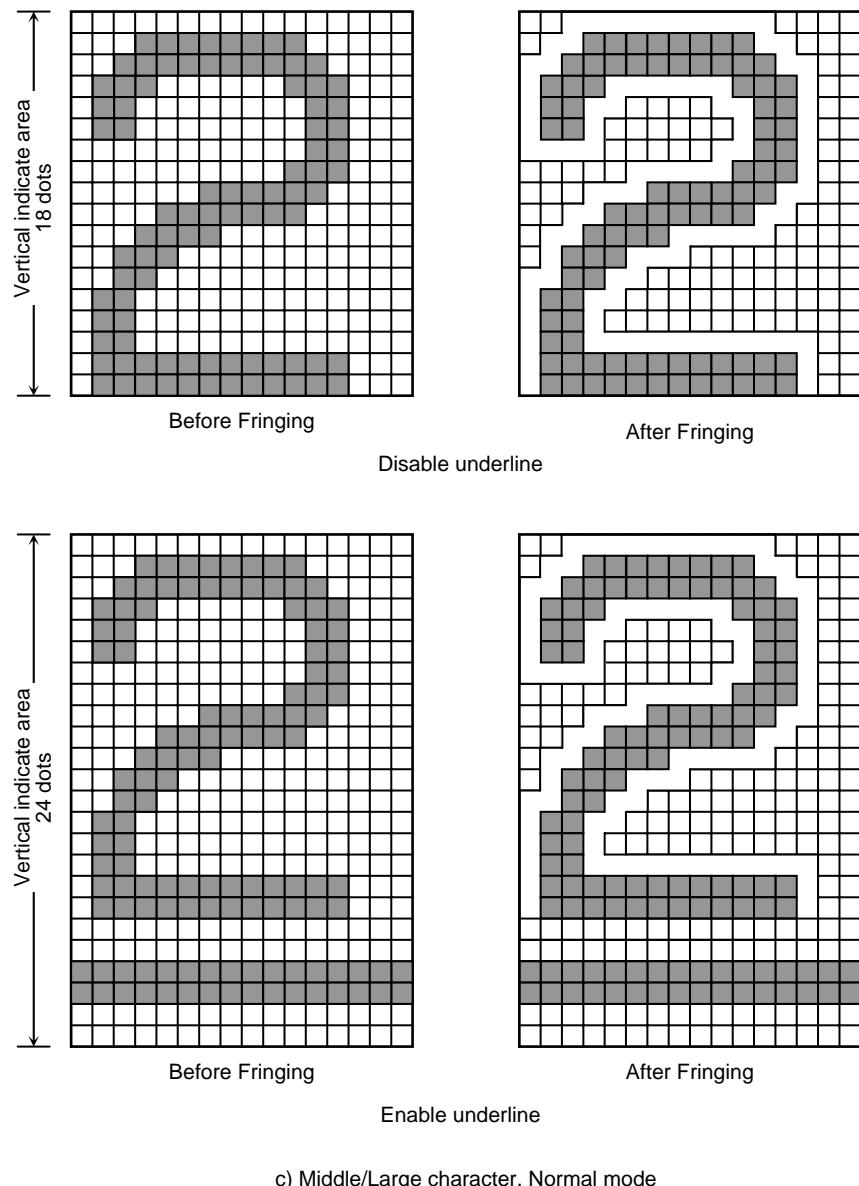

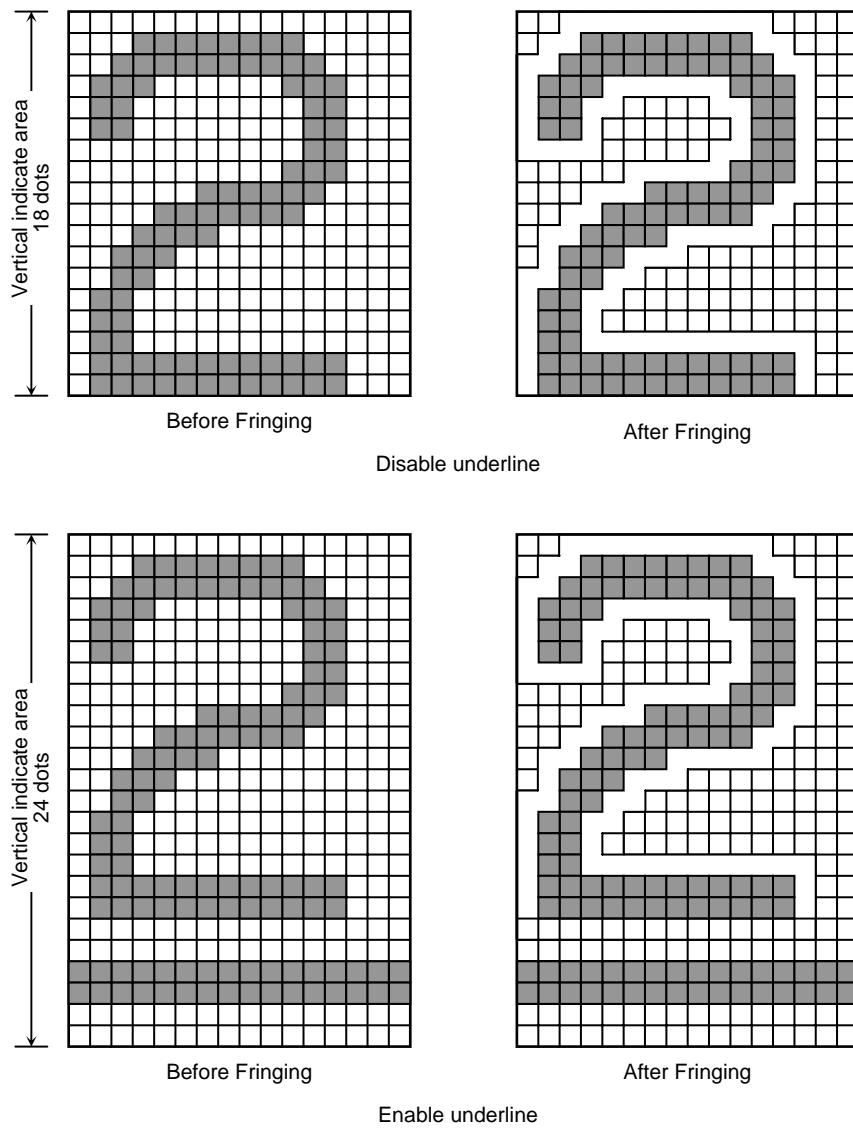

- Fringing, Smoothing, Slant, Underline, Blinking function

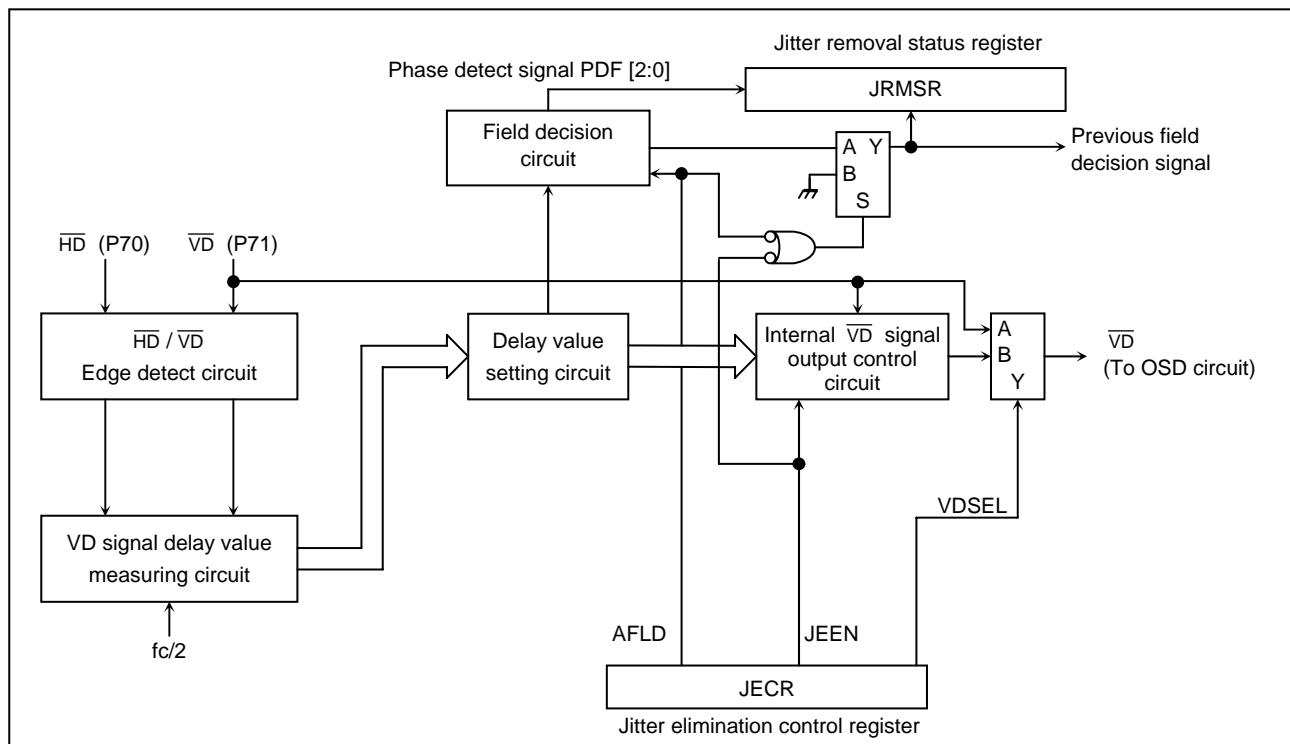

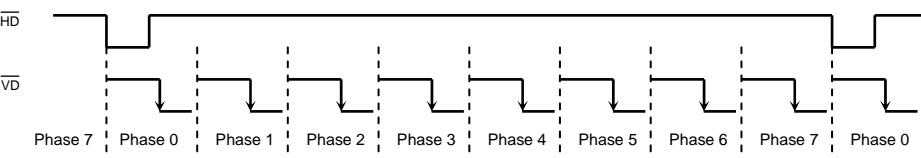

- ◆ Jitter elimination

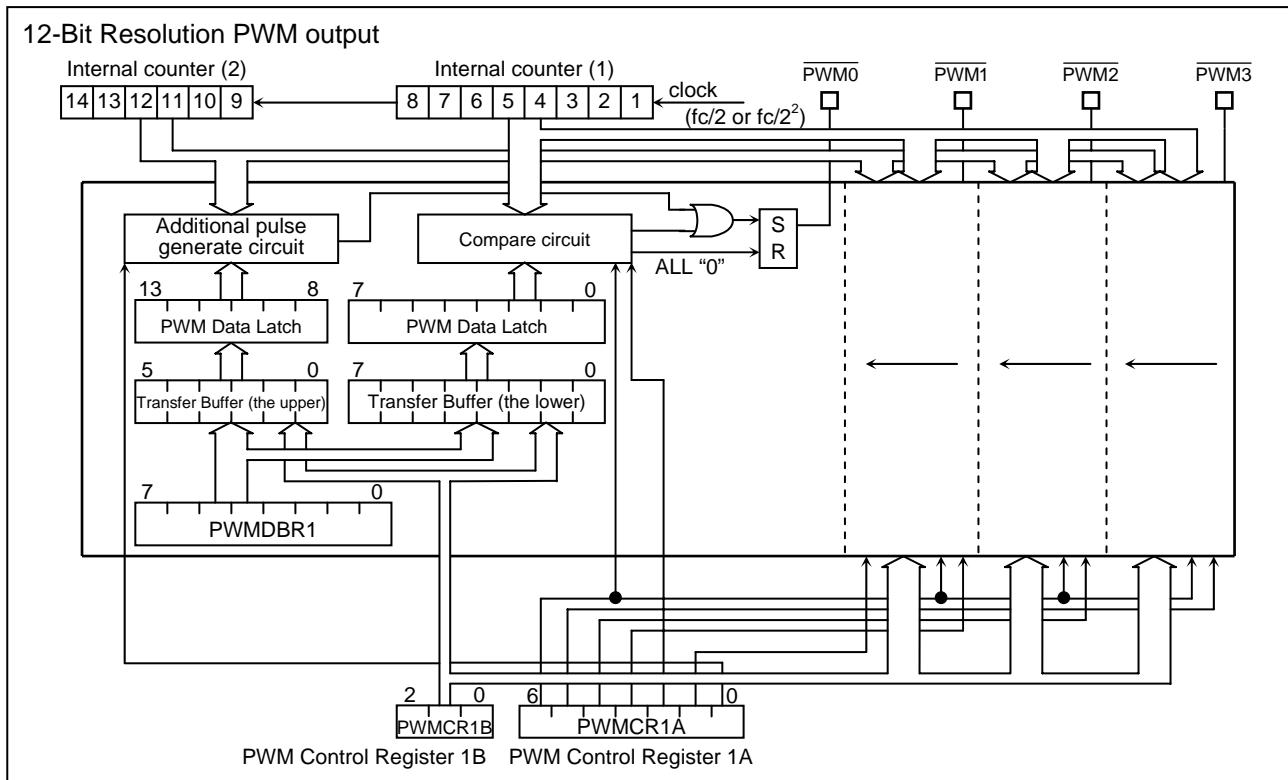

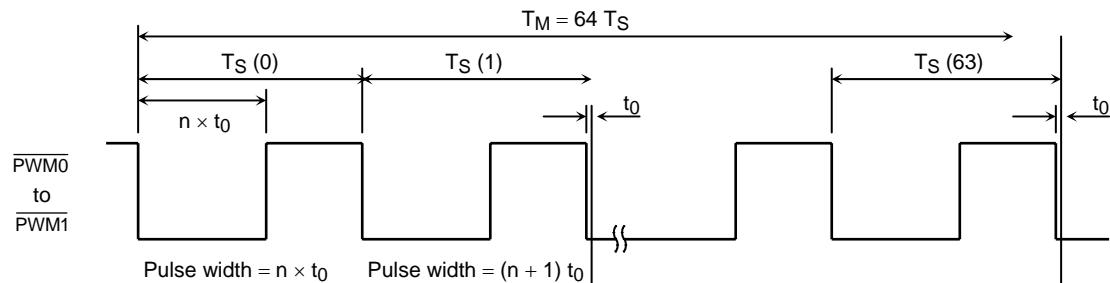

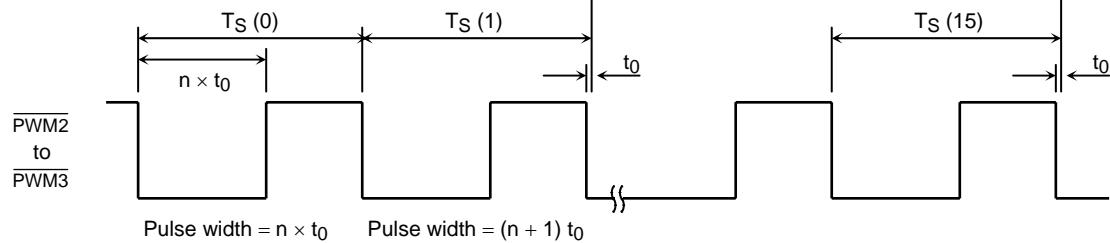

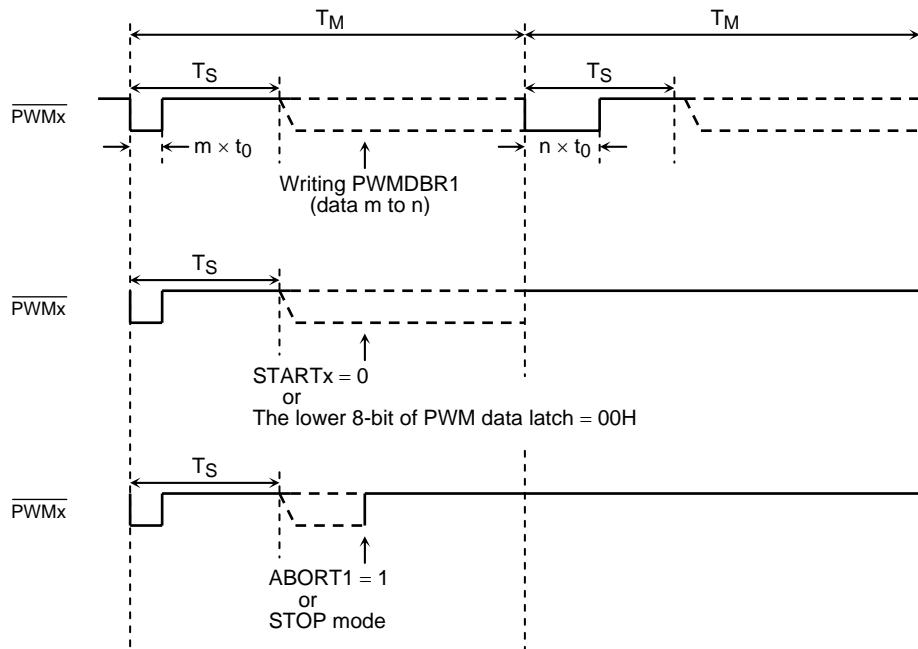

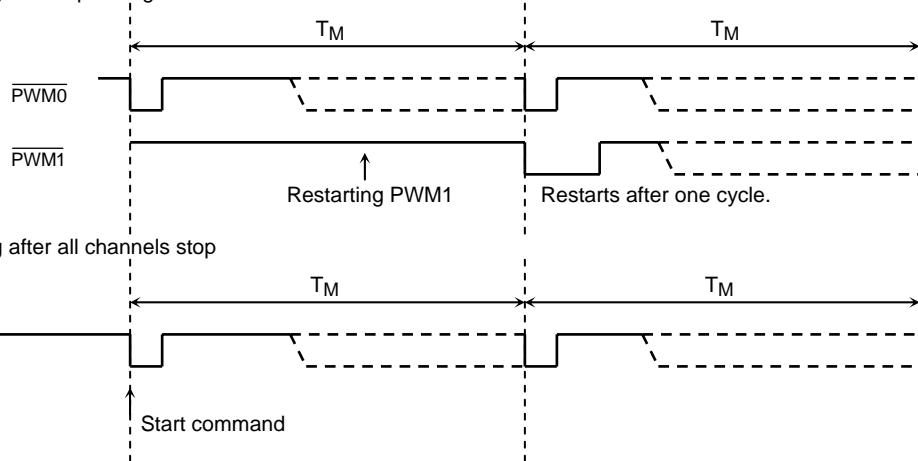

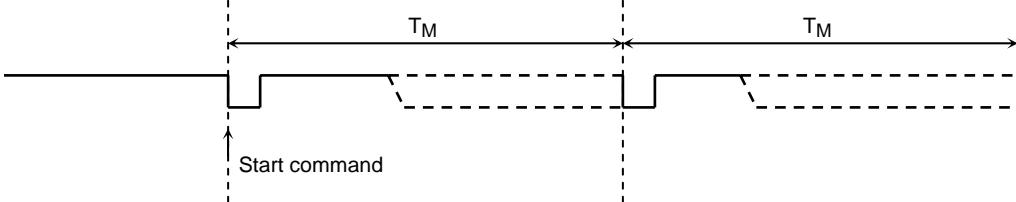

- ◆ DA conversion (Pulse Width Modulation) outputs

- 14/12-bit resolution (2 channels)

- 12-bit resolution (2 channels)

- ◆ 8-bit successive approximate type AD converter with sample and hold

- ◆ High current output: 1 pin (typ. 20 mA)

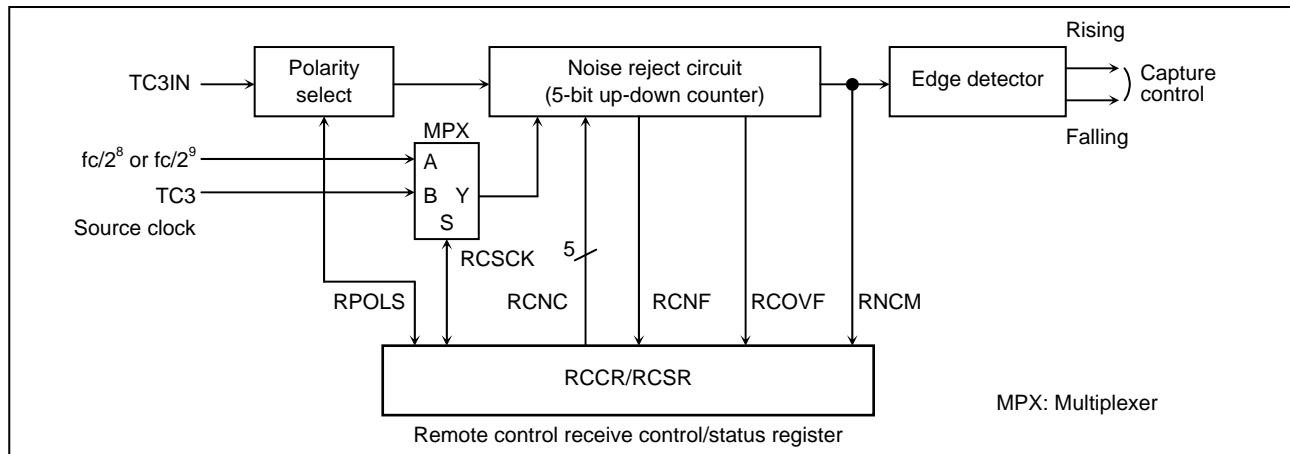

- ◆ Remote control signal preprocessor

- ◆ Two power saving operating modes

- STOP mode: Oscillation stops. Battery/Capacitor back-up. Port output hold/high-impedance.

- IDLE mode: CPU stops, and Peripherals operate using high-frequency clock. Release by interrupts.

- ◆ Operating voltage: 4.5 to 5.5 V at 16 MHz

- ◆ Emulation POD: BM88CS34N0A-M15

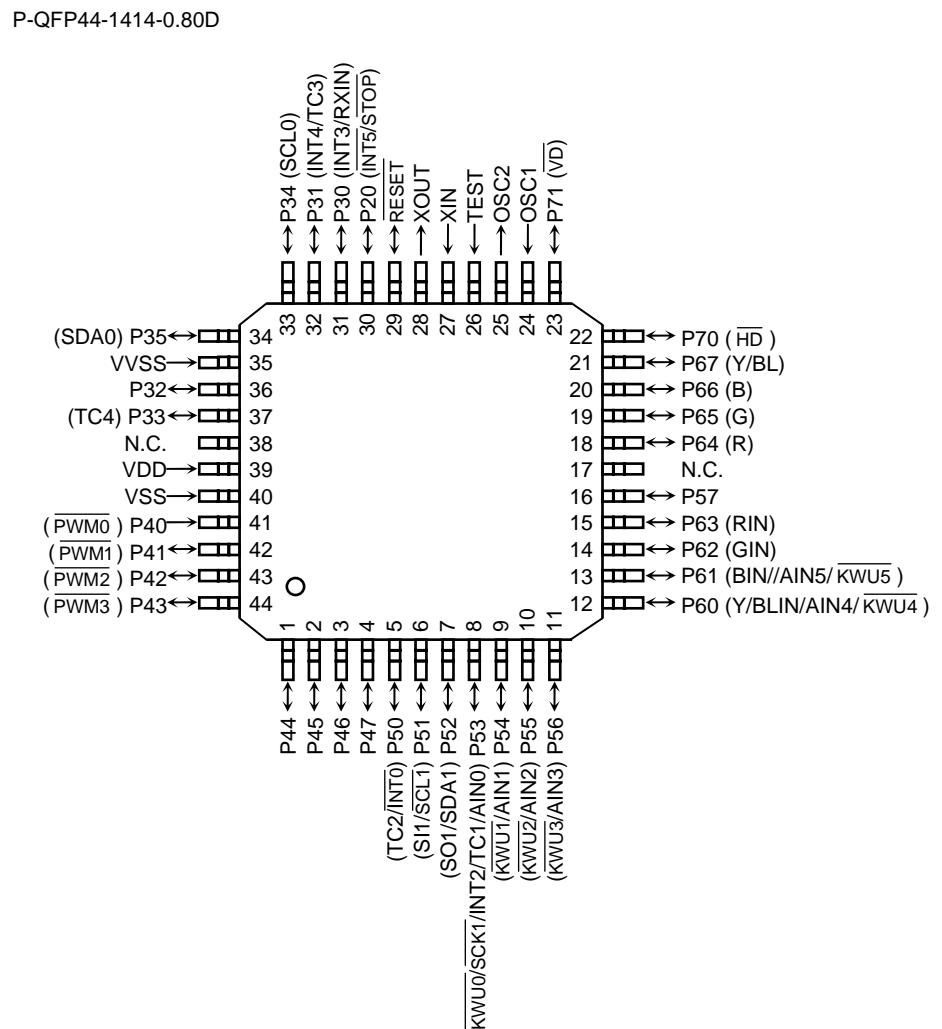

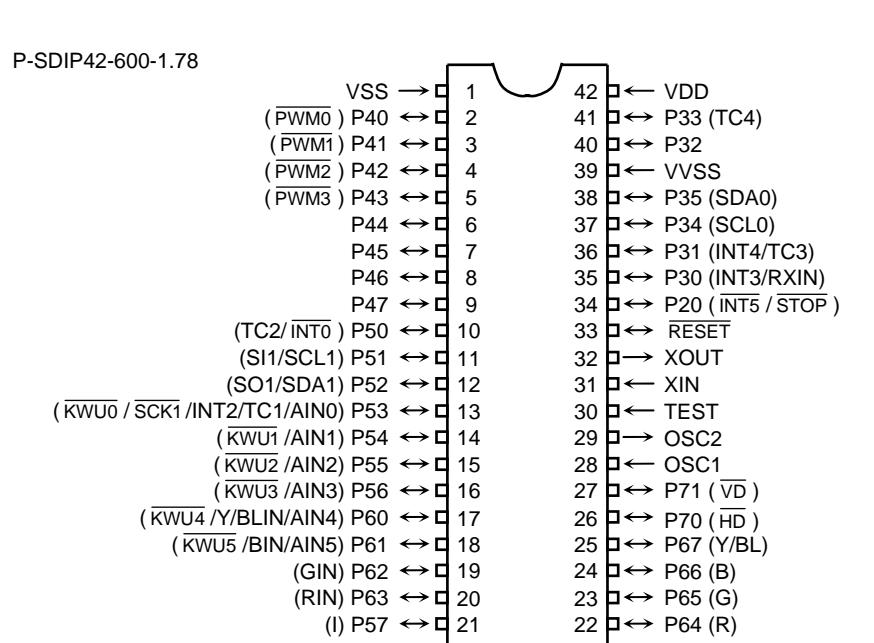

## Pin Assignments

## Pin Functions (1/2)

| Pin Name                                 | I/O                                          | Function                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                             |

|------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

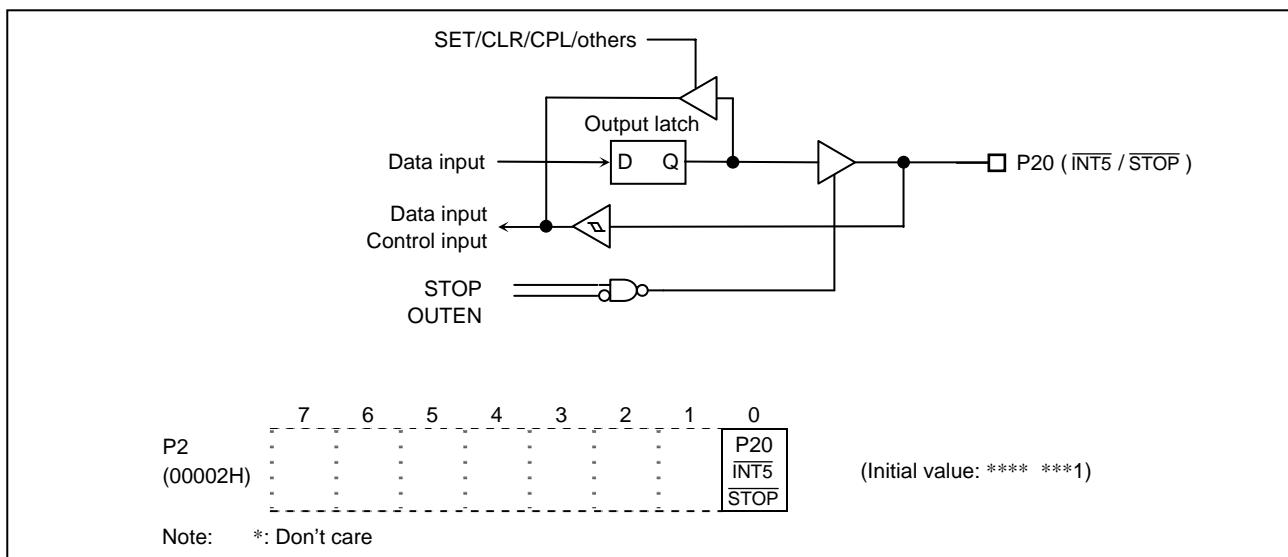

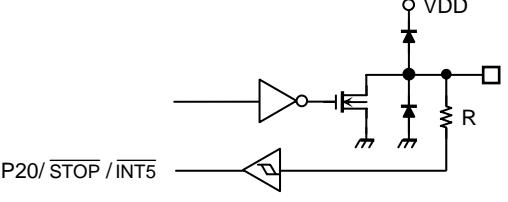

| P20 ( INT5 / STOP )                      | I/O (Input)                                  | 1-bit input/output port with latch. When used as an input port, the latch must be set to "1".                                                                                                                                                                                                                                                                           | External interrupt input 5 or STOP mode release signal input                                                                                |

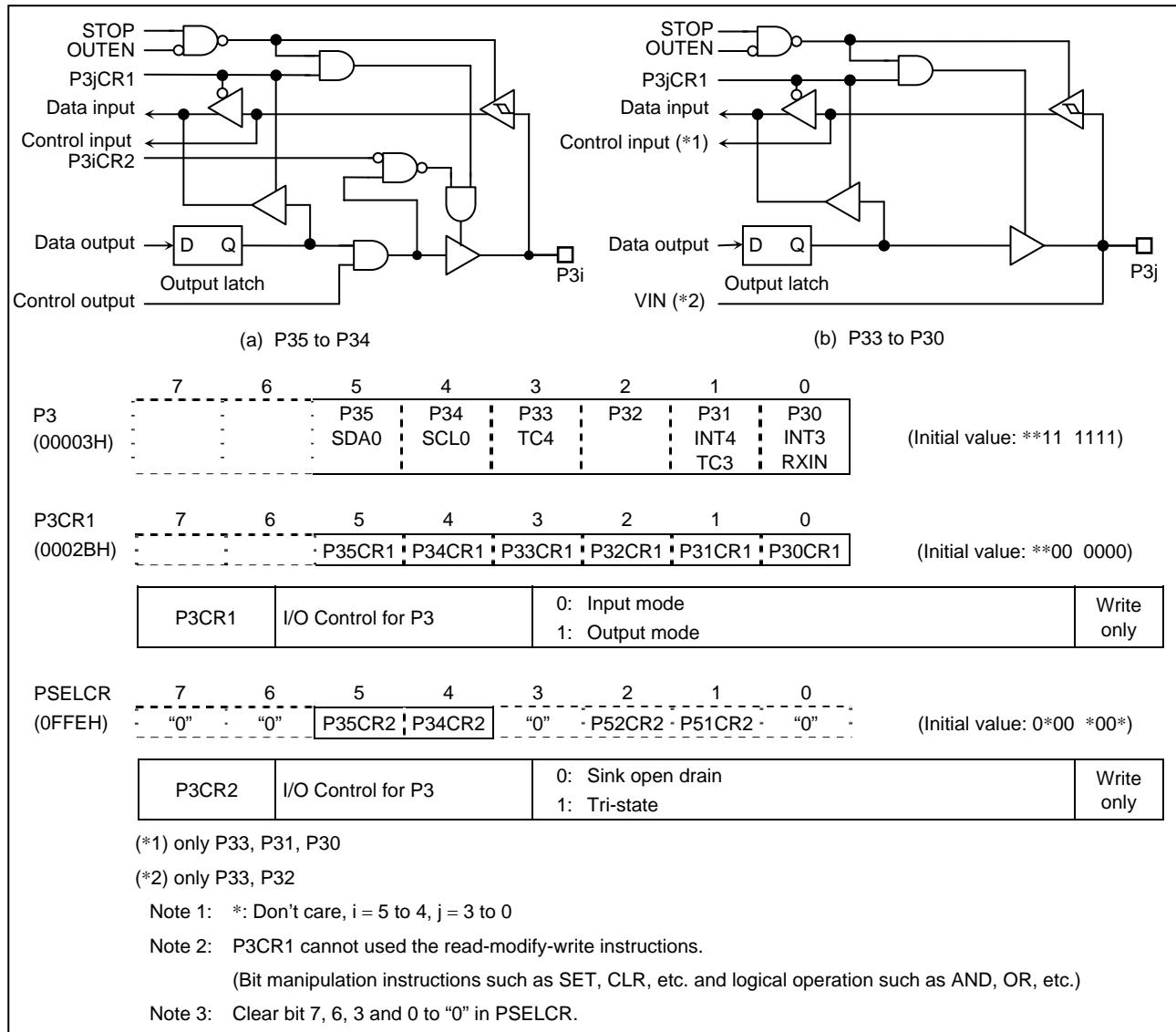

| P35 ( SDA0 )                             | I/O (Input/Output)                           | 6-bit programmable input/output port. Each bit of these ports can be individually configured as an input or an output under software control. During reset, all bits are configured as inputs. When used as a serial bus interface input/output, the latch must be set to "1".                                                                                          | I <sup>2</sup> C bus serial data input/output 0                                                                                             |

| P34 ( SCL0 )                             | I/O (Input/Output)                           |                                                                                                                                                                                                                                                                                                                                                                         | I <sup>2</sup> C bus serial clock input/output 0                                                                                            |

| P33 ( TC4 )                              | I/O (Input)                                  |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |

| P32                                      | I/O                                          |                                                                                                                                                                                                                                                                                                                                                                         | Video signal input 1 or Composite sync input                                                                                                |

| P31 ( INT4/TC3 )                         | I/O (Input)                                  |                                                                                                                                                                                                                                                                                                                                                                         | External interrupt input 4 or Timer/Counter input 3                                                                                         |

| P30 ( INT3/RXIN )                        | I/O (Input)                                  |                                                                                                                                                                                                                                                                                                                                                                         | External interrupt input 3 or Remote control signal preprocessor input                                                                      |

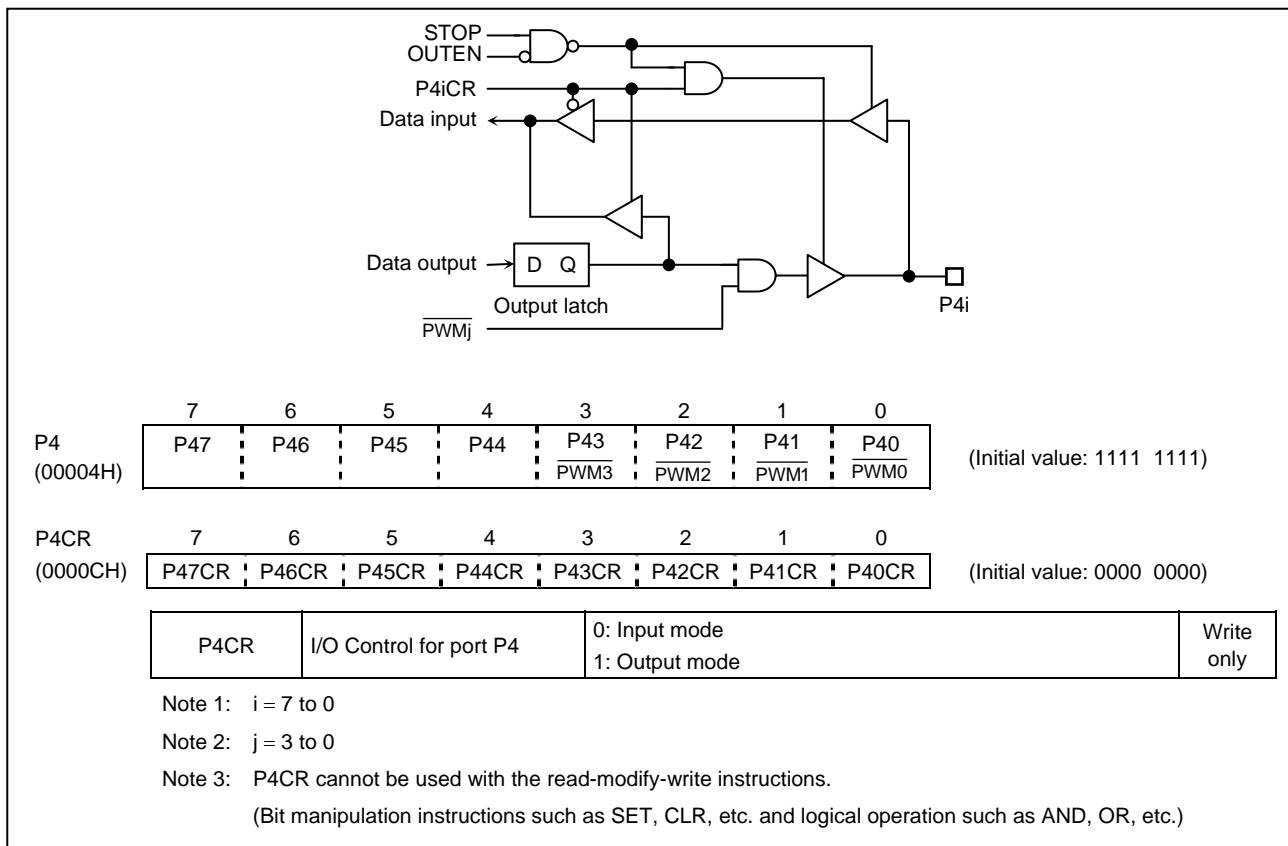

| P47                                      | I/O                                          | 8-bit programmable input/output port. Each bit of these ports can be individually configured as an input or an output under software control. During reset, all bits are configured as inputs.                                                                                                                                                                          |                                                                                                                                             |

| P46                                      | I/O                                          |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |

| P45                                      | I/O                                          |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |

| P44                                      | I/O                                          |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |

| P43 ( PWM3 )                             | I/O (Output)                                 |                                                                                                                                                                                                                                                                                                                                                                         | 12-bit DA conversion (PWM) outputs                                                                                                          |

| P42 ( PWM2 )                             | I/O (Output)                                 |                                                                                                                                                                                                                                                                                                                                                                         | 14/12-bit DA conversion (PWM) outputs                                                                                                       |

| P41 ( PWM1 )                             | I/O (Output)                                 |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |

| P40 ( PWM0 )                             | I/O (Output)                                 |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |

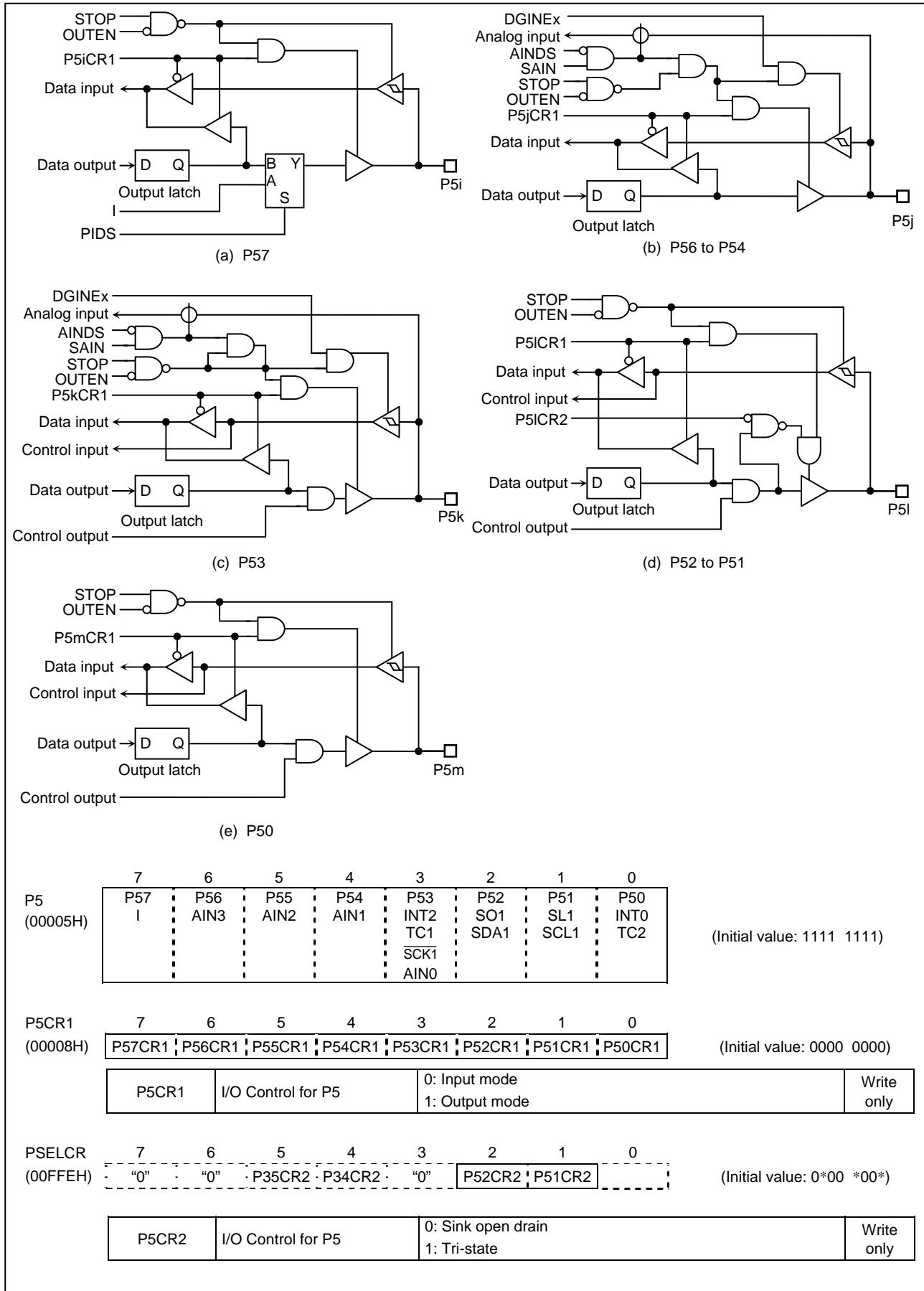

| P57 (I)                                  | I/O (Output)                                 | 8-bit programmable input/output port. Each bit of these ports can be individually configured as an input or an output under software control. During reset, all bits are configured as inputs. When used as a serial bus interface input/output, the latch must be set to "1".                                                                                          | Translucent signal output                                                                                                                   |

| P56 ( KWU3 /AIN3 )                       | I/O (Input)                                  |                                                                                                                                                                                                                                                                                                                                                                         | Key on wake-up inputs or AD converter analog inputs                                                                                         |

| P55 ( KWU2 /AIN2 )                       | I/O (Input)                                  |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |

| P54 ( KWU1 /AIN1 )                       | I/O (Input)                                  |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |

| P53<br>( KWU0 /AIN0/TC1<br>/INT2/ SCK1 ) | I/O<br>(Input/Output/Input<br>/Input/Output) |                                                                                                                                                                                                                                                                                                                                                                         | Key on wake-up input or AD converter analog input or Timer/counter input 1 or External interrupt input 2 or SIO serial clock input/output 1 |

| P52 ( SDA1/SO1 )                         | I/O<br>(Input/Output/Output)                 |                                                                                                                                                                                                                                                                                                                                                                         | I <sup>2</sup> C bus serial data Input/Output 1 or SIO serial data output 1                                                                 |

| P51 ( SCL1/SI1 )                         | I/O<br>(Input/Output/Input)                  |                                                                                                                                                                                                                                                                                                                                                                         | I <sup>2</sup> C bus serial data Input/Output 1 or SIO serial data input 1                                                                  |

| P50 ( TC2/ INT0 )                        | I/O<br>(Input/Input)                         |                                                                                                                                                                                                                                                                                                                                                                         | Timer/Counter input 2 or External interrupt input 0                                                                                         |

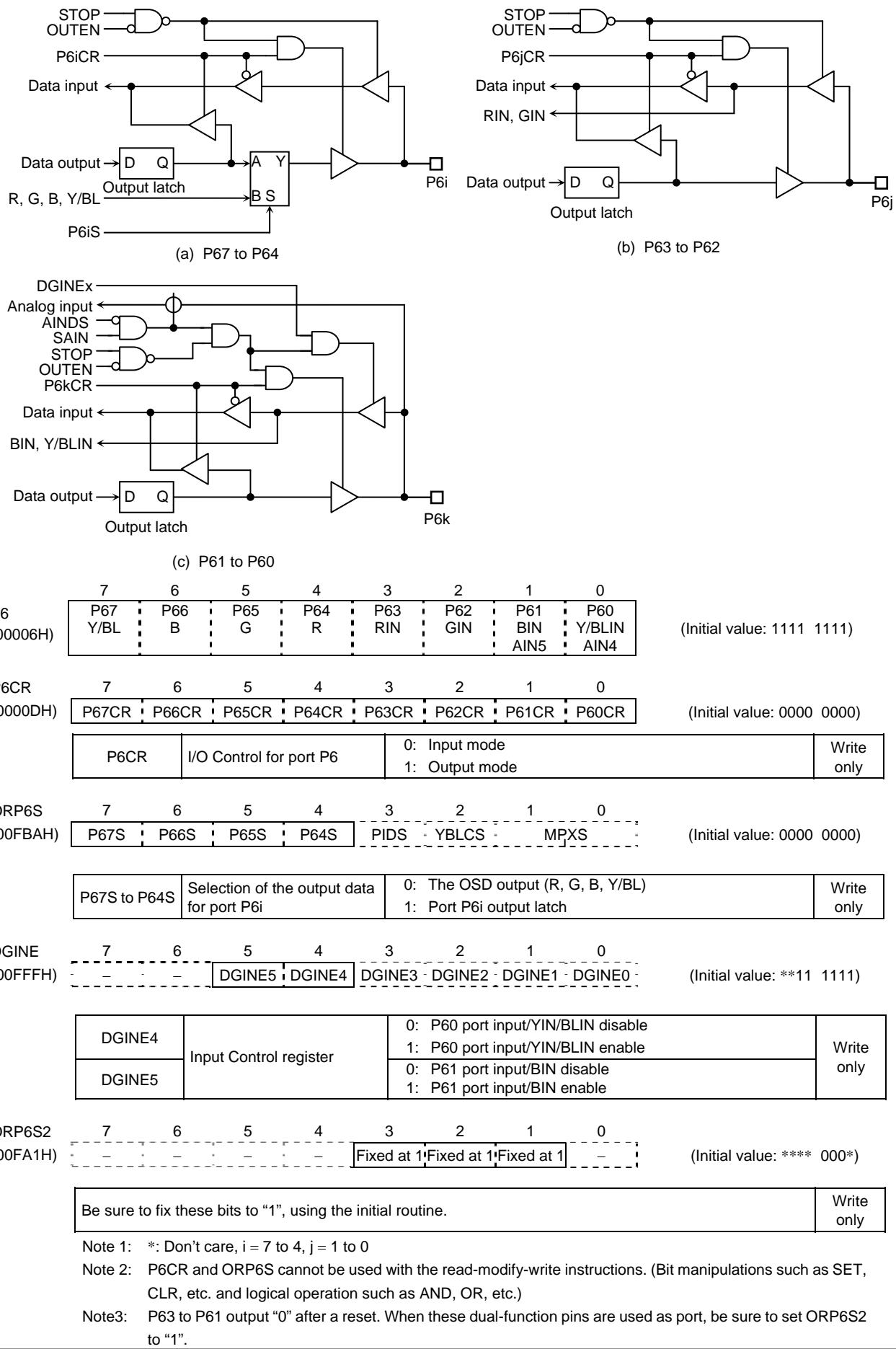

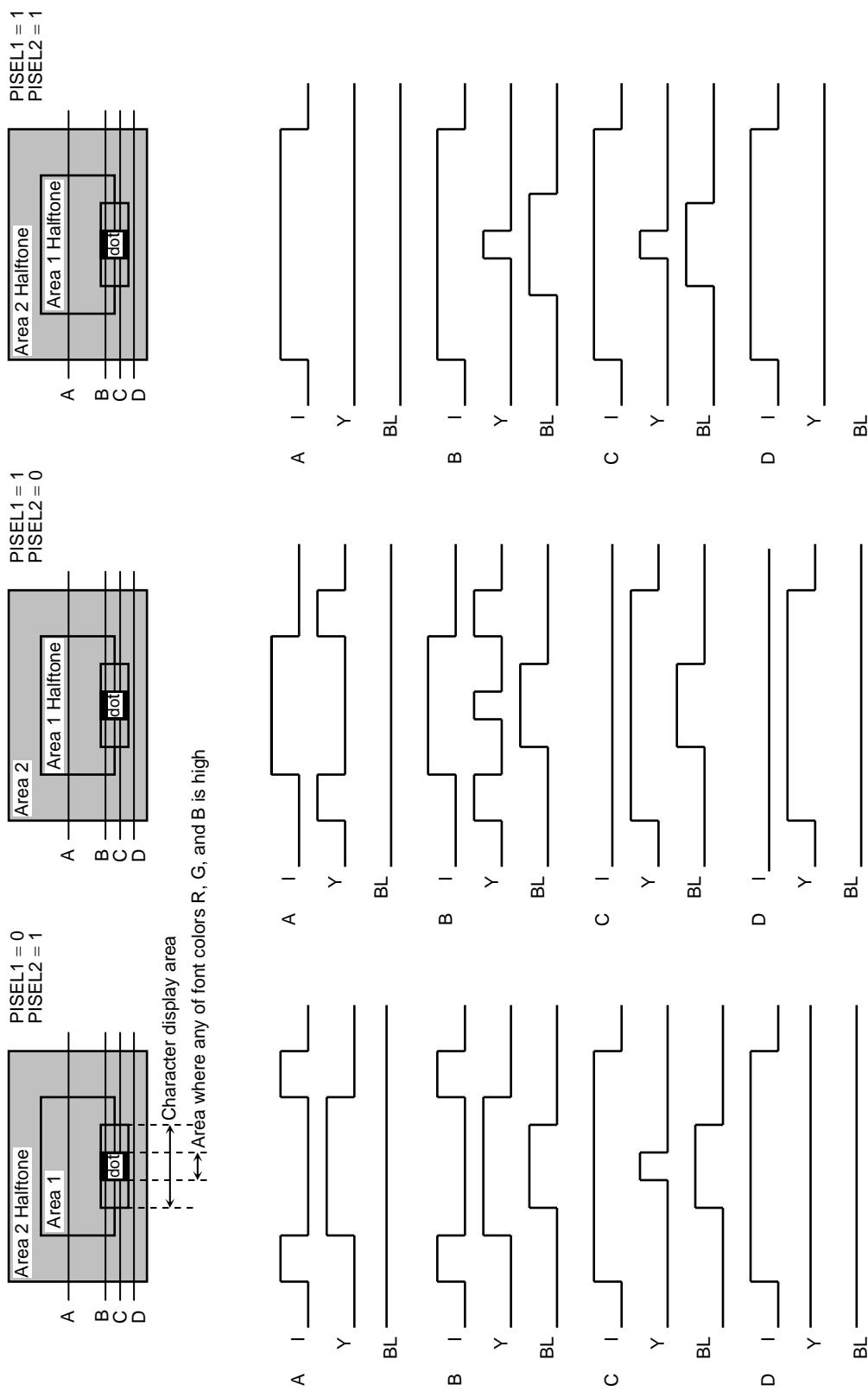

| P67 (Y/BL)                               | I/O (Output)                                 |                                                                                                                                                                                                                                                                                                                                                                         | Y or BL output                                                                                                                              |

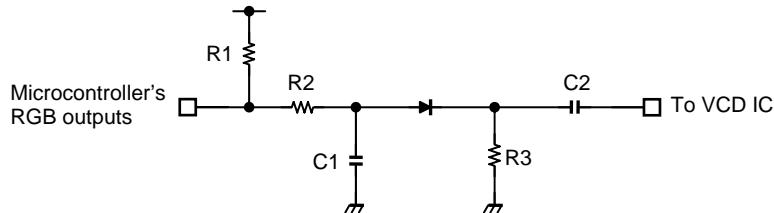

| P66 (B)                                  | I/O (Output)                                 | 8-bit programmable input/output port. (P67 to 61: Tri-State, P60: High current output) Each bit of these ports can be individually configured as an input or an output under software control. During reset, all bits are configured as inputs. When used P64 to P67 as port, each bit of the P6 port data selection register (bit 7 to 4 in ORP6S) must be set to "1". | R/G/B outputs                                                                                                                               |

| P65 (G)                                  | I/O (Output)                                 |                                                                                                                                                                                                                                                                                                                                                                         | R input                                                                                                                                     |

| P64 (R)                                  | I/O (Output)                                 |                                                                                                                                                                                                                                                                                                                                                                         | G input                                                                                                                                     |

| P63 (RIN)                                | I/O (Input)                                  |                                                                                                                                                                                                                                                                                                                                                                         | Key on wake-up input 5 or B input or AD converter analog input 5                                                                            |

| P62 (GIN)                                | I/O (Input)                                  | P63 to P61 output "0" after a reset. When these dual-function pins are used as ports, be sure to set ORP6S2 to "1".                                                                                                                                                                                                                                                     |                                                                                                                                             |

| P61<br>( KWU5 /BIN/AIN5 )                | I/O (Input)                                  |                                                                                                                                                                                                                                                                                                                                                                         | Key on wake-up input 4 or Y/BL input or AD converter analog input 4                                                                         |

| P60<br>( KWU4 /YBLIN/AIN4 )              | I/O (Input)                                  |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |

## Pin Functions (2/2)

| Pin Name                | I/O           | Function                                                                                                                                                                                          |                                     |

|-------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

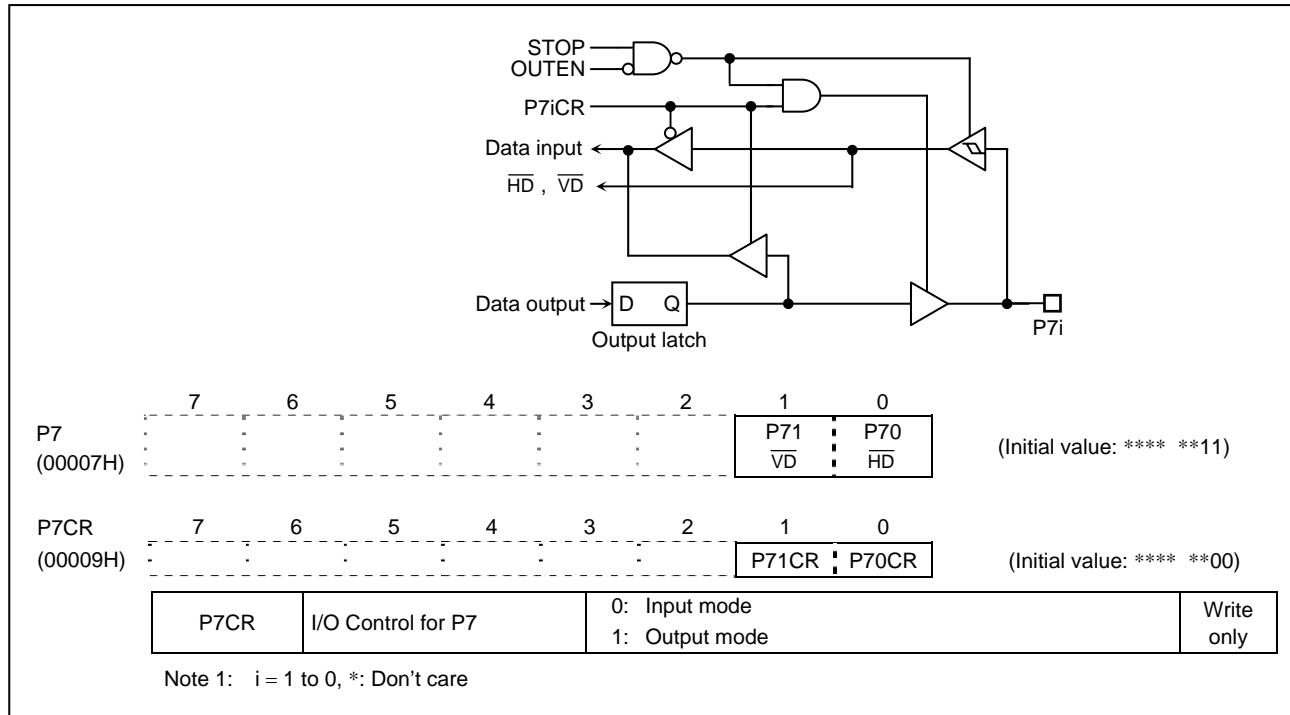

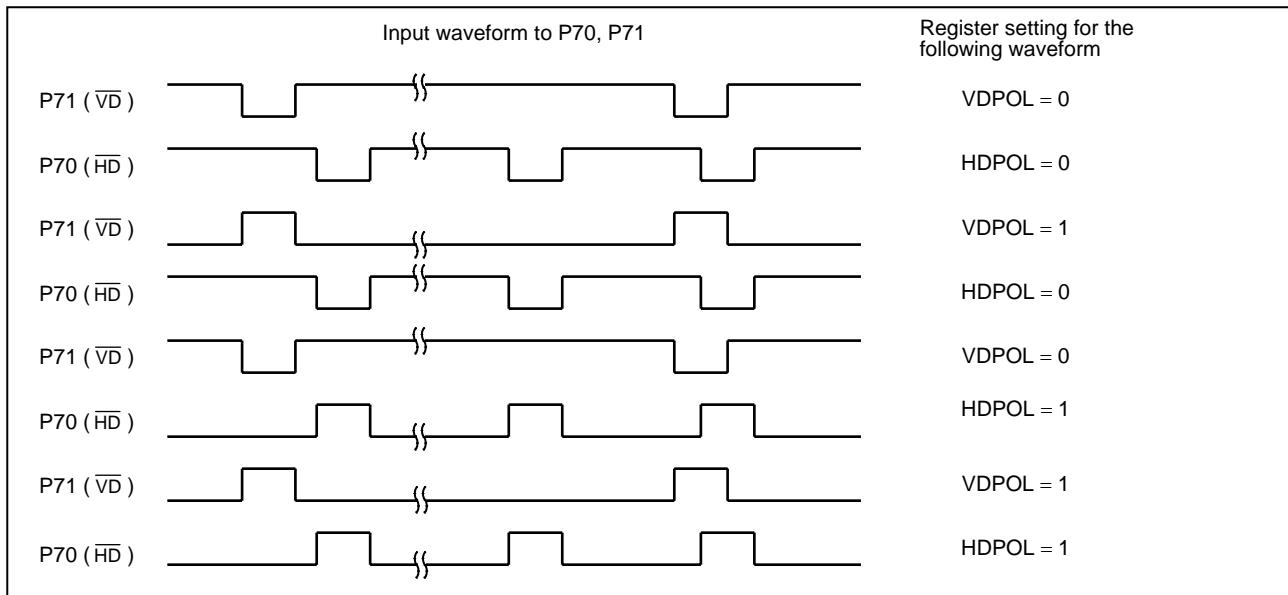

| P71 ( $\overline{VD}$ ) | I/O (Input)   | 2-bit programmable input/output port. Each bit of these ports can be individually configured as an input or an output under software control.<br>During reset, all bits are configured as inputs. | Vertical synchronous signal input   |

| P70 ( $\overline{HD}$ ) | I/O (Input)   |                                                                                                                                                                                                   | Horizontal synchronous signal input |

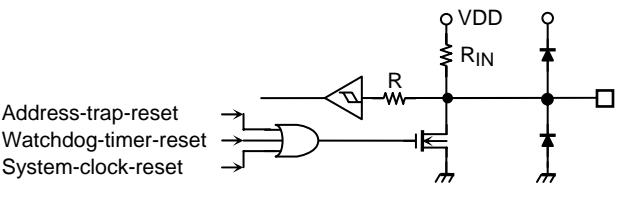

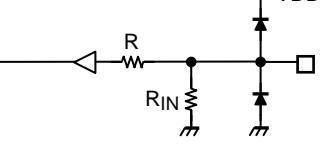

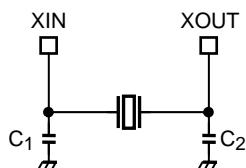

| XIN, XOUT               | Input, Output | Resonator connecting pins. For inputting external clock, XIN is used and XOUT is opened.                                                                                                          |                                     |

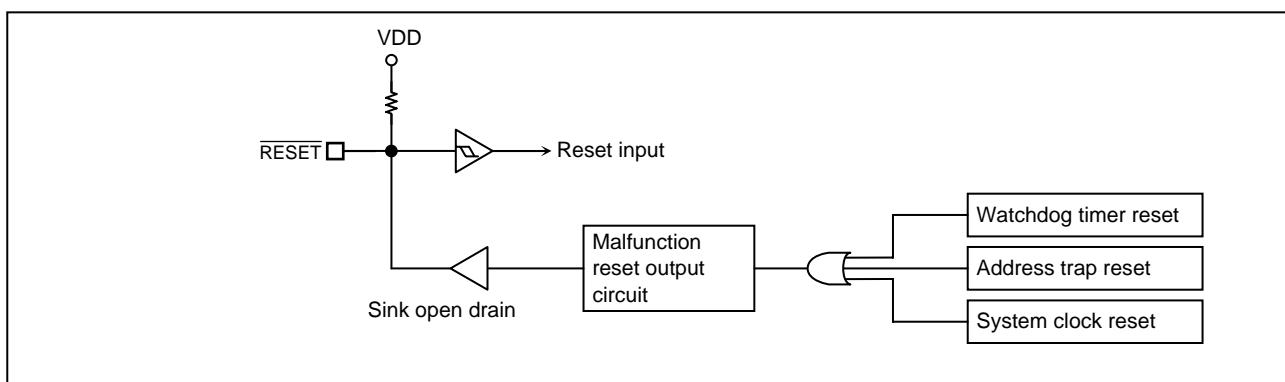

| RESET                   | I/O           | Reset signal input or watchdog timer output/address-trap-reset output/system-clock-rest output                                                                                                    |                                     |

| TEST                    | Input         | Test pin for out-going test. Be tied to low.                                                                                                                                                      |                                     |

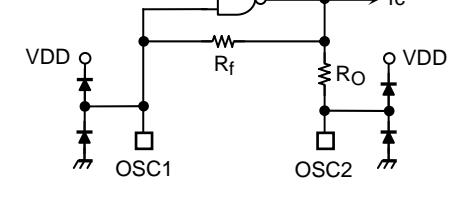

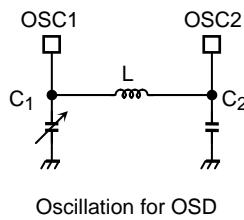

| OSC1, OSC2              | Input, Output | Resonator connecting pins for on-screen display circuitry                                                                                                                                         |                                     |

| VDD, VSS, VVSS          | Power Supply  | +5 V, 0 V (GND)                                                                                                                                                                                   |                                     |

## Block Diagram

## Operational Description

### 1. CPU Core Functions

The CPU core consists of a CPU, a system clock controller, and an interrupt controller.

This section provides a description of the CPU core, the program memory, the data memory, the external memory interface, and the reset circuit.

#### 1.1 Memory Address Map

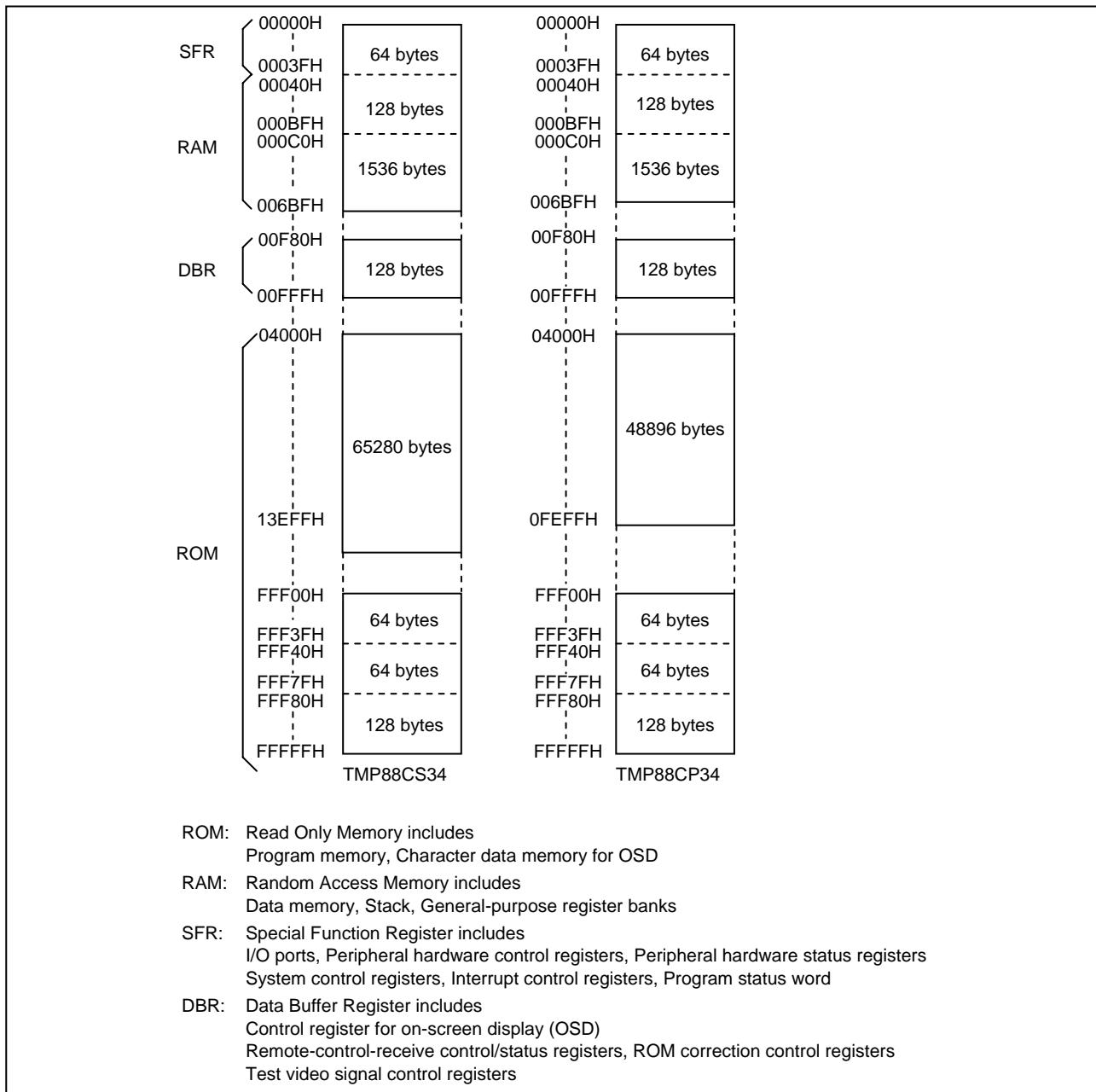

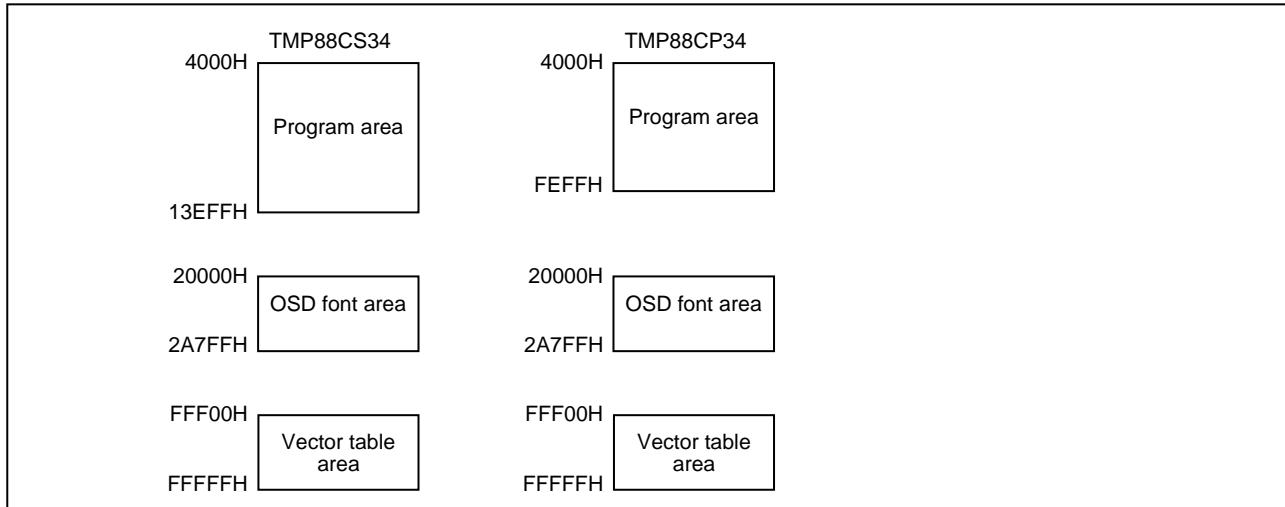

The TMP88CS34/CP34 memory consists of four blocks: ROM, RAM, SFR (Special Function Register), and DBR (Data Buffer Register). They are all mapped to a 1-Mbyte address space. Figure 1.1.1 shows the TMP88CS34/CP34 memory address map. There are 16 banks of the general-purpose register. The register banks are also assigned to the RAM address space.

Figure 1.1.1 Memory Address Map

## 1.2 Program Memory (ROM)

The TMP88CS34 contains a 64-Kbyte program memory (mask ROM) at addresses from 04000 to 13EFFH and FFF00 to FFFFFH.

The TMP88CP34 contains a 48-Kbyte program memory (mask ROM) at address from 04000 to 0FEFFH and FFF00 to FFFFFH.

Addresses FFF00 through FFFFFH in the program memory are also used for a particular purpose.

## 1.3 Data Memory (RAM)

The TMP88CS34/CP34 has a 1.5-Kbyte data memory (Static RAM) address from 0040 to 06BFH.

The first 128 bytes (addresses 00040 through 000BFH) in the built-in RAM are also available as general-purpose register banks.

The general-purpose registers are mapped in the RAM; therefore, do not clear RAM at the current bank addresses.

Example: Clears RAM to “00H” except the bank 0 (TMP88CS34/CP34):

```

LD   HL, 0048H ; Sets start address to HL register pair

LD   A, H       ; Sets initial data (00H) to A register

LD   BC, 0677H  ; Sets number of byte to BC register pair

SRAMCLR: LD   (HL+), A

DEC  BC

JRS  F, SRAMCLR

```

Note: The data memory contents become unstable when the power supply is turned on; therefore, the data memory should be initialized by an initialization routine. Note that the general-purpose registers are mapped in the RAM; therefore, do not clear RAM at the current bank addresses.

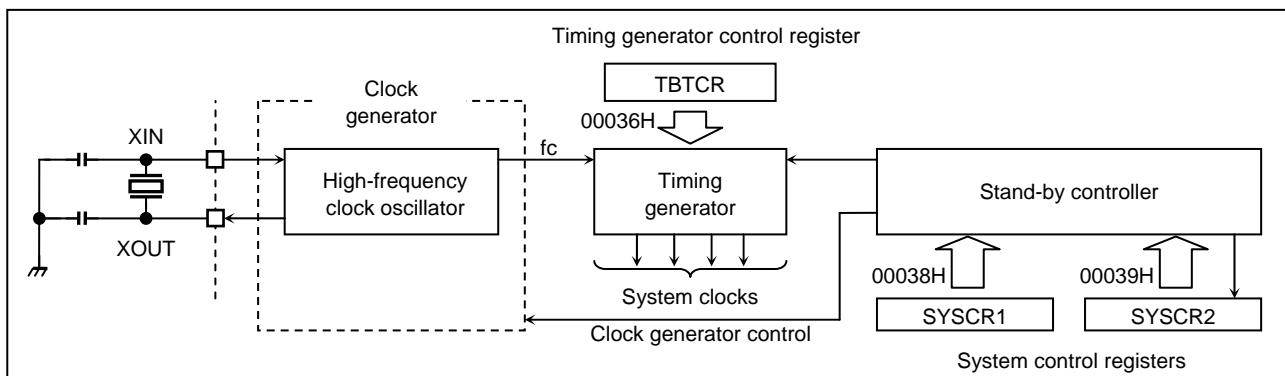

## 1.4 System Clock Controller

The system clock controller consists of a clock generator, a timing generator, and a stand-by controller.

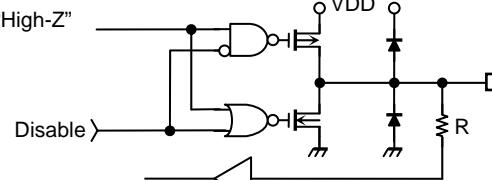

Figure 1.4.1 System Clock Controller

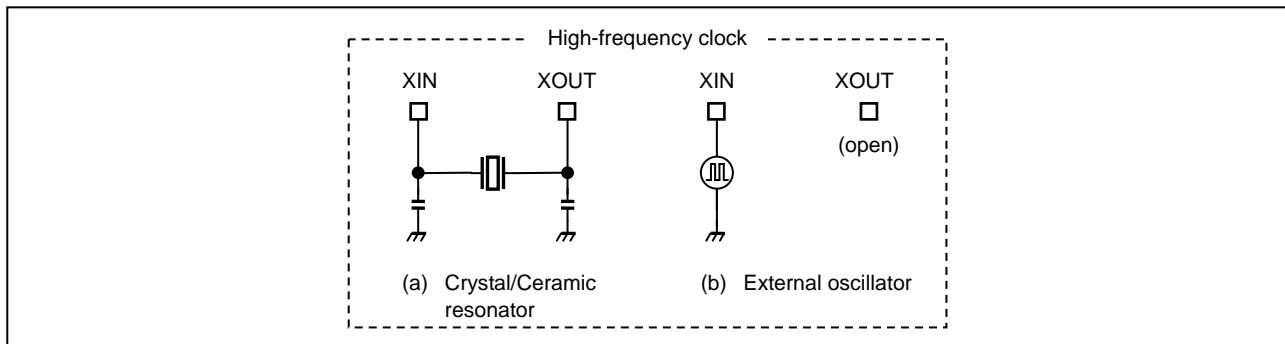

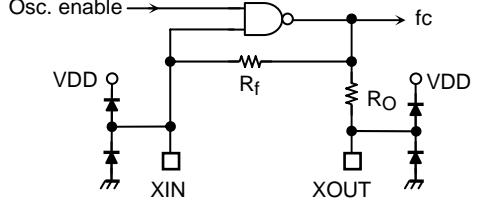

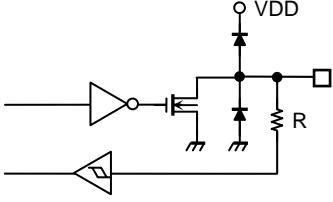

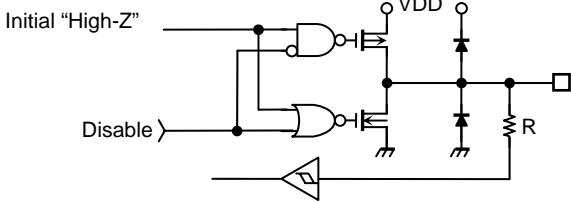

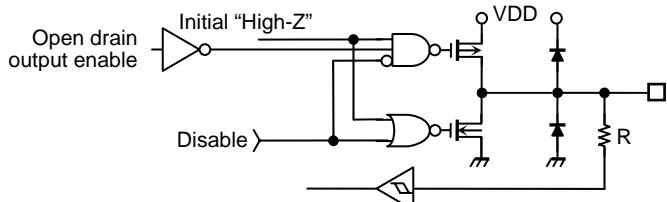

### 1.4.1 Clock Generator

The clock generator generates the basic clock which provides the system clocks supplied to the CPU core and peripheral hardware. It contains oscillation circuit: one for the high-frequency clock.

The high-frequency (fc) clock can be easily obtained by connecting a resonator between the XIN/XOUT pin, respectively. Clock input from an external oscillator is also possible. In this case, external clock is applied to XIN pin with XOUT pin not connected.

Figure 1.4.2 Examples of Resonator Connection

Note: Accurate adjustment of the oscillation frequency:

Although hardware to externally and directly monitor the basic clock pulse is not provided, the oscillation frequency can be adjusted by making the program to output fixed frequency pulses to the port while disabling all interrupts and monitoring this pulse. With a system requiring adjustment of the oscillation frequency, the adjusting program must be created beforehand.

### 1.4.2 Timing Generator

The timing generator generates from the basic clock the various system clocks supplied to the CPU core and peripheral hardware. The timing generator provides the following functions:

1. Generation of main system clock

2. Generation of source clocks for time base timer

3. Generation of source clocks for watchdog timer

4. Generation of internal source clocks for timer/counters TC1 to TC4

5. Generation of warm-up clocks for releasing STOP mode

6. Generation of a clock for releasing reset output

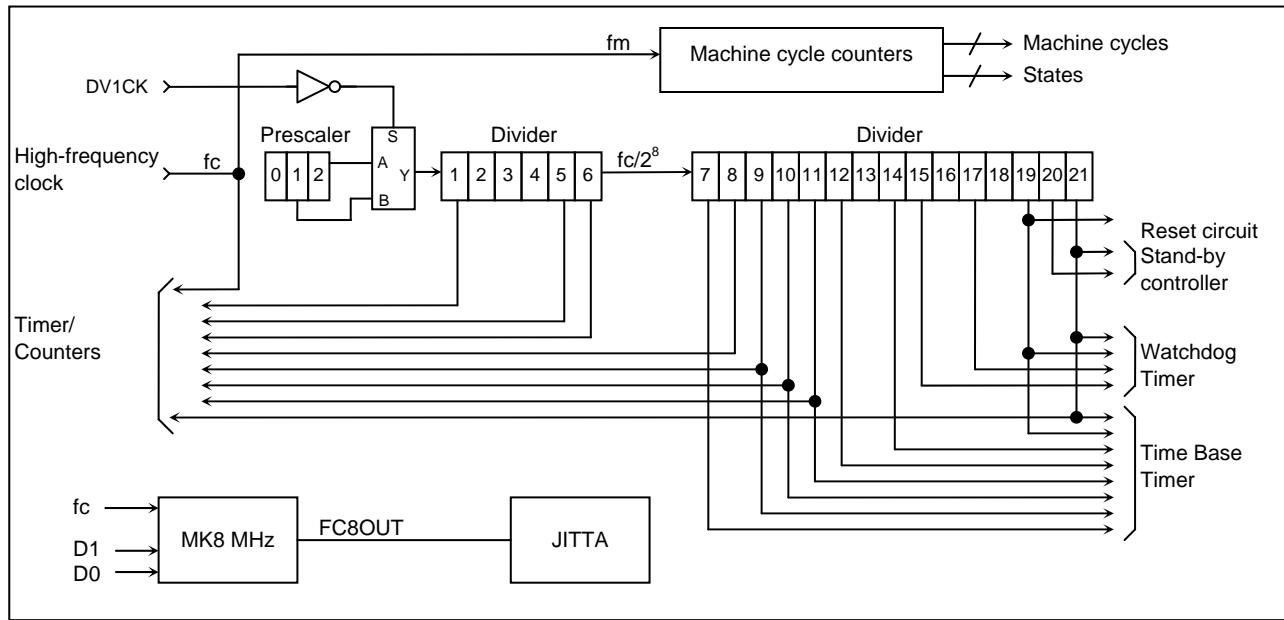

#### (1) Configuration of Timing Generator

The timing generator consists of a 21-stage divider with a divided-by-3 prescaler, a main system clock generator, and machine cycle counters.

During reset and at releasing STOP mode, the prescaler and the divider are cleared to "0", however, the prescaler is not cleared.

An input clock to the 7th stage of the divider depends on the operating mode.

A divided-by-256 of high-frequency clock ( $fc/2^8$ ) is input to the 7th stage of the divider.

Figure 1.4.3 Configuration of Timing Generator

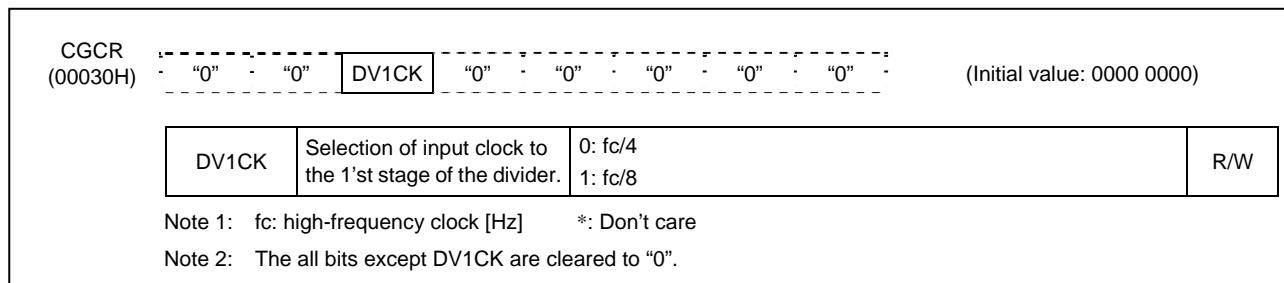

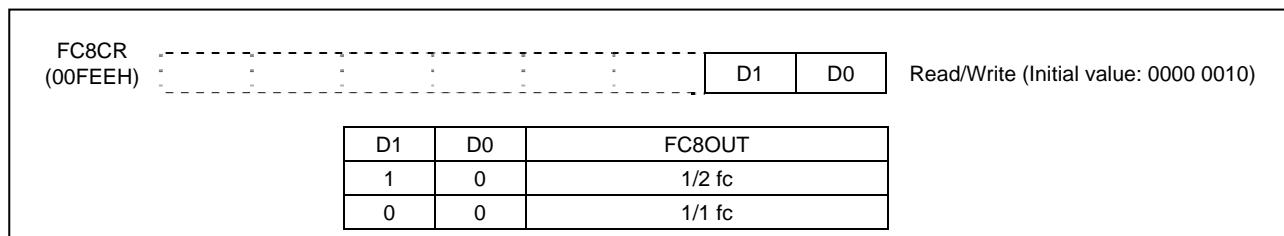

Figure 1.4.4 Divider Control Register

Figure 1.4.5 FC8 Control Register

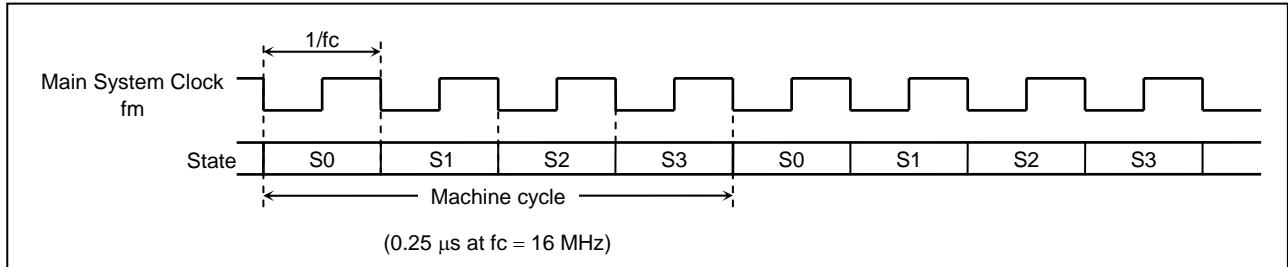

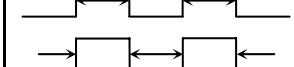

## (2) Machine Cycle

Instruction execution and peripheral hardware operation are synchronized with the main system clock. The minimum instruction execution unit is called a “machine cycle”.

There are a total of 15 different types of instructions for the TLCS-870/X Series: ranging from 1-cycle instructions which require one machine cycle for execution to 15-cycle instructions which require 15 machine cycles for execution.

A machine cycle consists of 4 states (S0 to S3), and each state consists of one main system clock.

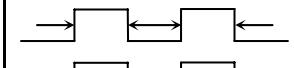

Figure 1.4.6 Machine Cycle

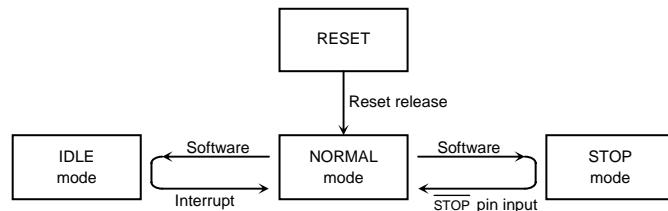

### 1.4.3 Stand-by Controller

The stand-by controller starts and stops the main system clock. These modes are controlled by the system control registers (SYSCR1, SYSCR2).

Figure 1.4.7 shows the operating mode transition diagram and Figure 1.4.8 shows the system control registers.

#### Single-clock mode

In the single-clock mode, the machine cycle time is  $4/fc$  [s] (0.25 μs at fc = 16 MHz).

##### 1. NORMAL mode

In this mode, both the CPU core and on-chip peripherals operate using the high-frequency clock.

##### 2. IDLE mode

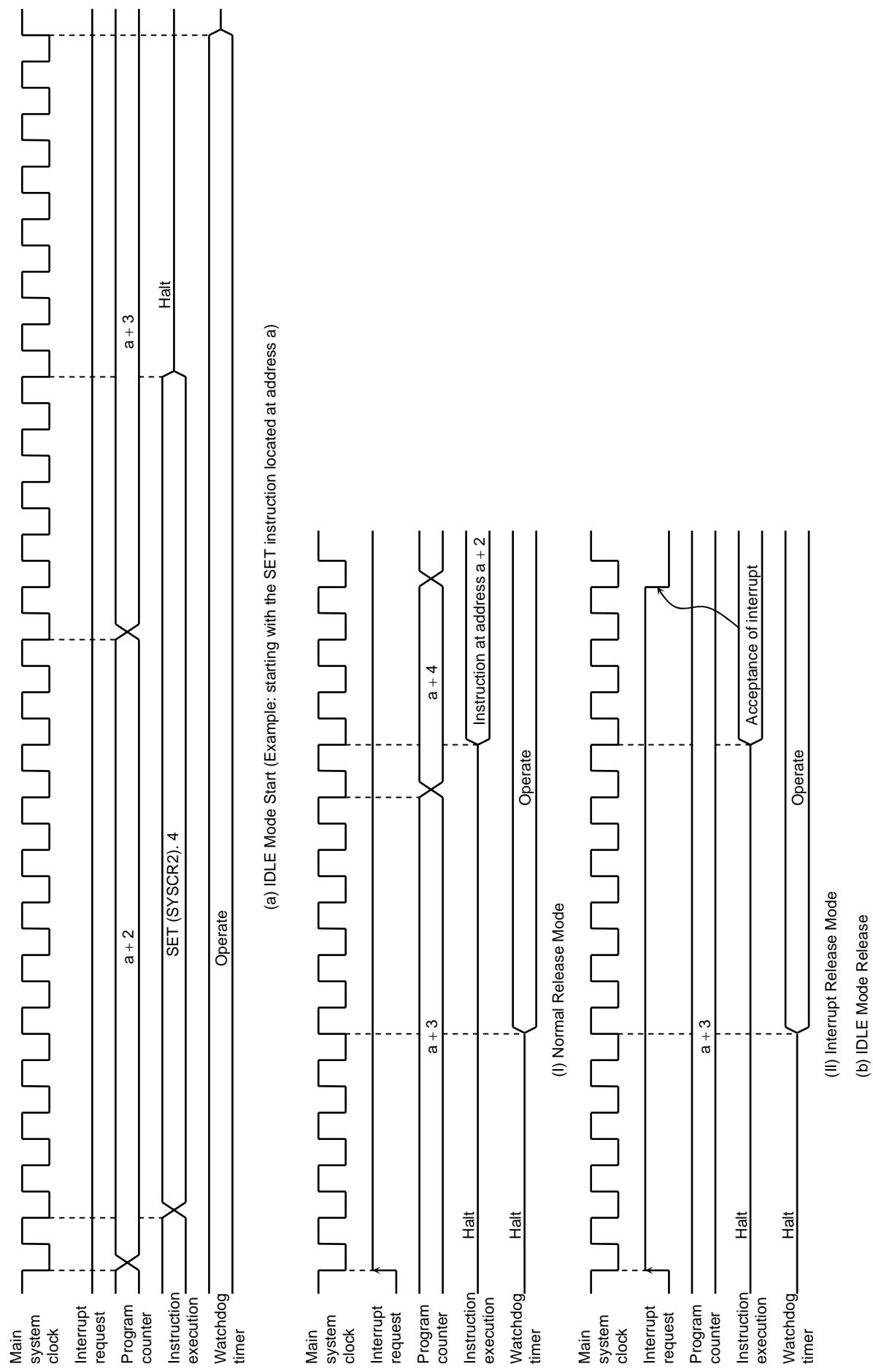

In this mode, the internal oscillation circuit remains active. The CPU and the watchdog timer are halted; however, on-chip peripherals remain active (operate using the high-frequency clock). IDLE mode is started by setting IDLE bit in the system control register 2 (SYSCR2), and IDLE mode is released to NORMAL mode by an interrupt request from on-chip peripherals or external interrupt inputs. When IMF (interrupt master enable flag) is “1” (interrupt enable), the execution will resume upon acceptance of the interrupt, and the operation will return to normal after the interrupt service is completed. When IMF is “0” (interrupt disable), the execution will resume with the instruction which follows IDLE mode start instruction.

##### 3. STOP mode

In this mode, the internal oscillation circuit is turned off, causing all system operations to be halted.

The internal status immediately prior to the halt is held with the lowest power consumption during this mode.

STOP mode is started by setting STOP bit in the system control register 1 (SYSCR1), and STOP mode is released by an input (either level-sensitive or edge-sensitive can be programmably selected) to the  $\overline{\text{STOP}}$  pin. After the warming-up period is completed, the execution resumes with the next instruction which follows the STOP mode start instruction.

(a) Single-clock mode

Note: NORMAL mode is generically called NORMAL; STOP mode is called STOP; and IDLE mode is called IDLE.

| Operating Mode |        | Frequency               |                         | CPU Core | On-chip Peripherals | Machine Cycle Time |

|----------------|--------|-------------------------|-------------------------|----------|---------------------|--------------------|

|                |        | High-frequency          | Low-frequency           |          |                     |                    |

| Single-Clock   | RESET  | Turning on oscillation  | Turning off oscillation | Reset    | Reset               | 4/fc [s]           |

|                | NORMAL |                         |                         | Operate  | Operate             |                    |

|                | IDLE   | Turning off oscillation | Turning on oscillation  | Halt     | Halt                | –                  |

|                | STOP   |                         |                         |          |                     |                    |

Figure 1.4.7 Operating Mode Transition Diagram

| System Control Register 1                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------|-----|--|-----------------------|--|--|--|-----------|-----------|--|----|----------------------|----------------------|--|----|-------------|-------------|--|----|----------|----------|--|----|----------|----------|--|

| SYSCR1                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                         | 6                    | 5   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3   | 2                          | 1 0 |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| (00038H)                                                                                                                                                                                                                                                                                                                                                                                                                                         | STOP                                      | RELM                 | “0” | “1”                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | WUT |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | (Initial value: 0000 00**) |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| STOP                                                                                                                                                                                                                                                                                                                                                                                                                                             | STOP mode start                           |                      |     | 0: CPU core and peripherals remain active<br>1: CPU core and peripherals are halted<br>(start STOP mode)                                                                                                                                                                                                                                                                                                                                                                                                 |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| RELM                                                                                                                                                                                                                                                                                                                                                                                                                                             | Release method for STOP mode              |                      |     | 0: Edge-sensitive release (Rising Edge)<br>1: Level-sensitive release (“H” Level)                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

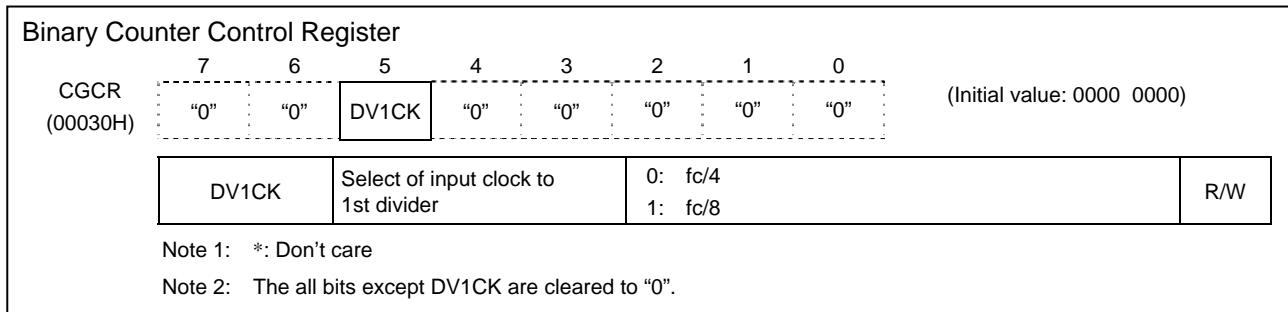

| WUT                                                                                                                                                                                                                                                                                                                                                                                                                                              | Warming-up time at releasing<br>STOP mode |                      |     | <table border="1"> <tr> <td></td><td colspan="3">Return to NORMAL mode</td></tr> <tr> <td></td><td>DV1CK = 0</td><td>DV1CK = 1</td><td></td></tr> <tr> <td>00</td><td><math>3 \times 2^{16}/fc</math></td><td><math>3 \times 2^{17}/fc</math></td><td></td></tr> <tr> <td>01</td><td><math>2^{16}/fc</math></td><td><math>2^{17}/fc</math></td><td></td></tr> <tr> <td>10</td><td>Reserved</td><td>Reserved</td><td></td></tr> <tr> <td>11</td><td>Reserved</td><td>Reserved</td><td></td></tr> </table> |     |                            |     |  | Return to NORMAL mode |  |  |  | DV1CK = 0 | DV1CK = 1 |  | 00 | $3 \times 2^{16}/fc$ | $3 \times 2^{17}/fc$ |  | 01 | $2^{16}/fc$ | $2^{17}/fc$ |  | 10 | Reserved | Reserved |  | 11 | Reserved | Reserved |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Return to NORMAL mode                     |                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DV1CK = 0                                 | DV1CK = 1            |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| 00                                                                                                                                                                                                                                                                                                                                                                                                                                               | $3 \times 2^{16}/fc$                      | $3 \times 2^{17}/fc$ |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| 01                                                                                                                                                                                                                                                                                                                                                                                                                                               | $2^{16}/fc$                               | $2^{17}/fc$          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reserved                                  | Reserved             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reserved                                  | Reserved             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| <p>Note 1: Always set bit 5 in SYSCR1 to “0”.</p> <p>Note 2: When STOP mode is released with <u>RESET</u> pin input, a return is made to NORMAL mode regardless of the RETM contents.</p> <p>Note 3: fc: High-frequency clock [Hz]</p> <p>*: Don't care</p> <p>Note 4: Bits 1 and 0 in SYSCR1 are read in as undefined data when a read instruction is executed.</p> <p>Note 5: Always set bit 4 in SYSCR1 to “1” when STOP mode is started.</p> |                                           |                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| System Control Register 2                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| SYSCR2                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                         | 6                    | 5   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3   | 2                          | 1 0 |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| (00039H)                                                                                                                                                                                                                                                                                                                                                                                                                                         | “1”                                       | “0”                  | “0” | IDLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | (Initial value: 1000 ****) |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| IDLE                                                                                                                                                                                                                                                                                                                                                                                                                                             | IDLE mode start                           |                      |     | 0: CPU and watchdog timer remain active<br>1: CPU and watchdog timer are stopped (start IDLE mode)                                                                                                                                                                                                                                                                                                                                                                                                       |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

| <p>Note 1: *: Don't care</p> <p>Note 2: Always set bit 7, 6 and 5 in SYSCR2 to “100”.</p>                                                                                                                                                                                                                                                                                                                                                        |                                           |                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                            |     |  |                       |  |  |  |           |           |  |    |                      |                      |  |    |             |             |  |    |          |          |  |    |          |          |  |

Figure 1.4.8 System Control Registers

#### 1.4.4 Operating Mode Control

##### (1) STOP mode

STOP mode is controlled by the system control register 1 (SYSCR1) and the  $\overline{\text{STOP}}$  pin input. The  $\overline{\text{STOP}}$  pin is also used both as a port P20 and an  $\overline{\text{INT5}}$  (external interrupt input 5) pin. STOP mode is started by setting STOP (bit 7 in SYSCR1) to “1”. During STOP mode, the following status is maintained.

1. Oscillations are turned off, and all internal operations are halted.

2. The data memory, registers and port output latches are all held in the status in effect before STOP mode was entered.

3. The prescaler and the divider of the timing generator are cleared to “0”.

4. The program counter holds the address of the instruction following the instruction which started the STOP mode.

STOP mode includes a level-sensitive release mode and an edge-sensitive release mode, either of which can be selected with RELM (bit 6 in SYSCR1).

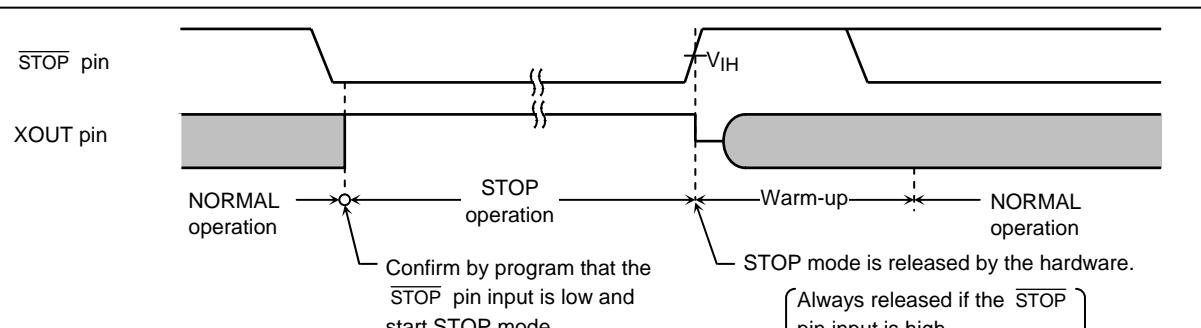

###### a. Level-sensitive release mode (RELM = 1)

In this mode, STOP mode is released by setting the  $\overline{\text{STOP}}$  pin high. This mode is used for capacitor back-up when the main power supply is cut off and long term battery back-up.

When the  $\overline{\text{STOP}}$  pin input is high, executing an instruction which starts the STOP mode will not place in STOP mode but instead will immediately start the release sequence (warm-up). Thus, to start STOP mode in the level-sensitive release mode, it is necessary for the program to first confirm that the  $\overline{\text{STOP}}$  pin input is low. The following method can be used for confirmation:

Using an external interrupt input  $\overline{\text{INT5}}$  ( $\overline{\text{INT5}}$  is a falling edge-sensitive input).

Example: Starting STOP mode with an INT5 interrupt.

```

PINT5: TEST (P2) . 0 ; To reject noise, the STOP mode does not

; start if port P20 is at high

; JRS F, SINT5

; LD (SYSCR1), 01010000B ; Sets up the level-sensitive release mode.

; SET (SYSCR1) . 7 ; Starts STOP mode

; LDW (IL), 1110011101010111B ; IL12, 11, 7, 5, 3 ← 0 (Clears interrupt latches)

SINT5: RETI

```

Note 1: After warming up is started, when  $\overline{\text{STOP}}$  pin input is changed “L” level, STOP mode is not placed.

Note 2: When changing to the level-sensitive release mode from the edge-sensitive release mode, the release mode is not switched until a rising edge of the  $\overline{\text{STOP}}$  pin input is detected.

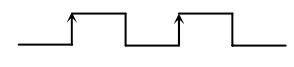

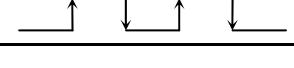

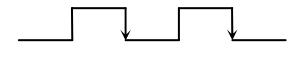

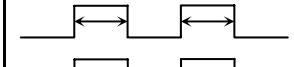

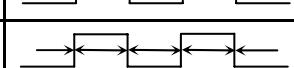

Figure 1.4.9 Level-sensitive Release Mode

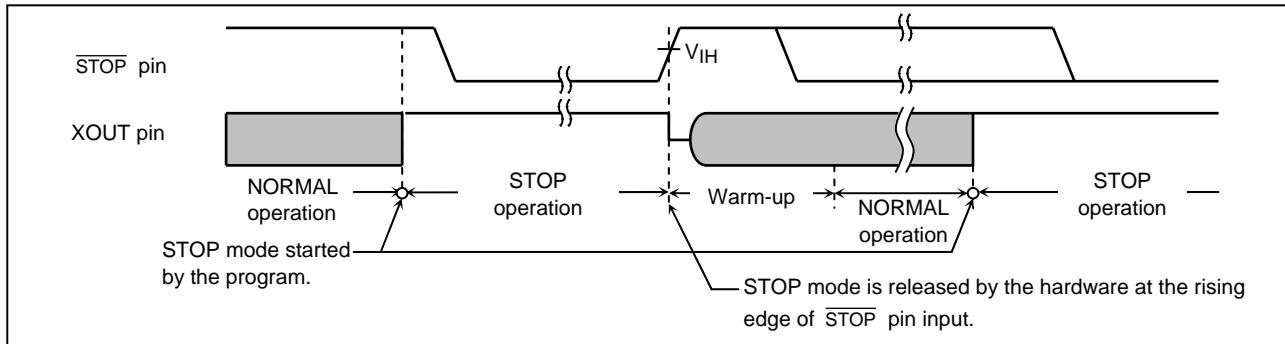

## b. Edge-sensitive release mode (RELM = 0)

In this mode, STOP mode is released by a rising edge of the  $\overline{\text{STOP}}$  pin input. This is used in applications where a relatively short program is executed repeatedly at periodic intervals. This periodic signal (for example, a clock from a low-power consumption oscillator) is input to the  $\overline{\text{STOP}}$  pin.

In the edge-sensitive release mode, STOP mode is started even when the  $\overline{\text{STOP}}$  pin input is high.

Example: Starting STOP mode from NORMAL mode

LD (SYSCR1), 10010000B ; Starts after specified to the edge-sensitive mode

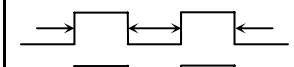

Figure 1.4.10 Edge-sensitive Release Mode

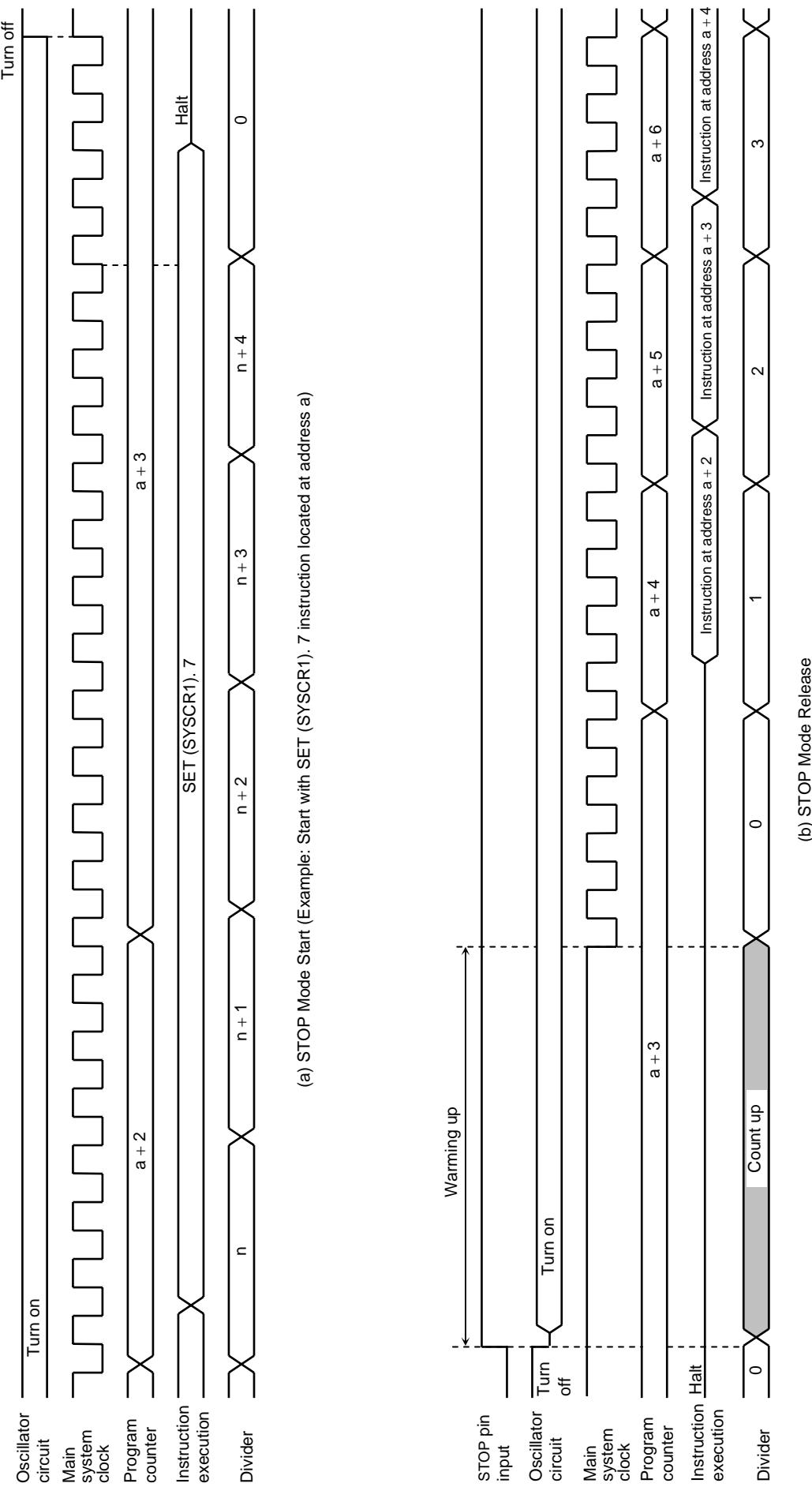

STOP mode is released by the following sequence:

1. When returning to NORMAL, clock oscillator is turned on.

2. A warming-up period is inserted to allow oscillation time to stabilize. During warm-up, all internal operations remain halted. Two different warming-up times can be selected with WUT (bits 2 and 3 in SYSCR1) as determined by the resonator characteristics.

3. When the warming-up time has elapsed, normal operation resumes with the instruction following the STOP mode start instruction (e.g. [SET (SYSCR1). 7]). The start is made after the divider of the timing generator is cleared to "0".

Table 1.4.1 Warming-up Time Example

| WUT | Warming-up Time [ms]            |                                 |                       |                       |

|-----|---------------------------------|---------------------------------|-----------------------|-----------------------|

|     | Return to NORMAL mode           |                                 |                       |                       |

|     | DV1CK = 0                       | DV1CK = 1                       | DV1CK = 0             | DV1CK = 1             |

| 00  | $3 \times 2^{16}/fc$<br>(12.29) | $3 \times 2^{17}/fc$<br>(24.58) | $2^{16}/fc$<br>(4.10) | $2^{17}/fc$<br>(8.20) |

| 01  | Reserved<br>( - )               | Reserved<br>( - )               | Reserved<br>( - )     | Reserved<br>( - )     |

| 10  | Reserved<br>( - )               | Reserved<br>( - )               | Reserved<br>( - )     | Reserved<br>( - )     |

| 11  | Reserved<br>( - )               | Reserved<br>( - )               | Reserved<br>( - )     | Reserved<br>( - )     |

Note: The warming-up time is obtained by dividing the basic clock by the divider: therefore, the warming-up time may include a certain amount of error if there is any fluctuation of the oscillation frequency when STOP mode is released. Thus, the warming-up time must be considered an approximate value.

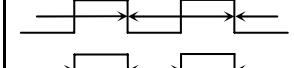

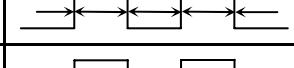

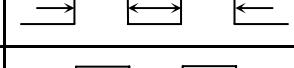

Figure 1.4.11 STOP Mode Start/Release

STOP mode can also be released by setting the RESET pin low, which immediately performs the normal reset operation.

Note: When STOP mode is released with a low hold voltage, the following cautions must be observed.

The power supply voltage must be at the operating voltage level before releasing STOP mode. The RESET pin input must also be high, rising together with the power supply voltage. In this case, if an external time constant circuit has been connected, the RESET pin input voltage will increase at a slower rate than the power supply voltage. At this time, there is a danger that a reset may occur if input voltage level of the RESET pin drops below the non-inverting high-level input voltage (hysteresis input).

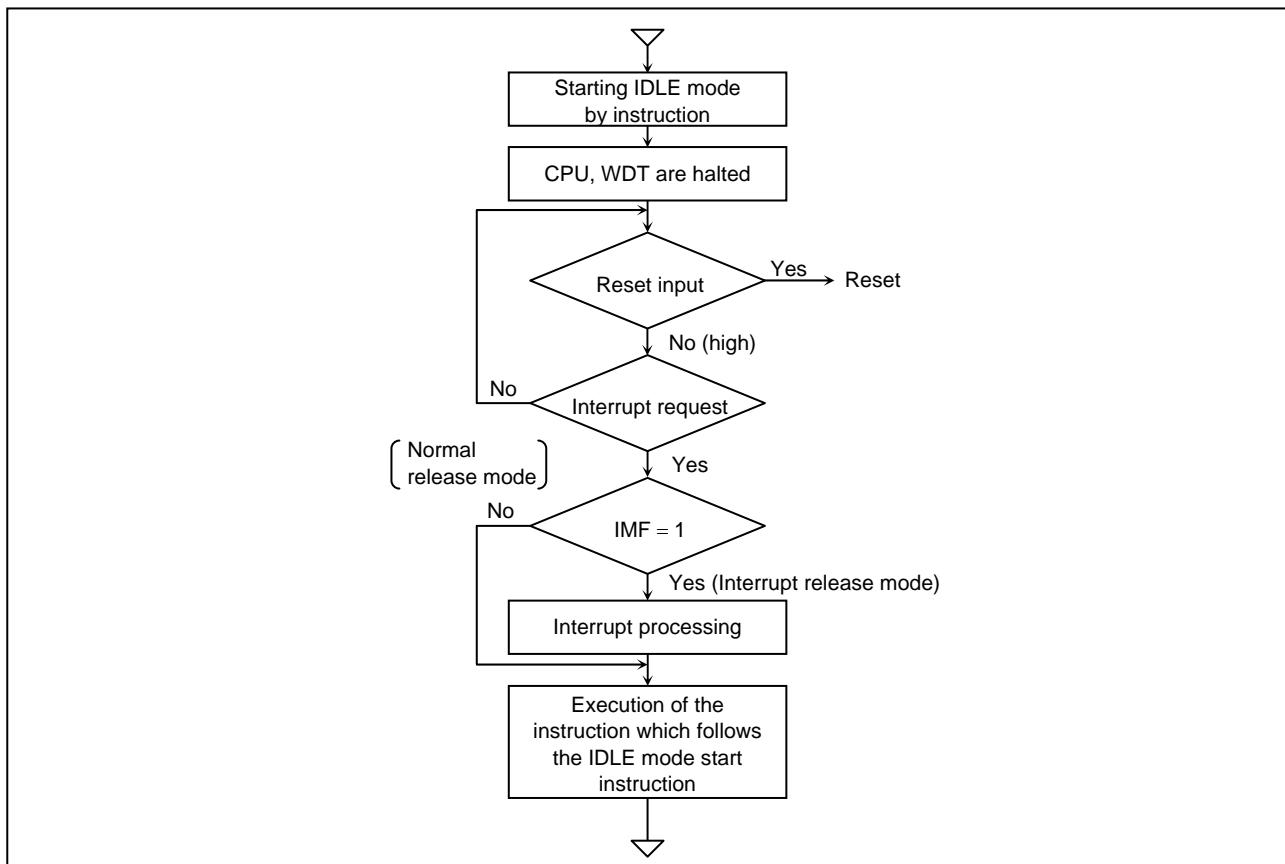

## (2) IDLE mode

IDLE mode is controlled by the system control register 2 and maskable interrupts. The following status is maintained during IDLE mode.

1. Operation of the CPU and watchdog timer is halted. On-chip peripherals continue to operate.

2. The data memory, CPU registers and port output latches are all held in the status in effect before IDLE mode was entered.

3. The program counter holds the address of the instruction following the instruction which started IDLE mode.

Example: Starting IDLE mode.

SET (SYSCR2) . 4 ; IDLE ← 1

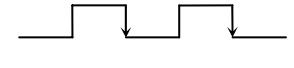

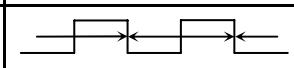

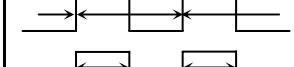

Figure 1.4.12 IDLE Mode

IDLE mode includes a normal release mode and an interrupt release mode. Selection is made with the interrupt master enable flag (IMF). Releasing the IDLE mode returns from IDLE to NORMAL.

a. Normal release mode (IMF = “0”)

IDLE mode is released by any interrupt source enabled by the individual interrupt enable flag (EF) or an external interrupt 0 ( $\overline{\text{INT0}}$  pin) request. Execution resumes with the instruction following the IDLE mode start instruction (e.g. [SET (SYSCR2).4]). Normally, IL (Interrupt Latch) of interrupt source to release IDLE mode must be cleared by load instructions.

b. Interrupt release mode (IMF = “1”)

IDLE mode is released and interrupt processing is started by any interrupt source enabled with the individual interrupt enable flag (EF) or an external interrupt 0 ( $\overline{\text{INT0}}$  pin) request. After the interrupt is processed, the execution resumes from the instruction following the instruction which started IDLE mode.

Note: When a watchdog timer interrupt is generated immediately before the IDLE mode is started, the watchdog timer interrupt will be processed but IDLE mode will not be started.

Figure 1.4.13 IDLE Mode Start/Release

IDLE mode can also be released by setting the  $\overline{\text{RESET}}$  pin low, which immediately performs the reset operation. After reset, the TMP88CS34/CP34 is placed in NORMAL mode.

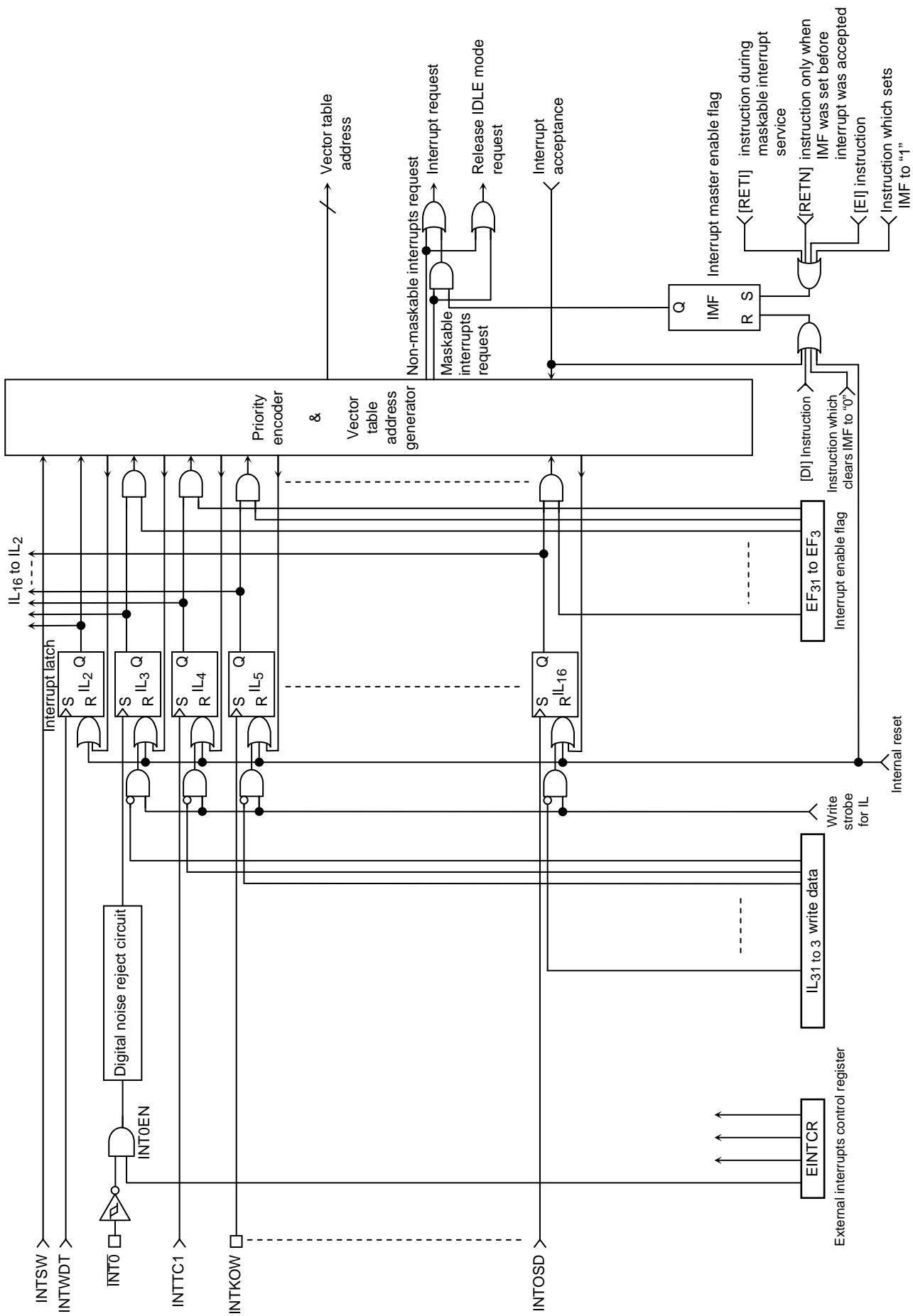

## 1.5 Interrupt Controller

The TMP88CS34/CP34 has a total of 16 interrupt sources; 6 externals and 10 internals. Multiple interrupts with priorities are also possible. Two of the internal sources are pseudo non-maskable interrupts; the remainder are all maskable interrupts.

Interrupt sources are provided with interrupt latches (IL), which hold interrupt requests, and independent vectors. The interrupt latch is set to "1" by the generation of its interrupt request which requests the CPU to accept its interrupts. Interrupts are enabled or disabled by software using the interrupt master enable flag (IMF) and interrupt enable flag (EF). If more than one interrupts are generated simultaneously, interrupts are accepted in order which is dominated by hardware. However, there are no prioritized interrupt factors among non-maskable interrupts.

Table 1.5.1 Interrupt Sources

| Interrupt source  |                                    | Enable condition                    | Interrupt latch  | Vector table address | Priority |

|-------------------|------------------------------------|-------------------------------------|------------------|----------------------|----------|

| Internal/External | (Reset)                            | Non-Maskable                        | –                | FFFFFCH              | High 0   |

| Internal          | INTSW (Software interrupt)         | Pseudo non-maskable                 | –                | FFFF8H               | 1        |

| Internal          | INTWDT (Watchdog timer interrupt)  |                                     | IL <sub>2</sub>  | FFFF4H               | 2        |

| External          | INT0 (External interrupt 0)        | IMF·EF <sub>3</sub> = 1, INT0EN = 1 | IL <sub>3</sub>  | FFFF0H               | 3        |

| Internal          | INTTC1 (16-bit TC1 interrupt)      | IMF·EF <sub>4</sub> = 1             | IL <sub>4</sub>  | FFFEC <sub>H</sub>   | 4        |

| External          | INTKWU (Key-On-Wake-Up)            | IMF·EF <sub>5</sub> = 1             | IL <sub>5</sub>  | FFF8EH               | 5        |

| Internal          | INTTBT (Time base timer interrupt) | IMF·EF <sub>6</sub> = 1             | IL <sub>6</sub>  | FFF4EH               | 6        |

| External          | INT2 (External interrupt 2)        | IMF·EF <sub>7</sub> = 1             | IL <sub>7</sub>  | FFF0EH               | 7        |

| Internal          | INTTC3 (8-bit TC3 interrupt)       | IMF·EF <sub>8</sub> = 1             | IL <sub>8</sub>  | FFFDCH               | 8        |

| Internal          | INTTSBI (SBI interrupt)            | IMF·EF <sub>9</sub> = 1             | IL <sub>9</sub>  | FFFD8H               | 9        |

| Internal          | INTTC4 (8-bit TC4 interrupt)       | IMF·EF <sub>10</sub> = 1            | IL <sub>10</sub> | FFFD4H               | 10       |

| External          | INT3 (External interrupt 3)        | IMF·EF <sub>11</sub> = 1            | IL <sub>11</sub> | FFFD0H               | 11       |

| External          | INT4 (External interrupt 4)        | IMF·EF <sub>12</sub> = 1            | IL <sub>12</sub> | FFFCCH               | 12       |

| Internal          | INTADC (AD Converter interrupt)    | IMF·EF <sub>13</sub> = 1            | IL <sub>13</sub> | FFFC8H               | 13       |

| Internal          | INTTC2 (16-bit TC2 interrupt)      | IMF·EF <sub>14</sub> = 1            | IL <sub>14</sub> | FFFC4H               | 14       |

| External          | INT5 (External interrupt 5)        | IMF·EF <sub>15</sub> = 1            | IL <sub>15</sub> | FFFC0H               | 15       |

| Internal          | INTOSD (OSD interrupt)             | IMF·EF <sub>16</sub> = 1            | IL <sub>16</sub> | FFFBCH               | 16       |

| Reserved          |                                    | IMF·EF <sub>17</sub> = 1            | IL <sub>17</sub> | FFFB8H               | 17       |

| Reserved          |                                    | IMF·EF <sub>18</sub> = 1            | IL <sub>18</sub> | FFFB4H               | 18       |

| Reserved          |                                    | IMF·EF <sub>19</sub> = 1            | IL <sub>19</sub> | FFFB0H               | 19       |

| Reserved          |                                    | IMF·EF <sub>20</sub> = 1            | IL <sub>20</sub> | FFFACH               | 20       |

| Reserved          |                                    | IMF·EF <sub>21</sub> = 1            | IL <sub>21</sub> | FFFA8H               | 21       |

| Reserved          |                                    | IMF·EF <sub>22</sub> = 1            | IL <sub>22</sub> | FFFA4H               | 22       |

| Reserved          |                                    | IMF·EF <sub>23</sub> = 1            | IL <sub>23</sub> | FFFA0H               | 23       |

| Reserved          |                                    | IMF·EF <sub>24</sub> = 1            | IL <sub>24</sub> | FFF9CH               | 24       |

| Reserved          |                                    | IMF·EF <sub>25</sub> = 1            | IL <sub>25</sub> | FFF98H               | 25       |

| Reserved          |                                    | IMF·EF <sub>26</sub> = 1            | IL <sub>26</sub> | FFF94H               | 26       |

| Reserved          |                                    | IMF·EF <sub>27</sub> = 1            | IL <sub>27</sub> | FFF90H               | 27       |

| Reserved          |                                    | IMF·EF <sub>28</sub> = 1            | IL <sub>28</sub> | FFF8CH               | 28       |

| Reserved          |                                    | IMF·EF <sub>29</sub> = 1            | IL <sub>29</sub> | FFF88H               | 29       |

| Reserved          |                                    | IMF·EF <sub>30</sub> = 1            | IL <sub>30</sub> | FFF84H               | 30       |

| Reserved          |                                    | IMF·EF <sub>31</sub> = 1            | IL <sub>31</sub> | FFF80H               | Low 31   |

Note : Before you change each enable flag (EF) and/or each interrupt latch (IL), be sure to clear the interrupt master enable flag (IMF) to "0" (to disable interrupts).

1. After a DI instruction is executed.

2. When an interrupt is accepted, IMF is automatically cleared to "0".

However, to enable nested interrupts change EF and/or IL before setting IMF to "1" (to enable interrupts).

If the individual enable flags (EF) and interrupts (IL) are set under conditions other than the above, proper operation cannot be guaranteed.

Figure 1.5.1 Interrupt Controller Block Diagram

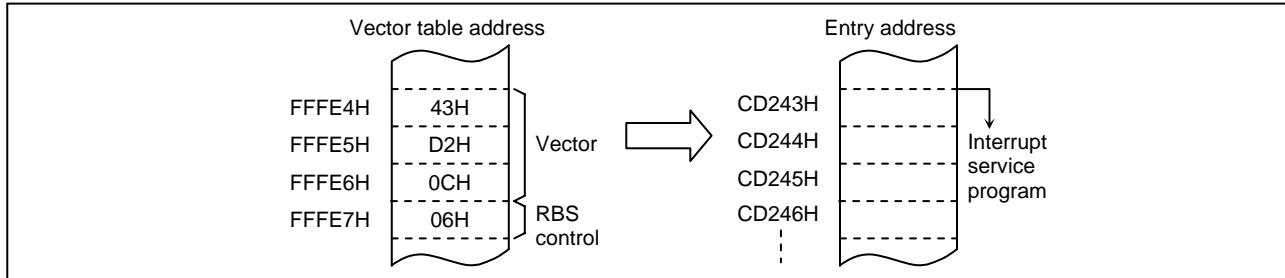

Interrupt latches (IL) that hold the interrupt requests are provided for interrupt sources. Each interrupt vector is independent.

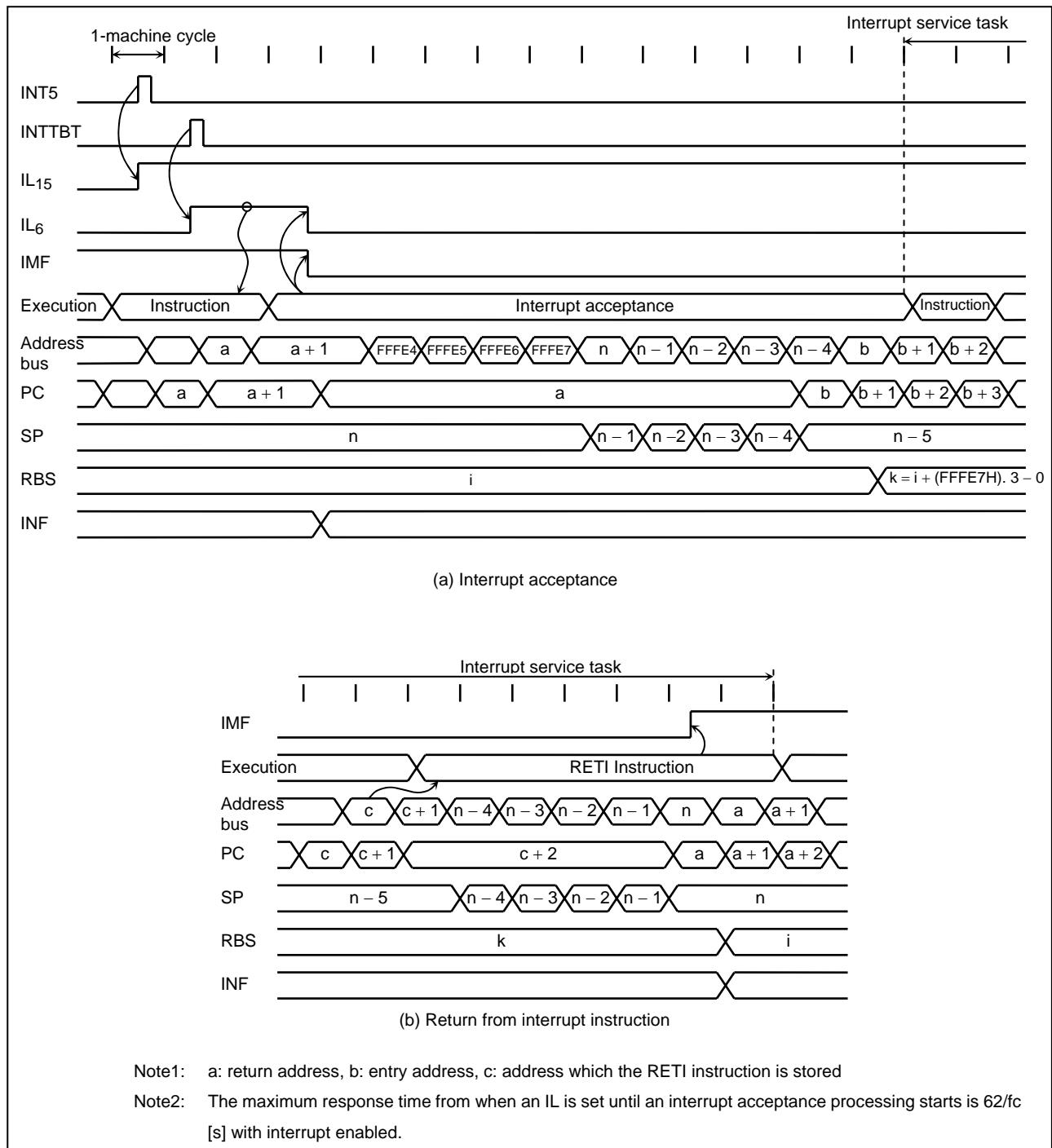

The interrupt latch is set to “1” when an interrupt request is generated, and requests the CPU to accept the interrupt. The acceptance of maskable interrupts can be selectively enabled and disabled by program using the interrupt master enable flag (IMF) and the individual interrupt enable flags (EF). When two or more interrupts are generated simultaneously, the interrupt is accepted in the highest priority order as determined by the hardware. Figure 1.5.1 shows the interrupt controller.

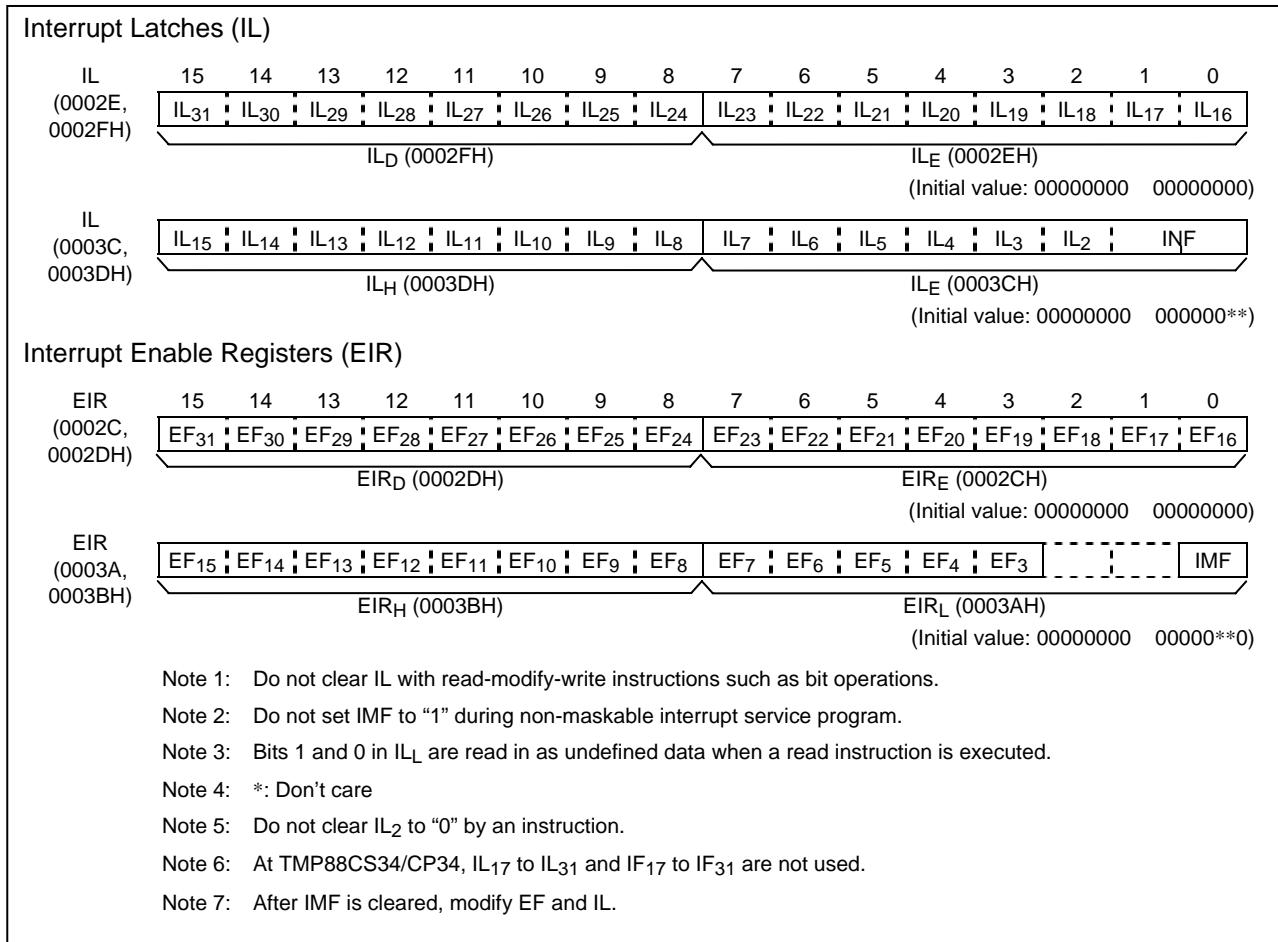

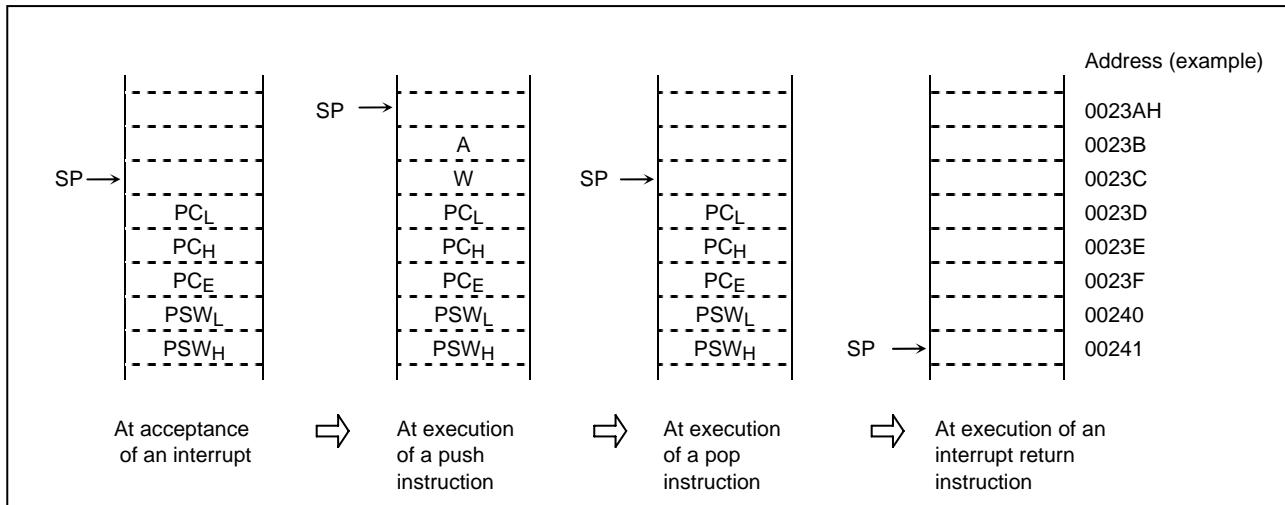

### (1) Interrupt Latches (IL31 to IL2)

Interrupt latches are provided for each source, except for a software interrupt. The latch is set to “1” when an interrupt request is generated, and requests the CPU to accept the interrupt. The latch is cleared to “0” just after the interrupt is accepted. All interrupt latches are initialized to “0” during reset.

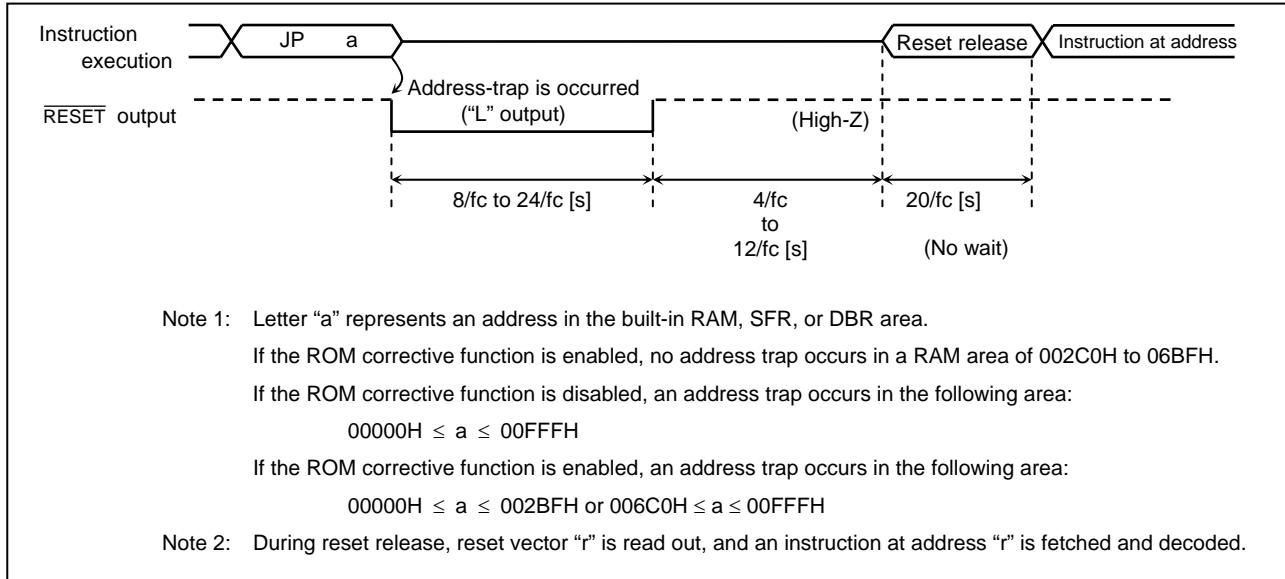

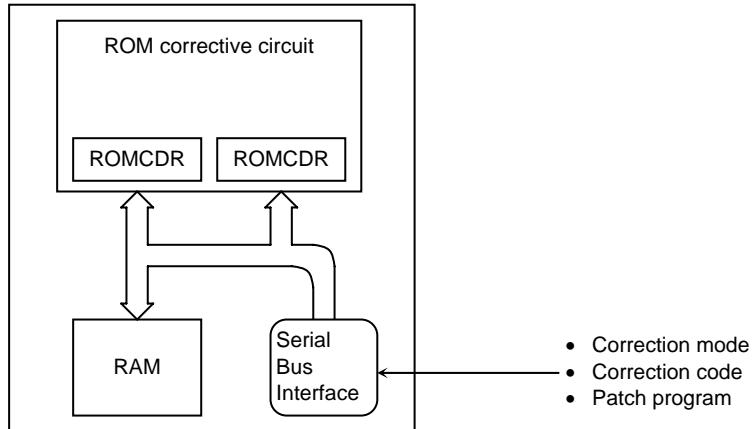

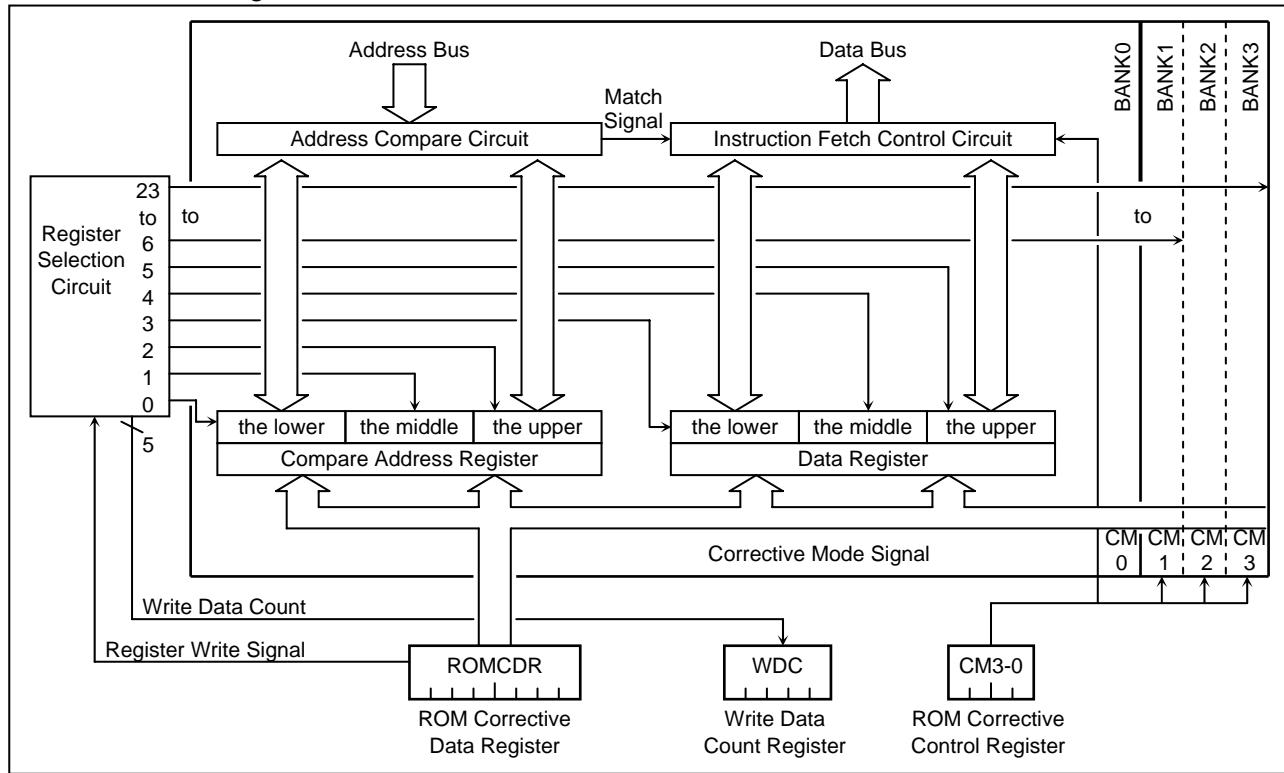

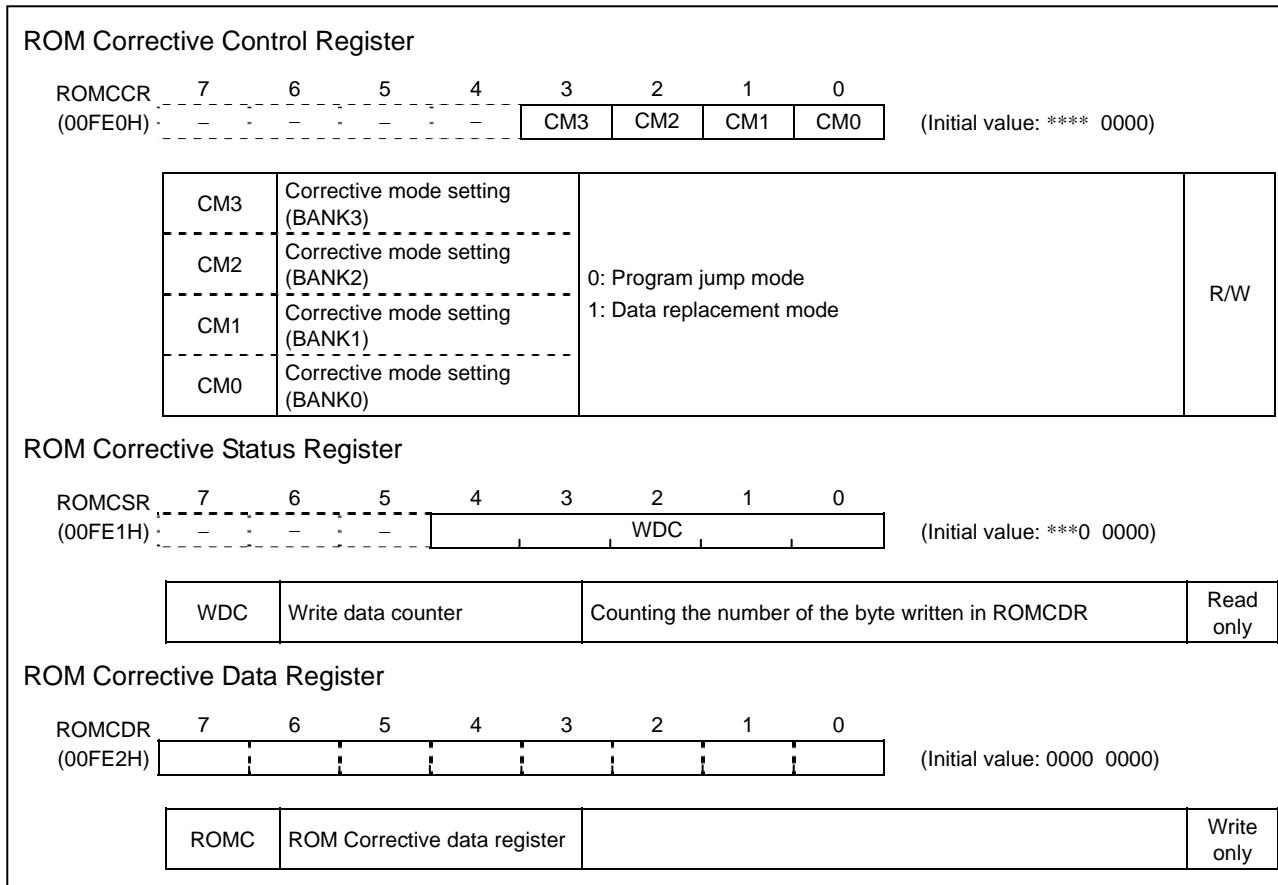

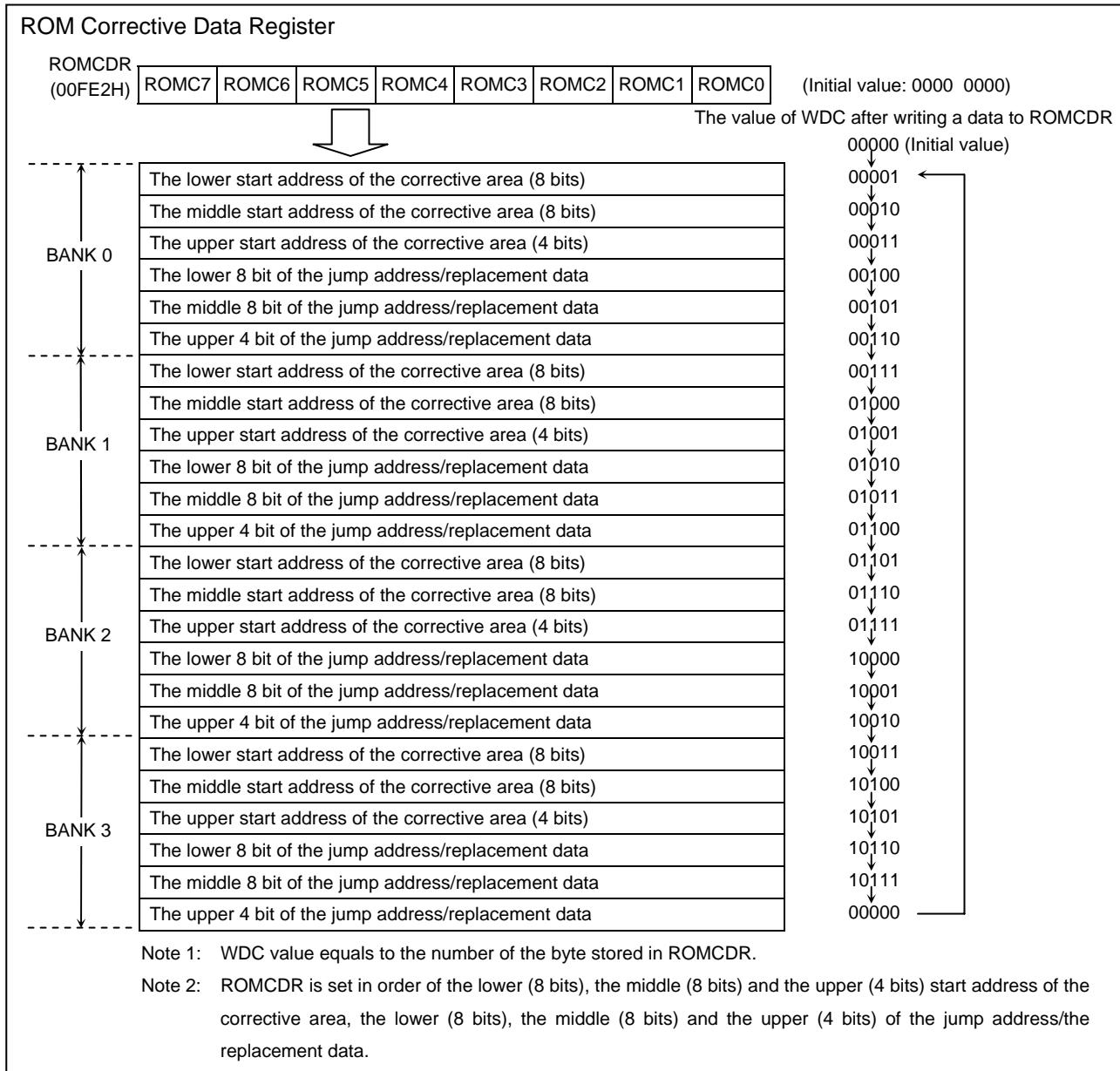

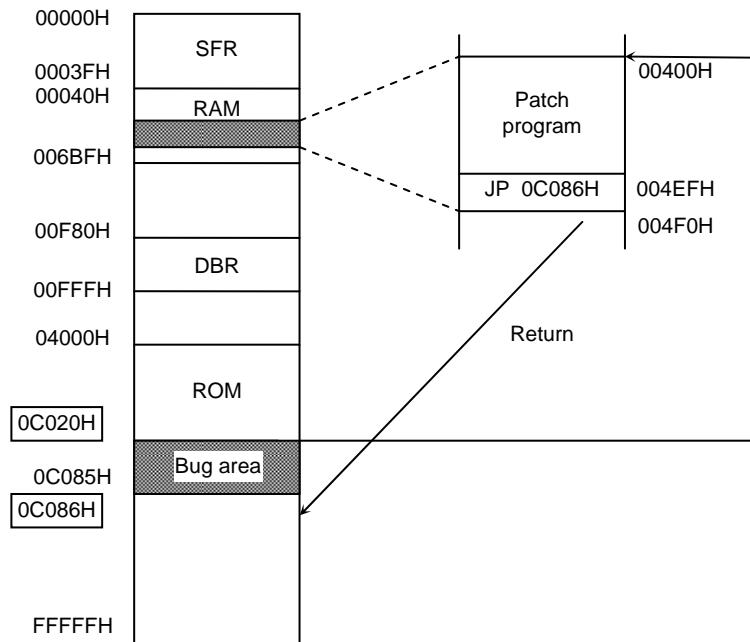

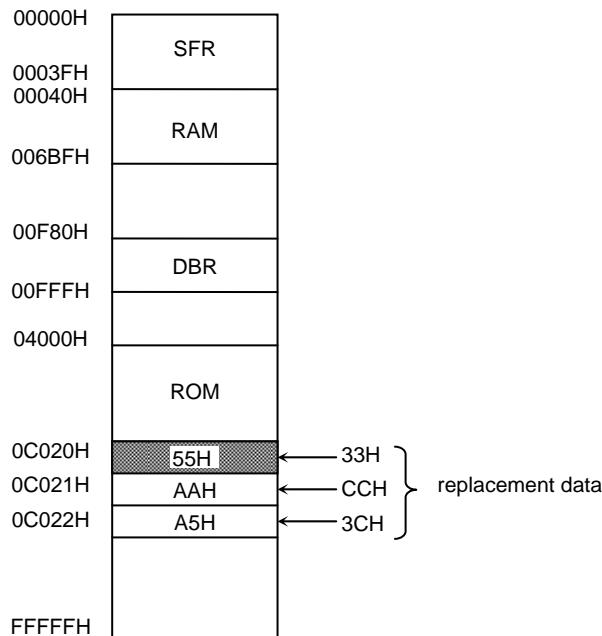

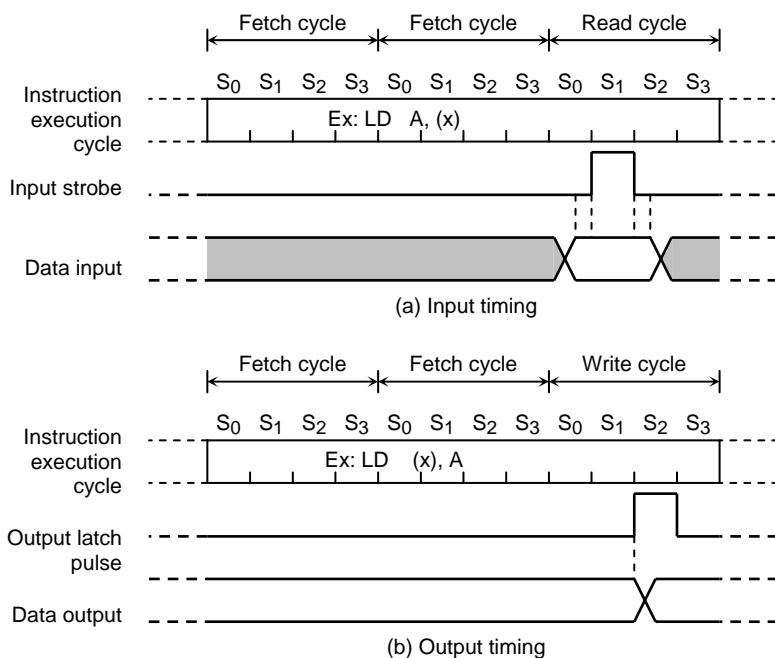

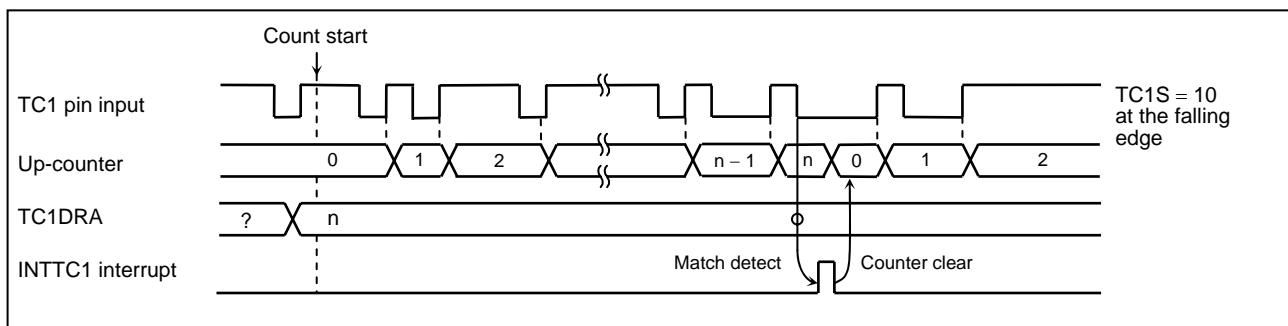

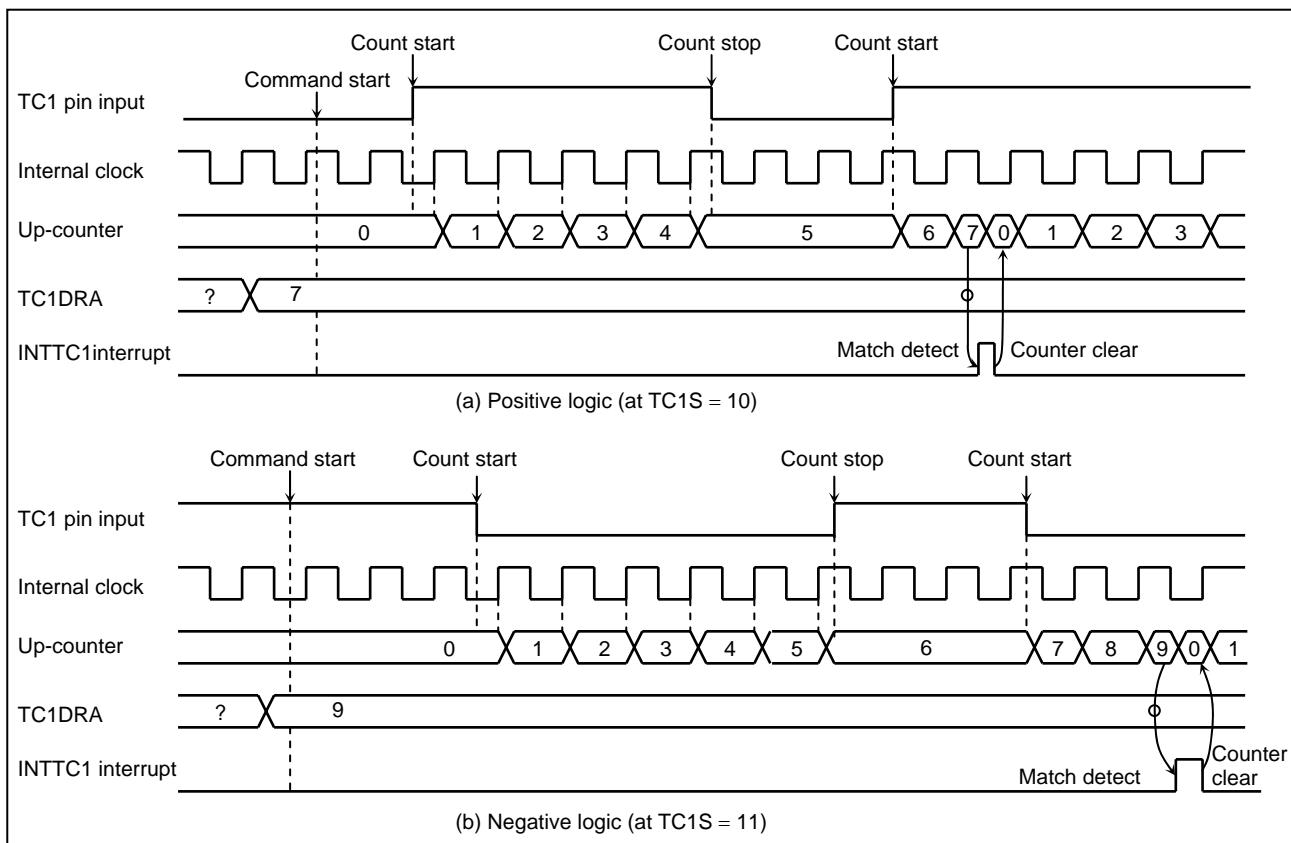

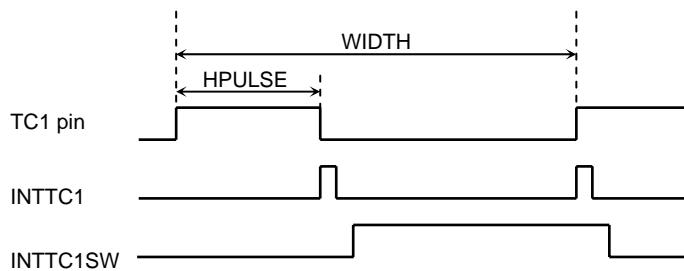

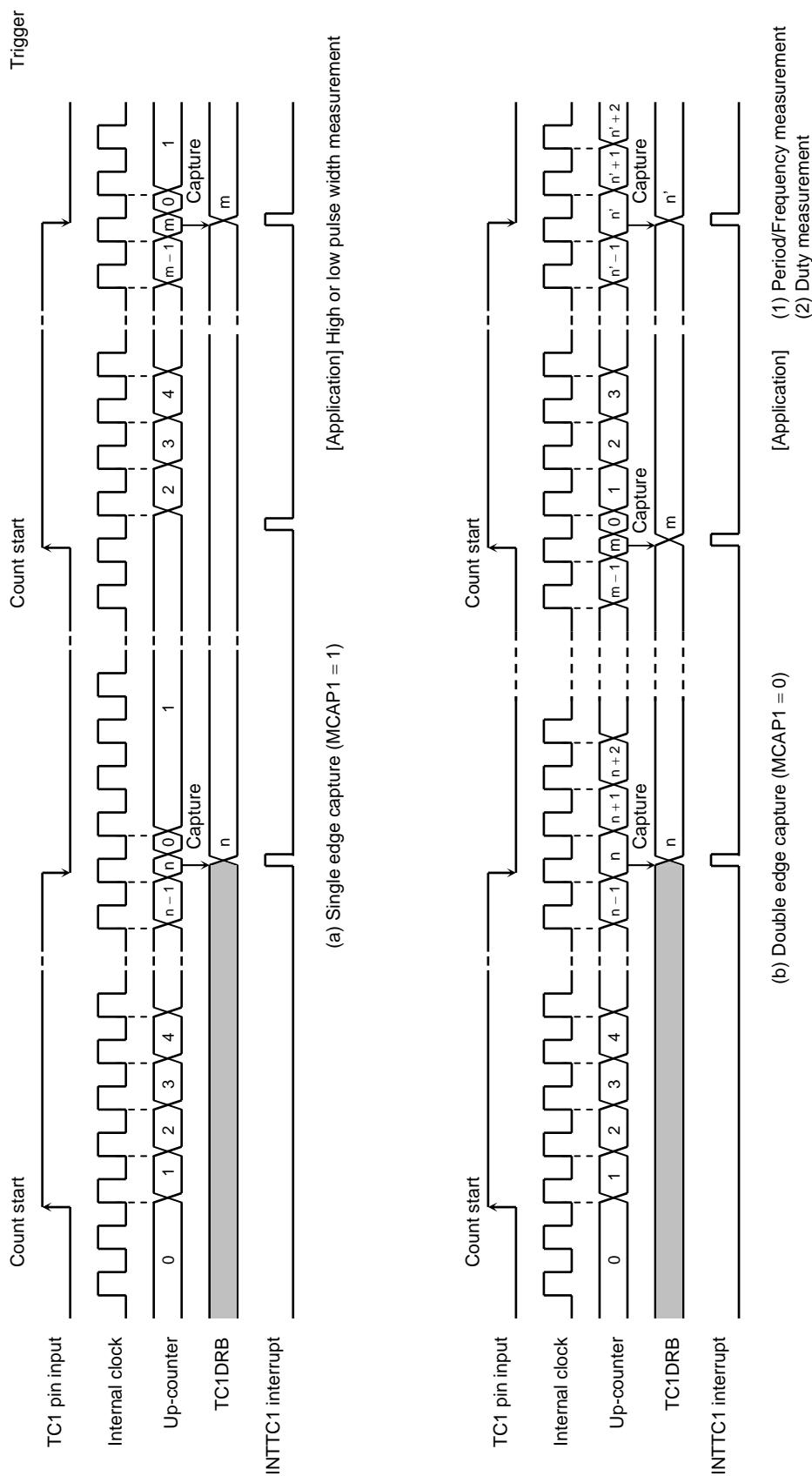

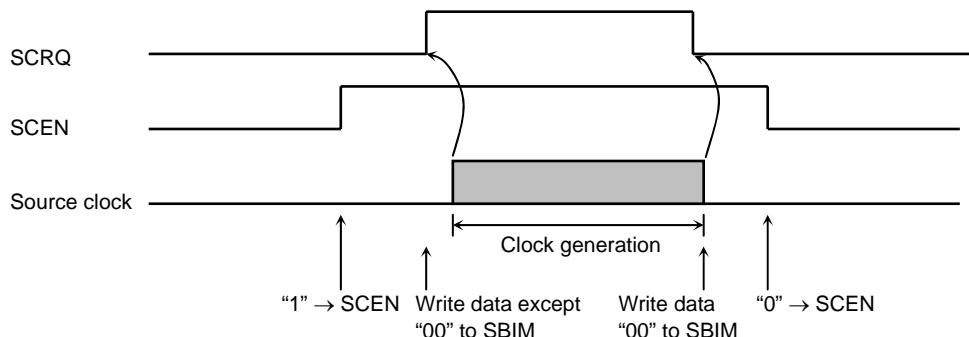

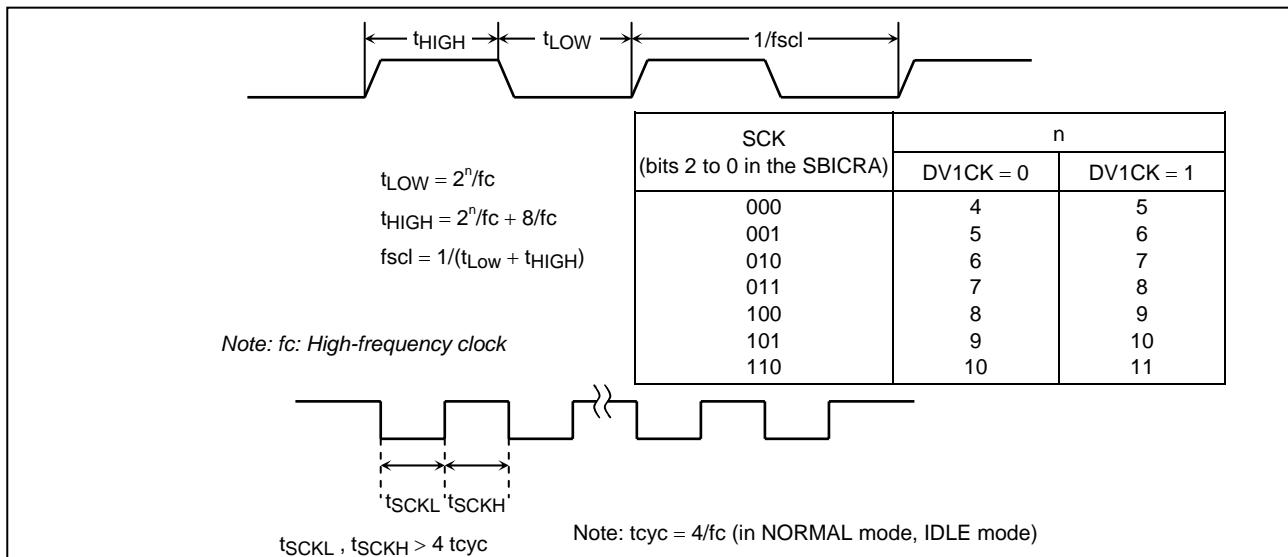

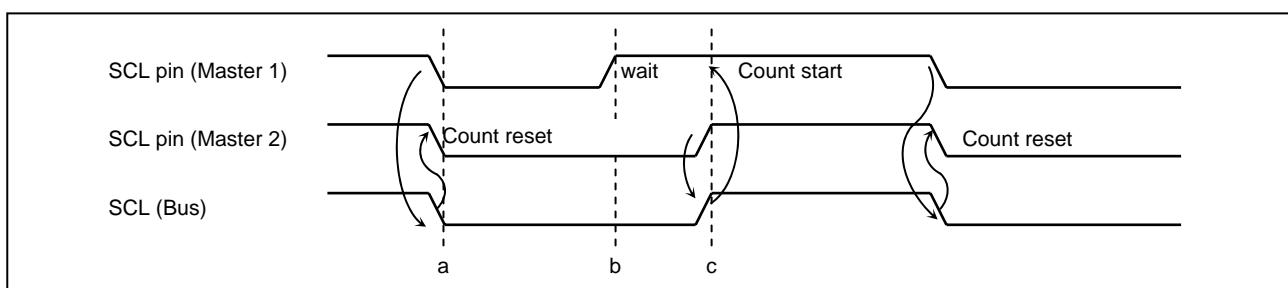

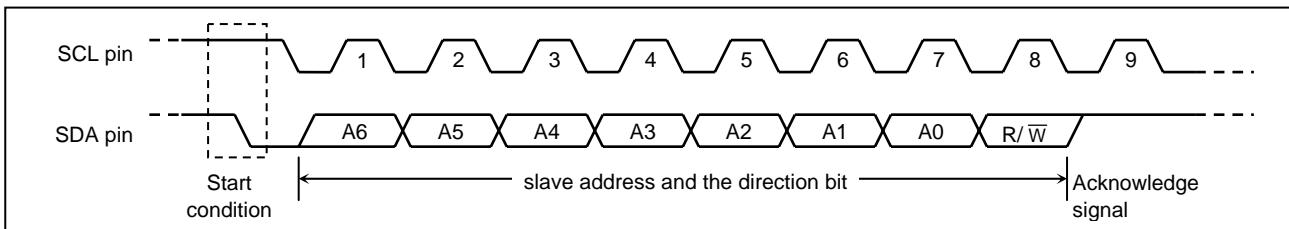

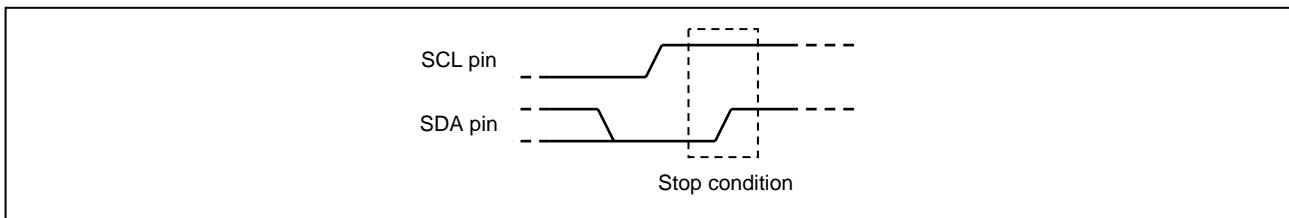

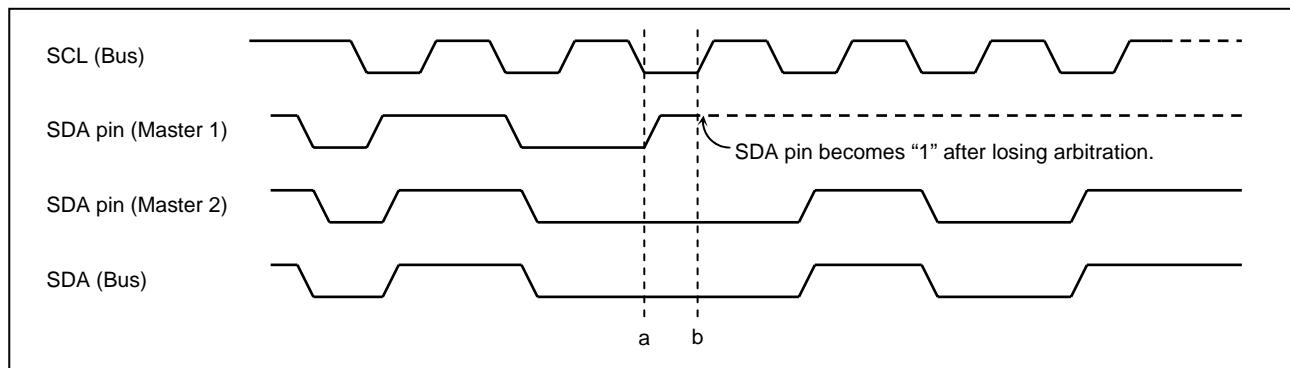

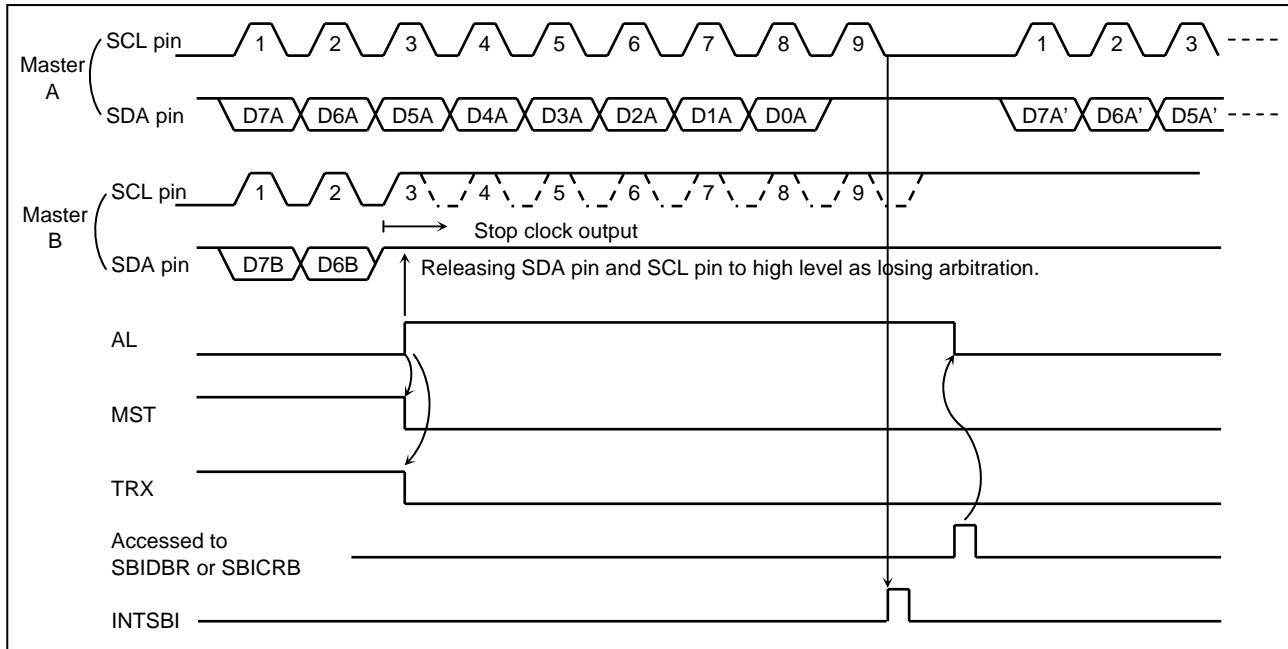

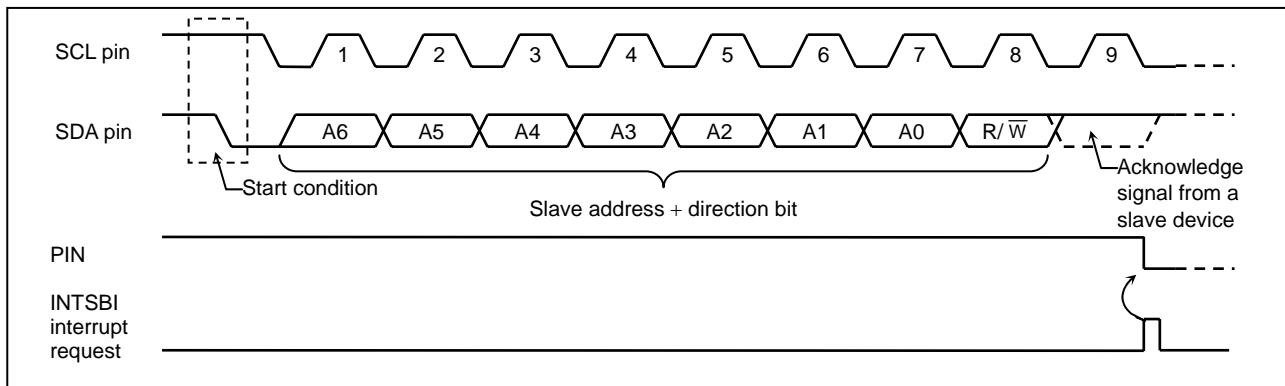

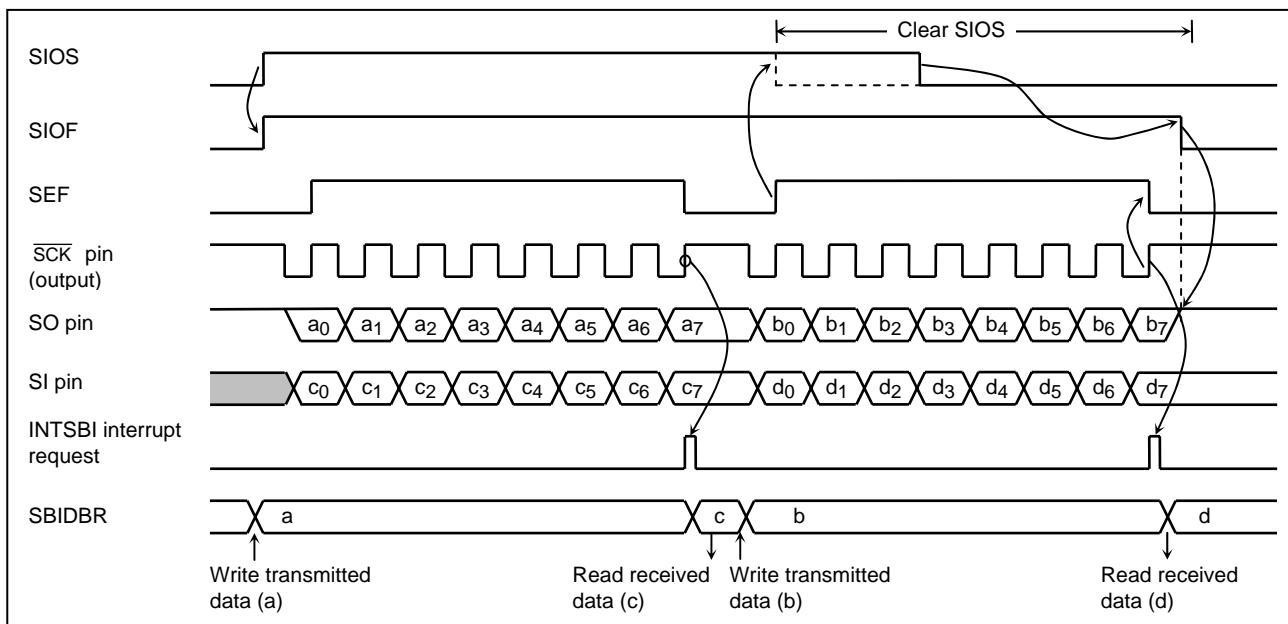

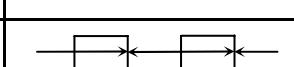

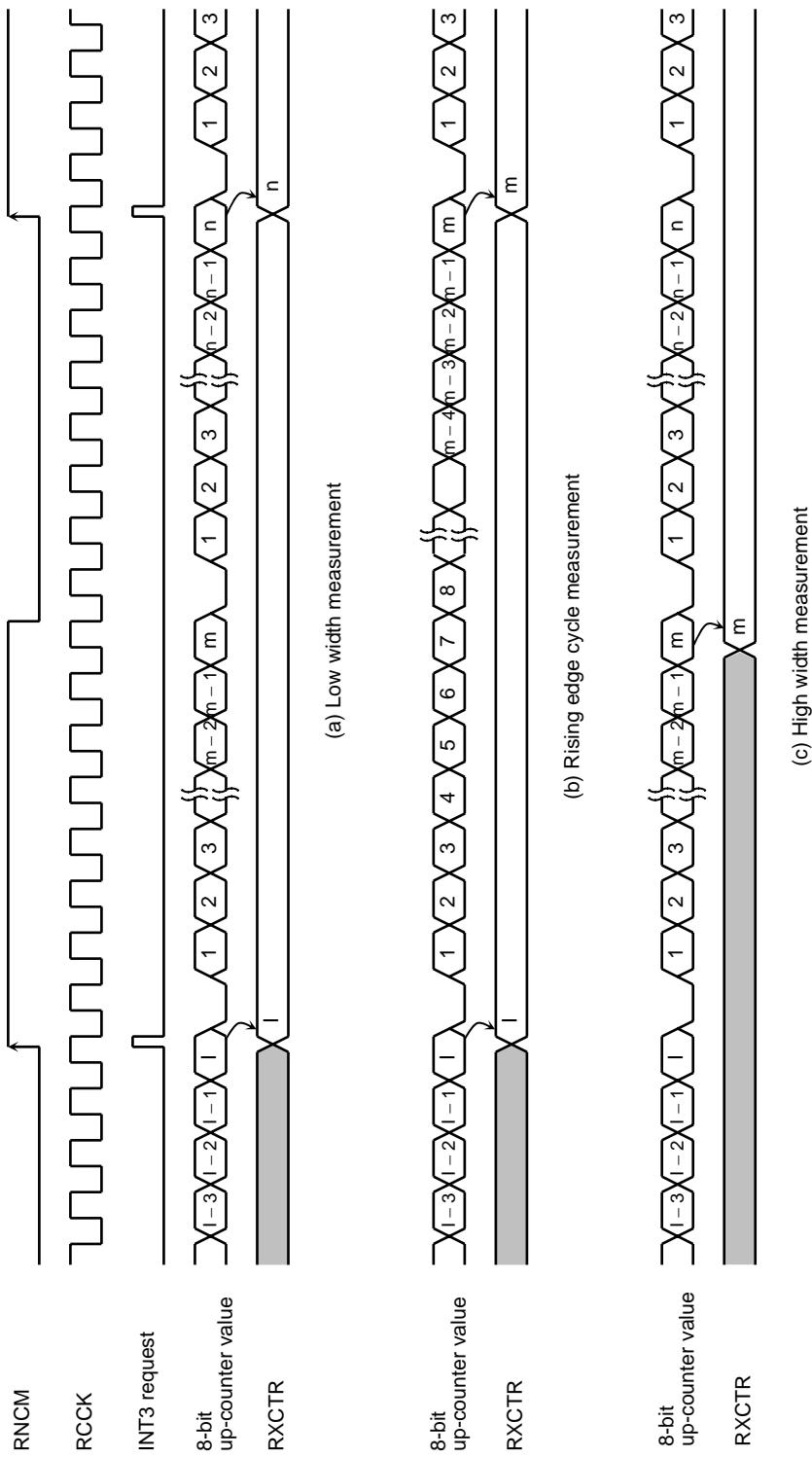

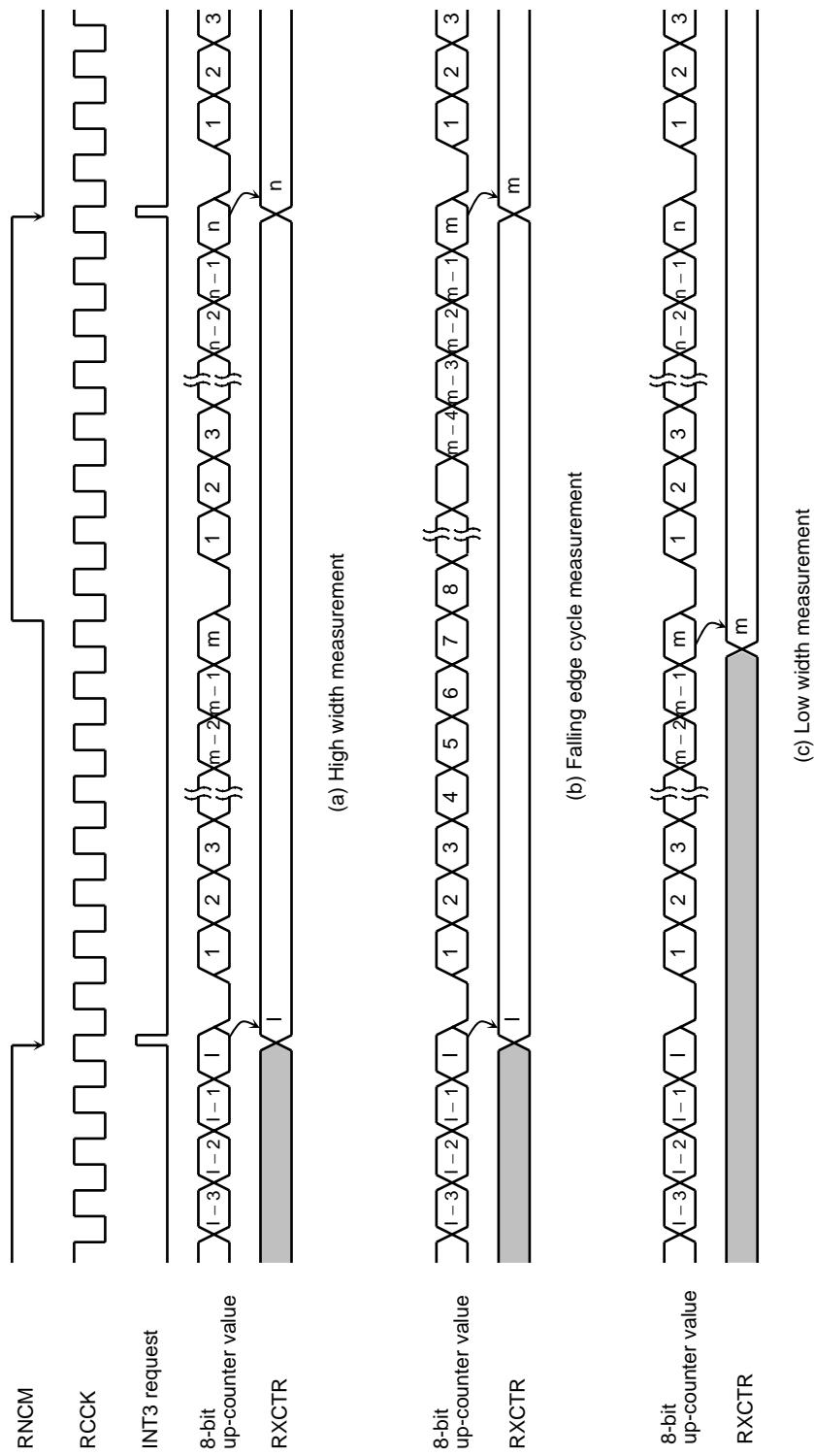

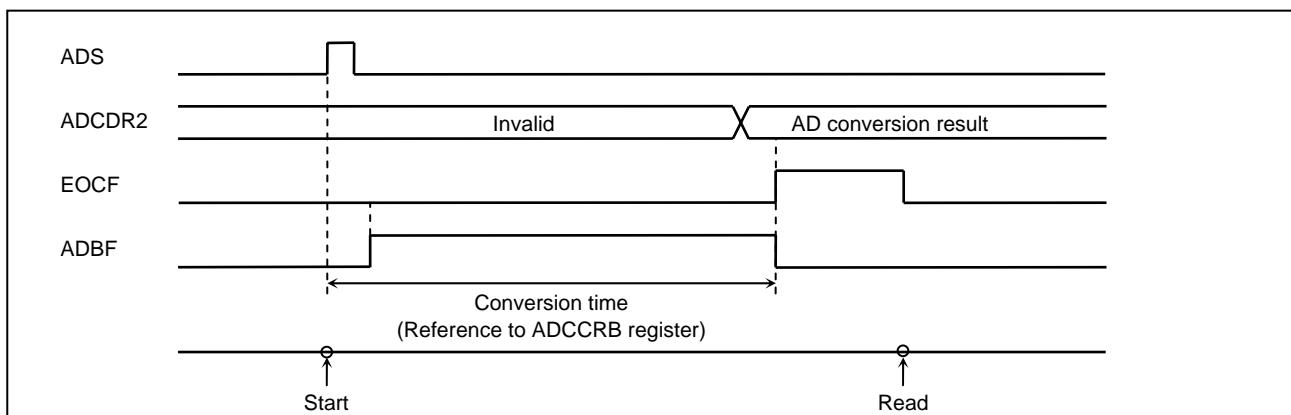

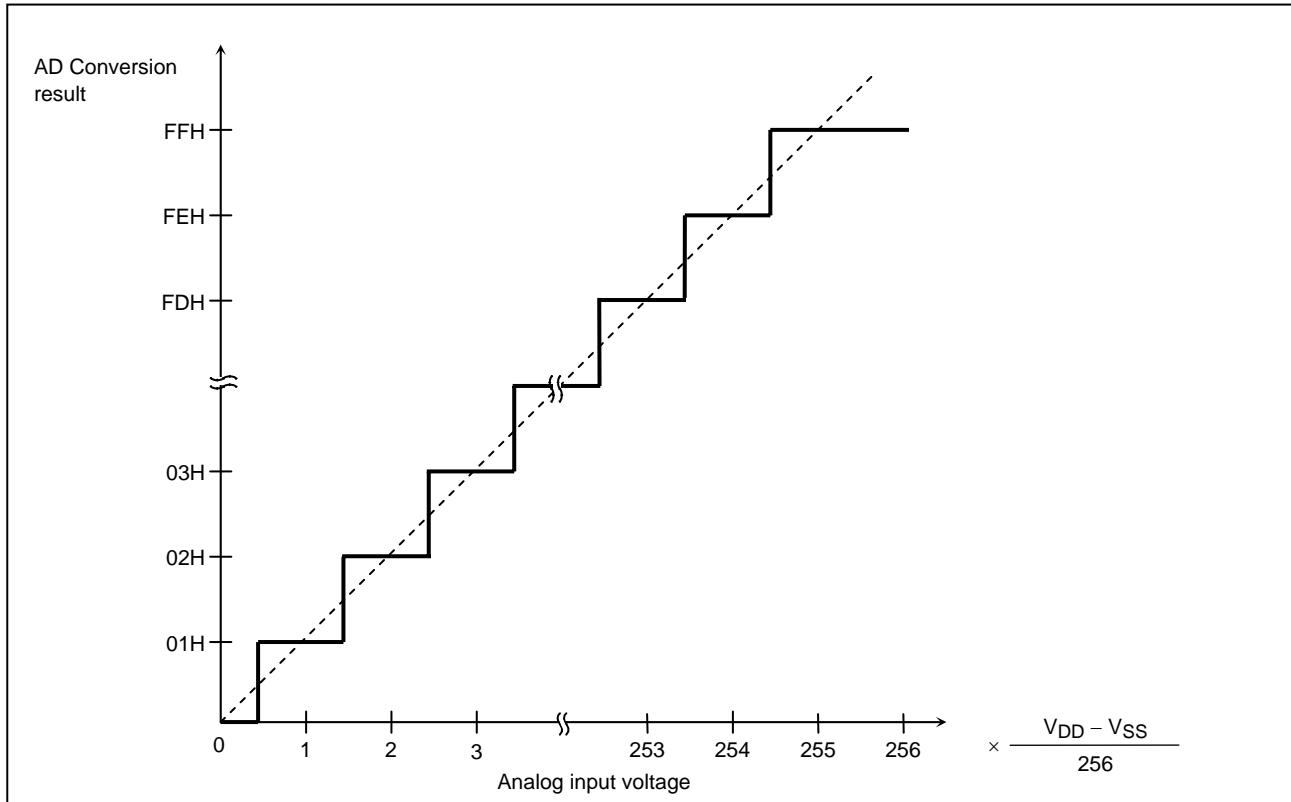

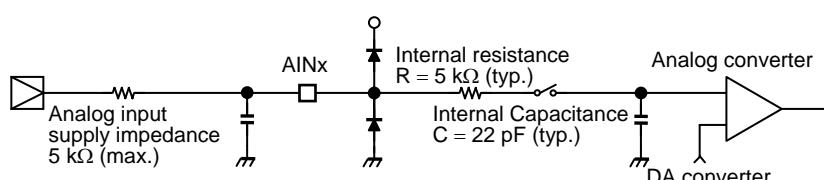

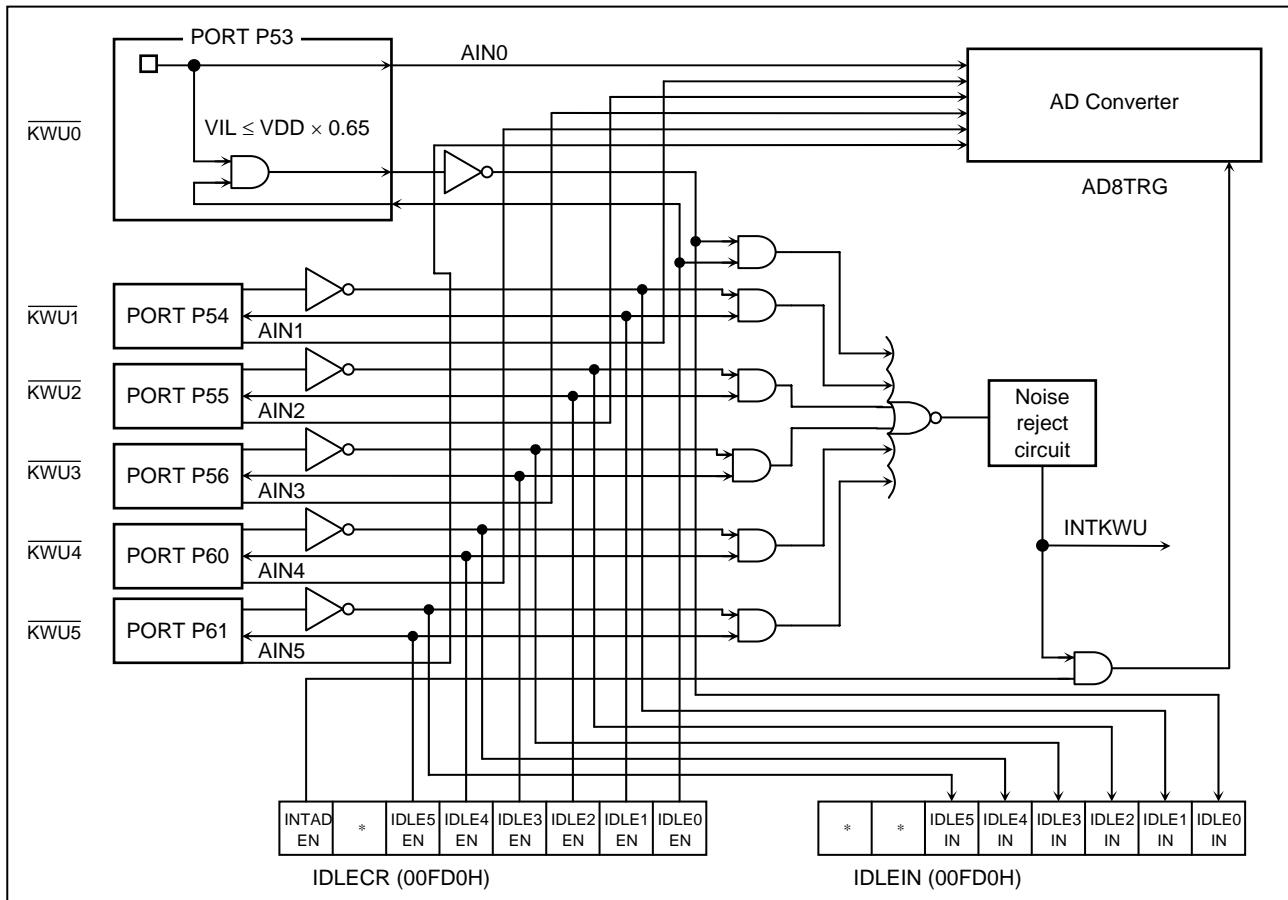

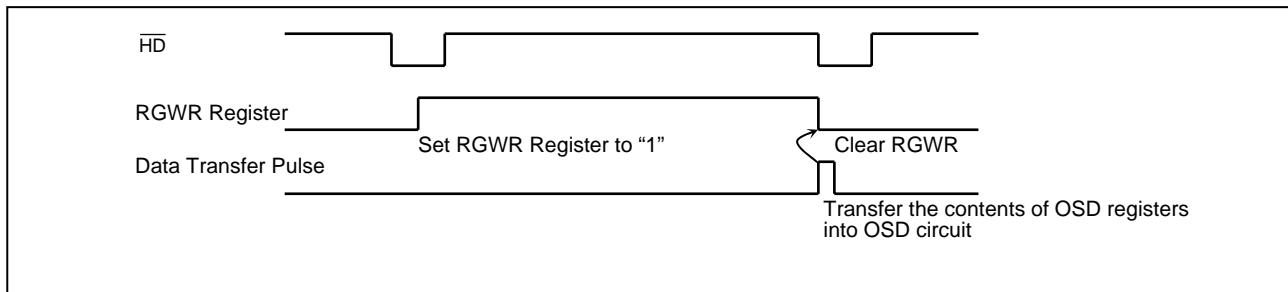

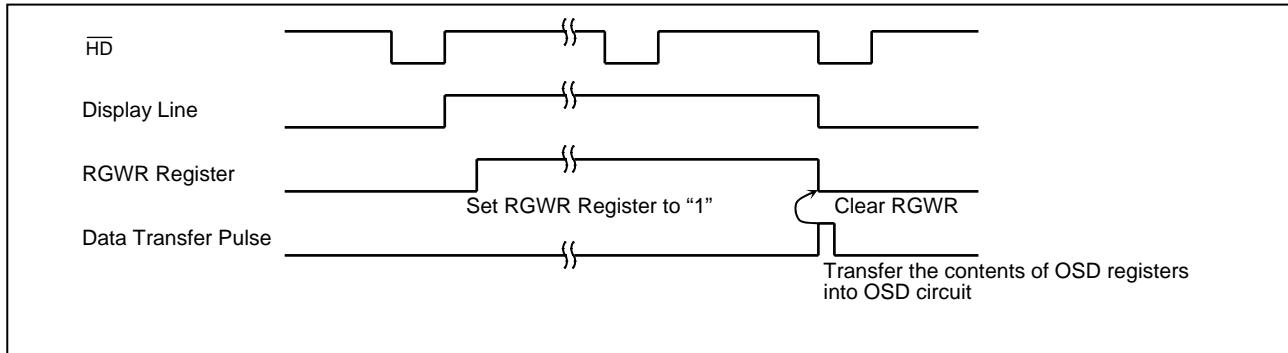

The interrupt latches are assigned to addresses 0003CH, 0003DH, 0002EH and 0002FH in the SFR. Except for IL<sub>2</sub>, each latch can be cleared to “0” individually by an instruction; however, the read-modify-write instruction such as bit manipulation or operation instructions cannot be used. When interrupt occurred during order execution, the reason is because interrupt request is cleared. Thus, interrupt requests can be canceled and initialized by the program. Note that request the interrupt latches cannot be set to “1” by an instruction. For example, it may be that each latch is cleared even if an interrupt request is generated during instruction execution.