SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

D OR PW PACKAGE (TOP VIEW)

- Conversion Time ≤ 10 μs

- 10-Bit-Resolution ADC

- Programmable Power-Down Mode . . . 1 μA

- Wide Range Single-Supply Operation of 2.7 V dc to 5.5 V dc

- Analog Input Range of 0 V to V<sub>CC</sub>

- Built-in Analog Multiplexer with 8 Analog Input Channels

- TMS320 DSP and Microprocessor SPI and QSPI Compatible Serial Interfaces

- End-of-Conversion (EOC) Flag

- Inherent Sample-and-Hold Function

- Built-In Self-Test Modes

- Programmable Power and Conversion Rate

- Asynchronous Start of Conversion for Extended Sampling

- Hardware I/O Clock Phase Adjust Input

#### description

The TLV1544 and TLV1548 are CMOS 10-bit switched-capacitor successive-approximation (SAR) analog-to-digital (A/D) converters. Each device has a chip select (CS), input-output clock (I/O CLK), data input (DATA IN) and serial data output (DATA OUT) that provide a direct 4-wire synchronous serial peripheral interface (SPI™, QSPI™) port of a host microprocessor. When interfacing with a TMS320 DSP, an additional frame sync signal (FS) indicates the start of a serial data frame. The devices allow high-speed data transfers from the host. The INV CLK input provides further timing flexibility for the serial interface.

In addition to a high-speed converter and versatile control capability, the device has an on-chip 11-channel multiplexer that can select any one of

DATA OUT  $\square$  cs 16 2 15 DATA IN ☐ REF+ 14 I/O CLK 🖂 T RFF-EOC I 13 FS  $\Box$  $V_{CC} \square$ 12 **INV CLK** A0 □ 6 11  $\Box$ GND 10 A1 🞞 □ CSTART 9 A2 🞞 **DB OR J PACKAGE** (TOP VIEW) A0 □ 10 □ V<sub>CC</sub> A1 □ 2 19 A2 🗆 3 18 I/O CLK A3 🞞 4 17 DATA IN 5 A4 □ 16 III DATA OUT  $\Box \Box \overline{\mathsf{cs}}$ A5 6 15 7 14 ☐ REF+ A6 □ Α7 8 13 REF-CSTART 9 12 TTFS IIIV CLK GND □ 10 11 **FK PACKAGE** (TOP VIEW) EOC 20 19 2 А3 I/O CLK DATA IN A4 17 DATA OUT A5 CS A6 15 **A7** REF+ 14

10 11

GND

12 13

FS REF-

eight analog inputs or any one of three internal self-test voltages. The sample-and-hold function is automatic except for the extended sampling cycle, where the sampling cycle is started by the falling edge of asynchronous CSTART. At the end of the A/D conversion, the end-of-conversion (EOC) output goes high to indicate that the conversion is complete. The TLV1544 and TLV1548 are designed to operate with a wide range of supply voltages with very low power consumption. The power saving feature is further enhanced with a software-programmed power-down mode and conversion rate. The converter incorporated in the device features differential high-impedance reference inputs that facilitate ratiometric conversion, scaling, and isolation of analog circuitry from logic and supply noise. A switched-capacitor design allows low-error conversion over the full operating temperature range.

SPI and QSPI are registered trademarks of Motorola, Inc.

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

#### description (continued)

The TLV1544 has four analog input channels while the TLV1548 has eight analog input channels. The TLV1544C and TLV1548C are characterized for operation from 0°C to 70°C. The TLV1544I and TLV1548I are characterized for operation over the full industrial temperature range of –40°C to 85°C. The TLV1548M is characterized for operation over the full military temperature range of –55°C to 125°C.

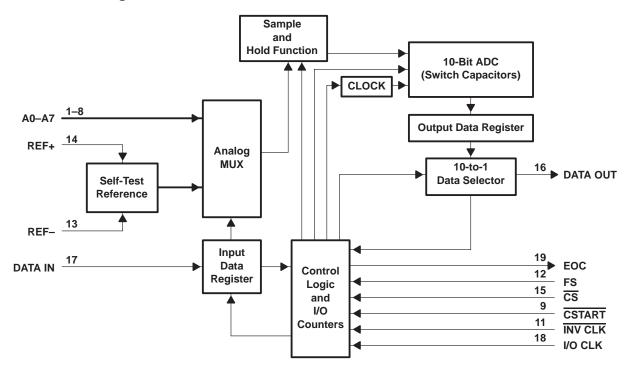

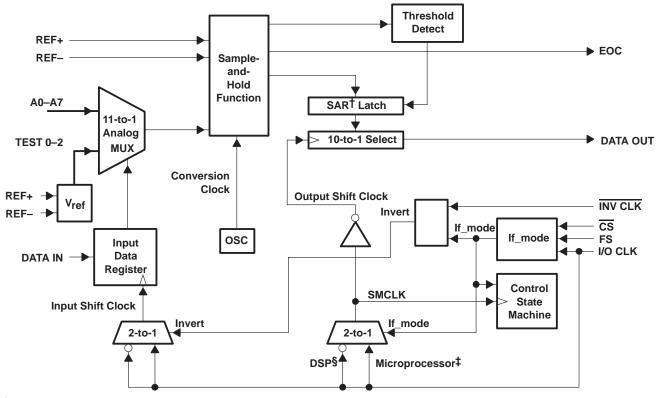

#### functional block diagram

Terminals shown are for the DB package.

#### **AVAILABLE OPTIONS**

|                |            |           | PACKAGE       |           |            |

|----------------|------------|-----------|---------------|-----------|------------|

| TA             |            |           | SMALL OUTLINE |           |            |

|                | (DB)       | (D)       | (PW)          | (J)       | (FK)       |

| 0°C to 70°C    | TLV1548CDB | TLV1544CD | TLV1544CPW    |           |            |

| -40°C to 85°C  | TLV1548IDB | TLV1544ID | TLV1544IPW    |           |            |

| −55°C to 125°C |            |           |               | TLV1548MJ | TLV1548MFK |

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{A}} \le 25^{\circ}\mbox{C}$ POWER RATING | DERATING FACTOR <sup>†</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|----------------------------------------------------|-------------------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|

| DB      | 785 mW                                             | 8.7 mW/°C                                                   | 393 mW                                | 261 mW                                | _                                      |

| D       | 799 mW                                             | 8.9 mW/°C                                                   | 399 mW                                | 266 mW                                | _                                      |

| PW      | 604 mW                                             | 6.7 mW/°C                                                   | 302 mW                                | 201 mW                                | _                                      |

| J       | 1894 mW                                            | 15.1 mW/°C                                                  | 1212 mW                               | 985 mW                                | 379 mW                                 |

| FK      | 1375 mW                                            | 11.0 mW/°C                                                  | 880 mW                                | 715 mW                                | 275 mW                                 |

<sup>†</sup> This is the inverse of the traditional junction-to-ambient thermal resistance ( $R\Theta_{JA}$ ).  $R\Theta_{JA}$  values are derived from Texas Instruments characterization data. Thermal resistance is not production tested and values are given for informational purposes only.

# TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

#### **Terminal Functions**

| TER            | RMINAL<br>NO.† | NO.‡       | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|----------------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A3<br>A4-A7 | 6–9            | 1–4<br>5–8 | ı   | Analog inputs. The analog inputs are internally multiplexed. (For a source impedance greater than 1 k $\Omega$ , the asynchronous start should be used to increase the sampling time.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CS             | 16             | 15         | I   | Chip select. A high-to-low transition on $\overline{\text{CS}}$ resets the internal counters and controls and enables DATA IN, DATA OUT, and I/O CLK within the maximum setup time. A low-to-high transition disables DATA IN, DATA OUT, and I/O CLK within the setup time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

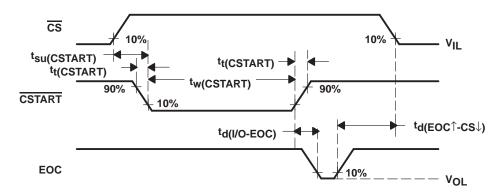

| CSTART         | 10             | 9          | ı   | Sampling/conversion start control. CSTART controls the start of the sampling of an analog input from a selected multiplex channel. A high-to-low transition starts the sampling of the analog input signal. A low-to-high transition puts the sample-and-hold function in hold mode and starts the conversion. CSTART is independent from I/O CLK and works when CS is high. The low CSTART duration controls the duration of the sampling cycle for the switched capacitor array. CSTART is tied to V <sub>CC</sub> if not used.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DATA IN        | 2              | 17         | I   | Serial data input. The 4-bit serial data selects the desired analog input and test voltage to be converted next in a normal cycle. These bits can also set the conversion rate and enable the power-down mode. When operating in the microprocessor mode, the input data is presented MSB first and is shifted in on the first four rising ( $\overline{\text{INV CLK}} = \text{V}_{\text{CC}}$ ) or falling ( $\overline{\text{INV CLK}} = \text{GND}$ ) edges of I/O CLK (after $\overline{\text{CS}} \downarrow$ ). When operating in the DSP mode, the input data is presented MSB first and is shifted in on the first four falling ( $\overline{\text{INV CLK}} = \text{V}_{\text{CC}}$ ) or rising ( $\overline{\text{INV CLK}} = \text{GND}$ ) edges of I/O CLK (after FS $\downarrow$ ). After the four input data bits have been read into the input data register, DATA IN is ignored for the remainder of the current conversion period. |

| DATA OUT       | 1              | 16         | 0   | Three-state serial output of the A/D conversion result. DATA OUT is in the high-impedance state when $\overline{\text{CS}}$ is high and active when $\overline{\text{CS}}$ is low or after FS $\downarrow$ (in DSP mode). With a valid $\overline{\text{CS}}$ signal, DATA OUT is removed from the high-impedance state and is driven to the logic level corresponding to the MSB or LSB value of the previous conversion result. DATA OUT changes on the falling (microprocessor mode) or rising (DSP mode) edge of I/O CLK.                                                                                                                                                                                                                                                                                                                                                                                                                        |

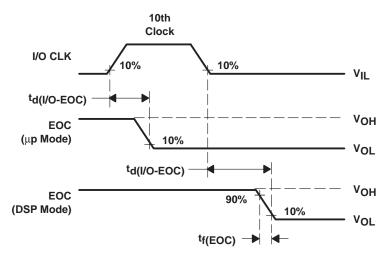

| EOC            | 4              | 19         | 0   | End of conversion. EOC goes from a high to a low logic level on the tenth rising (microprocessor mode) or tenth falling (DSP mode) edge of I/O CLK and remains low until the conversion is complete and data is ready for transfer. EOC can also indicate that the converter is busy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

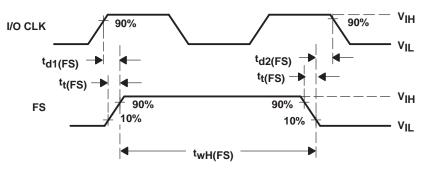

| FS             | 13             | 12         | I   | DSP frame synchronization input. FS indicates the start of a serial data frame into or out of the device. FS is tied to V <sub>CC</sub> when interfacing the device with a microprocessor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GND            | 11             | 10         |     | Ground return for internal circuitry. All voltage measurements are with respect to GND, unless otherwise noted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INV CLK        | 12             | 11         | I   | Inverted clock input. INV CLK is tied to GND when an inverted I/O CLK is used as the source of the input clock. This affects both microprocessor and DSP interfaces. INV CLK is tied to V <sub>CC</sub> if I/O CLK is not inverted. INV CLK can also invoke a built-in test mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

<sup>†</sup> Terminal numbers are for the D package.

<sup>‡</sup> Terminal numbers are for the DB, J, and FK packages.

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

#### **Terminal Functions (Continued)**

| TE      | RMINAL |      |     |                                                                                                                                                                                                                                                                                                                              |

|---------|--------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO.†   | NO.‡ | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |

| I/O CLK | 3      | 18   | ı   | Input/output clock. I/O CLK receives the serial I/O clock input in the two modes and performs the following four functions in each mode:                                                                                                                                                                                     |

|         |        |      |     | Microprocessor mode                                                                                                                                                                                                                                                                                                          |

|         |        |      |     | When INVCLK = V <sub>CC</sub> , I/O CLK clocks the four input data bits into the input data register on the first four rising edges of I/O CLK after CS↓ with the multiplexer address available after the fourth rising edge. When INV CLK = GND, input data bits are clocked in on the first four falling edges instead.    |

|         |        |      |     | On the fourth falling edge of I/O CLK, the analog input voltage on the selected multiplex input begins<br>charging the capacitor array and continues to do so until the tenth rising edge of I/O CLK except in the<br>extended sampling cycle where the duration of CSTART determines when to end the sampling cycle.        |

|         |        |      |     | Output data bits change on the first ten falling I/O clock edges regardless of the condition of INV CLK.                                                                                                                                                                                                                     |

|         |        |      |     | <ul> <li>I/O CLK transfers control of the conversion to the internal state machine on the tenth rising edge of I/O<br/>CLK regardless of the condition of INV CLK.</li> </ul>                                                                                                                                                |

|         |        |      |     | Digital signal processor (DSP) mode                                                                                                                                                                                                                                                                                          |

|         |        |      |     | When INV CLK = V <sub>CC</sub> , I/O CLK clocks the four input data bits into the input data register on the first four falling edges of I/O CLK after FS↓ with the multiplexer address available after the fourth falling edges. When INV CLK = GND, input data bits are clocked in on the first four rising edges instead. |

|         |        |      |     | On the fourth rising edge of I/O CLK, the analog input voltage on the selected multiplex input begins<br>charging the capacitor array and continues to do so until the tenth falling edge of I/O CLK except in the<br>extended sampling cycle where the duration of CSTART determines when to end the sampling cycle.        |

|         |        |      |     | <ul> <li>Output data MSB shows after FS↓ and the rest of the output data bits change on the first ten rising I/O CLK edges regarless of the condition of INV CLK.</li> </ul>                                                                                                                                                 |

|         |        |      |     | <ul> <li>I/O CLK transfers control of the conversion to the internal state machine on the tenth falling edge of I/O<br/>CLK regardless of the condition of INV CLK.</li> </ul>                                                                                                                                               |

| REF+    | 15     | 14   | ı   | Upper reference voltage (nominally $V_{CC}$ ). The maximum input voltage range is determined by the difference between the voltages applied to REF+ and REF $-$ .                                                                                                                                                            |

| REF-    | 14     | 13   | Ι   | Lower reference voltage (nominally ground)                                                                                                                                                                                                                                                                                   |

| VCC     | 5      | 20   | I   | Positive supply voltage                                                                                                                                                                                                                                                                                                      |

<sup>†</sup> Terminal numbers are for the D package.

#### detailed description

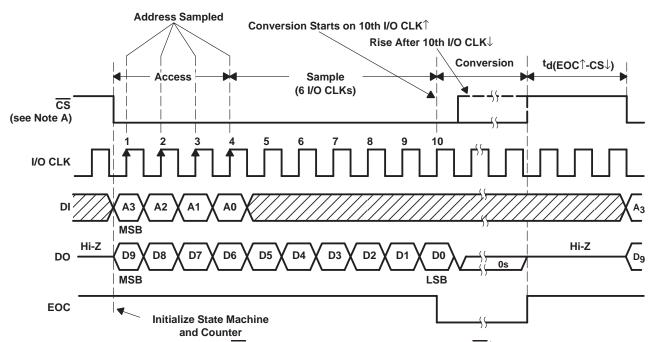

Initially, with  $\overline{\text{CS}}$  high (inactive), DATA IN and I/O CLK are disabled and DATA OUT is in the high-impedance state. When the serial interface takes  $\overline{\text{CS}}$  low (active), the conversion sequence begins with the enabling of I/O CLK and DATA IN and the removal of DATA OUT from the high-impedance state. The host then provides the 4-bit channel address to DATA IN and the I/O clock sequence to I/O CLK. During this transfer, the host serial interface also receives the previous conversion result from DATA OUT. I/O CLK receives an input sequence from the host that is from 10 to 16 clocks long. The first four valid I/O CLK cycles load the input data register with the 4-bit input data on DATA IN that selects the desired analog channel. The next six clock cycles provide the control timing for sampling the analog input. Sampling of the analog input is held after the first valid I/O CLK sequence of ten clocks. The tenth clock edge also takes EOC low and begins the conversion. The exact locations of the I/O clock edges depend on the mode of operation.

#### serial interface

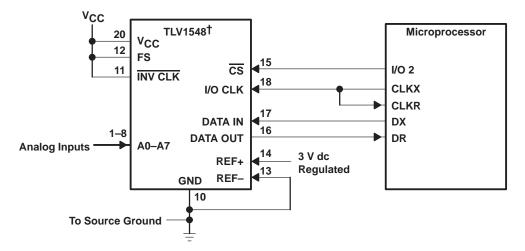

The TLV1548 is compatible with generic microprocessor serial interfaces such as SPI and QSPI, and a TMS320 DSP serial interface. The internal latched flag If\_mode is generated by sampling the state of FS at the falling edge of  $\overline{CS}$ . If\_mode is set to one (for microprocessor) when FS is high at the falling edge of  $\overline{CS}$ , and If\_mode is cleared to zero (for DSP) when FS is low at the falling edge of  $\overline{CS}$ . This flag controls the multiplexing of I/O CLK and the state machine reset function. FS is pulled high when interfacing with a microprocessor.

<sup>&</sup>lt;sup>‡</sup> Terminal numbers are for the DB, J, and FK packages.

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

#### I/O CLK

The I/O CLK can go up to 10 MHz for most of the voltage range when fast I/O is possible. The maximum I/O CLK is limited to 2.8 MHz for a supply voltage range from 2.7 V. Table 1 lists the maximum I/O CLK frequencies for all different supply voltage ranges. This also depends on input source impedance. For example, I/O CLK speed faster than 2.39 MHz is achievable if the input source impedance is less than 1 k $\Omega$ .

**MAXIMUM INPUT SOURCE IMPEDANCE** I/O CLK VCC RESISTANCE (Max)  $1 \text{ k}\Omega$ 2.39 MHz 2.7 V 5 K  $100 \Omega$ 2.81 MHz  $1 \text{ k}\Omega$ 7.18 MHz 4.5 V 1 K 100  $\Omega$ 10 MHz

Table 1. Maximum I/O CLK Frequency

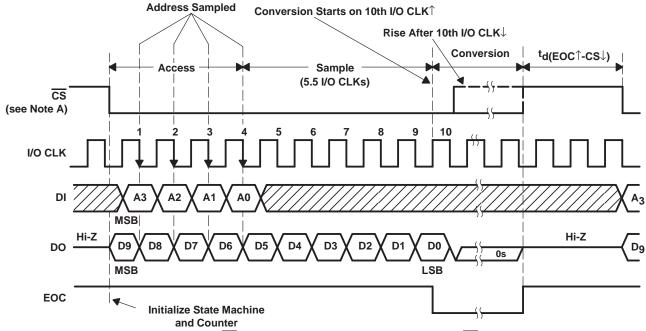

#### microprocessor serial interface

Input data bits from DATA IN are clocked in on the first four rising edges of the I/O CLK sequence if INV CLK is held high when the device is in microprocessor interface mode. Input data bits are clocked in on the first four falling edges of the I/O CLK sequence if INV CLK is held low. The MSB of the previous conversion appears on DATA OUT on the falling edge of CS. The remaining nine bits are shifted out on the next nine edges (depending on the state of INV CLK) of I/O CLK. Ten bits of data are transmitted to the host through DATA OUT.

A minimum of 9.5 clock pulses is required for the conversion to begin. On the tenth clock rising edge, the EOC output goes low and returns to the high logic level when the conversion is complete; then the result can be read by the host. On the tenth clock falling edge, the internal logic takes DATA OUT low to ensure that the remaining bit values are zero if the I/O CLK transfer is more than ten clocks long.

CS is inactive (high) between serial I/O CLK transfers. Each transfer takes at least ten I/O CLK cycles. The falling edge of CS begins the sequence by removing DATA OUT from the high-impedance state. The rising edge of CS ends the sequence by returning DATA OUT to the high-impedance state within the specified delay time. Also, the rising edge of CS disables I/O CLK and DATA IN within a setup time. A conversion does not begin until the tenth I/O CLK rising edge.

A high-to-low transition on  $\overline{\text{CS}}$  within the specified time during an ongoing cycle aborts the cycle, and the device returns to the initial state (the output data register holds the previous conversion result).  $\overline{\text{CS}}$  should not be taken low close to completion of conversion because the output data can be corrupted.

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

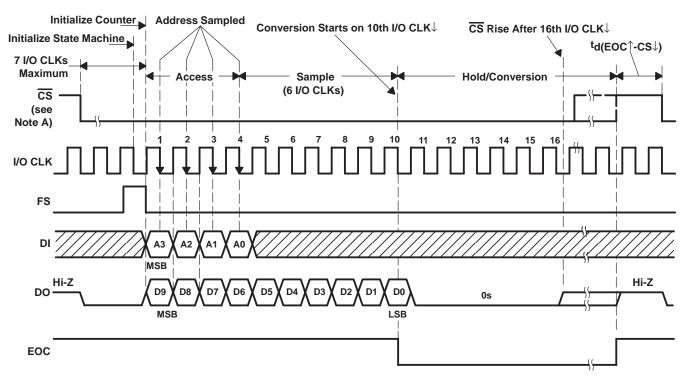

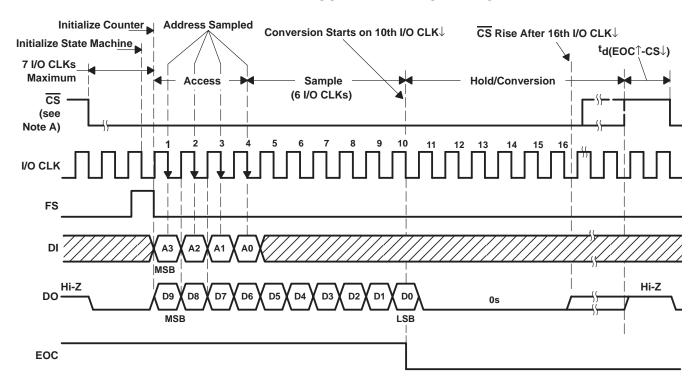

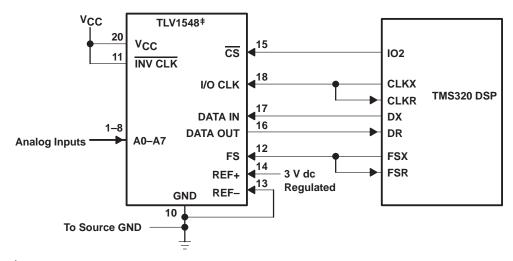

#### **DSP** interface

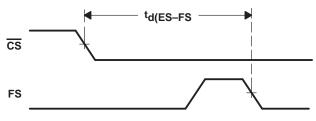

The TLV1544/1548 can also interface with a DSP, from the TMS320 family for example, through a serial port. The analog-to-digital converter (ADC) serves as a slave device where the DSP supplies FS and the serial I/O CLK. Transmit and receive operations are concurrent. The falling edge of FS must occur no later than seven I/O CLK periods after the falling edge of  $\overline{\text{CS}}$ .

DSP I/O cycles differ from microprocessor I/O cycles in the following ways:

- When interfaced with a DSP, the output data MSB is available after FS↓. The remaining output data changes on the rising edge of I/O CLK. The input data is sampled on the first four falling edges of I/O CLK after FS↓ and when INV CLK is high, or the first four rising edges of I/O CLK after FS↓ and when INV CLK is low. This operation is inverted when interfaced with a microprocessor.

- A new DSP I/O cycle is started on the rising edge of I/O CLK after the rising edge of FS. The internal state

machine is reset on each falling edge of I/O CLK when FS is high. This operation is opposite when interfaced

with a microprocessor.

- The TLV1544/1548 supports a 16-clock cycle when interfaced with a DSP. The output data is padded with six trailing zeros when it is operated in DSP mode.

Table 2. TLV1544/TLV1548 Serial Interface Modes

| 1/0      | INTERFACE MODE                                                                                      |                                                                                                                                                                        |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1/0      | MICROPROCESSOR ACTION                                                                               | DSP ACTION                                                                                                                                                             |  |  |  |

| CS↓      | Initializes counter                                                                                 | Samples state of FS                                                                                                                                                    |  |  |  |

| CS↑      | Resets state machine and disable I/O                                                                | Disables I/O                                                                                                                                                           |  |  |  |

| FS       | Connects to V <sub>CC</sub>                                                                         | Connects to DSP FSX output Initializes the state machine at each CLK↓ after FS↑ Starts a new cycle at each CLK↑ following the initialization (initializes the counter) |  |  |  |

| I/O CLK  | Starts sampling of the analog input started at fourth I/O CLK↑ Conversion started at tenth I/O CLK↑ | Starts sampling of the analog input at fourth I/O CLK↓ Starts sampling of the analog input at tenth I/O CLK↓                                                           |  |  |  |

| DATA IN  | Samples input data on I/O CLK↑ (INV CLK high) Samples input data on I/O CLK↓ (INV CLK low)          | Samples input data at I/O CLK↓ (INV CLK high) Samples input data at I/O CLK↑ (INV CLK low)                                                                             |  |  |  |

| DATA OUT | Makes MSB available on <del>CS</del> ↓<br>Changes remaining data on I/O CLK↓                        | Makes MSB available FS↓ Changes remaining data at each following I/O CLK↑ after FS↓                                                                                    |  |  |  |

#### input data bits

DATA IN is internally connected to a 4-bit serial input data register. The input data selects a different mode or selects different analog input channels. The host provides the data word with the MSB first. Each data bit clocks in on the edge (rising or falling depending on the status of INV CLK and FS) of the I/O CLK sequence. The input clock can be inverted by grounding INV CLK (see Table 3 for the list of software programmed operations set by the input data).

Table 3. TLV1544/1548 Software-Programmed Operation Modes

|                                                                       | INPUT DAT | A BYTE     |                                                   |

|-----------------------------------------------------------------------|-----------|------------|---------------------------------------------------|

| FUNCTION SELECT                                                       | A3 – A    | <b>A</b> 0 | COMMENT                                           |

|                                                                       | BINARY    | HEX        |                                                   |

| Analog channel A0 for TLV1548 selected                                | 0000b     | 0h         | Channel 0 for TLV1544                             |

| Analog channel A1 for TLV1548 selected                                | 0001b     | 1h         |                                                   |

| Analog channel A2 for TLV1548 selected                                | 0010b     | 2h         | Channel 1 for TLV1544                             |

| Analog channel A3 for TLV1548 selected                                | 0011b     | 3h         |                                                   |

| Analog channel A4 for TLV1548 selected                                | 0100b     | 4h         | Channel 2 for TLV1544                             |

| Analog channel A5 for TLV1548 selected                                | 0101b     | 5h         |                                                   |

| Analog channel A6 for TLV1548 selected                                | 0110b     | 6h         | Channel 3 for TLV1544                             |

| Analog channel A7 for TLV1548 selected                                | 0111b     | 7h         |                                                   |

| Software power down set                                               | 1000b     | 8h         | No conversion result (cleared by any access)      |

| Fast conversion rate (10 μs) set                                      | 1001b     | 9h         | No conversion result (cleared by setting to fast) |

| Slow conversion rate (40 µs) set                                      | 1010b     | Ah         | No conversion result (cleared by setting to slow) |

| Self-test voltage (V <sub>ref+</sub> - V <sub>ref-</sub> )/2 selected | 1011b     | Bh         | Output result = 200h                              |

| Self-test voltage V <sub>ref</sub> _ selected                         | 1100b     | Ch         | Output result = 000h                              |

| Self-test voltage V <sub>ref +</sub> selected                         | 1101b     | Dh         | Output result = 3FFh                              |

| Reserved                                                              | 1110b     | Eh         | No conversion result                              |

| Reserved                                                              | 1111b     | Fh         | No conversion result                              |

#### analog inputs and internal test voltages

The eight analog inputs and the three internal test inputs are selected by the 11-channel multiplexer according to the input data bit as shown in Table 3. The input multiplexer is a break-before-make type to reduce input-to-input noise injection resulting from channel switching.

The device can be operated in two distinct sampling modes: normal sampling mode (fixed sampling time) and extended sampling mode (flexible sampling time). When  $\overline{\text{CSTART}}$  is held high, the device is operated in normal sampling mode. When operated in normal sampling mode, sampling of the analog input starts on the rising edge of the fourth I/O CLK pulse in the microprocessor interface mode (and on the fourth falling edge of I/O CLK in the DSP interface mode). Sampling continues for 6 I/O CLK periods. The sample is held on the falling edge of the tenth I/O CLK pulse in the microprocessor interface mode. The sample is held on the falling edge of the tenth I/O CLK pulse in the DSP interface mode. The three test inputs are applied to the multiplexer, then sampled and converted in the same manner as the external analog inputs.

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

#### converter

The CMOS threshold detector in the successive-approximation conversion system determines the value of each bit by examining the charge on a series of binary-weighted capacitors (see Figure 1). In the first phase of the conversion process, the analog input is sampled by closing the  $S_C$  switch and all  $S_T$  switches simultaneously. This action charges all of the capacitors to the input voltage.

In the next phase of the conversion process, all  $S_T$  and  $S_C$  switches are opened and the threshold detector begins identifying bits by identifying the charge (voltage) on each capacitor relative to the reference (REF –) voltage. In the switching sequence, ten capacitors are examined separately until all ten bits are identified and then the charge-convert sequence is repeated. In the first step of the conversion phase, the threshold detector looks at the first capacitor (weight = 512). Node 512 of this capacitor is switched to the REF+ voltage, and the equivalent nodes of all the other capacitors on the ladder are switched to REF –. If the voltage at the summing node is greater than the trip point of the threshold detector (approximately one-half  $V_{CC}$ ), a bit 0 is placed in the output register and the 512-weight capacitor is switched to REF –. If the voltage at the summing node is less than the trip point of the threshold detector, a bit 1 is placed in the register and the 512-weight capacitor remains connected to REF + through the remainder of the successive-approximation process. The process is repeated for the 256-weight capacitor, the 128-weight capacitor, and so forth down the line until all bits are counted.

With each step of the successive-approximation process, the initial charge is redistributed among the capacitors. The conversion process relies on charge redistribution to count and weigh the bits from MSB to LSB.

Figure 1. Simplified Model of the Successive-Approximation System

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

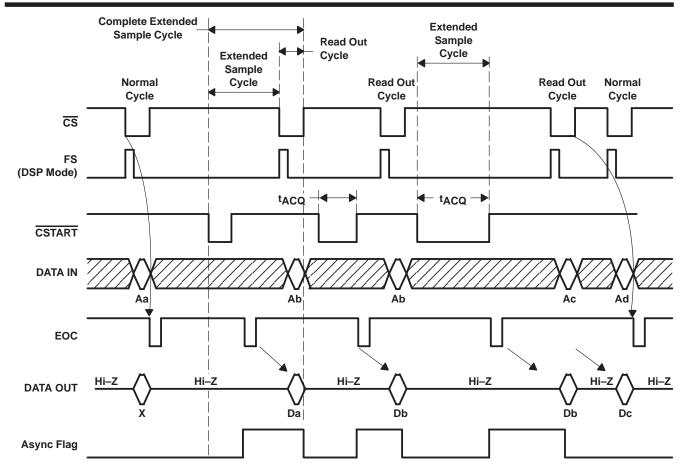

#### extended sampling, asynchronous start of sampling: CSTART operation

The extended sampling mode of operation programs the acquisition time ( $t_{ACQ}$ ) of the sample-and-hold circuit. This allows the analog inputs of the device to be directly interfaced to a wide range of input source impedances. The extended sampling mode consumes higher power depending on the duration of the sampling period chosen.

CSTART controls the sampling period and starts the conversion. The falling edge of CSTART initiates the sampling period of a preset channel. The low time of CSTART controls the acquisition time of the input sample-and-hold circuit. The sample is held on the rising edge of CSTART. Asserting CSTART causes the converter to perform a new sample of the signal on the preset valid MUX channel (one of the eight) and discard the current conversion result ready for output. Sampling continues as long as CSTART is active (negative). The rising edge of CSTART ends the sampling cycle. The conversion cycle starts two internal system clocks after the rising edge of CSTART.

Once the conversion is complete, the processor can initiate a normal I/O cycle to read the conversion result and set the MUX address for the next conversion. Since the internal flag AsyncFlag is set high, this flag setting indicates the cycle is an output cycle, so no conversion is performed during the cycle. The internal state machine tests the AsyncFlag on the falling edge of  $\overline{CS}$ . AsyncFlag is set high at the rising edge of  $\overline{CS}$ . A conversion cycle follows a sampling cycle only if AsyncFlag is tested as low at the falling edge of  $\overline{CS}$ . As shown in Figure 2, an asynchronous I/O cycle can be removed by two consecutive normal I/O cycles.

Table 4. TLV1544/1548 Hardware Configuration for Different Operating Modes

| OPERATING MODES            | CS   | CSTART | AsyncFlag at CS↓ | ACTION                                                                         |  |  |

|----------------------------|------|--------|------------------|--------------------------------------------------------------------------------|--|--|

| Normal sampling            | Low  | High   | Low              | Fixed 6 I/O CLK sampling, synchronous conversion follows                       |  |  |

| Normal I/O (read out only) | Low  | High   | High             | No sampling, no conversion                                                     |  |  |

| Extended sampling          | High | Low    | N/A              | Flexible sampling period controlled by CSTART, asynchronous conversion follows |  |  |

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

NOTES: A. Aa = Address for input channel a.

B. Da = Conversion result from channel a.

Figure 2. Extended Sampling Operation

#### reference voltage inputs

There are two reference inputs used with the TLV1544/TLV1548, REF+ and REF-. These voltage values establish the upper and lower limits of the analog inputs to produce a full-scale and zero-scale reading respectively. The values of REF+, REF-, and the analog input should not exceed the positive supply or be lower than GND consistent with the specified absolute maximum ratings. The digital output is at full scale when the input signal is equal to or higher than REF+ and is at zero when the input signal is equal to or lower than REF-.

#### programmable conversion rate

The TLV1544/TLV1548 offers two conversion rates to maximize battery life when high-speed operation is not necessary. The conversion rate is programmable. Once the conversion rate has been selected, it takes effect immediately in the same cycle and stays at the same rate until the other rate is chosen. The conversion rate should be set at power up. Activation and deactivation of the power-down state (digital logic active) has no effect on the preset conversion rate.

|                       | CONVERSION TIME.  | AVAILABLE VCC  |            | TYPICAL SUPPLY CURRENT, ICC |  |               |  |

|-----------------------|-------------------|----------------|------------|-----------------------------|--|---------------|--|

| CONVERSION RATE       | t <sub>conv</sub> | RANGE          | INPUT DATA | OPERATING                   |  | POWER<br>DOWN |  |

| Fast conversion speed | 7 μs typ          | 5.5 V to 3.3 V | 9h         | 0.6 mA typ 1.5 mA max       |  | 1 μA typ      |  |

| Slow conversion speed | 15 μs typ         | 5.5 V to 2.7 V | Ah         | 0.4 mA typ 1 mA max         |  | 1 μA typ      |  |

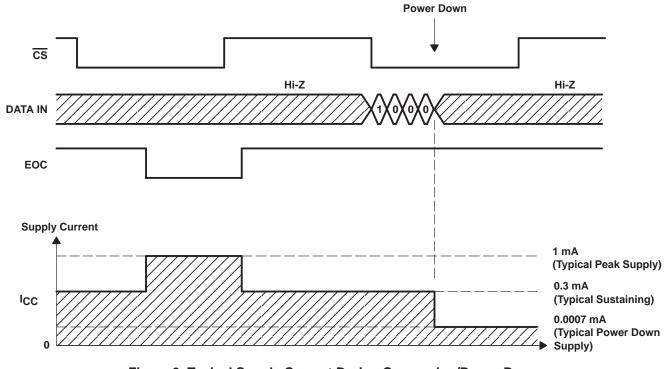

#### programmable power-down state

The device is put into the power-down state by writing 8h to DATA IN. The power-up state is restored during the next active access by pulling  $\overline{CS}$  low. The conversion rate selected before the device is put into the power-down state is not affected by the power-down mode. Power-down can be used to achieve even lower power consumption. This is because the sustaining power (when not converting) is only 1.3 mA maximum and standby power is only 1  $\mu$ A maximum. (By averaging out the power consumption can be much lower than the 1 mA peak when the conversion throughput is lower.)

Figure 3. Typical Supply Current During Conversion/Power Down

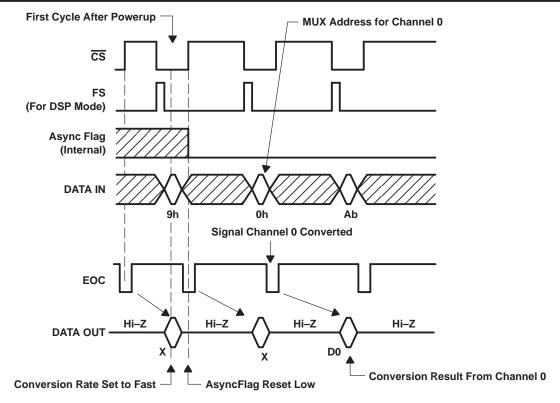

#### power up and initialization

After power up, if operating in DSP mode,  $\overline{CS}$  and FS must be taken from high to low to begin an I/O cycle. EOC is initially high, and the input data register is set to all zeroes. The content of the output data register is random, and the first conversion result should be ignored. For initialization during operation,  $\overline{CS}$  is taken high and returned low to begin the next I/O cycle. The first conversion after the device has returned from the power-down state can be invalid and should be disregarded.

When power is first applied to the device, the conversion rate must be programmed, and the internal Async Flag must be taken low once. The rising edge of  $\overline{CS}$  of the same cycle then takes Async Flag low.

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

Figure 4. Power Up Initialization

## input clock inversion – INV CLK

The input data register uses I/O CLK as the source of the sampling clock. This clock can be inverted to provide more setup time. INV CLK can invert the clock. When INV CLK is grounded, the input clock for the input data register is inverted. This allows an additional one-half I/O CLK period for the input data setup time. This is useful for some serial interfaces. When the input sampling clock is inverted, the output data changes at the same time that the input data is sampled.

Table 6. Function of INV CLK

| C       | CLOCK                       | I/O CLK ACTIVE EDGE       |                          |  |  |

|---------|-----------------------------|---------------------------|--------------------------|--|--|

| INV CLK | FS at CS↓                   | OUTPUT DATA<br>CHANGES ON | INPUT DATA<br>SAMPLED ON |  |  |

| High    | High (MP <sup>†</sup> mode) | $\downarrow$              | <b>↑</b>                 |  |  |

| High    | Low (DSP <sup>‡</sup> mode) | 1                         | $\downarrow$             |  |  |

| Low     | High (MP <sup>†</sup> mode) | $\downarrow$              | $\downarrow$             |  |  |

| Low     | Low (DSP‡ mode)             | <b>1</b>                  | <b>↑</b>                 |  |  |

<sup>†</sup>MP = microprocessor mode

<sup>‡</sup>DSP = digital signal processor mode

<sup>†</sup> Successive approximation register

Figure 5. Clock Scheme

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)     |                      |                                            |

|--------------------------------------------------------|----------------------|--------------------------------------------|

| Input voltage range, V <sub>I</sub> (any input)        |                      | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V}$ |

| Output voltage range, VO                               |                      | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V}$ |

| Positive reference voltage, V <sub>ref+</sub>          |                      | V <sub>CC</sub> + 0.1 V                    |

| Negative reference voltage, V <sub>ref</sub>           |                      | 0.1 V                                      |

| Peak input current, I <sub>I</sub> (any input)         |                      | ±20 mA                                     |

| Peak total input current (all inputs)                  |                      | 30 mA                                      |

| Operating free-air temperature range, T <sub>A</sub> : | TLV1544C, TLV1548C . | 0°C to 70°C                                |

|                                                        | TLV1544I, TLV1548I   | –40°C to 85°C                              |

|                                                        | TLV1548M             |                                            |

| Storage temperature range, T <sub>stq</sub>            |                      |                                            |

| Lead temperature 1,6 mm (1/16 inch) from               |                      |                                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to GND with REF - and GND wired together (unless otherwise noted).

<sup>‡</sup> If\_mode = 1, microprocessor interface mode

<sup>§</sup> If mode = 0, DSP interface mode

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

#### recommended operating conditions

|                                                                            |                                                                               | MIN         | NOM | MAX                  | UNIT               |  |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------|-----|----------------------|--------------------|--|

| Supply voltage, V <sub>CC</sub>                                            |                                                                               |             |     | 5.5                  | V                  |  |

| Positive reference voltage, V <sub>ref+</sub> (see Note 2)                 |                                                                               |             | Vcc |                      | V                  |  |

| Negative reference voltage, V <sub>ref</sub> (see Note 2)                  |                                                                               | Π           | 0   |                      | V                  |  |

| Differential reference voltage, V <sub>ref+</sub> – V <sub>ref-</sub> (see | Note 2)                                                                       | 2.5         | Vcc | V <sub>CC</sub> +0.2 | V                  |  |

| Analog input voltage, V <sub>I (analog)</sub> (see Note 2)                 |                                                                               | 0           |     | VCC                  | V                  |  |

| High-level control input voltage, VIH                                      |                                                                               | 2.1         |     |                      | V                  |  |

| Low-level control input voltage, V <sub>IL</sub>                           |                                                                               |             |     | 0.6                  | V                  |  |

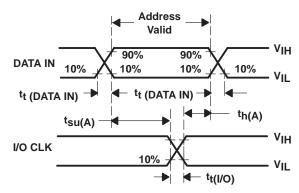

| Setup time, input data bits valid before I/O CLK1                          | , t <sub>su(A)</sub> (see Figure 9)                                           | 100         |     |                      | ns                 |  |

| Hold time, input data bits valid after I/O CLK↑↓, tլ                       | n(A) (see Figure 9)                                                           | 5           | 30  |                      | ns                 |  |

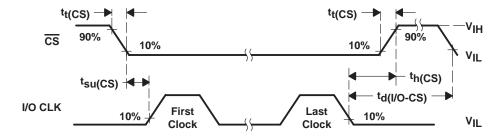

| Setup time, CS↓ to I/O CLK↑, t <sub>Su(CS)</sub>                           | See Figure 10                                                                 | 5           | 30  |                      | ns                 |  |

| Hold time, I/O CLK↓ to CS↑, th(CS)                                         | See Figure 10                                                                 | 65          |     |                      | ns                 |  |

| Pulse duration, FS high, t <sub>wH(FS)</sub>                               | See Figure 12                                                                 | 1           |     |                      | I/O CLK<br>periods |  |

| Pulse duration, CSTART, tw(CSTART)                                         | Source impedance $\leq$ 1 k $\Omega$ , V <sub>CC</sub> = 5.5 V, See Figure 14 | 0.84        |     |                      | μs                 |  |

| Setup time, CS↑ to CSTART↓, t <sub>SU</sub> (CSTART)                       | See Figure 14                                                                 | 10          |     |                      | ns                 |  |

|                                                                            | V <sub>CC</sub> = 5.5 V                                                       | 0.1         | 6   | 10                   | MHz                |  |

| Clock frequency at I/O CLK, f <sub>CLK</sub>                               | V <sub>CC</sub> = 2.7 V                                                       | 0.1         | 2   | 2.81                 |                    |  |

| Bules duration I/O CLK high to access                                      | V <sub>CC</sub> = 5.5 V                                                       | 50          |     |                      | no                 |  |

| Pulse duration, I/O CLK high, t <sub>wH(I/O)</sub>                         | V <sub>CC</sub> = 2.7 V                                                       | 100         |     |                      | ns                 |  |

| Bulgo duration I/O CLK law to a use                                        | V <sub>CC</sub> = 5.5 V                                                       | 50          |     |                      | 20                 |  |

| Pulse duration, I/O CLK low, t <sub>wL(I/O)</sub>                          | V <sub>CC</sub> = 2.7 V                                                       | 100         |     |                      | ns                 |  |

| Transition time, I/O CLK, t <sub>t(I/O)</sub> (see Figure 11 an            | d Note 4)                                                                     |             |     | 1                    | μs                 |  |

| Transition time, DATA IN, t <sub>t(DATA IN)</sub> (see Figure              | 9)                                                                            |             |     | 10                   | μs                 |  |

| Transition time, CS, t <sub>t(CS)</sub> (see Figure 10)                    |                                                                               |             |     | 10                   | μs                 |  |

| Transition time, FS, t <sub>t(FS)</sub> (see Figure 13)                    |                                                                               |             |     | 10                   | μs                 |  |

| Transition time, CSTART, t <sub>t(CSTART)</sub> (see Figure                | e 14)                                                                         |             |     | 10                   | μs                 |  |

|                                                                            | TLV1544C, TLV1548C                                                            | 0           |     | 70                   |                    |  |

| Operating free-air temperature, TA                                         | TLV1544I, TLV1548I                                                            | -40         |     | 85                   | °C                 |  |

|                                                                            | TLV1548M                                                                      | <i>–</i> 55 |     | 125                  |                    |  |

|                                                                            | TLV1544C, TLV1548C                                                            | 115<br>115  |     |                      |                    |  |

| Junction temperature, T <sub>J</sub>                                       | TLV1544I, TLV1548I                                                            |             |     | °C                   |                    |  |

|                                                                            | TLV1548M                                                                      |             |     | 150                  | <u> </u>           |  |

NOTES: 2. Analog input voltages greater than the voltage applied to REF+ convert as all ones (111111111111), while input voltages less than the voltage applied to REF- convert as all zeros (000000000000). The device is functional with reference (V<sub>ref+</sub> – V<sub>ref-</sub>) down to 1 V; however, the electrical specifications are no longer applicable.

3. To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS}$ ↓ before responding to control input signals. No attempt should be made to clock in an input dat until the minimum  $\overline{CS}$  setup time has elapsed.

4. This is the time required for the I/O CLK signal to fall from V<sub>IH</sub>max to V<sub>IL</sub>min or to rise from V<sub>IL</sub>max to V<sub>IH</sub>min. In the vicinity of normal room temperature, the devices function with an input clock transition time as slow as 1 μs for remote data-acquisition applications where the sensor and the A/D converter are placed several feet away from the controlling microprocessor.

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

# electrical characteristics over recommended operating free-air temperature range, $V_{CC} = V_{ref+} = 2.7 \text{ V}$ to 5.5 V, I/O CLK frequency = 2.2 MHz (unless otherwise noted)

|                  | PARAMETER                                         | TEST CON                                                                                                                    | DITIONS                                             | MIN     | TYP <sup>†</sup> | MAX  | UNIT |  |

|------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------|------------------|------|------|--|

| \/-··            | I limb level evident valte en                     | V <sub>CC</sub> = 5.5 V,                                                                                                    | $I_{OH} = -0.2 \text{ mA}$                          | 2.4     |                  |      | V    |  |

| VOH              | High-level output voltage                         | V <sub>CC</sub> = 2.7 V,                                                                                                    | I <sub>OH</sub> = -20 μA                            | VCC-0.1 |                  |      | V    |  |

| \/-·             | I am land a dant a dan                            | V <sub>CC</sub> = 5.5 V,                                                                                                    | I <sub>OL</sub> = 0.8 mA                            |         |                  | 0.4  | V    |  |

| VOL              | Low-level output voltage                          | V <sub>CC</sub> = 2.7 V,                                                                                                    | $C = 2.7 \text{ V}, \qquad I_{OL} = 20 \mu\text{A}$ |         |                  |      | V    |  |

| 1                | High important autout autout                      | $V_O = V_{CC}$                                                                                                              | CS = V <sub>CC</sub>                                |         | 1                | 2.5  | 4    |  |

| loz              | High-impedance output current                     | $V_{O} = 0,$                                                                                                                | CS = V <sub>CC</sub>                                |         | -1               | -2.5 | μΑ   |  |

| lіН              | High-level input current                          | VI = VCC                                                                                                                    |                                                     |         | 0.005            | 2.5  | μΑ   |  |

| Iμ               | Low-level input current                           | V <sub>I</sub> = 0                                                                                                          |                                                     |         | -0.005           | 2.5  | μΑ   |  |

|                  |                                                   | Conversion speed = fast,<br>For all digital inputs,<br>$0 \le V_1 \le 0.3 \text{ V or}$<br>$V_1 \ge V_{CC} - 0.3 \text{ V}$ | V <sub>CC</sub> = 3.3 V to 5.5 V                    |         | 0.6              | 1.5  | ^    |  |

| ICC Ope          | Operating supply current                          | Conversion speed = slow,<br>For all digital inputs,                                                                         | V <sub>CC</sub> = 3.3 V to 5.5 V                    | 0.4     |                  | 1    | mA   |  |

|                  |                                                   | $0 \le V_I \le 0.3 \text{ V or}$<br>$V_I \ge V_{CC} - 0.3 \text{ V}$                                                        | V <sub>CC</sub> = 2.7 V to 3.3 V                    |         | 0.35             | 0.75 |      |  |

| 1                | Extended sampling mode                            | V <sub>CC</sub> = 3.3 V to 5.5 V                                                                                            |                                                     |         | 1.5              |      | mA   |  |

| ICC(ES)          | operating current                                 | V <sub>CC</sub> = 2.7 V to 3.3 V                                                                                            |                                                     |         | 1                |      | mA   |  |

| ICC(ST)          | Sustaining supply current                         | Conversion speed = slow,<br>For all digital inputs,<br>$0 \le V_1 \le 0.3 \text{ V or}$<br>$V_1 \ge V_{CC} - 0.3 \text{ V}$ | V <sub>CC</sub> = 2.7 V to 3.3 V                    |         | 0.3              |      | mA   |  |

| ICC(PD)          | Power-down supply current                         | For all digital inputs,<br>$0 \le V_I \le 0.3 \text{ V or } V_I \ge V_{CC}$ -                                               | - 0.3 V                                             |         | 1                | 25   | μΑ   |  |

| L.               | Calcated shannel lackage surrent                  | Selected channel at V <sub>CC</sub> , u                                                                                     | nselected channel at 0 V                            |         |                  | 1    | μΑ   |  |

| likg             | Selected channel leakage current                  | Selected channel at 0 V, uns                                                                                                | selected channel at V <sub>CC</sub>                 |         |                  | -1   | μΑ   |  |

|                  | Maximum static analog reference current into REF+ | V <sub>ref+</sub> = V <sub>CC</sub> = 5.5 V,                                                                                | V <sub>ref</sub> _ = GND                            |         |                  | 1    | μΑ   |  |

| C: +             | Input capacitance, analog inputs                  |                                                                                                                             |                                                     |         | 20               | 55   | 25   |  |

| C <sub>i</sub> ‡ | Input capacitance, control inputs                 |                                                                                                                             |                                                     |         | 20               | 15   | pF   |  |

| 7. +             | Innut multiplever on registers                    | V <sub>CC</sub> = 4.5 V                                                                                                     |                                                     |         | 1                | kO   |      |  |

| Z <sub>i</sub> ‡ | Input multiplexer on resistance                   | V <sub>CC</sub> = 2.7 V                                                                                                     |                                                     |         |                  | 5    | kΩ   |  |

$<sup>\</sup>dagger$  All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

<sup>‡</sup> Not production tested.

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

## operating characteristics over recommended operating free-air temperature range, $V_{CC} = V_{ref+} = 2.7 \text{ V}$ to 5.5 V, I/O CLK frequency = 2.2 MHz (unless otherwise noted)

|                                     | PARAMETER                                                  | TEST<br>CONDITIONS       | MIN                                                  | түр† | MAX  | UNIT                 |                    |

|-------------------------------------|------------------------------------------------------------|--------------------------|------------------------------------------------------|------|------|----------------------|--------------------|

| EL                                  | Linearity error (see Note 6)                               |                          |                                                      |      | ±0.5 | ±1                   | LSB                |

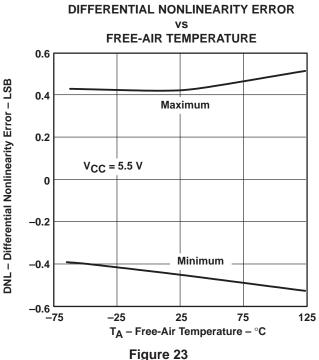

| E <sub>D</sub>                      | Differential linearity error                               |                          | See Note 2                                           |      | ±0.5 | ±1                   | LSB                |

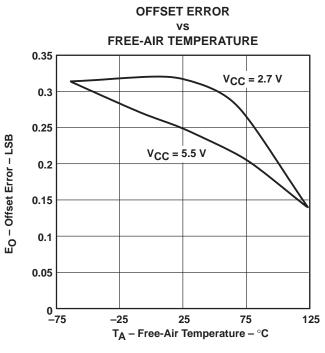

| EO                                  | Offset error (see Note 7)                                  |                          | See Note 2                                           |      |      | ±1.5                 | LSB                |

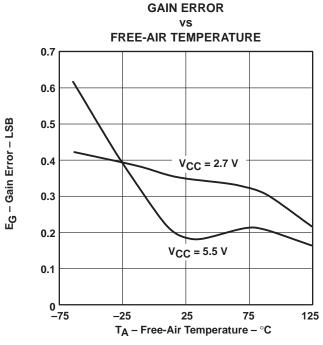

| E <sub>G</sub>                      | Gain error (see Note 7)                                    |                          | See Note 2                                           |      |      | ±1                   | LSB                |

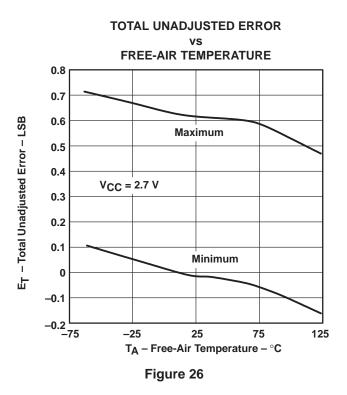

| E <sub>T</sub>                      | Total unadjusted error (see Note                           | 8)                       |                                                      |      |      | ±1.75                | LSB                |

|                                     |                                                            |                          | DATA IN = 1011                                       |      | 512  |                      |                    |

|                                     | Self-test output code (see Table 3                         | 3 and Note 9)            | DATA IN - 1100                                       |      | 0    |                      |                    |

|                                     |                                                            |                          |                                                      |      | 1023 |                      |                    |

|                                     | Conversion time                                            | Fast conversion speed    | See Figures 15                                       |      | 7    | 10                   | μs                 |

| <sup>t</sup> conv                   | Conversion time                                            | Slow conversion speed    | through 17                                           |      | 15   | 25                   | μs                 |

|                                     | Total cycle time (access,                                  | Fast conversion speed    | See Figures 15<br>through 18 and<br>Notes 10, 11, 12 |      |      | 10.1 +<br>10 I/O CLK |                    |

| t <sub>C</sub>                      | sample, conversion and EOC↑ to CS↓ delay)                  | Slow conversion speed    | See Figures 15<br>through 18 and<br>Notes 10 and 12  |      |      | 40.1 +<br>10 I/O CLK | μs                 |

| <sup>t</sup> acq                    | Channel acquisition time (sample                           | e)                       | See Figures 15<br>through 18 and<br>Note 10          |      |      | 6                    | I/O CLK<br>periods |

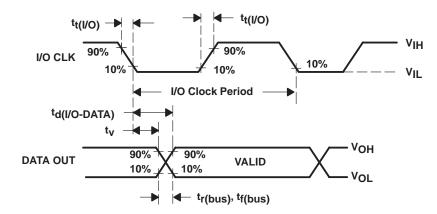

| t <sub>V</sub>                      | Valid time, DATA OUT remains va                            | alid after I/O CLK↓      | See Figure 11                                        | 50   |      |                      | ns                 |

| t <sub>d1(FS)</sub>                 | Delay time, I/O CLK high to FS hi                          | igh                      | See Figure 13                                        | 5    | 30   | 50                   | ns                 |

| t <sub>d2(FS)</sub>                 | Delay time, I/O CLK high to FS lo                          | w                        | See Figure 13                                        | 10   | 30   | 60                   | ns                 |

| $t_{d}(EOC\uparrow - CS\downarrow)$ | Delay time, EOC↑ to CS low                                 | See Figure 14 and Note 5 | 100                                                  |      |      | ns                   |                    |

| $t_{d(CS}\downarrow - FS\uparrow)$  | Delay time, CS↓ to FS↑                                     | See Figures 17 and 18    | 1                                                    |      | 7    | I/O CLK<br>periods   |                    |

| td(I/O -CS)                         | Delay time, 10th I/O CLK low to 0 conversion (see Note 13) | CS low to abort          | See Figure 10                                        |      |      | 1.1                  | μs                 |

<sup>†</sup> All typical values are at  $T_A = 25$ °C.

NOTES: 2. Analog input voltages greater than that applied to REF+ convert as all ones (111111111111), while input voltages less than that applied to REF- convert as all zeros (000000000000). The device is functional with reference down to 1 V (V<sub>ref</sub>+-V<sub>ref</sub>-1); however, the electrical specifications are no longer applicable.

- 5. For all operating modes.

- 6. Linearity error is the maximum deviation from the best straight line through the A/D transfer characteristics.

- 7. Zero error is the difference between 0000000000 and the converted output for zero input voltage. Full-scale error is the difference between 1111111111 and the converted output for full-scale input voltage.

- 8. Total unadjusted error comprises linearity, zero-scale, and full-scale errors.

- 9. Both the input data and the output codes are expressed in positive logic.

- 10. I/O CLK period = 1/(I/O CLK frequency) (see Figure 8).

- 11. For 3.3 V to 5.5 V only

- 12. For microprocessor mode

- 13. Any transitions of  $\overline{CS}$  are recognized as valid only when the level is maintained for a setup time after the transition.

# operating characteristics over recommended operating free-air temperature range, $V_{CC} = V_{ref+} = 2.7 \text{ V}$ to 5.5 V, I/O CLK frequency = 2.2 MHz (unless otherwise noted) (continued)

|              | PARAMETER                                                  | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------|------------------------------------------------------------|-----------------|-----|-----|-----|------|

| td(I/O-DATA) | Delay time, I/O CLK low to DATA OUT valid                  | See Figure 11   |     |     | 50  | ns   |

| td(I/O-EOC)  | Delay time, 10th I/O CLK↓ to EOC low                       | See Figure 12   |     | 70  | 240 | ns   |

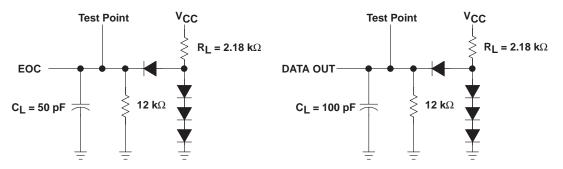

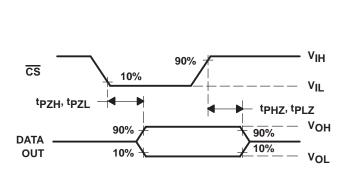

| tPZH, tPZL   | Enable time, CS low to DATA OUT valid (MSB driven)         | See Figure 8    |     | 0.7 | 1.3 | μs   |

| tPHZ, tPLZ   | Disable time, CS high to DATA OUT invalid (high impedance) | See Figure 8    |     | 70  | 150 | ns   |

| tf(EOC)      | Fall time, EOC                                             | See Figure 12   |     | 15  | 50  | ns   |

| tr(bus)      | Rise time, output data bus at 2.2 MHz I/O CLK              | See Figure 11   |     | 50  | 250 | ns   |

| tf(bus)      | Fall time, output data bus at 2.2 MHz I/O CLK              | See Figure 11   |     | 50  | 250 | ns   |

$<sup>\</sup>overline{\dagger}$  All typical values are at  $T_A = 25^{\circ}$ C.

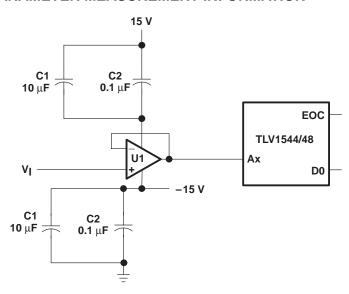

| LOCATION | DESCRIPTION                      | PART NUMBER                      |

|----------|----------------------------------|----------------------------------|

| U1       | OP27                             | _                                |

| C1       | 10-μF 35-V tantalum capacitor    | _                                |

| C2       | 0.1-μF ceramic NPO SMD capacitor | AVX 12105C104KA105 or equivalent |

Figure 6. Analog Input Buffer to Analog Inputs

Figure 7. Load Circuits

Figure 8. DATA OUT to Hi-Z Voltage Waveforms

Figure 9. DATA IN Setup Voltage Waveforms

Figure 10. CS and I/O CLK Voltage Waveforms

Figure 11. DATA OUT and I/O CLK Voltage Waveforms

Figure 12. CS Low to FS Low

Figure 13. I/O CLK and EOC Voltage Waveforms

Figure 14. FS and I/O CLK Voltage Waveforms

Figure 15. CSTART and CS Waveforms

NOTE A: To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS}$ ↓ before responding to control input signals. No attempt should be made to clock in input data until the minimum  $\overline{CS}$  setup time elapses.

Figure 16. Microprocessor Interface Timing (Normal Sample Mode, INV CLK = High)

NOTE A: To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS}$ ↓ before responding to control input signals. No attempt should be made to clock in input data until the minimum  $\overline{CS}$  setup time has elapsed.

Figure 17. Microprocessor Interface Timing (Normal Sample Mode, INV CLK = Low)

#### PARAMETER MEASUREMENT INFORMATION

NOTE A: To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS}$ ↓ before responding to control input signals. No attempt should be made to clock in input data until the minimum  $\overline{CS}$  setup time elapses.

Figure 18. DSP Interface Timing (16-Clock Transfer, Normal Sample Mode, INV CLK = High)

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

#### PARAMETER MEASUREMENT INFORMATION

NOTE A: To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS}$ ↓ before responding to control input signals. No attempt should be made to clock in input data until the minimum  $\overline{CS}$  setup time elapses.

Figure 19. DSP Interface Timing (16-Clock Transfer, Normal Sample Mode, INV CLK = Low)

#### TYPICAL CHARACTERISTICS

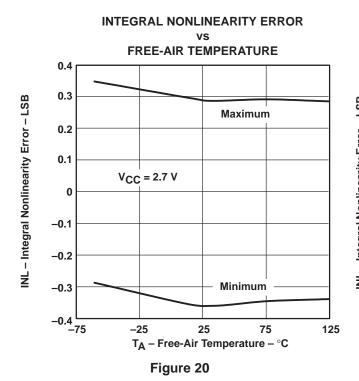

INTEGRAL NONLINEARITY ERROR FREE-AIR TEMPERATURE 0.5 0.4 INL - Integral Nonlinearity Error - LSB Maximum 0.3 0.2 0.1  $V_{CC} = 5.5 V$ 0 -0.1 -0.2-0.3 Minimum -0.4 -0.5\_75 -25 25 75 125 T<sub>A</sub> - Free-Air Temperature - °C Figure 21

#### TYPICAL CHARACTERISTICS

Figure 24

Figure 25

**TOTAL UNADJUSTED ERROR** FREE-AIR TEMPERATURE 1.2 E<sub>T</sub> - Total Unadjusted Error - LSB 0.8 Maximum 0.6 V<sub>CC</sub> = 5.5 V 0.4 0.2 0 Minimum -0.2 -0.4 <del>-</del> -75 25  $T_A$  – Free-Air Temperature –  $^{\circ}C$

Figure 27

125

#### **TYPICAL CHARACTERISTICS**

## **SUPPLY CURRENT** FREE-AIR TEMPERATURE 0.56 0.54 0.52 I<sub>CC</sub>- Supply Current - mA 0.5 0.48 0.46 0.44 $V_{CC} = 5.5 V$ Clock Mode = 0.42 **Fast Conversion** 0.4 <del>-</del> -75 -25 25 125 $T_{\mbox{A}}$ – Free-Air Temperature – $^{\circ}\mbox{C}$

Figure 28

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

#### TYPICAL CHARACTERISTICS

## **TYPICAL CHARACTERISTICS**

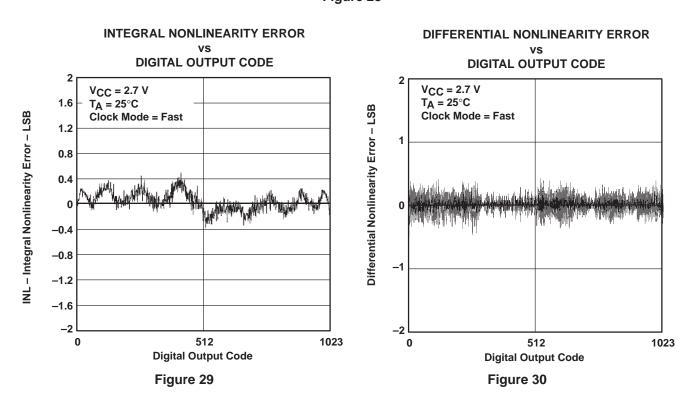

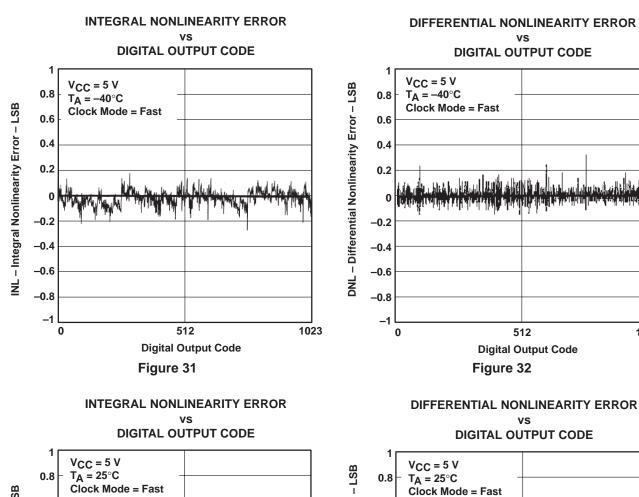

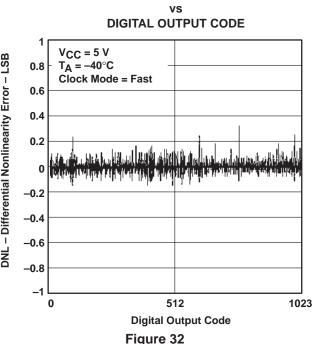

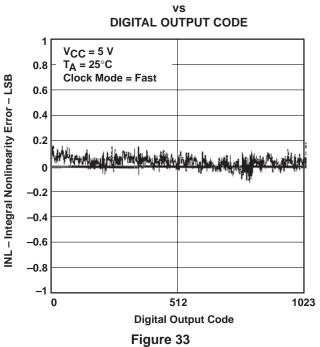

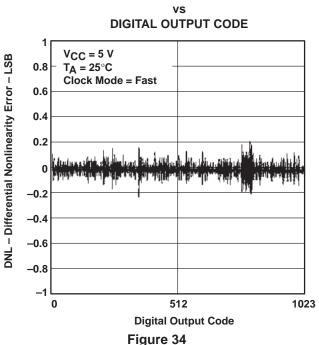

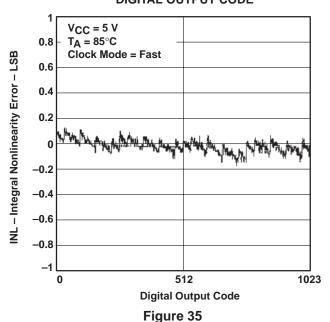

# INTEGRAL NONLINEARITY ERROR vs DIGITAL OUTPUT CODE

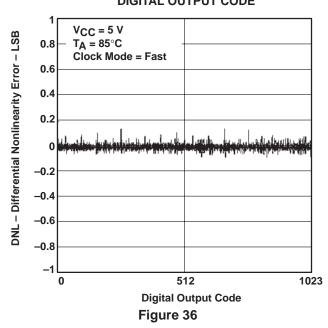

# DIFFERENTIAL NONLINEARITY ERROR vs DIGITAL OUTPUT CODE

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

#### APPLICATION INFORMATION

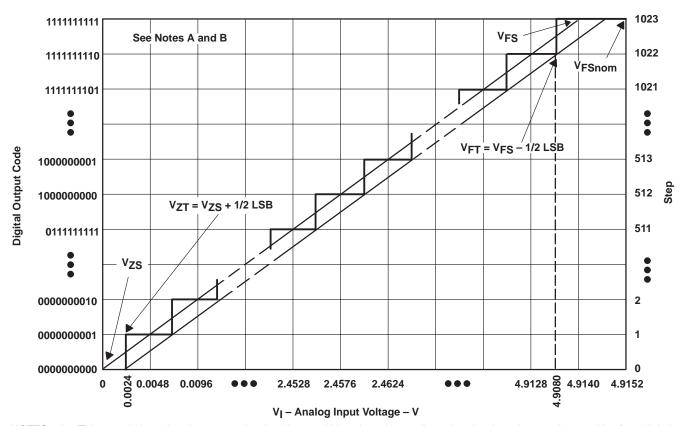

- NOTES: A. This curve is based on the assumption that  $V_{Tef+}$  and  $V_{Tef-}$  have been adjusted so that the voltage at the transition from digital 0 to 1 ( $V_{ZT}$ ) is 0.0024 V, and the transition to full scale ( $V_{FT}$ ) is 4.908 V. 1 LSB = 4.8 mV.

- B. The full-scale value (VFS) is the step whose nominal midstep value has the highest absolute value. The zero-scale value (VZS) is the step whose nominal midstep value equals zero.

Figure 37. Ideal Conversion Characteristics

#### **APPLICATION INFORMATION**

†DB package is shown for TLV1548

Figure 38. Typical Interface to a Microprocessor

<sup>‡</sup> DB package is shown for TLV1548

Figure 39. Typical Interface to a TMS320 DSP

SLAS139C - DECEMBER 1996 - REVISED JANUARY 1999

#### **APPLICATIONS INFORMATION**

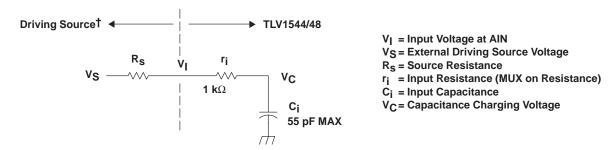

#### simplified analog input analysis

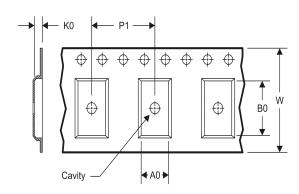

Using the equivalent circuit in Figure 33, the time required to charge the analog input capacitance from 0 to  $V_S$  within 1/2 LSB can be derived as follows:

The capacitance charging voltage is given by:

$$V_{C} = V_{S} \left( 1 - e^{-t_{C}/R_{t}C_{i}} \right)$$

where

$R_t = R_s + r_i$

$t_{c}$  = Cycle time

The input impedance  $Z_i$  is 1 k $\Omega$  at 5 V, and is higher (~ 5 k $\Omega$ ) at 2.7 V. The final voltage to 1/2 LSB is given by:

$$V_{C} (1/2 LSB) = V_{S} - (V_{S}/2048)$$

(2)

Equating equation 1 to equation 2 and solving for cycle time t<sub>c</sub> gives:

$$V_{S} - (V_{S}/2048) = V_{S} (1 - e^{-t_{C}/R_{t}C_{i}})$$

and time to change to 1/2 LSB (minimum sampling time) is:

(3)

3 ( 1 9

$$t_{ch}$$

(1/2 LSB) =  $R_t \times C_i \times ln(2048)$

where

$$ln(2048) = 7.625$$

Therefore, with the values given, the time for the analog input signal to settle is:

$$t_{ch} (1/2 LSB) = (R_S + 1 k\Omega) \times 55 pF \times ln(2048)$$

(4)

This time must be less than the converter sample time shown in the timing diagrams. Which is 6x I/O CLK.