# 54LS/74LS256 6//1/7

### **DUAL 4-BIT ADDRESSABLE LATCH**

**DESCRIPTION** — The '256 is a dual 4-bit addressable latch with common control inputs; these include two Address inputs (A<sub>0</sub>, A<sub>1</sub>), an active LOW Enable input ( $\overline{\mathbb{C}}$ ) and an active LOW Clear input ( $\overline{\mathbb{C}}$ L). Each latch has a Data input (D) and four outputs (Q<sub>0</sub> — Q<sub>3</sub>).

When the Enable  $(\overline{E})$  is HIGH and the Clear input  $(\overline{CL})$  is LOW, all outputs  $(Q_0-Q_3)$  are LOW. Dual 4-channel demultiplexing occurs when the  $\overline{CL}$  and  $\overline{E}$  are both LOW. When  $\overline{CL}$  is HIGH and  $\overline{E}$  is LOW, the selected output  $(Q_0-Q_3)$ , determined by the Address inputs, follows D. When the  $\overline{E}$  goes HIGH, the contents of the latch are stored. When operating in the addressable latch mode  $(\overline{E}=LOW, \overline{CL}=HIGH)$ , changing more than one bit of the Address  $(A_0,A_1)$  could impose a transient wrong address. Therefore, this should be done only while in the memory mode  $(\overline{E}=\overline{CL}=HIGH)$ .

- SERIAL-TO-PARALLEL CAPABILITY

- OUTPUT FROM EACH STORAGE BIT AVAILABLE

- RANDOM (ADDRESSABLE) DATA ENTRY

- EASILY EXPANDABLE

- ACTIVE LOW COMMON CLEAR

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                                    | MILITARY GRADE                                                                                  | PKG  |  |

|--------------------|-----|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|--|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V} \pm 5\%,$<br>$T_A = 0^{\circ} \text{ C} \text{ to } +70^{\circ} \text{ C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C to} + 125^{\circ} \text{ C}$ | TYPE |  |

| Plastic<br>DIP (P) | Α   | 74LS256PC                                                                                           |                                                                                                 | 9B   |  |

| Ceramic<br>DIP (D) | Α   | 74LS256DC                                                                                           | 54LS256DM                                                                                       | 6B   |  |

| Flatpak<br>(F)     | A   | 74LS256FC                                                                                           | 54LS256FM                                                                                       | 4L   |  |

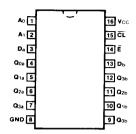

# CONNECTION DIAGRAM PINOUT A

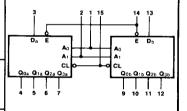

LOGIC SYMBOL

V<sub>CC</sub> = Pin 16 GND = Pin 8

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                         | DESCRIPTION                          | <b>54/74LS (U.L.)</b><br>HIGH/LOW |  |

|-----------------------------------|--------------------------------------|-----------------------------------|--|

| A <sub>0</sub> , A <sub>1</sub>   | Common Address Inputs                | 0.5/0.25                          |  |

| Da, Db                            | Data Inputs                          | 0.5/0.25                          |  |

| CL<br>CL                          | Common Enable Input (Active LOW)     | 1.0/0.5                           |  |

| CL                                | Conditional Clear Input (Active LOW) | 0.5/0.25                          |  |

| Q <sub>0a</sub> — Q <sub>3a</sub> | Side A Latch Outputs                 | 10/5.0                            |  |

|                                   |                                      | (2.5)                             |  |

| Q <sub>0b</sub> — Q <sub>3b</sub> | Side B Latch Outputs                 | 10/5.0                            |  |

|                                   |                                      | (2.5)                             |  |

#### TRUTH TABLE

| $\overline{}$ |   |                |             |                                                               |                                      |                                                           |                                                                     |                      |

|---------------|---|----------------|-------------|---------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------|----------------------|

| INPUTS        |   |                | OUTPUTS     |                                                               |                                      |                                                           | MODE                                                                |                      |

| CL            | Ē | A <sub>0</sub> | Αı          | $Q_0$                                                         | Q <sub>1</sub>                       | Q <sub>2</sub>                                            | Q <sub>3</sub>                                                      | WODE                 |

| L             | Н | ×              | X           | L                                                             | L                                    | L                                                         | L                                                                   | Clear                |

| L<br>L<br>L   |   | ברבר           | L<br>H<br>H | D<br>L<br>L                                                   | L<br>D<br>L<br>L                     | L<br>D<br>L                                               | L<br>L<br>D                                                         | Demultiplex          |

| Н             | Н | X              | Х           | Q <sub>t-1</sub>                                              | Q <sub>t-1</sub>                     | Q <sub>t-1</sub>                                          | Q <sub>t-1</sub>                                                    | Memory               |

| <b>1111</b>   |   | L<br>H<br>L    | LLHH        | D<br>Q <sub>t-1</sub><br>Q <sub>t-1</sub><br>Q <sub>t-1</sub> | $Q_{t-1} \\ D \\ Q_{t-1} \\ Q_{t-1}$ | $\begin{array}{c}Q_{t-1}\\Q_{t-1}\\D\\Q_{t-1}\end{array}$ | $\begin{aligned} &Q_{t-1}\\ &Q_{t-1}\\ &Q_{t-1}\\ &D \end{aligned}$ | Addressable<br>Latch |

t-1 = Bit time before address change or rising edge of E

#### **MODE SELECTION**

| Ē    | CL  | MODE                                                                         |

|------|-----|------------------------------------------------------------------------------|

| エーエー | LLL | Addressable Latch<br>Memory<br>Active HIGH 4-Channel Demultiplexers<br>Clear |

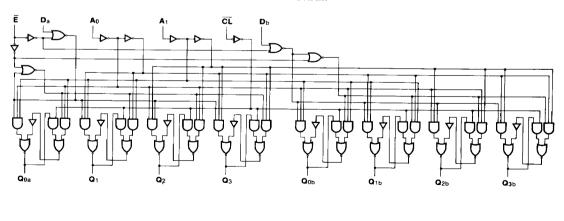

#### LOGIC DIAGRAM

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

# DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER            | 54/ | 74LS | UNITS | CONDITIONS |  |

|--------|----------------------|-----|------|-------|------------|--|

|        |                      | Min | Max  |       | CONDITIONS |  |

| lcc    | Power Supply Current |     | 25   | mA    | Vcc = Max  |  |

AC CHARACTERISTICS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25°C (See Section 3 for waveforms and load configurations)

| SYMBOL           |                                                       | 54/              | 54/74LS  |       |                 |  |

|------------------|-------------------------------------------------------|------------------|----------|-------|-----------------|--|

|                  | PARAMETER                                             | C <sub>L</sub> = | 15 pF    | UNITS | CONDITIONS      |  |

|                  |                                                       | Min              | Max      | 7     |                 |  |

| t <sub>PLH</sub> | Propagation Delay<br>E to Q <sub>n</sub>              |                  | 27<br>24 | ns    | Figs. 3-1, 3-9  |  |

| tpLH<br>tpHL     | Propagation Delay<br>D <sub>n</sub> to Q <sub>n</sub> |                  | 30<br>20 | ns    | Figs. 3-1, 3-5  |  |

| tPLH<br>tPHL     | Propagation Delay<br>A <sub>n</sub> to Q <sub>n</sub> |                  | 30<br>20 | ns    | Figs. 3-1, 3-20 |  |

| tpHL             | Propagation Delay<br>CL to Q <sub>n</sub>             |                  | 18       | ns    | Figs. 3-1, 3-16 |  |

## AC OPERATING REQUIREMENTS: $V_{CC} = \pm 5.0 \text{ V}, T_A = \pm 25^{\circ} \text{ C}$

| SYMBOL                                   | PARAMETER                          | 54/74LS |     | UNITS  | CONDITIONS |

|------------------------------------------|------------------------------------|---------|-----|--------|------------|

|                                          |                                    | Min     | Max | JUNITS | CONDITIONS |

| ts (H)                                   | Setup Time HIGH<br>Dn to E         | 20      |     | ns     | Fig. 3-13  |

| t <sub>h</sub> (H)                       | Hold Time HIGH<br>Dn to Ē          | 0       |     | ns     | Fig. 3-13  |

| t <sub>s</sub> (L)                       | Setup Time LOW<br>Dn to E          | 15      |     | ns     | Fig. 3-13  |

| t <sub>h</sub> (L)                       | Hold Time LOW<br>Dn to Ē           | 0       |     | ns     | Fig. 3-13  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW,<br>An to E | 0       |     | ns     | Fig. 3-21  |

| tw (L)                                   | Ē Pulse Width LOW                  | 17      |     | ns     | Fig. 3-21  |