# SmartLEWIS™ MCU

Smart Low Energy Wireless Systems with a Microcontroller Unit

# PMA51xx

RF Transmitter ASK/FSK 315/434/868/915 MHz, Embedded 8051 Microcontroller, 10-bit ADC, 125 kHz ASK LF Receiver

PMA5110 Version 1.0 PMA5105 Version 1.0

# **Data Sheet**

Revision 2.1, 2010-06-02

# Wireless Control

#### Edition 2010-06-02

Published by Infineon Technologies AG 81726 Munich, Germany © 2010 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### **Warnings**

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

PMA51xx RF Transmitter ASK/FSK 315/434/868/915 MHz, Embedded 8051 Microcontroller, 10-bit ADC, 125 kHz ASK LF Receiver

Revision History: 2010-06-02, Revision 2.1

| Previous Revision: 2.0 |                                                                                                                  |  |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Page                   | Subjects (major changes since last revision)                                                                     |  |  |  |  |

| 101, 86                | Added note to use Library function LFSensitivityCalibration() for LF Carrier Detector Threshold Level Selection. |  |  |  |  |

|                        |                                                                                                                  |  |  |  |  |

|                        |                                                                                                                  |  |  |  |  |

|                        |                                                                                                                  |  |  |  |  |

|                        |                                                                                                                  |  |  |  |  |

### **Trademarks of Infineon Technologies AG**

A-GOLD™, BlueMoon™, COMNEON™, CONVERGATE™, COSIC™, C166™, CROSSAVE™, CanPAK™, CIPOS™, CoolMOS™, CoolSET™, CONVERPATH™, CORECONTROL™, DAVE™, DUALFALC™, DUSLIC™, EasyPIM™, EconoBRIDGE™, EconoDUAL™, EconoPACK™, EconoPIM™, E-GOLD™, EiceDRIVER™, EUPEC™, ELIC™, EPIC™, FALC™, FCOS™, FLEXISLIC™, GEMINAX™, GOLDMOS™, HITFET™, HybridPACK™, INCA™, ISAC™, ISOFACE™, IsoPACK™, IWORX™, M-GOLD™, MIPAQ™, ModSTACK™, MUSLIC™, my-d™, NovalithIC™, OCTALFALC™, OCTAT™, OmniTune™, OmniVia™, OptiMOS™, OPTIVERSE™, ORIGA™, PROFET™, PRO-SIL™, PrimePACK™, QUADFALC™, RASIC™, ReverSave™, SatRIC™, SCEPTRE™, SCOUT™, S-GOLD™, SensoNor™, SEROCCO™, SICOFI™, SIEGET™, SINDRION™, SLIC™, SMARTi™, SmartLEWIS™, SMINT™, SOCRATES™, TEMPFET™, thinQ!™, TrueNTRY™, TriCore™, TRENCHSTOP™, VINAX™, VINETIC™, VIONTIC™, WildPass™, X-GOLD™, XMM™, X-PMU™, XPOSYS™, XWAY™.

#### Other Trademarks

AMBA™, ARM™, MULTI-ICE™, PRIMECELL™, REALVIEW™, THUMB™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO. OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Sattelite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2009-10-19

|                            | Table of Contents                            | . 4 |

|----------------------------|----------------------------------------------|-----|

|                            | List of Figures                              | . 9 |

|                            | List of Tables                               | 11  |

| 1                          | Product Description                          | 13  |

| 1.1                        | Overview                                     |     |

| 1.2                        | PMAx1xx Product Family                       | 14  |

| 1.3                        | Applications                                 | 14  |

| 1.4                        | Key Features                                 | 14  |

| 1.5                        | Pin Diagram                                  | 16  |

| 1.6                        | Pin Description                              | 17  |

| 1.7                        | Functional Block Diagram                     | 28  |

| 2                          | Functional Description                       | 29  |

| 2.1                        | Operating Modes and States                   |     |

| 2.1.1                      | Operating Mode Selection                     |     |

| 2.1.2                      | State Description                            |     |

| 2.1.2.1                    | INIT state                                   |     |

| 2.1.2.2                    | RUN state                                    | 32  |

| 2.1.2.3                    | IDLE state                                   | 32  |

| 2.1.2.4                    | POWER DOWN state (PDWN)                      | 33  |

| 2.1.2.5                    | State Transitions                            | 33  |

| 2.1.2.6                    | Status of PMA5110 Blocks in Different States | 34  |

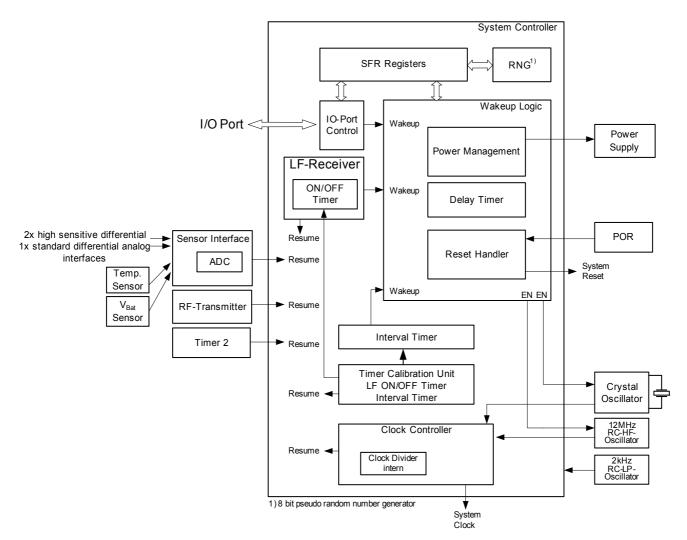

| 2.2                        | System Controller                            | 35  |

| 2.2.1                      | Wake-up Logic                                | 35  |

| 2.2.1.1                    | Register Description                         | 37  |

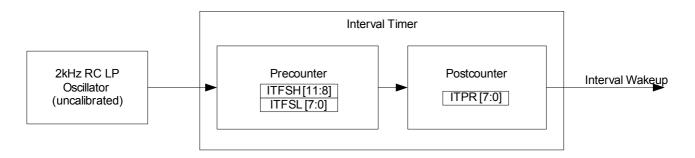

| 2.2.2                      | Interval Timer                               |     |

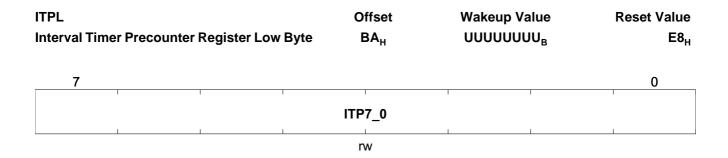

| 2.2.3                      | Register Description                         | 43  |

| 2.3                        | System Configuration Registers               |     |

| 2.3.1                      | Register Description                         |     |

| 2.4                        | Fault Protection                             |     |

| 2.4.1                      | Watchdog Timer                               |     |

| 2.4.2                      | Vmin Detector                                |     |

| 2.4.2.1                    | Register Description                         |     |

| 2.4.3                      | Brownout Detector                            |     |

| 2.4.4                      | FLASH Memory Checksum                        |     |

| 2.4.5                      | ADC Measurement Overflow and Underflow       |     |

| 2.5                        | Clock Controller                             |     |

| 2.5.1                      | Internal Clock Divider                       |     |

| 2.5.2                      | 2 kHz RC LP Oscillator (Low Power)           |     |

| 2.5.3<br>2.5.4             | Crystal Oscillator                           |     |

| 2.5. <del>4</del><br>2.5.5 | Register Description                         |     |

| 2.5.5<br>2.6               | Memory Organization                          |     |

| 2.6.1                      | ROM                                          |     |

| 2.6.1<br>2.6.2             | FLASH                                        |     |

| 2.6.2<br>2.6.2.1           | FLASH Organization                           |     |

| 2.6.2.2                    | FLASH Protection                             |     |

| 2.6.2.3                    | Register Description                         |     |

| _ · • · <b>_ · •</b>       |                                              |     |

| 2.6.3      | RAM                                                              | 60 |

|------------|------------------------------------------------------------------|----|

| 2.6.4      | Code Memory mapped SFRs                                          |    |

| 2.6.4.1    | Register Description                                             |    |

| 2.6.5      | Battery buffered data RAM                                        | 61 |

| 2.6.6      | Special Function Registers                                       | 61 |

| 2.7 N      | Microcontroller                                                  |    |

| 2.7.1      | Register Description                                             | 65 |

| 2.8 I      | nterrupt Sources                                                 | 67 |

| 2.8.1      | External Interrupts 0 and 1                                      | 67 |

| 2.8.2      | Timer Interrupts                                                 | 68 |

| 2.8.3      | I <sup>2</sup> C Interface Interrupts                            | 68 |

| 2.8.4      | SPI Interface Interrupts                                         | 68 |

| 2.8.5      | LF Receiver Interrupts                                           | 68 |

| 2.8.6      | RF Encoder Interrupts                                            | 68 |

| 2.8.7      | Register Description                                             | 69 |

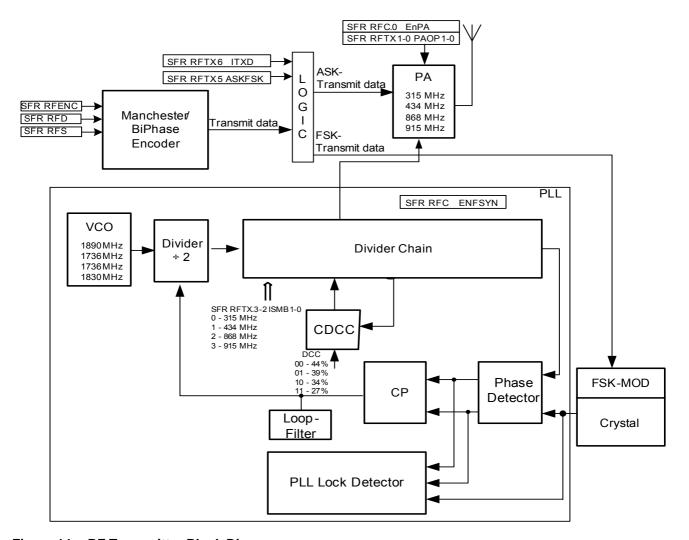

| 2.9 F      | RF Transmitter                                                   | 72 |

| 2.9.1      | Phase-Locked Loop (PLL)                                          | 72 |

| 2.9.2      | Voltage-Controlled Oscillator (VCO)                              |    |

| 2.9.3      | Power Amplifier (PA)                                             |    |

| 2.9.4      | ASK Modulator                                                    |    |

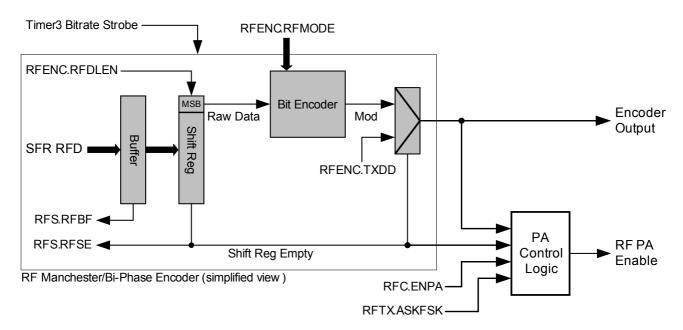

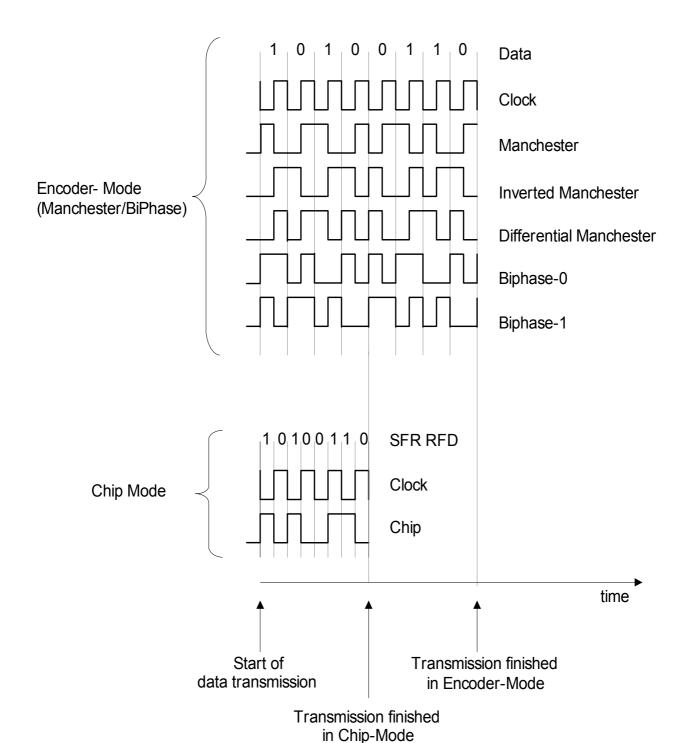

| 2.9.5      | Manchester/BiPhase Encoder with Bit Rate Generator               |    |

| 2.9.6      | Register Description                                             |    |

| 2.10 L     | F Receiver                                                       |    |

| 2.10.1     | LF Receiver Analog Front End Configuration                       |    |

| 2.10.1.1   | Attenuator (AGC) and Data Filter / Data Slicer                   |    |

| 2.10.1.2   | LF Carrier Detector                                              |    |

| 2.10.1.2.1 | Carrier Detector Threshold Calibration                           |    |

| 2.10.1.2.2 | Carrier Detector Filtering                                       |    |

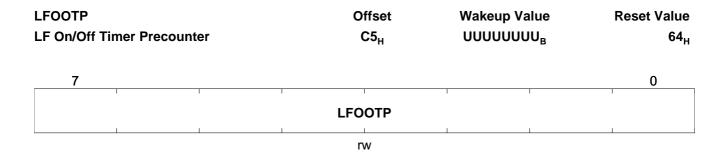

| 2.10.2     | LF Receiver On/Off Timer                                         |    |

| 2.10.2.1   | LF Receiver On/Off Timer Calibration                             |    |

| 2.10.3     | LF Receiver Baseband Processor                                   |    |

| 2.10.3.1   | Synchronizer                                                     |    |

| 2.10.3.2   | Bit rate Generator                                               |    |

| 2.10.3.3   | LF Data Decoder                                                  |    |

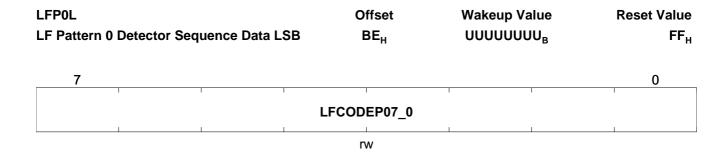

| 2.10.3.4   | Wake-up Pattern Detector                                         |    |

| 2.10.3.5   | LF Receiver Data Interface                                       |    |

| 2.10.3.5.1 | 8 bit data byte                                                  |    |

| 2.10.3.5.2 | Serial bit stream data                                           |    |

| 2.10.3.5.3 | RAW data                                                         |    |

| 2.10.3.5.4 | RAW Carrier Detect                                               |    |

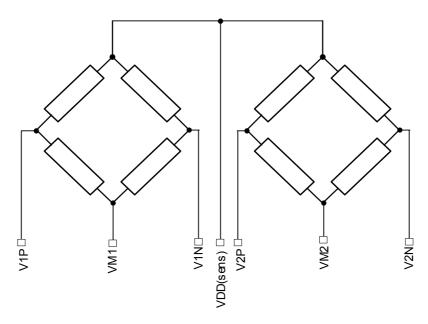

| 2.10.4     | Register Description                                             |    |

|            | Sensor Interfaces and Data Acquisition                           |    |

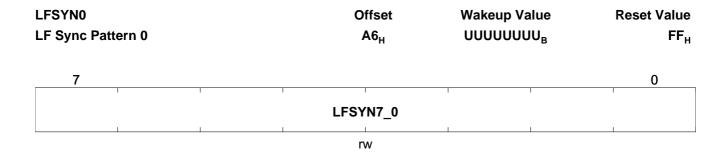

| 2.11.1     | Sensor Interface                                                 |    |

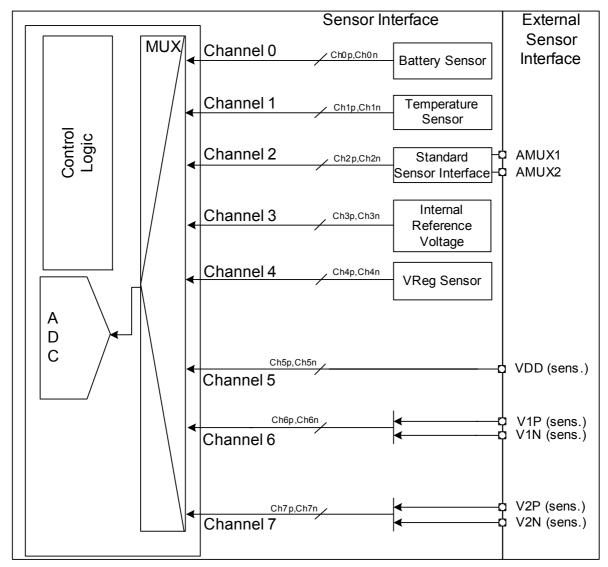

| 2.11.1.1   | Two Differential Highly Sensitive Interfaces to External Sensors |    |

| 2.11.1.2   | Interface to Other Signals                                       |    |

| 2.11.1.3   | Reference Voltages                                               |    |

| 2.11.2     | Temperature Sensor                                               |    |

| 2.11.3     | Battery Voltage Monitor                                          |    |

| 2.11.4     | Analog to Digital Converter (ADC)                                |    |

| 2.11.4.1   | ADC Timing                                                       |    |

| 2.11.4.1.1 | Clock Divider                                                    |    |

|            |                                                                  |    |

| 2.11.4.1.2 Sample Time Delay                                         | 113 |

|----------------------------------------------------------------------|-----|

| 2.11.4.1.3 Conversion Time                                           | 113 |

| 2.11.4.2 ADC Configuration                                           |     |

| 2.11.4.2.1 Reference- and Signal Voltage Selection                   | 114 |

| 2.11.4.2.2 Single ended / Differential Conversion                    | 114 |

| 2.11.4.2.3 Comparator Signal Inversion                               |     |

| 2.11.4.2.4 Channel Gain Selection                                    |     |

| 2.11.4.2.5 Full Conversion or Sub Conversion                         |     |

| 2.11.4.2.6 Analog Offset Correction of the Wheatstone Bridge Signals |     |

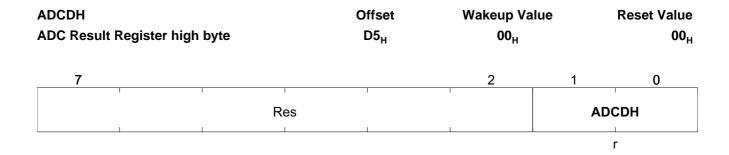

| 2.11.4.3 ADC Conversion Result                                       |     |

| 2.11.5 Register Description                                          |     |

| 2.12 16 bit CRC (Cyclic Redundancy Check) Generator/Checker          |     |

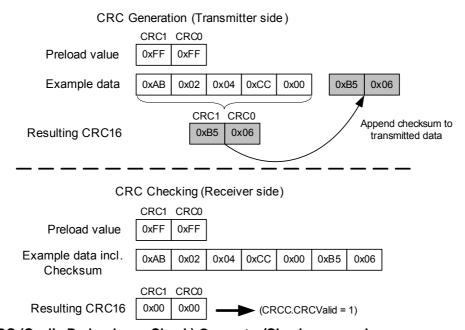

| 2.12.1 Byte-aligned CRC Generation                                   |     |

| 2.12.2 Byte-aligned CRC Checking                                     |     |

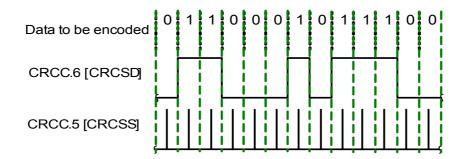

| 2.12.3 Serial bit stream CRC Generation/Checking                     |     |

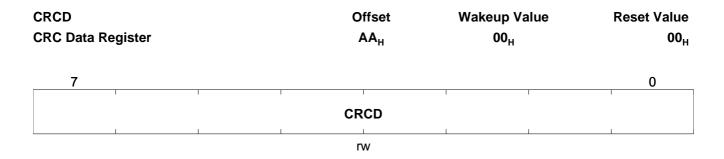

| 2.12.4 Register Description                                          |     |

| 2.13 8 bit Pseudo Random Number Generator                            |     |

| 2.13.1 Register Description                                          |     |

| 2.14 Timers                                                          |     |

| 2.14.1 Timer 0 and Timer 1                                           |     |

| 2.14.1.1 Basic Timer Operations                                      |     |

| 2.14.1.2 Timer Modes                                                 |     |

| 2.14.1.2.1 Timer/Counter 0/1 - Mode 0                                |     |

| 2.14.1.2.2 Timer/Counter 0/1 - Mode 1                                |     |

| 2.14.1.2.3 Timer/Counter 0/1 - Mode 2                                |     |

| 2.14.1.2.4 Timer/Counter 0/1 - Mode 3                                |     |

| 2.14.1.3 Timer/Counter 0/1 Interrupt support                         |     |

| 2.14.1.4 Register Description                                        |     |

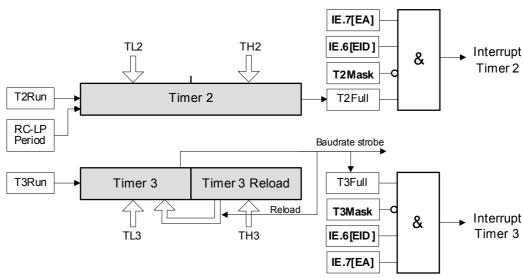

| 2.14.2 Timer 2 and Timer 3                                           |     |

| 2.14.2.1 Basic Timer Operations                                      |     |

| 2.14.2.2 Timer Modes                                                 |     |

| 2.14.2.2.1 Timer 2/3 - Mode 0                                        |     |

| 2.14.2.2.2 Timer 2/3 - Mode 1                                        |     |

| 2.14.2.2.3 Timer 2/3 - Mode 2                                        |     |

| 2.14.2.2.4 Timer 2/3 - Mode 3                                        |     |

| 2.14.2.2.5 Timer 2/3 - Mode 4                                        |     |

| 2.14.2.2.6 Timer 2/3 - Mode 5                                        |     |

| 2.14.2.2.7 Timer 2/3 - Mode 6                                        |     |

| 2.14.2.2.8 Timer 2/3 - Mode 7                                        |     |

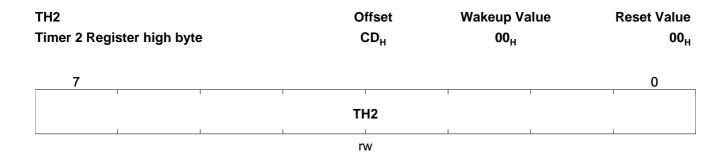

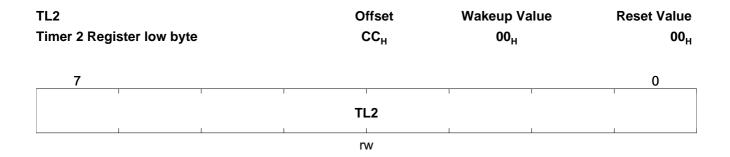

| 2.14.2.3 Register Description                                        |     |

| 2.15 General Purpose Input/Output (GPIO)                             |     |

| 2.15.1 GPIO Port Configuration                                       |     |

| 2.15.2 Spike Suppression on Input Pins                               |     |

| 2.15.3 External Wake-up on PP1-PP4 and PP6-PP9                       |     |

| 2.15.4 Alternative Port Functionality                                |     |

| 2.15.5 Register Description                                          |     |

| 2.16 I <sup>2</sup> C Interface                                      |     |

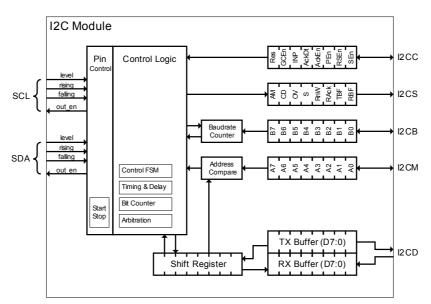

| 2.16.1 Module Structure                                              |     |

| 2.16.2 I <sup>2</sup> C Programming Instructions                     |     |

| 2.16.2.1 Slave Mode Sequence (Polling Mode)                          |     |

| 2.16.2.2 Slave Mode Sequence (Interrupt Mode)                        | 157 |

| 2.16.2.3               | General Call Sequence                        | 158 |

|------------------------|----------------------------------------------|-----|

| 2.16.2.4               | Master Mode Sequence (Polling Mode)          | 158 |

| 2.16.2.5               | Master Mode Sequence (Interrupt Mode)        | 158 |

| 2.16.3                 | Register Description                         | 160 |

| 2.17                   | SPI Interface                                | 165 |

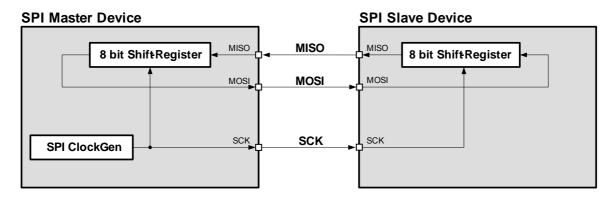

| 2.17.1                 | SPI Functionality                            | 165 |

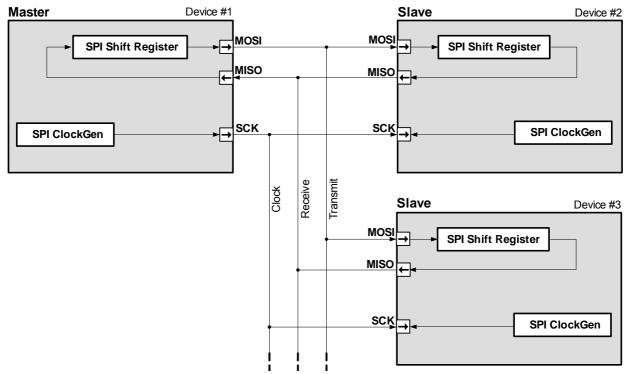

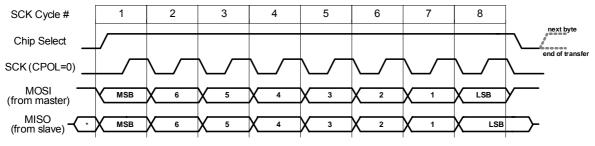

| 2.17.1.1               | Full-Duplex Operation                        | 166 |

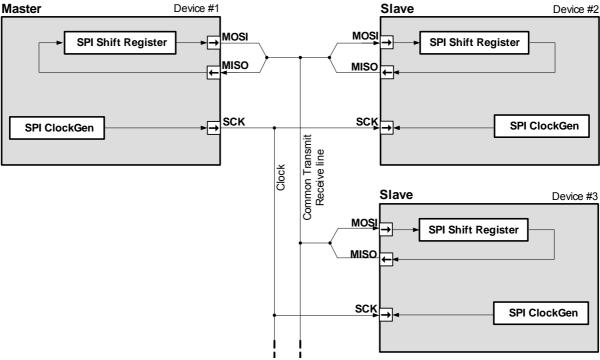

| 2.17.1.2               | Half-Duplex Operation                        | 167 |

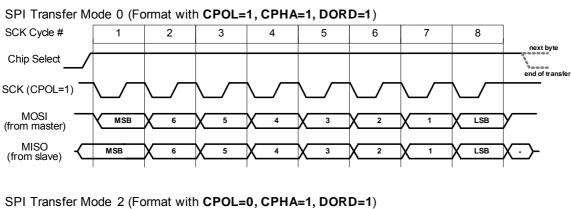

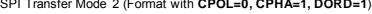

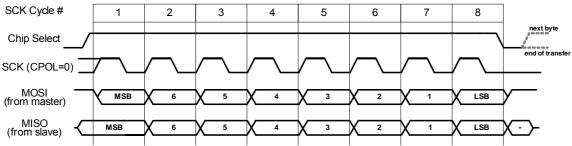

| 2.17.1.3               | Data Modes                                   | 168 |

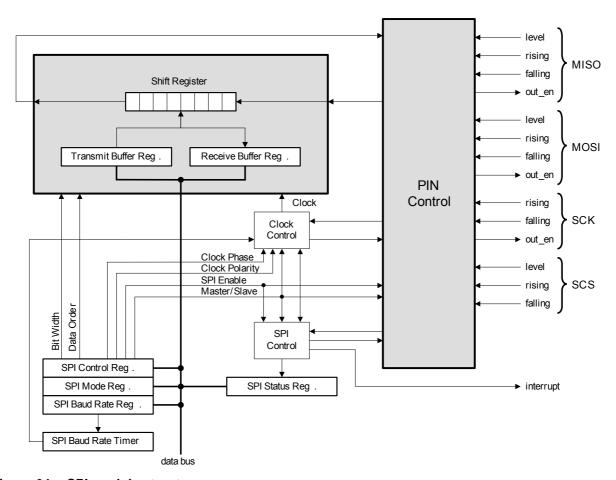

| 2.17.2                 | Module Structure                             | 169 |

| 2.17.3                 | Interrupt Support                            | 169 |

| 2.17.4                 | SPI Programming Instructions                 |     |

| 2.17.4.1               | Slave Mode Sequence                          |     |

| 2.17.4.2               | Master Mode Sequence                         |     |

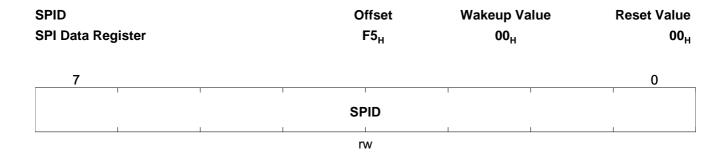

| 2.17.5                 | Register Description                         |     |

| 2.18                   | PROGRAMMING Mode Operation                   |     |

| 2.18.1                 | FLASH Write Line                             |     |

| 2.18.2                 | FLASH Read Line                              |     |

| 2.18.3                 | FLASH Erase                                  |     |

| 2.18.4                 | FLASH Check Erase Status                     |     |

| 2.18.5                 | FLASH Set Code Lock (Lockbyte 2)             |     |

| 2.18.6                 | FLASH Set User Data Sector Lock (Lockbyte 3) |     |

| 2.18.7                 | Read Status                                  |     |

| 2.19                   | DEBUG Mode Operation                         |     |

| 2.19.1                 | ROM Debug Function                           |     |

| 2.19.2                 | DEBUG Mode Commands                          |     |

| 2.19.2.1               | Set SFR                                      |     |

| 2.19.2.2               | Read SFR                                     |     |

| 2.19.2.3               | Set IData                                    |     |

| 2.19.2.4               | Read IData                                   |     |

| 2.19.2.5               | Set XData                                    |     |

| 2.19.2.6               | Read XData                                   |     |

| 2.19.2.7               | Set PC                                       |     |

| 2.19.2.7               | Read PC                                      |     |

| 2.19.2.6               | Single Step                                  |     |

|                        |                                              |     |

| 2.19.2.10<br>2.19.2.11 | ·                                            |     |

| 2.19.2.11              | Run until Breakpoint                         | 104 |

| 3                      | Reference                                    |     |

| 3.1                    | Electrical Data                              | 185 |

| 3.1.1                  | Absolute Maximum Ratings                     | 185 |

| 3.1.2                  | Operating Range                              | 186 |

| 3.1.3                  | Product Characteristics                      | 186 |

| 3.1.3.1                | Temperature Sensor                           | 186 |

| 3.1.3.2                | Battery Sensor                               | 186 |

| 3.1.3.3                | Supply Currents                              | 187 |

| 3.1.3.4                | RF-Transmitter                               | 188 |

| 3.1.3.5                | LF Receiver                                  | 189 |

| 3.1.3.6                | Crystal oscillator                           | 190 |

| 3.1.3.6.1              | Crystal oscillator recommendation            |     |

| 3.1.3.7                | 12 MHz RC HF oscillator                      |     |

| 3.1.3.8                | 2 kHz RC LP oscillator                       | 192 |

|                        |                                              |     |

## PMA51xx

| 5        | Package Outlines                         | 201 |

|----------|------------------------------------------|-----|

|          | References                               | 200 |

| 4        | Register Overview                        | 197 |

| 3.1.4    | Matching Network for the Power Amplifier | 196 |

| 3.1.3.15 | Digital I/O Pin                          | 195 |

| 3.1.3.14 | ADC Interface                            |     |

| 3.1.3.13 | 2 times 128 byte FLASH Data memory       | 194 |

| 3.1.3.12 | 6k FLASH Code memory data                | 194 |

| 3.1.3.11 | VMIN Detector                            | 194 |

| 3.1.3.10 | Power On Reset                           | 193 |

| 3.1.3.9  | Interval Timer                           | 193 |

|          |                                          |     |

## **List of Figures**

# **List of Figures**

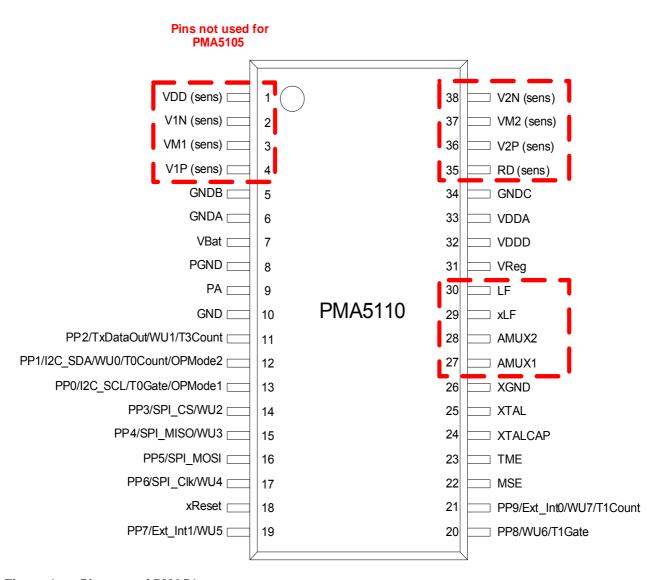

| Figure 1  | Pin-outs of PMA51xx                                           | . 16 |

|-----------|---------------------------------------------------------------|------|

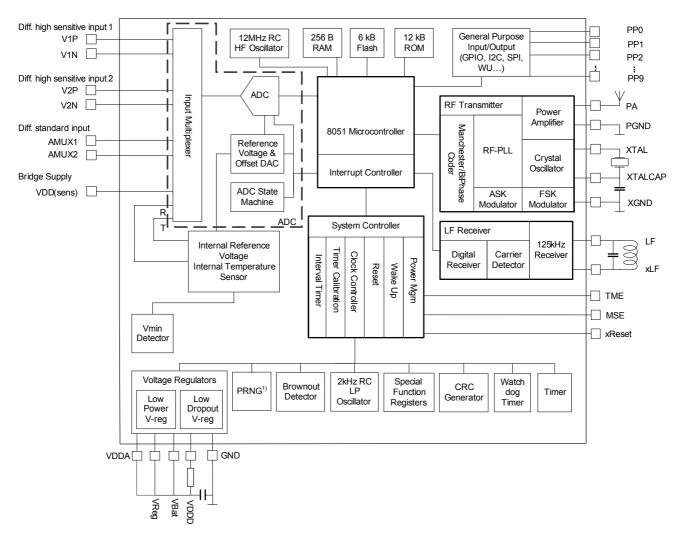

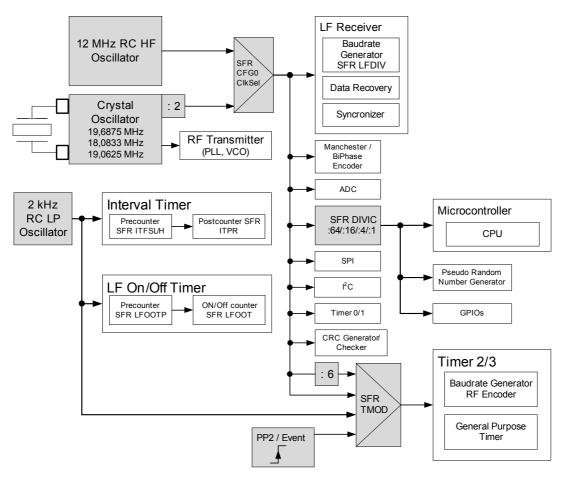

| Figure 2  | PMA51xx Block Diagram                                         | . 28 |

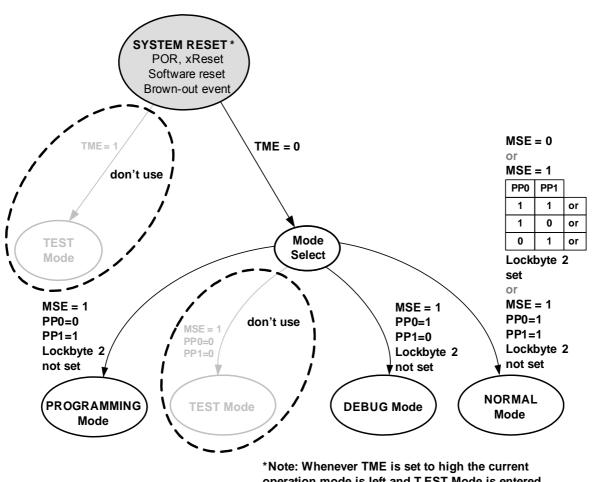

| Figure 3  | Operating Mode Selection of the PMA51xx after Reset           | . 29 |

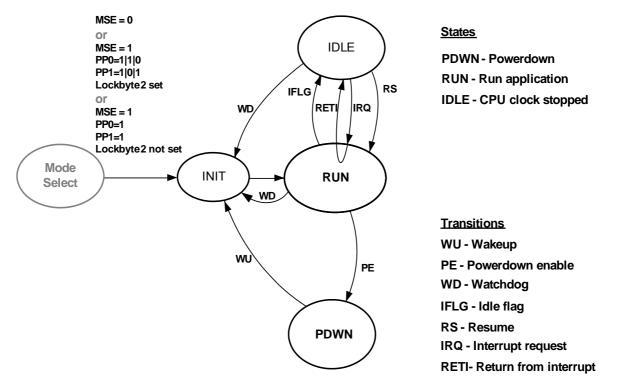

| Figure 4  | NORMAL mode - State Transition Diagram                        | . 30 |

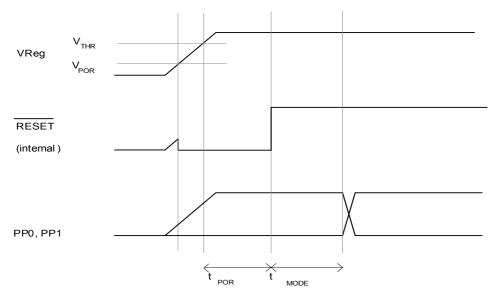

| Figure 5  | Power On Reset - Operating Mode Selection                     | . 31 |

| Figure 6  | Block Diagram of the System Controller                        | . 35 |

| Figure 7  | Interval Timer Block Diagram                                  | . 42 |

| Figure 8  | Calculation of Interval Timer period                          | . 42 |

| Figure 9  | PMA5110 Clock Concept                                         | . 52 |

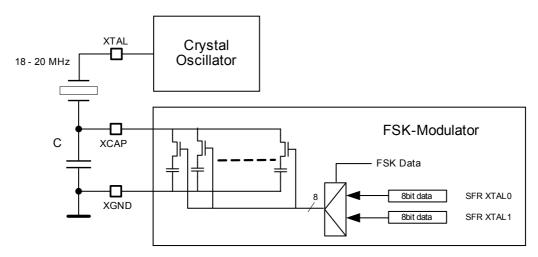

| Figure 10 | Formulas for Crystal selection dependent of RF Bands          | . 53 |

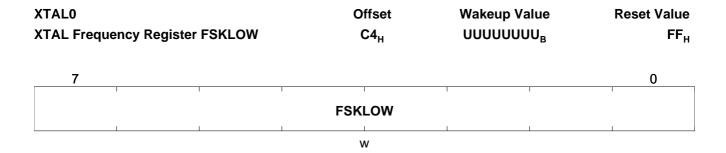

| Figure 11 | Crystal Oscillator and FSK-Modulator Block Diagram            | . 53 |

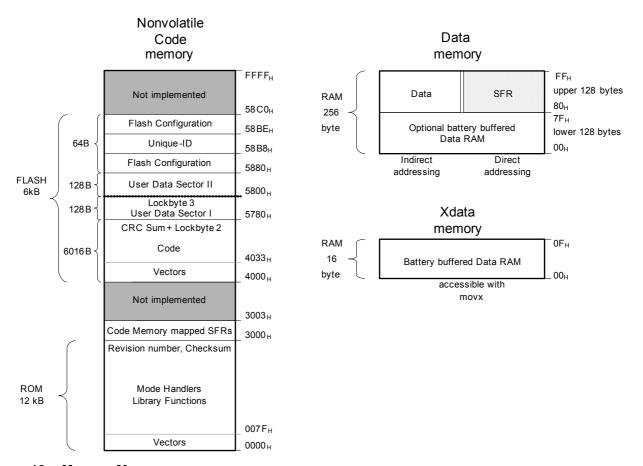

| Figure 12 | Memory Map                                                    | . 57 |

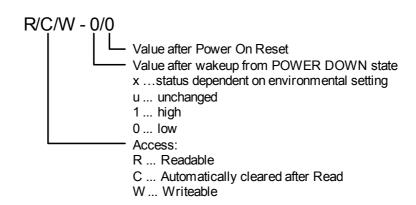

| Figure 13 | Naming Convention for Register Descriptions                   | . 61 |

| Figure 14 | RF Transmitter Block Diagram                                  | . 72 |

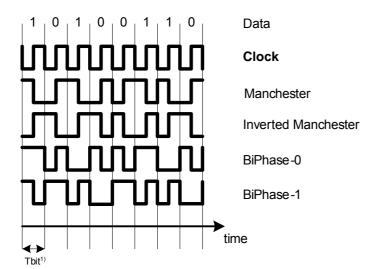

| Figure 15 | Manchester/BiPhase Encoder                                    | . 74 |

| Figure 16 | Diagram of the Different RF Encoder Modes                     | . 75 |

| Figure 17 | Calculation of RF bit rate timer value                        | . 76 |

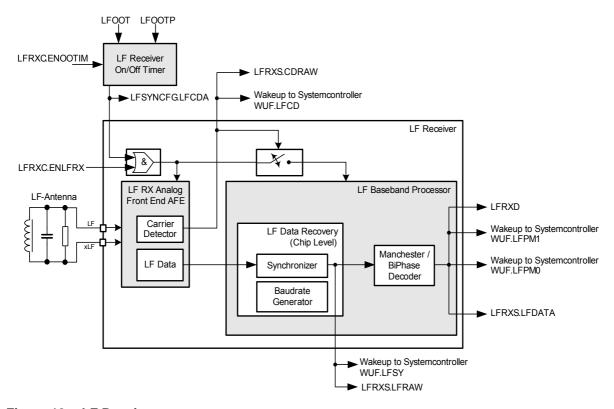

| Figure 18 | LF Receiver                                                   | . 84 |

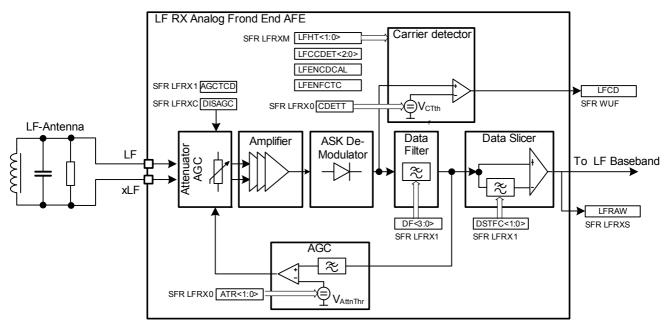

| Figure 19 | LF Receiver AFE Block Diagram                                 | . 85 |

| Figure 20 | LF Receiver AFE Block Diagram                                 | . 85 |

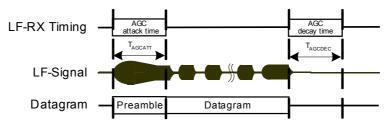

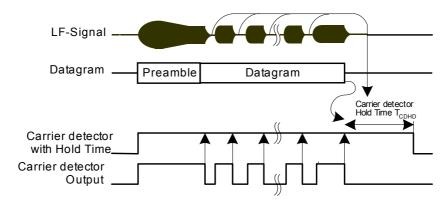

| Figure 21 | LF Receiver Carrier Detector Hold Time Behavior               | . 86 |

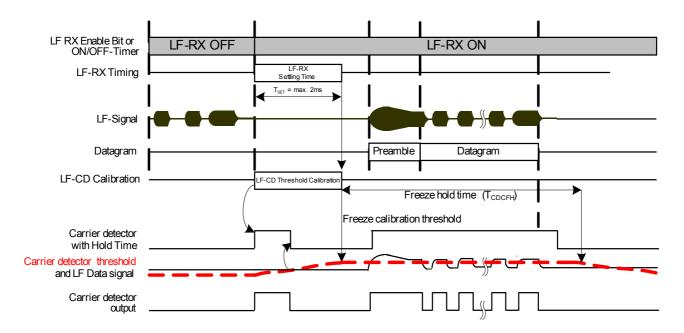

| Figure 22 | Carrier Detector Threshold Calibration Timing (with "freeze") |      |

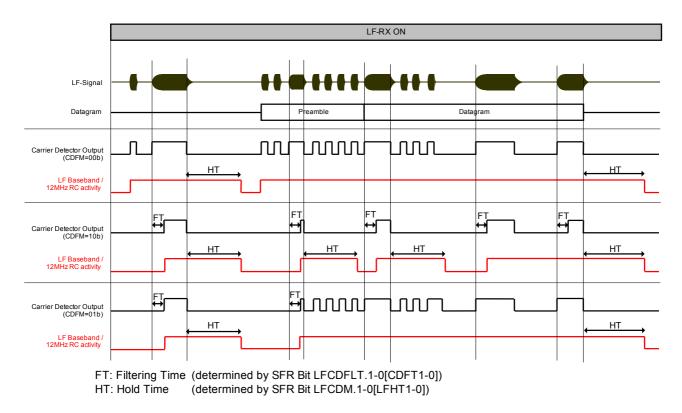

| Figure 23 | LF Receiver Carrier Detector Filtering                        |      |

| Figure 24 | Calculation of time base for LF Receiver On/Off Timer         |      |

| Figure 25 | Calculation of On time for LF Receiver On/Off Timer           |      |

| Figure 26 | Calculation of Off time for LF Receiver On/Off Timer          |      |

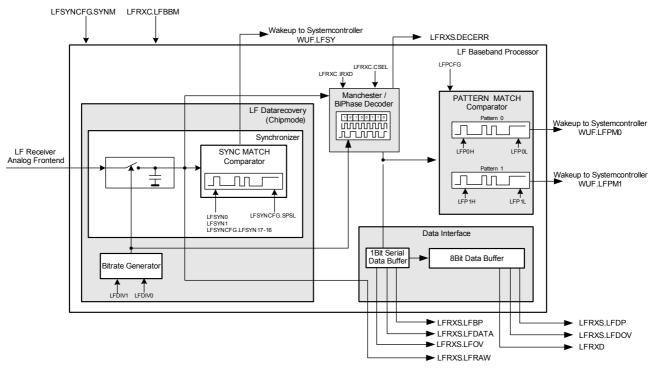

| Figure 27 | LF Receiver Baseband                                          |      |

| Figure 28 | LF Receiver Baseband Configurations                           |      |

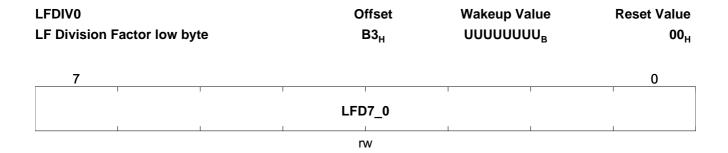

| Figure 29 | Calculation of LF Receiver bit rate                           |      |

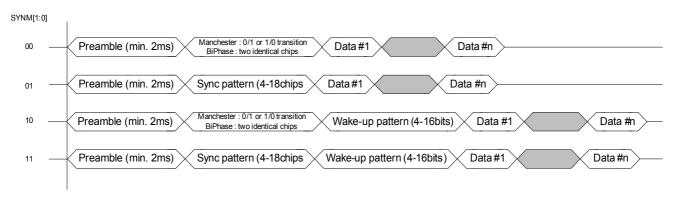

| Figure 30 | LF Receiver Data Decoder schemes                              |      |

| Figure 31 | Block Diagram of the Sensor Interface                         |      |

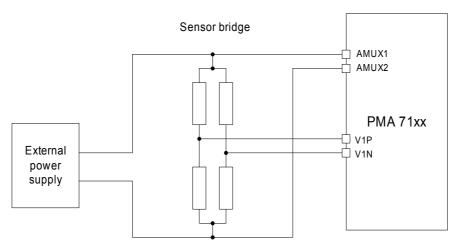

| Figure 32 | Wheatstone Bridge Sensor Connection                           |      |

| Figure 33 | External Sensor Use Channel 2 as Reference Voltage            |      |

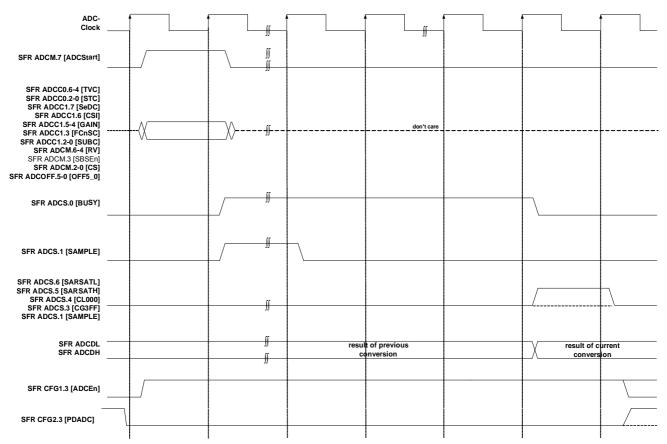

| Figure 34 | ADC Timing diagram (standard conversion)                      |      |

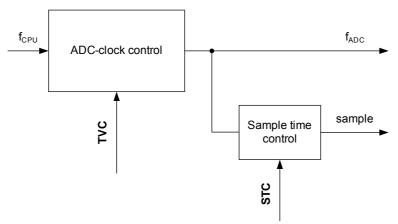

| Figure 35 | ADC frequency calculation                                     | 113  |

| Figure 36 | ADC sample time delay                                         |      |

| Figure 37 | Generation of ADC clock and the sample time signal            |      |

| Figure 38 | Calculation of the ADC conversion time using full conversion  |      |

| Figure 39 | Calculation of the ADC conversion time using sub conversion   |      |

| Figure 40 | ADC offset voltage calculation                                |      |

| Figure 41 | Calculation of single ended conversion                        |      |

| Figure 42 | Calculation of differential conversion                        |      |

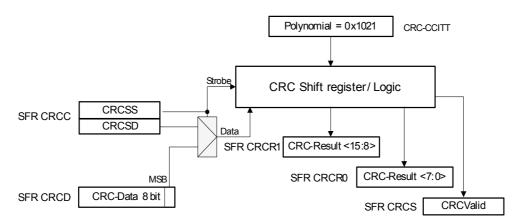

| Figure 43 | CRC (Cyclic Redundancy Check) Generator/Checker               |      |

| Figure 44 | CRC (Cyclic Redundancy Check) Generator/Checker example       |      |

| Figure 45 | Example of Serial CRC Generation/checking                     |      |

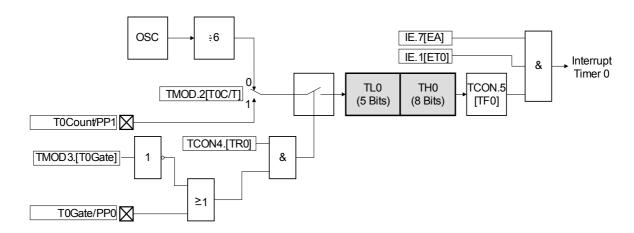

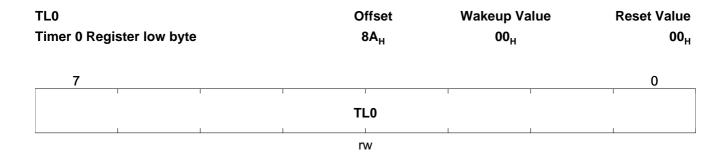

| Figure 46 | Timer/Counter 0, Mode 0, 13-Bit Timer/Counter                 |      |

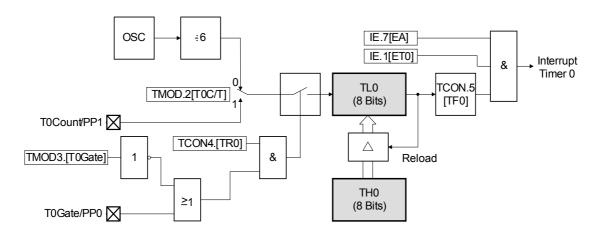

| Figure 47 | Timer/Counter 0, Mode 2: 8-bit Timer/Counter with auto-reload |      |

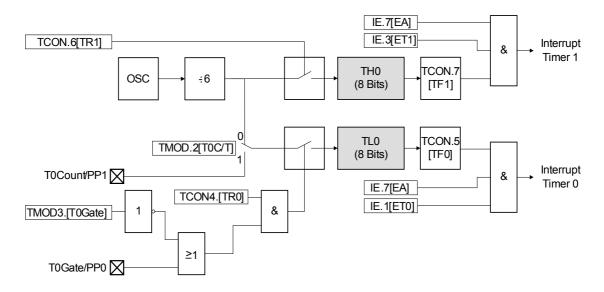

| Figure 48 | Timer/Counter 0, Mode 3: Two 8-bit Timers/Counters            |      |

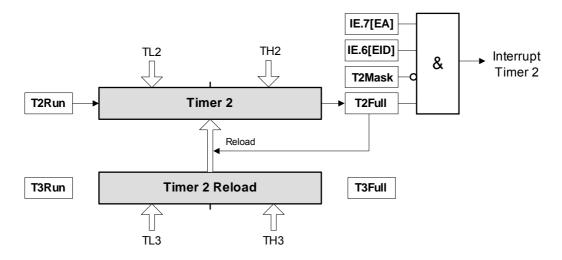

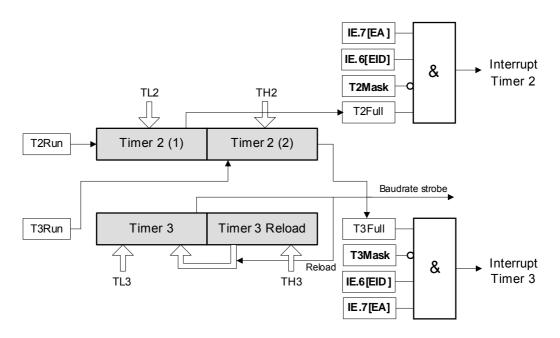

| Figure 49 | Timer 2/3 - Mode 0                                            | 136  |

## **List of Figures**

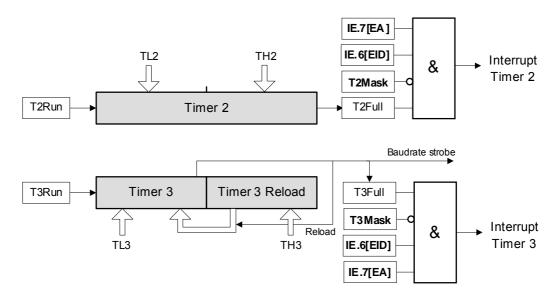

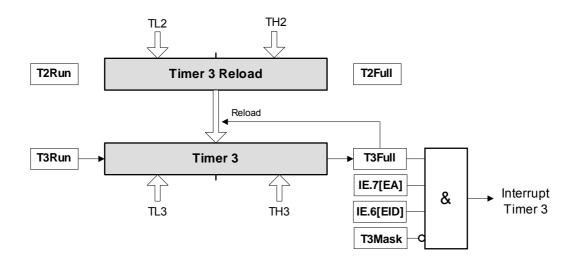

| Figure 50 | Timer 2/3 - Mode 1                                                                | 137 |

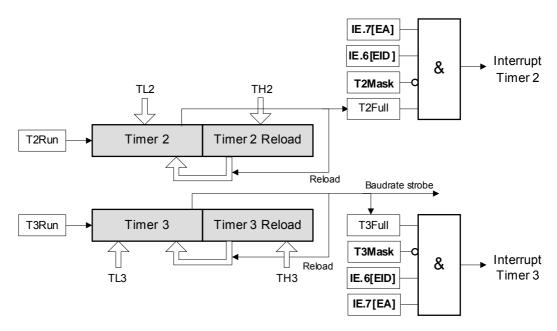

|-----------|-----------------------------------------------------------------------------------|-----|

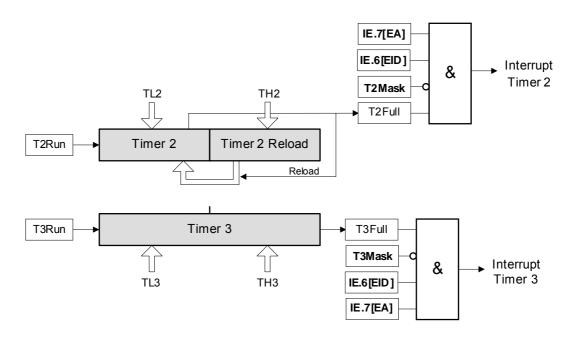

| Figure 51 | Timer 2/3 - Mode 2                                                                | 138 |

| Figure 52 | Timer 2/3 - Mode 3                                                                | 139 |

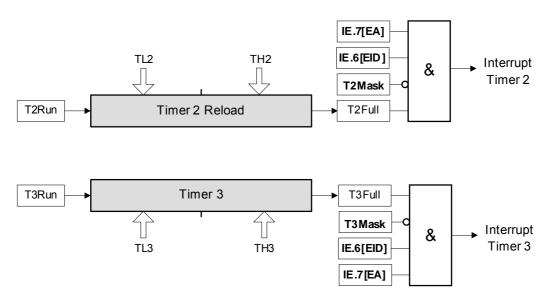

| Figure 53 | Timer 2/3 - Mode 4                                                                | 139 |

| Figure 54 | Timer 2/3 - Mode 5                                                                | 140 |

| Figure 55 | Timer 2/3 - Mode 6                                                                | 141 |

| Figure 56 | Timer 2/3 - Mode 7                                                                |     |

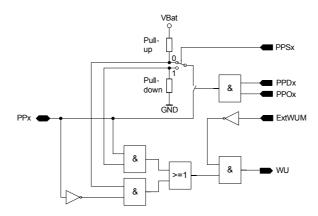

| Figure 57 | Logical description of external wake-ups and internal pull-up/pull-down resistors | 148 |

| Figure 58 | I <sup>2</sup> C module structure                                                 |     |

| Figure 59 | Calculation of I <sup>2</sup> C baud rate                                         | 160 |

| Figure 60 | SPI principle                                                                     | 165 |

| Figure 61 | Full-Duplex configuration                                                         | 166 |

| Figure 62 | Half-Duplex Configuration                                                         | 167 |

| Figure 63 | SPI data modes                                                                    | 168 |

| Figure 64 | SPI module structure                                                              | 169 |

| Figure 65 | Calculation of SPI baud rate                                                      |     |

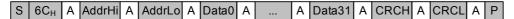

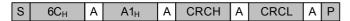

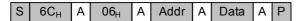

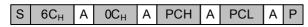

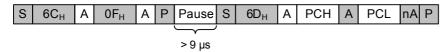

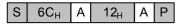

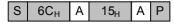

| Figure 66 | Legend for I <sup>2</sup> C-Commands in PROGRAMMING mode                          | 177 |

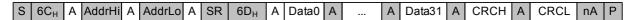

| Figure 67 | FLASH Write Line command                                                          | 178 |

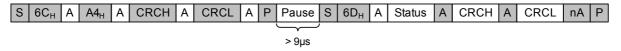

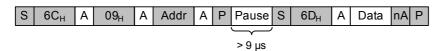

| Figure 68 | FLASH Read Line command                                                           | 178 |

| Figure 69 | FLASH Erase command                                                               | 178 |

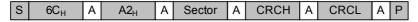

| Figure 70 | FLASH Erase: Sector byte                                                          | 178 |

| Figure 71 | FLASH Check Erase Status command                                                  | 179 |

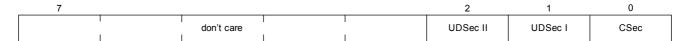

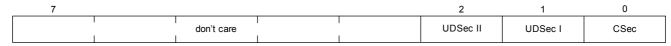

| Figure 72 | FLASH Check Erase Status: Sector byte                                             | 179 |

| Figure 73 | FLASH Check Erase Status: Status byte                                             | 179 |

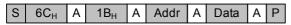

| Figure 74 | FLASH Set Lockbyte 3 command                                                      | 180 |

| Figure 75 | Read Status command                                                               | 180 |

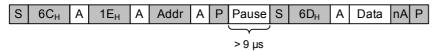

| Figure 76 | Read Status: Status byte                                                          |     |

| Figure 77 | Legend for I <sup>2</sup> C communication in DEBUG                                |     |

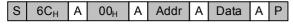

| Figure 78 | Set SFR command                                                                   | 181 |

| Figure 79 | Read SFR command                                                                  | 182 |

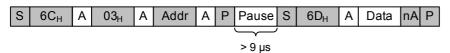

| Figure 80 | Set IData command                                                                 | 182 |

| Figure 81 | Read IData command                                                                |     |

| Figure 82 | Set XData command                                                                 |     |

| Figure 83 | Read XData command                                                                |     |

| Figure 84 | Set PC command                                                                    | 183 |

| Figure 85 | Read PC command                                                                   | 183 |

| Figure 86 | Single Step                                                                       | 183 |

| Figure 87 | Run Interruptible                                                                 | 183 |

| Figure 88 | Run until Breakpoint                                                              | 184 |

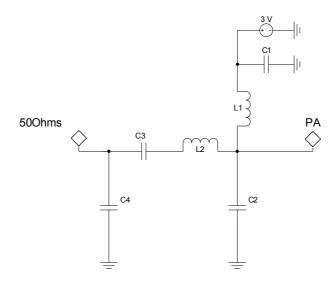

| Figure 89 | Matching network for the power amplifier                                          | 196 |

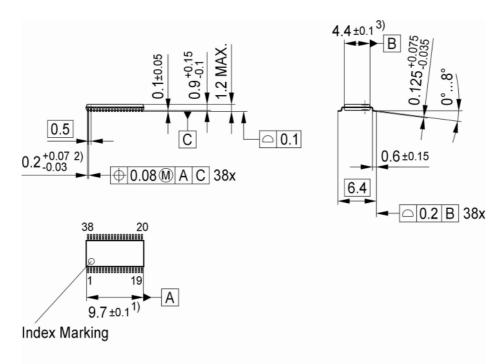

| Figure 90 | Package Outline PG-TSSOP-38                                                       | 201 |

## **List of Tables**

# **List of Tables**

| Table 1  | PMA51xx and PMA71xx Family                             | . 14 |

|----------|--------------------------------------------------------|------|

| Table 2  | Abbreviations for Pin Type                             | . 17 |

| Table 3  | Pin Description                                        | . 17 |

| Table 4  | Operating Mode Selection after Reset                   | . 30 |

| Table 5  | State Transitions in NORMAL mode                       |      |

| Table 6  | Status of Important PMA5110 Blocks in Different States | . 34 |

| Table 7  | Registers Overview                                     | . 37 |

| Table 8  | Registers Overview                                     | . 43 |

| Table 9  | Registers Overview                                     | . 45 |

| Table 10 | Registers Overview                                     | . 54 |

| Table 11 | Registers Overview                                     | . 60 |

| Table 12 | Special Function Registers Overview                    | . 61 |

| Table 13 | Registers Overview                                     | . 65 |

| Table 14 | Interrupt Vector Locations                             | . 67 |

| Table 15 | Registers Overview                                     | . 69 |

| Table 16 | Registers Overview                                     | . 76 |

| Table 17 | Registers Overview                                     | . 93 |

| Table 18 | Selection of the Gain Factor                           | 109  |

| Table 19 | Registers Overview                                     | 116  |

| Table 20 | Registers Overview                                     | 125  |

| Table 21 | Registers Overview                                     | 131  |

| Table 22 | Registers Overview                                     | 142  |

| Table 23 | GPIO Port Configuration                                | 147  |

| Table 24 | I/O Port 1 - Alternative Functionality                 | 148  |

| Table 25 | Registers Overview                                     | 150  |

| Table 26 | Registers Overview                                     | 160  |

| Table 27 | Registers Overview                                     | 170  |

| Table 28 | FLASH Erase: Sector byte                               | 178  |

| Table 29 | FLASH Check Erase Status: Sector byte                  | 179  |

| Table 30 | FLASH Check Erase Status: Status byte                  | 179  |

| Table 31 | Read Status: Status byte                               | 180  |

| Table 32 | Absolute Maximum Ratings                               | 185  |

| Table 33 | Operating Range                                        | 186  |

| Table 34 | Temperature Sensor Characteristics                     | 186  |

| Table 35 | Battery Sensor Characteristics                         | 186  |

| Table 36 | Supply Currents                                        |      |

| Table 37 | RF Transmitter                                         | 188  |

| Table 38 | LF Receiver, V <sub>Bat</sub> = 2.1-3.6V               | 189  |

| Table 39 | Crystal oscillator                                     | 190  |

| Table 40 | NDK crystal oscillator recommendation for PMA51xx      | 191  |

| Table 41 | 12 MHz RC HF oscillator                                | 192  |

| Table 42 | 2 kHz RC LP oscillator                                 | 192  |

| Table 43 | Interval Timer                                         | 193  |

| Table 44 | Power On Reset                                         | 193  |

| Table 45 | VMIN Detector                                          | 194  |

| Table 46 | 6k FLASH Code memory data                              | 194  |

| Table 47 | 2 times 128 byte FLASH Data memory                     | 194  |

| Table 48 | ADC Interface                                          | 195  |

| Table 49 | Digital I/O Pin                                        | 195  |

## PMA51xx

|   | ist | ٩f  | Ta | h  |   |

|---|-----|-----|----|----|---|

| ᆫ | 151 | OI. | Ιd | IJ | ш |

| Γable 50 | Values of the matching network for the power amplifier | 196 |

|----------|--------------------------------------------------------|-----|

| Γable 51 | Register Overview                                      | 197 |

## 1 Product Description

### 1.1 Overview

The SmartLEWIS™ MCU family comprises an ASK/FSK multiband transmitter for the sub 1GHz ISM frequency bands with an embedded 8051 microcontroller as base functionality. Additionally, the highly integrated single chip family has internal sensors and optional peripheral functions like an analog to digital converter (ADC) and a LF Receiver on chip. The operating voltage range of 1.9 to 3.6 V, the high efficiency Power Amplifier and an advanced power control system make the PMA51xx family ideal for battery operated applications where low current consumption is necessary. The pin-compatible product family requires only a few external components and is the basis for flexible wireless control transmitter platforms enabling applications for different frequency bands, output power levels and feature sets based on only one design - just through different mounting options.

The multiband ASK/FSK transmitter for 315/434/868/915 MHz frequency bands contains a fully integrated VCO, a PLL synthesizer, an ASK/FSK modulator and a high efficiency Power Amplifier with selectable output power. Fine tuning of the center frequency can be done by an on-chip capacitor bank.

The integrated microcontroller is instruction set compatible to the standard 8051 processor. It can be clocked with an internal 12 MHz RC HF or an external oscillator. 6 clock cycles are needed for the execution of one instruction. This results in 2 MIPS<sup>1)</sup> when using the 12 MHz RC HF oscillator. The microcontroller is equipped with various peripherals like a hardware Manchester/BiPhase Encoder/Decoder and a CRC Generator/Checker. To store the microcontroller application program code, a 6 kbyte on-chip FLASH memory is integrated. This FLASH memory is also used for saving the unique ID-number of the chip. A comprehensive software function library with high level commands in ROM allows easy and fast time to market development. The library provides many powerful functions like AES-encryption and EEPROM emulation, what helps to reduce the user code size.

Additional peripherals are an integrated temperature sensor and a low battery voltage sensor. Measurements via these internal sensors and reading signals from analog inputs (e.g. from an external analog sensor) are performed under software control.

Depending on the product variant, PMA51xx offers an embedded multi-channel 10-bit analog to digital converter with flexible high-gain settings as interface for a broad variety of analog sensors and an integrated 125 kHz LF Receiver. The LF Receiver enables wireless wake-up in battery operated applications with ultra-long-lifetime or even contactless configuration of the device.

Data Sheet 13 Revision 2.1, 2010-06-02

<sup>1)</sup> MIPS .. Million Instructions Per Second

## 1.2 PMAx1xx Product Family

The PMAx1xx product family contains various product variants listed in Table 1 "PMA51xx and PMA71xx Family" on Page 14.

Note: This data sheet documents the full feature set of the PMA5110, which has the full feature set of the PMA51xx product family available. When using the PMA51xx family data sheet for product variants other than the PMA5110, please keep in mind that not all of the features and data described are relevant for these other members of the family.

Following table shows the functional differences of the PMA51xx and PMA71xx family members:

Table 1 PMA51xx and PMA71xx Family

| Product Name | Ordering Code | RF Transmitter | Embedded<br>8051 MCU | ADC | 125 kHz<br>LF Receiver | Automotive Qualified |

|--------------|---------------|----------------|----------------------|-----|------------------------|----------------------|

| PMA7110      | SP000430596   | X              | Х                    | Х   | Х                      | no                   |

| PMA7107      | SP000450412   | Х              | Х                    |     | Х                      | no                   |

| PMA7106      | SP000450410   | Х              | Х                    | Х   |                        | no                   |

| PMA7105      | SP000450408   | Х              | Х                    |     |                        | no                   |

| PMA5110      | SP000373573   | Х              | Х                    | Х   | Х                      | yes                  |

| PMA5105      | SP000463432   | X              | Х                    |     |                        | yes                  |

The PMA51xx products are supporting a temperature range from -40 to +125°C and are full automotive qualified, tailored for automotive applications and industrial applications in harsh environment. Additionally, Infineon offers the PMA71xx product family with a temperature range of -40 to +85°C, tailored for consumer and industrial applications.

## 1.3 Applications

- Remote Keyless Entry (RKE)

- · Security and alarm systems requiring high quality standards

- · Industrial controls in harsh environments

- Wireless sensing

#### 1.4 Key Features

#### General:

- Supply voltage range from 1.9 V up to 3.6 V

- Operating temperature range from -40 to +125°C

- Low power down current consumption < 0.6 μA</li>

- Advanced power control system for lowest system current consumption, switching the microcontroller or transmitter part into POWER DOWN or IDLE state whenever possible

- PG-TSSOP-38 package

#### Transmitter:

- Multiband RF Transmitter for ISM frequency band 315/434/868/915 MHz

- SW configurable transmit power of 5/8/10 dBm into 50 Ohm load

- Selectable transmit data rates up to 32 kbit/s (64 kchips/s) for the temperature range -40°C to +85°C and 20 kbit/s (40 kchips/s) for temperatures above +85°C

- RF Encoder supporting Manchester-, BiPhase- or NRZ coded data (Chip Mode)

- ASK/FSK modulation capability

- FSK frequency deviation up to 100 kHz

- · Fully integrated VCO and PLL synthesizer

- · Crystal oscillator tuning on chip

#### Microcontroller:

- 8051 instruction set compatible microcontroller (cycle-optimized)

- 6 kbyte free programmable FLASH code memory

- 2 blocks of 128 byte FLASH data memory, alternatively usable as 31 byte emulated EEPROM

- ROM embedded software function library with preprogrammed functions and high level commands for easy programming

- 128 bit AES (Advanced Encryption Standard) embedded as software function

- 256 bytes RAM (128 bytes configurable to keep content in POWER DOWN state)

- 16 bytes XData memory (supplied in POWER DOWN state)

- 2 MIPS when using internal 12 MHz RC HF oscillator

#### Peripherals:

- · 125 kHz ASK LF Receiver

- LF Receiver data rate for typical 3.9 kbit/s (Manchester/BiPhase coded)

- 10 bit ADC with 3 pair differential channels and flexible high-gain settings (e.g. as inputs for external sensors)

- 10 free programmable bidirectional General Purpose Input Output pins (GPIO) with on-chip pull-up/pull-down resistors. 8 of them have wake-up functionality

- On-chip temperature sensor

- · On-chip voltage sensor for low battery voltage measurement

- Brownout Detector

- Manchester/BiPhase Encoder and Decoder

- 16 bit hardware CRC Generator

- 8 bit Pseudo Random Number Generator

- I<sup>2</sup>C bus interface

- SPI bus interface

#### Miscellaneous:

- · Watchdog Timer

- · 4 independent 16 bit timers

- Wake-up from POWER DOWN state possible by different sources: Interval Timer, Watchdog Timer, LF Receiver or external wake-up sources connected to GPIOs

- On-chip debugging via I<sup>2</sup>C interface

- 48 bit unique-ID on chip

## 1.5 Pin Diagram

Figure 1 Pin-outs of PMA51xx

## 1.6 Pin Description

### **Abbreviations**

Standard abbreviations for I/O are shown in Table 2.

Table 2 Abbreviations for Pin Type

| Abbreviations | Description                                 |

|---------------|---------------------------------------------|

| I             | Standard input-only pin. Digital levels.    |

| I/O           | I/O is a bidirectional input/output signal. |

| Al            | Input. Analog levels.                       |

| AO            | Output. Analog levels.                      |

| AI/O          | Input or Output. Analog levels.             |

| PWR           | Power                                       |

| GND           | Ground                                      |

Table 3 Pin Description

| Pin<br>No. | Name     | Pin<br>Type | Buffer Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Function                                                                                                   |

|------------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1          | VDD_sens | AO          | Supply_output  VBat  Voltage Regulator  VReg  VDD (sens)  GNDA  Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Sensor Bridge Positive Supply Output of V <sub>Reg</sub> during measurement.                               |

| 2          | V1N_sens | Al          | Analog  V1N  GNDA  GNDA  CALLER CONTROL OF THE CONT | Channel 6, High-gain ADC Input Negative input connect to sensor bridge. Output of wheatstone bridge sensor |

Table 3

Pin Description (cont'd)

| Pin<br>No. | Name     | Pin<br>Type | Buffer Type              | Function                                                                                                   |

|------------|----------|-------------|--------------------------|------------------------------------------------------------------------------------------------------------|

| 3          | VM1_sens | GND         | Supply  VM1  GNDA        | Channel 6, High-gain ADC Input<br>Sensor bridge negative supply.<br>Same voltage as chip GND.              |

| 4          | V1P_sens | AI          | Analog  VIP   GNDA  GNDA | Channel 6, High-gain ADC Input Positive input connect to sensor bridge. Output of wheatstone bridge sensor |

| 5          | GNDB     | GND         | Supply                   | Ground                                                                                                     |

|            |          |             | PGND GNDB                |                                                                                                            |

|            |          |             | XGND                     |                                                                                                            |

| 6          | GNDA     | GND         | Supply                   | Ground                                                                                                     |

|            |          |             | PGND GNDA                |                                                                                                            |

|            |          |             | XGND                     |                                                                                                            |

Table 3

Pin Description (cont'd)

| Pin<br>No. | Name | Pin<br>Type | Buffer Type            | Function                             |

|------------|------|-------------|------------------------|--------------------------------------|

| 7          | VBat |             | Supply                 | Battery Supply Voltage<br>Regulators |

|            |      |             | VBat Voltage Regulator |                                      |

|            |      |             | VReg                   |                                      |

| 3          | PGND | GND         | Supply                 | Power Amplifier Ground Double bond   |

|            |      |             | PGND •                 |                                      |

|            |      |             | GND -                  |                                      |

|            |      |             | XGND -                 |                                      |

| )          | PA   | AO          | Analog                 | Power Amplifier Output Stage         |

|            |      |             | PA PGND PGND           |                                      |

| 10         | GND  | GND         | Supply(Analog)         | Ground                               |

|            |      |             | GND 100                |                                      |

Table 3

Pin Description (cont'd)

| Pin | Name                                    | Pin  | Buffer Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Function                                                                                                                                                           |

|-----|-----------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Name                                    | Туре | Daniel Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                    |

| 11  | PP2/TxDataOut/<br>WU1/T3Count/          | I/O  | PP2  Data  PData  VBat  PPD2  Tristate  PPD2  Serial output of RF Encoder  PP12  T3Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -) Serial output of Manchester / Biphase encoded data) GPIO -) External wake-up source 1 -) Clock source for Timer 3 -) Internal, switchable pull-up/pull-down.    |

| 12  | PP1/I2C_SDA/<br>WU0/T0Count/<br>OPMode2 | I/O  | PP1  Data  Data  Data  PD1  Data  PPD1  Data  PPD1  PD1  Data  PPD1  Tristate  Data  Tristate  Data  PPD1  PPD1  Tristate  PPD1  PPD1  Tristate  PPD1  PPD1  PPD1  Tristate  PPD1  P | PP1 -) I2C bus interface data -) GPIO -) External wake-up source 0 -) Clock source for Timer 0 -) Select operation mode -) Internal, switchable pull-up/pull-down. |

| 13  | PP0/I2C_SCL/<br>T0Gate/OPMode1          | I/O  | Politicum Politi | PP0 -) I2C bus interface clock -) GPIO -) External enable for Timer 0 -) Select operation mode -) Internal, switchable pull-up/pull-down.                          |

Table 3 Pin Description (cont'd)

| Pin<br>No. | Name                 | Pin<br>Type | Buffer Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Function                                                                                                                     |

|------------|----------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 14         | PP3/SPI_CS/WU2       | I/O         | Pellup Pullown Tristate PPD3  VBat  VBat  VBat  VBat  VBat  VBat  Data  PPD3  PPD3  FPD3   | PP3 -) SPI bus interface chip select -) GPIO -) External wake-up source 2 -) Internal, switchable pull-up/pull-down.         |

| 15         | PP4/SPI_MISO/<br>WU3 | I/O         | PP4  Deta  D | PP4 -) SPI bus interface master in slave out -) GPIO -) External wake-up source 3 -) Internal, switchable pull-up/pull-down. |

| 16         | PP5/SPI_MOSI         | I/O         | PPS State Pullup Pullup PPS PPS PPD S PPI MOSI SPIEN PPI S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PP5 -) SPI bus interface master out slave in -) GPIO -) Internal, switchable pull-up/pull-down.                              |

Table 3 Pin Description (cont'd)

| Pin<br>No. | Name             | Pin<br>Type | Buffer Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Function                                                                                                           |

|------------|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

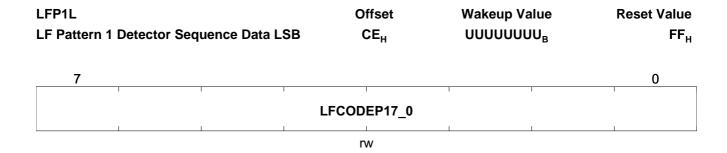

| 17         | PP6/SPI_Clk/WU4  | I/O         | Politicum Politi | PP6 -) SPI bus interface clock -) GPIO -) External wake-up source 4 -) Internal, switchable pull-up/pull-down.     |