## SEMICONDUCTOR

# BridgeMOS™ Reprogrammable PAL® Device

#### **Features**

- Advanced second generation PAL device architecture

- Windowed for reprogrammability

- Up to 22 input terms and 10 outputs

- Variable product terms

2 × (8 thru 16) product terms

- User programmable macro cell

- Output polarity control

- Individually selectable for registered or combinatorial operation

- High Performance

- Commercial

- 15 ns t<sub>CO</sub>

- 20 ns t<sub>S</sub> — 25 ns t<sub>PD</sub>

- Military

- 20 ns t<sub>CO</sub>

- 25 ns ts

- -- 30 ns t<sub>PD</sub>

- Low power 55 mA max (Commercial) 75 mA max (Military)

- Battery Backup Operation

- 2V data retention

- 50 mW Power

- Commercial and military Temperature range

- Enhanced test features

- Phantom array

- TOP TEST

- BOTTOM TEST

- PRELOAD

- · High reliability

- Proven EPROM technology

- >2000V input protection

- 100% programming and functional testing

#### **Functional Description**

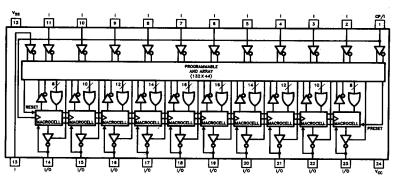

The Cypress CY8C322 is a CMOS second generation Programmable Logic Array device. It is implemented with the familiar sum-of-products (AND-OR) logic structure and a new concept, the "Programmable Macro Cell".

The CY8C322 is executed in a 24 pin 300 mil molded DIP and a 300 mil windowed Cerdip and provides up to 22 inputs and 10 outputs. When the windowed CERDIP is exposed to UV light, the CY8C322 is erased and then can be reprogrammed. The Programmable Macro Cell provides the capability of defining the architecture of each output individually. Each of the 10 potential outputs may be specified to be "REGISTERED" or "COMBINATO-RIAL". Polarity of each output may

#### Logic Symbol and Pinout

0071-2

ridgeMOSTM is a trademark of Cypress Semiconductor Corporation. AL® is a registered trademark of Monolithic Memories Inc.

0071-1

#### Functional Description (Continued)

also be individually selected allowing complete flexibility of output configuration. Further configurability is provided through "ARRAY" configurable "OUTPUT ENABLE" for each potential output. This feature allows the 10 outputs to be reconfigured as inputs on an individual basis or alternately used as a combination I/O controlled by the programmable array.

The CY8C322 features a "VARIABLE PRODUCT TERM" architecture. There are 5 pairs of product terms beginning at 8 product terms per output and incrementing by 2 to 16 product terms per output. By providing this variable structure the CY8C322 is optimized to the configurations found in a majority of applications without creating devices that burden the product term structures with unuseable product terms and lower performance.

Additional features of the Cypress CY8C322 include a synchronous PRESET and an asynchronous RESET product term. These product terms are common to all MACRO CELLS eliminating the need to dedicate standard product terms for initialization functions. The device automatically resets on power-up.

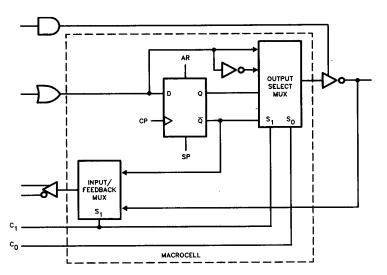

The CY8C322 featuring programmable macro cells and variable product terms provides a device with the flexibility to implement logic functions in the 500 to 800 gate array complexity. Since each of the 10 output pins may be individually configured as inputs on a temporary or permanent basis, functions requiring up to 21 inputs and only a single output down to 12 inputs and 10 outputs are possible. The 10 potential outputs are enabled through the use of product terms. Any output pin may be permanently selected as an output or arbitrarily enabled as an output and an input through the selective use of individual product terms associated with each output. Each of these outputs is achieved through an individual programmable macro cell. These macro cells are programmable to provide a combinatorial or registered inverting or non-inverting output. In a

registered mode of operation, the output of the register is fed back into the array providing current status information to the array. This information is available for establishing the next result in applications such as control-statemachines. In a combinatorial configuration, the combinatorial output or, if the output is disabled, the signal present on the I/O pin is made available to the array. The flexibility provided by both programmable macro cell product term control of the outputs and variable product terms allows a significant gain in functional density through the use of programmable logic.

Along with this increase in functional density, the Cypress CY8C322 provides lower power operation thru the use of CMOS technology, increased testability with a register precoad feature and guaranteed AC performance through the use of a phantom array. This phantom array (P<sub>0</sub>-P<sub>3</sub>) and the "TOP TEST" and "BOTTOM TEST" features allow the CY8C322 to be programmed with a test pattern and tested prior to shipment for full AC specifications without using any of the functionality of the device specified for the product application. In addition, this same phantom array may be used to test the CY8C322 at incoming inspection before committing the device to a specific function through programming. PRELOAD facilitates testing programmed devices by loading initial values into the registers.

#### **Configuration Table 1**

| Registered/Combinatorial |                |                           |  |  |  |

|--------------------------|----------------|---------------------------|--|--|--|

| C <sub>1</sub>           | C <sub>0</sub> | Configuration             |  |  |  |

| 0                        | 0              | Registered/Active Low     |  |  |  |

| 0                        | 1              | Registered/Active High    |  |  |  |

| 1                        | 0              | Combinatorial/Active Low  |  |  |  |

| 1                        | 1              | Combinatorial/Active High |  |  |  |

#### Macrocell

0071-3

#### Selection Guide

| Generic<br>Part | I <sub>CC</sub> mA |     | t <sub>PD</sub> ns |     | t <sub>S</sub> ns |     | t <sub>CO</sub> ns |     |

|-----------------|--------------------|-----|--------------------|-----|-------------------|-----|--------------------|-----|

| Number          | Com                | Mil | Com                | Mil | Com               | Mil | Com                | Mil |

| 8C322-25        | 55                 | _   | 25                 |     | 20                | _   | 15                 | _   |

| 8C322-30        |                    | 75  |                    | 30  | _                 | 25  |                    | 20  |

| 8C322-35        | 55                 |     | 35                 | _   | 30                |     | 25                 |     |

| 8C322-40        |                    | 75  | _                  | 40  |                   | 35  | _                  | 25  |

Maximum Ratings (Above which the useful life may be impaired)

Storage Temperature .....  $-65^{\circ}$ C to  $+150^{\circ}$ C Ambient Temperature with Supply Voltage to Ground Potential (Pin 20 to Pin 10)..... -0.5V to +7.0V DC Voltage Applied to Outputs in High Z State..... -0.5V to +7.0VDC Input Voltage ..... -3.0V to +7.0V

| DC Programming Voltage          | 14.0V    |

|---------------------------------|----------|

| Static Discharge Voltage        |          |

| (per MIL-STD-883 Method 3015.2) |          |

| Latchup Current                 | > 200 mA |

### **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>CC</sub> |  |  |

|------------|------------------------|-----------------|--|--|

| Commercial | 0°C to +70°C           | 5V ± 10%        |  |  |

| Military   | -55°C to +125°C        | 5V ± 10%        |  |  |

Electrical Characteristics Over Operating Range

| Parameters                  | Description                  | Test Conditions                                                                       | Min.       | Max.                    | Units |    |  |

|-----------------------------|------------------------------|---------------------------------------------------------------------------------------|------------|-------------------------|-------|----|--|

| V <sub>OH3</sub>            |                              | $V_{CC} = Min., I_{OH} = -20 \mu A$<br>$V_{IN} = V_{IH_2} \text{ or } V_{IL_2}$       | Commercial | 0.9 V <sub>CC</sub> [3] |       | ., |  |

| v <sub>oH<sub>2</sub></sub> | Output HIGH Voltage          | $V_{CC} = Min., I_{OH} = -3.2 \text{ mA}$<br>$V_{IN} = V_{IH_1} \text{ or } V_{IL_1}$ | Commercial | 2.4                     |       | V  |  |

| V <sub>OH3</sub>            | output III on the            | $V_{CC} = Min, I_{OH} = 20 \mu A$<br>$V_{IN} = V_{IH_2} \text{ or } V_{IL_2}$         | Military   | 0.9 V <sub>CC</sub> [3] |       |    |  |

| v <sub>OH1</sub>            |                              | $V_{CC} = Min, I_{OH} = -2 mA$<br>$V_{IN} = V_{IH_1} \text{ or } V_{IL_1}$            | Minitary   | 2.4                     |       | V  |  |

| $V_{OL_3}$                  |                              | $V_{CC} = Min, I_{OL} = 20 \mu A$<br>$V_{IN} = V_{IH_2} \text{ or } V_{IL_2}$         | Commercial |                         | 0.2   | v  |  |

| V <sub>OL2</sub>            | Output LOW Voltage           | $V_{CC} = Min, I_{OL} = 16 \text{ mA}$ $V_{IN} = V_{IH_1} \text{ or } V_{IL_1}$       |            |                         | 0.4   | V  |  |

| V <sub>OL3</sub>            | o aspar 20 m voltage         | $V_{CC} = Min., I_{OL} = 20 \mu A$<br>$V_{IN} = V_{IH_2} \text{ or } V_{IL_2}$        | Military   |                         | 0.2   | v  |  |

| V <sub>OL1</sub>            |                              | $V_{CC} = Min, I_{OL} = 12 \text{ mA}$<br>$V_{IN} = V_{IH_1} \text{ or } V_{IL_1}$    | Willitary  |                         | 0.4   |    |  |

| $v_{IH_1}$                  | Input HIGH Levels            | TTL Levels [1]                                                                        | 2.0        |                         |       |    |  |

| $V_{IH_2}$                  | Impat III Devels             | BridgeMOS Levels [1]                                                                  |            | 3.85                    |       | v  |  |

| $v_{IL_1}$                  | Input LOW Levels             | TTL Levels [1]                                                                        |            | ,                       | 0.8   |    |  |

| $v_{IL_2}$                  | Input LOW Levels             | BridgeMOS Levels [1]                                                                  |            |                         | 0.4   | v  |  |

| $I_{IX}$                    | Input Leakage Current        | $V_{SS} \leq V_{IN} \leq V_{CC}, V_{CC} = Max$                                        |            | -10                     | + 10  | μА |  |

| loz                         | Output Leakage Current       | $V_{CC} = Max, V_{SS} \le V_{IN} \le V_{CC}$                                          |            | -40                     | +40   | μΑ |  |

| I <sub>SC</sub>             | Output Short Circuit Current | $V_{CC} = Max, V_{OUT} = 0.5V$ [2]                                                    |            | -30                     | -90   | mA |  |

| I <sub>CC</sub>             |                              | $V_{IH} \geq 3.85V$ , $V_{IL} \leq 0.4V$                                              | Commercial |                         | 55    |    |  |

|                             | Power Supply Current         | *IH = 3.03 *, *IL ≥ 0.4 *                                                             | Military   |                         | 75    |    |  |

|                             |                              | $V_{IH} \ge 2.0V, V_{II} \le 0.8V$                                                    | Commercial |                         | 80    | mA |  |

|                             |                              | Military                                                                              |            |                         | 100   |    |  |

| I <sub>CC</sub> DR          | Data Retention Current       | $V_{CC} = 2.0V$<br>$V_{IN} \ge V_{CC} - 0.2V$ , or $\le 0.2V$                         |            |                         | 25    | mA |  |

These are absolute values with respect to ground and all overshoots due to system or tester noise are included.

<sup>2.</sup> For test purposes not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

<sup>3.</sup>  $V_{OH} = 0.9 V_{CC}$  or 4.2V, whichever is greater.

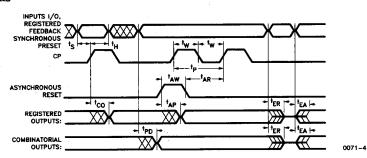

#### **Switching Characteristics CY8C322**

|                  |                                                  | Commercial |      |      | Military |      |      |      |      |       |

|------------------|--------------------------------------------------|------------|------|------|----------|------|------|------|------|-------|

| Parameters       | Description                                      | -25        |      | -35  |          | -30  |      | -40  |      | Units |

|                  |                                                  | Min.       | Max. | Min. | Max.     | Min. | Max. | Min. | Max. |       |

| tPD              | Input or Feedback to<br>Non-Registered Output    |            | 25   |      | 35       |      | 30   |      | 40   | ns    |

| tea              | Input to Output Enable                           | *          | 25   |      | 35       |      | 30   |      | 40   | ns    |

| ter              | Input to Output Disable                          |            | 25   |      | 35       |      | 30   |      | 40   | ns    |

| tco              | Clock to Output                                  |            | 15   |      | 25       |      | 20   |      | 25   | ns    |

| ts               | Input or Feedback Setup Time                     | 20         |      | 30   |          | 25   |      | 35   |      | ns    |

| tH               | Hold Time                                        | 0          |      | 0    |          | 0    |      | 0    |      | ns    |

| tP               | Clock Period (t <sub>s</sub> + t <sub>co</sub> ) | 35         |      | 55   |          | 45   |      | 60   |      | ns    |

| tw               | Clock Width                                      | 15         |      | 25   |          | 20   |      | 30   |      | ns    |

| f <sub>MAX</sub> | Maximum Frequency                                |            | 28.5 |      | 18       |      | 22   |      | 16.5 | MHz   |

| tAW              | Asynchronous Reset Width                         |            | 25   |      | 35       |      | 30   |      | 40   | ns    |

| tAR              | Asynchronous Reset Recovery<br>Time              |            | 25   |      | 35       |      | 30   |      | 40   | ns    |

| t <sub>AP</sub>  | Asynchronous Reset to<br>Registered Output Reset |            | 25   |      | 35       |      | 30   |      | 40   | ns    |

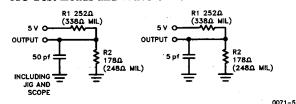

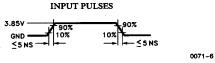

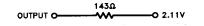

#### **AC Test Loads and Waveforms**

Figure 2

Figure 1a

Figure 1b

0071-7

Equivalent to:

TTL THÉVENIN EQUIVALENT (Commercial)

Equivalent to:

TTL THÉVENIN EQUIVALENT (Military)

0071-

OUTPUT O 2.07V

#### **Switching Waveforms**

#### **Erasure Characteristics**

Wavelengths of light less than 4000 Angstroms begin to erase the CY8C322 in the windowed CERDIP package. For this reason, an opaque label should be placed over the window if the PAL device is exposed to sunlight or fluorescent lighting for extended periods of time.

The recommended dose of ultraviolet light for erasure is a wavelength of 2537 Angstroms for a minimum dose (UV)

intensity  $\times$  exposure time) of 1800 mW  $\times$  min/cm<sup>2</sup>. For an ultraviolet lamp with a 40 mW/cm power rating the exposure time would be approximately 45 minutes. The 8C322 needs to be within 1 inch of the lamp during erasure. Permanent damage may result if the PROM is exposed to high intensity UV light for an extended period of time. 7258W  $\times$  sec/cm<sup>2</sup> is the recommended maximum dosage.

#### **Ordering Information**

| tpD<br>(ns) | ts<br>(ns) | tCO<br>(ns) | Ordering Code | Package | Operating Range |

|-------------|------------|-------------|---------------|---------|-----------------|

| 25          | 20         | 15          | CY8C322-25PC  | P13     | Commercial      |

|             |            |             | CY8C322-25WC  | W14     |                 |

|             |            |             | CY8C322-25JC  | J64     |                 |

| 30          | 25         | 20          | CY8C322-30DMB | D14     | Military        |

|             |            |             | CY8C322-30WMB | W14     |                 |

|             |            |             | CY8C322-30LMB | L64     |                 |

| 35          | 30         | 25          | CY8C322-35PC  | P13     | Commercial      |

|             |            |             | CY8C322-35WC  | W14     |                 |

|             |            |             | CY8C322-35JC  | J64     |                 |

| 40          | 40 35      | 25          | CY8C322-40DMB | D14     | Military        |

|             |            |             | CY8C322-40WMB | W14     |                 |

|             |            |             | CY8C322-40LMB | L64     |                 |