#### Complete DDR2/3 memory power supplies controller

**Preliminary Data**

#### Features switching

- Switching section (VDDQ)

- 4.5V to 36V input voltage range

- 0.9V, ±1% voltage reference

- 1.8V (DDR2) or 1.5V (DDR3) fixed output voltages

- 0.9V to 2.6V adjustable output voltage

- 1.237V ±1% reference voltage available

- Very fast load transient response using constant-on-time control loop

- No R<sub>SENSE</sub> current sensing using low side MOSFETs' R<sub>DS(ON)</sub>

- Negative current limit

- Latched OVP and UVP

- Soft start internally fixed at 3ms

- Selectable pulse skipping at light load

- selectable No-Audible (33KHz) pulse skip mode

- Ceramic output capacitors supported

- Output voltage ripple compensation

- VTT LDO and VTTREF

- 2Apk LDO with foldback for VTT

- Remote VTT sensing

- High-Z VTT output in SC

- Ceramic output car acitors supported

- ±15mA Low noise buffered reference

#### Applications

- DDR2'3 memory supply

- Digital TV system

- Handheld and PDAs

- CPU and chipset I/O supplies

- SSTL18, SSTL15 and HSTL bus termination

#### **Description**

The device PM6670A is a complete DDR2/3 power supply regulator designed to meet JEDEC specifications.

It integrates a Constant On-Time (C.O.T.) buck controller, a 2. Not sink/source Low Drop Out regulator and a 15mA low noise buffered reference.

rhe C.O.T. architecture assures fast transient response supporting both electrolytic and ceramic output capacitors. An embedded integrator control loop compensates the DC voltage error due to the output ripple.

The 2Apk sink/source linear regulator provides the memory termination voltage with fast load transient response.

The device is full compliant with system sleep states S3 and S4/S5, providing LDO output high impedance in Suspend-To-RAM and Tracking Discharge of all outputs in Suspend-To-Disk.

#### Order codes

| Part number | Package                     | Packaging |

|-------------|-----------------------------|-----------|

| PM6670A     | VFQFPN-24 4x4 (Exposed Pad) | Tube      |

Contents PM6670A

### **Contents**

| 1   | Typical application circuit          |

|-----|--------------------------------------|

| 2   | Pin settings                         |

|     | 2.1 Connections                      |

|     | 2.2 Pin description                  |

| 3   | Electrical data                      |

|     | 3.1 Maximum rating                   |

|     | 3.2 Thermal data                     |

|     | 3.3 Recommended operating conditions |

| 4   | Electrical characteristics           |

| 5   | Block diagram                        |

| 6   | Package mechanical data              |

| 7   | Revision history                     |

| 005 | olețe Producți(s)                    |

|     |                                      |

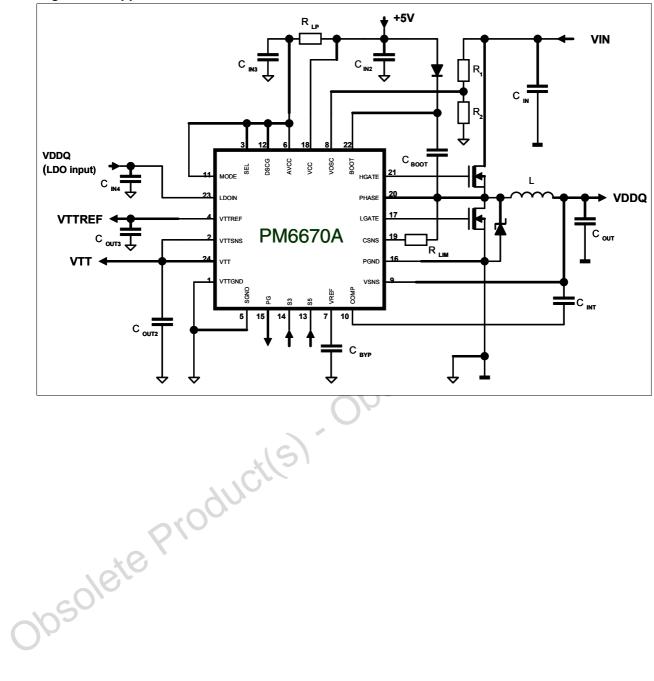

# 1 Typical application circuit

Figure 1. Application circuit

Pin settings PM6670A

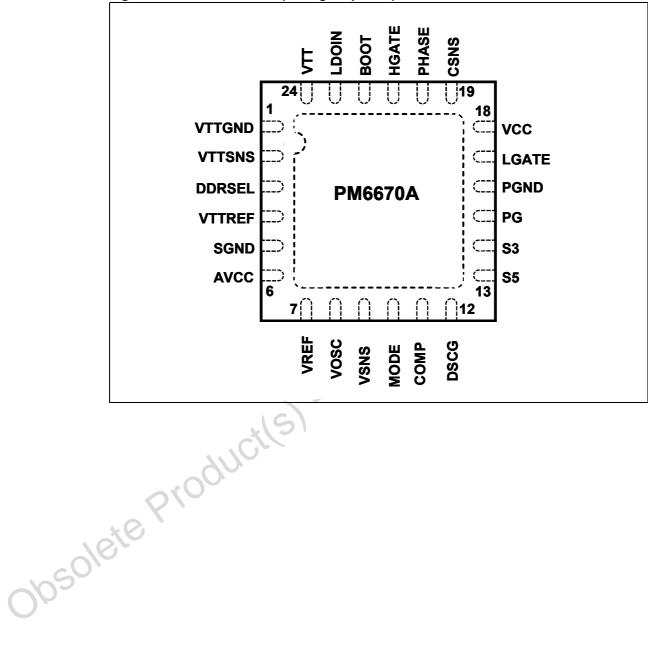

## 2 Pin settings

#### 2.1 Connections

Figure 2. Pin connection (through top view)

PM6670A Pin settings

# 2.2 Pin description

**Table 1. Pin functions**

| N° | Pin    | Function                                                                                                                                                                                                                                                     |  |  |  |

|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1  | VTTGND | LDO Power Ground. Connect to negative terminal of VTT output capacitor.                                                                                                                                                                                      |  |  |  |

| 2  | VTTSNS | LDO Remote Sensing. Connect as close as possible to the load via a low noise PCB trace.                                                                                                                                                                      |  |  |  |

| 3  | DDRSEL | DDR Voltage Selector (if MODE is tied to VCC) or Pulse-Skip/No-Audible Pulse-Skip Selector in Adjustable Mode (MODE voltage lower than 3V). See <i>Mode of Operation Selection</i> section for details.                                                      |  |  |  |

| 4  | VTTREF | Low Noise Buffered DDR Reference Voltage. A 22nF (minimum) ceramic bypass capacitor is required in order to achieve stability.                                                                                                                               |  |  |  |

| 5  | SGND   | Ground Reference for analog circuitry, control logic and VTTREF buffer. Connect together with the thermal pad and VTTGND to a low impedance ground plane. See the <i>Application Note</i> for details.                                                       |  |  |  |

| 6  | AVCC   | +5V Supply for internal logic. Connect to +5V rail through a simple RC filtering network.                                                                                                                                                                    |  |  |  |

| 7  | VREF   | High accuracy output Voltage Reference (1.237V) for multilevel pins setting. It can deliver up to $50\mu A$ . Connect a 100nF capacitor between VREF and SGND in order to enhance noise rejection.                                                           |  |  |  |

| 8  | VOSC   | Frequency Selection. Connect to the central tap of a resistor divider to set the desired switching frequency. The pin cannot be left floating. See <i>Device Description</i> section for details.                                                            |  |  |  |

| 9  | VSNS   | VDDQ Output Remote Sensing. Discharge path for VDDQ in Non-Tracking Discharge. Input for internal resistor divider that provides VDDQ/2 to VTTREF and VTT. Connect as close as possible to the load via a low noise PCB trace.                               |  |  |  |

| 10 | MODE   | Mode of operation selector. If MODE pin voltage is higher than 4V, the fixed output mode is selected. If MODE pin voltage is lower than 4V, it is used as negative input of the error amplifier. See <i>Mode of Operation Selection</i> section for details. |  |  |  |

| 11 | СОМР   | DC Voltage Error Compensation Input for the switching section. Refer to Mode of Operation Selection section for more details.                                                                                                                                |  |  |  |

| 12 | DSCG   | Discharge Mode Selection. Refer to <i>Output Discharge Selection</i> section for Tracking/Non-tracking Discharge or No-Discharge options.                                                                                                                    |  |  |  |

| 13 | S5     | Switching Controller Enable. Connect to S5 system status signal to meet S0-S5 power management states compliance. See <i>Power Management Pins</i> section for details.                                                                                      |  |  |  |

| 14 | S3     | Linear Regulator Enable. Connect to S3 system status signal to meet S0-S5 power management states compliance. See <i>Power Management Pins</i> section for details.                                                                                          |  |  |  |

| 15 | PG     | Power-Good Signal (open drain output). High when VDDQ output voltage is within ±10% of nominal value.                                                                                                                                                        |  |  |  |

| 16 | PGND   | Power Ground for the switching section.                                                                                                                                                                                                                      |  |  |  |

| 17 | LGATE  | Low-side Gate Driver Output.                                                                                                                                                                                                                                 |  |  |  |

Pin settings PM6670A

**Table 1. Pin functions (continued)**

|     | 1. I III Idilotion | (continued)                                                                                                                                                                                                                                          |

|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N°  | Pin                | Function                                                                                                                                                                                                                                             |

| 18  | VCC                | +5V Low-side Gate Driver Supply. Bypass with a 100nF capacitor to PGND.                                                                                                                                                                              |

| 19  | CSNS               | Current Sense Input for the switching section. This pin must be connected through a resistor to the drain of the synchronous rectifier (RDSon sensing)                                                                                               |

| 20  | PHASE              | Switch Node Connection and return path for the High-side Gate Driver.                                                                                                                                                                                |

| 21  | HGATE              | High-side Gate Driver Output                                                                                                                                                                                                                         |

| 22  | воот               | Bootstrap Capacitor Connection. Positive Supply Input of the High-side Gate Driver.                                                                                                                                                                  |

| 23  | LDOIN              | Linear Regulator Input. Connect to VDDQ in normal configuration or to a lower supply to reduce the power dissipation. A 10µF bypass ceramic capacitor is suggested for noise rejection enhancement. See Device Description section for more details. |

| 24  | VTT                | LDO Linear Regulator Output. Bypass with a 20μF (2x10μF MLCC) filter capacitor.                                                                                                                                                                      |

| 3,6 | Produ              | LDO Linear Regulator Output. Bypass with a 20μF (2x10μF MLCC) filter capacitor.                                                                                                                                                                      |

PM6670A Electrical data

### 3 Electrical data

#### 3.1 Maximum rating

Table 2. Absolute maximum ratings (1)

| Symbol             | Parameter                                                           | Value                           | Unit |

|--------------------|---------------------------------------------------------------------|---------------------------------|------|

| V <sub>AVCC</sub>  | AVCC to SGND                                                        | -0.3 to 6                       |      |

| V <sub>VCC</sub>   | VCC to SGND                                                         | -0.3 to 6                       |      |

|                    | PGND, VTTGND to SGND                                                | -0.3 to 0.3                     |      |

|                    | HGATE and BOOT to PHASE                                             | -0.3 to 6                       |      |

|                    | HGATE and BOOT to PGND                                              | -0.3 to 44                      |      |

| V <sub>PHASE</sub> | PHASE to SGND                                                       | -0.3 to 38                      | V    |

|                    | LGATE to PGND                                                       | -0.3 to V <sub>VCC</sub> +0.3   |      |

|                    | CSNS, PG, S3, S5, DSCG, COMP, VSNS, VOSC, VREF, MODE, DDRSEL to GND | -0.3 to V <sub>AVCC</sub> + 0.3 | 5)   |

|                    | VTTREF, VREF, VTT, VTTSNS to SGND                                   | -0.3 to V <sub>AVCC</sub> + 0.3 |      |

|                    | LDOIN, VTT, VTTREF, LDOIN to VTTGND                                 | -0.3 to V <sub>AVCC</sub> + 0.3 |      |

| P <sub>TOT</sub>   | Power dissipation @T <sub>A</sub> = 25°C                            | 2.3                             | W    |

Free air operating conditions unless otherwise specified. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

#### 3.2 Thermal data

Table 3. Thermal data

| Symbol            | Parameter                              | Value      | Unit |

|-------------------|----------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance junction to ambient | 42         | °C/W |

| T <sub>STG</sub>  | Storage temperature range              | -40 to 150 | °C   |

| T <sub>A</sub>    | Operating ambient temperature range    | -40 to 85  | °C   |

| Tj                | Junction operating temperature range   | -25 to 125 | °C   |

## 3.3 Recommended operating conditions

Table 4. Recommended operating conditions

| Symbol            | Parameter           | Min | Тур | Max | Unit |

|-------------------|---------------------|-----|-----|-----|------|

| V <sub>IN</sub>   | Input voltage range | 4.5 |     | 36  |      |

| V <sub>AVCC</sub> | IC supply voltage   | 4.5 |     | 5.5 | V    |

| V <sub>VCC</sub>  | IC supply voltage   | 4.5 |     | 5.5 |      |

Electrical characteristics PM6670A

## 4 Electrical characteristics

$\rm T_A=0^{\circ}C$  to  $85^{\circ}C$  , VCC = AVCC = +5V and LDOIN connected to VDDQ output if not otherwise specified.

**Table 5. Electrical characteristics**

| Symbol              | Parameter                                  | Test                                                             | condition                                     | Min.  | Тур.  | Max.  | Unit |

|---------------------|--------------------------------------------|------------------------------------------------------------------|-----------------------------------------------|-------|-------|-------|------|

| Supply se           | ection                                     | •                                                                |                                               |       |       |       |      |

| I <sub>IN</sub>     | Operating current                          | S3, S5, MODE<br>connected to A'<br>VTT and VTTR<br>VCC connected | VCC, No Load on<br>EF Outputs.                |       | 0.8   | 2     | A    |

| I <sub>STR</sub>    | Operating current in STR                   |                                                                  | DDRSEL connected and to SGND, No Load to AVCC |       | 0.6   | 1     | mA   |

| I <sub>SH</sub>     | Operating current in shutdown              | S3 and S5 tied<br>Discharge Mod<br>VCC connected                 | e active.                                     |       | 1     | 10    | μА   |

|                     | AVCC under voltage lockout upper threshold |                                                                  |                                               | 4.0   | 4.1   | 4.2   | V    |

| UVLO                | AVCC under voltage lockout lower threshold |                                                                  | 10,18                                         | 3.8   | 3.9   | 4.0   | v    |

|                     | UVLO hysteresis                            |                                                                  | c0/10                                         | 50    |       |       | mV   |

| ON-time (           | (SMPS)                                     |                                                                  | 103                                           |       |       |       | •    |

|                     |                                            | MODE and                                                         | VOSC = 300mV                                  | 650   | 750   | 850   |      |

| t <sub>ON</sub>     | On-time duration                           | DDRSEL<br>high,<br>V <sub>VSNS</sub> = 2V                        | VOSC = 500mV                                  | 390   | 450   | 510   | ns   |

| OFF-time            | (SMPS)                                     |                                                                  |                                               |       |       |       |      |

| t <sub>OFFMIN</sub> | Minimum Off Time                           |                                                                  |                                               |       | 300   | 350   | ns   |

| Voltage re          | eference                                   | 1                                                                |                                               |       |       |       |      |

|                     | Voltage accuracy                           | 4.5V < V <sub>IN</sub> < 25                                      | 5V                                            | 1.224 | 1.237 | 1.249 | ٧    |

| -0                  | Load regulation                            | -50μA< I <sub>VREF</sub> <                                       | 50μΑ                                          | -4    |       | 4     | mV   |

| OS                  | Undervoltage lockout fault threshold       |                                                                  |                                               |       | 800   |       |      |

| VDDQ ou             | tput                                       |                                                                  |                                               |       |       |       |      |

|                     | DDR3 VDDQ output voltage                   | MODE connect<br>DDRSEL tied to                                   | ed to AVCC,<br>o SGND, No Load                |       | 1.5   |       | V    |

| $V_{VDDQ}$          | DDR2 VDDQ output voltage                   | MODE and DD<br>AVCC, No Load                                     | RSEL connected to                             |       | 1.8   |       | V    |

|                     | VDDQ output accuracy                       | MODE connect<br>No Load                                          | ed to AVCC,                                   | -2    |       | 2     | %    |

Table 5. Electrical characteristics (continued)

| Symbol               | Parameter                                                                                          | Test condition                                               | Min. | Тур. | Max. | Unit             |

|----------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|------------------|

| Current li           | mit and zero crossing compa                                                                        | rator                                                        | ı    |      | T.   | 1                |

| I <sub>CSNS</sub>    | CSNS input bias current                                                                            |                                                              | 90   | 100  | 110  | μΑ               |

|                      | Comparator offset                                                                                  |                                                              | -5   |      | 5    | mV               |

|                      | Positive current limit threshold                                                                   | Rsense = $1k\Omega$<br>V <sub>PGND</sub> - V <sub>CSNS</sub> |      | -100 |      | mV               |

|                      | Fixed negative current limit threshold                                                             |                                                              |      | 110  |      | mV               |

| V <sub>ZC,OFFS</sub> | Zero crossing comparator offset                                                                    |                                                              | -10  | -5   | 0    | mV               |

| High and             | low side gate drivers                                                                              |                                                              |      |      |      |                  |

|                      | HGATE driver on-resistance                                                                         | HGATE high state (pull-up)                                   |      | 2.0  | 3    |                  |

|                      | HGATE UNIVER ON-TESISTATICE                                                                        | HGATE low state (pull-down)                                  |      | 1.8  | 2.7  |                  |

|                      | LGATE driver on-resistance                                                                         | LGATE high state (pull-up)                                   |      | 1.4  | 2.1  | $\supset \Omega$ |

|                      | LGATE driver on-resistance                                                                         | LGATE low state (pull-down)                                  |      | 0.6  | 0.9  | •                |

| UVP/OVP              | protections and PGOOD SIGI                                                                         | NAL (SMPS only)                                              | .c(  | JO., |      |                  |

| OVP                  | Over voltage threshold                                                                             |                                                              | 112  | 115  | 118  |                  |

| UVP                  | Under voltage threshold                                                                            | 3                                                            | 67   | 70   | 73   |                  |

| D000D                | Power-good upper threshold                                                                         | 76                                                           | 107  | 110  | 113  | %                |

| PGOOD                | Power-good lower threshold                                                                         | : 50'                                                        | 87   | 90   | 93   | 1                |

| I <sub>PG,LEAK</sub> | PG leakeage current                                                                                | PG forced to 5V                                              |      |      | 1    | μΑ               |

| V <sub>PG,LOW</sub>  | PG low-level voltage                                                                               | I <sub>PG,SINK</sub> = 4mA                                   |      | 150  | 250  | mV               |

| Soft start           | section (SMPS)                                                                                     | 15)                                                          | l    |      |      |                  |

|                      | Soft-start ramp time (4 steps current limit)                                                       |                                                              | 2    | 3    | 4    | ms               |

| Soft end             | Soft-start current limit step                                                                      |                                                              |      | 25   |      | μА               |

| cO                   | VDDQ Discharge resistance in non-tracking discharge mode                                           |                                                              | 15   | 25   | 35   |                  |

| 02                   | VTT discharge resistance in non-tracking discharge mode                                            |                                                              | 15   | 25   | 35   | Ω                |

|                      | VTTREF discharge<br>resistance in non-tracking<br>discharge mode                                   |                                                              | 1k   | 1.5k | 2k   |                  |

|                      | VDDQ Output threshold<br>synchronous for final tracking<br>to non-tracking discharge<br>transition |                                                              | 0.2  | 0.4  | 0.6  | V                |

Electrical characteristics PM6670A

Table 5. Electrical characteristics (continued)

| Symbol                       | Parameter                                        | Test condition                                                    | Min. | Тур.  | Max. | Unit |  |

|------------------------------|--------------------------------------------------|-------------------------------------------------------------------|------|-------|------|------|--|

| V <sub>TT</sub> LDO          | section                                          |                                                                   |      | I     |      |      |  |

| I <sub>LDOIN,ON</sub>        | LDO input bias current in full-<br>on state      | S3 = S5 = +5V, No Load on VTT                                     |      | 1     | 10   |      |  |

| I <sub>LDOIN,</sub><br>STR   | LDO input bias current in suspend-to-RAM state   | S3 = 0V, S5 = +5V,<br>No Load on VTT                              |      |       | 10   | μА   |  |

| I <sub>LDOIN,</sub><br>STD   | LDO input bias current in suspend-to-disk state  | S3 = S5 = 0V, No Load on VTT                                      |      |       | 1    |      |  |

| I <sub>VTTSNS,</sub><br>BIAS | VTTSNS bias current                              | S3 = +5V, S5 = +5V,<br>V <sub>VTTSNS</sub> = V <sub>VSNS</sub> /2 |      |       | 1    |      |  |

| I <sub>VTTSNS,</sub><br>LEAK | VTTSNS leakage current                           | S3 = 0V, S5 = +5V,<br>V <sub>VTTSNS</sub> = V <sub>VSNS</sub> /2  |      |       | 1    | μА   |  |

| I <sub>VTT,LEAK</sub>        | VTT leakage current                              | S3 = 0V, S5 = +5V,<br>V <sub>VTT</sub> = V <sub>VSNS</sub> /2     | -10  |       | 10   |      |  |

|                              | LDO linear regulator output voltage (DDR2)       | S3 = S5= +5V, I <sub>VTT</sub> = 0A, MODE<br>= DDRSEL = +5V       |      | 0.9   | Cil  | 21   |  |

|                              | LDO linear regulator output voltage (DDR3)       | S3 = S5= +5V, I <sub>VTT</sub> = 0A,<br>MODE = +5V, DDRSEL = 0V   | 04   | 0.75  | •    | , V  |  |

| $V_{VTT}$                    |                                                  | S3 = S5 = MODE = + 5V,<br>-1mA < I <sub>VTT</sub> < 1mA           | -20  |       | 20   |      |  |

|                              | LDO output accuracy respect to VTTREF            | S3 = S5 = MODE = +5V,<br>-1A < I <sub>VTT</sub> < 1A              | -25  |       | 25   | mV   |  |

|                              |                                                  | S3 = S5 = MODE = +5V,<br>-2A < I <sub>VTT</sub> < 2A              | -35  |       | 35   |      |  |

|                              | LDO secures surrent limit                        | V <sub>VTT</sub> < 1.10*( V <sub>VSNS</sub> /2)                   | 2    | 2.3   | 2.6  |      |  |

|                              | LDO source current limit                         | V <sub>VTT</sub> > 1.10*( V <sub>VSNS</sub> /2)                   | 1    | 1.15  | 1.3  | _    |  |

| I <sub>VTT,CL</sub>          | LDO sink current limit                           | V <sub>VTT</sub> > 0.90*( V <sub>VSNS</sub> /2)                   | -2.6 | -2.3  | -2   | -2 A |  |

|                              | LDO SINK CURRENT III'II                          | V <sub>VTT</sub> < 0.90*( V <sub>VSNS</sub> /2)                   | -1.3 | -1.15 | -1   |      |  |

| VTTREF s                     | section                                          |                                                                   |      |       |      |      |  |

|                              | VTTREF output voltage                            | I <sub>VTTREF</sub> = 0A, V <sub>VSNS</sub> = 1.8V                |      | 0.9   |      | V    |  |

| V <sub>VTTREF</sub>          | VTTREF output voltage accuracy respect to VSNS/2 | -15mA < I <sub>VTTREF</sub> < 15mA,<br>V <sub>VSNS</sub> = 1.8V   | -2   |       | 2    | %    |  |

| I <sub>VTTREF</sub>          | VTTREF current limit                             | VTTREF= 0 or VSNS                                                 | -40  |       | +40  | mA   |  |

Table 5. Electrical characteristics (continued)

| Symbol                    | Parameter                                      | Test condition                | Min.                   | Тур. | Max.                    | Unit |

|---------------------------|------------------------------------------------|-------------------------------|------------------------|------|-------------------------|------|

| Power m                   | anagement section                              |                               |                        |      | 1                       |      |

| S3,S5                     | Turn OFF level                                 |                               | 0.4                    |      |                         |      |

| 53,55                     | Turn ON level                                  |                               |                        |      | 1.6                     |      |

| V                         | MODE pin high level threshold <sup>(1)</sup>   |                               | V <sub>AVCC</sub> -0.7 |      |                         |      |

| V <sub>MODE</sub>         | MODE pin low level threshold <sup>(1)</sup>    |                               |                        |      | V <sub>AVCC</sub> - 1.3 |      |

|                           | DDRSEL pin high level threshold <sup>(1)</sup> |                               | V <sub>AVCC</sub> -0.8 |      |                         |      |

| V <sub>DDRSEL</sub>       | DDRSEL pin middle level window <sup>(1)</sup>  |                               | 1.0                    |      | V <sub>AVCC</sub> - 1.5 | V    |

|                           | DDRSEL pin low level threshold <sup>(1)</sup>  |                               |                        |      | 0.5                     | 5)   |

|                           | DSCG pin high level threshold <sup>(1)</sup>   |                               | V <sub>AVCC</sub> -0.8 | 41   | Cr                      | Þ    |

| $V_{\rm DSCG}$            | DSCG pin middle level window <sup>(1)</sup>    |                               | 1.0                    | 0    | V <sub>AVCC</sub> - 1.5 |      |

|                           | DSCG pin low level threshold <sup>(1)</sup>    | 76,                           | (8)                    |      | 0.5                     |      |

| I <sub>IN,LEAK</sub>      | Logic inputs leakage current                   | S3, S5 = 5V                   |                        |      | 10                      | μΑ   |

| I <sub>IN3,LEAK</sub>     | Multilevel inputs leakage current              | MODE, DDRSEL and<br>DSCG = 5V |                        |      | 10                      | μΑ   |

| I <sub>OSC,</sub><br>LEAK | VOSC input leakage current                     | VOSC = 500mV                  |                        |      | 1                       | μА   |

| Thermal                   | shutdown                                       |                               |                        |      |                         |      |

| T <sub>SHDN</sub>         | Shutdown temperature (1)                       |                               |                        | 150  |                         | °C   |

Guaranteed by design. Not production tested.

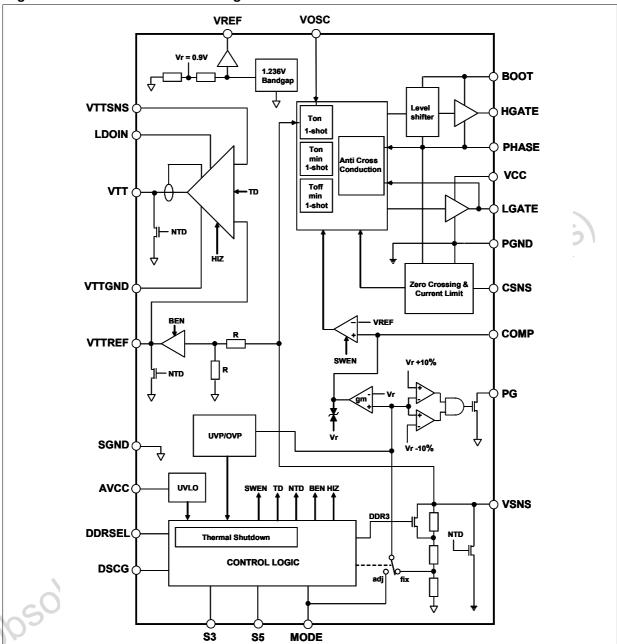

Block diagram PM6670A

# 5 Block diagram

Figure 3. Functional and block diagram

Table 6. Legend

| SWEN | Switching controller enable    |

|------|--------------------------------|

| TD   | Tracking discharge enable      |

| NTD  | Non-tracking discharge enable  |

| BEN  | VTTREF buffer enable           |

| HIZ  | LDO high impedance mode enable |

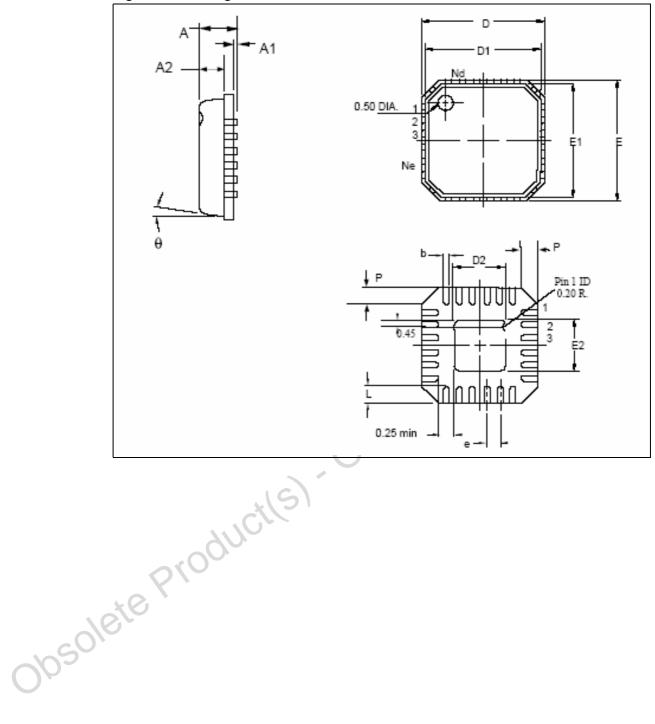

## 6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Table 7. VFQFPN-24 4mm x 4mm mechanical data

| Dim.         |       | mm.  |       |  |

|--------------|-------|------|-------|--|

| Dim.         | Тур   | Min. | Max.  |  |

| A            |       | 0.80 | 1.00  |  |

| A1           | 0.00  | 0.05 | 0.05  |  |

| A2           | 0.65  |      | 0.80  |  |

| D            | 4.00  |      | *(5)  |  |

| D1           | 3.75  |      | 1.100 |  |

| E            | 4.00  |      | 0,0   |  |

| E1           | 3.75  | 01   | )     |  |

| θ            |       |      | 12°   |  |

| Р            | 0.42  | 0.24 | 0.60  |  |

| е            | 0.50  | -0/  |       |  |

| N            | 24.00 | 9    |       |  |

| Nd           | 6.00  |      |       |  |

| Ne           | 6.00  |      |       |  |

| L            | 0.40  | 0.30 | 0.50  |  |

| b            | 10,   | 0.18 | 0.30  |  |

| D2           | 2.10  | 1.95 | 2.25  |  |

| E2           | 2.10  | 1.95 | 2.25  |  |

| osoleite per |       |      |       |  |

Figure 4. Package dimensions

PM6670A Revision history

# 7 Revision history

**Table 8. Revision history**

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 11-Oct-2006 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2006 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics: PM6670ATR