TOSHIBA CMOS Digital Integrated Circuits Silicon Monolithic

## TC9WMB1AFK,TC9WMB1AFU,TC9WMB2AFK,TC9WMB2AFU

TC9WMB1AFK/FU: 1024 Bit (128  $\times$  8 Bit) 2 Wire Serial EEPROM TC9WMB2AFK/FU: 2048 Bit (256  $\times$  8 Bit) 2 Wire Serial EEPROM

The TC9WMB1A and TC9WMB2A are electrically erasable/programmable nonvolatile memory (EEPROM).

### **Features**

- 2-wire serial interface (I<sup>2</sup>C BUS)

- Single power supply

Read:  $V_{CC} = 1.8 \text{ to } 3.6 \text{ V}$

Write:  $V_{CC} = 2.3$  to 3.6 V

• Low power consumption:  $5 \mu A$  (in standby state) 0.5 mA (in read state)

• Operating frequency: 400 kHz (VCC = 2.3 to 3.6 V)

• Byte write and page (8-byte) write

- Write protection

- · Sequential read

- Write time:  $10 \text{ ms} (V_{CC} = 3.0 \text{ to } 3.6 \text{ V})$

$12 \text{ ms } (V_{CC} = 2.3 \text{ to } 2.7 \text{ V})$

• Rewrite endurance: 10<sup>5</sup> times

• Data retention: 10 years

• Wide operating temperature range: -40 to 85°C

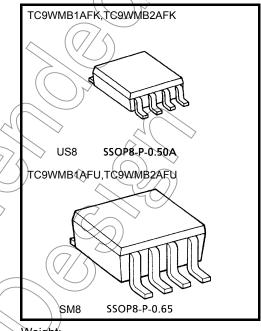

Package: US8, SM8

Weight:

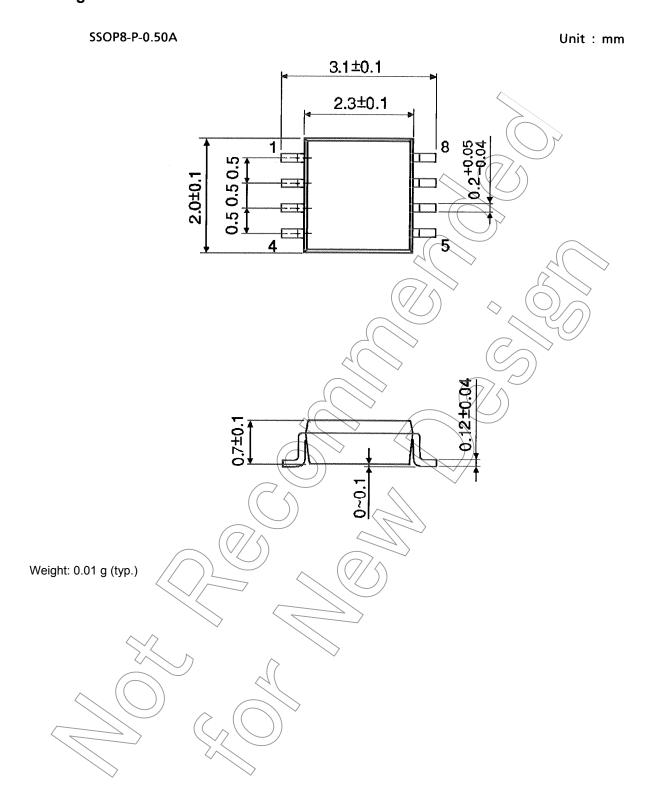

SSOP8-P-0.50A: 0.01 g (typ.) SSOP8-P-0.65: 0.02 g (typ.)

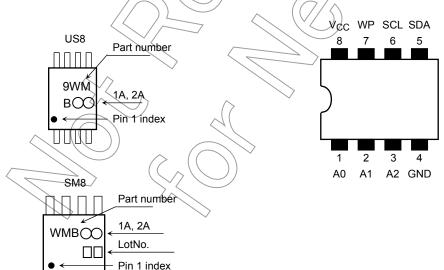

# Product Marking

### Pin Assignment (top view)

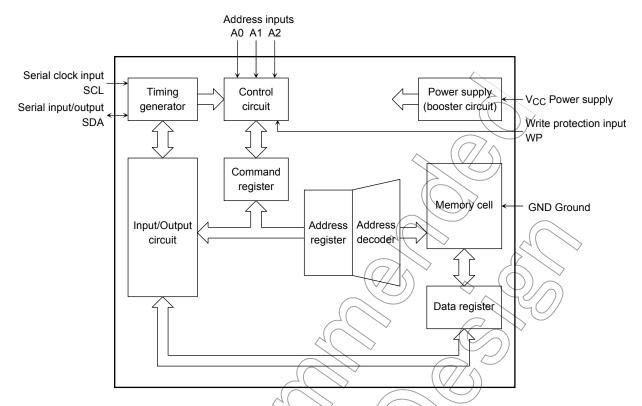

## **Block Diagram**

## **Pin Function**

| Pin Name        | Input/Output | Description                                                                                                                   |

|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------|

| SCL             | Input        | Serial clock input Data is latched on the rising edge of SCL and transferred the falling edge of SCL.                         |

| SDA             | Input/output | Serial input/output This pin must be pulled up with a resistor because it is configured as an N-ch open-drain pin for output. |

| WP              | Input        | Write protection input A high on this input disables writing. A low on this input enables writing.                            |

| A0, A1, A2      | Input        | Address input This pin is used to configure the slave address.                                                                |

| v <sub>cc</sub> | Power supply | 1.8 to 3.6 V (for reading)<br>2.3 to 3.6 V (for writing)                                                                      |

| GND             |              | Q √ (GND)                                                                                                                     |

2

## **Functional Description**

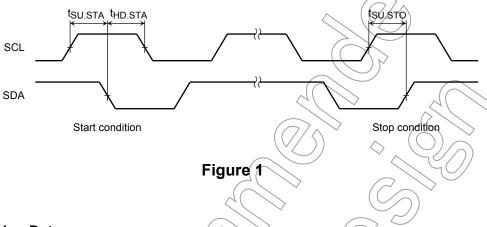

### 1. Start and Stop Conditions

When SCL is high, pulling SDA low produces a start condition and pulling SDA high produces a stop condition. Every instruction is started when a start condition occurs and terminated when a stop condition occurs.

During a read, a stop condition causes the read to terminate and the device to enter the standby state.

During a write, a stop condition causes the fetching of write data to terminate, after which writing starts automatically. Upon the completion of writing, the device enters the standby state.

Start conditions of five times or more cannot be generated from stop condition to the next stop condition.

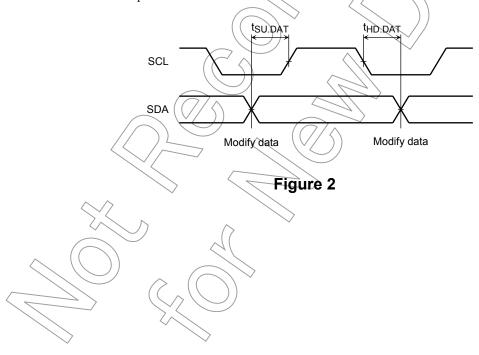

### 2. Modifying Data

Data on the SDA input can be modified while SCL is low. When SCL is high, modifying the SDA input means a start or stop condition.

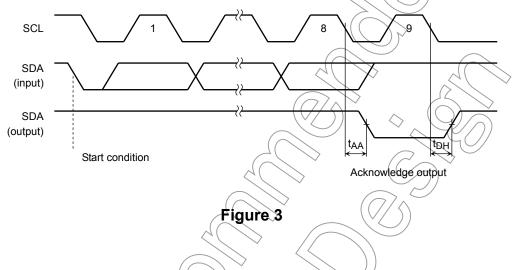

### 3. Acknowledge

Data is transmitted in 8-bit units. The device sends "low" of an acknowledge signal, by pulling SDA during the 9th clock cycle, indicating that it has received data normally. The host releases the bus in the 9th clock cycle to receive an acknowledge signal.

During a write operations, the device is always the receiver so that an acknowledge signal is sent each time it has received 8-bit of data.

During a read operations, the device sends an acknowledge signal after it receives an address following a start condition. Then, a read data is sent and releases the bus to wait for an acknowledge signal from the master. When an acknowledge signal is detected, next address data is sent if a stop condition is not detected. If the device does not detect an acknowledge signal, a read operations is stopped, and enters the standby mode when a stop condition occurs subsequently.

If the device does not detect an acknowledge signal nor a stop condition, it keeps the bus released.

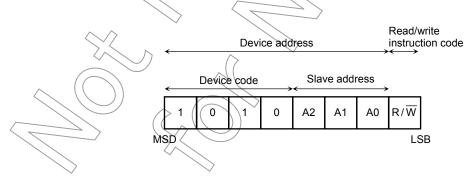

### 4. Device Addressing

After a start condition occurs, 7-bit device address and a 1-bit read/write instruction code are transferred to the device.

The first four bits are called device code, which must always be "1", "0", "1", "0". The next two bits are called slave address and are used to select a device on the bus. The slave address is compared to the value on the address inputs (A0, A1 and A2).

The least significant bit (R/W:READ/WRITE) indicates a read instruction when set to "1" and a write instruction when set to "0".

An instruction is not executed if the device address does not match the specified value.

Figure 4

4

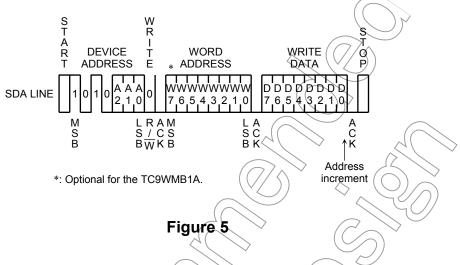

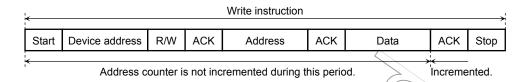

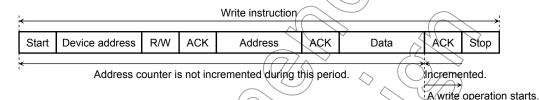

### 5. Write Operation

#### (1) Byte write

A data is written to the specified address at a byte write operation. After a start condition, a device address,  $R/\overline{W}$  (= 0), a word address, and write data are received to the device.

When a stop condition is generated subsequently, write operation starts automatically, rewriting the data at the specified address with the input data. A next instruction cannot be received while write operation is in progress. Therefore, no acknowledge signal is returned. After writing the data, the device automatically enters the standby state.

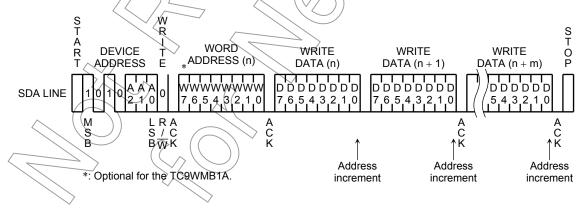

#### (2) Page write

A Data is written up to 8 bytes to the specified page at a page write operation. After a start condition, a device address,  $R/\overline{W}$  (= 0), a word address (n), and write data (n) are received to the device, in the same way as for a byte write operation. Then, write data (n + 1) is immediately received without entering a stop condition, while checking that an acknowledge signal is asserted (0).

The first five bits (W3 to W7) of the word address are the same and the lower three bits (W0 to W2) are automatically incremented so that up to 8 bytes of data can be written.

When the last address within the page is reached, the lower three bits (W0 to W2) of the word address are rolled over to the first address of the page. If more than 8 bytes of write data are transferred, the last 8 bytes are valid.

When a stop condition is generated subsequently, write operation starts automatically, rewriting the data at the specified addresses with the input data.

Figure 6

#### (3) Acknowledge polling

Acknowledge polling is a feature for determining whether rewrite operation is in progress. During rewrite operation, generate a start condition followed by a device address, and  $R/\overline{W}$  (= 0 or 1). The acknowledge feature does not generate an acknowledge signal while rewrite operation is in progress. A low acknowledge signal is generated if rewriting has already completed.

If the next instruction is a write, supply a word address and write data subsequently. If the next instruction is a read, supply a stop condition and then start read operation.

#### (4) Write protection

When "high" is received to the write protection (WP) pin, the TC9WMB1A to protect the entire memory area from being written and the TC9WMB2A to protect the bottom half (80h to FFh) of the memory area from being written. Rewriting is allowed when "low" is received to the write protection pin. While a write is in progress, driving the WP pin high does not stop write operation.

Reading is always enabled regardless of whether the WP pin is "high" or "low"

### 6. Read Operation

Read operation is performed in one of three modes: current address read, random read, and sequential read.

For reading, a device receives a device address and  $R/\overline{W}(=1)$  after a start condition. After read data is sent, terminate a read operation by generating a high acknowledge signal (or releasing the bus without supplying an acknowledge signal) and then supplying a stop condition.

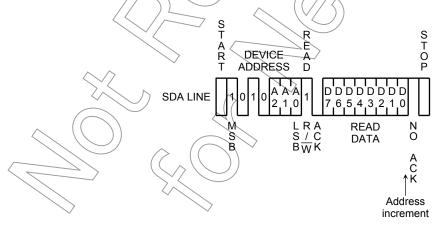

#### (1) Current address read

The internal address counter maintains the address that is next to the last accessed (read or written) word address (n). In current address read mode, data is read from address n + 1, as indicated by the address counter.

In current address read mode, supplying a device address and  $R/\overline{W}$  (= 1) after a start condition, causes the device to generate a low acknowledge signal and send a data at the address indicated by the internal address counter.

The address counter is incremented on the falling edge of the SCL pulse where a data at the eighth bit is sent. If the previous operation was reading data from the last address, the current address is rolled over to address 0. If the previous operation was writing data to the last address of the page, the address is rolled over to the first address of the page.

The current address is maintained in an internal register so that it is lost when the power is turned off. For the first read after power-up, specify an address by performing a random read.

Figure 7

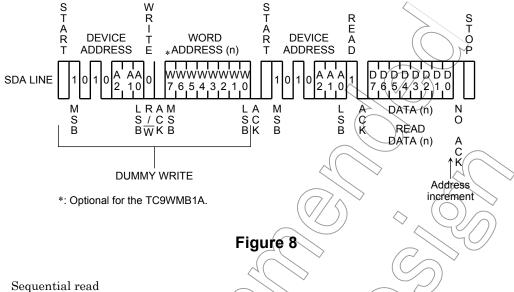

#### (2)Random read

A random read reads data at a specified address. A dummy write is necessary to specify an address. In random read mode, supply a device address,  $R/\overline{W} = 0$ , and a word address after a start condition. Unlike a byte or page write, where write data is supplied immediately, a dummy write only specifies a word address. Then, supply a start condition and transfer a device address and  $R/\overline{W}$  (= 1) in the same way as for a current address read, to read data from the specified address.

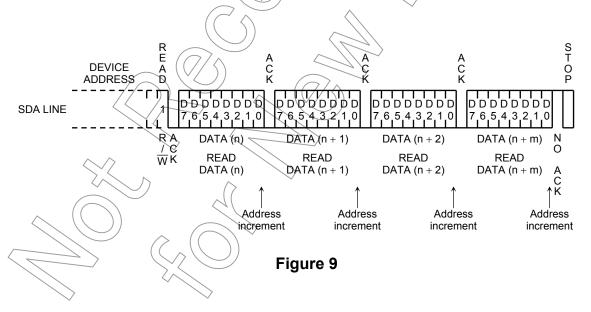

A sequential read reads data sequentially from successive word addresses.

For either current address read or random read, upon receiving a start condition, a device address and R/W (= 1), an acknowledge (low) is placed on the SDA line, followed by the data at the address pointed to by the internal address counter. When an acknowledge (low) is then received, the word address is automatically incremented so that the next data is driven out.

After the last address is reached, the word address is rolled over to address 0.

7

#### 7. Notes on Use

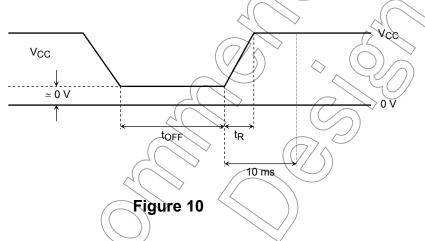

(1) Powering up the device

This device contains a power-on clear circuit, which initializes the internal circuit of the device when the power is turned on. After initialization, the address counter returns to the first address 00H and the SDA pin goes to the high-impedance state (standby state). If initialization fails, the device may malfunction. When powering up the device, observe the following precautions to assure that the clear circuit will operate normally:

- (a) Pull SCL and SDA "high".

- (b) The power rising time (t<sub>R</sub>) must be 10 ms or less.

- (c) After turning off the power, wait at least 100 ms (tOFF) before attempting to power up the device again.

- (d) The supply voltage must rise from  $\approx 0$  V.

- (e) After turning on the power, wait at least 10 ms before attempting to send an instruction to the device.

(2) Pulling up the SDA and SCL pins

The device requires the SDA and SCL pins to be pulled up with an external resistor. The recommended pull-up resistance range is  $1 \text{ k}\Omega$  to  $10 \text{ k}\Omega$ .

(3) Noise elimination time for the SDA and SCL pins

The device contains a low-pass filter for eliminating noise on the SDA and SCL pins. Its guaranteed value corresponds to the noise suppression time Ti, given in the AC characteristics table.

- (4) Write operation

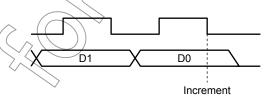

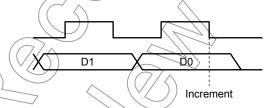

- (a) The address counter is incremented when a write instruction is received successfully. It is incremented on the falling edge of the SCL pulse where the least significant bit of data is received.

Figure 11 Increment Timing Diagram

(b) If a start condition is issued while the device is receiving a write instruction (device address, R/W, address, and data), this write instruction is discarded and the next instruction is accepted. (A byte write is given below as an example. This is the same as a page write.)

(c) If a stop condition is issued while the device is receiving a write instruction (device address, R/W, address, and data), the device enters the standby state. However, the device ignores the stop condition while sending an acknowledge signal after it receives the D0 bit. (A write operation starts.)

(A byte write is given below as an example. This is the same as a page write.)

(d) No instruction is accepted while a write operation is in progress (after a stop condition for a write instruction is received).

(The device does not receive a start or stop condition during this time.)

#### (5) Read operation

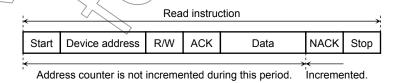

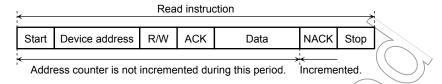

(a) The address counter is incremented when a read instruction is received successfully. It is incremented on the falling edge of the SCL pulse where the least significant bit of data is driven.

Figure 12 Increment Timing Diagram

(b) If a start condition is issued while the device is receiving a read instruction (device address, R/W, address, or data), this read instruction is discarded and the next instruction is accepted. (A start condition is accepted even during data transfer.)

(A current address read is given below as an example. This is the same as the other read modes.)

9 2007-10-19

(c) If a stop condition is issued while data is read (device address, R/W, address, and data), the device enters the standby state.

(A stop condition is accepted even during data transfer.)

(A current address read is given below as an example. This is the same as the other read modes.)

(d) If a start condition is issued while data is read, the SDA pin changes from output to input mode and the device is ready to accept the next instruction.

#### (6) Software reset

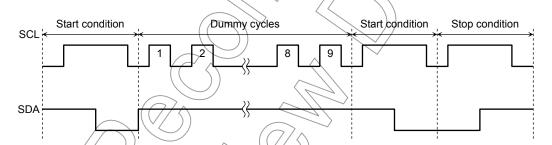

The device cannot be reset externally because it does not incorporate a RESET pin. Instead, the device is reset by software. The software resets the device to the same state using the power-on clear circuit. The address counter returns to the first address 00H and the SDA pin goes to the high-impedance state (standby state).

The software reset is invoked when a start condition is generated followed by nine SCL clock pulses (dummy cycles). While a dummy cycle is inserted, the SDA line must be pulled high. This reset operation stops an acknowledge output and data transfer. The reset is completed by generating another start condition. Issue a stop condition before starting a new transfer.

Start conditions of five times or more cannot be generated from stop condition to the next stop condition.

Figure 13 Software reset

### Absolute Maximum Ratings (Note) (GND = 0 V)

| Characteristics       | Symbol           | Rating                   | Unit  |  |

|-----------------------|------------------|--------------------------|-------|--|

| Supply voltage        | V <sub>CC</sub>  | -0.3 to 7.0              | V     |  |

| Input voltage         | V <sub>IN</sub>  | $-0.3$ to $V_{CC} + 0.3$ | V     |  |

| Output voltage        | V <sub>OUT</sub> | $-0.3$ to $V_{CC} + 0.3$ | V     |  |

| Power dissipation     | PD               | 300 (25°C,SM8)           | mW    |  |

| r ower dissipation    | ۲۵               | 200 (25°C,US8)           | IIIVV |  |

| Storage temperature   | T <sub>stg</sub> | -55 to 125               | °C    |  |

| Operating temperature | T <sub>opr</sub> | -40 to 85                | °6    |  |

Note: Exceeding any of the absolute maximum ratings, even briefly, lead to deterioration in IC performance or even destruction.

Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings and the operating ranges.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook ("Handling Precautions"/"Derating Concept and Methods") and individual reliability data (i.e. reliability test report and estimated failure rate, etc).

## Operating Ranges (Note) (GND = 0 V, T<sub>opr</sub> = -40 to 85°C)

| Characteristics              | Symbol                                 | Test Condition                                      | Min                      | Max                                                 | Unit     |  |

|------------------------------|----------------------------------------|-----------------------------------------------------|--------------------------|-----------------------------------------------------|----------|--|

| Supply voltage (for reading) | V <sub>CC</sub>                        |                                                     | 1.8                      | 3.6                                                 | V        |  |

| Supply voltage (for writing) | Vc¢ (                                  |                                                     | 2.3                      | 3.6                                                 | V        |  |

| High-level input voltage     | V <sub>IH</sub>                        | $2.3 \text{ V} \le \text{V}_{CC} \le 3.6 \text{ V}$ | 0.7 ×<br>V <sub>CC</sub> | V <sub>CC</sub>                                     | V        |  |

| Thigh-level input voltage    | VIH                                    | 1.8 V ≤ V <sub>CC</sub> < 2.3 V                     | 0.8 ×<br>V <sub>CC</sub> | V <sub>CC</sub>                                     |          |  |

| Low-level input voltage      | V <sub>IL</sub>                        | 2.3 V ≤ V <sub>CC</sub> ≤ 3.6 V                     | 0                        | $\begin{array}{c} 0.3 \times \\ V_{CC} \end{array}$ | <b>V</b> |  |

| Low-level input voltage      | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 1.8 V≤V <sub>CC</sub> < 2.3 V                       | 0                        | 0.2 ×<br>V <sub>CC</sub>                            | V        |  |

| Operating frequency          | , <u> </u>                             | $2.3 \text{ V} \le \text{V}_{CC} \le 3.6 \text{ V}$ | 0                        | 400                                                 | kHz      |  |

| Operating frequency          | f <sub>SCL</sub>                       | $1.8 \text{ V} \le \text{V}_{CC} < 2.3 \text{ V}$   | 0                        | 100                                                 | N T Z    |  |

Note: The operating ranges must be maintained to ensure the normal operation of the device. Unused inputs must be tied to either VCC or GND.

SDAC

$C_{L} = 100 \text{ pF}$

### **Electrical Characteristics**

### DC Characteristics (GND = 0 V, $T_{opr} = -40$ to 85°C)

| Characteristics             | Symbol           | Test<br>Condition         | $1.8 \le V_{CC} < 2.3 \ V$ |      | $2.3 \leq V_{CC} \leq 3.6~V$ |            | Unit  |

|-----------------------------|------------------|---------------------------|----------------------------|------|------------------------------|------------|-------|

| Characteristics             | Syllibol         |                           | Min                        | Max  | Min                          | Max        | Offic |

| Input current               | ILI              | _                         | _                          | ±1   | _                            | ⟨±1        | μА    |

| Output leakage current      | I <sub>LO</sub>  | _                         | _                          | ±1   | _                            | ±1         | μА    |

| Low-level output voltage    | V <sub>OL</sub>  | $I_{OL} = 3.2 \text{ mA}$ | _                          | _    | _                            | 0.4        | 1     |

| Low-level output voltage    |                  | I <sub>OL</sub> = 1.5 mA  | _                          | 0.5  |                              |            |       |

| Quiescent supply current    | I <sub>CC1</sub> | _                         | _                          | 5    | <u>~</u> (                   | <b>//5</b> | μА    |

| Supply current during read  | I <sub>CC2</sub> | f = 400 kHz               | _                          | 0.2* |                              | 0.3        | mA    |

| Supply current during write | I <sub>CC3</sub> | f = 400 kHz               | _                          | _    | (-                           | 1.5        | mA    |

\*: f = 100 kHz

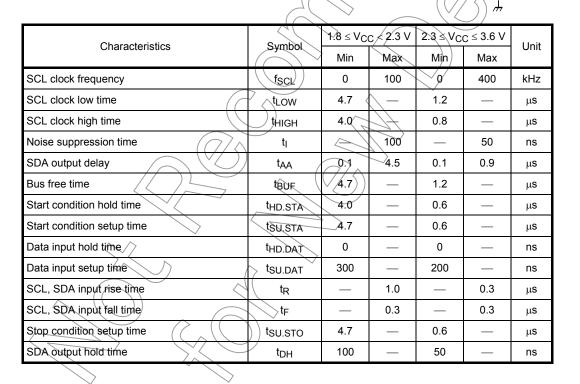

## AC Characteristics (GND = 0 V, $T_{opr} = -40$ to 85°C) Test Conditions

| Input rise/fall time         | 20 ns                                  |

|------------------------------|----------------------------------------|

| Input/output testing voltage | 0.5 × V <sub>CC</sub>                  |

| Output load                  | 100 pF + 1 k $\Omega$ pull-up resistor |

## EEPROM Characteristics (GND = 0 V, 2.3 V $\leq$ V<sub>CC</sub> $\leq$ 2.7 V, T<sub>opr</sub> = -40 to $85^{\circ}$ C)

| Characteristics     | Symbol           | Test Condition | Min                 | Тур. | Max | Unit  |

|---------------------|------------------|----------------|---------------------|------|-----|-------|

| Write time          | t <sub>WR</sub>  | _              | _                   | _    | 12  | ms    |

| Rewrite endurance   | N <sub>EW</sub>  | _              | 1 × 10 <sup>5</sup> | _    | _   | Times |

| Data retention time | t <sub>RET</sub> |                | 10                  | _    | _   | Years |

## **EEPROM Characteristics (GND = 0 V, 2.7 V < V\_{CC} \le 3.6 \text{ V}, T\_{opr} = -40 \text{ to } (85^{\circ}\text{C})**

| Characteristics     | Symbol           | Test Condition Min | Typ. | Max | Unit  |

|---------------------|------------------|--------------------|------|-----|-------|

| Write time          | t <sub>WR</sub>  | -                  | _    | 10  | ms    |

| Rewrite endurance   | N <sub>EW</sub>  | $ 1 \times 10^5$   | _    | _   | Times |

| Data retention time | t <sub>RET</sub> | _ 10               |      |     | Years |

## **Capacitance Characteristics (Ta = 25°C)**

| Characteristics    | Symbol          | Test Condition | ♦ Yec (V) | Typ. | Unit |

|--------------------|-----------------|----------------|-----------|------|------|

| Input capacitance  | C <sub>IN</sub> | 7(>-           | 3.3       | 4    | pF   |

| Output capacitance | CO              | ~ (\) -        | 3.3       | 3    | pF   |

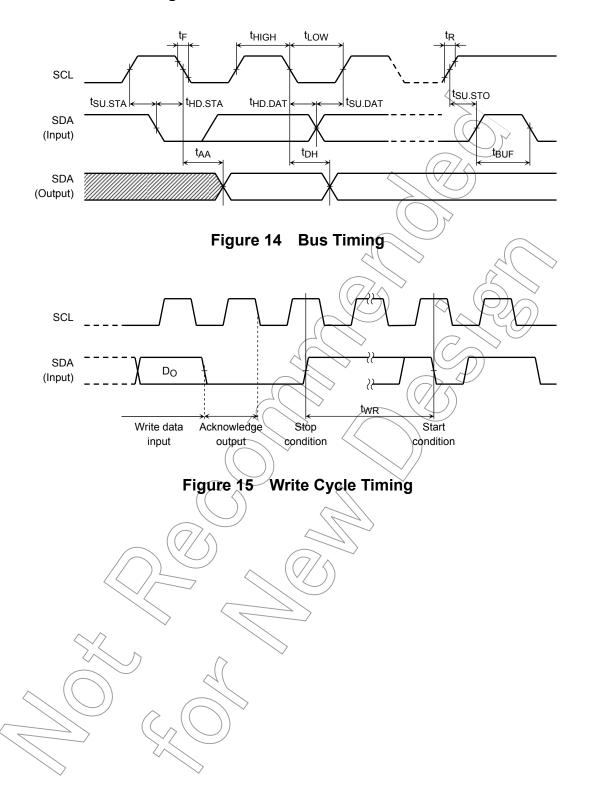

## **AC Characteristics Timing Charts**

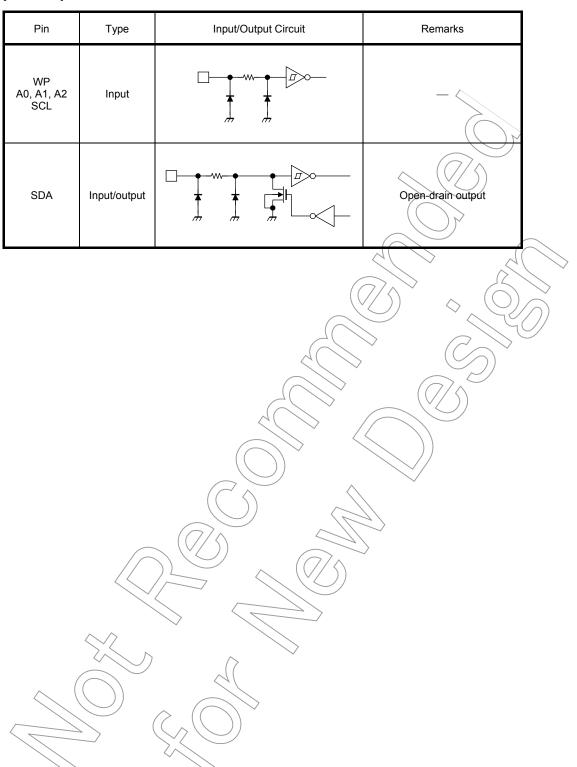

# **Input/Output Circuits of Pins**

## **Package Dimensions**

## **Package Dimensions**

SSOP8-P-0.65 Unit: mm 4.0±0.1 2.8±0.1 1 0.650.650.65 2.9±0.1 540.05 Weight: 0.02 g (typ.)

#### RESTRICTIONS ON PRODUCT USE

- Toshiba Corporation, and its subsidiaries and affiliates (collectively "TOSHIBA"), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively "Product") without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before creating and producing designs and using, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application that Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- Product is intended for use in general electronics applications (e.g., computers, personal equipment, office equipment, measuring equipment, industrial robots and home electronics applications or for specific applications as expressly stated in this document. Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life bodily injury, serious property damage or serious public impact ("Unintended Use"). Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for Unintended Use unless specifically permitted in this document.

- . Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE

FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY

WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR

LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND

LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO

SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product.

Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.