### **General Description**

The MAX4490/MAX4491/MAX4492 single/dual/quad, low-cost CMOS op amps feature Rail-to-Rail® input and output capability from either a single 2.7V to 5.5V supply or dual ±1.35V to ±2.75V supplies. These amplifiers exhibit a high slew rate of 10V/µs and a gain-bandwidth product of 10MHz. They can drive  $2k\Omega$  resistive loads to within 55mV of either supply rail and remain unitygain stable with capacitive loads up to 300pF.

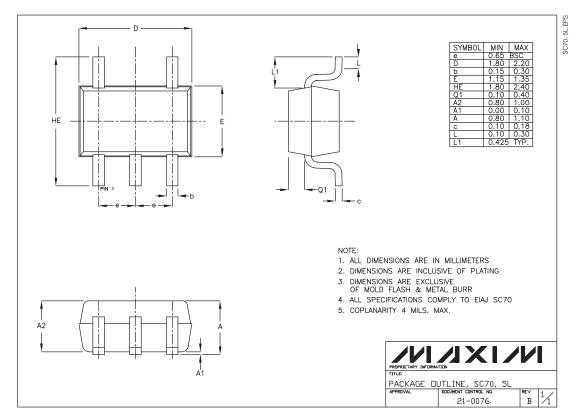

The MAX4490 is offered in the ultra-small, 5-pin SC70 package, which is 50% smaller than the standard 5-pin SOT23 package. Specifications for all parts are guaranteed over the automotive (-40°C to +125°C) temperature range.

### Features

- ♦ 2.7V to 5.5V Single-Supply Operation

- ♦ 10V/µs Slew Rate

- ♦ Rail-to-Rail Input Common-Mode Voltage Range

- ♦ Rail-to-Rail Output Voltage Swing

- ♦ 10MHz Gain-Bandwidth Product

- ♦ Unity-Gain Stable with Capacitive Loads Up to 300pF

- ♦ 50pA Input Bias Current

- ♦ Ultra-Small, 5-Pin SC70 Package (MAX4490)

### **Applications**

**Battery-Powered Instruments**

Portable Equipment

Audio Signal Conditioning

Low-Power/Low-Voltage Applications

Sensor Amplifiers

RF Power Amplifier Control

High-Side/Low-Side Current Sensors

### **Ordering Information**

| PART         | TEMP RANGE      | PIN-<br>PACKAGE | TOP<br>MARK |

|--------------|-----------------|-----------------|-------------|

| MAX4490AXK-T | -40°C to +125°C | 5 SC70-5        | AAB         |

| MAX4490AUK-T | -40°C to +125°C | 5 SOT23-5       | ADKQ        |

| MAX4491AKA-T | -40°C to +125°C | 8 SOT23-5       | AADB        |

| MAX4491AUA   | -40°C to +125°C | 8 µMAX          | _           |

| MAX4492AUD   | -40°C to +125°C | 14 TSSOP        | _           |

| MAX4492ASD   | -40°C to +125°C | 14 SO           | _           |

|              |                 |                 |             |

### Capacitive-Load Stability

### 6000 5000 CAPACITIVE LOAD (pF) 4000 3000 UNSTABLE 2000 1000 0 100 RESISTIVE LOAD $(\Omega)$

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

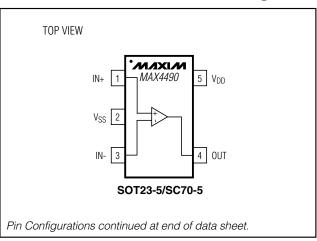

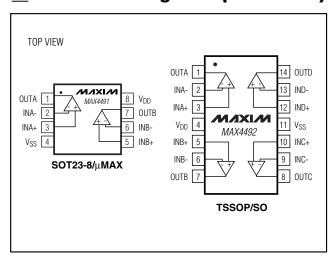

### **Pin Configurations/** Functional Diagrams

MIXIM

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>DD</sub> to V <sub>SS</sub> )  | 6V     |

|-------------------------------------------------------|--------|

| All Other Pins(VSS - 0.3V) to (VDD                    |        |

| Output Short-Circuit Duration                         | 10s    |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |        |

| 5-Pin SC70 (derate 2.5mW/°C above +70°C)              | 200mW  |

| 5-Pin SOT23 (derate 7.1mW/°C above +70°C)             | 571mW  |

| 8-Pin SOT23 (derate 5.26mW/°C above +70°C)            | 421 mW |

| 8-Pin µMAX (derate 4.1mW/°C above +70°C)   | 330mW  |

|--------------------------------------------|--------|

| 14-Pin TSSOP (derate 8.3mW/°C above +70°C) |        |

| 14-Pin SO (derate 8.3mW/°C above +70°C)    | 667mW  |

| Operating Temperature Range40°C to         | +125°C |

| Junction Temperature                       | +150°C |

| Storage Temperature Range65°C to           |        |

| Lead Temperature (soldering, 10s)          | +300°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 5V, V_{SS} = 0, V_{CM} = 0, V_{OUT} = V_{DD}/2, R_L = 100k\Omega$  connected to  $V_{DD}/2$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 1)

| PARAMETER                      | SYMBOL          | CONDITIONS                                               |                              | MIN             | TYP    | MAX      | UNITS   |

|--------------------------------|-----------------|----------------------------------------------------------|------------------------------|-----------------|--------|----------|---------|

| Supply Voltage Range           | V <sub>DD</sub> | (Note 2)                                                 |                              | 2.7             |        | 5.5      | V       |

| Supply Current (per amplifier) | Is              |                                                          |                              |                 | 0.8    | 2        | mA      |

| lace of Office Notes           | \/              | (Note 3)                                                 | T <sub>A</sub> = +25°C       |                 | ±1.5   | ±10      | - mV    |

| Input Offset Voltage           | Vos             | (Note 3)                                                 | $T_A = T_{MIN}$ to $T_{MAX}$ |                 |        | 16       |         |

| Input Bias Current             | ΙΒ              | (Note 3)                                                 |                              |                 | ±0.05  | ±2.5     | nA      |

| Input Offset Current           | los             | (Note 3)                                                 |                              |                 | ±0.05  | ±2.5     | nA      |

| Input Resistance               | RIN             |                                                          |                              |                 | 1000   |          | МΩ      |

| Input Common-Mode Range        | V <sub>CM</sub> | Inferred from CMRR te                                    | st                           | V <sub>SS</sub> |        | $V_{DD}$ | V       |

| Common-Mode Rejection Ratio    | CMRR            | $V_{SS} \le V_{CM} \le V_{DD}$                           |                              | 54              | 75     |          | dB      |

| Power-Supply Rejection Ratio   | PSRR            | $2.7V \le V_{DD} \le 5.5V$                               |                              | 65              | 100    |          | dB      |

| Large-Signal Voltage Gain      | Δ.,             | $(V_{SS} + 0.25V) \le V_{OUT}$<br>$\le (V_{DD} - 0.25V)$ | $R_L = 100k\Omega$           |                 | 110    |          | - dB    |

| Large-Signal Voltage Gain      | Av              |                                                          | $R_L = 2k\Omega$             | 65              | 85     |          |         |

| Output-Voltage Swing High      | VoH             | Specified as<br>VDD - VOH                                | $R_L = 100k\Omega$           |                 | 1.5    |          | - mV    |

| Output-voilage Swing Flight    |                 |                                                          | $R_L = 2k\Omega$             |                 | 55     | 200      |         |

| Output-Voltage Swing Low       | V <sub>OL</sub> | Specified as<br>V <sub>OL</sub> - V <sub>SS</sub>        | $R_L = 100k\Omega$           |                 | 1.5    |          | - mV    |

| Output-voltage Swing Low       |                 |                                                          | $R_L = 2k\Omega$             |                 | 35     | 150      |         |

| Output Short-Circuit Current   | IOUT(SC)        | Sourcing or sinking                                      |                              |                 | ±50    |          | mA      |

| Gain-Bandwidth Product         | GBWP            | $C_L = 10pF$                                             | $C_L = 10pF$                 |                 | 10     |          | MHz     |

| Input Capacitance              | CIN             |                                                          |                              |                 | 5      |          | pF      |

| Phase Margin                   |                 | $C_L = 10pF$                                             |                              |                 | 60     |          | degrees |

| Gain Margin                    |                 | $C_L = 10pF$                                             |                              |                 | 10     |          | dB      |

| Slew Rate                      | SR              | Measured from 10% to 90% of 4V <sub>P-P</sub> step       |                              |                 | 10     |          | V/µs    |

| Voltage-Noise Density          | en              | f = 10 kHz  12                                           |                              |                 | nV/√Hz |          |         |

| Current-Noise Density          | in              | f = 10kHz                                                |                              |                 | fA√Hz  |          |         |

| Capacitive-Load Drive          |                 | Av(CL) = 1, no sustained oscillations 300                |                              |                 | pF     |          |         |

Note 1: All units production tested at TA = +25°C. Limits over temperature guaranteed by design.

Note 2: Guaranteed by the Power-Supply Rejection Ratio (PSRR) test.

Note 3: Input Offset Voltage, Input Bias Current, and Input Offset Current are all tested and guaranteed at both ends of the common-mode range.

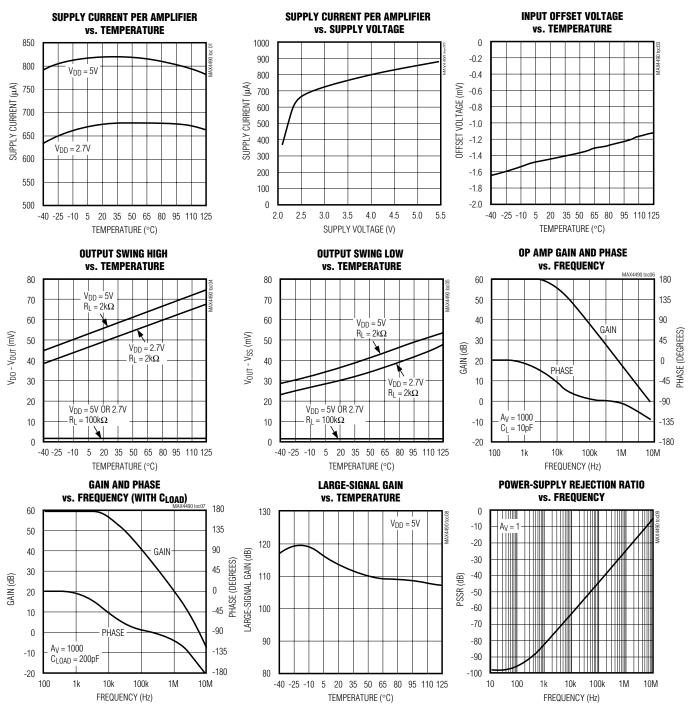

### **Typical Operating Characteristics**

$(V_{DD} = 5V, V_{SS} = 0, V_{CM} = V_{DD}/2, R_L = 100k\Omega$  to  $V_{DD}/2, T_A = +25^{\circ}C$ , unless otherwise noted.)

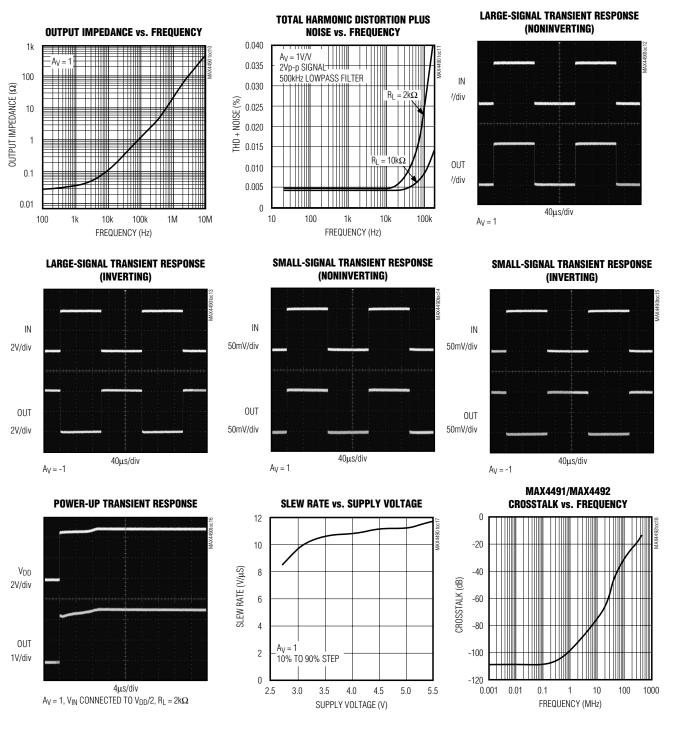

### Typical Operating Characteristics (continued)

$(V_{DD} = 5V, V_{SS} = 0, V_{CM} = V_{DD}/2, R_L = 100k\Omega$  to  $V_{DD}/2, T_A = +25^{\circ}C$ , unless otherwise noted.)

### **Pin Description**

| PIN     |         |         |                 | FUNCTION                                                              |  |

|---------|---------|---------|-----------------|-----------------------------------------------------------------------|--|

| MAX4490 | MAX4491 | MAX4492 | NAME            | FUNCTION                                                              |  |

| 1       | _       | _       | IN+             | Noninverting Input                                                    |  |

| 2       | 4       | 11      | V <sub>SS</sub> | Negative Supply Input. Connect to ground for single-supply operation. |  |

| 3       | _       | _       | IN-             | Inverting Input                                                       |  |

| 4       | _       | _       | OUT             | Amplifier Output                                                      |  |

| 5       | 8       | 4       | V <sub>DD</sub> | Positive Supply Input                                                 |  |

| _       | 3       | 3       | INA+            | Noninverting Input to Amplifier A                                     |  |

| _       | 2       | 2       | INA-            | Inverting Input to Amplifier A                                        |  |

| _       | 1       | 1       | OUTA            | Amplifier A Output                                                    |  |

| _       | 5       | 5       | INB+            | Noninverting Input to Amplifier B                                     |  |

| _       | 6       | 6       | INB-            | Inverting Input to Amplifier B                                        |  |

| _       | 7       | 7       | OUTB            | Amplifier B Output                                                    |  |

| _       | _       | 10, 12  | INC+, IND+      | Noninverting Inputs to Amplifiers C and D                             |  |

| _       | _       | 9, 13   | INC-, IND-      | Inverting Inputs to Amplifiers C and D                                |  |

| _       | _       | 8, 14   | OUTC, OUTD      | Amplifiers C and D Outputs                                            |  |

### **Detailed Description**

### Rail-to-Rail Input Stage

The MAX4490/MAX4491/MAX4492 CMOS operational amplifiers have parallel-connected N- and P-channel differential input stages that combine to accept a common-mode range extending to both supply rails. The N-channel stage is active for common-mode input voltages typically greater than (VSS + 1.2V), and the P-channel stage is active for common-mode input voltages typically less than (VDD - 1.2V).

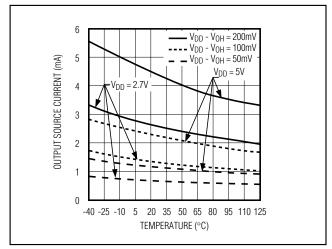

### Rail-to-Rail Output Stage

The MAX4490/MAX4491/MAX4492 CMOS operational amplifiers feature class-AB push-pull output stages that can drive a  $100k\Omega$  load to within 1.5mV of either supply rail. Short-circuit output current is typically  $\pm 50mA$ .

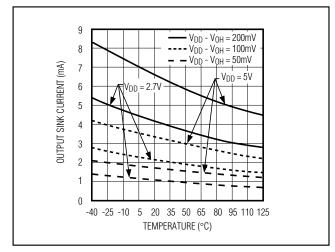

Figures 1a and 1b show the typical temperature dependence of output source and sink currents, respectively, for three fixed values of (VDD - VOH) and (VOL - VSS). For example, at VDD = 5.0V, the load currents that maintain (VDD - VOH) = 100mV and (VOL - VSS) = 100mV at  $T_A = +25^{\circ}C$  are 2.2mA and 3.3mA, respectively, when

the load is connected to V<sub>DD</sub>/2. Consistent resistive-drive capability is (2.5 - 0.1) / 2.2 = 1.1k $\Omega$ . For the same application, resistive-drive capability is 2.2k $\Omega$  when the load is connected to V<sub>DD</sub> or V<sub>SS</sub>.

### Applications Information

### **Power-Supply Considerations**

The MAX4490/MAX4491/MAX4492 operate from a single 2.7V to 5.5V supply or from dual ±1.35V to ±2.75V supplies with typically 800µA supply current per amplifier. A high power-supply rejection ratio of 100dB allows for extended operation from a decaying battery voltage, thereby simplifying designs for portable applications. For single-supply operation, bypass the power supply with a 0.1µF ceramic capacitor placed close to the VDD pin. For dual-supply operation, bypass each supply to ground.

### Input Capacitance

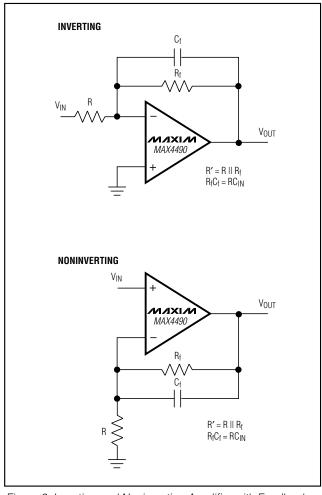

One consequence of the parallel-connected differential input stages for rail-to-rail operation is a relatively large input capacitance C<sub>IN</sub> (typically 5pF). This introduces a

pole at frequency  $(2\pi R'CIN)^{-1}$ , where R' is the parallel combination of the gain-setting resistors for the inverting or noninverting amplifier configuration (Figure 2). If the pole frequency is less than or comparable to the unity-gain bandwidth (10MHz), the phase margin will be reduced, and the amplifier will exhibit degraded AC performance through either ringing in the step response or sustained oscillations. The pole frequency is 10MHz when R' =  $3.2k\Omega$ . To maximize stability, R' <3k $\Omega$  is recommended.

Applications that require rail-to-rail operation with minimal loading (for small  $V_{DD}$  -  $V_{OH}$  and  $V_{OL}$  -  $V_{SS}$ ) will typically require R' values >3k $\Omega$ . To improve step response under these conditions, connect a small

Figure 1a. Output Source Current vs. Temperature

Figure 1b. Output Sink Current vs. Temperature

capacitor  $C_f$  between the inverting input and output. Choose  $C_f$  as follows:

$$C_f = 5(R / R_f) [pf]$$

where R<sub>f</sub> is the feedback resistor and R is the gain-setting resistor (Figure 2).

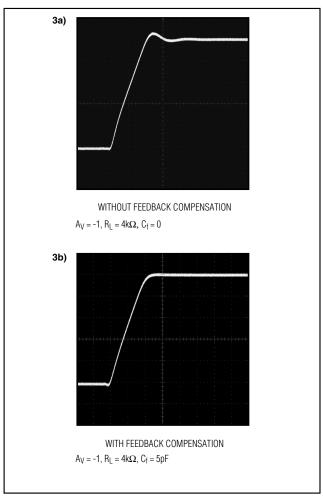

Figure 3 shows the step response for a noninverting amplifier subject to R' =  $4k\Omega$  with and without the Cf feedback capacitor.

Figure 2. Inverting and Noninverting Amplifier with Feedback Compensation

### **Driving Capacitive Loads**

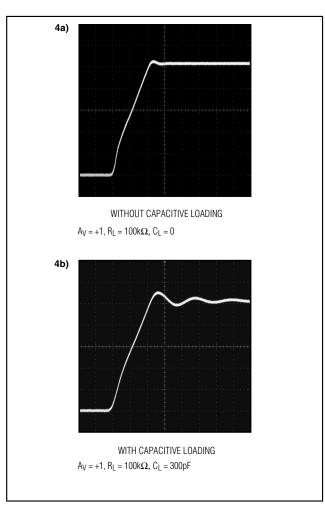

In conjunction with op amp output resistance, capacitive loads introduce a pole frequency that can reduce phase margin and lead to unstable operation. The MAX4490/MAX4491/MAX4492 drive capacitive loads up to 300pF without significant degradation of step response and slew rate (Figure 4). Capacitive-Load Stability (page 1) shows regions of stable and marginally stable (step overshoot <10%) operation for different combinations of capacitive and resistive loads.

Improve stability for large capacitive loads by adding an isolation resistor (typically  $10\Omega$ ) in series with the output (Figure 5). Note that the isolation resistor forms a voltage divider with potential for gain error.

### **Chip Information**

MAX4490 TRANSISTOR COUNT: 60 MAX4491 TRANSISTOR COUNT: 120 MAX4492 TRANSISTOR COUNT: 240 SUBSTRATE CONNECTED TO VSS

Figure 3. Step Response With and Without Feedback Compensation

Figure 4. Step Response With and Without Capacitive Loading

# V<sub>IN</sub> Rs V<sub>OUT</sub> MAX4490 CLOAD

Figure 5. Isolation Resistor for Large Capacitive Loads

## Pin Configurations/ Functional Diagrams (continued)

### Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

8 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600