# Low Power Multiclock Generator with VCXO

## AK8136A

### Features

- 27MHz Crystal Input

- One 27MHz-Reference Output

- 2 wire serial register interface

- Selectable Clock out Frequencies:

- 148.352, 148.5MHz

- 100.71, 108MHz

- 22.5792, 24.576, 33.8688, 36.864MHz

- 27.0MHz

- Built-in VCXO

- Pull Range:  $\pm 150$ ppm (typ.)

- Low Jitter Performance

- Period Jitter:

- 150 psec (Typ.) at CLK2,CLK3,CLK4

- TIE:

- 100 psec (Max) at CLK1p,CLK1n

- Long term jitter:

- 160 psec (Typ.) at REFOUT

- Low Current Consumption:

- 32 mA (Typ.) at 3.3V

- Supply Voltage:

- 3.0 – 3.6V

- Operating Temperature Range:

- 20 to +85°C

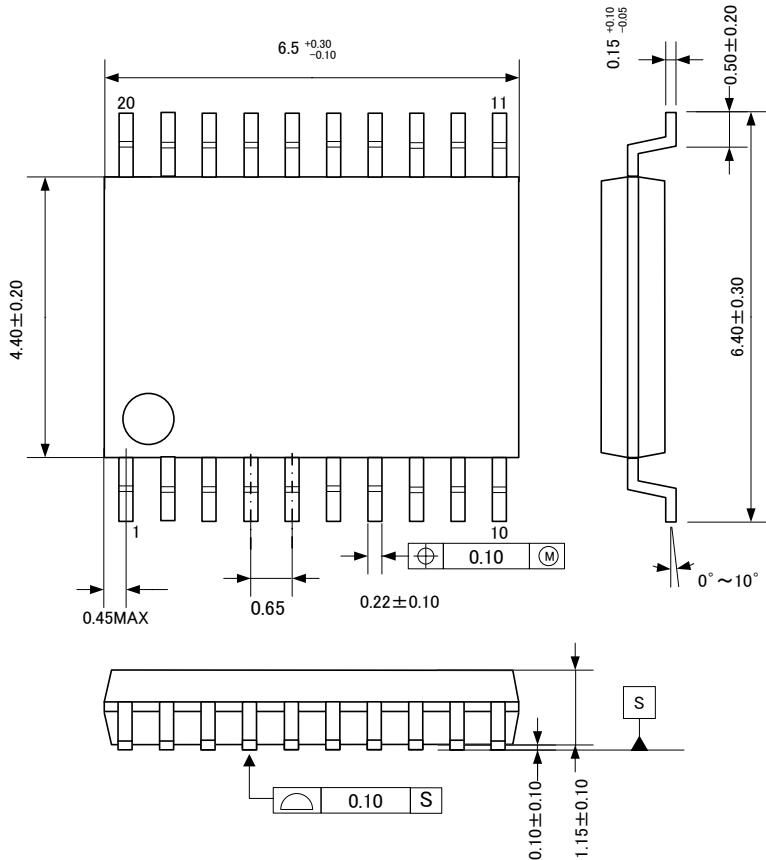

- Package:

- 20-pin SSOP (Lead free, Halogen free)

### Description

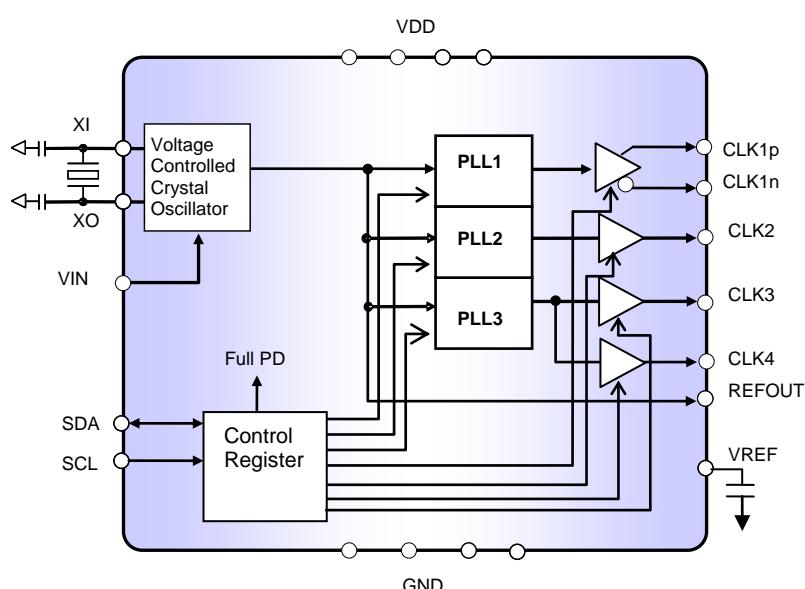

The AK8136A is a member of AKM's low power multi clock generator family designed for a feature rich DTV or STB, requiring a range of system clocks with high performance. The AK8136A generates different frequency clocks from a 27MHz crystal oscillator and provides them to up to four outputs configured by register-setting. The on-chip VCXO accepts a voltage control input to allow the output clocks to vary by  $\pm 150$  ppm for synchronizing to the external clock system. Both circuitries of VCXO and PLL in AK8136A are derived from AKM's long-term-experienced clock device technology, and enable clock output to perform low jitter and to operate with very low current consumption. The AK8136A is available in a 20-pin SSOP package.

### Applications

- Set-Top-Boxes

AK8136A Multi Clock Generator

## Pin Descriptions

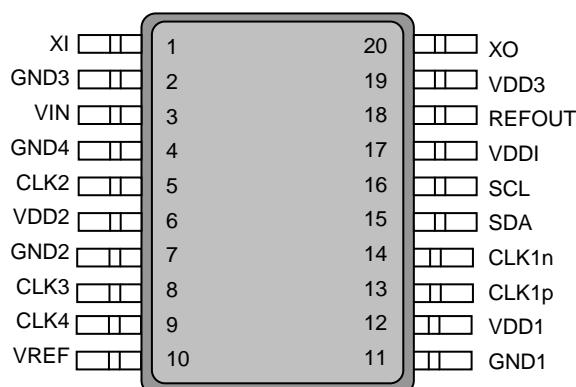

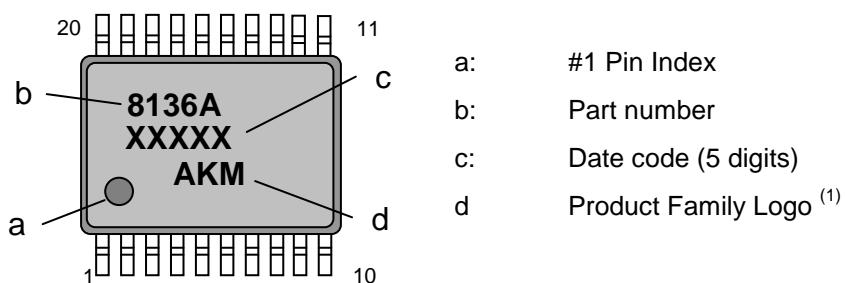

Package: 20-Pin SSOP(Top View)

| Pin No. | Pin Name | Pin Type | Description                                                                                                  |

|---------|----------|----------|--------------------------------------------------------------------------------------------------------------|

| 1       | XI       | AIN      | Crystal connection, Connect to 27.000MHz crystal                                                             |

| 2       | GND3     | PWR      | Ground 3                                                                                                     |

| 3       | VIN      | AIN      | VCXO Control Voltage Input                                                                                   |

| 4       | GND4     | PWR      | Ground 4                                                                                                     |

| 5       | CLK2     | DO       | Clock output 2, See register description.<br>In full power down or disable, this pin is "L".                 |

| 6       | VDD2     | PWR      | Power Supply 2                                                                                               |

| 7       | GND2     | PWR      | Ground 2                                                                                                     |

| 8       | CLK3     | DO       | Clock output 3, See register description<br>In full power down or disable, this pin is "L".                  |

| 9       | CLK4     | DO       | Clock output 4, Copy of CLK3 See register description<br>In full power down or disable, this pin is "L".     |

| 10      | VREF     | AO       | VREF Pin Connect 1uF capacitor.<br>Hi-Z in full power down state.                                            |

| 11      | GND1     | PWR      | Ground 1                                                                                                     |

| 12      | VDD1     | PWR      | Power Supply 1                                                                                               |

| 13      | CLK1p    | DO       | Clock output 1, these are differential pair. See register description                                        |

| 14      | CLK1n    | DO       | In full power down or disable, these pins are "L".                                                           |

| 15      | SDA      | DI/DO    | Serial data input and output pin. Open drain.                                                                |

| 16      | SCL      | DI       | Serial interface clock input.                                                                                |

| 17      | VDDI     | PWR      | Power supply for serial interface.<br>1.8V or 3.3V can be used.                                              |

| 18      | REFOUT   | DO       | Reference Clock Output of VCXO based on 27.000MHz Crystal<br>In full power down or disable, this pin is "L". |

| 19      | VDD3     | PWR      | Power Supply 3                                                                                               |

| 20      | XO       | AO       | Crystal connection, Connect to 27.000MHz crystal                                                             |

## Ordering Information

| Part Number | Marking | Shipping Packaging | Package     | Temperature Range |

|-------------|---------|--------------------|-------------|-------------------|

| AK8136A     | 8136A   | Tape and Reel      | 20-pin SSOP | -20 to 85°C       |

## Absolute Maximum Rating

Over operating free-air temperature range unless otherwise noted <sup>(1)</sup>

| Items                                    | Symbol           | Ratings            | Unit |

|------------------------------------------|------------------|--------------------|------|

| Supply voltage                           | VDD/VDD1         | -0.3 to 4.6        | V    |

| Input voltage                            | Vin              | VSS-0.3 to VDD+0.3 | V    |

| Input current (any pins except supplies) | I <sub>IN</sub>  | ±10                | mA   |

| Storage temperature                      | T <sub>STG</sub> | -55 to 130         | °C   |

Note

(1) Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rating conditions for extended periods may affect device reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

## ESD Sensitive Device

This device is manufactured on a CMOS process, therefore, generically susceptible to damage by excessive static voltage. Failure to observe proper handling and installation procedures can cause damage. AKM recommends that this device is handled with appropriate precautions.

## Recommended Operation Conditions

| Parameter                       | Symbol         | Conditions                       | Min | Typ | Max | Unit |

|---------------------------------|----------------|----------------------------------|-----|-----|-----|------|

| Operating temperature           | T <sub>a</sub> |                                  | -20 |     | 85  | °C   |

| Supply voltage 1 <sup>(1)</sup> | VDD1           | Pin: VDD1                        | 1.7 |     | 3.6 | V    |

| Supply voltage 2 <sup>(2)</sup> | VDD            | Pin: VDD1,VDD2,VDD3              | 3.0 | 3.3 | 3.6 | V    |

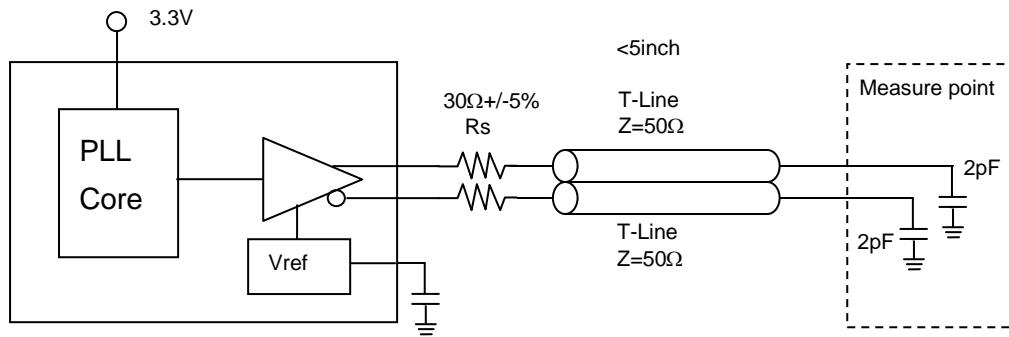

| Output Load Condition           | CL1            | Pin: CLK1p,CLK1n<br>See Figure 1 |     |     |     |      |

| Output Load Capacitance         | Cp1            | Pin: CLK2,CLK3,CLK4              |     |     | 15  | pF   |

|                                 | Cp2            | Pin: REFOUT                      |     |     | 25  | pF   |

Note:

(1) A decoupling capacitor for power supply line should be installed close to VDD1 pin.

(2) Power to VDD1, VDD2, VDD3 requires to be supplied from a single source. A decoupling capacitor for power supply line should be installed close to each VDD pin.

## DC Characteristics

VDD: over 3.0 to 3.6V, VDDI: over 1.7 to 3.6V, Ta: -20 to +85°C, 27MHz Crystal, unless otherwise noted

| Parameter                 | Symbol     | Conditions                                                             | MIN     | TYP | MAX     | Unit     |

|---------------------------|------------|------------------------------------------------------------------------|---------|-----|---------|----------|

| High Level Input Voltage  | $V_{IH}$   | Pin: SDA,SCL                                                           | 0.7VDDI |     |         | V        |

| Low Level Input Voltage   | $V_{IL}$   | Pin: SDA,SCL                                                           |         |     | 0.3VDDI | V        |

| Input Current 1           | $I_{L1}$   | Pin: SDA,SCL                                                           | -10     |     | +10     | $\mu A$  |

| Input Current 2           | $I_{L2}$   | Pin: VIN                                                               | -3      |     | +3      | $\mu A$  |

| High Level Output Voltage | $V_{OH}$   | Pin: CLK2-4, REFOUT<br>$I_{OH}=-4mA$                                   | 0.8VDD  |     |         | V        |

| Low level Output Voltage  | $V_{OL}$   | Pin: CLK2-4, REFOUT<br>$I_{OL}=+4mA$                                   |         |     | 0.2VDD  | V        |

| Output impedance          |            | Pin:CLK1p,CLK1n<br>Ta=25°C,3.3V                                        | 14      | 20  | 26      | $\Omega$ |

| VREF Voltage              | $V_{REF}$  | Pin:VREF<br>$C_{vref}=1\mu F$                                          | 0.72    | 0.8 | 0.88    | V        |

| Current Consumption 1     | $I_{DD1}$  | No load<br>Clock out selection by note(1)<br>VDD/VDDI=3.3V, Ta=25°C    |         | 32  |         | mA       |

| Current Consumption 2     | $I_{DD2}$  | On load(2)<br>Clock out selection by note(1)<br>VDD/VDDI=3.3V, Ta=25°C |         | 46  |         | mA       |

| Current Consumption 3     | $I_{DDPD}$ | <b>FULL_PD="H"</b><br>VDD/VDDI=3.3V, Ta=25°C                           |         | 0   | 150     | $\mu A$  |

(1) CLK1p/1n:148.5MHz, CLK2=108MHz,CLK3/4=36.864MHz,REFOUT=27.0MHz

(2) CLK1p/1n: Figure1, CLK2-4: Cp1=15pF, REFOUT:Cp2=25pF

## AC Characteristics (Clock signals)

VDD: over 3.0 to 3.6V, VDDI over 1.7 to 3.6V, Ta: over -20 to +85°C, 27MHz Crystal, unless otherwise noted

| Parameter                                 | Symbol              | Conditions                                                    | MIN  | TYP                  | MAX  | Unit  |

|-------------------------------------------|---------------------|---------------------------------------------------------------|------|----------------------|------|-------|

| Crystal Clock Frequency                   | $F_{osc}$           | Pin:XI,XO                                                     |      | 27.0000              |      | MHz   |

| Output Clock Accuracy                     | $F_{accuracy}$      | Pin:CLK2 100.71MHz<br>Relative to 27.0MHz                     |      | 106.25               |      | ppm   |

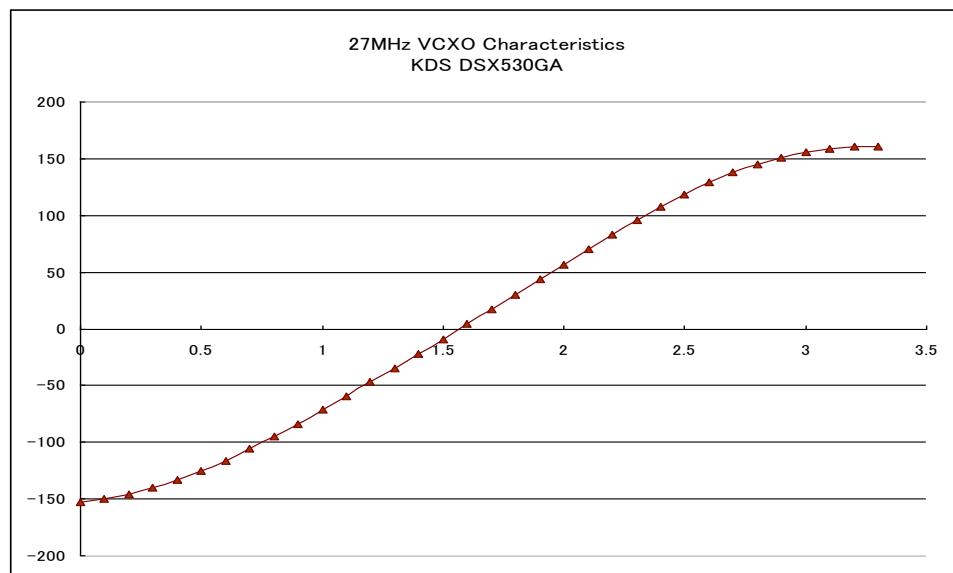

| VCXO Pullable Range <sup>(1)</sup>        | $PR_{vcxo}$         | VIN at over 0 to VDD V                                        |      | $\pm 150$            |      | ppm   |

| VCXO Gain                                 | $G_{vcxo}$          | VIN range at 1.5V $\pm 1.0$ V                                 |      | 150                  |      | ppm/V |

| Period Jitter <sup>(5)</sup>              | $Jit_{period}$      | Pin:REFOUT <sup>(2)</sup> ,CLK2-4 <sup>(3)</sup>              |      | 150<br>(6 $\sigma$ ) |      | ps    |

| Time Interval Error <sup>(6)</sup>        | $Jit_{tie}$         | Pin:CLK1 <sup>(4)</sup>                                       |      |                      | 100  | ps    |

| Long Term Jitter <sup>(7)</sup>           | $Jit_{long}$        | Pin:REFOUT<br>1000 cycle delay                                |      | 160                  |      | ps    |

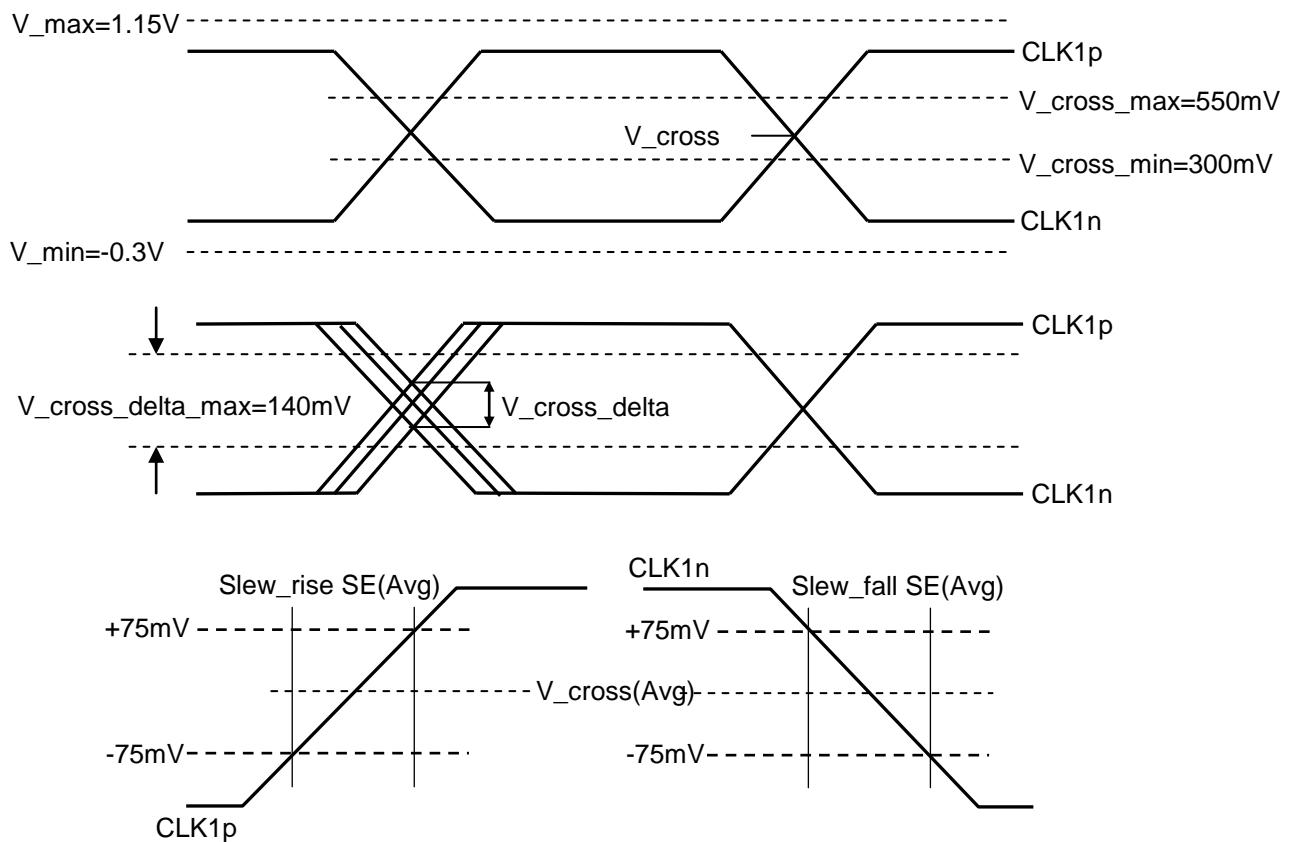

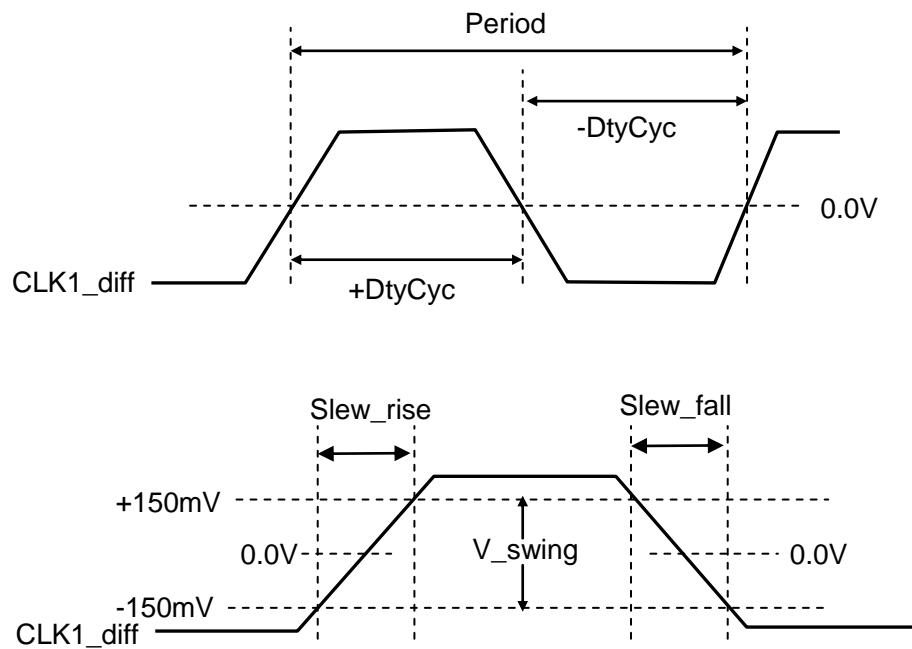

| Output Clock Duty Cycle                   | DtyCyc              | Pin: CLK1p,n <sup>(4)</sup> Figure.3<br>CLK2-4 <sup>(3)</sup> | 45   | 50                   | 55   | %     |

|                                           |                     | Pin: REFOUT <sup>(2)</sup>                                    | 40   | 50                   | 60   | %     |

| Output Clock Slew Rate                    | $Slew_{rise\_fall}$ | Pin:CLK1p,n <sup>(4)</sup> Figure.3                           | 2.5  |                      | 8.0  | V/ns  |

| Slew rate matching                        | $Slew_{ver}$        | Pin:CLK1p,n <sup>(4)</sup> Figure.2                           |      |                      | 20   | %     |

| Differential output swing                 | $V_{swing}$         | Pin:CLK1p,n <sup>(4)</sup> Figure.3                           | 300  |                      |      | mV    |

| Crossing point voltage                    | $V_{cross}$         | Pin:CLK1p,n <sup>(4)</sup> Figure.2                           | 300  |                      | 550  | mV    |

| Variation of Vcrs                         | $V_{cross\_delta}$  | Pin:CLK1p,n <sup>(4)</sup> Figure.2                           |      |                      | 140  | mV    |

| Maximum output voltage                    | $V_{max}$           | Pin:CLK1p,n <sup>(4)</sup> Figure.2                           |      |                      | 1.15 | V     |

| Minimum output voltage                    | $V_{min}$           | Pin:CLK1p,n <sup>(4)</sup> Figure.2                           | -0.3 |                      |      | V     |

| Output Clock Rise Time                    | $T_{rise}$          | Pin: CLK2-4 <sup>(3)</sup>                                    |      | 1.0                  | 3.0  | ns    |

|                                           |                     | Pin: REFOUT <sup>(2)</sup>                                    |      | 2.5                  | 5.0  | ns    |

| Output Clock Fall Time                    | $T_{fall}$          | Pin: CLK2-4 <sup>(3)</sup>                                    |      | 1.0                  | 3.0  | ns    |

|                                           |                     | Pin: REFOUT <sup>(2)</sup>                                    |      | 2.5                  | 5.0  | ns    |

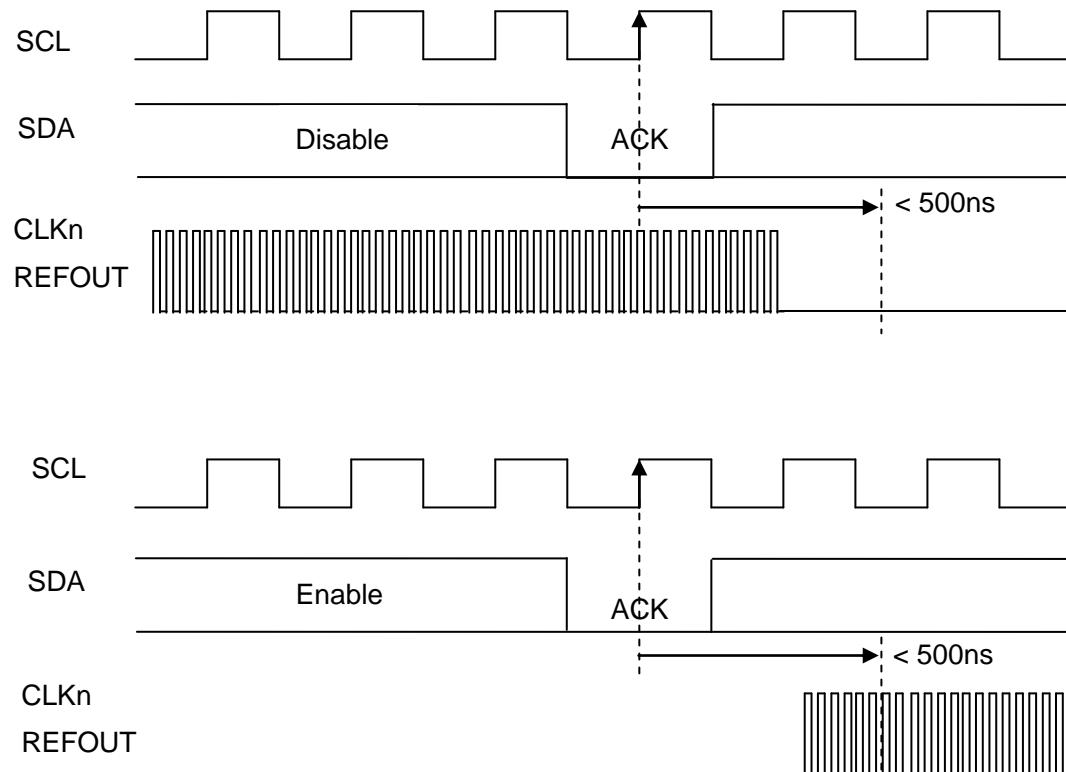

| Output enable/disable Time <sup>(8)</sup> | $T_{en\_dis}$       | Pin: REFOUT,CLK1p,n<br>CLK2-4                                 |      |                      | 500  | ns    |

| Power-up Time 1 <sup>(9)</sup>            | $T_{put1}$          | Pin: REFOUT,CLK1p,n<br>CLK2-4                                 |      |                      | 4    | ms    |

| Power-up Time 2 <sup>(10)</sup>           | $T_{put2}$          | Pin: REFOUT,CLK1p,n<br>CLK2-4                                 |      |                      | 150  | ms    |

(1) Pullable range depends on crystal characteristics, on-chip load capacitance, and stray capacity of PCB.

Typ.  $\pm 150$ ppm is applied to AKM's authorized test condition.

Please contact us when you plan the use of other crystal unit.

(2) Measured with load capacitance of 25pF

(3) Measured with load capacitance of 15pF

(4) Measured with load condition shown in Figure.1

(5)  $\pm 3\sigma$  in 10000 sampling or more

(6) 16ms accumulate with higher than 10GSa/s.

(7)  $\pm 3\sigma$  in 10000 sampling or more

(8) Refer to Figure.7 on Clock enable and disable sequence.

(9) Time to settle output into 0.1% of specified frequency from **FULL\_PD** is "L". Refer to Figure.6 on "Full Power Down sequence".

(10) Refer to Figure.5 on "Power on Reset sequence".

Figure.1 CLK1 Load condition

Figure.2 Single ended (SE) measurement waveforms

**Figure.3 Differential (DIFF) measurement waveforms**

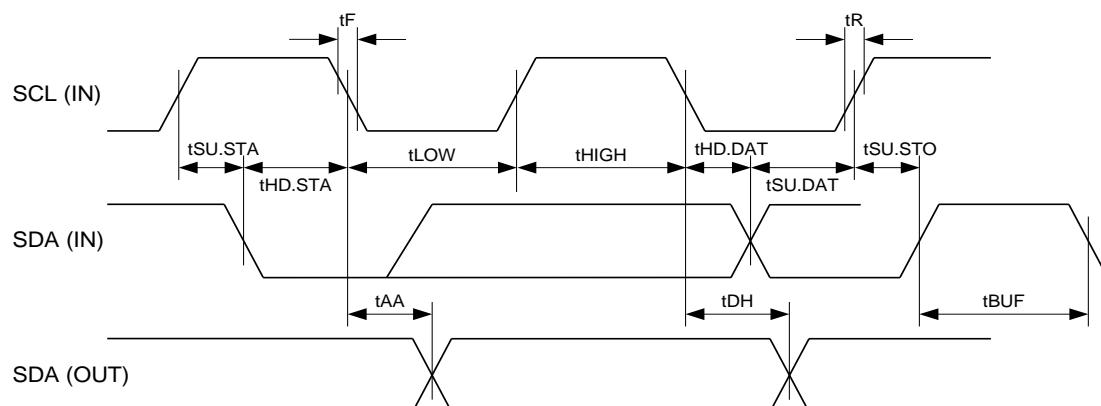

### AC Characteristics (Serial interface)

VDD: over 3.0 to 3.6V, VDDI over 1.7 to 3.6V, Ta: over -20 to +85°C, 27MHz Crystal, unless otherwise noted

| Parameter                                                   | Symbol         | Conditions | MIN | MAX | Unit |

|-------------------------------------------------------------|----------------|------------|-----|-----|------|

| SCL clock frequency                                         | fSCL           |            |     | 400 | kHz  |

| SCL Clock Low Period                                        | tLOW           |            | 1.3 |     | μs   |

| SCL Clock High Period                                       | tHIGH          |            | 0.6 |     | μs   |

| Pulse width of spikes which must be suppressed              | tl             |            |     | 50  | ns   |

| SLC Low to SDA Data Out                                     | tAA            |            | 0.3 |     | μs   |

| Bus free time between a STOP and START condition            | tBUF           |            | 1.3 |     | μs   |

| Start Condition Hold Time                                   | tHD.STA        |            | 0.6 |     | μs   |

| Start Condition Setup Time (for a Repeated Start condition) | tSU.STA        |            | 0.6 |     | ms   |

| Data in Hold Time                                           | tHD.DAT        |            | 0   |     | s    |

| Data in Setup Time                                          | tSU.DAT        |            | 100 |     | ns   |

| SDA and SCL Rise Time                                       | tR             |            |     | 0.3 | μs   |

| SDA and SCL Fall Time                                       | tF             |            |     | 0.3 | μs   |

| Stop Condition Setup Time                                   | tSU.STO        |            | 0.6 |     | μs   |

| Bus Line Load                                               | C <sub>b</sub> |            |     | 200 | pF   |

Figure.4 Serial Interface Timing

## Function Description

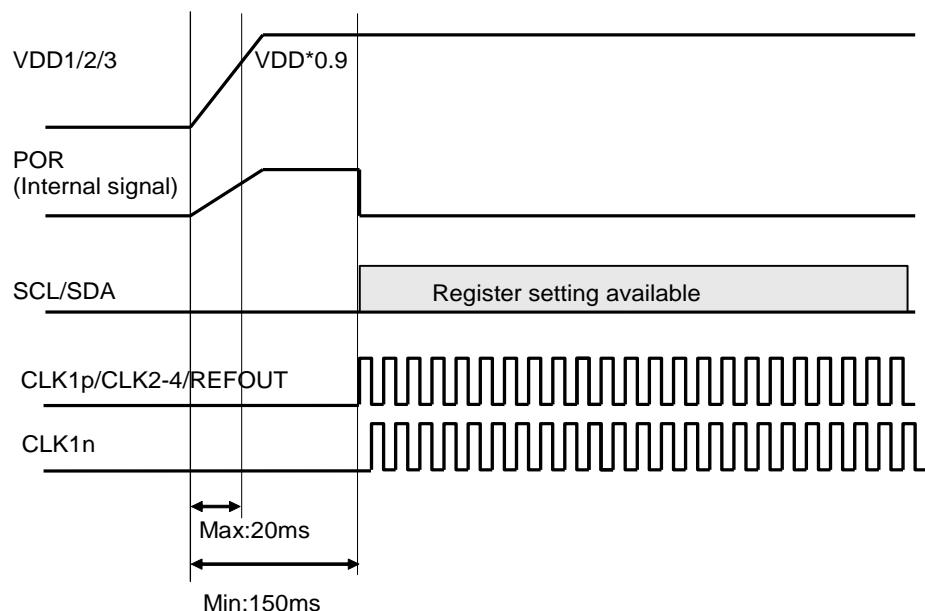

### Power On Reset sequence

AK8136A has the POR(Power On Reset) circuit. In power up, the POR works and the register is set to the initial value and all clock output becomes enable without glitch.

Note1) The assumption power start time to reach 90 % of VDD is within 20 ms.

Note2) The first register setting should be done after the 150 ms elapse after the power on.

Figure.5 Recommend Power Up Sequence

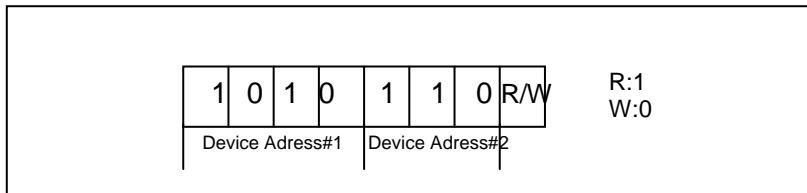

## Serial interface

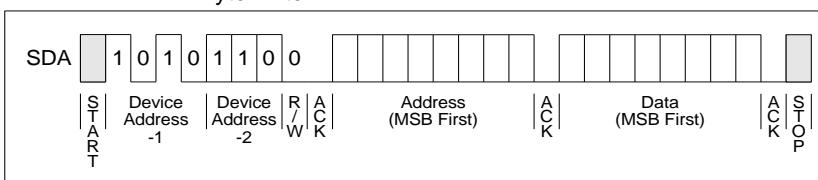

Read/Write performance of serial interface is expressed below. The device address #1 of AK8136A is fixed as "1010". The device address #2 is "110".

Device address of AK8136A

### Byte write operation

Byte write operation is described below. Data must be sent after sending 8 bits address and receiving ACK.

Byte write

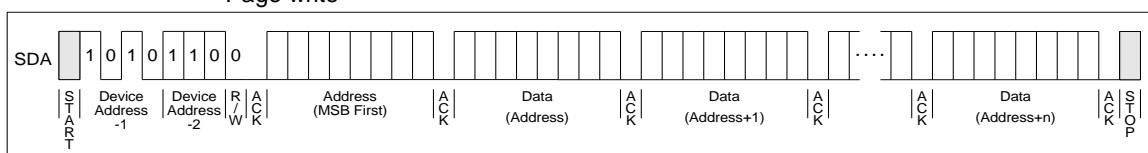

### Page write operation

Page write operation is described below. Only lower 4 bits of address are valid. Upper 4 bits are fixed as "1111". Therefore the address which is written after "1111 1111" becomes "1111 1110".

Page write

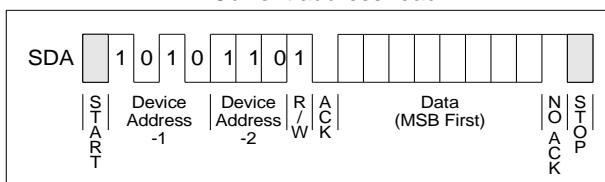

### Current address read

Current address read operation is described below. The data that is read by this operation is obtained as "last accessed address + 1". Therefore, It is consequent to return "1111 1110" after accessing the address "1111 1111".

Current address read

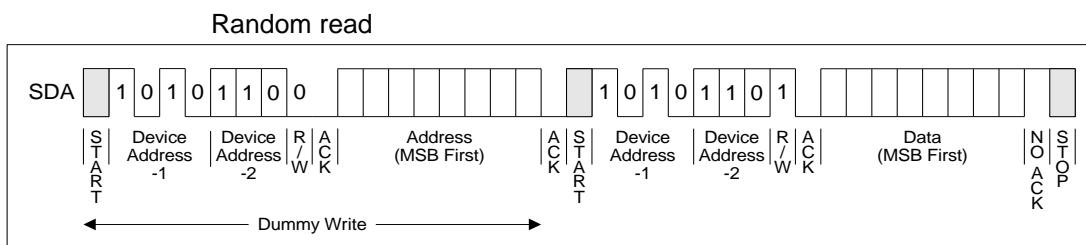

### Random read

Random read operation is described below. It is necessary to operate “dummy write” before sending read command. Dummy write is to send the address to read.

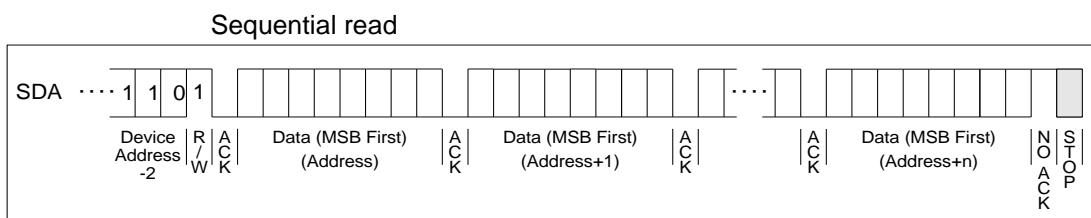

### Sequential read

Sequential read operation is described below. It is possible to read next address sequentially by sending ACK instead of stop condition.

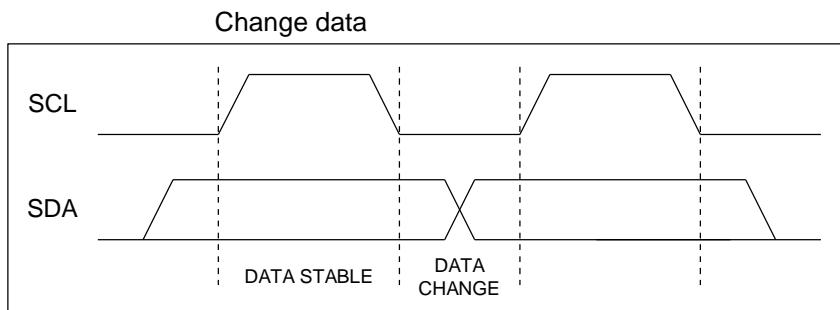

### Change data

Change data operation is described below. It is available when SCL is Low.

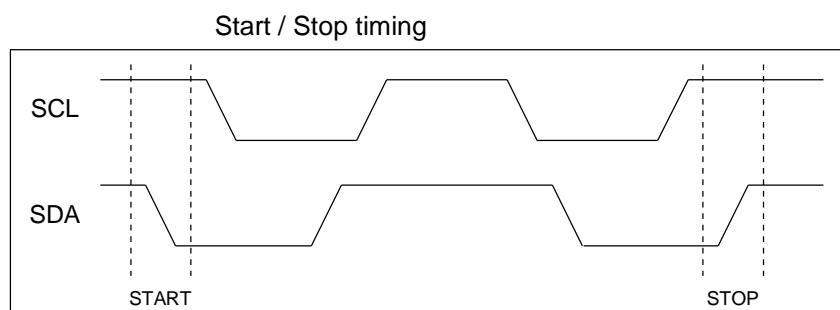

### Start / Stop timing

Start / Stop timing is described below. The sequence is started when SDA goes from high to low during SCL is high. The sequence is stopped when SDA goes from low to high during SCL is high.

## Register description

The AK8136A generates a range of low-jitter and hi-accuracy clock frequencies with three built-in PLLs and provides up to five assigned outputs. A frequency selection at assigned output pin and power down control is configured by register-setting.

## Register Map

| Address | D7              | D6              | D5              | D4              | D3              | D2              | D1           | D0           | Note    |

|---------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------|--------------|---------|

| FF      | <b>FULL_PD</b>  | -               | -               | -               | <i>CLK3S[1]</i> | <i>CLK3S[0]</i> | <i>CLK2S</i> | <i>CLK1S</i> |         |

|         | 0               | -               | -               | -               | 1               | 1               | 0            | 0            | Default |

| FE      | <i>CLK4_DIS</i> | <i>CLK3_DIS</i> | <i>CLK2_DIS</i> | <i>CLK1_DIS</i> | <i>REF_DIS</i>  |                 |              |              |         |

|         | 0               | 0               | 0               | 0               | 0               |                 |              |              | Default |

## Register definition

**FULL\_PD** (Address FF:D7)

| Power Down Control |                                                      |           |

|--------------------|------------------------------------------------------|-----------|

| 0                  | Device Active (PLL ON)<br>Enable VCXO, VREF and PLLs | (default) |

| 1                  | Full Power Down<br>Disable VCXO, VREF and PLLs       |           |

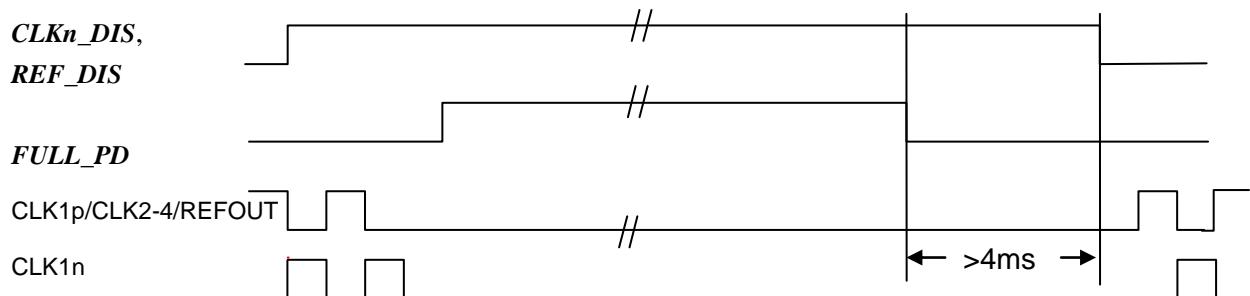

### Full Power Down sequence

The full power down setting is done by following sequence.

- 1) Change **CLKn\_DIS**(n=1,2,3,4) and **REF\_DIS** to "1".

- 2) Change **FULL\_PD** to "1" from "0".

The output transfers to the disabled state without glitch.

The full power down state is released by following sequence.

- 1) Changing **FULL\_PD** to "0" from "1".

- 2) After more than 4 ms elapse, change **CLKn\_DIS** and **REF\_DIS** "0" to "1".

The output transfers to the enable state without glitch.

Figure.6 Full Down sequence

**CLK3S[1:0]** (Address FF:D3,D2)

CLK3&4 Output frequency selection

|    |                     |

|----|---------------------|

| 00 | 22.5792MHz          |

| 01 | 24.576MHz           |

| 10 | 33.8688MHz          |

| 11 | 36.864MHz (default) |

**CLK2S** (Address FF:D1)

CLK2 Output frequency selection

|   |                   |

|---|-------------------|

| 0 | 108MHz. (default) |

| 1 | 100.71MHz         |

**CLK1S** (Address FF:D0)

CLK1 Output frequency selection

|   |                          |

|---|--------------------------|

| 0 | 148.5MHz/1.001 (default) |

| 1 | 148.5MHz                 |

**CLK4\_DIS** (Address FE:D7)

CLK4 Output Disable

|   |                                |

|---|--------------------------------|

| 0 | Enable (CLK4 Active) (default) |

| 1 | Disable(CLK4="L")              |

**CLK3\_DIS** (Address FE:D6)

CLK3 Output Disable

|   |                                |

|---|--------------------------------|

| 0 | Enable (CLK3 Active) (default) |

| 1 | Disable(CLK3="L")              |

**CLK2\_DIS** (Address FE:D5)

CLK2 Output Disable

|   |                                |

|---|--------------------------------|

| 0 | Enable (CLK2 Active) (default) |

| 1 | Disable(CLK2="L")              |

**CLK1\_DIS** (Address FE:D4)

CLK1 Output Disable

|   |                                |

|---|--------------------------------|

| 0 | Enable (CLK1 Active) (default) |

| 1 | Disable(CLK1p,CLK1n="L")       |

**REF\_DIS** (Address FE:D3)

## REFOUT Output Disable

|   |                                  |

|---|----------------------------------|

| 0 | Enable (REFOUT Active) (default) |

| 1 | Disable(REFOUT="L")              |

**Clock Enable and Disable sequence**

The enabling and disabling of the clock output are executed without glitch within 500 ns from the rising edge of SCL during the acknowledge operation after the corresponding byte data reception.

**Figure.7 Output Enable and Disable sequence**

## Voltage Controlled Crystal Oscillator (VCXO)

The AK8136A has a voltage controlled crystal oscillator (VCXO), featuring fine frequency tuning for 27MHz of primary clock frequency by external DC voltage control. This tuning enables output clock frequency to synchronize the external clock system. VIN (Pin3) accepts DC voltage control from a processor or a system controller, and pulls the primary frequency of crystal to higher or lower. This pulling range is determined by crystal characteristic, on-chip load capacitor, and stray capacitance of PCB. The AK8136A is designed to range  $\pm 150$ ppm of primary frequency in AKM's authorized condition, and the typical pulling profile is shown in **Figure 8**. For details about the condition and other specific crystal application case, refer the AK8136A application note.

**Figure 8: Typical VCXO Pulling Profile**

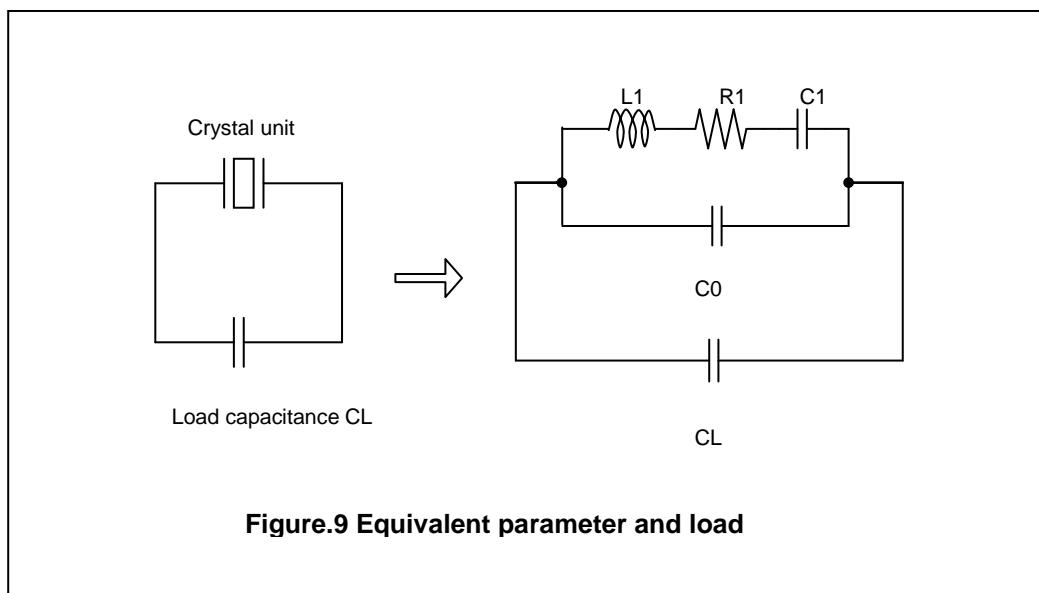

## KDS DSX530GA

| Item                  |    | MIN | TYP    | MAX | Unit     | Remark    |

|-----------------------|----|-----|--------|-----|----------|-----------|

| Nominal frequency     | f0 |     | 27.000 |     | MHz      | CL=10.0pF |

| Equivalent resistance | R1 |     |        | 50  | $\Omega$ |           |

| Shunt capacitance     | C0 |     | 3.0    |     | pF       |           |

| Motional capacitance  | C1 |     | 11.4   |     | fF       |           |

| Motional inductance   | L1 |     | 3.0    |     | mH       |           |

| Drive Level           |    |     | 10     | 300 | uW       |           |

Spurious • No spurious within  $3f_0 \pm 13\text{kHz}$

- Within  $f_0 \pm 500\text{kHz}$  the attenuation of the spurious response should be more than 3dB.

Figure.9 Equivalent parameter and load

## Package Information

### • Marking

### • RoHS Compliance

All integrated circuits from Asahi Kasei Microdevices Corporation (AKM) assembled in "lead-free" packages\* are fully compliant with RoHS.

(\* ) RoHS compliant products from AKM are identified with "Pb free" letter indication on product label posted on the anti-shield bag and boxes.

## IMPORTANT NOTICE

0. Asahi Kasei Microdevices Corporation ("AKM") reserves the right to make changes to the information contained in this document without notice. When you consider any use or application of AKM product stipulated in this document ("Product"), please make inquiries the sales office of AKM or authorized distributors as to current status of the Products.

1. All information included in this document are provided only to illustrate the operation and application examples of AKM Products. AKM neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of AKM or any third party with respect to the information in this document. You are fully responsible for use of such information contained in this document in your product design or applications. **AKM ASSUMES NO LIABILITY FOR ANY LOSSES INCURRED BY YOU OR THIRD PARTIES ARISING FROM THE USE OF SUCH INFORMATION IN YOUR PRODUCT DESIGN OR APPLICATIONS.**

2. The Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact, including but not limited to, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for the above use unless specifically agreed by AKM in writing.

3. Though AKM works continually to improve the Product's quality and reliability, you are responsible for complying with safety standards and for providing adequate designs and safeguards for your hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of the Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption.

4. Do not use or otherwise make available the Product or related technology or any information contained in this document for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). When exporting the Products or related technology or any information contained in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. The Products and related technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

5. Please contact AKM sales representative for details as to environmental matters such as the RoHS compatibility of the Product. Please use the Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. AKM assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.

6. Resale of the Product with provisions different from the statement and/or technical features set forth in this document shall immediately void any warranty granted by AKM for the Product and shall not create or extend in any manner whatsoever, any liability of AKM.

7. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of AKM.