# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

### **General Description**

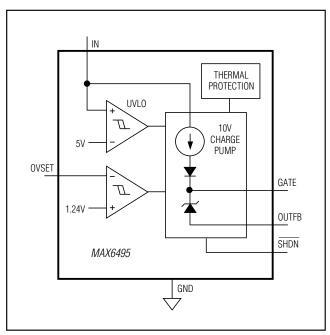

The MAX6495–MAX6499 is a family of small, low-current, overvoltage-protection circuits for high-voltage transient systems such as those found in automotive and industrial applications. These devices monitor the input voltage and control an external n-channel MOSFET switch to isolate the load at the output during an input overvoltage condition. The MAX6495–MAX6499 operate over a wide supply voltage range from +5.5V to +72V.

The gate of the n-channel MOSFET is driven high while the monitored input is below the user-adjustable overvoltage threshold. An integrated charge-pump circuit provides a 10V gate-to-source voltage to fully enhance the n-channel MOSFET. When the input voltage exceeds the user-adjusted overvoltage threshold, the gate of the MOSFET is quickly pulled low, disconnecting the load from the input. In some applications, disconnecting the output from the load is not desirable. In these cases, the protection circuit can be configured to act as a voltage limiter where the GATE output sawtooths to limit the voltage to the load (MAX6495/MAX6496).

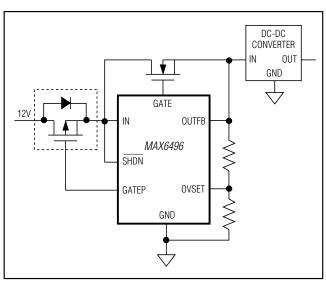

The MAX6496 supports lower input voltages and reduces power loss by replacing the external reverse battery diode with an external series p-channel MOSFET. The MAX6496 generates the proper bias voltage to ensure that the p-channel MOSFET is on during normal operations. The gate-to-source voltage is clamped during load-dump conditions, and the p-channel MOSFET is off during reverse-battery conditions.

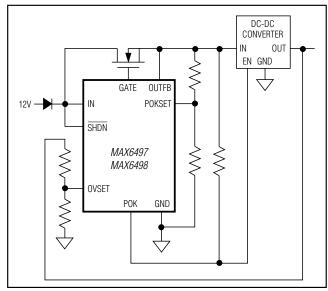

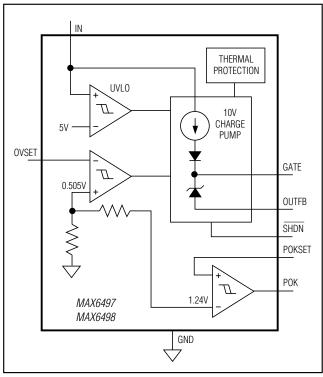

The MAX6497/MAX6498 feature an open-drain, undedicated comparator that notifies the system if the output falls below the programmed threshold. The MAX6497 keeps the MOSFET switch latched off until either the input power or the  $\overline{SHDN}$  pin is cycled. The MAX6498 will autoretry when  $V_{OVSET}$  falls below 130mV.

These devices are available in small, thermally enhanced, 6-pin and 8-pin TDFN packages and are fully specified from -40°C to +125°C.

#### **Applications**

Automotive

Industrial

Telecom/Servers/Networking

FireWire®

Notebook Computers

FireWire is a registered trademark of Apple, Inc.

#### **Features**

- ♦ Wide Supply Voltage Range: +5.5V to +72V

- ♦ Overvoltage-Protection Switch Controller Allows User to Size External n-Channel MOSFETs

- Fast Gate Shutoff During Overvoltage with 100mA Sink Capability

- ♦ Internal Charge-Pump Circuit Ensures 10V Gate-to-Source Enhancement for Low R<sub>DS(ON)</sub> Performance

- ♦ n-Channel MOSFET Latches Off After an Overvoltage Condition (MAX6497/MAX6499)

- ♦ Adjustable Overvoltage Threshold

- **♦ Thermal Shutdown Protection**

- ♦ Supports Series p-Channel MOSFET for Reverse-Battery Voltage Protection (MAX6496)

- **♦ POK Indicator (MAX6497/MAX6498)**

- **♦** Adjustable Undervoltage Threshold (MAX6499)

- ♦ -40°C to +125°C Operating Temperature Range

- ♦ Small, 3mm x 3mm TDFN Package

#### Ordering Information

| PART           | PIN-PACKAGE | TOP MARK |  |

|----------------|-------------|----------|--|

| MAX6495ATT+T   | 6 TDFN-EP*  | AJM      |  |

| MAX6495ATT/V+T | 6 TDFN-EP*  | AUG      |  |

#### Ordering Information continued at end of data sheet.

**Note:** All devices are specified over the -40°C to +125°C operating temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

\*EP = Exposed pad.

/V denotes an automotive qualified part.

Selector Guide appears at end of data sheet.

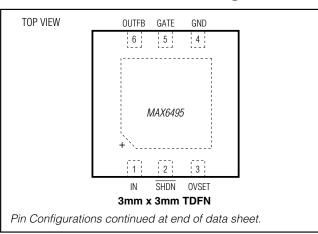

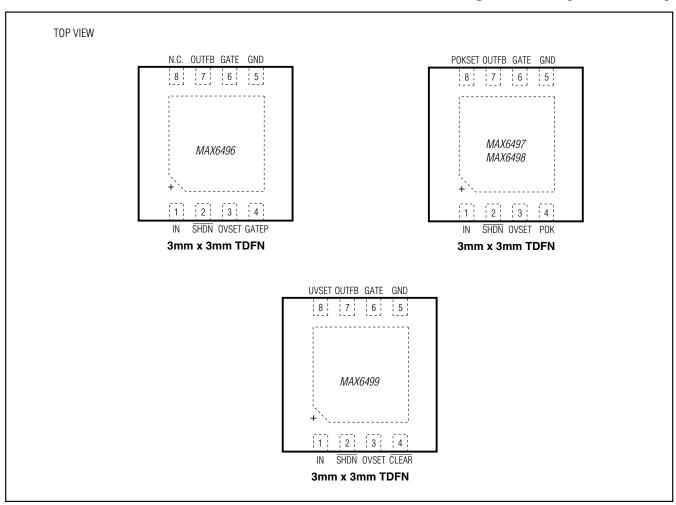

## Pin Configurations

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

#### **ABSOLUTE MAXIMUM RATINGS**

| (All pins referenced to GND.)  |                             |                                                      |                |

|--------------------------------|-----------------------------|------------------------------------------------------|----------------|

| IN, GATE, GATEP                | 0.3V to +80V                | Continuous Power Dissipation (T <sub>A</sub> = +70°C | C)             |

| SHDN, CLEAR                    | $0.3V$ to $(V_{IN} + 0.3V)$ | 6-Pin TDFN (derate 18.2mW/°C above +                 | ·70°C)1455mW   |

| POK, OUTFB                     | 0.3V to +80V                | 8-Pin TDFN (derate 18.2mW/°C above +                 | ·70°C)1455mW   |

| GATE to OUTFB                  | 0.3V to +12V                | Operating Temperature Range                          | 40°C to +125°C |

| GATEP to IN                    | 12V to +0.3V                | Junction Temperature                                 | +150°C         |

| OVSET, UVSET, POKSET           | 0.3V to +12V                | Storage Temperature Range                            | 60°C to +150°C |

| Current Sink/Source (All Pins) | 50mA                        | Lead Temperature (soldering, 10s)                    | +300°C         |

| All Other Pins to GND          | $0.3V$ to $(V_{IN} + 0.3V)$ | Soldering Temperature (reflow)                       | +260°C         |

|                                |                             |                                                      |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 14V, C_{GATE} = 6nF, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                            | SYMBOL            |                          | CONDITIONS                                              | MIN   | TYP  | MAX  | UNITS    |  |

|------------------------------------------------------|-------------------|--------------------------|---------------------------------------------------------|-------|------|------|----------|--|

| Supply Voltage Range                                 | VIN               |                          |                                                         | 5.5   |      | 72.0 | V        |  |

|                                                      |                   |                          | SHDN = high                                             |       | 100  | 150  |          |  |

| Input Supply Current                                 | I <sub>IN</sub>   | No load                  | SHDN = low (MAX6497/MAX6498/<br>MAX6499)                |       | 15   | 24   | μΑ       |  |

|                                                      |                   |                          | $\overline{\text{SHDN}} = \text{low (MAX6495/MAX6496)}$ |       | 24   | 32   |          |  |

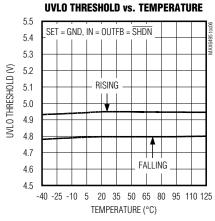

| IN Undervoltage Lockout                              |                   | V <sub>IN</sub> rising   | , enables GATE                                          | 4.75  | 5    | 5.25 | V        |  |

| IN Undervoltage Lockout<br>Hysteresis                |                   | V <sub>IN</sub> falling  | ı, disables GATE                                        |       | 155  |      | mV       |  |

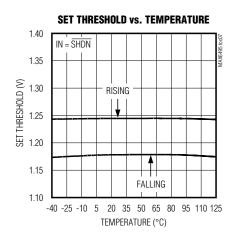

| OVSET Threshold Voltage                              | V <sub>TH+</sub>  | OVSET ris                | sing                                                    | 1.22  | 1.24 | 1.26 | V        |  |

| (MAX6495/MAX6496)                                    | V <sub>TH</sub> - | OVSET fa                 | lling                                                   |       | 1.18 |      | V        |  |

| OVSET Threshold Hysteresis (MAX6495/MAX6496)         | VHYST             | OVSET fa                 | lling                                                   |       | 5    |      | %        |  |

| OVSET Threshold Voltage                              | V <sub>TH+</sub>  | OVSET rising 0.494 0.505 |                                                         | 0.518 | V    |      |          |  |

| (MAX6497/MAX6498)                                    | V <sub>TH</sub> - | OVSET fa                 | lling                                                   |       | 0.13 |      |          |  |

| OVSET Threshold Voltage                              | V <sub>TH+</sub>  | OVSET rising             |                                                         | 1.22  | 1.24 | 1.26 | <u> </u> |  |

| (MAX6499)                                            | V <sub>TH</sub> - | OVSET fa                 | lling                                                   | 1.18  |      |      | v        |  |

| UVSET Threshold Voltage                              | V <sub>TH+</sub>  | UVSET rising             |                                                         | 1.22  | 1.24 | 1.26 | - v      |  |

| (MAX6499)                                            | V <sub>TH</sub> - | UVSET fa                 | lling                                                   | 1.18  |      |      | v        |  |

| OVSET/UVSET Threshold<br>Hysteresis (MAX6499)        | VHYST             | OVSET fa                 | OVSET falling                                           |       | 5    |      | %        |  |

| POKSET Threshold Voltage                             | VPOKSET+          | POKSET i                 | rising                                                  | 1.22  | 1.24 | 1.26 | V        |  |

| (MAX6497/MAX6498)                                    | VPOKSET-          | POKSET f                 | alling                                                  |       | 1.18 |      | V        |  |

| POKSET Threshold<br>Hysteresis (MAX6497/<br>MAX6498) | VHYST             | POKSET falling           |                                                         |       | 5    |      | %        |  |

| OVSET, UVSET, POKSET<br>Input Current                | I <sub>SET</sub>  |                          |                                                         | -50   |      | +50  | nA       |  |

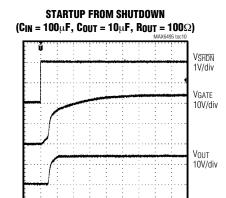

| Startup Response Time                                | tstart            | SHDN risi                | ng (Note 2)                                             |       | 100  |      | μs       |  |

| GATE Rise Time                                       |                   | GATE risii<br>OUTFB =    | ng from GND to V <sub>OUTFB</sub> + 8V,<br>GND          |       | 1    |      | ms       |  |

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 14V, C_{GATE} = 6nF, T_A = -40$ °C to +125°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 1)

| PARAMETER                                      | SYMBOL            | CONDITIONS                                                                    | MIN                   | TYP                   | MAX                   | UNITS |

|------------------------------------------------|-------------------|-------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-------|

| OVSET to GATE Propagation Delay                | tov               | SET rising from V <sub>TH</sub> - 100mV to V <sub>TH</sub> + 100mV            |                       |                       | 0.6                   | μs    |

| UVSET to GATE, POKSET to POK Propagation Delay |                   | POKSET, UVSET falling from V <sub>TH</sub> + 100mV to V <sub>TH</sub> - 100mV |                       | 20                    |                       | μs    |

| GATE Output High Voltage                       | Voн               | $V_{OUTFB} = V_{IN} = 5.5V$ , $R_{GATE}$ to $IN = 1M\Omega$                   | V <sub>IN</sub> + 3.4 | V <sub>IN</sub> + 3.8 | V <sub>IN</sub> + 4.2 | V     |

| CATE Output High Voltage                       | VOH               | $V_{OUTFB} = V_{IN}, V_{IN} \ge 14V, R_{GATE}$ to $IN = 1M\Omega$             | V <sub>IN</sub> + 8   | V <sub>IN</sub> + 10  | V <sub>IN</sub> + 11  | V     |

| GATE Output Low Voltage                        | V <sub>OL</sub>   | GATE sinking 15mA, OUTFB = GND                                                |                       |                       | 1                     | V     |

| CATE Output Low Voltage                        | VOL               | V <sub>IN</sub> = 5.5V, GATE sinking 1mA, OUTFB = GND                         |                       |                       | 0.9                   | V     |

| GATE Charge-Pump Current                       | IGATE             | GATE = GND                                                                    |                       | 100                   |                       | μΑ    |

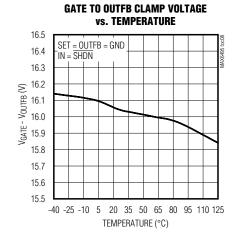

| GATE to OUTFB Clamp<br>Voltage                 | V <sub>CLMP</sub> |                                                                               | 12                    |                       | 18                    | V     |

| IN to GATEP Output Low Voltage                 |                   | IGATEP_SINK = 75μA, IGATEP_SOURCE = 1μA                                       | 7.5                   |                       | 11.7                  | ٧     |

| IN to GATEP Clamp Voltage                      |                   | V <sub>IN</sub> = 24V, I <sub>GATEP</sub> _SOURCE = 10µA                      | 12                    |                       | 18                    | V     |

| SHDN, CLEAR Logic-High<br>Input Voltage        | VIH               |                                                                               | 1.4                   |                       |                       | .,    |

| SHDN, CLEAR Logic-Low<br>Input Voltage         | VIL               |                                                                               |                       |                       | 0.4                   | V     |

| SHDN Input Pulse Width                         |                   |                                                                               | 7                     |                       |                       | μs    |

| CLEAR Input Pulse Width                        |                   |                                                                               |                       | 0.5                   |                       | μs    |

| SHDN, CLEAR Input<br>Pulldown Current          |                   | SHDN is Internally pulled down to GND                                         | 0.6                   | 1.0                   | 1.4                   | μΑ    |

| Thermal Shutdown                               |                   | (Note 3)                                                                      |                       | +160                  |                       | °C    |

| Thermal-Shutdown<br>Hysteresis                 |                   |                                                                               |                       | 20                    |                       | °C    |

| POKSET to POK Delay<br>(MAX6497/MAX6498)       |                   |                                                                               |                       | 35                    |                       | μs    |

| POK Output Low Voltage                         | Ma                | V <sub>IN</sub> ≥ 14V, POKSET = GND, I <sub>SINK</sub> = 3.2mA                |                       |                       | 0.4                   | .,    |

| (MAX6497/MAX6498)                              | V <sub>OL</sub>   | V <sub>IN</sub> ≥ 2.8V, POKSET = GND, I <sub>SINK</sub> = 100µA               |                       |                       | 0.4                   | V     |

| POK Leakage Current<br>(MAX6497/MAX6498)       |                   | VPOKSET = 14V                                                                 |                       |                       | 100                   | nA    |

**Note 1:** Specifications to  $T_A = -40^{\circ}C$  are guaranteed by design and not production tested.

Note 2: The MAX6495–MAX6499 power up with the external MOSFET in off mode (V<sub>GATE</sub> = GND). The external MOSFET turns on t<sub>START</sub> after all input conditions are valid.

Note 3: For accurate overtemperature-shutdown performance, place the device in close thermal contact with the external MOSFET.

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

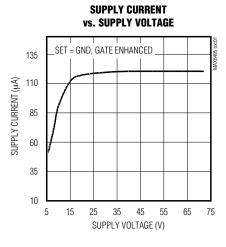

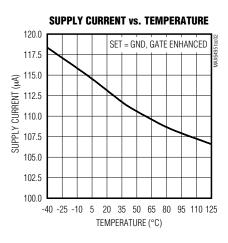

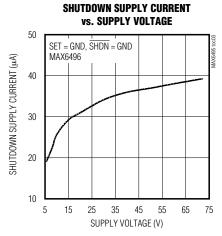

## **Typical Operating Characteristics**

$(V_{IN} = +12V, T_A = +25^{\circ}C, unless otherwise noted.)$

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

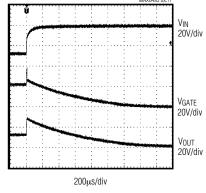

## Typical Operating Characteristics (continued)

$(V_{IN} = +12V, T_A = +25^{\circ}C, unless otherwise noted.)$

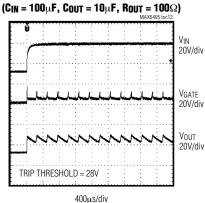

# **STARTUP WAVEFORM** (CIN = 100 $\mu$ F, COUT = 10 $\mu$ F, ROUT = 100 $\Omega$ ) 10V/div VGATE 10V/div

Vout 10V/div  $400\mu\text{s/div}$

## **OVERVOLTAGE LIMITER**

$400\mu\text{s/div}$

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

## **Pin Description**

|         | P       | IN              |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|---------|---------|-----------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX6495 | MAX6496 | MAX6497/MAX6498 | MAX6499 | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 1       | 1       | 1               | 1       | IN     | Positive Supply Voltage. Connect IN to the positive side of the input voltage. Bypass IN with a 10µF capacitor to GND.                                                                                                                                                                                                                                                                                                               |  |  |

| 2       | 2       | 2               | 2       | SHDN   | Shutdown Input. Drive \$\overline{SHDN}\$ low to force GATE low and turn off the external n-channel MOSFET. Drive \$\overline{SHDN}\$ low and then high to reset the overvoltage-condition latch. \$\overline{SHDN}\$ is internally pulled to GND with 1\(\mu\)A of current. Connect \$\overline{SHDN}\$ to IN for normal operation.                                                                                                 |  |  |

| 3       | 3       | 3               | 3       | OVSET  | Overvoltage-Threshold Adjustment Input. Connect OVSET to an external resistive voltage-divider network to adjust the desired overvoltage-disable or overvoltage-limit threshold. Connect the resistor network to the input side (drain) of the n-channel MOSFET for overvoltage switch turn-off applications or to the output side (source) of the n-channel MOSFET for overvoltage-limiting applications (MAX6495/MAX6496/MAX6499). |  |  |

| 4       | 5       | 5               | 5       | GND    | Ground                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 5       | 6       | 6               | 6       | GATE   | Gate-Driver Output. Connect GATE to the gate of the external n-channel MOSFET switch. GATE is the output of a charge pump with a 100µA pullup current to 10V (typ) above IN during normal operation. GATE is quickly clamped to OUTFB during an overvoltage condition. GATE pulls low when SHDN is low.                                                                                                                              |  |  |

| 6       | 7       | 7               | 7       | OUTFB  | Output-Voltage-Sense Input. Connect OUTFB to the source of the external n-channel MOSFET switch.                                                                                                                                                                                                                                                                                                                                     |  |  |

| _       | 4       | _               | _       | GATEP  | p-Channel Gate-Driver Output. Connect GATEP to the gate of an external p-channel MOSFET to provide low-drop reverse-voltage protection. GATEP is biased to ensure that the p-channel MOSFET is on during normal operating modes, the gate-to-source is not overstressed during load-dump/overvoltage conditions, and the p-channel MOSFET is off during reverse-battery conditions.                                                  |  |  |

| _       | 8       | _               | _       | N.C.   | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| _       | _       | 4               | _       | POK    | Power-OK Output. POK is an open-drain output. POK remains low while POKSET is below the internal POKSET threshold. POK goes high impedance when POKSET goes above the internal POKSET threshold. Connect POK to an external pullup resistor.                                                                                                                                                                                         |  |  |

| _       | _       | 8               | _       | POKSET | Power-OK Threshold-Adjustment Input. POK remains low while POKSET is below the internal POKSET threshold (1.18V). POK goes high impedance when POKSET goes above the internal POKSET threshold (1.24V). Connect a resistive divider from OUTFB to POKSET to adjust the desired undervoltage threshold.                                                                                                                               |  |  |

| _       | _       | _               | 4       | CLEAR  | Latch Clear Input. Connect CLEAR to a logic-high to latch the device off after an overvoltage condition. With OVSET below V <sub>TH</sub> , pulse CLEAR low (5µs typ) to reset the output latch. Connect CLEAR to GND to make the latch transparent.                                                                                                                                                                                 |  |  |

|         | _       | _               | 8       | UVSET  | Undervoltage-Threshold Adjustment Input. Connect UVSET to an external resistive voltage-divider network to adjust the desired undervoltage threshold.                                                                                                                                                                                                                                                                                |  |  |

| _       | _       | _               | _       | EP     | Exposed Pad. EP is internally connected to GND. Connect EP to the ground plane to provide a low thermal-resistance path from the IC junction to the PC board. Do not use as the primary electrical connection to GND.                                                                                                                                                                                                                |  |  |

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

### **Detailed Description**

#### **Overvoltage Monitoring**

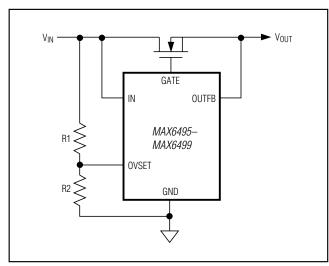

When operating in overvoltage mode, the MAX6495–MAX6499 feedback path (Figure 1) consists of IN, OVSET's internal comparator, the internal gate charge pump, and the external n-channel MOSFET, resulting in a switch-on/off function. When the programmed overvoltage threshold is tripped, the internal fast comparator turns off the external MOSFET, clamping GATE to OUTFB within 0.5µs and disconnecting the power source from the load. When IN decreases below the adjusted overvoltage threshold, the MAX6495–MAX6499 slowly enhance GATE above OUTFB, reconnecting the load to the power source.

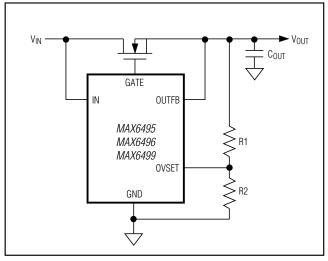

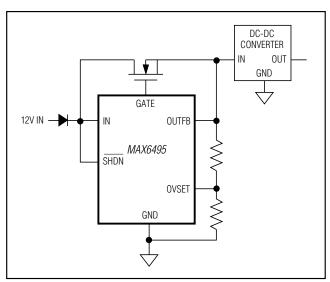

# Overvoltage Limiter (MAX6495/MAX6496/MAX6499)

When operating in overvoltage-limiter mode, the MAX6495/MAX6496/MAX6499 feedback path (Figure 2) consists of OUTFB, OVSET's internal comparator, the internal gate charge pump, and the external n-channel MOSFET, resulting in the external MOSFET operating as a voltage regulator.

During normal operation, GATE is enhanced 10V above OUTFB. The external MOSFET source voltage is monitored through a resistive divider between OUTFB and OVSET. When OUTFB rises above the adjusted overvoltage threshold, an internal comparator sinks the charge-pump current, discharging the external GATE, regulating OUTFB at the OVSET overvoltage threshold. OUTFB remains active during the overvoltage transients and the MOSFET continues to conduct during the overvoltage event, operating in switched-linear mode.

As the transient begins decreasing, OUTFB fall time will depend on the MOSFET's GATE charge, the internal charge-pump current, the output load, and the tank capacitor at OUTFB.

For fast-rising transients and very large-sized MOSFETs, add an additional bypass capacitor from GATE to GND to reduce the effect of the fast-rising voltages at IN. The external capacitor acts as a voltage-divider working against the MOSFET's drain-to-gate capacitance. For a 6000pF gate-to-source capacitance, a 0.1µF capacitor at GATE will reduce the impact of the fast-rising V<sub>IN</sub> input.

Caution must be exercised when operating the MAX6495/MAX6496/MAX6499 in voltage-limiting mode for long durations. If the  $V_{\text{IN}}$  is a DC voltage greater than the MOSFET's maximum gate voltage, the MOSFET dissipates power continuously. To prevent damage to the external MOSFET, proper heatsinking should be implemented.

Figure 1. Overvoltage Threshold (MAX6495–MAX6499)

Figure 2. Overvoltage-Limiter Protection Switch Configuration

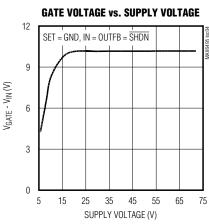

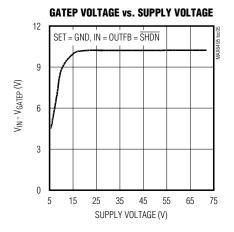

## GATE Voltage

The MAX6495–MAX6499 use a high-efficiency charge pump to generate the GATE voltage. Upon VIN exceeding the 5V (typ) UVLO threshold, GATE enhances 10V above VIN (for VIN  $\geq$  14V) with a 100µA pullup current. An overvoltage condition occurs when the voltage at OVSET goes above its VTH+ threshold. When the threshold is crossed, GATE falls to OUTFB within 0.5µs with a 100mA pulldown current. The MAX6495–MAX6499 include an internal clamp to OUTFB that ensures GATE is limited to 18V (max) above OUTFB to prevent gate-to-source damage of the external MOSFET.

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

The gate cycles during overvoltage-limit and overvoltage-switch modes are quite similar but have distinct characteristics. In overvoltage-switch mode, GATE is enhanced to (VIN + 10V) while the monitored VIN voltage remains below the overvoltage fault threshold (OVSET < VTH+). When an overvoltage fault occurs (OVSET  $\geq$  VTH+), GATE is pulled one diode drop below OUTFB, turning off the external MOSFET and disconnecting the load from the input. GATE remains low (MOSFET off) as long as the VIN voltage is above the overvoltage fault threshold. As VIN falls back below the overvoltage fault threshold, GATE is again enhanced to (VIN + 10V).

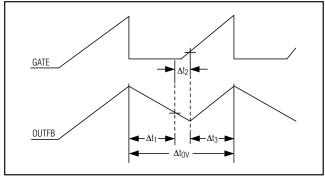

In overvoltage-limit mode, GATE is enhanced to (VIN +10V) while the monitored OUTFB voltage remains below the overvoltage fault threshold (OVSET < V<sub>TH+</sub>). When an overvoltage fault occurs (OVSET ≥ V<sub>TH+</sub>), GATE is pulled one diode drop below OUTFB until OUTFB drops 5% below the overvoltage fault threshold (MAX6495/MAX6496/MAX6499). GATE is then turned back on until OUTFB reaches the overvoltage fault threshold and GATE is again turned off. GATE cycles in a sawtooth waveform until OUTFB remains below the overvoltage fault threshold and GATE remains constantly on (VIN +10V). The overvoltage limiter's sawtooth GATE output operates the MOSFET in a switched-linear mode while the input voltage remains above the overvoltage fault threshold. The sawtooth frequency depends on the load capacitance, load current, and MOSFET turn-on time (GATE charge current and GATE capacitance).

GATE goes high when the following startup conditions are met:  $V_{\text{IN}}$  is above the UVLO threshold,  $\overline{\text{SHDN}}$  is high, an overvoltage fault is not present, and the device is not in thermal shutdown.

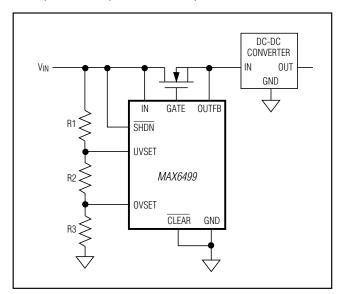

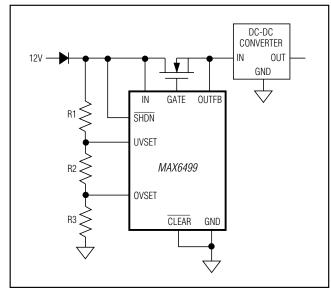

#### **Undervoltage Monitoring (MAX6499)**

The MAX6499 includes undervoltage and overvoltage comparators for window detection (see Figures 3 and 12). GATE is enhanced and the n-channel MOSFET is on when the monitored voltage is within the selected "window." When the monitored voltage falls below the lower limit (VTRIPLOW) or exceeds the upper limit (VTRIPHIGH) of the window, GATE falls to OUTFB turning off the MOSFET. The application in Figure 3 shows the MAX6499 enabling the DC-DC converter when the monitored voltage is in the selected window.

The resistor values R1, R2, and R3 can be calculated as follows:

$$V_{TRIPLOW} = (V_{TH-}) \left( \frac{R_{TOTAL}}{R2 + R3} \right)$$

$V_{TRIPHIGH} = (V_{TH+}) \left( \frac{R_{TOTAL}}{R3} \right)$

where  $R_{TOTAL} = R_1 + R_2 + R_3$ .

Use the following steps to determine the values for R1, R2, and R3:

- 1) Choose a value for R<sub>TOTAL</sub>, the sum of R1, R2, and R3. Because the MAX6499 has very high input impedance, R<sub>TOTAL</sub> can be up to  $5M\Omega$ .

- 2) Calculate R3 based on R<sub>TOTAL</sub> and the desired upper trip point:

$$R3 = \frac{V_{TH+} \times R_{TOTAL}}{V_{TRIPHIGH}}$$

3) Calculate R2 based on R<sub>TOTAL</sub>, R3, and the desired lower trip point:

$$R2 = \left\lceil \frac{\left(V_{TH-}\right) \times R_{TOTAL}}{V_{TRIPLOW}} \right\rceil - R3$$

4) Calculate R1 based on RTOTAL, R2, and R3:

$$R1 = RTOTAL - R2 - R3$$

To improve ESD protection, keep R3  $\geq$  1k $\Omega$ .

Figure 3. MAX6499 Window-Detector Circuit

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

#### Power-OK Output (MAX6497/MAX6498)

POK is an open-drain output that remains low when the voltage at POKSET is below the internal POKSET threshold (1.18V). POK goes high impedance when POKSET goes above the internal POKSET threshold (1.24V). Connect a resistive divider from OUTFB to POKSET to adjust the desired undervoltage threshold. Use a resistor in the  $100k\Omega$  range from POKSET to GND to minimize current consumption.

#### **Overvoltage Latch Function**

The MAX6497/MAX6499 offers a latch function that prevents the external MOSFET from turning on until the latch is cleared. For the MAX6497, the latch can be cleared by cycling the power on the input IN to a voltage below the undervoltage lockout or by pulling the shutdown input low and then back to a logic-high state. The MAX6499 offers a CLEAR input that latches the n-MOSFET off when CLEAR is high. The latch is removed when the CLEAR input is plused low. Connect CLEAR low to make the latch transparent.

#### **Overvoltage Retry Function**

The MAX6498 offers an automatic retry function that tries to enhance the external n-channel MOSFET after the overvoltage condition is removed. When the monitored input voltage detects an overvoltage condition (VSET > VTH+), the n-MOSFET is turned off. The MOSFET stays off until the voltage at VSET falls below its VTH- (typically 0.13V), at which point the output tries to turn on again.

## **Applications Information**

#### **Load Dump**

Most automotive applications run off a multicell "12V" lead-acid battery with a nominal voltage that swings between 9V and 16V (depending on load current, charging status, temperature, battery age, etc.). The battery voltage is distributed throughout the automobile and is locally regulated down to voltages required by the different system modules. Load dump occurs when the alternator is charging the battery and the battery becomes disconnected. The alternator voltage regulator is temporarily driven out of control. Power from the alternator flows into the distributed power system and elevates the voltage seen at each module. The voltage spikes have rise times typically greater than 5ms and decays within several hundred milliseconds but can extend out to 1s or more depending on the characteristics of the charging system. These transients are capable of destroying sensitive electronic equipment on the first "fault event."

#### **Setting Overvoltage Thresholds**

OVSET provides an accurate means to set the overvoltage level for the MAX6495–MAX6499. Use a resistive divider to set the desired overvoltage condition (see Figure 2). OVSET has a rising 1.24V threshold with a 5% falling hysteresis (MAX6495/MAX6496/MAX6499) and a rising 0.505V threshold with a falling 0.15V threshold (MAX6497/MAX6498).

Begin by selecting the total end-to-end resistance,  $R_{TO-TAL} = R1 + R2$ . Choose  $R_{TO-TAL}$  to yield a total current equivalent to a minimum 100 x ISET (OVSET's input bias current) at the desired overvoltage threshold.

For example:

With an overvoltage threshold (VoV) set to 20V for the MAX6495/MAX6496/MAX6499,  $R_{TOTAL} < 20V$  / (100 x ISET), where ISET is OVSET's 50nA (max) input bias current.

RTOTAL

$$< 4M\Omega$$

Use the following formula to calculate R2:

$$R2 = V_{TH+} \times \frac{R_{TOTAL}}{V_{OV}}$$

where  $V_{TH+}$  is the 1.24V OVSET rising threshold and  $V_{OV}$  is the desired overvoltage threshold.

$R2 = 248k\Omega$ . Use a  $249k\Omega$  standard resistor.

$R_{TOTAL} = R_2 + R_1$ , where  $R_1 = 3.751 M\Omega$ . Use a 3.74M $\Omega$  standard resistor.

A lower value for total resistance dissipates more power but provides slightly better accuracy. To improve ESD protection, keep R2  $\geq$  1k $\Omega$ .

#### **Reverse-Battery Protection**

The MAX6496 is an overvoltage-protection circuit that is capable of driving a p-channel MOSFET to prevent reverse-battery conditions. This MOSFET eliminates the need for external diodes, thus minimizing the input voltage drop (see Figure 8).

#### Inrush/Slew-Rate Control

Inrush current control can be implemented by placing a capacitor from GATE to GND to slowly ramp up the GATE, thus limiting the inrush current and controlling GATE's slew rate during initial turn-on. The inrush current can be approximated using the following equation:

$$I_{INRUSH} = \frac{C_{OUT}}{C_{GATE}} \times I_{GATE} + I_{LOAD}$$

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

where IGATE is GATE's 100 $\mu$ A sourcing current, ILOAD is the load current at startup, and COUT is the output capacitor.

#### **MOSFET Selection**

Select external MOSFETs according to the application current level. The MOSFET's on-resistance (RDS(ON)) should be chosen low enough to have a minimum voltage drop at full load to limit the MOSFET power dissipation. Determine the device power rating to accommodate an overvoltage fault when operating the MAX6495/MAX6496/MAX6499 in overvoltage-limit mode.

During normal operation, the external MOSFET dissipates little power. The power dissipated in the MOSFET during normal operation is:

$$P = ILOAD^2 \times RDS(ON)$$

where P is the power dissipated in the MOSFET, I<sub>LOAD</sub> is the output load current, and R<sub>DS(ON)</sub> is the drain-to-source resistance of the MOSFET.

Most power dissipation in the MOSFET occurs during a prolonged overvoltage event when operating the MAX6495/MAX6496/MAX6499 in voltage-limiter mode. The power dissipated across the MOSFET is as follows (see the *Thermal Shutdown in Overvoltage-Limiter Mode* section):

where  $V_{DS}$  is the voltage across the MOSFET's drain and source.

#### Thermal Shutdown

The MAX6495-MAX6499 thermal-shutdown feature turns off GATE if it exceeds the maximum allowable thermal dissipation. Thermal shutdown also monitors the PC board temperature of the external n-channel MOSFET when the devices sit on the same thermal island. Good thermal contact between the MAX6495-MAX6499 and the external n-channel MOSFET is essential for the thermal-shutdown feature to operate effectively. Place the n-channel MOSFET as close to possible to OUTFB.

When the junction temperature exceeds  $T_J = +160^{\circ} C$ , the thermal sensor signals the shutdown logic, turning off the GATE output and allowing the device to cool. The thermal sensor turns the GATE on again after the IC's junction temperature cools by 20°C. Thermal-overload protection is designed to protect the MAX6495–MAX6499 and the external MOSFET in the event of current-limit fault conditions. For continuous operation, do

not exceed the absolute maximum junction-temperature rating of  $T_J = +150$ °C.

#### **Peak Power-Dissipation Limit**

The MAX6495–MAX6499 activate an internal 100mA pulldown on GATE when SHDN goes low, OVSET exceeds its threshold or UVSET falls below its threshold. Once the voltage on GATE falls below the OUTFB voltage, current begins to flow from OUTFB to the 100mA pulldown through the internal clamp diode, discharging the output capacitors.

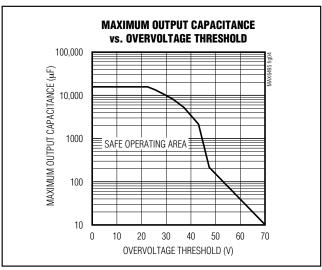

Depending on the output capacitance and the initial voltage, a significant amount of energy may be dissipated by the internal 100mA pulldown. To prevent damage to the device ensure that for a given overvoltage threshold, the output capacitance does not exceed the limit provided in Figure 4. This output capacitance represents the sum of all capacitors connected to OUTFB, including reservoir capacitors and DC-DC input filter capacitors.

#### Thermal Shutdown in Overvoltage-Limiter Mode

When operating the MAX6495/MAX6496/MAX6499 in overvoltage-limit mode for a prolonged period of time, a thermal shutdown is possible. The thermal shutdown is dependent on a number of different factors:

- The device's ambient temperature

- The output capacitor (Cout)

- The output load current (I<sub>OUT</sub>)

- The overvoltage threshold limit (V<sub>OV</sub>)

Figure 4. Safe Operating Area for 100mA Pulldown.

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

- The overvoltage waveform period (toy)

- The power dissipated across the package (PDISS)

During an initial overvoltage occurrence, the discharge time ( $\Delta t_1$ ) of C<sub>OUT</sub>, caused by I<sub>OUT</sub> and I<sub>GATEPD</sub>. The discharge time is approximately:

$$\Delta t_1 = C_{OUT} \frac{V_{OV} \times 0.05}{(l_{OUT} + l_{GATEPD})}$$

where Vov is the overvoltage threshold, IouT is the load current, and IgaTEPD is the GATE's 100mA pulldown current

Upon OUT falling below the threshold point, the MAX6495/MAX6496/MAX6499s' charge-pump current must recover and begins recharging the external GATE voltage. The time needed to recharge GATE from -VD to the MOSFET's gate threshold voltage is:

$$\Delta t_2 = C_{ISS} \frac{V_{GS(TH)} + V_D}{I_{GATE}}$$

where C<sub>ISS</sub> is the MOSFET's input capacitance, V<sub>GS(TH)</sub> is the MOSFET's gate threshold voltage, V<sub>D</sub> is the internal clamp (from OUTFB to GATE) diode's forward voltage (1.5V, typ) and I<sub>GATE</sub> is the charge-pump current (100 $\mu$ A typ).

During  $\Delta t_2$ ,  $C_{OUT}$  loses charge through the output load. The voltage across  $C_{OUT}$  ( $\Delta V_2$ ) decreases until the MOSFET reaches its  $V_{GS(TH)}$  threshold and can be approximated using the following formula:

Figure 5. MAX6495/MAX6496/MAX6499 Timing

$$\Delta V_2 = I_{OUT} \frac{\Delta t_2}{C_{OUT}}$$

Once the MOSFET  $V_{GS(TH)}$  is obtained, the slope of the output-voltage rise is determined by the MOSFET  $Q_g$  charge through the internal charge pump with respect to the drain potential. The new rise time needed to reach a new overvoltage event can be calculated using the following formula:

$$\Delta t_3 \cong \frac{Q_{GD}}{V_{GS}} \frac{\Delta V_{OUT}}{I_{GATE}}$$

where QGD is the gate-to-drain charge.

The total period of the overvoltage waveform can be summed up as follows:

$$\Delta t_{OV} = \Delta t_1 + \Delta t_2 + \Delta t_3$$

The MAX6495/MAX6496/MAX6499 dissipate the most power during an overvoltage event when I<sub>OUT</sub> = 0. The maximum power dissipation can be approximated using the following equation:

$$P_{DISS} = V_{OV} \times 0.975 \times I_{GATEPD} \times \frac{\Delta t_1}{\Delta t_{OV}}$$

The die-temperature increase is related to  $\theta_{JC}$  (8.3°C/W and 8.5°C/W for the MAX6495/MAX6496/MAX6499, respectively) of the package when mounted correctly with a strong thermal contact to the circuit board. The MAX6495/MAX6496/MAX6499 thermal shutdown is governed by the equation:

$$T_J = T_A + P_{DISS} (\theta_{JC} + \theta_{CA}) < +170^{\circ}C$$

Based on these calculations, the parameters of the MOSFET, the overvoltage threshold, the output load current, and the output capacitors are external variables affecting the junction temperature. If these parameters are fixed, the junction temperature can also be affected by increasing  $\Delta t_3$ , which is the time the switch is on. By increasing the capacitance at the GATE pin,  $\Delta t_3$  increases as it increases the amount of time required to charge up this additional capacitance (75µA gate current). As a result,  $\Delta t_0$ V increases, thereby reducing the power dissipated (PDISS).

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

## **Typical Application Circuits**

Figure 6. Overvoltage Limiter (MAX6495)

Figure 7. Overvoltage Limiter with Low-Voltage-Drop Reverse-Protection Circuit (MAX6496)

Figure 8. Overvoltage Protection to a DC-DC Converter (MAX6497/MAX6498)

Figure 9. Overvoltage and Undervoltage Window Detector (MAX6499)

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

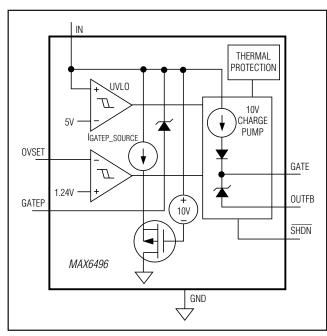

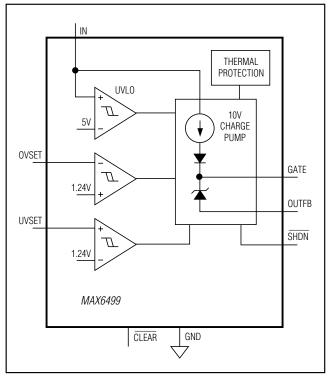

#### **Functional Diagrams**

Figure 10. Functional Diagram (MAX6495)

Figure 12. Functional Diagram (MAX6497/MAX6498)

Figure 11. Functional Diagram (MAX6496)

Figure 13. Functional Diagram (MAX6499)

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

#### **Selector Guide**

| PART    | FUNCTION             | p-CHANNEL<br>DRIVER | POK<br>FUNCTION | UNDERVOLTAGE | LATCH/<br>AUTORETRY | PACKAGE CODE |

|---------|----------------------|---------------------|-----------------|--------------|---------------------|--------------|

| MAX6495 | OV Switch/Limiter    | _                   | _               | _            | _                   | T633-2       |

| MAX6496 | OV Switch/Limiter    | Yes                 |                 | _            |                     | T833-2       |

| MAX6497 | OV Switch            | _                   | Yes             | _            | Latch               | T833-2       |

| MAX6498 | OV Switch            | _                   | Yes             | _            | Autoretry           | T833-2       |

| MAX6499 | OV/UV Switch/Limiter | _                   | _               | Yes          | Latch               | T833-2       |

## Pin Configurations (continued)

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

## Ordering Information (continued)

| PART           | PIN-PACKAGE | TOP MARK |

|----------------|-------------|----------|

| MAX6496ATA+T   | 8 TDFN-EP*  | AOF      |

| MAX6496ATA/V+T | 8 TDFN-EP*  | AOF      |

| MAX6497ATA+T   | 8 TDFN-EP*  | AOC      |

| MAX6498ATA+T   | 8 TDFN-EP*  | AOD      |

| MAX6499ATA+T   | 8 TDFN-EP*  | AOE      |

| MAX6499ATA/V+T | 8 TDFN-EP*  | AOE      |

**Note:** All devices are specified over the -40°C to +125°C operating temperature range.

/V denotes an automotive qualified part.

## \_Chip Information

PROCESS: BICMOS

## Package Information

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 6 TDFN-EP       | T633+2          | 21-0137        | 90-0058             |

| 8 TDFN-EP       | T833+2          | 21-0137        | 90-0059             |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

<sup>\*</sup>EP = Exposed pad.

# 72V, Overvoltage-Protection Switches/ Limiter Controllers with an External MOSFET

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                          | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 7/05             | Initial release.                                                                                                                                                     | _                |

| 1                  | 12/05            | Corrected text and formula in the Detailed Description.                                                                                                              | 10, 11           |

| 2                  | 1/07             | Updated text in the Applications Information.                                                                                                                        | 9                |

| 3                  | 12/08            | Updated package codes in the Selector Guide.                                                                                                                         | 1, 13            |

| 4                  | 1/09             | Added automotive qualified part for MAX6495.                                                                                                                         | 1, 14            |

| 5                  | 3/09             | Updated <i>Electrical Characteristics</i> , added <i>Peak Power Dissipation Limit</i> section and new Figure 4. Renumbered subsequent figures throughout data sheet. | 3, 9, 10–15      |

| 6                  | 7/09             | Corrected the MAX6495ATT/V+T top mark in the <i>Ordering Information</i> table from AJM to AUG.                                                                      | 2                |

| 7                  | 8/09             | Updated <i>Undervoltage Monitoring (MAX6499)</i> and <i>Setting Overvoltage Thresholds</i> sections.                                                                 | 8, 9             |

| 8                  | 1/11             | Added soldering temperature in the <i>Absolute Maximum Ratings</i> section and corrected equation.                                                                   | 2, 11            |

| 9                  | 2/12             | Added automotive package for MAX6499.                                                                                                                                | 15               |

| 10                 | 6/12             | Added automotive package for MAX6496.                                                                                                                                | 15               |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Maxim Integrated:

MAX6495ATT+T MAX6495ATT/V+T MAX6496ATA+T MAX6497ATA+T MAX6498ATA+T MAX6499ATA+T