## **DATA COMMUNICATIONS**

# 27-Line Plug and Play SCSI Terminator

The 27-channel IMP5121 SCSI terminator is part of IMP's family of high-performance SCSI terminators that deliver true UltraSCSI performance. The BiCMOS design offers superior performance over first generation linear regulator/resistor based terminators.

IMP's new architecture employs high-speed adaptive elements for each channel, thereby providing the fastest response possible - typically 35MHz, which is 100 times faster than the older linear regulator terminator approach. The bandwidth of terminators based on the older regulator/resistor terminator architecture is limited to 500kHz since a large output stabilization capacitor is required. The IMP architecture eliminates the external output compensation capacitor and the need for transient output capacitors while maintaining pin compatibility with first generation designs. Reduced component count is inherent with the IMP5121.

The IMP5121 architecture tolerates marginal system designs. A key improvement offered by the IMP5121 lies in its ability to insure reliable, error-free communications even in systems which do not adhere to recommended SCSI hardware design guidelines, such as improper cable lengths and impedance. Frequently, this situation is not controlled by the peripheral or host designer.

For portable and configurable peripherals, the IMP5121 can be placed in a sleep mode with TTL compatible signals. Quiescent current is less than  $150\mu A$  when disabled.

## **Key Features**

- ♦ SCSI Plug and Play

- Host bus adapter with 3 SCSI connectors

- Ultra-Fast response for Fast-20 SCSI

- Split disconnect for mixing 16-bit (wide) or 8-bit (narrow) buses

- ◆ 35MHz channel bandwidth

- ♦ Sleep-mode current less than 150µA

- ♦ NO external compensation capacitors

- ◆ Compatible with active negation drivers

- ♦ Hot swap compatible

- ◆ Superior replacement for the LX5121 and UCC5621

For Host Bus Adapters and three SCSI connectors, the IMP5121 has multiple disable pins for Plug and Play SCSI capability. It also splits the upper nine termination lines for mixing 16-bit (wide) and 8-bit (narrow) buses with minimal board trace capacitance.

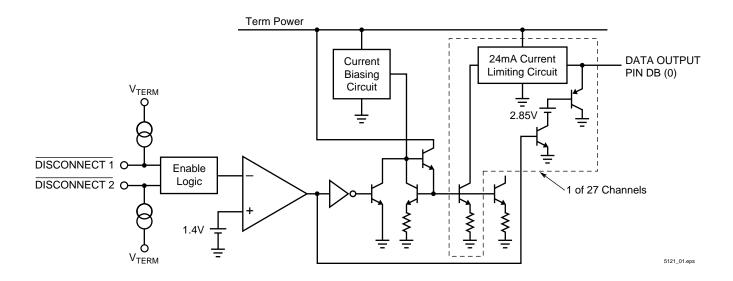

# **Block Diagrams**

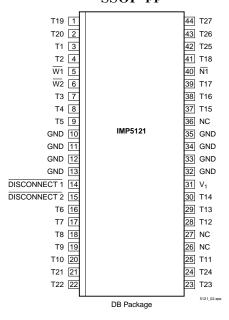

# Pin Configuration

#### SSOP-44

#### TSSOP-56

|              |    |            | L  |              |

|--------------|----|------------|----|--------------|

| T19          | 1  |            | 56 | T27          |

| T20          | 2  |            | 55 | T26          |

| T1           | 3  |            | 54 | T25          |

| T2           | 4  |            | 53 | T18          |

| W1           | 5  |            | 52 | N1           |

| W2           | 6  |            | 51 | T17          |

| T3           | 7  |            | 50 | T16          |

| T4           | 8  |            | 49 | T15          |

| T5           | 9  |            | 48 | NC           |

| GND          | 10 |            | 47 | GND          |

| GND          | 11 |            | 46 | GND          |

| HEAT SINK    | 12 |            | 45 | HEAT SINK    |

| HEAT SINK    | 13 |            | 44 | HEAT SINK    |

| HEAT SINK    | 14 | IMP5121    | 43 | HEAT SINK    |

| HEAT SINK    | 15 |            | 42 | HEAT SINK    |

| HEAT SINK    | 16 |            | 41 | HEAT SINK    |

| HEAT SINK    | 17 |            | 40 | HEAT SINK    |

| GND          | 18 |            | 39 | GND          |

| GND          | 19 |            | 38 | GND          |

| DISCONNECT 1 | 20 |            | 37 | $V_1$        |

| DISCONNECT 2 | 21 |            | 36 | T14          |

| Т6           | 22 |            | 35 | T13          |

| T7           | 23 |            | 34 | T12          |

| T8           | 24 |            | 33 | NC           |

| Т9           | 25 |            | 32 | NC           |

| T10          | 26 |            | 31 | T11          |

| T21          | 27 |            | 30 | T24          |

| T22          | 28 |            | 29 | T23          |

|              | l  | PW Package | J  | 5121_02a.eps |

# **Ordering Information**

| Part Number | Temperature Range | Package              |  |

|-------------|-------------------|----------------------|--|

| IMP5121CDB  | 0°C to 125°C      | 44-pin Plastic SSOP  |  |

| IMP5121CPW  | 0°C to 125°C      | 56-pin Plastic TSSOP |  |

5121\_t01.at3

# Absolute Maximum Ratings<sup>1</sup>

Storage Temperature Range ......-65°C to 150°C Lead Temperature (Soldering, 10 sec.) ...... 300°C

Note: 1. Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. Currents are positive into, negative out of the specified terminal.

# Thermal Data

PW and DB Package

Thermal Resistance Junction-to-Ambient,  $\theta_{JA}$  . . . . . .  $50^{\circ}C/W$

Junction Temperature Calculation:  $T_J = T_A + (P_D x \theta_{JA})$ .

The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/pc-board system. All of the ambient airflow is assumed.

# **Recommended Operating Conditions**

| Parameter                                       | Symbol            | Min | Тур | Max               | Units |

|-------------------------------------------------|-------------------|-----|-----|-------------------|-------|

| Termpwr Voltage                                 | V <sub>TERM</sub> | 4.0 |     | 5.5               | V     |

| High Level Disable Input Voltage                | V <sub>IH</sub>   | 2   |     | V <sub>TERM</sub> | V     |

| Low Level Disable Input Voltage                 | V <sub>IL</sub>   | 0   |     | 0.8               | V     |

| Operating Junction Temperature Range – IMP5121C |                   | 0   |     | 125               | °C    |

Note: 2. Recommended operating conditions indicate the range over which the device is functional.

5225\_t02.eps

## **Electrical Characteristics**

Unless otherwise specified, these specifications apply at an ambient operating temperature of  $T_A = 25^{\circ}C$ . TermPwr = 4.75V. Low duty cycle pulse testing techniques are used which maintains junction and case temperatures equal to the ambient temperature.

| Parameter                             | Symbol            | Conditions                                    | Min  | Тур  | Max | Units |

|---------------------------------------|-------------------|-----------------------------------------------|------|------|-----|-------|

| Output High Voltage                   | V <sub>OUT</sub>  |                                               | 2.65 | 2.85 |     | V     |

| TermPwr Supply Current                | I <sub>CC</sub>   | All data lines = Open                         |      | 12   | 20  | mA    |

|                                       |                   | All data lines = 0.5V                         |      | 635  | 670 |       |

|                                       |                   | Disable Pins 1, 2 < 0.8V                      |      | 50   | 150 | μA    |

| Output Current                        | I <sub>OUT</sub>  | V <sub>OUT</sub> = 0.5V                       | -20  | -22  | -24 | mA    |

| Disconnect Input Current              | I <sub>IN</sub>   | DISCONNECT Pins = 0V                          |      |      | -10 | μA    |

| Output Leakage Current                | I <sub>OL</sub>   | DISCONNECT Pins < 0.8V, V <sub>O</sub> = 0.2V |      |      | 1   | μA    |

| Channel Bandwidth                     | BW                |                                               |      | 35   |     | MHz   |

| Termination Sink Current, per Channel | I <sub>SINK</sub> | V <sub>OUT</sub> = 4V                         | 7    |      |     | mA    |

5121\_t03.eps

© 2002 IMP, Inc. Data Communications 3

## **Application Information**

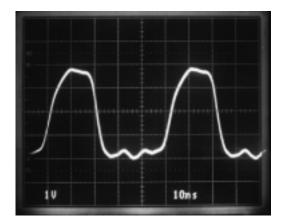

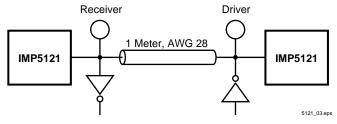

Figure 1. Receiving Waveform - 20MHz

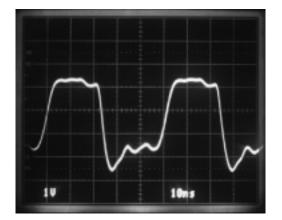

Figure 2. Driving Waveform - 20MHz

Figure 3.

#### **IMP5121 Maximizes Line Current**

Cable transmission theory suggests to optimize signal speed and quality, the termination should act both as an ideal voltage reference when the line is released (deasserted) and as an ideal current source when the line is active (asserted). Common active terminators which consist of linear regulators in series with resistors (typically  $110\Omega$ ) are a compromise. With coventional linear terminators as the line voltage increases the amount of current decreases linearly by the equation;

$$\frac{\left(V_{REF}-V_{LINE}\right)}{R}=I.$$

The IMP5121, with its unique new architecture, applies the maximum amount of current regardless of line voltage until the termination high threshold (2.85V) is reached.

Acting as a near ideal line terminator, the IMP5121 closely reproduces the optimum case when the device is enabled. To enable the device the DISC1 and DISC2 pins must be driven per *Table 1*. When enabled, quiescent current is 12mA and the device will respond to line demands by delivering 24mA on assertion and by imposing 2.85V on de-assertion.

## Disable/Sleep Mode

Disable mode places the device in a sleep state, where quiescent current is reduced to less than  $150\mu A$ . When disabled, all outputs are in a high impedance state. Sleep mode can be used for power conservation or to remove the terminator from the SCSI chain.

An additional feature of the IMP5121 is its compatibility with active negation drivers.

# **Application Information**

**Table 1. Power Up/ Power Down Function Table**

| DISCONNECT 1 | DISCONNECT 2 | W1 | W2 | N1 | T1-T18   | T19-T27  |

|--------------|--------------|----|----|----|----------|----------|

| Н            | L            | DC | DC | DC | Enabled  | Disabled |

| L            | Н            | DC | DC | DC | Disabled | Enabled  |

| L            | L            | DC | DC | DC | Disabled | Disabled |

| Н            | Н            | Н  | Н  | Н  | Enabled  | Enabled  |

| Н            | Н            | Н  | Н  | L  | Enabled  | Enabled  |

| Н            | Н            | Н  | L  | Н  | Enabled  | Enabled  |

| Н            | Н            | Н  | L  | L  | Disabled | Enabled  |

| Н            | Н            | L  | Н  | Н  | Enabled  | Enabled  |

| Н            | Н            | L  | Н  | L  | Disabled | Enabled  |

| Н            | Н            | L  | L  | Н  | Disabled | Disabled |

| Н            | Н            | Ĺ  | L  | L  | Disabled | Disabled |

5121\_t04.eps

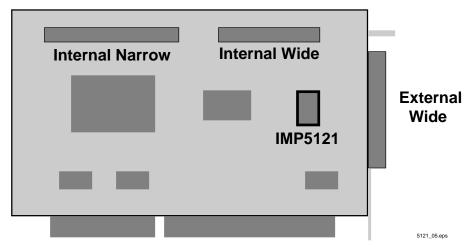

For Plug and Play SCSI auto-termination disabling, connect pin 50 of the External Wide SCSI connector to  $\overline{W1}$  of the IMP5121, connect pin  $\underline{50}$  of the Internal Wide SCSI connector to  $\overline{W2}$  of the IMP5121, and connect pin 22 of the Internal Narrow connector to  $\overline{N1}$  of the IMP5121.

Figure 4. Plug and Play Diagram

© 2002 IMP, Inc. Data Communications 5

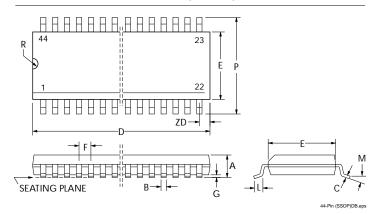

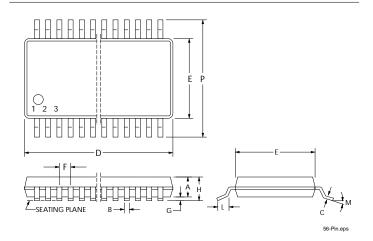

# Package Dimensions

### SSOP (44-Pin)

## TSSOP (56-Pin)

| Inches        |              |          | Millimeters |       |  |  |  |

|---------------|--------------|----------|-------------|-------|--|--|--|

|               | Min          | Max      | Min         | Max   |  |  |  |

| SSOP (44-Pin) |              |          |             |       |  |  |  |

| Α             | 0.096        | 0.104    | 2.44        | 2.64  |  |  |  |

| В             | 0.011        | 0.020    | 0.28        | 0.51  |  |  |  |

| С             | 0.0091       | 0.0125   | 0.23        | 0.32  |  |  |  |

| D             | 0.698        | 0.706    | 17.73       | 17.93 |  |  |  |

| Е             | 0.291        | 0.299    | 7.40        | 7.60  |  |  |  |

| F             | 0.031        | 5 BSC    | 0.80 BSC    |       |  |  |  |

| G             | 0.004        | 0.012    | 0.10        | 0.30  |  |  |  |

| L             | 0.016        | 0.050    | 0.40        | 1.27  |  |  |  |

| М             | 0°           | 8°       | 0°          | 8°    |  |  |  |

| Р             | 0.396        | 0.414    | 10.11       | 10.51 |  |  |  |

| R             | 0.025        | 0.035    | 0.63        | 0.89  |  |  |  |

| ZD            | 0.033        | REF      | 0.51 REF    |       |  |  |  |

| LC*           | <del>_</del> | 0.004    | _           | 0.10  |  |  |  |

|               |              | TSSOP (5 | 6-Pin)      |       |  |  |  |

| Α             | 0.032        | 0.041    | 0.80        | 1.05  |  |  |  |

| В             | 0.007        | 0.011    | 0.17        | 0.27  |  |  |  |

| С             | 0.004        | 0.008    | 0.09        | 0.20  |  |  |  |

| D             | 0.547        | 0.555    | 13.90       | 14.10 |  |  |  |

| Е             | 0.236        | 0.244    | 6.0         | 6.2   |  |  |  |

| F             | 0.02         | BSC      | 0.50 BSC    |       |  |  |  |

| G             | 0.002        | 0.005    | 0.05        | 0.15  |  |  |  |

| Н             | _            | 0.047    | _           | 1.20  |  |  |  |

| L             | 0.018        | 0.030    | 0.45        | 0.75  |  |  |  |

| М             | 0°           | 8°       | 0°          | 8°    |  |  |  |

| Р             | 0.32 BSC     |          | 8.1 BSC     |       |  |  |  |

| LC*           | <u> </u>     | 0.004    |             | 0.10  |  |  |  |

\* Lead Coplanarity

5225\_t05.at3

IMP, Inc.

Corporate Headquarters 2830 N. First Street

San Jose, CA 95134-2071

Tel: 408-432-9100 Fax: 408-432-1085

e-mail: info@impinc.com http://www.impweb.com