SLAS162 - SEPTEMBER 1998

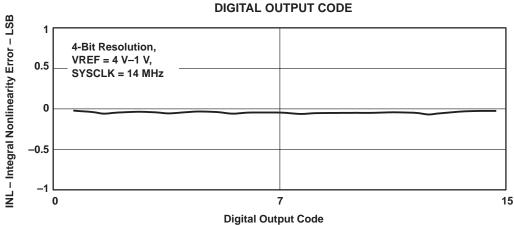

- 2 MSPS Max Throughput at 10 Bit (Single Channel), ±1 LSB DNL, ±1 LSB INL MAX

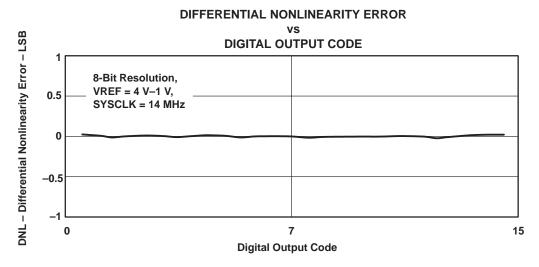

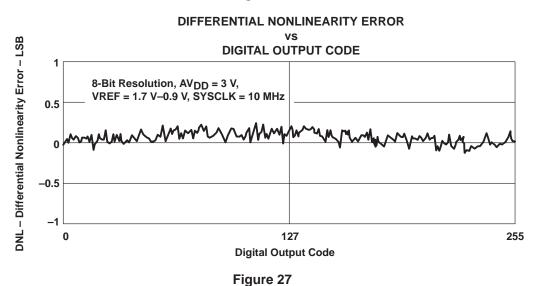

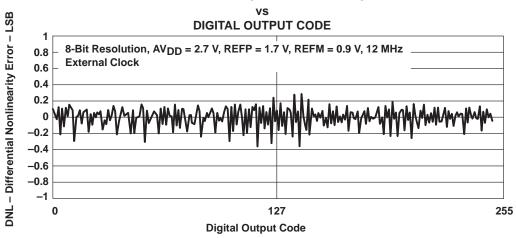

- 3 MSPS Max Throughput at 8 Bit (Single Channel), ±1 LSB DNL, ±1 LSB INL MAX

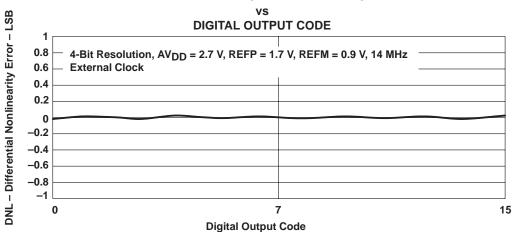

- 7 MSPS Max Throughput at 4 Bit (Single Channel), ±0.4 LSB DNL, ±0.4 LSB INL MAX

- No Missing Code for External Clock Up to 15 MHz at 5.5 V, 12 MHz at 2.7 V

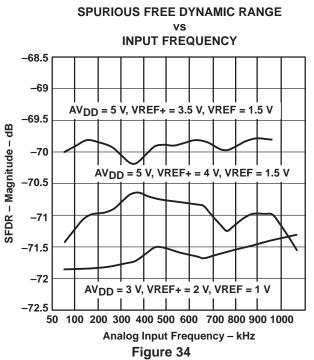

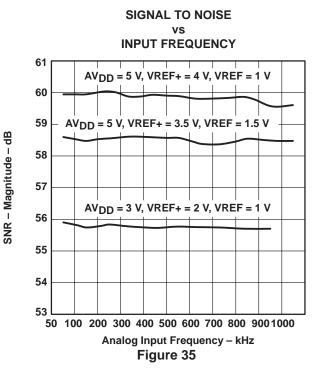

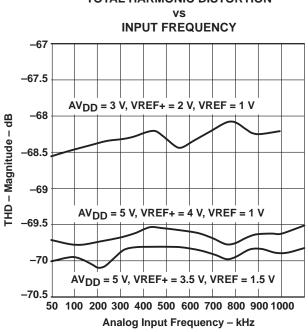

- ENOB 9.4 Bit, SINAD 57.8 dB, SFDR

-70.8 dB, THD -68.8 dB, at fi = 800 kHz,

10 Bit

- Wide Input Bandwidth for Undersampling (75 MHz at 1 dB, >120 MHz at -3 dB) at  $R_s = 1 \text{ k}\Omega$

- Software Programmable Power Down, (1 μA), Auto Powerdown (120 μA)

- Single Wide Range Supply 2.7 VDC to 5.5 VDC

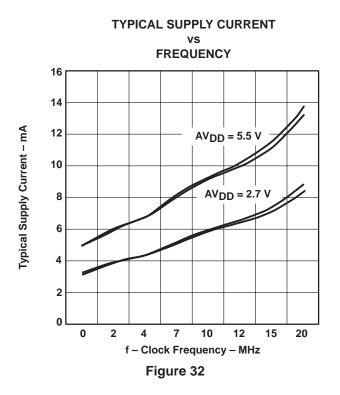

- Low Supply Current 11 mA at 5.5 V, 10 MHz;

7 mA at 2.7 V, 8 MHz Operating

- Simultaneous Sample and Hold: Dual Sample and Hold Matched Channels Multi Chip Simultaneous Sample and Hold Capable

- Programmable Conversion Modes: Interrupt-Driven for Shorter Latency Continuous Modes Optimized for MIPS Sensitive DSP Solutions

- Built-In Internal/System Mid-Scale Error Calibration

- Built-In Mux With 2 Differential or 4 Single-Ended Input Channels

- Low Input Capacitance (10 pF Max Fixed, 1 pF Max Switching)

- DSP/μ P-Compatible Parallel Interface

# applications

- Portable Digital Radios

- Personal Communication Assistants

- Cellular

- Pager

- Scanner

- Digitizers

- Process Controls

- Motor Control

- Remote Sensing

- Automotive

- Servo Controls

- Cameras

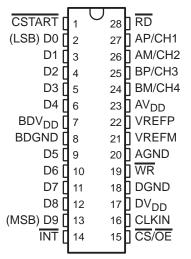

# DW OR PW PACKAGE (TOP VIEW)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

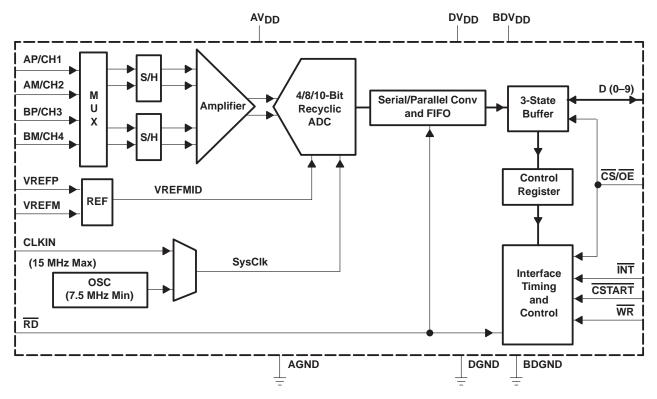

# functional block diagram

# description

The TLV1562 is a 10-bit CMOS low-power, high-speed programmable resolution analog-to-digital converter based on a low-power recyclic architecture. The unique architecture delivers a throughput up to 2 MSPS (million samples per second) at 10-bit resolution. The programmable resolution allows a higher conversion throughput as a tradeoff of lower resolution. A high speed 3-state parallel port directly interfaces to a digital signal processor (DSP) or microprocessor ( $\mu$ P) system data bus. D0 through D9 are the digital output terminals with D0 being the least significant bit (LSB). The TLV1562 is designed to operate for a wide range of supply voltages (2.7 V to 5.5 V) with very low power consumption (11 mA maximum at 5.5 V, 10 MHz CLKIN). The power saving feature is further enhanced with a software power-down feature (1  $\mu$ A maximum) and auto power-down (1  $\mu$ A maximum) feature.

Many programmable features make this device a flexible general-purpose data converter. The device can be configured as either four single-ended inputs to maximize the capacity or two differential inputs to improve noise immunity. The internal system clock (SYSCLK) may come from either an internally generated OSC or an external clock source (CLKIN). Four different modes of conversion are available for different applications. The interrupt driven modes are mostly suitable for asynchronous applications, while the continuous modes take advantage of the high speed nature of a pipelined architecture. A pair of built-in sample-and-hold amplifiers allow simultaneous sampling of two input channels. This makes the TLV1562 perfect for communication applications. Conversion is started by the  $\overline{\text{RD}}$  signal, which can also be used for reading data, to maximize the throughput. Conversion can be started either by the  $\overline{\text{RD}}$  or  $\overline{\text{CSTART}}$  signal when the device is operating in the interrupt-driven modes. The dedicated conversion start pin,  $\overline{\text{CSTART}}$ , provides a mechanism to simultaneously sample and convert multiple channels when multiple converters are used in an application.

SLAS162 - SEPTEMBER 1998

# description (continued)

The converter incorporates a pair of differential high-impedance reference inputs that facilitate ratiometric conversion, scaling, and isolation of analog circuitry from logic and supply noise. Other features such as low input capacitance (10 pF) and very wide input bandwidth (75 MHz) make this device a perfect digital signal processing (DSP) companion for mobile communication applications. A switched-capacitor design allows low-error conversion over the full operating free-air temperature range.

The features that make this device truly a DSP friendly converter include: 1) programmable continuous conversion modes, 2) programmable 2s complement output code format, and 3) programmable resolution. The TLV1562 is offered in both 28-pin TSSOP and SOIC packages. The TLV1562C is characterized for operation from 0°C to 70°C. The TLV1562I is characterized for operation over the full industrial temperature range of –40°C to 85°C.

## **AVAILABLE OPTIONS**

|               | PACKAGE                            | D DEVICE                          |

|---------------|------------------------------------|-----------------------------------|

| TA            | 28-TSSOP<br>(25 MIL PITCH)<br>(PW) | 28-SOIC<br>(50 MIL PITCH)<br>(DW) |

| 0°C to 70°C   | TLV1562CPW                         | TLV1562CDW                        |

| –40°C to 85°C | TLV1562IPW                         | TLV1562IDW                        |

SLAS162 - SEPTEMBER 1998

# **Terminal Functions**

| TERMIN            | NAL  |     | DECORPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO.  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AGND              | 20   | I   | Analog ground return for the internal circuitry. Unless otherwise noted, all analog voltage measurements are with respect to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AM/CH2            | 26   | ı   | Differential channel A input minus or single-ended channel 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AP/CH1            | 27   | ı   | Differential channel A input plus or single-ended channel 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $AV_{DD}$         | 23   | Ι   | Positive analog supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BDGND             | 8    | _   | Digital ground return for the I/O buffers. Unless otherwise noted, all digital interface voltage measurements are with respect to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BDV <sub>DD</sub> | 7    | I   | Positive digital supply voltage for I/O buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BM/CH4            | 24   | I   | Differential channel B input minus or single-ended channel 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BP/CH3            | 25   | I   | Differential channel B input plus or single-ended channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLKIN             | 16   | I   | External clock input. (1 MHz to 15 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CS/OE             | 15   | _   | Chip select. A high-to-low transition on this input resets the internal counters and controls and enables the output data bus D(0–9) and control inputs ( $\overline{RD}$ , $\overline{WR}$ ) within a maximum setup time. A low-to-high transition disables the output data bus D(9–0) and $\overline{WR}$ within a maximum setup time. This signal also serves as an output enable signal when the device is programmed into both mono and dual interrupt-driven modes using $\overline{CSTART}$ as the start of conversion signal.                           |

| CSTART            | 1    | _   | Conversion start signal. A falling edge starts the sampling period and a rising edge starts the conversion. This signal acts without $\overline{\text{CS}}$ activated. $\overline{\text{CSTART}}$ connects to $DV_{DD}$ via a $10\text{-k}\Omega$ pull-up resistor if not used.                                                                                                                                                                                                                                                                                 |

| D(0-4)            | 2–6  | I/O | The lower bits of the 3-state parallel data bus. Bidirectional. The data bus is 3-stated except when $\overline{RD}$ or $\overline{WR}$ is low when $\overline{CS}$ is low.                                                                                                                                                                                                                                                                                                                                                                                     |

| D(5-9)            | 9–13 | I/O | The higher bits of the 3-state parallel data bus. Bidirectional. The data bus is 3-stated except when RD or WR is low when CS is low. When the host processor writes to the converter, D(9,8) are used as an index to the internal registers.                                                                                                                                                                                                                                                                                                                   |

| DGND              | 18   | Ι   | Digital ground return for the internal digital logic circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $DV_{DD}$         | 17   | I   | Positive digital supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ĪNT               | 14   | 0   | Interrupt output. The falling edge of $\overline{\text{INT}}$ signals the end of conversion. This output goes from a high impedance state to low logic level on the fifth falling edge of the system clock and remains low until reset by the rising edge of $\overline{\text{CS}}$ or $\overline{\text{RD}}$ . $\overline{\text{INT}}$ requires connection of a 10-k $\Omega$ pull-up resistor.                                                                                                                                                                |

| RD                | 28   | Ι   | Processor read strobe or synchronous start of conversion/sampling. The falling edge of $\overline{RD}$ is used to 1) start the conversion in interrupt-driven mode (if $\overline{RD}$ is programmed as the start conversion signal); 2) start both conversion and next sampling plus release of the previous conversion data in both continuous modes. The rising edge of $\overline{RD}$ serves as a read strobe and data is 3-stated (approximately 10 ns at 50 pF bus loading) after this edge. Connection of a 10-k $\Omega$ pull-up resistor is optional. |

| VREFM             | 21   | ı   | The lower voltage reference value is applied to this terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VREFP             | 22   | Ι   | The upper reference voltage value is applied to this terminal. The maximum input voltage range is determined by the difference between the voltage applied to this terminal and the VREFM terminal.                                                                                                                                                                                                                                                                                                                                                             |

| WR                | 19   | I   | Processor write strobe. Active low. Connection of a 10-kΩ pull-up resistor is optional.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# detailed description

The TLV1562 analog-to-digital converter is based on an advanced low power recyclic architecture. Two bits of the conversion result are presented per system clock cycle. A total of 5 system clock (SYSCLK) cycles is required to complete the conversion. The serial conversion results are converted to a parallel word for output. The device supports both interrupt-driven (typically found in a SAR type ADC) and continuous (natural for a pipeline type ADC) modes of conversion. An innovative conversion scheme makes this device perfect for power sensitive applications with uncompromised speed.

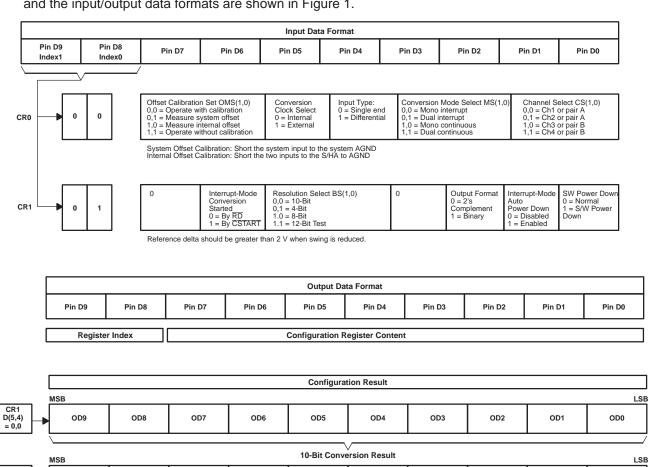

# control register

The TLV1562 is software configurable. The first two bits, MSBs (D9,8), are used to address the register set. The rest of the 8 bits are used as data. There are two control registers, CR0 and CR1, for user configuration. All of these register bits are written to the control register during a write cycle. A description of the control registers and the input/output data formats are shown in Figure 1.

NOTE: Z indicates bits write zero read zero back.

OD2

OD6

OD1

OD5

ODO

OD4

OD3

OD7

MSB

CR1

D(5,4) = 1,0

Figure 1. Input/Output Data Formats

z

OD3

z

OD2

4-Bit Conversion Result

8-Bit Conversion Result

z

OD1

z

OD0

z

Z

z

Z

LSB

### NOTE:

Channel select bits CR0.(1,0), CS(1,0) are ignored when the device is in the dual (interrupt or continuous) modes using differential inputs, since both differential input pairs are automatically selected. CR0.0 (i.e., CS0 bit) is used to determine if channels 1 and 3 or channels 2 and 4 are selected if single-ended input mode is used.

# detailed description (continued)

**Table 1. Select Input Channels**

| CR0.4<br>(INPUT TYPE) | CR0.(3,2)<br>(CONVERSION MODE<br>SELECT) | CR0.(1,0)<br>(CHANNEL SELECT) | CHANNEL(S)<br>SELECTED          | NOTE           |

|-----------------------|------------------------------------------|-------------------------------|---------------------------------|----------------|

| 0 (Single-ended)      | 00 or 10                                 | 0,0                           | CH1                             | Single channel |

| 0 (Single-ended)      | 00 or 10                                 | 0,1                           | CH2                             | Single channel |

| 0 (Single-ended)      | 00 or 10                                 | 1,0                           | CH3                             | Single channel |

| 0 (Single-ended)      | 00 or 10                                 | 1,1                           | CH4                             | Single channel |

| 1 (Differential)      | 00 or 10                                 | 0,X                           | Differential pair A             | Single channel |

| 1 (Differential)      | 00 or 10                                 | 1,X                           | Differential pair B             | Single channel |

| 0 (Single-ended)      | 01 or 11                                 | X,0                           | Both CH1 and CH3                | Dual channels  |

| 0 (Single-ended)      | 01 or 11                                 | X,1                           | Both CH2 and CH4                | Dual channels  |

| 0 (Single-ended)      | 01 or 11                                 | X,0                           | Both CH1 and CH3                | Dual channels  |

| 0 (Single-ended)      | 01 or 11                                 | X,1                           | Both CH2 and CH4                | Dual channels  |

| 1 (Differential)      | 01 or 11                                 | X,X                           | Both differential pairs A and B | Dual channels  |

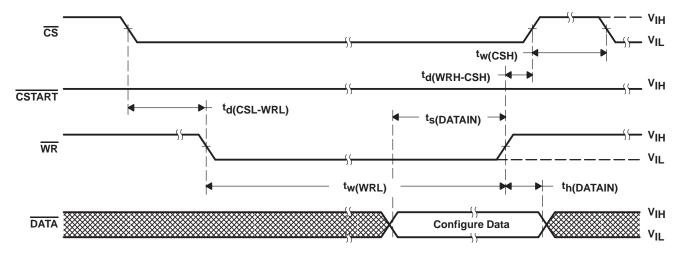

# configure the device

The device can be configured by writing to control registers CR0 and CR1. A read register is carried out by auto-sequence when the device is put into the software power-down state. CR0 is read first and then CR1 at the next two  $\overline{RD}$  rising edges after the device is in the software power-down state. The falling edge of  $\overline{RD}$  has no meaning and does not trigger a conversion in the software power-down state.

Figure 2. Configuration Cycle Timing

# detailed description (continued)

The following examples show how to program configuration registers CR0 and CR1 for different settings.

# Example 1:

| REGISTER | IND | EX |    |    |    |    |    |    |    |                                                   | COMMENT                                        |

|----------|-----|----|----|----|----|----|----|----|----|---------------------------------------------------|------------------------------------------------|

| REGISTER | D9  | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0                                                | COMMENT                                        |

| CR0      | 0   | 0  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0                                                 | Mono interrupt mode, use RD, write 0D0h to ADC |

| CR1      | 0   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 0 Use 2s complementary output, use RD, write 10 |                                                |

## Example 2:

| •   |   |   |   |   |   |   |   |   |   |   |                                                    |

|-----|---|---|---|---|---|---|---|---|---|---|----------------------------------------------------|

| CR0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | Mono interrupt mode, use CSTART, write 0D0h to ADC |

| CR1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | Use 2s complementary output, write 144h to ADC     |

# Example 3:

| _ |     |   |   |   |   |   |   |   |   |   |   |                                                         |

|---|-----|---|---|---|---|---|---|---|---|---|---|---------------------------------------------------------|

|   | CR0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | Dual interrupt mode, use CSTART only, write 0D4h to ADC |

| ſ | CR1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | Use 2s complementary output, write 144h to ADC          |

# Example 4:

|   | CR0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | Mono continuous mode, use RD only, write 0D8h to ADC |

|---|-----|---|---|---|---|---|---|---|---|---|---|------------------------------------------------------|

| ľ | CR1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Use 2s complementary output, write 104h to ADC       |

# Example 5:

| _ | <u> </u> |   |   |   |   |   |   |   |   |   |   |                                                      |

|---|----------|---|---|---|---|---|---|---|---|---|---|------------------------------------------------------|

|   | CRO      | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | Dual continuous mode, use RD only, write 0DCh to ADC |

|   | CR1      | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | Binary output, write 104h to ADC                     |

# analog input

## input types

The four analog inputs can be configured as two pairs of differential inputs or four single-ended inputs by setting the control register 0 bit 4 input type selection (dual or single channel).

# differential input (CR0.4=1)

Up to two channels are available when the TLV1562 is programmed for differential input. The output data format is bipolar when the device is operated in differential input mode.

# single-ended input (CR0.4=0)

Up to four channels are available when the TLV1562 is programmed for single-ended input. The output data format is unipolar when the device is operated in single-ended input mode.

# detailed description (continued)

# input signal range

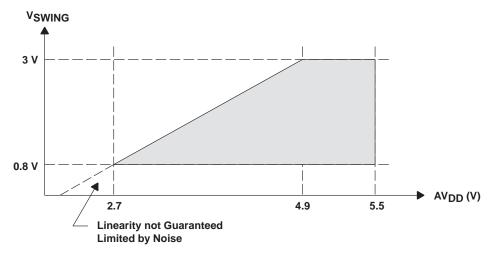

The analog input signal range for a specific supply voltage  $AV_{DD}$  ranges from  $(AV_{DD} - 1.9 \text{ V})$  to 0.8 V.

Figure 3. Analog Input Range vs AVDD

$$VREFCM + 0.5 \times V_{SWING} \le AV_{DD} - 1 V$$

$VREFCM - 0.5 \times V_{SWING} \ge 0.8 V$

### Where:

VREFCM = (VREFP + VREFM)/2 is the common mode reference voltage.

V<sub>SWING</sub> = dynamic range of the input signal,

$V_{SWING} = VINP - VINM$ ,

And the common mode input voltage is:

VINCM = (VINP + VINM)/2,

MAX

$$V_{SWING} = MIN [(AV_{DD} - 1.9 V), 3 V]$$

For single-ended input, the analog input range is between VREFP and VREFM. So the range of single-ended VIN is:

$$3 \text{ V}$$

if  $AV_{DD} = 3 \text{ V}$

$1 \text{ V}$  if  $AV_{DD} = 3 \text{ V}$

$0.8 \text{ V}$  if  $AV_{DD} = 2.7 \text{ V}$

For differential input, the input common mode voltage VINCM can be between AV<sub>DD</sub> and AGND as long as  $3 \text{ V} \ge (\text{VINP-VINM}) \ge 0.8 \text{ V}$ .

This means VINCM ≥ 0.4 V.

So the range of differential analog input voltage, (VINP–VINM) is:

$$3 \text{ V}$$

if  $AV_{DD} = 3 \text{ V}$

$1 \text{ V}$  if  $AV_{DD} = 3 \text{ V}$

$0.8 \text{ V}$  if  $AV_{DD} = 2.7 \text{ V}$

# detailed description (continued)

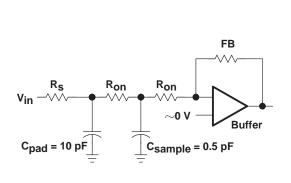

# equivalent input impedance

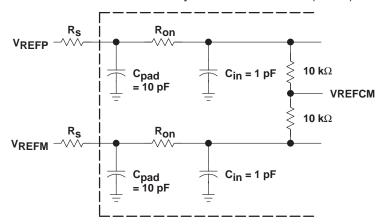

Figure 4. Equivalent Input Circuit

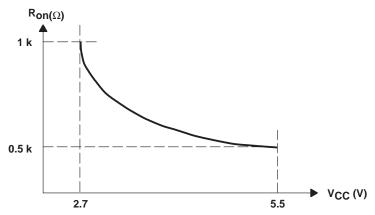

Figure 5. Input Mux On Resistance vs Analog Supply Voltage

Req = Vin/leq = (Q/Cin)/(Q/T) = T/Cin =  $1/(fs \times Csample)$  =  $1/(2 MHz \times 0.5 pF)$  =  $1 M\Omega$

Where f<sub>s</sub> is the sampling frequency, and f<sub>c</sub> is the conversion frequency

$f_S = f_C/5$  when the device is in one channel/continuous conversion mode,

$f_s = f_c/10$  when the device is in one channel/continuous conversion mode,

$f_S$  = Conversion trigger strobe frequency when the device is in interrupt mode ( $\overline{RD}$  or  $\overline{CSTART}$ )

Csample = Input capacitance = 0.5 pF

Cparasitic = Parasitic capacitance = 0.5 pF

Cpad = Input PAD capacitance = 10 pF

Ron = Mux switch on series resistance = 1 k $\Omega$  at 2.7 V

Rs = Source output resistance =  $1 \text{ k}\Omega$

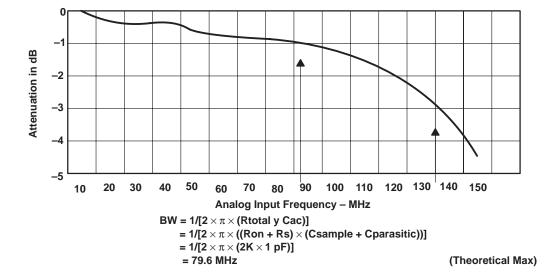

# input bandwidth (full power 0 dB input, BW at -1 dB)

Figure 6. Typical Analog Input Frequency Input Bandwidth

SLAS162 - SEPTEMBER 1998

# reference voltage inputs

The TLV1562 has two reference input pins: REFP and REFM. The voltage levels applied to these pins establish the upper and lower limits of the analog inputs to produce a full-scale and zero-scale reading respectively. The values of VREFP, VREFM, and the analog input should not exceed the positive supply or be less than GND consistent with the specified absolute maximum ratings. The digital output is at full scale when the input signal is equal to or higher than VREFP and is at zero when the input signal is equal to or lower than VREFM. The internal resistance from VREFP to VREFM may be as low as  $20 \text{ k}\Omega$  ( $\pm 10\%$ ).

The reference voltages must satisfy the following conditions:

$\begin{array}{l} \text{VREFP} \leq \text{AV}_{DD} - 1 \text{ V}, \\ \text{AGND} + 0.9 \text{ V} < \text{VREFM and} \\ \text{3 V} \geq (\text{VREFP} - \text{VREFM}) \geq 0.8 \text{ V} \\ \end{array}$

Figure 7. Equivalent Circuit for Reference input

# sampling/conversion

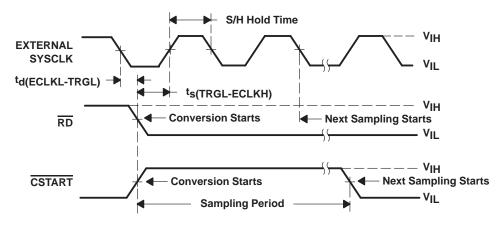

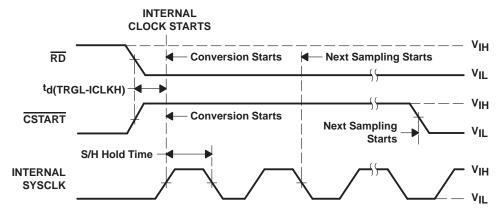

All of the sampling, conversion, and data output in the device are started by a trigger. This trigger can be the  $\overline{RD}$  or  $\overline{CSTART}$  signal depending on the mode of conversion and configuration. The falling edge of the  $\overline{RD}$  signal and the rising edge of the  $\overline{CSTART}$  signal are extremely important since they are used to start the conversion. These edges need to stay as close to the falling edges of the external clock, if they are used as SYSCLK. The minimum setup time with respect to the rising edge of the external SYSCLK should be 5 ns minimum. When the internal SYSCLK is used, this is not an issue, since these two edges start the internal clock automatically; therefore, the setup time is always met.

### **USING EXTERNAL CLOCK**

Figure 8. Conversion Trigger Timing – External Clock

## **USING INTERNAL CLOCK**

Figure 9. Conversion Trigger Timing – Internal Clock

# TLV1562

# 2.7 V TO 5.5 V, HIGH-SPEED LOW-POWER RECONFIGURABLE ANALOG-TO-DIGITAL CONVERTER WITH 4-INPUT, DUAL S/H, PARALLEL INTERFACE, AND POWER DOWN

SLAS162 - SEPTEMBER 1998

# Table 2. Conversion Trigger Edge

| CONVERSION<br>MODE | CONVERSION<br>TRIGGER | START OF<br>SAMPLING           | START OF<br>CONVERSION | CONVERSION<br>TIME<br>(INTERNAL CLK) | CONVERSION<br>TIME<br>(EXTERNAL CLK) | INTERRUPT<br>CANCELED<br>BY | DATA OUT            |

|--------------------|-----------------------|--------------------------------|------------------------|--------------------------------------|--------------------------------------|-----------------------------|---------------------|

| Mono<br>Interrupt  | RD                    | WR ↑‡ or<br>2 SYSCLK from RD ↓ | RD↓                    | 6 SYSCLK                             | 5 SYSCLK                             | RD ↑                        | 41 ns§ from INT low |

|                    | CSTART†               | CSTART ↓                       | CSTART ↑               | 6 SYSCLK                             | 5 SYSCLK                             | RD ↓                        | 41 ns§ from RD low  |

| Dual<br>Interrupt  | CSTART                | CSTART ↓                       | CSTART ↑               | 12 SYSCLK                            | 10 SYSCLK                            | First RD ↓                  | 41 ns§ from RD low  |

| Mono<br>Continuous | RD                    | WR ↑‡ or<br>2 SYSCLK from RD ↓ | RD↓                    | 6 SYSCLK                             | 5 SYSCLK                             | N/A                         | 41 ns§ from RD low  |

| Dual<br>Continuous | RD                    | WR ↑‡ or<br>7 SYSCLK from RD ↓ | RD↓                    | 12 SYSCLK                            | 10 SYSCLK                            | N/A                         | 41 ns§ from RD low  |

<sup>†</sup> CSTART works with or without CS active.

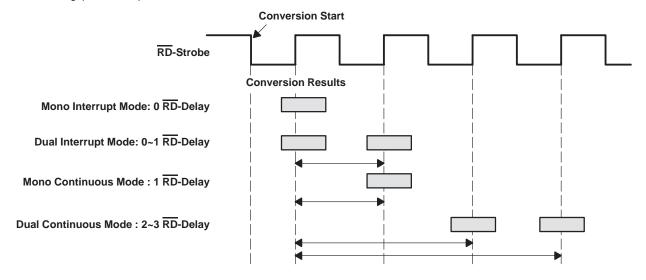

The TLV1562 provides four types of conversion modes. The two interrupt-driven conversion modes are asynchronous and are simple one-shot conversions. The auto-powerdown conversion feature can be enabled when interrupt-driven conversion modes are used. The other two continuous conversion modes are synchronous with the  $\overline{RD}$  signal (as a clock) from the processor and are more suitable for repetitive signal measurement. These different modes of conversion offer a tradeoff between simplicity and speed.

<sup>&</sup>lt;sup>‡</sup> The first sampling period starts at the last RD low of the previous cycle or WR high of the configuration cycle. RD low is the falling edge of RD and WR high is the rising edge of the WR signal. (Minimum sample/hold amp settling time = one SYSCLK, approximately 100 ns min, at Rs ≤ 1 kΩ).

<sup>§</sup> Output data enable time is dependent on bus loading and supply voltage (BDV<sub>DD</sub>). For BDV<sub>DD</sub> = 5 V, the enable time is 19 ns at 25 pF, 23 ns at 50 pF, and 25 ns at 100 pF. For BDV<sub>DD</sub> = 2.7 V, the enable time is 37 ns at 25 pF, 41 ns at 50 pF, and 56 ns at 100 pF.

# detailed description (continued)

Table 3. Maximum Conversion Speed (for 1 LSB INL and DNL at 10 bit)

|                                        |                             |           | MAXIMUM CONVERS            | SION THROUGHPUT†          |

|----------------------------------------|-----------------------------|-----------|----------------------------|---------------------------|

| CONVERSION                             | N MODE                      | CR0.(3,2) | EXTERNAL CLOCK<br>(10 MHz) | INTERNAL CLOCK<br>(8 MHz) |

|                                        | RD                          |           | 1.5 MSPS                   | 1.1 MSPS                  |

| Mono interrupt-driven conversion mode  | RD with auto power down     | 00        | 0.82 MSPS                  | 0.68 MSPS                 |

| Mono interrupt-anven conversion mode   | CSTART                      |           | 1.5 MSPS                   | 1.1 MSPS                  |

|                                        | CSTART with auto power down |           | 0.82 MSPS                  | 0.68 MSPS                 |

| Dual interrupt-driven conversion mode‡ | CSTART                      | 01        | 1.5 MSPS                   | 0.91 MSPS                 |

| Duai interrupt-driven conversion mode+ | CSTART with auto power down | ] "       | 1.05 MSPS                  | 0.83 MSPS                 |

| Mono continuous conversion mode        | RD                          | 10        | 2 MSPS§                    | 1.33 MSPS§                |

| Dual continuous conversion mode        | RD                          | 11        | 2 MSPS¶                    | 1.33 MSPS¶                |

<sup>†</sup> Speed is calculated for 5-V with a 2-V reference

<sup>¶</sup> Combined throughputs from a pair of selected channels.

Figure 10. Digital Delays for Different Conversion Modes

<sup>(5.5</sup> V to 3 V, I-temperature and C-temperature: 2 MSPS at 10 bit, 3 MSPS at 8 bit, 7 MSPS at 4 bit;

<sup>3</sup> V to 2.7 V, C-temperature: 2 MSPS at 10 bit, 2.5 MSPS at 8 bit, 7 MSPS at 4 bit;

<sup>3</sup> V to 2.7 V, I-temperature: 1.6 MSPS at 10 bit, 2.5 MSPS at 8 bit, 7 MSPS at 4 bit).

Higher throughput is possible when the linearity requirement is relaxed.

<sup>&</sup>lt;sup>‡</sup> Dual interrupt mode is available to 8-bit or 10-bit resolution and single-ended input type.

<sup>§</sup> Throughput from single selected channel.

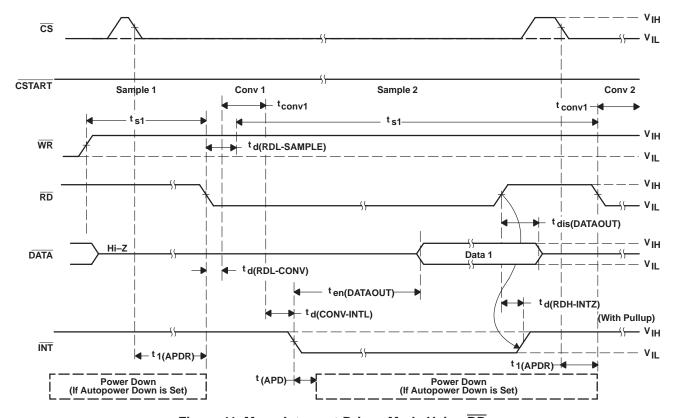

# mono interrupt-driven mode (CR0.(3,2) = 0,0)

The mono interrupt-driven conversion mode provides a one-shot conversion. Sampling, conversion, and data output are all performed in a single cycle. The analog signal is sampled 2 SYSCLKs after the falling edge of  $\overline{RD}$  (or the rising edge of  $\overline{WR}$  if this is the first sample after configuration) and then converted on the falling edge of  $\overline{RD}$ . Once the data is ready,  $\overline{INT}$  falls and the data is output to the bus. The rising edge of  $\overline{RD}$  cancels  $\overline{INT}$  and initiates a read of the data. The data bus is 3-stated when  $\overline{RD}$  goes high. It is not necessary to configure the converter for each cycle or toggle  $\overline{CS}$  between cycles.

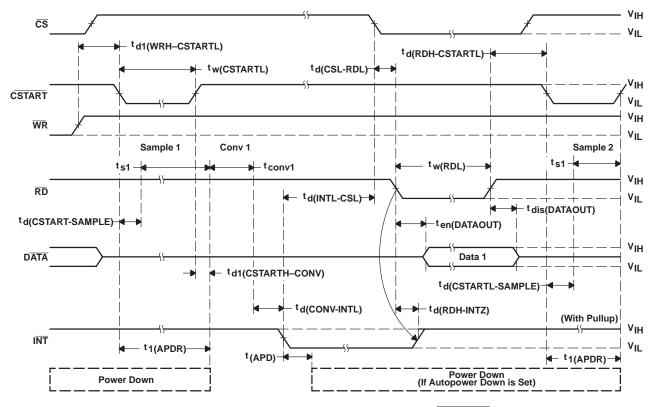

Figure 11. Mono Interrupt-Driven Mode Using RD

Conversion can also be started with CSTART. This is useful when an application requires multiple TLV1562s for simultaneous samplings and conversions. The falling edge of CSTART starts the sampling and the rising edge of CSTART starts the conversion. Once the data is ready INT falls. INT is terminated by the following falling edge of RD which also outputs the data to the bus. On the rising edge of RD, the data is read and the data bus is 3-stated.

Figure 12. Mono Interrupt-Driven Mode Using CSTART

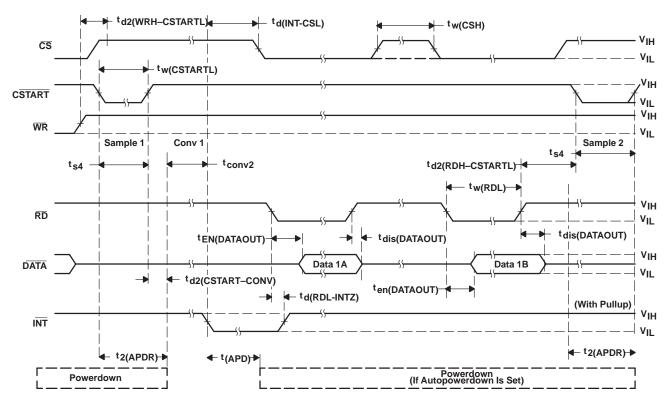

# dual interrupt-driven mode (CR0.(3,2) = 0,1)

The dual interrupt-driven conversion mode provides a similar one-shot conversion, sampling, and conversion but also samples both selected channels simultaneously. Conversion can only be started with the  $\overline{CSTART}$  signal. The falling edge of  $\overline{CSTART}$  starts the sampling of both of the input channels selected, and the rising edge of  $\overline{CSTART}$  starts the conversion. Since it takes two consecutive conversions internally, the conversion time required is doubled (10 SYSCLK cycles). Once the data are ready,  $\overline{INT}$  falls.  $\overline{INT}$  is terminated by the first falling edge of  $\overline{RD}$ , which also outputs the first data to the bus. On the rising edge of  $\overline{RD}$ , data is read and the data bus is 3-stated. The second  $\overline{RD}$  falling edge outputs the second data to the bus and then reads it on the rising edge and 3-states the bus. It is not necessary to configure the converter for each cycle or toggle  $\overline{CS}$  between cycles.

**NOTE:** Dual interrupt mode is available to 10-bit or 8-bit resolution and single-ended input type.

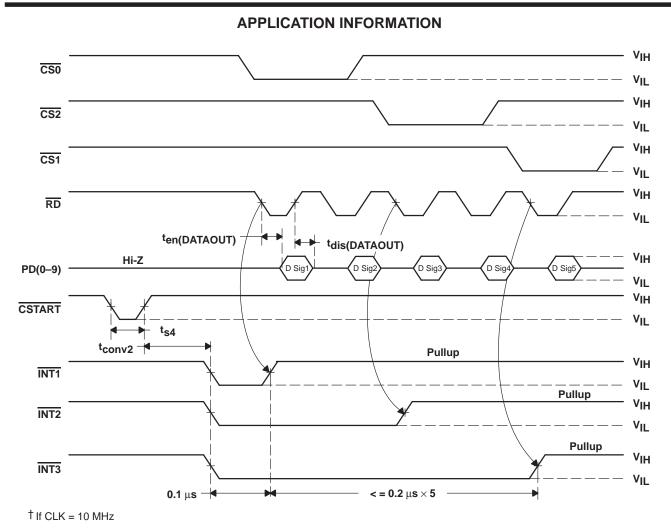

Figure 13. Dual Interrupt Conversion Mode (Conversion can only be started with CSTART for the dual interrupt mode)

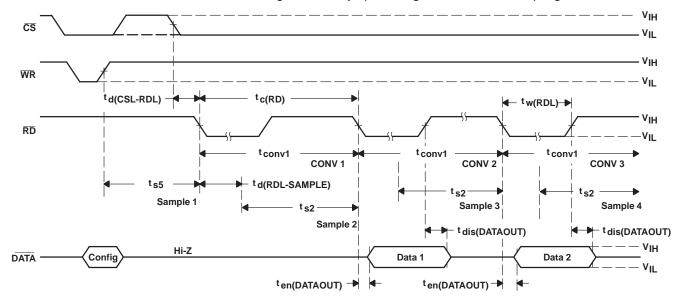

# mono continuous mode (CR0.(3,2) = 1,0)

The mono continuous mode of conversion is synchronous with the  $\overline{RD}$  signal. Its cycle time is approximately 5 SYSCLK cycles when an external SYSCLK is used (6 SYSCLK cycles when an internal SYSCLK is used). In the mono continuous mode, the TLV1562 is always sampling the input regardless of the state of other control signals when it is not in the hold state (the first half SYSCLK cycle after each falling edge of  $\overline{RD}$ ). This simplifies control of the ADC. There is no need to generate any special signal to start the sampling.

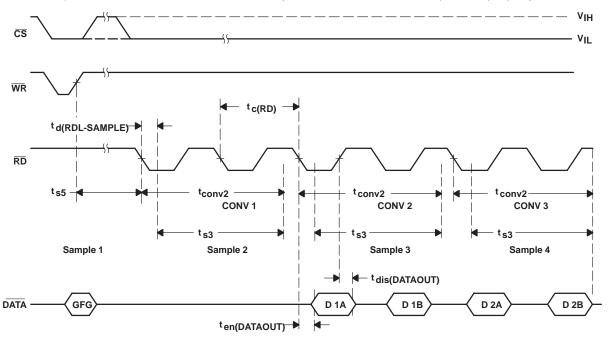

Figure 14. Mono Continuous Mode

# dual continuous mode (CR0.(3,2) = 1,1)

When the TLV1562 operates in the dual continuous mode, it samples and then holds two preselected channels (differential or single ended) simultaneously as  $\overline{\text{RD}}$  clocks. These samples are then converted in sequence. This is designed to optimize the DSP MIPS for communication applications. Its cycle time is approximately 10 SYSCLK cycles when an external SYSCLK is used (12 SYSCLK cycles when an internal SYSCLK is used). When operating in the dual continuous mode, the TLV1562 is always sampling the input regardless of the state of the other control signals when it is not in the hold state. This simplifies control of the ADC. There is no need to generate any special signal to start the sampling. The TLV1562 goes into hold mode on the odd number (starting from the rising edge of  $\overline{\text{WR}}$ ) falling edge of  $\overline{\text{RD}}$  for one SYSCLK clock cycle.

A two-depth FIFO is used (only in the dual continuous mode) to ensure the output correlation. Thus on every alternate  $\overline{\text{RD}}$  edge, the result of the previous two conversions is read out. This allows a slower  $\overline{\text{RD}}$  clock frequency (slower than 1/5 of the SYSCLK frequency). Each dual continuous mode cycle (while  $\overline{\text{CS}}$  remains active low) must have an even number of  $\overline{\text{RD}}$  cycles to ensure the FIFO operates properly.

Figure 15. Dual Continuous Mode

# system clock source

The TLV1562 uses multiple clocks for different internal tasks. SYSCLK is used for most conversion subtasks. The source of SYSCLK is programmable via control register 0, bit 5 (CR0.5). The source of SYSCLK is changed at the rising edge of WR of the cycle when CR0.5 is programmed.

# internal oscillator (CR0.5 = 0, SYSCLK = internal OSC)

The TLV1562 has a built-in 8-MHz oscillator. When the internal OSC is selected as the source of SYSCLK, the internal clock starts with a delay (one half of the OSC clock period max) after the falling edge of the conversion trigger (RD or CSTART).

# external clock input (CR0.5 = 1, SYSCLK = External Clk)

The TLV1562 is designed to operate with an external clock input (CMOS/TTL) with a frequency from 100 kHz to 14 MHz. When an external clock is used as the source of SYSCLK, the setup time from the falling edge of RD to the rising edge of SYSCLK, ts(TRGL-ECLKH) is 5 ns minimum. The internal OSC is shut down when the external clock mode is selected.

# host processor interface

## parallel processor interface

The TLV1562 provides a generic high-speed parallel interface that is compatible with high-performance DSPs and general-purpose microprocessors. These include D(0,9),  $\overline{RD}$ ,  $\overline{WR}$ , and  $\overline{INT}$ .  $\overline{RD}$  transitions from high to low to signal the end of acquisition. The parallel I/O has its own power supply to minimize digital noise.

# output data format

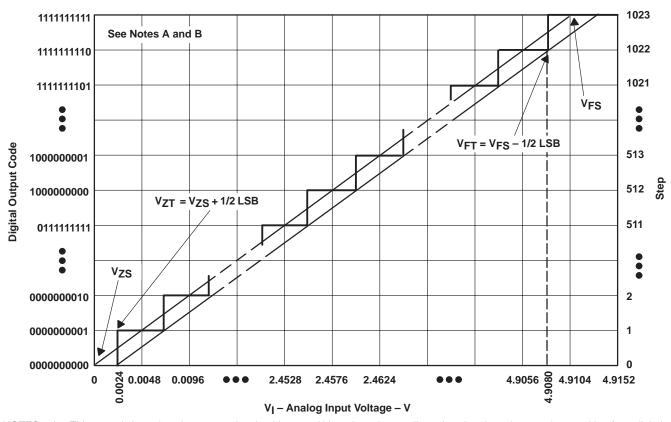

The output data format is unipolar binary (1023 to 0) when the device is operated in the single-ended input mode and is bipolar (511 to –512) when the device is operated in differential input mode. The output code format can be either binary or 2s compliment. The output data format is controlled by CR1.2.

# power down

The device offers two different power-down modes: Auto power-down mode for interrupt-driven conversions and software power-down mode for all conversion modes. All configuration information is kept intact when the device is in software or auto power-down mode.

# auto-power down for interrupt-driven conversion modes

When auto-power down is enabled, the device turns off the analog section (the converter except for the reference network) at the falling edge of  $\overline{\text{INT}}$  and resumes after the falling edge of  $\overline{\text{CS}}$  (if  $\overline{\text{RD}}$  is the conversion trigger) or  $\overline{\text{CSTART}}$  (if  $\overline{\text{CSTART}}$  is the conversion trigger). The reference current and I/O are kept alive to ensure a fast recovery. Average power consumption can be reduced by accessing the converter less often. Special requirements for using this feature are:

- It is necessary to toggle  $\overline{CS}$  between cycles so the converter knows when to resume.

- There is an additional delay to a conversion after the device is accessed due to the auto-power-down control. Therefore, the time between RD (or CSTART) triggers is longer (longer RD or CSTART high time).

# software power down (CR.10 = 1, software power down enabled)

In addition to the auto-power-down feature, the device has a software powerdown feature to further reduce power consumption when the device is idle. Writing a 1 to control register bit CR1.0 puts the TLV1562 into software power-down mode in 200 ns after  $\overline{\text{CS}}$  is up. The device consumes less than 1  $\mu$ A when in the power-down mode. Writing a 0 to control register bit CR1.0 wakes up the device. Conversion can start 1  $\mu$ s after the device is resumed.  $\overline{\text{CS}}$  must be high when the device is in power-down mode. Software power-down operation is slower than auto-power down but is more flexible and consumes almost no power.

SLAS162 - SEPTEMBER 1998

### Table 4. TLV1562 Powerdown Features

| FUNCTION BLOCK/POWERDOWN MODE   | SOFTWARE F                | POWERDOWN                 | AUTO POV | VERDOWN  |

|---------------------------------|---------------------------|---------------------------|----------|----------|

| DIGITAL CONTROL VOLTAGE LEVEL   | CMOS                      | TTL                       | CMOS     | TTL      |

| Converter analog section        | Inactive                  | Inactive                  | Inactive | Inactive |

| Reference current (amps)        | Inactive                  | Inactive                  | Active   | Active   |

| Digital I/O buffers             | Active                    | active                    | Active   | Active   |

| Estimated supply current, ICC   | 1 μΑ                      | 80 μΑ                     | 120 μΑ   | 200 μΑ   |

| Power-down time                 | 200 ns                    | 200 ns                    | 200 ns   | 200 ns   |

| Resume time                     | 1 μs                      | 1 μs                      | 700 ns   | 700 ns   |

| Maximum throughput <sup>†</sup> | 1.2/0.7 MSPS <sup>‡</sup> | 1.2/0.7 MSPS <sup>‡</sup> | 1 MSPS   | 1 MSPS   |

<sup>†</sup> Dual interrupt, 10-bit, 5-V AVDD, 10-MHz external clock, and 2 V (REFP-REFM).

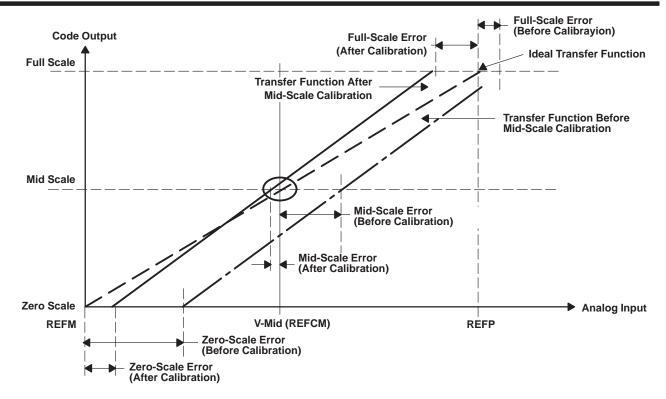

### mid-scale error calibration

The device has a  $\pm 5\%$  maximum full-scale error, mid-scale error, and zero-scale error due to the gain error in the sample and hold amplifier.

The TLV1562 is capable of calibrating the mid-scale error. There are two calibration modes: system mid-scale error calibration and internal mid-scale error calibration as described below.

### NOTE:

Set register CR0.(7,6) = 1,1 when the device is not in mid-scale error calibration mode.

These mid-scale error calibrations affect the ADCs transfer characteristics as shown in Figure 16. The absolute error at code 512 is zero-out (this is the reference point for mid-scale error calibration). The calibration also makes the FS error and ZS error equal.

# internal mid-scale error calibration (CR0.(7,6) = 1,0)

The internal mid-scale error calibration mode is set by writing to the configuration registers with CR0.(7,6) set to 10. The ADC analog inputs are internally shorted to mid-voltage (REFP+REFM)/2 when the mid-scale error calibration mode is enabled. One conversion (initiated by the falling edge of  $\overline{\text{RD}}$ ) is performed to calculate the offset. The result of this conversion is stored in the mid-scale error register and is subtracted from all subsequent conversions thus removing any offset. Internal calibration removes any offsets internal to the device. Internal mid-scale error calibration reduces the mid-scale error to  $\pm 2.5\%$  FS single ended inputs (0.3% FS differential inputs).

# system mid-scale error calibration (CR0.(7,6) = 0,1)

System mid-scale error calibration is set by writing to the configuration registers with CR0.(7,6) set to 01. The analog input to be calibrated is externally connected to the voltage corresponding to mid-code. For differential operation, this is achieved by shorting the two inputs together; for a single-ended input this is achieved by connecting the analog input to the system mid-voltage, (SYSTEM\_REFP + SYSTEM\_REFM)/2. One conversion (initiated by  $\overline{\text{RD}}$  falling edge) is performed to calculate the offset. The result of this conversion is stored in the mid-scale error register and is subtracted from all subsequent conversions thus removing any offset. System mid-scale error calibration removes the offset of not only the ADC but any offsets in the entire analog circuitry driving the ADC input. System mid-scale error calibration reduces the mid-scale error to  $\pm 0.4\%$  FS single ended inputs (0.25% FS differential inputs).

<sup>&</sup>lt;sup>‡</sup> This assumes the TLV1562 is software powered down between every cycle. In reality this is not the case since auto-power down makes much more sense in this case. So the realistic maximum throughput for software power down will be close to the maximum throughput without powerdown which is 1.2 MSPS for dual-interrupt mode (and 1.5 MSPS if mono-interrupt mode is used). But this really depends on how long the device is powered down.

Figure 16. Mid-Scale Error Calibration

# resume normal conversion from mid-scale error calibration modes

A follow on write operation sets CR0.(7,6) to 00 which resumes the normal conversion mode. Typically mid-scale error calibration needs to be performed only once after power up. If however the operation mode is changed from single ended to differential, then preferably mid-scale error calibration should be performed again.

The user writes a bit to enable mid-scale error calibration. Inputs to the ADC are internally shorted therefore the offset value can be converted to a digital word. The result (a digital word representing the offset) is stored in a latch. This offset value is then subtracted from the digital output of all conversions except when in mid-scale error calibration mode.

## system design consideration regarding to mid-scale error calibration

Mid-scale error calibration may limit the dynamic range of the ADC. If the offset is negative and has a magnitude x, then the range of the converter codes is x to 1023. If the offset is positive and has a magnitude of x, then the range of converter codes is 1 to 1023 –x. Thus the ADCs dynamic range is reduced by x (say x = 20 codes) on either side of the range effectively with mid-scale error calibration. However this should not be a limitation for most users.

# **APPLICATION INFORMATION**

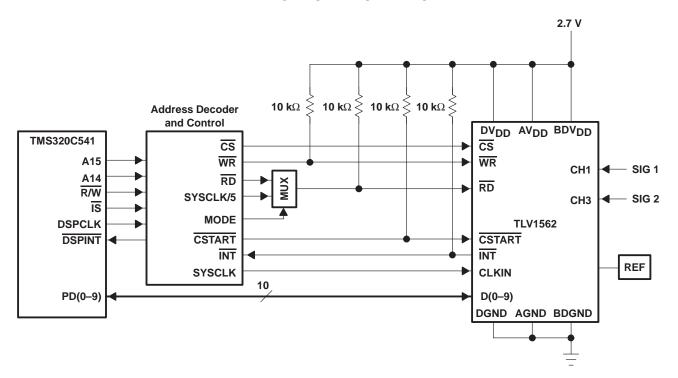

Figure 17. Typical Interface to a TMS320 DSP

# **APPLICATION INFORMATION**

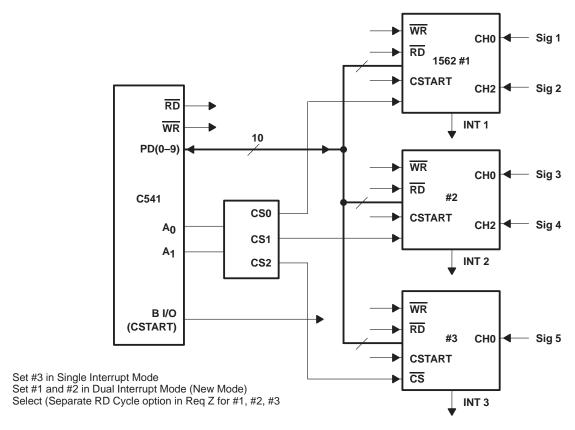

Figure 18. Multiple Chips Simultaneous Sampling/Conversion Application

Figure 19. Multiple Chips Simultaneous Sampling/Conversion Application System Timing

SLAS162 - SEPTEMBER 1998

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range: AV <sub>DD</sub> (see Note 1)                 |                                    |

|---------------------------------------------------------------------|------------------------------------|

| BDV <sub>DD</sub> , DV <sub>DD</sub> (see Note 2)                   |                                    |

| AV <sub>DD</sub> to DV <sub>DD</sub> or BDV <sub>DD</sub>           |                                    |

| Voltage range between AGND and DGND or BDGND                        |                                    |

| Digital input voltage range, CLKIN, CS, WR, RD, CSTART (see Note 2) | –0.3 V to DV <sub>DD</sub> +0.3 V  |

| Digital data input voltage range (see Note 2)                       | –0.3 V to DV <sub>DD</sub> +0.3 V  |

| Digital data output voltage range (see Note 2)                      | –0.3 V to DV <sub>DD</sub> +0.3 V  |

| Analog output voltage range, INT (see Note 2)                       | 0.1 V to AV <sub>DD</sub> + 0.1 V  |

| Reference input voltage range, REFP (see Note 1)                    | –0.1 V to AV <sub>DD</sub> + 0.1 V |

| Reference input voltage range, REFM (see Note 1)                    |                                    |

| Peak input current (any input)                                      |                                    |

| Peak total input current (all inputs)                               | –30 mA                             |

| Operating free-air temperature range, T <sub>A</sub> : TLV1562C     | –0°C to 70°C                       |

| TLV1562I                                                            | –40°C to 85°C                      |

| Storage temperature range                                           | 65°C to 150°C                      |

| Lead temperature 1,6 mm (1/16 inch) from the case for 10 seconds    | 260°C                              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Measured with respect to AGND with REF - and GND wired together (unless otherwise noted).

# recommended operating conditions

| PARAMETE                                                                          | RS              | MIN                                      | NOM MAX                        | UNIT |

|-----------------------------------------------------------------------------------|-----------------|------------------------------------------|--------------------------------|------|

| Supply voltage, AV <sub>DD</sub> , BDV <sub>DD</sub> , DV <sub>DD</sub> (see Note | 3)              | 2.7                                      | 5.5                            | V    |

| Positive external reference voltage input, VREFP                                  | AGND +1.7       | AV <sub>DD</sub> – 1                     | V                              |      |

| Negative external reference voltage input, VREFM                                  | // (see Note 4) | AGND +0.9                                | AV <sub>DD</sub> – 1           | V    |

| Differential reference voltage input, (VREFP–VRE                                  | 0.8             | MIN of<br>AV <sub>DD</sub> – 1.9<br>or 3 | V                              |      |

| Single-ended analog input voltage, (AIN – AGND)                                   | VREFM           | VREFP                                    | V                              |      |

| Differential analog input voltage, (AINP-AINM)                                    | 0.8             | 3                                        | V                              |      |

| Common mode analog input voltage, (AINP+AINN                                      | AGND            | $AV_{DD}$                                | V                              |      |

| External SYSCLK 40/60 cycle time, t <sub>C(EXTSYSCI</sub>                         | 0.067           | 1                                        | μs                             |      |

| External SYSCLK pulse duraton high, twH(EXTS)                                     | 40%             | 60%                                      | t <sub>C</sub> (EXT<br>SYSCLK) |      |

| External SYSCLK pulse duration low, twL(EXTSY                                     | 40%             | 60%                                      | t <sub>C</sub> (EXT<br>SYSCLK) |      |

| High-level digital and control input voltage, VIH                                 | 2.1             |                                          | V                              |      |

| Low-level digital and control input voltage, VIL                                  |                 | 0.8                                      | V                              |      |

| Operating free air temperature T.                                                 | TLV1562C        | 0                                        | 70                             | °C   |

| Operating free-air temperature, TA                                                | TLV1562I        | -40                                      | 85                             |      |

NOTES: 3. The absolute difference between AVDD, BDVDD and DVDD should be less than 0.5 V.

<sup>2.</sup> Measured with respect to DGND.

<sup>4.</sup> Analog input voltages greater than that applied to VREFP convert as all ones (11111111111), while input voltages less than that applied to VREFM convert as all zeros (00000000000).

SLAS162 - SEPTEMBER 1998

electrical characteristics over recommended operating free-air temperature range, differential input,  $AV_{DD} = DV_{DD} = BDV_{DD} = 3$  V, VREFP – VREFM = 1 V, external SYSCLK = 10 MHz (unless otherwise noted)

| PARAMETER       |                                                               | TEST CONDITIONS                                                                                      | MIN                    | TYP    | MAX  | UNIT  |  |  |

|-----------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------|--------|------|-------|--|--|

| \/a             | Digital high-level output voltage                             | $BDV_{DD} = 5.5 \text{ V},  I_{OH} = -0.2 \text{ mA}$                                                | 2.4                    |        |      | V     |  |  |

| VOH             | Digital high-level output voltage                             | BDV <sub>DD</sub> = 2.7 V, $I_{OH} = -20 \mu A$                                                      | BDV <sub>DD</sub> -0.1 |        |      | V     |  |  |

| \/o.            | Digital low-level output voltage                              | $BDV_{DD} = 5.5 \text{ V},  I_{OL} = 0.8 \text{ mA}$                                                 |                        |        | 0.4  | V     |  |  |

| VOL             | Digital low-level output voltage                              | $BDV_{DD} = 2.7 \text{ V},  I_{OL} = 20 \mu\text{A}$                                                 | 0.                     |        |      |       |  |  |

| lo-             | Off-state output current                                      | $V_O = BDV_{DD}$ , $\overline{CS} = BDV_{DD}$                                                        |                        | 0.005  | 1    | μА    |  |  |

| loz             | (high-impedance state)                                        | $V_O = BDGND$ , $\overline{CS} = BDV_{DD}$                                                           | -1                     | -0.005 |      | μΑ    |  |  |

| l <sub>IH</sub> | High-level input current                                      | $V_I = BDV_{DD}$                                                                                     |                        | 0.005  | 1    | μΑ    |  |  |

| IJĽ             | Low-level input current                                       | V <sub>I</sub> = BDGND                                                                               |                        | -0.005 | 1    | μΑ    |  |  |

|                 | Total operating supply current, (from                         | $\overline{\text{CS}}$ at BDGND, AVDD = 5.5 V, SYSCLK = 10 MHz                                       |                        | 8.5    | 11   | mA    |  |  |

|                 | AV <sub>DD</sub> , DV <sub>DD</sub> , and BDV <sub>DD</sub> ) | $\overline{\text{CS}}$ at BDGND, $\text{AV}_{\text{DD}}$ = 2.7 V, $\text{SYSCLK}$ = 8 MHz            |                        | 5      | 7    | mA    |  |  |

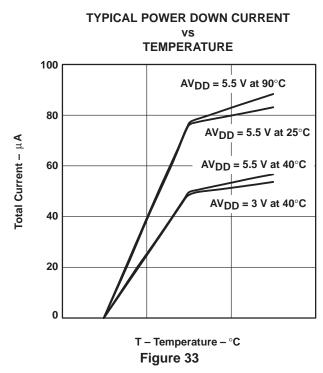

|                 | Total auto-powerdown supply current                           | CS at BDGND, AV <sub>DD</sub> = 5.5 V,<br>SYSCLK = 10 MHz,<br>CMOS control level, Auto powerdown = 1 |                        | 85     | 120  | ^     |  |  |

| I <sub>DD</sub> | (from AV $_{DD}$ , DV $_{DD}$ , and BDV $_{DD}$ )             | CS at BDGND, AV <sub>DD</sub> = 5.5 V,<br>SYSCLK = 10 MHz,<br>TTL control level, Auto powerdown = 1  |                        | 200    | 300  | μА    |  |  |

|                 | Total S/W powerdown supply current                            | CS at BDGND, AV <sub>DD</sub> = 5.5 V,<br>SYSCLK = 10 MHz,<br>CMOS control level, S/W powerdown = 1  |                        | 0.2    | 1 μΑ |       |  |  |

|                 | (from AV $_{DD}$ , DV $_{DD}$ , and BDV $_{DD}$ )             | CS at BDGND, AV <sub>DD</sub> = 5.5 V,<br>SYSCLK = 10 MHz,<br>TTL control level, S/W powerdown = 1   |                        | 60     | 80   | μΑ    |  |  |

|                 | Colocted shapped lookage current                              | Selected channel at AVDD                                                                             |                        | 0.25   | 1    |       |  |  |

|                 | Selected channel leakage current                              | Selected channel at AGND                                                                             |                        | 0.25   | -1   | μΑ    |  |  |

|                 | Maximum static analog reference current into REFP             | VREFP = AV <sub>DD</sub> - 1.9 V, AV <sub>DD</sub> = 5.5 V,<br>VREFM = AGND + 0.9 V, SYSCLK = 10 MHz |                        | 150    | 180  | μΑ    |  |  |

|                 | Reference input impedance                                     | $V_{DD} = 5.5 \text{ V}, \overline{CS} = 0, \text{SCLK} = 10 \text{ MHz}$                            | 17                     | 25     | 30   | kΩ    |  |  |

|                 | Output capacitance                                            |                                                                                                      |                        |        | 5    | pF    |  |  |

| Ci              |                                                               | Analog inputs fixed                                                                                  |                        | 9      | 10   |       |  |  |

|                 | Input capacitance                                             | Analog inputs switching                                                                              |                        | 0.5    | 1    | pF    |  |  |

|                 |                                                               | Control inputs                                                                                       |                        | 20     | 25   |       |  |  |

| Ron             | Input MUX ON resistance                                       | V <sub>DD</sub> = 5.5 V                                                                              |                        |        | 0.5  | kΩ    |  |  |

| '\ON            | input won on resistance                                       | V <sub>DD</sub> = 2.7 V                                                                              |                        |        | 1    | 1 K12 |  |  |

$<sup>\</sup>overline{\dagger}$  All typical values are at  $V_{DD} = 5$  V,  $T_A = 25$ °C.

# timing requirements

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS         | MIN  | TYP | MAX  | UNIT     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-----|------|----------|

| Delay time, CS↓ to WR↓, t <sub>d</sub> (CSL–WRL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                         | 2    |     | 4    | ns       |

| Delay time, $\overline{RD}$ to $\overline{CSTART}$ $\downarrow$ , $t_{d1}(RDH - CSTARTL)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         | 100  |     |      | ns       |

| Delay time, RD↑ to CSTART↓, td2(RDH – CSTARTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                         | 300  |     |      | ns       |

| Delay time, WR↑ to CSTART↓, td1(WRH – CSTARTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                         | 100  |     |      | ns       |

| Delay time, WR↑ to CSTART↓, td2(WRH – CSTARTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                         | 300  |     |      | ns       |