# SN75ALS053

## QUAD FUTUREBUS TRANSCEIVER

TI0267—D3077, JANUARY 1988—REVISED SEPTEMBER 1989

- High Speed Quad Transceiver

- Fully Compatible with IEEE Standard 896.1-1987 Futurebus Requirements

- Drives Load Impedances as Low as  $10\ \Omega$

- High-Speed Advanced Low-Power Schottky Circuits

- Low Power Dissipation ... 81 mW Max per Channel

- High-Impedance P-N-P Inputs

- BTL™ Logic Level 1-V Bus Swing Reduces Power Consumption

- Low Bus-Port Capacitance

- Power-Up/Power-Down Protection (Glitch-Free)

- Open-Collector Driver Outputs Allows Wired-OR Connections

- Multiple Bus Channel Ground Returns to Reduce Channel Noise Interference

- Designed to Be a Faster, Lower Power Functional Equivalent of National DS3893

### description

The SN75ALS053 is a four-channel, monolithic, high-speed, advanced low-power Schottky device designed for two-way data communication in a densely populated backplane. The SN75ALS053 has independent driver input (Dn) and receiver output (Rn) pins and separate driver and receiver disables. This transceiver is designed for use in high-speed bus systems and is similar to the SN75ALS057 transceiver except that the trapezoidal feature has been eliminated to speed up the propagation delays.

These transceivers feature open-collector driver outputs, each with a series Schottky diode to reduce capacitive loading to the bus. By using a 2-V pullup on the bus, the output signal swing will be approximately 1 V, which reduces the power necessary to drive the bus load capacitance. The driver outputs are capable of driving an equivalent dc load of as low as  $10\ \Omega$ .

The receivers have a precision threshold set by an internal bandgap reference to give accurate input thresholds over  $V_{CC}$  and temperature variations.

These transceivers are compatible with Backplane Transceiver Logic (BTL™) technology at significantly reduced power dissipation per channel.

The SN75ALS053 is characterized for operation from 0°C to 70°C.

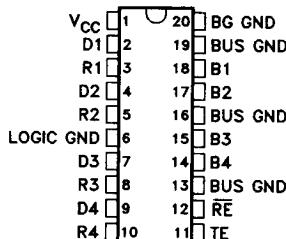

### N PACKAGE (TOP VIEW)

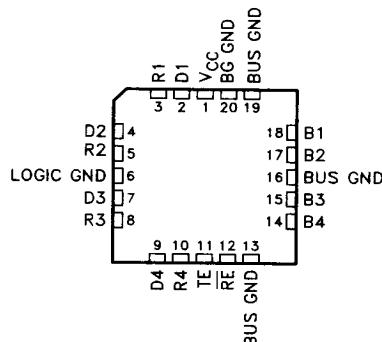

### FN CHIP CARRIER PACKAGE (TOP VIEW)

BTL is a trademark of National Semiconductor Corporation.

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1989, Texas Instruments Incorporated

**TEXAS

INSTRUMENTS**

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

# SN75ALS053 QUAD FUTUREBUS TRANSCEIVER

D3077, JANUARY 1988—REVISED SEPTEMBER 1989—TI0267

FUNCTION TABLE

TRANSMIT/RECEIVE

| CONTROLS |    | CHANNELS |       |

|----------|----|----------|-------|

| TE       | RE | D → B    | B → R |

| L        | L  | D        | R     |

| L        | H  | D        | D     |

| H        | L  | T        | R     |

| H        | H  | T        | D     |

H = high level, L = low level, R = receive, T = transmit,

D = disable

Direction of data transmission is from Dn to Bn, direction of data

reception is from Bn to Rn.

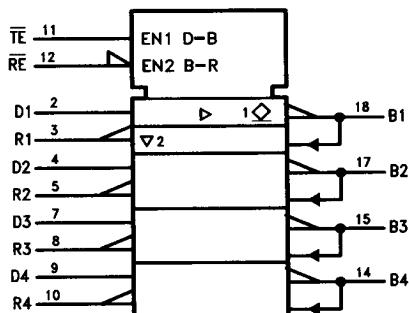

logic symbol†

† This symbol is in accordance with ANSI/IEEE Std 91-1984 and

IEC Publication 617-12.

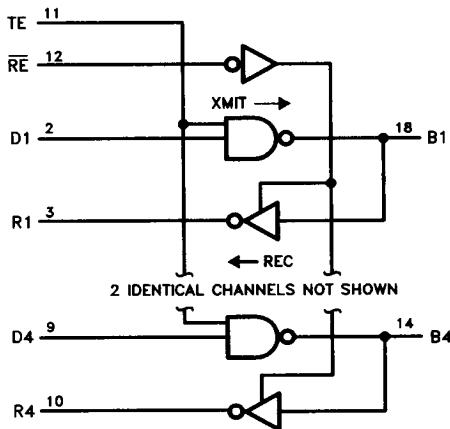

logic diagram (positive logic)

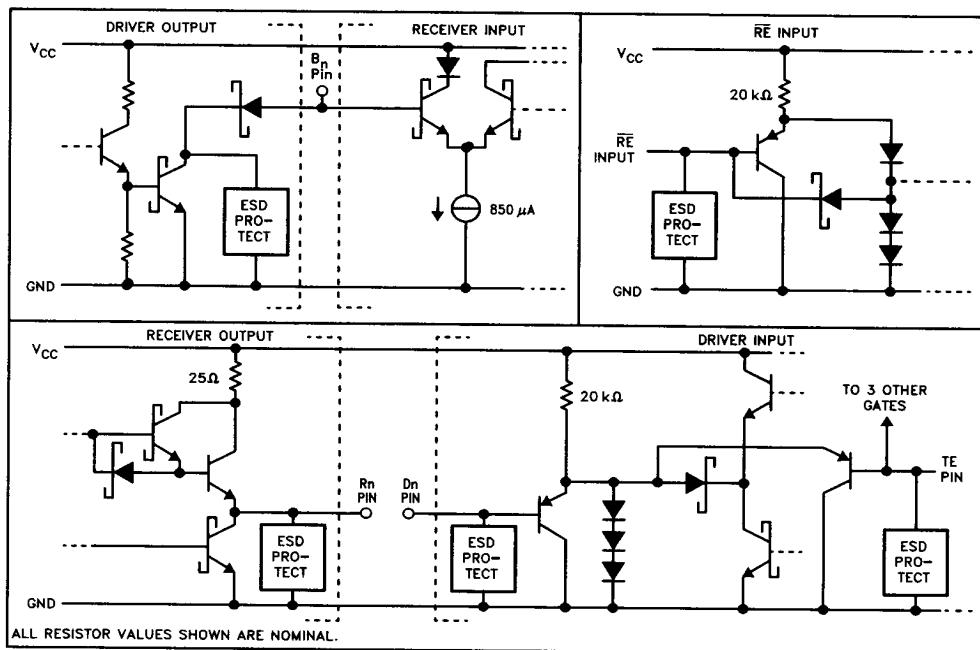

schematics of inputs and outputs

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

|                                                                                 |                              |

|---------------------------------------------------------------------------------|------------------------------|

| Supply voltage, $V_{CC}$ (see Note 1) . . . . .                                 | 6 V                          |

| Control input voltage . . . . .                                                 | 5.5 V                        |

| Driver input voltage . . . . .                                                  | 5.5 V                        |

| Driver output voltage . . . . .                                                 | 2.5 V                        |

| Receiver input voltage . . . . .                                                | 2.5 V                        |

| Receiver output voltage . . . . .                                               | 5.5 V                        |

| Continuous total power dissipation . . . . .                                    | See Dissipation Rating Table |

| Operating free-air temperature range . . . . .                                  | 0°C to 70°C                  |

| Storage temperature range . . . . .                                             | -65°C to 150°C               |

| Case temperature for 10 seconds: FN package . . . . .                           | 260°C                        |

| Lead temperature 1.6mm (1/16 in.) from case for 10 seconds: N package . . . . . | 260°C                        |

NOTE 1: Voltage values are with respect to network ground terminal.

**SN75ALS053**

**QUAD FUTUREBUS TRANSCEIVER**

D3077, JANUARY 1988—REVISED SEPTEMBER 1989—TI0267

**DISSIPATION RATING TABLE**

| PACKAGE | TA ≤ 25°C    |  | DERATING FACTOR<br>ABOVE TA = 25°C | TA = 70°C<br>POWER RATING |

|---------|--------------|--|------------------------------------|---------------------------|

|         | POWER RATING |  |                                    |                           |

| FN      | 1400 mW      |  | 11.2 mW/°C                         | 896 mW                    |

| N       | 1150 mW      |  | 9.2 mW/°C                          | 736 mW                    |

**recommended operating conditions**

|                 |                                             | MIN  | NOM | MAX  | UNIT |

|-----------------|---------------------------------------------|------|-----|------|------|

| V <sub>CC</sub> | Supply voltage                              | 4.75 | 5   | 5.25 | V    |

| V <sub>IH</sub> | High-level driver and control input voltage |      | 2   |      | V    |

| V <sub>IL</sub> | Low-level driver and control input voltage  |      |     | 0.8  | V    |

|                 | Bus termination voltage                     |      | 1.9 | 2.1  | V    |

| T <sub>A</sub>  | Operating free-air temperature              | 0    | 70  |      | °C   |

**electrical characteristics over recommended ranges of operating free-air temperature and supply voltage (unless otherwise noted)**

| PARAMETER                                                                                  |                                       | TEST CONDITIONS                                                                                       | MIN   | TYP   | MAX   | UNIT |

|--------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| V <sub>IK</sub> Input clamp voltage at D <sub>n</sub> , D <sub>E</sub> , or R <sub>E</sub> |                                       | I <sub>I</sub> = - 18 mA                                                                              |       |       | - 1.5 | V    |

| V <sub>T</sub> Receiver input threshold at B <sub>n</sub>                                  |                                       |                                                                                                       | 1.426 | 1.674 |       | V    |

| V <sub>OH</sub> High-level output voltage at R <sub>n</sub>                                |                                       | B <sub>n</sub> at 1.2 V, R <sub>E</sub> at 0.8 V,<br>I <sub>OH</sub> = - 1 mA                         | 2.5   |       |       | V    |

| V <sub>OL</sub> Low-level output voltage                                                   | R <sub>n</sub>                        | B <sub>n</sub> at 2 V, R <sub>E</sub> at 0.8 V,<br>I <sub>OL</sub> = 20 mA                            |       |       | 0.5   | V    |

|                                                                                            | B <sub>n</sub>                        | D <sub>n</sub> at 2.4 V, TE at 2.4 V,<br>V <sub>L</sub> = 2 V, R <sub>L</sub> = 10 Ω,<br>See Figure 1 | 0.75  | 1.2   |       |      |

| I <sub>IH</sub> High-level input current                                                   | D <sub>n</sub> , TE or R <sub>E</sub> | V <sub>I</sub> = V <sub>CC</sub>                                                                      |       | 40    |       | μA   |

|                                                                                            | B <sub>n</sub>                        | V <sub>I</sub> = 2 V, V <sub>CC</sub> = 0 or 5.25 V,<br>D <sub>n</sub> at 0.8 V, TE at 0.8 V,         |       | 100   |       |      |

| I <sub>IL</sub> Low-level input current at D <sub>n</sub> , TE or R <sub>E</sub>           |                                       | V <sub>I</sub> = 0.4 V                                                                                |       | - 400 |       | μA   |

| I <sub>OS</sub> Short-circuit output current at R <sub>n</sub>                             |                                       | R <sub>n</sub> at 0 V, B <sub>n</sub> at 1.2 V,<br>R <sub>E</sub> at 0.8 V                            | - 70  | - 200 |       | mA   |

| I <sub>CC</sub> Supply current                                                             |                                       |                                                                                                       |       | 65    |       | mA   |

| C <sub>O(B)</sub> Driver output capacitance                                                |                                       | V <sub>CC</sub> = 5 V, T <sub>A</sub> = 25°C                                                          |       | 6.5   |       | pF   |

**switching characteristics over recommended ranges of operating free-air temperature and  $V_{CC}$  (unless otherwise noted)**

**driver**

| PARAMETER                                                        | FROM (INPUT) | TO (OUTPUT) | TEST CONDITIONS            | MIN | MAX | UNIT |

|------------------------------------------------------------------|--------------|-------------|----------------------------|-----|-----|------|

| $t_{PLH}$<br>Propagation delay time,<br>low-to-high-level output | Dn           | Bn          | TE at 3 V,<br>See Figure 2 | 2   | 7   | ns   |

|                                                                  |              |             |                            |     |     |      |

| $t_{PHL}$<br>Propagation delay time<br>high-to-low-level output  | Dn           | Bn          | Dn at 3 V,<br>See Figure 2 | 2   | 7   | ns   |

|                                                                  |              |             |                            |     |     |      |

| $t_{PLH}$<br>Propagation delay time,<br>low-to-high-level output | Dn           | Bn          | Dn at 3 V,<br>See Figure 2 | 2   | 7   | ns   |

|                                                                  |              |             |                            |     |     |      |

| $t_{PHL}$<br>Propagation delay time<br>high-to-low-level output  | Dn           | Bn          | TE at 3 V,<br>See Figure 2 | 0.5 | 5   | ns   |

|                                                                  |              |             |                            |     |     |      |

| Transition time,<br>low-to-high-level output                     | Dn           | Bn          | TE at 3 V,<br>See Figure 2 | 0.5 | 5   | ns   |

|                                                                  |              |             |                            |     |     |      |

| Skew between driver<br>channels <sup>†</sup>                     | Dn           | Bn          | TE at 3 V,<br>$V_L = 2 V$  | 1   | ns  |      |

|                                                                  |              |             |                            |     |     |      |

**receiver**

| PARAMETER                                                        | FROM (INPUT) | TO (OUTPUT) | TEST CONDITIONS                                                                                 | MIN | MAX | UNIT |

|------------------------------------------------------------------|--------------|-------------|-------------------------------------------------------------------------------------------------|-----|-----|------|

| $t_{PLH}$<br>Propagation delay time,<br>low-to-high-level output | Bn           | Rn          | RE at 0.3 V, TE at 0.3 V, See Figure 3                                                          | 2   | 8   | ns   |

|                                                                  |              |             |                                                                                                 |     |     |      |

| $t_{PHL}$<br>Propagation delay time<br>high-to-low-level output  | RE           | Rn          | Bn at 2 V, TE at 0.3 V, $V_L = 5 V$ ,<br>$C_L = 5 pF$ , $R_{L1} = 500 \Omega$ ,<br>See Figure 4 | 2   | 8   | ns   |

|                                                                  |              |             |                                                                                                 |     |     |      |

| $t_{PLZ}$<br>Output disable time<br>from low level               | RE           | Rn          | Bn at 2 V, TE at 0.3 V, $V_L = 5 V$ ,<br>$C_L = 5 pF$ , $R_{L1} = 500 \Omega$ ,<br>See Figure 4 | 6   | ns  |      |

|                                                                  |              |             |                                                                                                 |     |     |      |

| $t_{PZL}$<br>Output enable time<br>to low level                  | RE           | Rn          | Bn at 2 V, TE at 0.3 V, $V_L = 5 V$ ,<br>$C_L = 5 pF$ , $R_{L1} = 500 \Omega$ ,<br>See Figure 4 | 12  | ns  |      |

|                                                                  |              |             |                                                                                                 |     |     |      |

| $t_{PHZ}$<br>Output disable time<br>from high level              | RE           | Rn          | Bn at 1 V, TE at 0.3 V, $V_L = 0$ ,<br>$C_L = 5 pF$ , $R_{L1} = 500 \Omega$ ,<br>See Figure 4   | 6   | ns  |      |

|                                                                  |              |             |                                                                                                 |     |     |      |

| $t_{PZH}$<br>Output enable time<br>to high level                 | RE           | Rn          | Bn at 1 V, TE at 0.3 V, $V_L = 0$ ,<br>$C_L = 5 pF$ , $R_{L1} = 500 \Omega$ ,<br>See Figure 4   | 12  | ns  |      |

|                                                                  |              |             |                                                                                                 |     |     |      |

| Skew between receiver<br>channels <sup>†</sup>                   | Bn           | Rn          | RE at 0.3 V, TE at 0.3 V                                                                        | 1   | ns  |      |

<sup>†</sup> Skew is the difference between the propagation delay time ( $t_{PLH}$  or  $t_{PHL}$ ) of one receiver channel and that same propagation delay time of any other receiver channel. It applies for both  $t_{PLH}$  and  $t_{PHL}$ .

# SN75ALS053 QUAD FUTUREBUS TRANSCEIVER

D3077, JANUARY 1988—REVISED SEPTEMBER 1989—TI0267

## PARAMETER MEASUREMENT INFORMATION

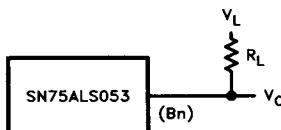

FIGURE 1. DRIVER LOW-LEVEL-OUTPUT-VOLTAGE TEST CIRCUIT

TEST CIRCUIT

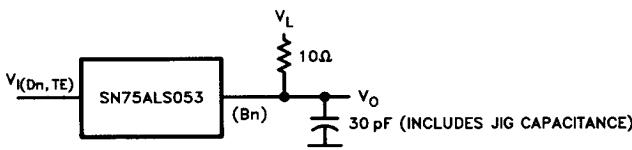

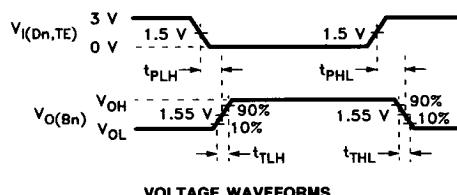

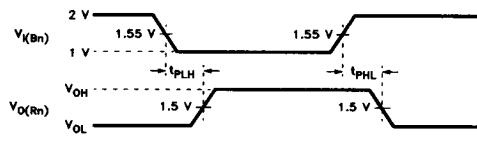

NOTE:  $t_r = t_f \leq 5$  ns from 10% to 90%

FIGURE 2. DRIVER PROPAGATION DELAY TIMES

PARAMETER MEASUREMENT INFORMATION

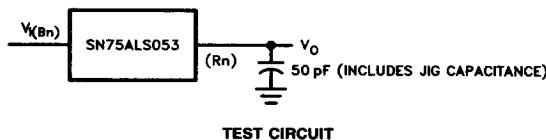

NOTE:  $t_r = t_f \leq 10$  ns from 10% to 90%

FIGURE 3. RECEIVER PROPAGATION DELAY TIMES

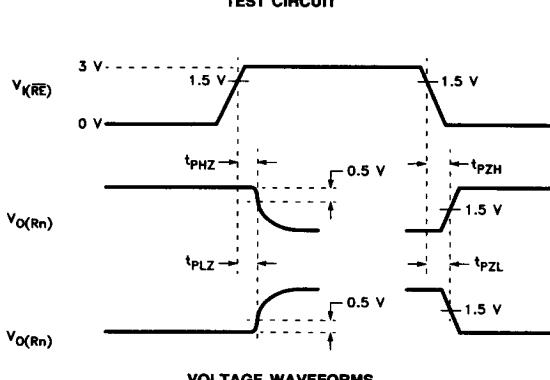

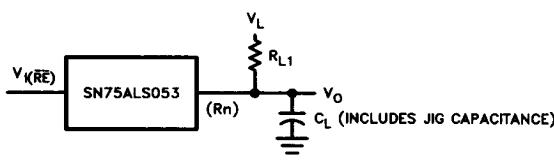

NOTE:  $t_r = t_f \leq 5$  ns from 10% to 90%

FIGURE 4. PROPAGATION DELAY FROM  $\overline{RE}$  TO  $R_n$