# Si8650/51/52/55 Data Sheet

## Low Power Five-Channel Digital Isolator

Silicon Lab's family of ultra-low-power digital isolators are CMOS devices offering substantial data rate, propagation delay, power, size, reliability, and external BOM advantages over legacy isolation technologies. The operating parameters of these products remain stable across wide temperature ranges and throughout device service life for ease of design and highly uniform performance. All device versions have Schmitt trigger inputs for high noise immunity and only require VDD bypass capacitors.

Data rates up to 150 Mbps are supported, and all devices achieve propagation delays of less than 10 ns. Enable inputs provide a single point control for enabling and disabling output drive. Ordering options include a choice of isolation ratings (1.0, 2.5, 3.75 and 5 kV) and a selectable fail-safe operating mode to control the default output state during power loss. All products >1 kV $_{\rm RMS}$  are safety certified by UL, CSA, VDE, and CQC, and products in wide-body packages support reinforced insulation withstanding up to 5 kV $_{\rm RMS}$ .

Automotive Grade is available for certain part numbers. These products are built using automotive-specific flows at all steps in the manufacturing process to ensure the robustness and low defectivity required for automotive applications.

## Industrial Applications

- Industrial automation systems

- Medical electronics

- Isolated switch mode supplies

- · Isolated ADC. DAC

- · Motor control

- · Power inverters

- · Communication systems

## **Safety Regulatory Approvals**

- · UL 1577 recognized

- Up to 5000  $V_{\mbox{RMS}}$  for 1 minute

- CSA component notice 5A approval

- IEC 60950-1, 62368-1, 60601-1 (reinforced insulation)

- · VDE certification conformity

- VDE 0884-10

- EN60950-1 (reinforced insulation)

- · CQC certification approval

- GB4943.1

## **Automotive Applications**

- On-board chargers

- · Battery management systems

- · Charging stations

- Traction inverters

- · Hybrid Electric Vehicles

- · Battery Electric Vehicles

### **KEY FEATURES**

- · High-speed operation

- DC to 150 Mbps

- · No start-up initialization required

- Wide Operating Supply Voltage

- 2.5-5.5 V

- Up to 5000 V<sub>RMS</sub> isolation

- · 60-year life at rated working voltage

- · High electromagnetic immunity

- · Ultra low power (typical)

- 5 V Operation

- 1.6 mA per channel at 1 Mbps

- 5.5 mA per channel at 100 Mbps

- 2.5 V Operation

- 1.5 mA per channel at 1 Mbps

- 3.5 mA per channel at 100 Mbps

- · Tri-state outputs with ENABLE

- · Schmitt trigger inputs

- · Selectable fail-safe mode

- Default high or low output (ordering option)

- · Precise timing (typical)

- · 10 ns propagation delay

- · 1.5 ns pulse width distortion

- 0.5 ns channel-channel skew

- 2 ns propagation delay skew5 ns minimum pulse width

- Transient Immunity 50 kV/μs

- Transient infinitionity 50 kV/µs

- AEC-Q100 qualificationWide temperature range

- –40 to 125 °C

- -40 to 125 O

- RoHS-compliant packages

- · SOIC-16 wide body

- · SOIC-16 narrow body

- QSOP-16

- · Automotive-grade OPNs available

- AIAG compliant PPAP documentation support

- IMDS and CAMDS listing support

## 1. Ordering Guide

Table 1.1. Ordering Guide for Valid OPNs<sup>1, 2, 3</sup>

| Ordering Part<br>Number (OPN) | Number of<br>Inputs<br>VDD1 Side | Number of<br>Inputs<br>VDD2 Side | Max Data<br>Rate<br>(Mbps) | Default<br>Output<br>State | Isolation rating<br>(kV) | Temp (°C)     | Package    |

|-------------------------------|----------------------------------|----------------------------------|----------------------------|----------------------------|--------------------------|---------------|------------|

| QSOP-16 Packages              |                                  |                                  |                            |                            |                          |               |            |

| Si8650BB-B-IU                 | 5                                | 0                                | 150                        | Low                        | 2.5                      | –40 to 125 °C | QSOP-16    |

| Si8650EB-B-IU                 | 5                                | 0                                | 150                        | High                       | 2.5                      | –40 to 125 °C | QSOP-16    |

| Si8651BB-B-IU                 | 4                                | 1                                | 150                        | Low                        | 2.5                      | –40 to 125 °C | QSOP-16    |

| Si8651EB-B-IU                 | 4                                | 1                                | 150                        | High                       | 2.5                      | -40 to 125°C  | QSOP-16    |

| Si8652BB-B-IU                 | 3                                | 2                                | 150                        | Low                        | 2.5                      | -40 to 125°C  | QSOP-16    |

| Si8652EB-B-IU                 | 3                                | 2                                | 150                        | High                       | 2.5                      | -40 to 125°C  | QSOP-16    |

| Si8655BA-B-IU                 | 5                                | 0                                | 150                        | Low                        | 1.0                      | –40 to 125 °C | QSOP-16    |

| Si8655BA-C-IU                 | 5                                | 0                                | 150                        | Low                        | 1.0                      | –40 to 125 °C | QSOP-16    |

| SOIC-16 Packages              | I                                |                                  |                            |                            |                          |               |            |

| Si8650BB-B-IS1                | 5                                | 0                                | 150                        | Low                        | 2.5                      | –40 to 125 °C | NB SOIC-16 |

| Si8650BD-B-IS                 | 5                                | 0                                | 150                        | Low                        | 5.0                      | –40 to 125 °C | WB SOIC-16 |

| Si8650EC-B-IS1                | 5                                | 0                                | 150                        | High                       | 3.75                     | –40 to 125 °C | NB SOIC-16 |

| Si8650ED-B-IS                 | 5                                | 0                                | 150                        | High                       | 5.0                      | –40 to 125 °C | WB SOIC-16 |

| Si8651BB-B-IS1                | 4                                | 1                                | 150                        | Low                        | 2.5                      | –40 to 125 °C | NB SOIC-16 |

| Si8651BC-B-IS1                | 4                                | 1                                | 150                        | Low                        | 3.75                     | –40 to 125 °C | NB SOIC-16 |

| Si8651BD-B-IS                 | 4                                | 1                                | 150                        | Low                        | 5.0                      | –40 to 125 °C | WB SOIC-16 |

| Si8651EC-B-IS1                | 4                                | 1                                | 150                        | High                       | 3.75                     | –40 to 125 °C | NB SOIC-16 |

| Si8651ED-B-IS                 | 4                                | 1                                | 150                        | High                       | 5.0                      | –40 to 125 °C | WB SOIC-16 |

| Si8652BB-B-IS1                | 3                                | 2                                | 150                        | Low                        | 2.5                      | –40 to 125 °C | NB SOIC-16 |

| Si8652BC-B-IS1                | 3                                | 2                                | 150                        | Low                        | 3.75                     | –40 to 125 °C | NB SOIC-16 |

| Si8652BD-B-IS                 | 3                                | 2                                | 150                        | Low                        | 5.0                      | –40 to 125 °C | WB SOIC-16 |

| Si8652EC-B-IS1                | 3                                | 2                                | 150                        | High                       | 3.75                     | –40 to 125 °C | NB SOIC-16 |

| Si8652ED-B-IS                 | 3                                | 2                                | 150                        | High                       | 5.0                      | –40 to 125 °C | WB SOIC-16 |

| Si8655BA-B-IS                 | 5                                | 0                                | 150                        | Low                        | 1.0                      | –40 to 125 °C | WB SOIC-16 |

| Si8655BB-B-IS1                | 5                                | 0                                | 150                        | Low                        | 2.5                      | –40 to 125 °C | NB SOIC-16 |

| Si8655BD-B-IS                 | 5                                | 0                                | 150                        | Low                        | 5.0                      | –40 to 125 °C | WB SOIC-16 |

- 1. All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard classifications and peak solder temperatures.

- 2. "Si" and "SI" are used interchangeably.

- 3. An "R" at the end of the part number denotes tape and reel packaging option.

#### **Automotive Grade OPNs**

Automotive-grade devices are built using automotive-specific flows at all steps in the manufacturing process to ensure robustness and low defectivity. These devices are supported with AIAG-compliant Production Part Approval Process (PPAP) documentation, and feature International Material Data System (IMDS) and China Automotive Material Data System (CAMDS) listing. Qualifications are compliant with AEC-Q100, and a zero-defect methodology is maintained throughout definition, design, evaluation, qualification, and mass production steps.

Table 1.2. Ordering Guide for Automotive Grade OPNs<sup>1, 2, 4, 5</sup>

| Ordering Part<br>Number (OPN) | Number of<br>Inputs<br>VDD1 Side | Number of<br>Inputs<br>VDD2 Side | Max Data<br>Rate<br>(Mbps) | Default<br>Output<br>State | Isolation rating<br>(kV) | Temp (°C)     | Package    |

|-------------------------------|----------------------------------|----------------------------------|----------------------------|----------------------------|--------------------------|---------------|------------|

| QSOP-16 Packages              |                                  |                                  |                            |                            |                          |               |            |

| Si8655BA-AU                   | 5                                | 0                                | 150                        | Low                        | 1.0                      | –40 to 125 °C | QSOP-16    |

| SOIC-16 Packages              |                                  |                                  |                            |                            |                          |               |            |

| Si8651BB-AS1                  | 4                                | 1                                | 150                        | Low                        | 2.5                      | –40 to 125 °C | NB SOIC-16 |

| Si8651BD-AS                   | 4                                | 1                                | 150                        | Low                        | 5.0                      | –40 to 125 °C | WB SOIC-16 |

| Si8652BD-AS                   | 3                                | 2                                | 150                        | Low                        | 5.0                      | –40 to 125 °C | WB SOIC-16 |

| Si8655BA-AS                   | 5                                | 0                                | 150                        | Low                        | 1.0                      | –40 to 125 °C | WB SOIC-16 |

- All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard classifications.

- 2. "Si" and "SI" are used interchangeably.

- 3. An "R" at the end of the part number denotes tape and reel packaging option.

- 4. Automotive-Grade devices (with an "-A" suffix) are identical in construction materials, topside marking, and electrical parameters to their Industrial-Grade (with a "-I" suffix) version counterparts. Automotive-Grade products are produced utilizing full automotive process flows and additional statistical process controls throughout the manufacturing flow. The Automotive-Grade part number is included on shipping labels.

- 5. Additional Ordering Part Numbers may be available in Automotive-Grade. Please contact your local Silicon Labs sales representative for further information.

# **Table of Contents**

| 1. | Ordering Guide                            | 2          |

|----|-------------------------------------------|------------|

| 2. | Functional Description                    | 5          |

|    | 2.1 Theory of Operation                   | 5          |

|    | 2.2 Eye Diagram                           | 6          |

| 3. | Device Operation                          | 7          |

|    | 3.1 Device Startup                        | 8          |

|    | 3.2 Undervoltage Lockout                  | 8          |

|    | 3.3 Layout Recommendations                | 9          |

|    | 3.3.2 Output Pin Termination              |            |

|    | 3.5 Typical Performance Characteristics   |            |

| 1  | Electrical Specifications                 |            |

|    |                                           |            |

| 5. | Pin Descriptions                          |            |

|    | 5.1 Si8650/51/52 Pin Descriptions         |            |

| c  |                                           |            |

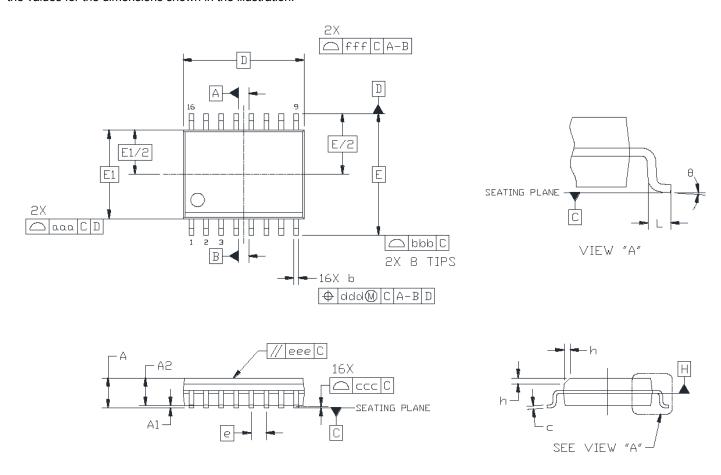

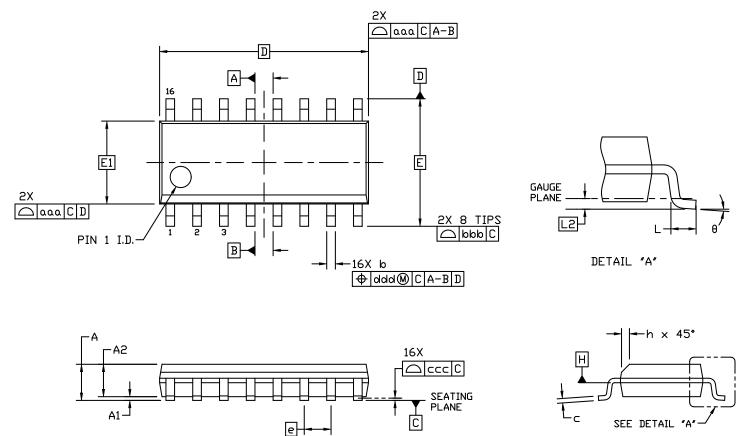

|    | Package Outline (16-Pin Wide Body SOIC)   |            |

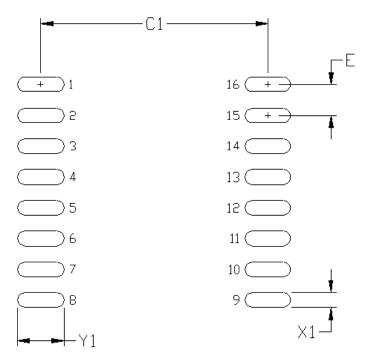

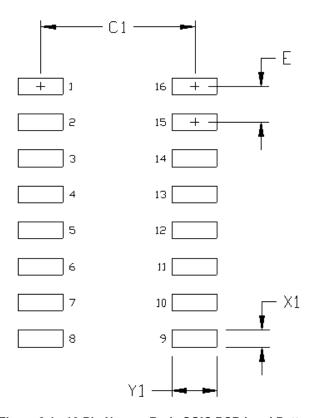

|    | Land Pattern (16-Pin Wide-Body SOIC)      |            |

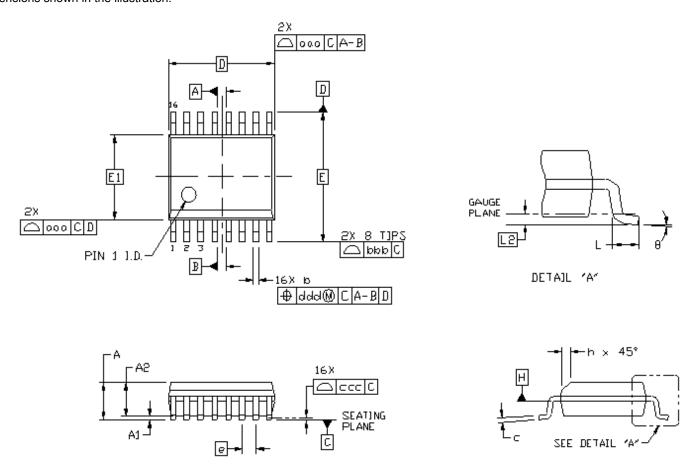

| 8. | Package Outline (16-Pin Narrow Body SOIC) | 1          |

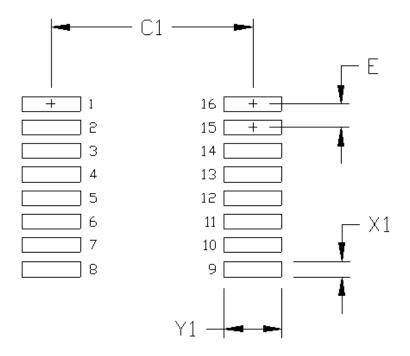

| 9. | Land Pattern (16-Pin Narrow Body SOIC)    | 3          |

| 10 | . Package Outline (16-Pin QSOP)           | <b>3</b> 4 |

| 11 | . Land Pattern (16-Pin QSOP)              | <b>6</b>   |

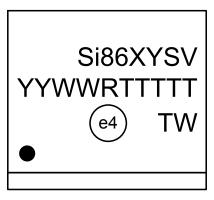

| 12 | . Top Marking (16-Pin Wide Body SOIC)     | 37         |

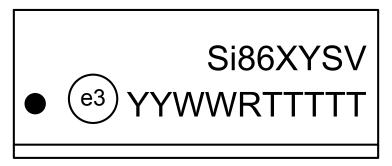

| 13 | . Top Marking (16-Pin Narrow Body SOIC)   | 38         |

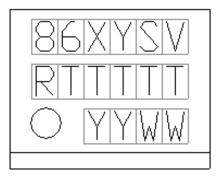

|    | . Top Marking (16-Pin QSOP)               |            |

| 15 | . Revision History                        | łO         |

## 2. Functional Description

## 2.1 Theory of Operation

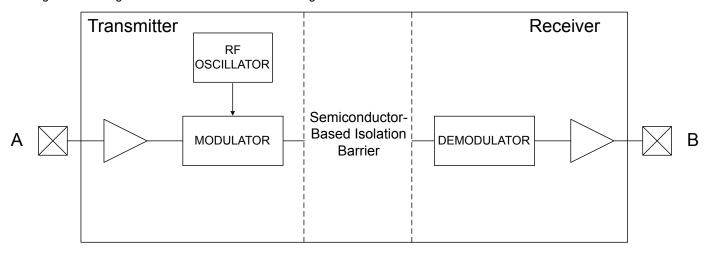

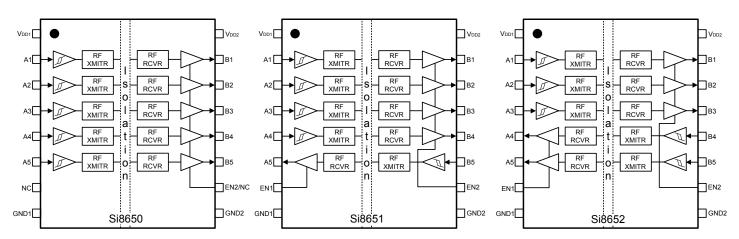

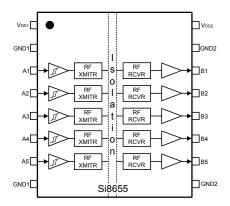

The operation of an Si865x channel is analogous to that of an opto coupler, except an RF carrier is modulated instead of light. This simple architecture provides a robust isolated data path and requires no special considerations or initialization at start-up. A simplified block diagram for a single Si865x channel is shown in the figure below.

Figure 2.1. Simplified Channel Diagram

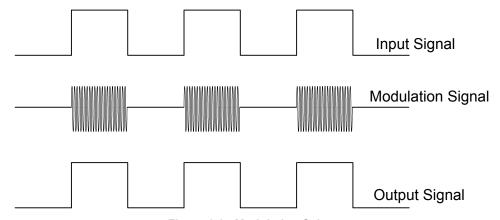

A channel consists of an RF Transmitter and RF Receiver separated by a semiconductor-based isolation barrier. Referring to the Transmitter, input A modulates the carrier provided by an RF oscillator using on/off keying. The Receiver contains a demodulator that decodes the input state according to its RF energy content and applies the result to output B via the output driver. This RF on/off keying scheme is superior to pulse code schemes as it provides best-in-class noise immunity, low power consumption, and better immunity to magnetic fields. See the figure below for more details.

Figure 2.2. Modulation Scheme

## 2.2 Eye Diagram

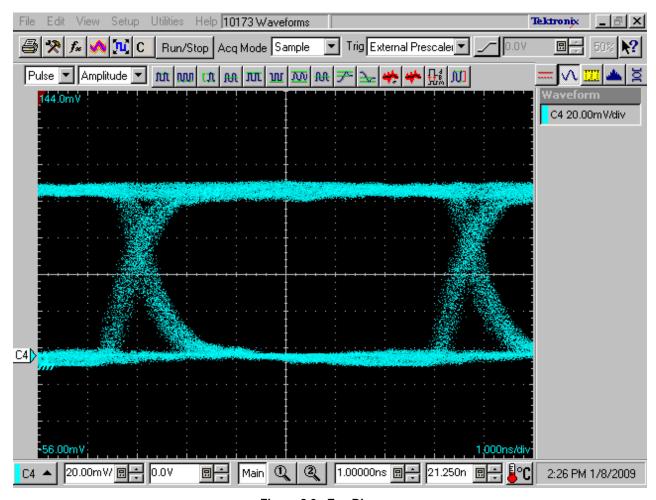

The figure below illustrates an eye-diagram taken on an Si8650. For the data source, the test used an Anritsu (MP1763C) Pulse Pattern Generator set to 1000 ns/div. The output of the generator's clock and data from an Si8650 were captured on an oscilloscope. The results illustrate that data integrity was maintained even at the high data rate of 150 Mbps. The results also show that 2 ns pulse width distortion and 350 ps peak jitter were exhibited.

Figure 2.3. Eye Diagram

## 3. Device Operation

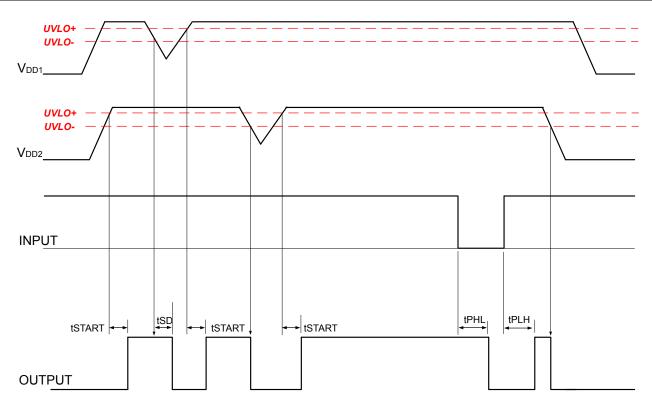

Device behavior during start-up, normal operation, and shutdown is shown in Figure 3.1 Device Behavior during Normal Operation on page 9, where UVLO+ and UVLO- are the positive-going and negative-going thresholds respectively. Refer to the table below to determine outputs when power supply (VDD) is not present. Additionally, refer to the table on the following page for logic conditions when enable pins are used.

Table 3.1. Si865x Logic Operation

| V <sub>I</sub> Input <sup>1,2</sup> | EN Input<br>1,2,3,4 | VDDI State<br>1,5,6 | VDDO State<br>1,5,6 | V <sub>O</sub> Output <sup>1,2</sup> | Comments                                                                                                                                                                                                                                                  |

|-------------------------------------|---------------------|---------------------|---------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н                                   | H or NC             | Р                   | Р                   | Н                                    | Enabled, normal operation.                                                                                                                                                                                                                                |

| L                                   | H or NC             | Р                   | Р                   | L                                    |                                                                                                                                                                                                                                                           |

| X 7                                 | L                   | Р                   | Р                   | Hi-Z <sup>8</sup>                    | Disabled.                                                                                                                                                                                                                                                 |

| X 7                                 | H or NC             | UP                  | Р                   | L <sup>9</sup>                       | Upon transition of VDDI from unpowered to powered, $V_{O}$ returns to the same state as $V_{I}$ in less than 1 $\mu$ s.                                                                                                                                   |

| X 7                                 | L                   | UP                  | Р                   | Hi-Z <sup>8</sup>                    | Disabled.                                                                                                                                                                                                                                                 |

| X 7                                 | Х7                  | Р                   | UP                  | Undetermined                         | Upon transition of VDDO from unpowered to powered, $V_O$ returns to the same state as $V_I$ within 1 $\mu$ s, if EN is in either the H or NC state. Upon transition of VDDO from unpowered to powered, $V_O$ returns to Hi-Z within 1 $\mu$ s if EN is L. |

- 1. VDDI and VDDO are the input and output power supplies.  $V_I$  and  $V_O$  are the respective input and output terminals. EN is the enable control input located on the same output side.

- 2. X = not applicable; H = Logic High; L = Logic Low; Hi-Z = High Impedance.

- 3. It is recommended that the enable inputs be connected to an external logic high or low level when the Si865x is operating in noisy environments.

- 4. No Connect (NC) replaces EN1 on Si8650. No Connects are not internally connected and can be left floating, tied to VDD, or tied to GND.

- 5. "Powered" state (P) is defined as 2.5 V < VDD < 5.5 V.

- 6. "Unpowered" state (UP) is defined as VDD = 0 V.

- 7. Note that an I/O can power the die for a given side through an internal diode if its source has adequate current.

- 8. When using the enable pin (EN) function, the output pin state is driven into a high-impedance state when the EN pin is disabled (EN = 0).

- 9. See 1. Ordering Guide for details. This is the selectable fail-safe operating mode (ordering option). Some devices have default output state = H, and some have default output state = L, depending on the ordering part number (OPN). For default high devices, the data channels have pull-ups on inputs/outputs. For default low devices, the data channels have pull-downs on inputs/outputs.

Table 3.2. Enable Input Truth <sup>1</sup>

| P/N    | EN1 <sup>1,2</sup> | EN2 <sup>1,2</sup> | Operation                                                                                      |

|--------|--------------------|--------------------|------------------------------------------------------------------------------------------------|

| Si8650 | _                  | Н                  | Outputs B1, B2, B3, B4, B5 are enabled and follow input state.                                 |

|        | _                  | L                  | Outputs B1, B2, B3, B4, B5 are disabled and Logic Low or in high impedance state. <sup>3</sup> |

| Si8651 | Н                  | Х                  | Output A5 enabled and follow input state.                                                      |

|        | L                  | Х                  | Output A5 disabled and in high impedance state. <sup>3</sup>                                   |

|        | Х                  | Н                  | Outputs B1, B2, B3, B4 are enabled and follow input state.                                     |

|        | Х                  | L                  | Outputs B1, B2, B3, B4 are disabled and in high impedance state. <sup>3</sup>                  |

| Si8652 | Н                  | Х                  | Outputs A4 and A5 are enabled and follow input state.                                          |

|        | L                  | Х                  | Outputs A4 and A5 are disabled and in high impedance state. <sup>3</sup>                       |

|        | Х                  | Н                  | Outputs B1, B2, B3 are enabled and follow input state.                                         |

|        | Х                  | L                  | Outputs B1, B2, B3 are disabled and in high impedance state. <sup>3</sup>                      |

| Si8655 | _                  | _                  | Outputs B1, B2, B3, B4, B5 are enabled and follow input state.                                 |

- 1. Enable inputs EN1 and EN2 can be used for multiplexing, for clock sync, or other output control. These inputs are internally pulled-up to local VDD by a 2 μA current source allowing them to be connected to an external logic level (high or low) or left floating. To minimize noise coupling, do not connect circuit traces to EN1 or EN2 if they are left floating. If EN1, EN2 are unused, it is recommended they be connected to an external logic level, especially if the Si865x is operating in a noisy environment.

- 2. X = not applicable; H = Logic High; L = Logic Low.

- 3. When using the enable pin (EN) function, the output pin state is driven into a high-impedance state when the EN pin is disabled (EN = 0).

### 3.1 Device Startup

Outputs are held low during powerup until VDD is above the UVLO threshold for time period tSTART. Following this, the outputs follow the states of inputs.

## 3.2 Undervoltage Lockout

Undervoltage Lockout (UVLO) is provided to prevent erroneous operation during device startup and shutdown or when VDD is below its specified operating circuits range. Both Side A and Side B each have their own undervoltage lockout monitors. Each side can enter or exit UVLO independently. For example, Side A unconditionally enters UVLO when  $V_{DD1}$  falls below  $V_{DD1(UVLO-)}$  and exits UVLO when  $V_{DD1}$  rises above  $V_{DD1(UVLO-)}$ . Side B operates the same as Side A with respect to its  $V_{DD2}$  supply.

Figure 3.1. Device Behavior during Normal Operation

## 3.3 Layout Recommendations

To ensure safety in the end user application, high voltage circuits (i.e., circuits with  $>30 \text{ V}_{AC}$ ) must be physically separated from the safety extra-low voltage circuits (SELV is a circuit with  $<30 \text{ V}_{AC}$ ) by a certain distance (creepage/clearance). If a component, such as a digital isolator, straddles this isolation barrier, it must meet those creepage/clearance requirements and also provide a sufficiently large high-voltage breakdown protection rating (commonly referred to as working voltage protection). Table 4.5 Regulatory Information <sup>1</sup> on page 21 and Table 4.6 Insulation and Safety-Related Specifications on page 22 detail the working voltage and creepage/clearance capabilities of the Si86xx. These tables also detail the component standards (UL1577, IEC60747, CSA 5A), which are readily accepted by certification bodies to provide proof for end-system specifications requirements. Refer to the end-system specification (61010-1, 60950-1, 60601-1, etc.) requirements before starting any design that uses a digital isolator.

## 3.3.1 Supply Bypass

The Si865x family requires a 0.1  $\mu$ F bypass capacitor between  $V_{DD1}$  and GND1 and  $V_{DD2}$  and GND2. The capacitor should be placed as close as possible to the package. To enhance the robustness of a design, the user may also include resistors (50–300  $\Omega$ ) in series with the inputs and outputs if the system is excessively noisy.

## 3.3.2 Output Pin Termination

The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ ,  $\pm$ 40%, which is a combination of the value of the onchip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be appropriately terminated with controlled impedance PCB traces.

## 3.4 Fail-Safe Operating Mode

Si86xx devices feature a selectable (by ordering option) mode whereby the default output state (when the input supply is unpowered) can either be a logic high or logic low when the output supply is powered. See Table 3.1 Si865x Logic Operation on page 7 and 1. Ordering Guide for more information.

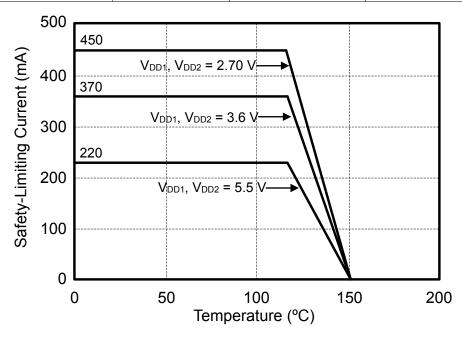

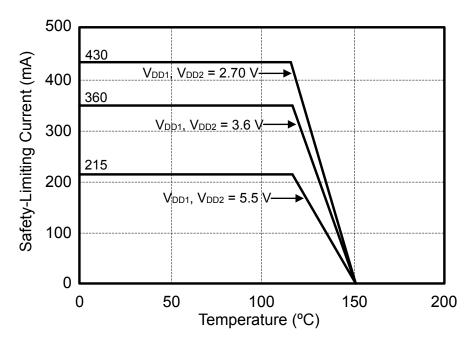

## 3.5 Typical Performance Characteristics

The typical performance characteristics depicted in the following diagrams are for information purposes only. Refer to Table 4.2 Electrical Characteristics on page 12 through Table 4.4 Electrical Characteristics on page 18 for actual specification limits.

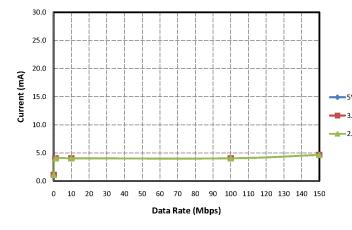

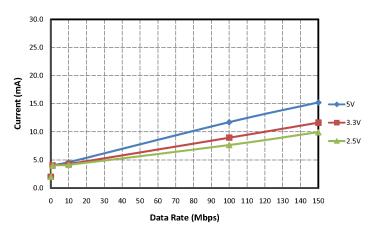

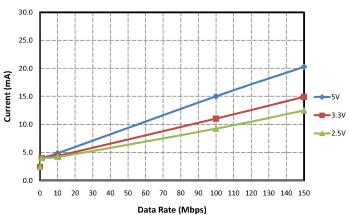

Figure 3.2. Si8650/55 Typical V<sub>DD1</sub> Supply Current vs. Data Rate 5, 3.3, and 2.5 V Operation

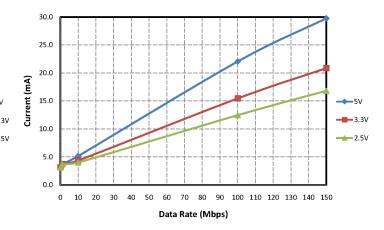

Figure 3.3. Si8650/55 Typical  $V_{DD2}$  Supply Current vs. Data Rate 5, 3.3, and 2.5 V Operation (15 pF Load)

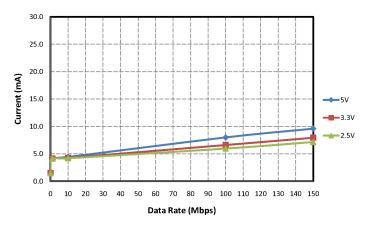

Figure 3.4. Si8651 Typical V<sub>DD1</sub> Supply Current vs. Data Rate 5, 3.3, and 2.5 V Operation (15 pF Load)

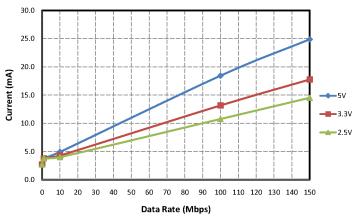

Figure 3.5. Si8651 Typical V<sub>DD2</sub> Supply Current vs. Data Rate 5, 3.3, and 2.5 V Operation (15 pF Load)

5, 3.3, and 2.5 V Operation (15 pF Load)

Figure 3.6. Si8652 Typical V<sub>DD1</sub> Supply Current vs. Data Rate Figure 3.7. Si8652 Typical V<sub>DD2</sub> Supply Current vs. Data Rate 5, 3.3, and 2.5 V Operation (15 pF Load)

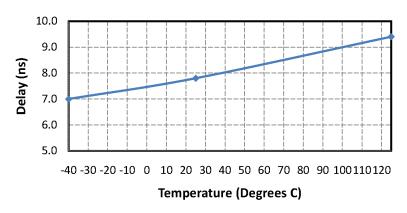

Figure 3.8. Propagation Delay vs. Temperature

## 4. Electrical Specifications

**Table 4.1. Recommended Operating Conditions**

| Parameter                                  | Symbol           | Min   | Тур | Max | Unit |

|--------------------------------------------|------------------|-------|-----|-----|------|

| Junction Operating Temperature             | TJ               | _     | _   | 150 | °C   |

| Ambient Operating Temperature <sup>1</sup> | T <sub>A</sub>   | -40   | 25  | 125 | °C   |

| Supply Voltage                             | V <sub>DD1</sub> | 2.375 | _   | 5.5 | V    |

| Supply Voltage                             | V <sub>DD2</sub> | 2.375 | _   | 5.5 | V    |

## Note:

**Table 4.2. Electrical Characteristics**

$(V_{DD1} = 5 V \pm 10\%, V_{DD2} = 5 V \pm 10\%, T_A = -40 \text{ to } 125 \text{ °C})$

| Parameter                         | Symbol             | Test Condition                              | Min                                      | Тур  | Max   | Unit |

|-----------------------------------|--------------------|---------------------------------------------|------------------------------------------|------|-------|------|

| VDD Undervoltage Threshold        | VDDUV+             | V <sub>DD1</sub> , V <sub>DD2</sub> rising  | 1.95                                     | 2.24 | 2.375 | V    |

| VDD Undervoltage Threshold        | VDDUV-             | V <sub>DD1</sub> , V <sub>DD2</sub> falling | 1.88                                     | 2.16 | 2.325 | V    |

| VDD Undervoltage<br>Hysteresis    | VDD <sub>HYS</sub> |                                             | 50                                       | 70   | 95    | mV   |

| Positive-Going Input Threshold    | VT+                | All inputs rising                           | 1.4                                      | 1.67 | 1.9   | V    |

| Negative-Going<br>Input Threshold | VT-                | All inputs falling                          | 1.0                                      | 1.23 | 1.4   | V    |

| Input Hysteresis                  | V <sub>HYS</sub>   |                                             | 0.38                                     | 0.44 | 0.50  | V    |

| High Level Input Voltage          | V <sub>IH</sub>    |                                             | 2.0                                      | _    | _     | V    |

| Low Level input voltage           | V <sub>IL</sub>    |                                             | _                                        | _    | 0.8   | V    |

| High Level Output Voltage         | V <sub>OH</sub>    | loh = –4 mA                                 | V <sub>DD1</sub> ,V <sub>DD2</sub> – 0.4 | 4.8  | _     | V    |

| Low Level Output Voltage          | V <sub>OL</sub>    | IoI = 4 mA                                  | _                                        | 0.2  | 0.4   | V    |

| Input Leakage Current             | ΙL                 |                                             | _                                        | _    | ±10   | μA   |

| Output Impedance 1                | Z <sub>O</sub>     |                                             | _                                        | 50   | _     | Ω    |

| Enable Input High Current         | I <sub>ENH</sub>   | V <sub>ENx</sub> = V <sub>IH</sub>          | _                                        | 2.0  | _     | μA   |

| Enable Input Low Current          | I <sub>ENL</sub>   | $V_{ENx} = V_{IL}$                          | _                                        | 2.0  | _     | μA   |

| DC Supply Current (All Inputs 0 V | or at Supply)      |                                             | ·                                        |      |       | I    |

| Si8650Bx, Ex, Si8655Bx            |                    |                                             |                                          |      |       |      |

| $V_{DD1}$                         |                    | $V_1 = 0(Bx), 1(Ex)$                        | _                                        | 1.1  | 1.8   | mA   |

| $V_{DD2}$                         |                    | $V_1 = 0(Bx), 1(Ex)$                        | _                                        | 3.1  | 4.7   |      |

| $V_{DD1}$                         |                    | $V_I = 1(Bx), 0(Ex)$                        | _                                        | 7.0  | 9.8   |      |

| $V_{DD2}$                         |                    | $V_1 = 1(Bx), 0(Ex)$                        | _                                        | 3.3  | 5.0   |      |

<sup>1.</sup> The maximum ambient temperature is dependent on data frequency, output loading, number of operating channels, and supply voltage.

| Parameter                          | Symbol       | Test Condition                      | Min                      | Тур      | Max  | Unit |

|------------------------------------|--------------|-------------------------------------|--------------------------|----------|------|------|

| Si8651Bx, Ex                       |              |                                     |                          |          |      |      |

| $V_{DD1}$                          |              | $V_{I} = 0(Bx), 1(Ex)$              | _                        | 1.5      | 2.4  | mA   |

| $V_{DD2}$                          |              | $V_{I} = 0(Bx), 1(Ex)$              | _                        | 2.7      | 4.1  |      |

| V <sub>DD1</sub>                   |              | $V_{I} = 1(Bx), 0(Ex)$              | _                        | 6.6      | 9.2  |      |

| $V_{DD2}$                          |              | $V_{I} = 1(Bx), 0(Ex)$              | _                        | 4.0      | 6.0  |      |

| Si8652Bx, Ex                       |              |                                     |                          |          |      |      |

| $V_{DD1}$                          |              | $V_{I} = 0(Bx), 1(Ex)$              | _                        | 2.0      | 3.0  | mA   |

| $V_{DD2}$                          |              | $V_I = 0(Bx), 1(Ex)$                | _                        | 2.4      | 3.6  |      |

| $V_{DD1}$                          |              | $V_I = 1(Bx), 0(Ex)$                | _                        | 5.6      | 7.8  |      |

| $V_{DD2}$                          |              | $V_{I} = 1(Bx), 0(Ex)$              | _                        | 5.0      | 7.5  |      |

| 1 Mbps Supply                      | Current (All | Inputs = 500 kHz Square Wa          | ive, CI = 15 pF on All ( | Dutputs) |      |      |

| Si8650Bx, Ex, Si8655Bx             |              |                                     |                          |          |      |      |

| $V_{DD1}$                          |              |                                     | _                        | 4.1      | 5.7  | mA   |

| $V_{DD2}$                          |              |                                     | _                        | 3.7      | 5.2  |      |

| Si8651Bx, Ex                       |              |                                     |                          |          |      |      |

| $V_{DD1}$                          |              |                                     | _                        | 4.2      | 5.8  | mA   |

| $V_{DD2}$                          |              |                                     | _                        | 3.8      | 5.3  |      |

| Si8652Bx, Ex                       |              |                                     |                          |          |      |      |

| $V_{DD1}$                          |              |                                     | _                        | 4.0      | 5.6  | mA   |

| $V_{DD2}$                          |              |                                     | _                        | 4.0      | 5.6  |      |

| 10 Mbps Supply Current (All Inputs | = 5 MHz Sq   | uare Wave, CI = 15 pF on All        | Outputs)                 |          |      |      |

| Si8650Bx, Ex, Si8655Bx             |              |                                     |                          |          |      |      |

| $V_{DD1}$                          |              |                                     | _                        | 4.1      | 5.7  | mA   |

| $V_{DD2}$                          |              |                                     | _                        | 5.2      | 7.2  |      |

| Si8651Bx, Ex                       |              |                                     |                          |          |      |      |

| V <sub>DD1</sub>                   |              |                                     | _                        | 4.4      | 6.2  | mA   |

| V <sub>DD2</sub>                   |              |                                     | _                        | 4.9      | 6.9  |      |

| Si8652Bx, Ex                       |              |                                     |                          |          |      |      |

| V <sub>DD1</sub>                   |              |                                     | _                        | 4.6      | 6.4  | mA   |

| V <sub>DD2</sub>                   |              |                                     | _                        | 4.9      | 6.8  |      |

| 100 Mbps Supply Current (All Input | s = 50 MHz   | Square Wave, CI = 15 pF on <i>I</i> | All Outputs)             | I        | I    | I    |

| Si8650Bx, Ex, Si8655Bx             |              |                                     |                          |          |      |      |

| $V_{DD1}$                          |              |                                     | _                        | 4.1      | 5.7  | mA   |

| V <sub>DD2</sub>                   |              |                                     | _                        | 22.1     | 28.7 |      |

| Si8651Bx, Ex                       |              |                                     |                          |          |      |      |

| Parameter                                                      | Symbol                              | Test Condition                                                                                              | Min | Тур  | Max  | Unit  |

|----------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| V <sub>DD1</sub>                                               |                                     |                                                                                                             | _   | 8.0  | 10.8 | mA    |

| $V_{DD2}$                                                      |                                     |                                                                                                             | _   | 18.4 | 24   |       |

| Si8652Bx, Ex                                                   |                                     |                                                                                                             |     |      |      |       |

| $V_{DD1}$                                                      |                                     |                                                                                                             | _   | 11.7 | 15.2 | mA    |

| $V_{DD2}$                                                      |                                     |                                                                                                             | _   | 15   | 19.5 |       |

| Timing Characteristics                                         |                                     |                                                                                                             | l   |      |      |       |

| Si865xBx, Ex                                                   |                                     |                                                                                                             |     |      |      |       |

| Maximum Data Rate                                              |                                     |                                                                                                             | 0   | _    | 150  | Mbps  |

| Minimum Pulse Width                                            |                                     |                                                                                                             | _   | _    | 5.0  | ns    |

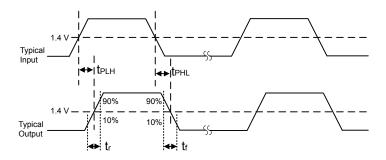

| Propagation Delay                                              | t <sub>PHL</sub> , t <sub>PLH</sub> | See Figure 4.2 Propagation<br>Delay Timing on page 15                                                       | 5.0 | 8.0  | 13   | ns    |

| Pulse Width Distortion<br> t <sub>PLH</sub> – t <sub>PHL</sub> | PWD                                 | See Figure 4.2 Propagation<br>Delay Timing on page 15                                                       | _   | 0.2  | 4.5  | ns    |

| Propagation Delay Skew <sup>2</sup>                            | t <sub>PSK(P-P)</sub>               |                                                                                                             | _   | 2.0  | 4.5  | ns    |

| Channel-Channel Skew                                           | t <sub>PSK</sub>                    |                                                                                                             | _   | 0.4  | 2.5  | ns    |

| All Models                                                     |                                     |                                                                                                             |     |      | I    | 1     |

| Output Rise Time                                               | t <sub>r</sub>                      | C <sub>L</sub> = 15 pF                                                                                      | _   | 2.5  | 4.0  | ns    |

|                                                                |                                     | See Figure 4.2 Propagation<br>Delay Timing on page 15                                                       |     |      |      |       |

| Output Fall Time                                               | t <sub>f</sub>                      | C <sub>L</sub> = 15 pF                                                                                      | _   | 2.5  | 4.0  | ns    |

|                                                                |                                     | See Figure 4.2 Propagation<br>Delay Timing on page 15                                                       |     |      |      |       |

| Peak eye diagram jitter                                        | t <sub>JIT(PK)</sub>                | See Figure 2.3 Eye Diagram on page 6                                                                        | _   | 350  | _    | ps    |

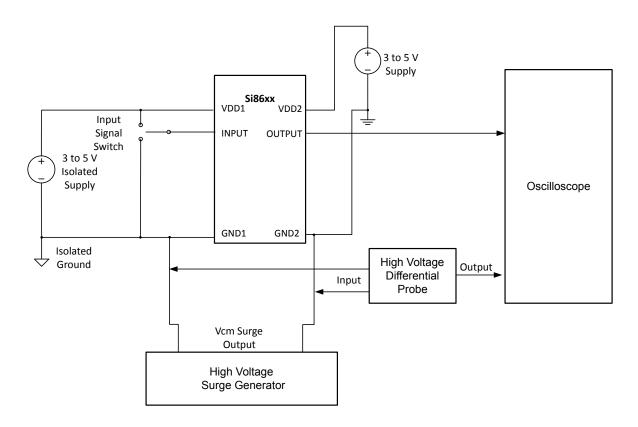

| Common Mode                                                    | CMTI                                | V <sub>I</sub> = V <sub>DD</sub> or 0 V                                                                     | 35  | 50   | _    | kV/µs |

| Transient Immunity                                             |                                     | V <sub>CM</sub> = 1500 V (see Figure<br>4.3 Common Mode Transi-<br>ent Immunity Test Circuit on<br>page 15) |     |      |      |       |

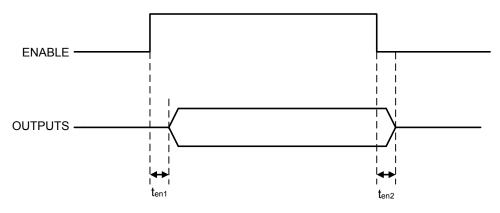

| Enable to Data Valid                                           | t <sub>en1</sub>                    | See Figure 4.1 ENABLE<br>Timing Diagram on page<br>15                                                       | _   | 6.0  | 11   | ns    |

| Enable to Data Tri-State                                       | t <sub>en2</sub>                    | See Figure 4.1 ENABLE<br>Timing Diagram on page<br>15                                                       | _   | 8.0  | 12   | ns    |

| Start-up Time <sup>3</sup>                                     | t <sub>SU</sub>                     |                                                                                                             | _   | 15   | 40   | μs    |

- 1. The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ , ±40%, which is a combination of the value of the on-chip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be appropriately terminated with controlled impedance PCB traces.

- 2. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

- 3. Start-up time is the time period from the application of power to valid data at the output.

Figure 4.1. ENABLE Timing Diagram

Figure 4.2. Propagation Delay Timing

Figure 4.3. Common Mode Transient Immunity Test Circuit

**Table 4.3. Electrical Characteristics**

$(V_{DD1} = 3.3 \ V \pm 10\%, \ V_{DD2} = 3.3 \ V \pm 10\%, \ T_A = -40 \ to \ 125 \ ^{\circ}C)$

| Parameter                           | Symbol             | Test Condition                              | Min                                      | Тур  | Max   | Unit |

|-------------------------------------|--------------------|---------------------------------------------|------------------------------------------|------|-------|------|

| VDD Undervoltage Threshold          | VDDUV+             | V <sub>DD1</sub> , V <sub>DD2</sub> rising  | 1.95                                     | 2.24 | 2.375 | V    |

| VDD Undervoltage Threshold          | VDDUV-             | V <sub>DD1</sub> , V <sub>DD2</sub> falling | 1.88                                     | 2.16 | 2.325 | V    |

| VDD Undervoltage<br>Hysteresis      | VDD <sub>HYS</sub> |                                             | 50                                       | 70   | 95    | mV   |

| Positive-Going Input Threshold      | VT+                | All inputs rising                           | 1.4                                      | 1.67 | 1.9   | V    |

| Negative-Going Input Threshold      | VT–                | All inputs falling                          | 1.0                                      | 1.23 | 1.4   | V    |

| Input Hysteresis                    | V <sub>HYS</sub>   |                                             | 0.38                                     | 0.44 | 0.50  | V    |

| High Level Input Voltage            | V <sub>IH</sub>    |                                             | 2.0                                      | _    | _     | V    |

| Low Level Input Voltage             | V <sub>IL</sub>    |                                             | _                                        | _    | 0.8   | V    |

| High Level Output Voltage           | V <sub>OH</sub>    | loh = –4 mA                                 | V <sub>DD1</sub> ,V <sub>DD2</sub> – 0.4 | 3.1  | _     | V    |

| Low Level Output Voltage            | V <sub>OL</sub>    | IoI = 4 mA                                  | _                                        | 0.2  | 0.4   | V    |

| Input Leakage Current               | ΙL                 |                                             | _                                        | _    | ±10   | μA   |

| Output Impedance 1                  | Z <sub>O</sub>     |                                             | _                                        | 50   | _     | Ω    |

| Enable Input High Current           | I <sub>ENH</sub>   | V <sub>ENx</sub> = V <sub>IH</sub>          | _                                        | 2.0  | _     | μA   |

| Enable Input Low Current            | I <sub>ENL</sub>   | $V_{ENx} = V_{IL}$                          | _                                        | 2.0  | _     | μA   |

| DC Supply Current (all Inputs 0 V o | r at Supply)       |                                             |                                          |      |       |      |

| Si8650Bx, Ex, Si8655Bx              |                    |                                             |                                          |      |       |      |

| $V_{DD1}$                           |                    | $V_I = 0(Bx), 1(Ex)$                        | _                                        | 1.1  | 1.8   | mA   |

| $V_{DD2}$                           |                    | $V_I = 0(Bx), 1(Ex)$                        | _                                        | 3.1  | 4.7   |      |

| $V_{DD1}$                           |                    | $V_I = 1(Bx), 0(Ex)$                        | _                                        | 7.0  | 9.8   |      |

| $V_{DD2}$                           |                    | $V_{I} = 1(Bx), 0(Ex)$                      | _                                        | 3.3  | 5.0   |      |

| Si8651Bx, Ex                        |                    |                                             |                                          |      |       |      |

| $V_{DD1}$                           |                    | $V_I = 0(Bx), 1(Ex)$                        | _                                        | 1.5  | 2.4   | mA   |

| $V_{DD2}$                           |                    | $V_I = 0(Bx), 1(Ex)$                        | _                                        | 2.7  | 4.1   |      |

| V <sub>DD1</sub>                    |                    | $V_I = 1(Bx), 0(Ex)$                        | _                                        | 6.6  | 9.2   |      |

| $V_{DD2}$                           |                    | $V_{I} = 1(Bx), 0(Ex)$                      | _                                        | 4.0  | 6.0   |      |

| Si8652Bx, Ex                        |                    |                                             |                                          |      |       |      |

| $V_{DD1}$                           |                    | $V_I = 0(Bx), 1(Ex)$                        | _                                        | 2.0  | 3.0   | mA   |

| $V_{DD2}$                           |                    | $V_I = 0(Bx), 1(Ex)$                        | _                                        | 2.4  | 3.6   |      |

| $V_{DD1}$                           |                    | $V_{I} = 1(Bx), 0(Ex)$                      | _                                        | 5.6  | 7.8   |      |

| V <sub>DD2</sub>                    |                    | $V_{I} = 1(Bx), 0(Ex)$                      | _                                        | 5.0  | 7.5   |      |

| 1 Mbps Supply Current (All Inputs   | ∟<br>= 500 kHz Sq  | uare Wave, CI = 15 pF on A                  | II Outputs)                              | 1    |       |      |

| Si8650Bx, Ex, Si8655Bx              |                    |                                             |                                          |      |       |      |

| Parameter                                                      | Symbol                              | Test Condition                                        | Min          | Тур  | Max  | Unit |

|----------------------------------------------------------------|-------------------------------------|-------------------------------------------------------|--------------|------|------|------|

| V <sub>DD1</sub>                                               |                                     |                                                       | _            | 4.1  | 5.7  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 3.7  | 5.2  |      |

| Si8651Bx, Ex                                                   |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 4.2  | 5.8  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 3.8  | 5.3  |      |

| Si8652Bx, Ex                                                   |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 4.0  | 5.6  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 4.0  | 5.6  |      |

| 10 Mbps Supply Current (All Input                              | s = 5 MHz Sq                        | uare Wave, CI = 15 pF on All                          | Outputs)     |      |      |      |

| Si8650Bx, Ex, Si8655Bx                                         |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 4.1  | 5.7  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 4.4  | 6.1  |      |

| Si8651Bx, Ex                                                   |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 4.3  | 6.0  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 4.3  | 6.0  |      |

| Si8652Bx, Ex                                                   |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 4.3  | 6.0  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 4.4  | 6.1  |      |

| 100 Mbps Supply Current (All Inpu                              | its = 50 MHz                        | Square Wave, CI = 15 pF on <i>F</i>                   | All Outputs) |      |      |      |

| Si8650Bx, Ex, Si8655Bx                                         |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 4.1  | 5.7  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 15.5 | 20.1 |      |

| Si8651Bx, Ex                                                   |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 6.6  | 8.9  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 13.2 | 17.1 |      |

| Si8652Bx, Ex                                                   |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 8.9  | 11.6 | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 11.1 | 14.4 |      |

| Timing Characteristics                                         |                                     |                                                       |              |      |      |      |

| Si865xBx, Ex                                                   |                                     |                                                       |              |      |      |      |

| Maximum Data Rate                                              |                                     |                                                       | 0            | _    | 150  | Mbps |

| Minimum Pulse Width                                            |                                     |                                                       | _            | _    | 5.0  | ns   |

| Propagation Delay                                              | t <sub>PHL</sub> , t <sub>PLH</sub> | See Figure 4.2 Propagation<br>Delay Timing on page 15 | 5.0          | 8.0  | 13   | ns   |

| Pulse Width Distortion<br> t <sub>PLH</sub> - t <sub>PHL</sub> | PWD                                 | See Figure 4.2 Propagation<br>Delay Timing on page 15 | _            | 0.2  | 4.5  | ns   |

| Parameter                           | Symbol                | Test Condition                                                                                                              | Min | Тур | Max | Unit  |

|-------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Propagation Delay Skew <sup>2</sup> | t <sub>PSK(P-P)</sub> |                                                                                                                             | _   | 2.0 | 4.5 | ns    |

| Channel-Channel Skew                | t <sub>PSK</sub>      |                                                                                                                             | _   | 0.4 | 2.5 | ns    |

| All Models                          |                       |                                                                                                                             |     |     |     |       |

| Output Rise Time                    | t <sub>r</sub>        | C <sub>L</sub> = 15 pF  See Figure 4.2 Propagation Delay Timing on page 15                                                  | _   | 2.5 | 4.0 | ns    |

| Output Fall Time                    | t <sub>f</sub>        | C <sub>L</sub> = 15 pF  (See Figure 4.2 Propagation Delay Timing on page 15)                                                | _   | 2.5 | 4.0 | ns    |

| Peak eye diagram jitter             | t <sub>JIT(PK)</sub>  | See Figure 2.3 Eye Diagram on page 6                                                                                        | _   | 350 | _   | ps    |

| Common Mode Transient Immunity      | СМТІ                  | $V_I = V_{DD}$ or 0 V<br>$V_{CM} = 1500$ V<br>(See Figure 4.3 Common<br>Mode Transient Immunity<br>Test Circuit on page 15) | 35  | 50  | _   | kV/µs |

| Enable to Data Valid                | t <sub>en1</sub>      | See Figure 4.1 ENABLE<br>Timing Diagram on page 15                                                                          | _   | 6.0 | 11  | ns    |

| Enable to Data Tri-State            | t <sub>en2</sub>      | See Figure 4.1 ENABLE<br>Timing Diagram on page 15                                                                          | _   | 8.0 | 12  | ns    |

| Start-Up Time <sup>3</sup>          | t <sub>SU</sub>       |                                                                                                                             | _   | 15  | 40  | μs    |

- 1. The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ , ±40%, which is a combination of the value of the on-chip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be appropriately terminated with controlled impedance PCB traces.

- 2. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

- 3. Start-up time is the time period from the application of power to valid data at the output.

## **Table 4.4. Electrical Characteristics**

(V<sub>DD1</sub> = 2.5 V ±5%, V<sub>DD2</sub> = 2.5 V ±5%, T<sub>A</sub> = –40 to 125 °C)

| Parameter                      | Symbol             | Test Condition                              | Min                                      | Тур  | Max   | Unit |

|--------------------------------|--------------------|---------------------------------------------|------------------------------------------|------|-------|------|

| VDD Undervoltage Threshold     | VDDUV+             | $V_{DD1}$ , $V_{DD2}$ rising                | 1.95                                     | 2.24 | 2.375 | V    |

| VDD Undervoltage Threshold     | VDDUV-             | V <sub>DD1</sub> , V <sub>DD2</sub> falling | 1.88                                     | 2.16 | 2.325 | V    |

| VDD Undervoltage Hysteresis    | VDD <sub>HYS</sub> |                                             | 50                                       | 70   | 95    | mV   |

| Positive-Going Input Threshold | VT+                | All inputs rising                           | 1.4                                      | 1.67 | 1.9   | V    |

| Negative-Going Input Threshold | VT–                | All inputs falling                          | 1.0                                      | 1.23 | 1.4   | V    |

| Input Hysteresis               | V <sub>HYS</sub>   |                                             | 0.38                                     | 0.44 | 0.50  | V    |

| High Level Input Voltage       | V <sub>IH</sub>    |                                             | 2.0                                      | _    | _     | V    |

| Low Level Input Voltage        | V <sub>IL</sub>    |                                             | _                                        | _    | 0.8   | V    |

| High Level Output Voltage      | V <sub>OH</sub>    | loh = –4 mA                                 | V <sub>DD1</sub> ,V <sub>DD2</sub> – 0.4 | 2.3  | _     | V    |

| Parameter                           | Symbol           | Test Condition                     | Min      | Тур | Max | Unit |

|-------------------------------------|------------------|------------------------------------|----------|-----|-----|------|

| Low Level Output Voltage            | V <sub>OL</sub>  | IoI = 4 mA                         | _        | 0.2 | 0.4 | V    |

| Input Leakage Current               | ΙL               |                                    | _        | _   | ±10 | μA   |

| Output Impedance <sup>1</sup>       | Z <sub>O</sub>   |                                    | _        | 50  | _   | Ω    |

| Enable Input High Current           | I <sub>ENH</sub> | V <sub>ENx</sub> = V <sub>IH</sub> | _        | 2.0 | _   | μA   |

| Enable Input Low Current            | I <sub>ENL</sub> | $V_{ENx} = V_{IL}$                 | _        | 2.0 | _   | μA   |

| DC Supply Current (All Inputs 0 V o | or at Supply)    |                                    | L        |     |     |      |

| Si8650Bx, Ex, Si8655Bx              |                  |                                    |          |     |     |      |

| $V_{DD1}$                           |                  | $V_1 = 0(Bx), 1(Ex)$               | _        | 1.1 | 1.8 | mA   |

| $V_{DD2}$                           |                  | $V_{I} = 0(Bx), 1(Ex)$             | _        | 3.1 | 4.7 |      |

| V <sub>DD1</sub>                    |                  | $V_I = 1(Bx), 0(Ex)$               | _        | 7.0 | 9.8 |      |

| $V_{DD2}$                           |                  | $V_1 = 1(Bx), 0(Ex)$               | _        | 3.3 | 5.0 |      |

| Si8651Bx, Ex                        |                  |                                    |          |     |     |      |

| V <sub>DD1</sub>                    |                  | $V_1 = 0(Bx), 1(Ex)$               | _        | 1.5 | 2.4 | mA   |

| $V_{DD2}$                           |                  | $V_I = 0(Bx), 1(Ex)$               | _        | 2.7 | 4.1 |      |

| V <sub>DD1</sub>                    |                  | $V_{I} = 1(Bx), 0(Ex)$             | _        | 6.6 | 9.2 |      |

| $V_{DD2}$                           |                  | $V_I = 1(Bx), 0(Ex)$               | _        | 4.0 | 6.0 |      |

| Si8652Bx, Ex                        |                  |                                    |          |     |     |      |

| V <sub>DD1</sub>                    |                  | $V_I = 0(Bx), 1(Ex)$               | _        | 2.0 | 3.0 | mA   |

| $V_{DD2}$                           |                  | $V_I = 0(Bx), 1(Ex)$               | _        | 2.4 | 3.6 |      |

| $V_{DD1}$                           |                  | $V_I = 1(Bx), 0(Ex)$               | _        | 5.6 | 7.8 |      |

| $V_{DD2}$                           |                  | $V_I = 1(Bx), 0(Ex)$               | _        | 5.0 | 7.5 |      |

| 1 Mbps Supply Current (All Inputs : | = 500 kHz Sq     | uare Wave, CI = 15 pF on All       | Outputs) |     |     |      |

| Si8650Bx, Ex, Si8655Bx              |                  |                                    |          |     |     |      |

| $V_{DD1}$                           |                  |                                    | _        | 4.1 | 5.7 | mA   |

| $V_{DD2}$                           |                  |                                    | _        | 3.7 | 5.2 |      |

| Si8651Bx, Ex                        |                  |                                    |          |     |     |      |

| $V_{DD1}$                           |                  |                                    | _        | 4.2 | 5.8 | mA   |

| $V_{DD2}$                           |                  |                                    | _        | 3.8 | 5.3 |      |

| Si8652Bx, Ex                        |                  |                                    |          |     |     |      |

| $V_{DD1}$                           |                  |                                    | _        | 4.0 | 5.6 | mA   |

| $V_{DD2}$                           |                  |                                    | _        | 4.0 | 5.6 |      |

| 10 Mbps Supply Current (All Inputs  | = 5 MHz Sq       | uare Wave, CI = 15 pF on All       | Outputs) |     |     |      |

| Si8650Bx, Ex, Si8655Bx              |                  |                                    |          |     |     |      |

| $V_{DD1}$                           |                  |                                    | _        | 4.1 | 5.7 | mA   |

| $V_{DD2}$                           |                  |                                    | _        | 4.0 | 5.6 |      |

| Parameter                                                      | Symbol                              | Test Condition                                        | Min          | Тур  | Max  | Unit |

|----------------------------------------------------------------|-------------------------------------|-------------------------------------------------------|--------------|------|------|------|

| Si8651Bx, Ex                                                   |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 4.2  | 5.9  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 4.0  | 5.6  |      |

| Si8652Bx, Ex                                                   |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 4.1  | 5.8  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 4.2  | 5.9  |      |

| 100 Mbps Supply Current (All Ing                               | outs = 50 MHz                       | ⊔<br>Square Wave, Cl = 15 pF on <i>A</i>              | All Outputs) |      |      |      |

| Si8650Bx, Ex, Si8655Bx                                         |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 4.1  | 5.7  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 12.5 | 16.2 |      |

| Si8651Bx, Ex                                                   |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 6.0  | 8.1  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 10.8 | 14   |      |

| Si8652Bx, Ex                                                   |                                     |                                                       |              |      |      |      |

| $V_{DD1}$                                                      |                                     |                                                       | _            | 7.6  | 9.9  | mA   |

| $V_{DD2}$                                                      |                                     |                                                       | _            | 9.3  | 12.0 |      |

| Timing Characteristics                                         |                                     |                                                       |              |      |      |      |

| Si865xBx, Ex                                                   |                                     |                                                       |              |      |      |      |

| Maximum Data Rate                                              |                                     |                                                       | 0            | _    | 150  | Mbps |

| Minimum Pulse Width                                            |                                     |                                                       | _            | _    | 5.0  | ns   |

| Propagation Delay                                              | t <sub>PHL</sub> , t <sub>PLH</sub> | See Figure 4.2 Propagation<br>Delay Timing on page 15 | 5.0          | 8.0  | 14   | ns   |

| Pulse Width Distortion<br> t <sub>PLH</sub> - t <sub>PHL</sub> | PWD                                 | See Figure 4.2 Propagation<br>Delay Timing on page 15 | _            | 0.2  | 5.0  | ns   |

| Propagation Delay Skew <sup>2</sup>                            | t <sub>PSK(P-P)</sub>               |                                                       | _            | 2.0  | 5.0  | ns   |

| Channel-Channel Skew                                           | t <sub>PSK</sub>                    |                                                       | _            | 0.4  | 2.5  | ns   |

| All Models                                                     |                                     |                                                       |              |      |      |      |

| Output Rise Time                                               | t <sub>r</sub>                      | C <sub>L</sub> = 15 pF                                | _            | 2.5  | 4.0  | ns   |

|                                                                |                                     | See Figure 4.2 Propagation<br>Delay Timing on page 15 |              |      |      |      |

| Output Fall Time                                               | t <sub>f</sub>                      | C <sub>L</sub> = 15 pF                                | _            | 2.5  | 4.0  | ns   |

|                                                                |                                     | See Figure 4.2 Propagation<br>Delay Timing on page 15 |              |      |      |      |

| Peak Eye Diagram Jitter                                        | t <sub>JIT(PK)</sub>                | See Figure 2.3 Eye Diagram on page 6                  | _            | 350  | _    | ps   |

| Parameter                      | Symbol           | Test Condition                                                                                              | Min | Тур | Max | Unit  |

|--------------------------------|------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Common Mode Transient Immunity | CMTI             | $V_I = V_{DD}$ or 0 V                                                                                       | 35  | 50  | _   | kV/μs |

|                                |                  | V <sub>CM</sub> = 1500 V (See Figure<br>4.3 Common Mode Transi-<br>ent Immunity Test Circuit on<br>page 15) |     |     |     |       |

| Enable to Data Valid           | t <sub>en1</sub> | See Figure 4.1 ENABLE<br>Timing Diagram on page 15                                                          | _   | 6.0 | 11  | ns    |

| Enable to Data Tri-State       | t <sub>en2</sub> | See Figure 4.1 ENABLE<br>Timing Diagram on page 15                                                          | _   | 8.0 | 12  | ns    |

| Startup Time <sup>3</sup>      | t <sub>SU</sub>  |                                                                                                             | _   | 15  | 40  | μs    |

- 1. The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ , ±40%, which is a combination of the value of the on-chip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be appropriately terminated with controlled impedance PCB traces.

- 2. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

- 3. Start-up time is the time period from the application of power to valid data at the output.

## Table 4.5. Regulatory Information <sup>1</sup>

#### CSA

The Si865x is certified under CSA Component Acceptance Notice 5A. For more details, see Master Contract Number 232873.

60950-1, 62368-1: Up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

60601-1: Up to 250 V<sub>RMS</sub> working voltage and 2 MOPP (Means of Patient Protection).

#### **VDE**