# LIS25BA

# MEMS digital output motion sensor: low-noise, high-bandwidth 3-axis accelerometer with TDM interface

Datasheet - production data

#### **Features**

- ±3.85 g full scale

- · TDM slave interface

- Low noise

- Signal bandwidth 2400 Hz

- · High, flat bandwidth

- 16-bit data output

- 20000 g high shock survivability

- Lead-free, ECOPACK, RoHS and "Green" compliant

# **Description**

The LIS25BA is a low-noise high-bandwidth three-axis digital accelerometer with a dedicated TDM interface.

The LIS25BA has a full scale of  $\pm 3.85~g$  and works with a Time-Division Multiplexing (TDM) interface.

The LIS25BA is available in a small thin plastic land grid array package (LGA) and is guaranteed to operate over an extended temperature range from -40 °C to +85 °C.

Table 1. Device summary

| Order codes | Temp.<br>range [°C] | Package | Packaging     |

|-------------|---------------------|---------|---------------|

| LIS25BA     | -40 to +85          | LGA-14  | Tray          |

| LIS25BATR   | -40 to +85          | LGA-14  | Tape and reel |

Contents LIS25BA

# **Contents**

| 1 | Pin (             | description 6                              |

|---|-------------------|--------------------------------------------|

| 2 | Mec               | hanical and electrical specifications7     |

|   | 2.1               | Mechanical characteristics                 |

|   | 2.2               | Electrical characteristics                 |

|   | 2.3               | Absolute maximum ratings                   |

| 3 | TDM               | l interface characteristics11              |

|   | 3.1               | I <sup>2</sup> C interface characteristics |

| 4 | TDM               | l interface specifications15               |

|   | 4.1               | TDM interface overview                     |

|   | 4.2               | Frame synchronization (WCLK)               |

|   | 4.3               | Serial clock (BCLK) 16                     |

|   | 4.4               | TDM axes mapping                           |

|   | 4.5               | TDM configurations                         |

|   |                   | 4.5.1 Configuration 1                      |

|   |                   | 4.5.2 Configuration 2                      |

|   |                   | 4.5.3 Configuration 3                      |

|   |                   | 4.5.4 Configuration 4                      |

|   | 4.6               | TDM clocks and MCLK requirements           |

|   | 4.7               | I <sup>2</sup> C axis disable              |

| 5 | I <sup>2</sup> C- | inter-IC control interface21               |

|   | 5.1               | I <sup>2</sup> C interface                 |

|   | 5.2               | I <sup>2</sup> C interface details         |

|   | 5.3               | I <sup>2</sup> C slave address             |

|   | 5.4               | I <sup>2</sup> C read and write sequences  |

| 6 | Feat              | ures 23                                    |

|   | 6.1               | Self-test mode                             |

|   | 6.2               | Power cycle/reset information              |

|   |                   | 6.2.1 TDM interface power-on sequence      |

|   |                   |                                            |

LIS25BA Contents

|    |      | 6.2.2 D     | Disabled mode      | 2 | 4 |

|----|------|-------------|--------------------|---|---|

| 7  | Regi | ster mapp   | ing                |   | 5 |

| 8  | Regi | ster descr  | ription            |   | 6 |

|    | 8.1  | TEST_RE     | EG (0Bh)           |   | 6 |

|    | 8.2  | WHO_AM      | 1_I (0Fh)          |   | 6 |

|    | 8.3  | TDM_cma     | ax (24h-25h)       |   | 6 |

|    | 8.4  | CTRL_RE     | EG (26h)           |   | 6 |

|    | 8.5  | TDM_CTF     | RL_REG (2Eh)       | 2 | 7 |

|    | 8.6  | AXES_CT     | FRL_REG (2Fh)      | 2 | 7 |

| 9  | Pack | kage inforr | mation             |   | 8 |

|    | 9.1  | LGA-14 p    | ackage information |   | 8 |

|    | 9.2  | LGA-14 p    | acking information |   | 9 |

| 10 | Revi | sion histo  | ry                 |   | 1 |

List of tables LIS25BA

# List of tables

| Table 1.  | Device summary                                                                | 1  |

|-----------|-------------------------------------------------------------------------------|----|

| Table 2.  | Pin description                                                               | 6  |

| Table 3.  | Mechanical characteristics                                                    | 7  |

| Table 4.  | Electrical characteristics                                                    |    |

| Table 5.  | Absolute maximum ratings                                                      | 10 |

| Table 6.  | TDM interface characteristics                                                 |    |

| Table 7.  | Digital input/output voltage for I <sup>2</sup> C pins                        | 12 |

| Table 8.  | I <sup>2</sup> C interface characteristics                                    |    |

| Table 9.  | I <sup>2</sup> C high-speed mode specifications at 1 MHz                      | 14 |

| Table 10. | I <sup>2</sup> C serial interface pin description                             | 21 |

| Table 11. | I <sup>2</sup> C terminology                                                  | 21 |

| Table 12. | Transfer when master is writing one byte to slave                             | 22 |

| Table 13. | Transfer when master is writing multiple bytes to slave                       | 22 |

| Table 14. | Transfer when master is receiving (reading) one byte of data from slave       | 22 |

| Table 15. | Transfer when master is receiving (reading) multiple bytes of data from slave | 22 |

| Table 16. | Register address map                                                          | 25 |

| Table 17. | TEST_REG register                                                             | 26 |

| Table 18. | TEST_REG register description                                                 | 26 |

| Table 19. | WHO_AM_I register                                                             | 26 |

| Table 20. | TDM_cmax register                                                             | 26 |

| Table 21. | CTRL_REG register                                                             | 26 |

| Table 22. | CTRL_REG register description                                                 | 26 |

| Table 23. | TDM_CTRL_REG register                                                         | 27 |

| Table 24. | TDM_CTRL_REG register description                                             | 27 |

| Table 25. | AXES_CTRL_REG register                                                        |    |

| Table 26. | AXES_CTRL_REG register description                                            | 27 |

| Table 27. | Reel dimensions for carrier tape of LGA-14 package                            | 30 |

| Table 28  | Document revision history                                                     | 31 |

LIS25BA List of figures

# **List of figures**

| Figure 1.  | Pin connections                                            | . 6 |

|------------|------------------------------------------------------------|-----|

| Figure 2.  | RMS noise (in band)                                        |     |

| Figure 3.  | RMS noise (out of band)                                    |     |

| Figure 4.  | TDM interface characteristics                              | 12  |

| Figure 5.  | I <sup>2</sup> C slave timing diagram                      | 13  |

| Figure 6.  | TDM block diagram                                          | 15  |

| Figure 7.  | Axes X, Y, Z mapped to SLOT0, SLOT1, SLOT2                 | 17  |

| Figure 8.  | Axes X, Y, Z mapped to SLOT4, SLOT5, SLOT6                 | 17  |

| Figure 9.  | WCLK, SDOUT change on the falling edge of BCLK             |     |

|            | and are valid on the rising edge of BCLK, no delay         | 18  |

| Figure 10. | WCLK, SDOUT change on the rising edge of BCLK              |     |

|            | and are valid on the falling edge of BCLK, no delay        | 18  |

| Figure 11. | WCLK, SDOUT change on the falling edge of BCLK             |     |

|            | and are valid on the rising edge of BCLK, delayed          | 19  |

| Figure 12. | WCLK, SDOUT change on the rising edge of BCLK              |     |

|            | and are valid on the falling edge of BCLK, delayed         |     |

| Figure 13. | Power-on sequence (TDM interface)                          | 23  |

| Figure 14. | Disabled mode sequence                                     |     |

| Figure 15. | LGA-14 2.5x2.5x0.86 mm package outline and mechanical data |     |

| Figure 16. | Carrier tape information for LGA-14 package                |     |

| Figure 17. | LGA-14 package orientation in carrier tape                 |     |

| Figure 18. | Reel information for carrier tape of LGA-14 package        | 30  |

Pin description LIS25BA

# 1 Pin description

Figure 1. Pin connections RES (GND) RES (GND) RES (GND) 14 12 13 1 I2C\_SCL I2C\_A0 11 LGA 14L 2.5x2.5x0.86mm 2 I2C\_SDA RES (VDD) 10 (TOP VIEW) 3 TDM\_BCLK 9 **BOTTOM** DIRECTION OF THE DETECTABLE ACCELERATIONS **GND VIEW** VDD 8 4 TDM\_WCLK Decoupling ceramic capacitor of 10µF 6 has to be placed between VDD and GND pins TDM\_MCLK RES (GND) TDM\_SDOUT

Table 2. Pin description

| Pin# | Name                   | IN/OUT | Function                                 |

|------|------------------------|--------|------------------------------------------|

| 1    | I2C_SCL <sup>(1)</sup> | IN     | l²C serial clock - SCL                   |

| 2    | I2C_SDA <sup>(1)</sup> | IN/OUT | I <sup>2</sup> C serial data - SDA       |

| 3    | TDM_BCLK               | IN     | TDM bit clock                            |

| 4    | TDM_WCLK               | IN     | TDM word clock                           |

| 5    | TDM_SDOUT              | OUT    | TDM serial data output                   |

| 6    | RES (GND)              | -      | Reserved pin (connect to GND)            |

| 7    | TDM_MCLK               | IN     | TDM master clock                         |

| 8    | VDD                    |        | Power supply                             |

| 9    | GND                    |        | 0 V supply                               |

| 10   | RES (VDD)              | -      | Reserved pin (connect to VDD)            |

| 11   | I2C_A0                 | IN     | I <sup>2</sup> C slave address selection |

| 12   | RES (GND)              | -      | Reserved pin (connect to GND)            |

| 13   | RES (GND)              | -      | Reserved pin (connect to GND)            |

| 14   | RES (GND)              | -      | Reserved pin (connect to GND)            |

<sup>1.</sup> Only for test and trim. I<sup>2</sup>C timing values are not guaranteed.

# 2 Mechanical and electrical specifications

### 2.1 Mechanical characteristics

@ Vdd = 1.8 V, T = 25 °C unless otherwise noted<sup>(a)</sup>.

**Table 3. Mechanical characteristics**

| Symbol | Parameter                                           | Test conditions                                                            | Min.   | Typ. <sup>(1)</sup> | Max.   | Unit           |

|--------|-----------------------------------------------------|----------------------------------------------------------------------------|--------|---------------------|--------|----------------|

| FS     | Measurement range                                   | After factory calibration (trimming performed with 1 <i>g</i> DC stimulus) | 3.26   | 3.85                | 4.16   | g              |

|        |                                                     | After factory calibration (trimming performed with 1 <i>g</i> DC stimulus) | 0.112  | 0.122               | 0.132  | mg/LSB         |

| So     | Sensitivity                                         | After factory calibration (trimming performed with 1 <i>g</i> DC stimulus) | -11.37 | -11.71              | -12.38 | dBFS/g         |

|        |                                                     | After factory calibration - 100 Hz 1 grms sine stimulus                    | -8.37  | -8.71               | -9.38  | dBFS/grms      |

| TCSo   | Sensitivity change vs. temperature                  |                                                                            | -0.08  |                     | +0.08  | %/°C           |

| TyOff  | Zero-g level offset accuracy                        |                                                                            | -300   |                     | +300   | m <i>g</i>     |

| TCOff  | Zero-g level change vs. temperature                 |                                                                            | -3.5   |                     | +3.5   | m <i>g</i> /°C |

| An     | Acceleration noise                                  | X-axis, Y-axis, FS = $\pm 3.85 g$ , BW = 2400 Hz                           |        |                     | 1.5    | ma rmo         |

| All    |                                                     | Z-axis, FS = ±3.85 g, BW = 2400 Hz                                         |        |                     | 2.4    | mg rms         |

| BW     | Signal bandwidth <sup>(2)</sup> (DC coupling)       | MCLK accuracy ±0.1%                                                        |        | 2400                |        | Hz             |

| NL     | Non-linearity <sup>(3)</sup>                        |                                                                            | -2     |                     | +2     | %FS            |

|        | Mechanical resonant                                 | X-axis                                                                     |        | 5150                |        | Hz             |

| RFm    | frequency of the                                    | Y-axis                                                                     |        | 5150                |        | Hz             |

|        | MEMS element                                        | Z-axis                                                                     |        | 4950                |        | Hz             |

|        |                                                     | X-axis                                                                     | 300    |                     | 950    | m <i>g</i>     |

| ST     | Self-test <sup>(4)</sup>                            | Y-axis                                                                     | 300    |                     | 950    | m <i>g</i>     |

|        |                                                     | Z-axis                                                                     | 500    |                     | 2700   | m <i>g</i>     |

| THD+N  | Total Harmonic<br>Distortion + Noise <sup>(5)</sup> | @ sinusoidal vibration of 1 <i>g</i> peak, freq = 1 kHz                    |        | _                   | 1      | %              |

<sup>1.</sup> Typical specifications are not guaranteed.

a. The product is factory calibrated at 1.8 V. The operational power supply range is from 1.71 V to 1.99 V.

DocID031510 Rev 4

<sup>2.</sup> By design.

<sup>3.</sup> MEMS non-linearity based on simulation data.

<sup>4.</sup> Values are based on preliminary corner simulation data.

<sup>5.</sup> Max. value is guaranteed by characterization and not tested in production.

# 2.2 Electrical characteristics

@ Vdd = 1.8 V, T = 25 °C unless otherwise noted<sup>(b)</sup>.

Table 4. Electrical characteristics (1)

| Symbol               | Parameter                                            | Test conditions                                                                                   | Min.      | Typ. <sup>(2)</sup> | Max.    | Unit              |

|----------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------|---------------------|---------|-------------------|

| Vdd                  | Supply voltage                                       |                                                                                                   | 1.71      | 1.8                 | 1.99    | V                 |

| IddT                 | Current consumption in triaxial mode <sup>(3)</sup>  |                                                                                                   |           | 2.58                | 3.3     | mA                |

| IddB                 | Current consumption in biaxial mode <sup>(3)</sup>   |                                                                                                   |           | 2.13                | 2.75    | mA                |

| lddM                 | Current consumption in monoaxial mode <sup>(3)</sup> |                                                                                                   |           | 1.68                | 2.2     | mA                |

| lddD0                | Current consumption in disabled mode                 | no external clock<br>switching <sup>(4)</sup>                                                     |           |                     | 10      | uA                |

| lddD1                | Current consumption in disabled mode                 | TDM standard clock<br>(MCLK = 12.288 MHz,<br>BCLK=3.072 MHz) <sup>(4)</sup>                       |           |                     | 205     | uA                |

|                      |                                                      | TDM @ 8 kHz                                                                                       |           | 8                   |         | kHz               |

| ODR                  | Output data rate                                     | TDM @ 16 kHz                                                                                      |           | 16                  |         | kHz               |

|                      |                                                      | TDM @ 24 kHz                                                                                      |           | 24                  |         | kHz               |

| Tstart               | Startup time                                         |                                                                                                   |           |                     | 10      | ms                |

| VIH                  | Digital high-level input voltage                     | all pins,<br>except pin 10 and 11                                                                 | 0.7*Vdd   |                     |         | V                 |

|                      | input voltage                                        | pin 10 and 11                                                                                     | 0.8*Vdd   |                     |         | V                 |

| VIL                  | Digital low-level input voltage                      |                                                                                                   |           |                     | 0.2*Vdd | V                 |

| VOH                  | High-level output voltage                            | IOH = 2 mA <sup>(5)</sup>                                                                         | Vdd - 0.2 |                     |         | V                 |

| VOL                  | Low-level output voltage                             | IOL = 2 mA <sup>(5)</sup>                                                                         |           |                     | 0.2     | V                 |

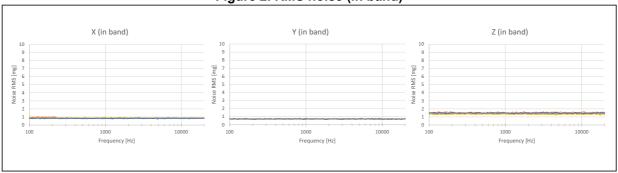

| PSR <sub>IBX/Y</sub> | PSR in band                                          | "Electrical noise" test mode.<br>Vdd = 1.8 V,<br>Vripple = 50 mVpp sin(2πωt)                      |           |                     | 3.16    | mg <sub>rms</sub> |

| PSR <sub>IBZ</sub>   |                                                      | Sweep $\omega$ from 20 Hz to 20 kHz<br>See <i>Figure 2</i>                                        |           |                     | 6.32    | mg <sub>rms</sub> |

| PSR <sub>OBX/Y</sub> | PSR out of band                                      | "Electrical noise" test mode.<br>Vdd = 1.8  V,<br>$Vripple = 50 \text{ mVpp } \sin(2\pi\omega t)$ |           |                     | 31.6    | mg <sub>rms</sub> |

| PSR <sub>OBZ</sub>   |                                                      | Sweep ω from 1 MHz to<br>10 MHz<br>See <i>Figure 3</i>                                            |           |                     | 63.2    | mg <sub>rms</sub> |

| Тор                  | Operating temperature range                          |                                                                                                   | -40       |                     | +85     | °C                |

b. The product is factory calibrated at 1.8 V. The operational power supply range is from 1.71 V to 1.99 V.

8/32 DocID031510 Rev 4

- 1. The product is factory calibrated at 1.8 V. The operational power supply range is from 1.71 V to 1.99 V.

- 2. Typical specifications are not guaranteed.

- Min. and max. values are guaranteed by characterization and not tested in production. Values are intended in the temperature and voltage operating range.

- 4. Min. and max. values are guaranteed by characterization and not tested in production.

- 5. 2 mA is the maximum driving capability, i.e. the maximum DC current that can be sourced/sunk by the digital pad in order to guarantee the correct digital output voltage levels VOH and VOL.

Figure 2. RMS noise (in band)

Figure 3. RMS noise (out of band)

#### 2.3 **Absolute maximum ratings**

Stresses above those listed as "Absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 5. Absolute maximum ratings

| Symbol           | Ratings                                                     | Maximum value | Unit |

|------------------|-------------------------------------------------------------|---------------|------|

| Vdd              | Supply voltage                                              | -0.3 to 4.8   | V    |

| STR              | Storage temperature range                                   | -40 to +125   | °C   |

|                  | MIL-STD-883H, Method 2002.5, Condition F                    | 20,000        |      |

| Sg               | MIL-STD-883H, Method 2002.5, Condition E                    | 10,000        | g    |

|                  | MIL-STD-883H, Method 2002.5, Condition D                    | 5,000         |      |

| EDP              | Electrostatic discharge protection (HBM)                    | 2             | kV   |

| V <sub>MAX</sub> | Maximum input voltage on all input pins                     | 4.8           | V    |

| V <sub>MIN</sub> | Minimum input voltage on all input pins                     | -0.3          | V    |

| I <sub>IN</sub>  | Input current on all I/O pins (does not cause SCR latch-up) | +/-10         | mA   |

Note: Supply voltage on any pin should never exceed 4.8 V

This device is sensitive to mechanical shock, improper handling can cause permanent damage to the part.

This device is sensitive to electrostatic discharge (ESD), improper handling can cause permanent damage to the part.

DocID031510 Rev 4

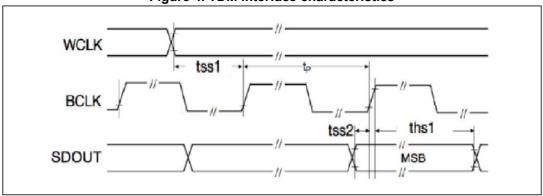

# 3 TDM interface characteristics

Please refer to Section 4: TDM interface specifications for additional details.

Table 6. TDM interface characteristics (1)

| Symbol             | Parameter                                                    | Test conditions  | Min. | Тур.   | Max. | Unit                 |

|--------------------|--------------------------------------------------------------|------------------|------|--------|------|----------------------|

| MCLK               | MCLK frequency nominal                                       |                  |      | 12.288 |      | MHz                  |

| MCLKA              | MCLK frequency accuracy                                      |                  | -0.1 |        | 0.1  | %                    |

| MCLKJ              | MCLK jitter                                                  |                  |      |        | 1    | ns (peak<br>to peak) |

|                    |                                                              | in disabled mode |      |        | MCLK | MHz                  |

| BCLK               | BCLK frequency (1/tp)                                        | WCLK = 8 kHz     |      | 1.024  |      | MHz                  |

| DCLK               | BOLK frequency (1/tp)                                        | WCLK = 16 kHz    |      | 2.048  |      | MHz                  |

|                    |                                                              | WCLK = 24 kHz    |      | 3.072  |      | MHz                  |

| WCLK8              | 8 kHz WCLK mode                                              |                  |      | 8      |      |                      |

| WCLK16             | 16 kHz WCLK mode                                             |                  |      | 16     |      | kHz                  |

| WCLK24             | 24 kHz WCLK mode                                             |                  |      | 24     |      |                      |

| PDC                | All clock pin duty cycle (except WCLK)                       |                  | 45   |        | 55   | %                    |

| WT                 | WCLK setup time before BCLK rising/falling edge (tss1)       |                  | 20   |        |      | ns                   |

| SDOST              | SDOUT setup time before BCLK rising/falling edge (tss2)      |                  | 15   |        |      | ns                   |

| SDOHTR             | SDOUT hold time after BCLK rising/falling edge (ths1)        |                  | 15   |        |      | ns                   |

| SDOHTZ             | SDOUT hold time of LSB after BCLK rising/falling edge (ths2) |                  | 15   |        | 50   | ns                   |

| C <sub>MCLK</sub>  | MCLK pin capacitance                                         |                  |      |        | 10   |                      |

| C <sub>BCLK</sub>  | BCLK pin capacitance                                         |                  |      |        | 10   | ]<br>                |

| C <sub>WCLK</sub>  | VCLK pin capacitance                                         |                  |      |        | 10   | pF                   |

| C <sub>SDOUT</sub> | SDOUT load capacitance                                       |                  |      |        | 60   |                      |

| FR <sub>REL</sub>  | Relative frequency response <sup>(2)</sup>                   | (3)              | -0.5 |        | 0.4  | dB                   |

All setup times and hold times in Table 6 and in Figure 4 are valid for BCLK polarity set to "clock on rising". If BCLK polarity is set to "clock on falling", then all setup and hold times will refer to the falling edge of BCLK instead. Please refer to Section 4: TDM interface specifications for additional details.

<sup>2.</sup> Data by simulation

<sup>3.</sup> All the DUT measurement points are normalized to the 294 Hz measurement. The deviation between each point and 294 Hz is calculated. The maximum deviation for points measured at frequencies below 2.0 kHz is given as FR<sub>REL</sub>.

Figure 4. TDM interface characteristics

# 3.1 I<sup>2</sup>C interface characteristics

Please refer to Section 5: I<sup>2</sup>C- inter-IC control interface for additional details.

Table 7. Digital input/output voltage for I<sup>2</sup>C pins<sup>(1)</sup>

| Symbol | Parameter                        | Test conditions           | Min.    | Typ. <sup>(2)</sup> | Max.    | Unit |

|--------|----------------------------------|---------------------------|---------|---------------------|---------|------|

| VIH    | Digital high-level input voltage |                           | 0.7*Vdd |                     |         | ٧    |

| VIL    | Digital low-level input voltage  |                           |         |                     | 0.2*Vdd | V    |

| VOL    | Low-level output voltage         | IOL = 4 mA <sup>(3)</sup> | 0.2     |                     |         | V    |

Data based on standard I<sup>2</sup>C protocol requirement, intended only for test and trim. Values are not guaranteed.

4

<sup>2.</sup> Typical specifications are not guaranteed.

<sup>3. 4</sup> mA is the maximum driving capability, i.e. the maximum DC current that can be sourced/sunk by the digital pad in order to guarantee the correct digital output voltage levels VOH and VOL.

| Table 6. I-C Interis | lace characteristics |  |  |  |  |

|----------------------|----------------------|--|--|--|--|

| neter                | Test conditions      |  |  |  |  |

| Symbol                | Parameter                                      | Test conditions             | Min. | Typ. <sup>(1)</sup> | Max. | Unit |

|-----------------------|------------------------------------------------|-----------------------------|------|---------------------|------|------|

| f <sub>(SCL)</sub>    | SCL                                            |                             | 96   |                     | 400  | kHz  |

| C <sub>SDA-N</sub>    | SDA/SCL bus capacitance normal mode            | R <sub>SDA</sub> = 2.5 kOhm |      |                     | 150  | pF   |

| C <sub>SDA-HS</sub>   | SDA/SCL bus capacitance high speed mode        | R <sub>SDA</sub> = 2.5 kOhm |      |                     | 50   | pF   |

| R <sub>SDA</sub>      | SDA/SCL pull-up resistance                     |                             | 2500 |                     |      | Ohm  |

| t <sub>w(SCLL)</sub>  | SCL clock low time                             |                             | 1.3  |                     |      |      |

| t <sub>w(SCLH)</sub>  | SCL clock high time                            |                             | 0.6  |                     |      | μs   |

| t <sub>su(SDA)</sub>  | SDA setup time                                 |                             | 100  |                     |      | ns   |

| t <sub>h(SDA)</sub>   | SDA data hold time                             |                             | 0    |                     | 0.9  | μs   |

| t <sub>h(ST)</sub>    | START condition hold time                      |                             | 0.6  |                     |      |      |

| t <sub>su(SR)</sub>   | Repeated START condition setup time            |                             | 0.6  |                     |      | ]    |

| t <sub>su(SP)</sub>   | STOP condition setup time                      |                             | 0.6  |                     |      | μs   |

| t <sub>w(SP:SR)</sub> | Bus free time between STOP and START condition |                             | 1.3  |                     |      |      |

| I2C_HYST              | SDA/SCL minimum pulse width hysteresis         |                             |      |                     | 50   | ns   |

<sup>1.</sup> Typical specifications are not guaranteed.

Figure 5. I<sup>2</sup>C slave timing diagram REPEATED START START START SDA  $t_{\text{su}(\text{SDA})}$ t<sub>h(SDA)</sub>  $t_{su(SP)}$ STOP SCL

Measurement points are done at 0.2·Vdd and 0.8·Vdd, for both ports. Note:

Table 9. I<sup>2</sup>C high-speed mode specifications at 1 MHz

|                     | Symbol              | Parameter                                                         | Min        | Max | Unit  |

|---------------------|---------------------|-------------------------------------------------------------------|------------|-----|-------|

|                     | f <sub>SCL</sub>    | SCL clock frequency                                               | 0          | 1   | MHz   |

|                     | t <sub>HD;STA</sub> | Hold time (repeated) START condition                              | 260        | -   |       |

|                     | t <sub>LOW</sub>    | Low period of the SCL clock                                       | 500        | -   |       |

|                     | t <sub>HIGH</sub>   | High period of the SCL clock                                      | 260        | -   |       |

|                     | t <sub>SU;STA</sub> | Setup time for a repeated START condition                         | 260        | -   |       |

|                     | t <sub>HD;DAT</sub> | Data hold time                                                    | 0          | -   |       |

|                     | t <sub>SU;DAT</sub> | Data setup time                                                   | 50         | -   | ns    |

|                     | t <sub>rDA</sub>    | Rise time of SDA signal                                           | -          | 120 |       |

| Fast mode           | t <sub>fDA</sub>    | Fall time of SDA signal                                           | -          | 120 |       |

| plus <sup>(1)</sup> | t <sub>rCL</sub>    | Rise time of SCL signal                                           | 20*Vdd/5.5 | 120 |       |

|                     | t <sub>fCL</sub>    | Fall time of SCL signal                                           | 20*Vdd/5.5 | 120 |       |

|                     | t <sub>SU;STO</sub> | Setup time for STOP condition                                     | 260        | -   |       |

|                     | C <sub>b</sub>      | Capacitive load for each bus line                                 | -          | 550 | pF    |

|                     | t <sub>VD;DAT</sub> | Data valid time                                                   | -          | 450 | ns    |

|                     | t <sub>VD;ACK</sub> | Data valid acknowledge time                                       | -          | 450 | 7 115 |

|                     | V <sub>nL</sub>     | Noise margin at low level                                         | 0.1Vdd     | -   | _ v   |

|                     | $V_{nH}$            | Noise margin at high level                                        | 0.2Vdd     | -   | │     |

|                     | t <sub>SP</sub>     | Pulse width of spikes that must be suppressed by the input filter | 0          | 50  | ns    |

<sup>1.</sup> Data based on characterization, not tested in production

# 4 TDM interface specifications

Time-division multiplexing (TDM) is a method of putting multiple data streams in one data signal by separating the signal into many frames. There are many ways to accomplish this.

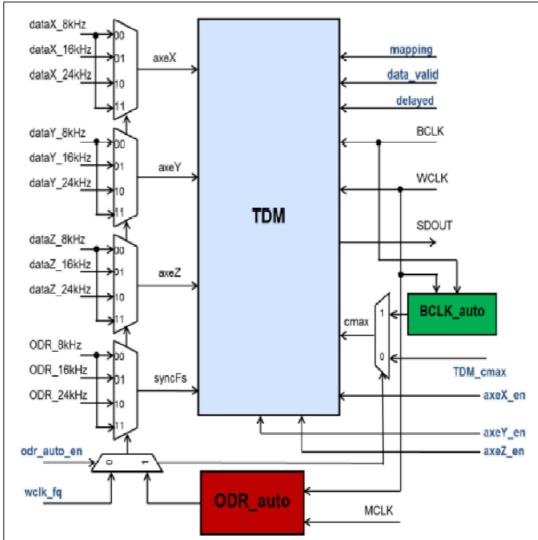

#### 4.1 TDM interface overview

The block diagram of the TDM interface implemented in the LIS25BA device is given in *Figure 6*.

Figure 6. TDM block diagram

As depicted in the figure above, the TDM interface is comprised of two control clocks, a frame synchronization (WCLK) a serial clock (BCLK), and the serial data out (SDOUT).

# 4.2 Frame synchronization (WCLK)

The function of the WCLK is simply to identify the beginning of a frame. In particular the frame start at the rising edge of WCLK, and the WCLK widths supported are:

- 50% duty cycle

- One slot width (16 BCLK)

- One BCLK width

In TDM mode, LIS25BA shall output accelerometer data on the SDOUT pin at the following sampling rates:

- WCLK = 8 kHz

- WCLK = 16 kHz

- WCLK = 24 kHz

As depicted in *Figure 6*, the TDM input sampling rate (ODR\_8kHz, ODR\_16kHz and ODR\_24kHz), and the associated data inputs (dataX\_8kHz, dataX\_16kHz, dataX\_24kHz, dataY\_8kHz, dataY\_16kHz, dataY\_24kHz, dataZ\_8kHz, dataZ\_16kHz and dataZ\_24kHz) can be selected in two different ways:

- 1. Using the I<sup>2</sup>C register wclk\_fq (TDM\_CTRL\_REG (2Eh), bits 2 and 1). In this case the I<sup>2</sup>C register ODR\_AUTO\_EN (AXES\_CTRL\_REG (2Fh), bit 0) is equal to zero, that means that the ODR\_auto functionality is disabled.

- Using the output of the ODR\_auto block (ODR\_AUTO\_EN (AXES\_CTRL\_REG (2Fh), bit 0) equal to one). This latter simply receives as inputs both the MCLK and the WCLK and it computes the current sampling frequency as a ratio between the MCLK and WCLK.

The possible outputs of the ODR auto block are:

- a) 00: sampling rate equal to 8 kHz (MCLK/WCLK = 1536)

- b) 01: sampling rate equal to 16 kHz (MCLK/WCLK = 768)

- c) 10: sampling rate equal to 24 kHz (MCLK/WCLK = 512)

Observing *Figure 6*, it is possible to see, that if a ratio between MCLK and WCLK differ from 1536, 768 and 512, the sampling rate equal to 8 kHz is selected.

# 4.3 Serial clock (BCLK)

The sole purpose of the serial clock BCLK is to shift the data out of the serial SDOUT port. To this purpose, the TDM interface uses an internal counter that is set to one when the rising edge of the WCLK is detected, and it is reset to zero when the maximum number of BCLK in a WCLK period is reached.

The maximum number of BCLK contained in a WCLK period (cmax input of the TDM in *Figure 6*) can be expressed as a function of both the BCLK and WCLK frequencies, and can be computed using the following equation:

#### **Equation 1**

$$cmax = \frac{BCLK}{WCLK} - 1$$

In order to support a serial clock BCLK variable in the range [1024 MHz, 12.288 MHz], and consequently to compute the correct maximum value of the internal TDM counter, two possible solutions can be selected:

- The cmax value at the input of the TDM interface can be computed on the fly employing the BCLK\_AUTO block (see Figure 6), which is able to compute the cmax value using Equation 1. This functionality by default is enabled, and can be disabled employing the I<sup>2</sup>C register ODR AUTO EN (AXES CTRL REG (2Fh) bit 0).

- The TDM cmax can be programmed through the I<sup>2</sup>C registers *TDM cmax (24h-25h)*.

# 4.4 TDM axes mapping

Within one frame, the data signal (DOUT) is divided into multiple segments. We call each segment a slot thereafter in this document.

The data slot width is fixed and equal to 16 bits.

In each slot, data should be left-justified (MSB first).

The number of slots in a WCLK frame can be variable, and it depends on the ratio between BCLK and WCLK. However, as depicted in *Figure 7* and *Figure 8*, only the slots 0,1,2 and 4,5,6 can be used to send accelerometer data, all the others slots are always set in high-impedance.

The mapping between the input data and the TDM output slots is flexible and can be configured through the I<sup>2</sup>C register mapping (TDM\_CTRL\_REG (2Eh) bit 4) in Figure 6.

In particular two possible configurations can be selected:

- Axes data (X,Y,Z) mapped on TDM slots (0,1,2) (mapping = 0)

- Axes data (X,Y,Z) mapped on TDM slots (4,5,6) (mapping = 1)

Figure 7. Axes X, Y, Z mapped to SLOT0, SLOT1, SLOT2

| SLOT0  | SLOT1  | SLOT2  | SLOT3 | SLOT4 | SLOT5 | SLOT6 | SLOT7 | <br>SLOTN |

|--------|--------|--------|-------|-------|-------|-------|-------|-----------|

| X-axis | Y-axis | Z-axis | HiZ   | HiZ   | HiZ   | HiZ   | HiZ   | HiZ       |

Figure 8. Axes X, Y, Z mapped to SLOT4, SLOT5, SLOT6

| SLOT0 | SLOT1 | SLOT2 | SLOT3 | SLOT4  | SLOT5  | SLOT6  | SLOT7 | SLOTN   |  |

|-------|-------|-------|-------|--------|--------|--------|-------|---------|--|

| HiZ   | HiZ   | HiZ   | HiZ   | X-axis | Y-axis | Z-axis | HiZ   | <br>HiZ |  |

### 4.5 TDM configurations

In the following subsections all the LIS25BA TDM configurations programmable through the I<sup>2</sup>C interface will be detailed.

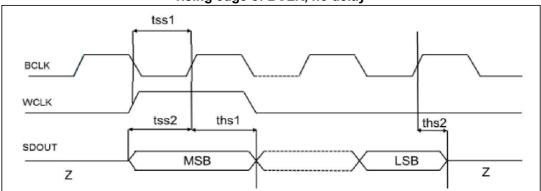

#### 4.5.1 Configuration 1

- No delay: SLOT0 data MSB is sampled on the first rising edge of BCLK after rising edge of WCLK (delayed I<sup>2</sup>C register TDM\_CTRL\_REG (2Eh) bit 6 equal to zero)

- Data valid: data valid on the rising edge of BCLK (data\_valid I²C register TDM\_CTRL\_REG (2Eh) bit 5 equal to zero)

Figure 9. WCLK, SDOUT change on the falling edge of BCLK and are valid on the rising edge of BCLK, no delay

Note: Setup and hold times are defined in Table 6: TDM interface characteristics.

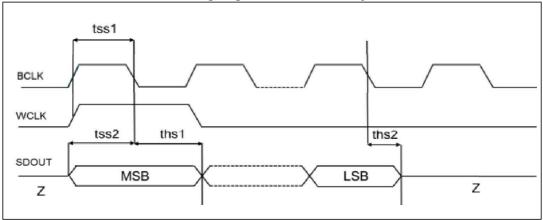

#### 4.5.2 Configuration 2

- No delay: SLOT0 data MSB is sampled on the first falling edge of BCLK after rising edge of WCLK (delayed I<sup>2</sup>C register TDM\_CTRL\_REG (2Eh) bit 6 equal to zero)

- Data valid: data valid on the falling edge of BCLK (data\_valid I<sup>2</sup>C register TDM CTRL REG (2Eh) bit 5 equal to one)

Figure 10. WCLK, SDOUT change on the rising edge of BCLK and are valid on the falling edge of BCLK, no delay

Note: Setup and hold times are defined in Table 6: TDM interface characteristics.

18/32 DocID031510 Rev 4

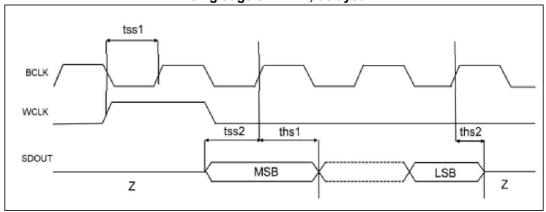

#### 4.5.3 Configuration 3

- Delayed: SLOT0 data MSB is sampled on the second rising edge of BCLK after rising edge of WCLK (delayed I<sup>2</sup>C register TDM\_CTRL\_REG (2Eh) bit 6 equal to one)

- Data valid: data valid on the rising edge of BCLK (data\_valid I<sup>2</sup>C register *TDM\_CTRL\_REG (2Eh)* bit 5 equal to zero)

Figure 11. WCLK, SDOUT change on the falling edge of BCLK and are valid on the rising edge of BCLK, delayed

Note: Setup and hold times are defined in Table 6: TDM interface characteristics.

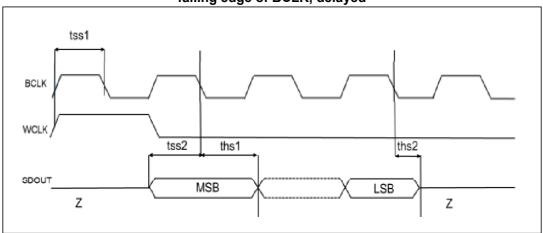

#### 4.5.4 Configuration 4

- Delayed: SLOT0 data MSB is sampled on the second falling edge of BCLK after rising edge of WCLK (delayed I<sup>2</sup>C register TDM\_CTRL\_REG (2Eh) bit 6 equal to one)

- Data valid: data valid on the falling edge of BCLK (data\_valid I<sup>2</sup>C register TDM\_CTRL\_REG (2Eh) bit 5 equal to one)

Figure 12. WCLK, SDOUT change on the rising edge of BCLK and are valid on the falling edge of BCLK, delayed

Note: Setup and hold times are defined in Table 6: TDM interface characteristics.

# 4.6 TDM clocks and MCLK requirements

The relationship between TDM clocks and MCLK should be:

- Both BCLK and WCLK must be obtained from MCLK by integer division. This requirement is mandatory since ADC is clocked by MCLK, so the TDM data rate must be perfectly synchronous in frequency and phase with the decimated ADC data rate.

- The BCLK/WCLK ratio must be an integer value.

#### 4.7 I<sup>2</sup>C axis disable

In TDM mode, a host processor can power down each axis of the LIS25BA accelerometer independently, overriding the I<sup>2</sup>C registers (AXISX\_EN, AXISY\_EN, AXISZ\_EN in *AXES\_CTRL\_REG (2Fh)*) interface to reduce power consumption during operation. When an axis is powered down, the corresponding TDM slot will be put in HiZ.

### 5 I<sup>2</sup>C- inter-IC control interface

#### 5.1 I<sup>2</sup>C interface

The registers embedded inside the LIS25BA may be accessed also through the I<sup>2</sup>C serial interfaces.

Table 10. I<sup>2</sup>C serial interface pin description

| Pin name | Pin description                     |

|----------|-------------------------------------|

| I2C_SCL  | I <sup>2</sup> C serial clock (SCL) |

| I2C_SDA  | I²C serial data (SDA)               |

The LIS25BA I<sup>2</sup>C is a bus slave. The I<sup>2</sup>C is employed to write data into registers whose content can also be read back.

The relevant I<sup>2</sup>C terminology is given in the table below.

Table 11. I<sup>2</sup>C terminology

| Term        | Description                                                                              |

|-------------|------------------------------------------------------------------------------------------|

| Transmitter | The device which sends data to the bus                                                   |

| Receiver    | The device which receives data from the bus                                              |

| Master      | The device which initiates a transfer, generates clock signals and terminates a transfer |

| Slave       | The device addressed by the master                                                       |

There are two signals associated with the I<sup>2</sup>C bus: the serial clock line (SCL) and the serial data line (SDA). The latter is a bidirectional line used for sending and receiving the data to/from the interface. Both lines must be connected to Vdd through an external pull-up resistor. When the bus is free, both lines are high.

The I<sup>2</sup>C interface is compliant with fast mode (400 kHz) I<sup>2</sup>C standards as well as with the normal mode.

#### 5.2 I<sup>2</sup>C interface details

The transaction on the bus is started through a START signal. A START condition is defined as a HIGH to LOW transition on the data line while the SCL line is held HIGH (refer to ST condition in the following paragraph). After this signal has been transmitted by the master, the bus is considered busy. The next byte of data transmitted after the start condition contains the address of the slave in the first 7 bits and the eighth bit tells whether the master is receiving data from the slave or transmitting data to the slave (SAD subsequences). When an address is sent, each device in the system compares the first seven bits after a start condition with its address. If they match, the device considers itself addressed by the master. The address can be made up of a programmable part and a fixed part, thus allowing more than one device of the same type to be connected to the I²C bus.

Data transfer with acknowledge is mandatory. The transmitter must release the SDA line during the acknowledge pulse. The receiver must then pull the data line LOW so that it remains stable low during the HIGH period of the acknowledge clock pulse (SAK subsequence). A receiver which has been addressed is obliged to generate an

acknowledge after each byte of data has been received. The I²C embedded inside the LIS25BA behaves like a slave device and the following protocol must be adhered to. After the start condition (ST) a slave address is sent, once a slave acknowledge has been returned (SAK), an 8-bit sub-address will be transmitted (SUB): the 7 LSB represent the actual register address while the MSB enables address auto-increment. If the MSB of the SUB field is '1', the SUB (register address) will be automatically incremented to allow multiple data read/write at increasing addresses. Otherwise if the MSB of the SUB field is '0', the SUB will remain unchanged and multiple read/write on the same address can be performed. If the LSB of the slave address is '1' (read), a repeated START (SR) condition will have to be issued after the sub-address byte; if the LSB is '0' (write) the master will transmit to the slave with direction unchanged.

#### 5.3 I<sup>2</sup>C slave address

The slave address is equal to 001100yx (TDM mode, where  $y = not(I2C\_A0 pin)$ ) or in case of writing or reading respectively.

### 5.4 I<sup>2</sup>C read and write sequences

Previous subsequences are used for the actual write and read sequences described in the tables below.

Table 12. Transfer when master is writing one byte to slave

| Master | ST | SAD + W |     | SUB |     | DATA |     | SP |

|--------|----|---------|-----|-----|-----|------|-----|----|

| Slave  |    |         | SAK |     | SAK |      | SAK |    |

Table 13. Transfer when master is writing multiple bytes to slave

| Master | ST | SAD + W |     | SUB |     | DATA |     | DATA |     | SP |

|--------|----|---------|-----|-----|-----|------|-----|------|-----|----|

| Slave  |    |         | SAK |     | SAK |      | SAK |      | SAK |    |

Table 14. Transfer when master is receiving (reading) one byte of data from slave

| Master | ST | SAD + W |     | SUB |     | SR | SAD + R |     |      | NMAK | SP |

|--------|----|---------|-----|-----|-----|----|---------|-----|------|------|----|

| Slave  |    |         | SAK |     | SAK |    |         | SAK | DATA |      |    |

Table 15. Transfer when master is receiving (reading) multiple bytes of data from slave

|   | Master | ST | SAD+W |     | SUB |     | SR | SAD+R |     |      | MAK |      | MAK |      | NMAK | SP |

|---|--------|----|-------|-----|-----|-----|----|-------|-----|------|-----|------|-----|------|------|----|

| ſ | Slave  |    |       | SAK |     | SAK |    |       | SAK | DATA |     | DATA |     | DATA |      |    |

Data are transmitted in byte format (DATA). Each data transfer contains 8 bits. The number of bytes transferred per transfer is unlimited. Data is transferred with the Most Significant Bit (MSB) first. If a receiver can't receive another complete byte of data until it has performed some other function, it can hold the clock line, SCL LOW to force the transmitter into a wait state. Data transfer only continues when the receiver is ready for another byte and releases the data line. If a slave receiver doesn't acknowledge the slave address (i.e. it is not able to receive because it is performing some real time function) the data line must be left HIGH by the slave. The master can then abort the transfer. A LOW to HIGH transition on the SDA line while the SCL line is HIGH is defined as a STOP condition (SP). Each data transfer must be terminated by the generation of a STOP condition.

LIS25BA Features

#### 6 Features

#### 6.1 Self-test mode

In self-test mode the mechanical element is stimulated by electrostatic force to obtain an equivalent input force applied to the sensor. This equivalent input force applied has to be comparable with the full-scale range in order to have an effective self-test mode.

The self-test mode can be enabled using the I<sup>2</sup>C interface, setting the ST bit in register *TEST\_REG (0Bh)* to '1'.

For the self-test values of each axis please refer to Table 3: Mechanical characteristics.

# 6.2 Power cycle/reset information

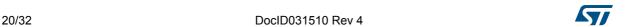

### 6.2.1 TDM interface power-on sequence

In TDM, the LIS25BA starts in disabled mode with the following sequence.

Figure 13. Power-on sequence (TDM interface)

In *Figure 13* T<sub>0</sub> represents the time when Vdd reaches 90% of the final value.

After  $T_{DIS}$  = 5.5 ms the LIS25BA reaches the disabled mode condition.

The TDM interface must be activated explicitly with I<sup>2</sup>C configuration. The first 3 samples after the enabling of the TDM may be invalid samples due to the fact that the interface should sync on the external WCLK. The samples will be invalid also after any subsequent Disable-Enable transition that may happen. TDM protocol can be changed on the fly, but also in this case the first 3 samples after the TDM configuration change will be invalid.

Features LIS25BA

### 6.2.2 Disabled mode

The LIS25BA can be put in disabled mode using the I<sup>2</sup>C interface. The power-down command will be executed immediately (no wait state).

The LIS25BA can be resumed from disabled mode using the I<sup>2</sup>C as well. In this case the MCLK/BCLK/WCLK clocks must be set to the correct values before writing to the I<sup>2</sup>C.

Please refer to Figure 14 for the disabled mode sequence.

$T_0$

DISABLE NODE 12C writing Power on Power

Figure 14. Disabled mode sequence

t

T = 4.5 ms

LIS25BA Register mapping

# 7 Register mapping

The table given below provides a list of the 8-bit registers embedded in the device and their respective addresses.

Table 16. Register address map

| Name           | Type <sup>(1)</sup> | Register | address  | Default   |

|----------------|---------------------|----------|----------|-----------|

| Name           | Type                | Hex      | Binary   | Delauit   |

| TEST_REG       | rw                  | 0B       | 000 1100 | 0000 0000 |

| WHO_AM_I       | r                   | 0F       | 000 1111 | 0010 0000 |

| TDM_cmax[11:8] | rw                  | 24       | 010 0100 | 0000 0000 |

| TDM_cmax[7:0]  | rw                  | 25       | 010 0101 | 0111 1111 |

| CTRL_REG       | rw                  | 26       | 0100110  | 0010 0000 |

| TDM_CTRL_REG   | rw                  | 2E       | 010 1110 | 1111 0000 |

| AXES_CTRL_REG  | rw                  | 2F       | 010 1111 | 1110 0001 |

<sup>1.</sup> Read only (r) - read/write (rw)

Register description LIS25BA

# 8 Register description

# 8.1 TEST\_REG (0Bh)

Self-test register (r/w).

Table 17. TEST\_REG register

|                  |                  | iab              | 10 17. 1 <b>L</b> O 1 | _iveo iegi | 3101             |                  |                  |

|------------------|------------------|------------------|-----------------------|------------|------------------|------------------|------------------|

| 0 <sup>(1)</sup> | 0 <sup>(1)</sup> | 0 <sup>(1)</sup> | 0 <sup>(1)</sup>      | ST         | 0 <sup>(1)</sup> | 0 <sup>(1)</sup> | 0 <sup>(1)</sup> |

<sup>1.</sup> For proper operation of the device, this bit must be set to '0'.

#### Table 18. TEST\_REG register description

| ST | Enables self-test mode. Default value: 0 |

|----|------------------------------------------|

|    | (0: disabled; 1: enabled)                |

# 8.2 WHO\_AM\_I (0Fh)

Table 19. WHO\_AM\_I register

|--|

Device identification register.

# 8.3 TDM\_cmax (24h-25h)

TDM counter max value when the BCLK autoconfiguration feature is disabled.

Table 20. TDM\_cmax register

| - | - | - | - | TDM_cmax[11:8] MSB |

|---|---|---|---|--------------------|

|---|---|---|---|--------------------|

TDM\_cmax[7:0] LSB

# 8.4 CTRL\_REG (26h)

Control register (r/w)

Table 21. CTRL\_REG register

| $0^{(1)}$ $0^{(1)}$ PD $0^{(1)}$ $0^{(1)}$ $0^{(1)}$ |

|------------------------------------------------------|

|------------------------------------------------------|

<sup>1.</sup> For proper operation of the device, this bit must be set to '0'.

#### Table 22. CTRL\_REG register description

| PD | Device in disabled mode. Default value: 1                                                    |

|----|----------------------------------------------------------------------------------------------|

|    | (0: Normal mode; 1: Disabled mode: minimum power consumption, I <sup>2</sup> C still active) |

# 8.5 TDM\_CTRL\_REG (2Eh)

#### Table 23. TDM\_CTRL\_REG register

| TDM_pd | Delayed | data_valid | mapping | 0 <sup>(1)</sup> | WCLK_fq1 | WCLK_fq0 | 0 <sup>(1)</sup> |

|--------|---------|------------|---------|------------------|----------|----------|------------------|

<sup>1.</sup> For proper operation of the device, this bit must be set to '0'.

#### Table 24. TDM\_CTRL\_REG register description

| TDM_pd        | TDM enable. Default value: 1 (0: TDM on; 1: TDM off)                                                                 |

|---------------|----------------------------------------------------------------------------------------------------------------------|

| Delayed       | TDM delayed configuration. Default value: 1 (0: TDM no delayed configuration; 1: TDM delayed configuration)          |

| data_valid    | TDM data valid. Default value: 1 (0: data valid on the rise edge of BCLK; 1: data valid on the falling edge of BCLK) |

| mapping       | TDM mapping. Default value: 1 (0: AXEX> SLOT0; AXEY> SLOT1; AXEZ> SLOT2; 1: AXEX> SLOT4; AXEY> SLOT5; AXEZ> SLOT6)   |

| WCLK_fq [1:0] | TDM clock frequencies. Default value: 00 (00: WCLK = 8 kHz; 01: WCLK = 16 kHz; 10: WCLK = 24 kHz)                    |

# 8.6 AXES\_CTRL\_REG (2Fh)

#### Table 25. AXES CTRL REG register

|          |          |          | _                | _                | _                |                  |             |

|----------|----------|----------|------------------|------------------|------------------|------------------|-------------|

| AXISZ_EN | AXISY_EN | AXISX_EN | 0 <sup>(1)</sup> | 0 <sup>(1)</sup> | 0 <sup>(1)</sup> | 0 <sup>(1)</sup> | ODR_AUTO_EN |

<sup>1.</sup> For proper operation of the device, this bit must be set to '0'.

#### Table 26. AXES\_CTRL\_REG register description

| AXISZ_EN    | Z-axis enable. Default value: 1 (0: disabled; 1: enabled)                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| AXISY_EN    | Y-axis enable. Default value: 1 (0: disabled; 1: enabled)                                                                       |

| AXISX_EN    | X-axis enable. Default value: 1 (0: disabled; 1: enabled)                                                                       |

| ODR_AUTO_EN | ODR AUTO enable. Default value: 1 (0: ODR and BCLK auto disabled <sup>(1)</sup> ; 1: ODR and BCLK auto enabled <sup>(2)</sup> ) |

<sup>1.</sup> In this case it is mandatory to set TDM\_CTRL\_REG (2Eh) bits 2 and 1 to match the WCLK sampling rate and TDM\_cmax (24h-25h) to match the BCLK/WCLK ratio

<sup>2.</sup> LIS25BA automatically measures the ratio r = MCLK/WCLK. The WCLK frequency is internally determined as FW=12.288 MHz/r. FW will be used to configure automatically the decimation ratio between the ADC and TDM input data rate (same as TDM output data rate) bypassing TDM\_CTRL\_REG (2Eh) bits 2 and 1 configuration. When ODR\_AUTO is '1' also the BCLK/WCLK ratio is automatically computed for proper TDM configuration as described in TDM\_cmax (24h-25h).

Package information LIS25BA

# 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

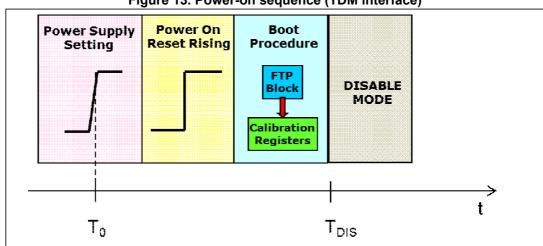

# 9.1 LGA-14 package information

The LGA-14 package is classified MSL 3.

Figure 15. LGA-14 2.5x2.5x0.86 mm package outline and mechanical data

LIS25BA Package information

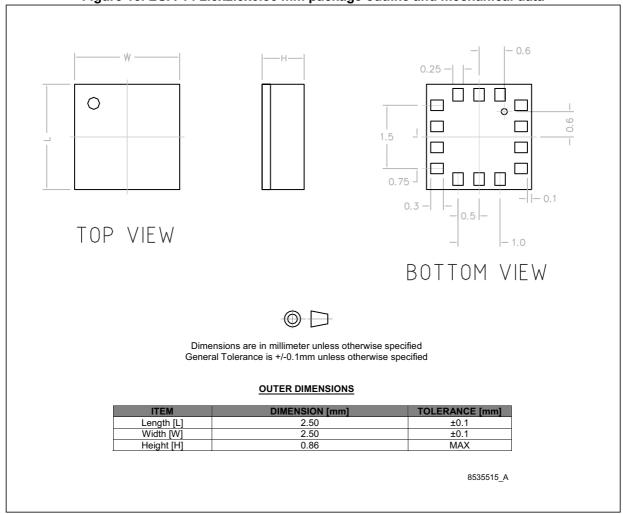

# 9.2 LGA-14 packing information

Figure 16. Carrier tape information for LGA-14 package

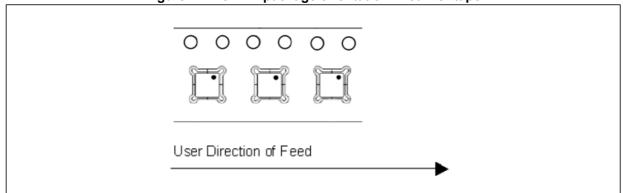

Figure 17. LGA-14 package orientation in carrier tape

Package information LIS25BA

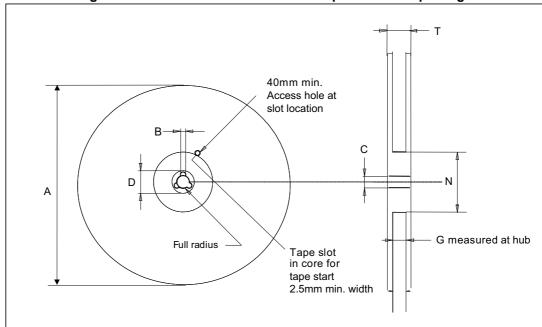

Figure 18. Reel information for carrier tape of LGA-14 package

Table 27. Reel dimensions for carrier tape of LGA-14 package

| Reel dimensions (mm) |            |  |  |  |

|----------------------|------------|--|--|--|

| A (max)              | 330        |  |  |  |

| B (min)              | 1.5        |  |  |  |

| С                    | 13 ±0.25   |  |  |  |

| D (min)              | 20.2       |  |  |  |

| N (min)              | 60         |  |  |  |

| G                    | 12.4 +2/-0 |  |  |  |

| T (max)              | 18.4       |  |  |  |

30/32

LIS25BA Revision history

# 10 Revision history

Table 28. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                            |  |  |  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 05-Feb-2018 | 1        | Initial release                                                                                                                                                                                                                                                                                                    |  |  |  |

| 07-May-2018 | 2        | Document status promoted to production data Updated pin 11 in Table 2: Pin description Added footnote 5 to Table 3: Mechanical characteristics Updated footnote 3 and 4 of Table 4: Electrical characteristics Updated Section 6.1: Self-test mode Updated TEST_REG (0Bh), CTRL_REG (26h), and AXES_CTRL_REG (2Fh) |  |  |  |

| 24-May-2018 | 3        | Updated bandwidth in Features and in Table 3: Mechanical characteristics Updated test conditions of IddD1 in Table 4: Electrical characteristics Updated Table 16: Register address map Updates throughout Section 8: Register description                                                                         |  |  |  |

| 03-May-2019 | 4        | Added Section 9.2: LGA-14 packing information                                                                                                                                                                                                                                                                      |  |  |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2019 STMicroelectronics - All rights reserved