*Product Preview*

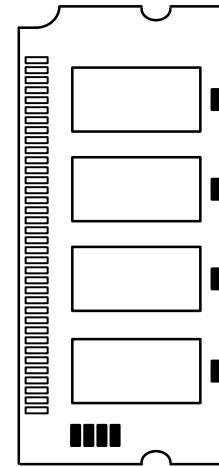

## 1M x 32 Bit DRAM Small Outline Memory Module

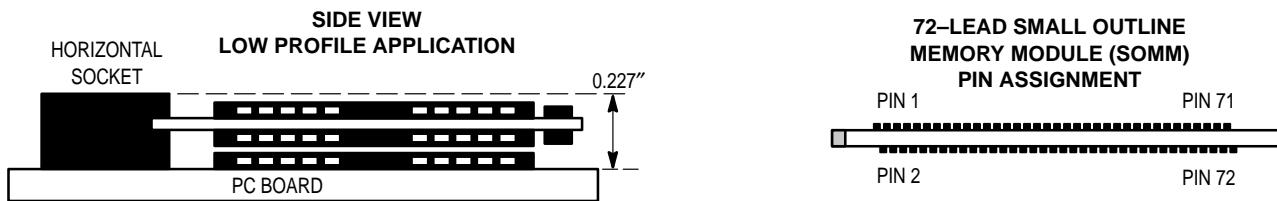

The MCM32100D is a dynamic random access memory (DRAM) module organized as 1,048,576 x 32 bits. The module is a JEDEC-standard 72-lead member of the small outline dual-in-line memory module (SO-DIMM) class of products with 36 separate contacts per side, consisting of eight MCM54400A DRAMs housed in 300 mil thin small outline packages (TSOP), mounted on a substrate along with a 0.22  $\mu$ F (min) decoupling capacitor mounted adjacent to each DRAM. The MCM54400A is a 0.7 $\mu$  CMOS high-speed, DRAM organized as 1,048,576 four-bit words and fabricated with CMOS silicon-gate process technology.

- Ideal for Portable System Applications

- MCM32100 Designed for Industry Standard 5 V Operation

- MCM32103 and MCM32L103 Designed for Low Voltage 3.3 V Operation

- Reduced Size (2.35" Length) Achieved by Using Separate Front/Back Contacts

- Allows 0.227" Three-Tiered Memory Solution When Using Horizontal Sockets

- Three-State Data Output

- Early-Write Common I/O Capability

- Fast Page Mode Capability

- TTL-Compatible Inputs and Outputs

- RAS-Only Refresh

- CAS Before RAS Refresh

- Hidden Refresh

- 1024 Cycle Refresh: 16 ms for MCM32100D and MCM32103D, 128 ms for MCM32L103D

- Consists of Eight 1M x 4 DRAMs and Eight 0.22  $\mu$ F (Min) Decoupling Capacitors

- Fast Access Time (tRAC): MCM32100D-60 = 60 ns (Max)

MCM32100D-70 = 70 ns (Max)

MCM32(L)103D-80 = 80 ns (Max)

- Low Active Power Dissipation: MCM32100D-60 = 5.28 W (Max)

MCM32100D-70 = 4.40 W (Max)

MCM32(L)103D-80 = 1.73 W (Max)

- Low Standby Power Dissipation:

MCM32100D TTL Levels = 88 mW (Max)

CMOS Levels = 44 mW (Max)

MCM32(L)103D TTL Levels = 26.4 mW (Max)

MCM32103D CMOS Levels = 13.2 mW (Max)

MCM32L103D CMOS Levels = 6.6 mW (Max)

## MCM32100D MCM32103D MCM32L103D

### D PACKAGE SMALL OUTLINE DIMM MODULE MCM32100D, CASE 992-01

### MCM32103D, MCM32L103D CASE 992A-01

### PIN ASSIGNMENTS

| Front Side |                 |     |                 | Back Side |                 |     |                 |

|------------|-----------------|-----|-----------------|-----------|-----------------|-----|-----------------|

| Pin        | Name            | Pin | Name            | Pin       | Name            | Pin | Name            |

| 1          | V <sub>SS</sub> | 37  | DQ16            | 2         | DQ0             | 38  | DQ17            |

| 3          | DQ1             | 39  | V <sub>SS</sub> | 4         | DQ2             | 40  | CAS0            |

| 5          | DQ3             | 41  | CAS2            | 6         | DQ4             | 42  | CAS3            |

| 7          | DQ5             | 43  | CAS1            | 8         | DQ6             | 44  | RAS0            |

| 9          | DQ7             | 45  | NC              | 10        | V <sub>CC</sub> | 46  | NC              |

| 11         | PD1             | 47  | W               | 12        | A0              | 48  | NC              |

| 13         | A1              | 49  | DQ18            | 14        | A2              | 50  | DQ19            |

| 15         | A3              | 51  | DQ20            | 16        | A4              | 52  | DQ21            |

| 17         | A5              | 53  | DQ22            | 18        | A6              | 54  | DQ23            |

| 19         | NC              | 55  | NC              | 20        | NC              | 56  | DQ24            |

| 21         | DQ8             | 57  | DQ25            | 22        | DQ9             | 58  | DQ26            |

| 23         | DQ10            | 59  | DQ28            | 24        | DQ11            | 60  | DQ27            |

| 25         | DQ12            | 61  | V <sub>CC</sub> | 26        | DQ13            | 62  | DQ29            |

| 27         | DQ14            | 63  | DQ30            | 28        | A7              | 64  | DQ31            |

| 29         | NC              | 65  | NC              | 30        | V <sub>CC</sub> | 66  | PD2             |

| 31         | A8              | 67  | PD3             | 32        | A9              | 68  | PD4             |

| 33         | NC              | 69  | PD5             | 34        | RAS2            | 70  | PD6             |

| 35         | DQ15            | 71  | PD7             | 36        | NC              | 72  | V <sub>SS</sub> |

### PIN NAMES

|                       |                       |                       |                   |

|-----------------------|-----------------------|-----------------------|-------------------|

| A0 – A9 .....         | Address Inputs        | DQ0 – DQ31 ..         | Data Input/Output |

| CAS0 – CAS3 ..        | Column Address Strobe | PD1 – PD7 ...         | Presence Detect   |

| RAS0, RAS2 .....      | Row Address Strobe    | W .....               | Read/Write Input  |

| V <sub>CC</sub> ..... | Power Supply          | V <sub>SS</sub> ..... | Ground            |

| NC .....              | No Connection         |                       |                   |

All power supply and ground pins must be connected for proper operation of the device.

This document contains information on a new product under development. Motorola reserves the right to change or discontinue this product without notice.

**BLOCK DIAGRAM**

| PRESENCE DETECT PIN OUT |          |          |          |

|-------------------------|----------|----------|----------|

| Pin Name                | 60 ns    | 70 ns    | 80 ns    |

| PD1                     | NC       | NC       | NC       |

| PD2                     | $V_{SS}$ | $V_{SS}$ | $V_{SS}$ |

| PD3                     | $V_{SS}$ | $V_{SS}$ | $V_{SS}$ |

| PD4                     | NC       | NC       | NC       |

| PD5                     | NC       | $V_{SS}$ | NC       |

| PD6                     | NC       | NC       | $V_{SS}$ |

| PD7                     | NC       | NC       | NC       |

## ABSOLUTE MAXIMUM RATINGS (See Note)

| Rating                                                                                                       | Symbol                             | Value                                        | Unit |

|--------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------|------|

| Power Supply Voltage MCM32100D<br>MCM32103D, MCM32L103D                                                      | V <sub>CC</sub>                    | – 1 to + 7<br>– 0.5 to + 4.6                 | V    |

| Voltage Relative to V <sub>SS</sub> (For Any Pin Except V <sub>CC</sub> ) MCM32100D<br>MCM32103D, MCM32L103D | V <sub>in</sub> , V <sub>out</sub> | – 1 to + 7<br>– 0.5 to V <sub>CC</sub> + 0.5 | V    |

| Data Output Current per DQ Pin                                                                               | I <sub>out</sub>                   | 50                                           | mA   |

| Power Dissipation                                                                                            | P <sub>D</sub>                     | 7.2                                          | W    |

| Operating Temperature Range                                                                                  | T <sub>A</sub>                     | 0 to + 70                                    | °C   |

| Storage Temperature Range                                                                                    | T <sub>stg</sub>                   | – 55 to + 125                                | °C   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to these high-impedance circuits.

## DC OPERATING CONDITIONS AND CHARACTERISTICS

(MCM32100D V<sub>CC</sub> = 5.0 V ± 10%, MCM32103D, MCM32L103D V<sub>CC</sub> = 3.3 V ± 0.3 V)

### RECOMMENDED OPERATING CONDITIONS (All voltages referenced to V<sub>SS</sub>)

| Parameter                                                                   | Symbol          | Min            | Typ        | Max                          | Unit |

|-----------------------------------------------------------------------------|-----------------|----------------|------------|------------------------------|------|

| Supply Voltage (Operating Voltage Range) MCM32100D<br>MCM32103D, MCM32L103D | V <sub>CC</sub> | 4.5<br>3.0     | 5.0<br>3.3 | 5.5<br>3.6                   | V    |

|                                                                             | V <sub>SS</sub> | 0              | 0          | 0                            |      |

| Logic High Voltage, All Inputs MCM32100D<br>MCM32103D, MCM32L103D           | V <sub>IH</sub> | 2.4<br>2.2     | —          | 6.5<br>V <sub>CC</sub> + 0.3 | V    |

| Logic Low Voltage, All Inputs MCM32100D<br>MCM32103D, MCM32L103D            | V <sub>IL</sub> | – 1.0<br>– 0.3 | —          | 0.8<br>0.6                   | V    |

### DC CHARACTERISTICS AND SUPPLY CURRENTS

| Characteristic                                                                                                                                                                                                     | Symbol             | Min         | Max               | Unit | Notes |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|-------------------|------|-------|

| V <sub>CC</sub> Power Supply Current MCM32100D–60, t <sub>RC</sub> = 110 ns<br>MCM32100D–70, t <sub>RC</sub> = 130 ns<br>MCM32103D–80, MCM32L103D–80, t <sub>RC</sub> = 150 ns                                     | I <sub>CC1</sub>   | —<br>—<br>— | 960<br>800<br>480 | mA   | 1, 2  |

| V <sub>CC</sub> Power Supply Current (Standby) (RAS = CAS = V <sub>IH</sub> ) MCM32100D<br>MCM32103D, MCM32L103D                                                                                                   | I <sub>CC2</sub>   | —<br>—      | 16<br>8           | mA   |       |

| V <sub>CC</sub> Power Supply Current During RAS only Refresh Cycles MCM32100D–60, t <sub>RC</sub> = 110 ns<br>MCM32100D–70, t <sub>RC</sub> = 130 ns<br>MCM32103D–80, MCM32L103D–80, t <sub>RC</sub> = 150 ns      | I <sub>CC3</sub>   | —<br>—<br>— | 960<br>800<br>480 | mA   | 1, 2  |

| V <sub>CC</sub> Power Supply Current MCM32100D–60, t <sub>PC</sub> = 45 ns<br>MCM32103D–80, MCM32L103D–80, t <sub>PC</sub> = 50 ns                                                                                 | I <sub>CC4</sub>   | —<br>—      | 560<br>320        | mA   | 1, 2  |

| V <sub>CC</sub> Power Supply Current (Standby) (RAS = CAS = V <sub>CC</sub> – 0.2 V) MCM32100D<br>MCM32103D<br>MCM32L103D                                                                                          | I <sub>CC5</sub>   | —<br>—<br>— | 8<br>4<br>2       | mA   |       |

| V <sub>CC</sub> Power Supply Current During CAS Before RAS Refresh Cycle MCM32100D–60, t <sub>RC</sub> = 110 ns<br>MCM32100D–70, t <sub>RC</sub> = 130 ns<br>MCM32103D–80, MCM32L103D–80, t <sub>RC</sub> = 150 ns | I <sub>CC6</sub>   | —<br>—<br>— | 960<br>800<br>480 | mA   | 1     |

| Input Leakage Current (V <sub>SS</sub> ≤ V <sub>in</sub> ≤ V <sub>CC</sub> )                                                                                                                                       | I <sub>kg(I)</sub> | – 80        | + 80              | μA   |       |

| Output Leakage Current (CAS at Logic 1, V <sub>SS</sub> ≤ V <sub>out</sub> ≤ V <sub>CC</sub> )                                                                                                                     | I <sub>kg(O)</sub> | – 10        | 10                | μA   |       |

| Output High Voltage MCM32100D (I <sub>OH</sub> = – 5 mA)<br>MCM32103D, MCM32L103D (I <sub>OH</sub> = – 2 mA)                                                                                                       | V <sub>OH</sub>    | 2.4         | —                 | V    |       |

| Output Low Voltage MCM32100D (I <sub>OL</sub> = 4.2 mA)<br>MCM32103D, MCM32L103D (I <sub>OL</sub> = 2 mA)                                                                                                          | V <sub>OL</sub>    | —           | 0.4               | V    |       |

#### NOTES:

1. Current is a function of cycle rate and output loading; maximum current is measured at the fastest cycle rate with the output open.

2. Column Address can be changed once or less while RAS = V<sub>IL</sub> and CAS = V<sub>IH</sub>.

**CAPACITANCE** ( $f = 1.0$  MHz,  $T_A = 25^\circ\text{C}$ , MCM32100D  $V_{CC} = 5$  V,

MCM32103D, MCM32L103D  $V_{CC} = 3.3$  V, Periodically Sampled Rather Than 100% Tested)

| Characteristic                                     |  |  |  | Symbol    | Max                                               | Unit |

|----------------------------------------------------|--|--|--|-----------|---------------------------------------------------|------|

| Input Capacitance                                  |  |  |  | $C_{in}$  | 50<br>66<br>38<br>24                              | pF   |

|                                                    |  |  |  |           | $A0 - A9$<br>$W$<br>$RAS0, RAS2$<br>$CAS0 - CAS3$ |      |

| I/O Capacitance (CAS = $V_{IH}$ to Disable Output) |  |  |  | $C_{I/O}$ | 17                                                | pF   |

| DQ0 - DQ31                                         |  |  |  |           |                                                   |      |

NOTE: Capacitance measured with a Boonton Meter or effective capacitance calculated from the equation:  $C = I \Delta t / \Delta V$ .

### AC OPERATING CONDITIONS AND CHARACTERISTICS

(MCM32100D  $V_{CC} = 5.0$  V  $\pm 10\%$ , MCM32103D and MCM32L103D  $V_{CC} = 3.3$  V  $\pm 0.3$  V,

$T_A = 0$  to  $70^\circ\text{C}$ , Unless Otherwise Noted)

#### READ AND WRITE CYCLES (See Notes 1, 2, 3, and 4)

| Parameter                        | Symbol       |            | MCM32100D-60 |       | MCM32100D-70 |       | MCM32103D-80<br>MCM32L103D-80 |       | Unit | Notes |

|----------------------------------|--------------|------------|--------------|-------|--------------|-------|-------------------------------|-------|------|-------|

|                                  | Std          | Alt        | Min          | Max   | Min          | Max   | Min                           | Max   |      |       |

| Random Read or Write Cycle Time  | $t_{RELREL}$ | $t_{RC}$   | 110          | —     | 130          | —     | 150                           | —     | ns   | 5     |

| Fast Page Mode Cycle Time        | $t_{CELCEL}$ | $t_{PC}$   | 45           | —     | 45           | —     | 50                            | —     | ns   |       |

| Access Time from RAS             | $t_{RELQV}$  | $t_{RAC}$  | —            | 60    | —            | 70    | —                             | 80    | ns   | 6, 7  |

| Access Time from CAS             | $t_{CELQV}$  | $t_{CAC}$  | —            | 20    | —            | 20    | —                             | 20    | ns   | 6, 8  |

| Access Time from Column Address  | $t_{AVQV}$   | $t_{AA}$   | —            | 30    | —            | 35    | —                             | 40    | ns   | 6, 9  |

| Access Time from Precharge CAS   | $t_{CEHQV}$  | $t_{CPA}$  | —            | 40    | —            | 40    | —                             | 45    | ns   | 6     |

| CAS to Output in Low-Z           | $t_{CELQX}$  | $t_{CLZ}$  | 0            | —     | 0            | —     | 0                             | —     | ns   | 6     |

| Output Buffer and Turn-Off Delay | $t_{CEHQZ}$  | $t_{OFF}$  | 0            | 20    | 0            | 20    | 0                             | 20    | ns   | 10    |

| Transition Time (Rise and Fall)  | $t_T$        | $t_T$      | 3            | 50    | 3            | 50    | 3                             | 50    | ns   |       |

| RAS Precharge Time               | $t_{REHREL}$ | $t_{RP}$   | 40           | —     | 50           | —     | 60                            | —     | ns   |       |

| RAS Pulse Width                  | $t_{RELREH}$ | $t_{RAS}$  | 60           | 10 k  | 70           | 10 k  | 80                            | 10 k  | ns   |       |

| RAS Pulse Width (Fast Page Mode) | $t_{RELREH}$ | $t_{RASP}$ | 60           | 200 k | 70           | 200 k | 80                            | 200 k | ns   |       |

| RAS Hold Time                    | $t_{CELREH}$ | $t_{RSH}$  | 20           | —     | 20           | —     | 20                            | —     | ns   |       |

| CAS Hold Time                    | $t_{RELCEH}$ | $t_{CSH}$  | 60           | —     | 70           | —     | 80                            | —     | ns   |       |

| CAS Precharge to RAS Hold Time   | $t_{CEHREH}$ | $t_{RHCP}$ | 40           | —     | 40           | —     | 45                            | —     | ns   |       |

| CAS Pulse Width                  | $t_{CELCEH}$ | $t_{CAS}$  | 20           | 10 k  | 20           | 10 k  | 20                            | 10 k  | ns   |       |

| RAS to CAS Delay Time            | $t_{RELCEL}$ | $t_{RCD}$  | 20           | 40    | 20           | 50    | 20                            | 60    | ns   | 11    |

| RAS to Column Address Delay Time | $t_{RELAV}$  | $t_{RAD}$  | 15           | 30    | 15           | 35    | 15                            | 40    | ns   | 12    |

NOTES: (continued)

- $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals. Transition times are measured between  $V_{IH}$  and  $V_{IL}$ .

- An initial pause of 200  $\mu\text{s}$  for the MCM32100D and 2 ms for the MCM32103D or MCM32L102D is required after power-up followed by 8 RAS cycles before proper device operation is guaranteed.

- The transition time specification applies for all input signals. In addition to meeting the transition rate specification, all input signals must transition between  $V_{IH}$  and  $V_{IL}$  (or between  $V_{IL}$  and  $V_{IH}$ ) in a monotonic manner.

- AC measurements  $t_T = 5.0$  ns.

- The specification for  $t_{RC}$  (min) is used only to indicate cycle time at which proper operation over the full temperature range ( $0^\circ\text{C} \leq T_A \leq 70^\circ\text{C}$ ) is ensured.

- MCM32100D measured with a current load equivalent to 2 TTL ( $-200 \mu\text{A}$ ,  $+4$  mA) loads and 100 pF with the data output trip points set at  $V_{OH} = 2.0$  V and MCM32103D and MCM32L103D measured with a load equivalent to 100 pF and  $V_{OH} = 2.0$  V ( $I_{out} = -2$  mA) and  $V_{OL} = 0.8$  V, ( $I_{out} = 2$  mA).

- Assumes that  $t_{RCD} \leq t_{RCD}$  (max).

- Assumes that  $t_{RCD} \geq t_{RCD}$  (max).

- Assumes that  $t_{RAD} \geq t_{RAD}$  (max).

- $t_{OFF}$  (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- Operation within the  $t_{RCD}$  (max) limit ensures that  $t_{RAC}$  (max) can be met.  $t_{RCD}$  (max) is specified as a reference point only; if  $t_{RCD}$  is greater than the specified  $t_{RCD}$  (max) limit, then access time is controlled exclusively by  $t_{CAC}$ .

- Operation within the  $t_{RAD}$  (max) limit ensures that  $t_{RAC}$  (max) can be met.  $t_{RAD}$  (max) is specified as a reference point only; if  $t_{RAD}$  is greater than the specified  $t_{RAD}$  (max), then access time is controlled exclusively by  $t_{AA}$ .

**READ AND WRITE CYCLES (Continued)**

| Parameter                                            | Symbol       |            | MCM32100D-60 |     | MCM32100D-70 |     | MCM32103D-80<br>MCM32L103D-80 |           | Unit | Notes |

|------------------------------------------------------|--------------|------------|--------------|-----|--------------|-----|-------------------------------|-----------|------|-------|

|                                                      | Std          | Alt        | Min          | Max | Min          | Max | Min                           | Max       |      |       |

| CAS to RAS Precharge Time                            | $t_{CEHREL}$ | $t_{CRP}$  | 5            | —   | 5            | —   | 5                             | —         | ns   |       |

| CAS Precharge Time                                   | $t_{CEHCEL}$ | $t_{CP}$   | 10           | —   | 10           | —   | 10                            | —         | ns   |       |

| Row Address Setup Time                               | $t_{AVREL}$  | $t_{ASR}$  | 0            | —   | 0            | —   | 0                             | —         | ns   |       |

| Row Address Hold Time                                | $t_{RELAX}$  | $t_{RAH}$  | 10           | —   | 10           | —   | 10                            | —         | ns   |       |

| Column Address Setup Time                            | $t_{AVCEL}$  | $t_{ASC}$  | 0            | —   | 0            | —   | 0                             | —         | ns   |       |

| Column Address Hold Time                             | $t_{CELAX}$  | $t_{CAH}$  | 15           | —   | 15           | —   | 15                            | —         | ns   |       |

| Column Address to RAS Lead Time                      | $t_{AVREH}$  | $t_{RAL}$  | 30           | —   | 35           | —   | 40                            | —         | ns   |       |

| Read Command Setup Time                              | $t_{WHCEL}$  | $t_{RCS}$  | 0            | —   | 0            | —   | 0                             | —         | ns   |       |

| Read Command Hold Time Referenced to CAS             | $t_{CEHWX}$  | $t_{RCH}$  | 0            | —   | 0            | —   | 0                             | —         | ns   | 13    |

| Read Command Hold Time Referenced to RAS             | $t_{REHWX}$  | $t_{RRH}$  | 0            | —   | 0            | —   | 0                             | —         | ns   | 13    |

| Write Command Hold Time Referenced to CAS            | $t_{CELWH}$  | $t_{WCH}$  | 10           | —   | 15           | —   | 15                            | —         | ns   |       |

| Write Command Pulse Width                            | $t_{WLWH}$   | $t_{WP}$   | 10           | —   | 15           | —   | 15                            | —         | ns   |       |

| Write Command to RAS Lead Time                       | $t_{WLREH}$  | $t_{RWL}$  | 20           | —   | 20           | —   | 20                            | —         | ns   |       |

| Write Command to CAS Lead Time                       | $t_{WLCEH}$  | $t_{CWL}$  | 20           | —   | 20           | —   | 20                            | —         | ns   |       |

| Data in Setup Time                                   | $t_{DVCEL}$  | $t_{DS}$   | 0            | —   | 0            | —   | 0                             | —         | ns   | 14    |

| Data in Hold Time                                    | $t_{CELDX}$  | $t_{DH}$   | 15           | —   | 15           | —   | 15                            | —         | ns   | 14    |

| Refresh Period<br>MCM32L103D                         | $t_{RVRV}$   | $t_{RFSH}$ | —            | 16  | —            | 16  | —                             | 16<br>128 | ms   |       |

| Write Command Setup Time                             | $t_{WLCEL}$  | $t_{WCS}$  | 0            | —   | 0            | —   | 0                             | —         | ns   | 15    |

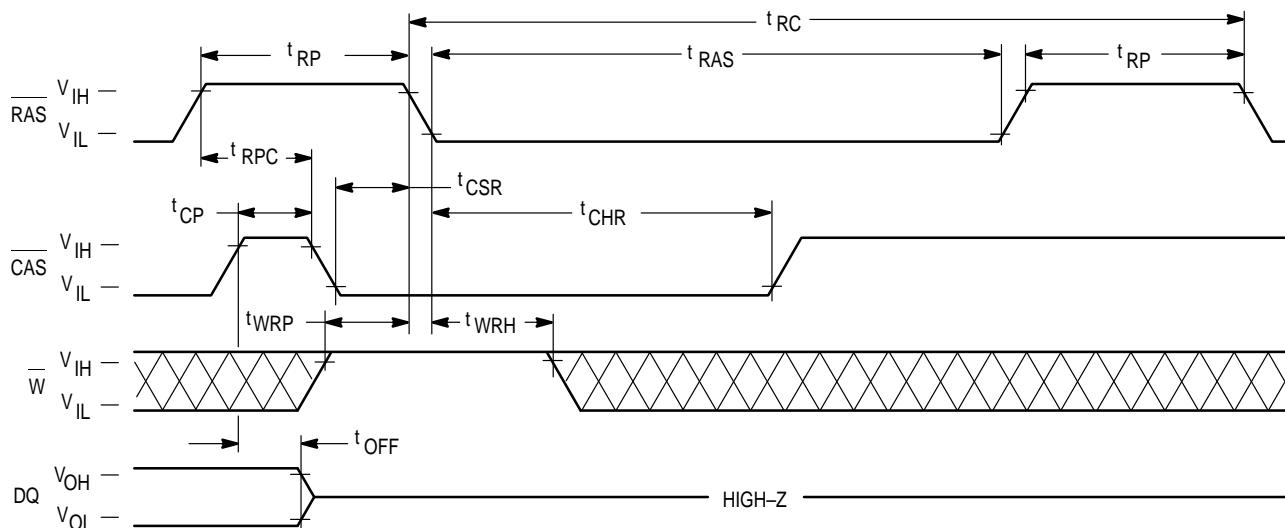

| CAS Setup Time for CAS Before RAS Refresh            | $t_{RELCEL}$ | $t_{CSR}$  | 5            | —   | 5            | —   | 5                             | —         | ns   |       |

| CAS Hold Time for CAS Before RAS Refresh             | $t_{RELCEH}$ | $t_{CHR}$  | 15           | —   | 15           | —   | 15                            | —         | ns   |       |

| RAS Precharge to CAS Active Time                     | $t_{REHCEL}$ | $t_{RPC}$  | 0            | —   | 0            | —   | 0                             | —         | ns   |       |

| CAS Precharge Time for CAS Before RAS Counter Time   | $t_{CEHCEL}$ | $t_{CPT}$  | 30           | —   | 40           | —   | 40                            | —         | ns   |       |

| Write to RAS Precharge Time (CAS Before RAS Refresh) | $t_{WHREL}$  | $t_{WRP}$  | 10           | —   | 10           | —   | 10                            | —         | ns   |       |

| Write to RAS Hold Time (CAS Before RAS Refresh)      | $t_{RELWL}$  | $t_{WRH}$  | 10           | —   | 10           | —   | 10                            | —         | ns   |       |

NOTES:

13. Either  $t_{RRH}$  or  $t_{RCH}$  must be satisfied for a read cycle.

14. These parameters are referenced to CAS leading edge in random write cycles.

15.  $t_{WCS}$  is not a restrictive operating parameter. It is included in the data sheet as an electrical characteristic only; if  $t_{WCS} \geq t_{WCS}$  (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle. If this condition is not satisfied, the condition of the data out (at access time) is indeterminate.

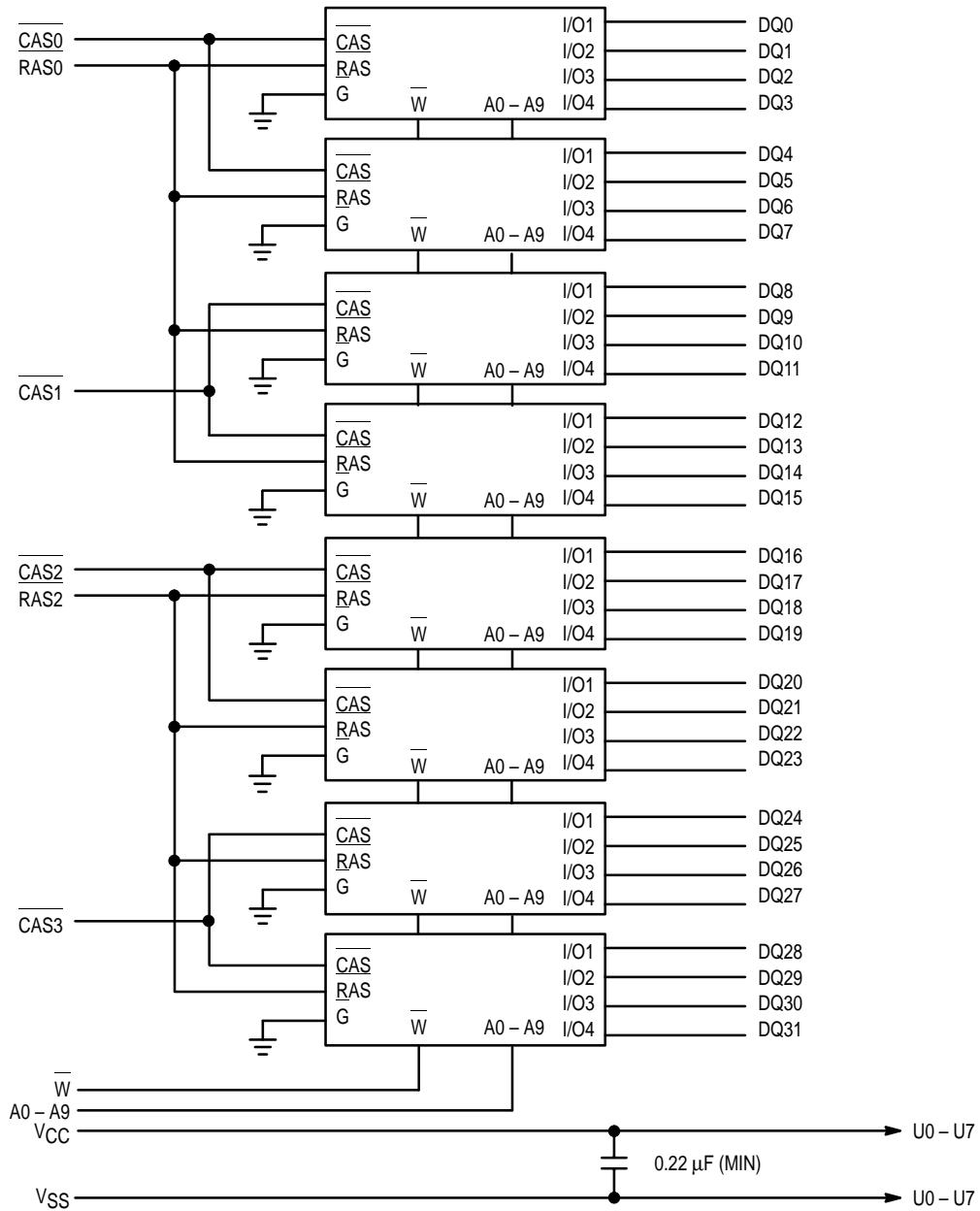

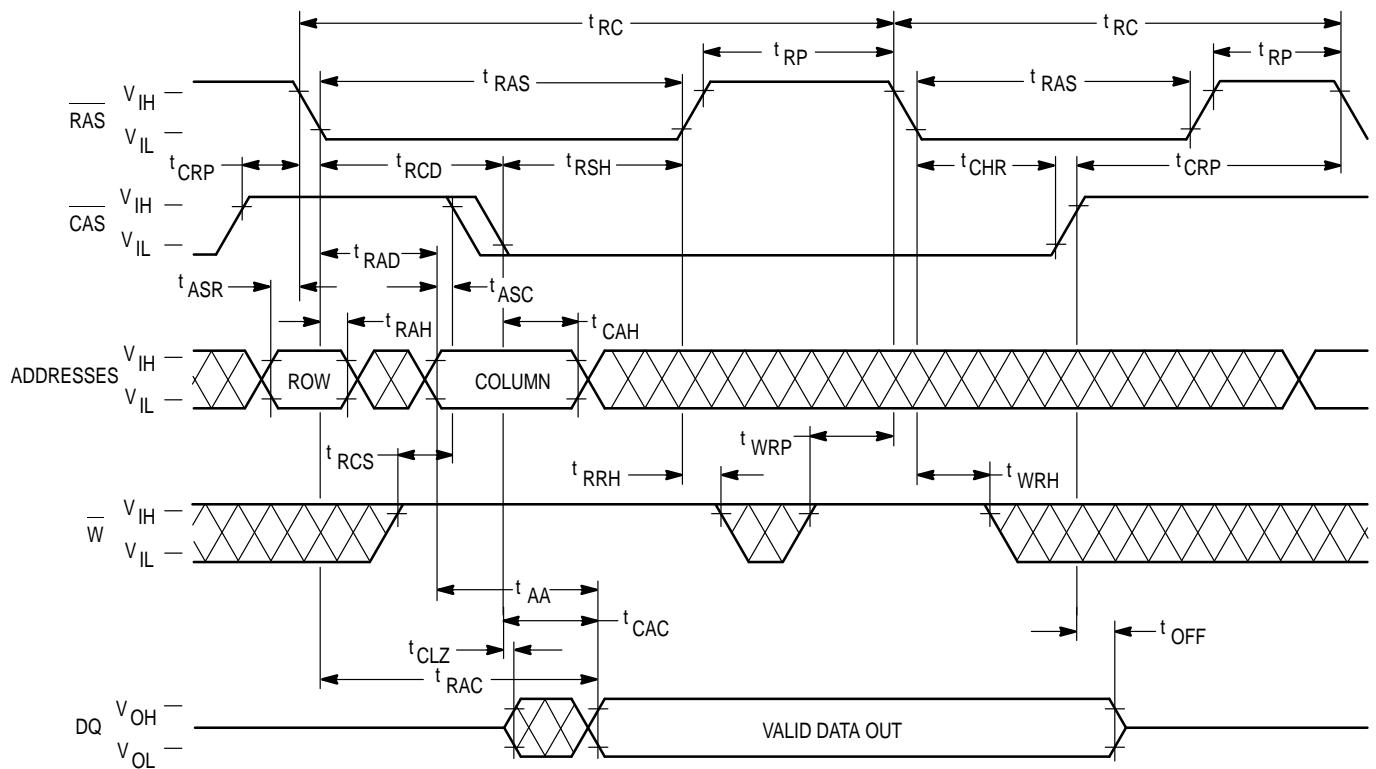

## READ CYCLE

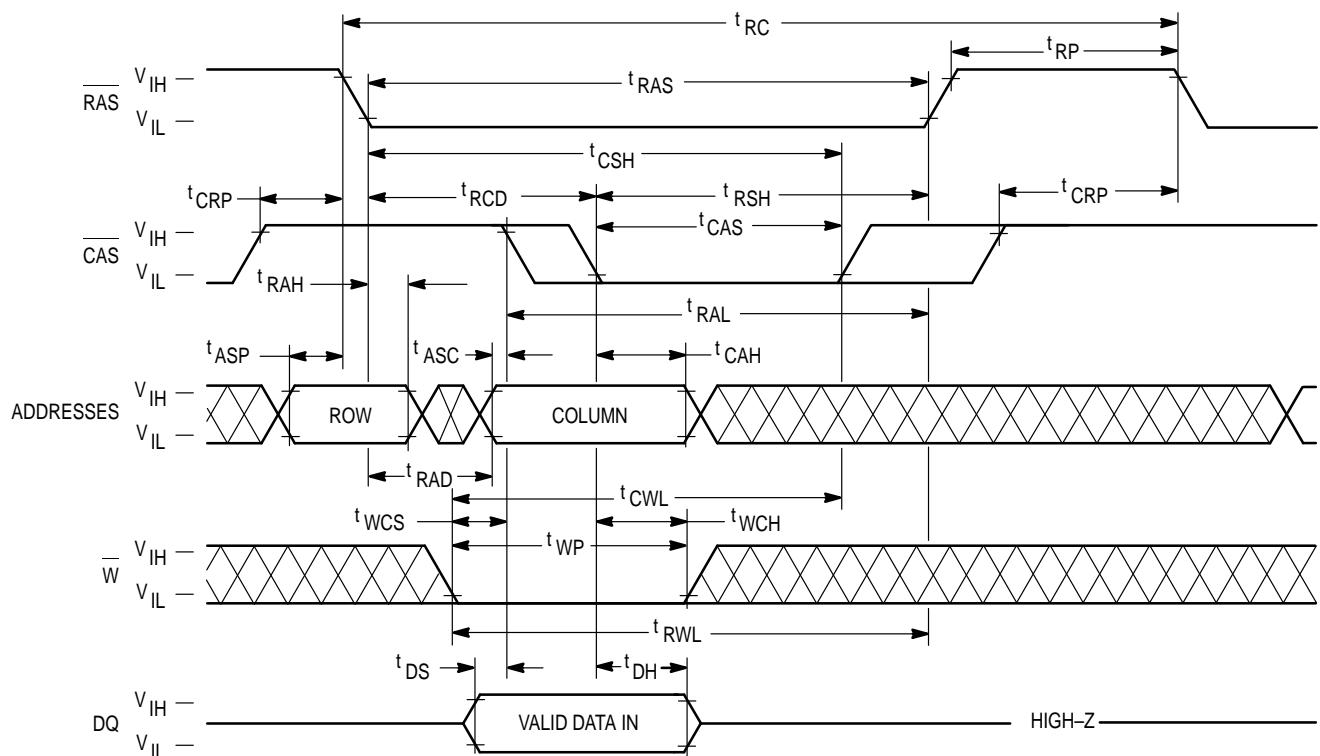

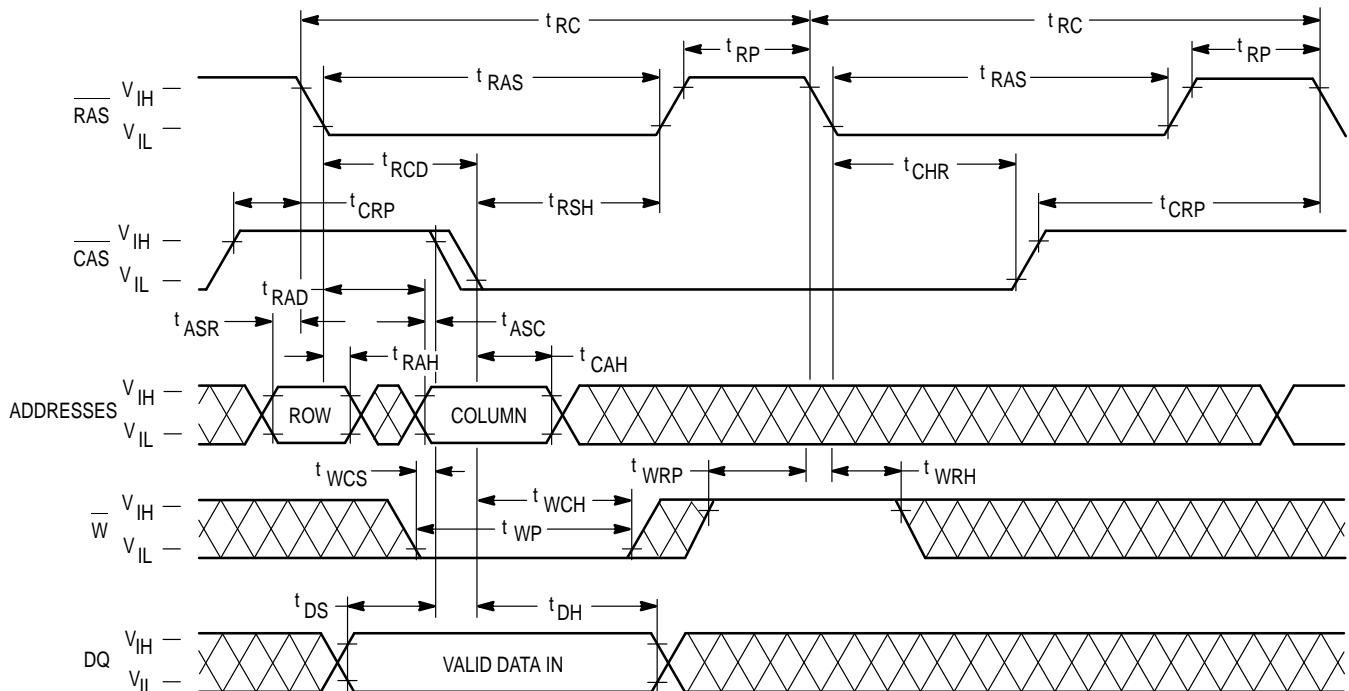

## EARLY WRITE CYCLE

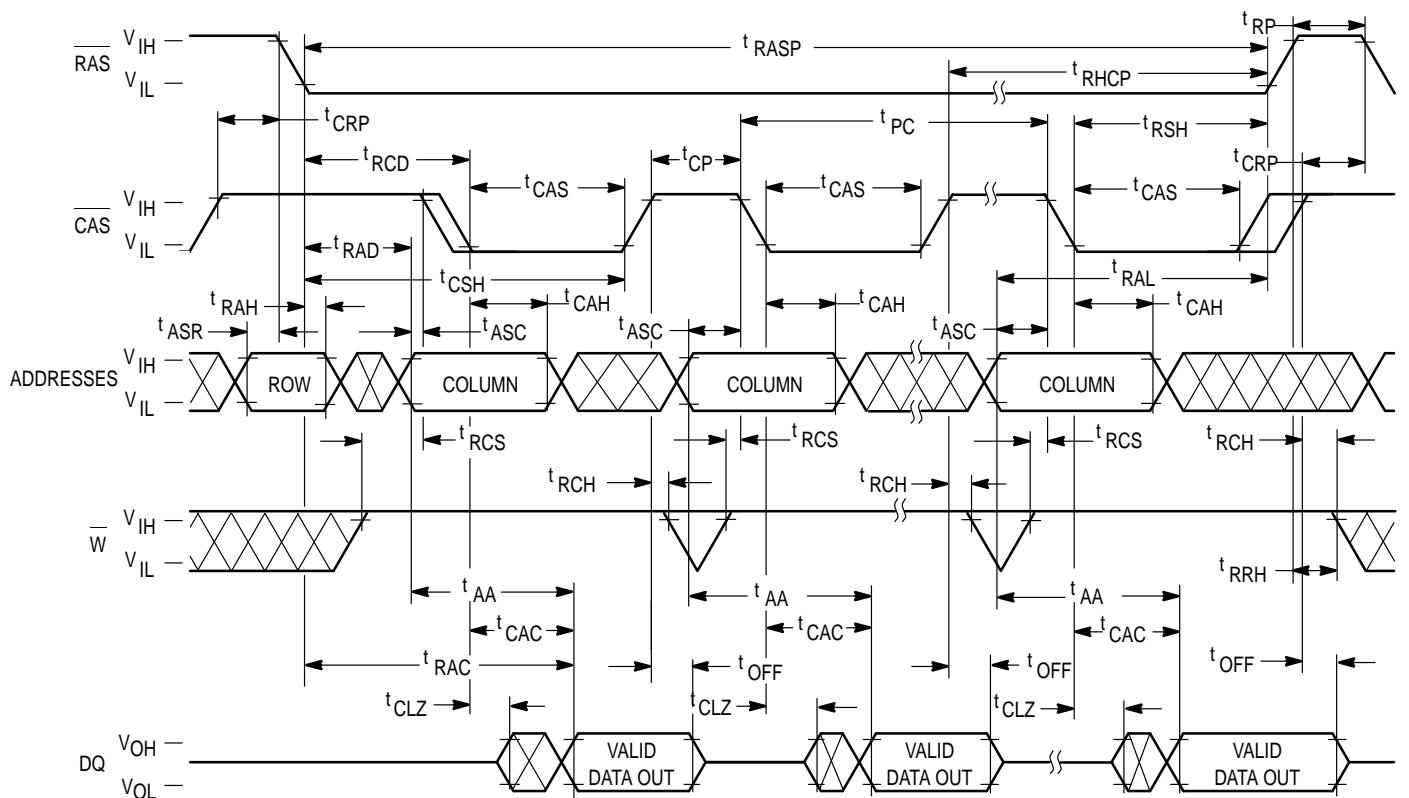

## FAST PAGE MODE READ CYCLE

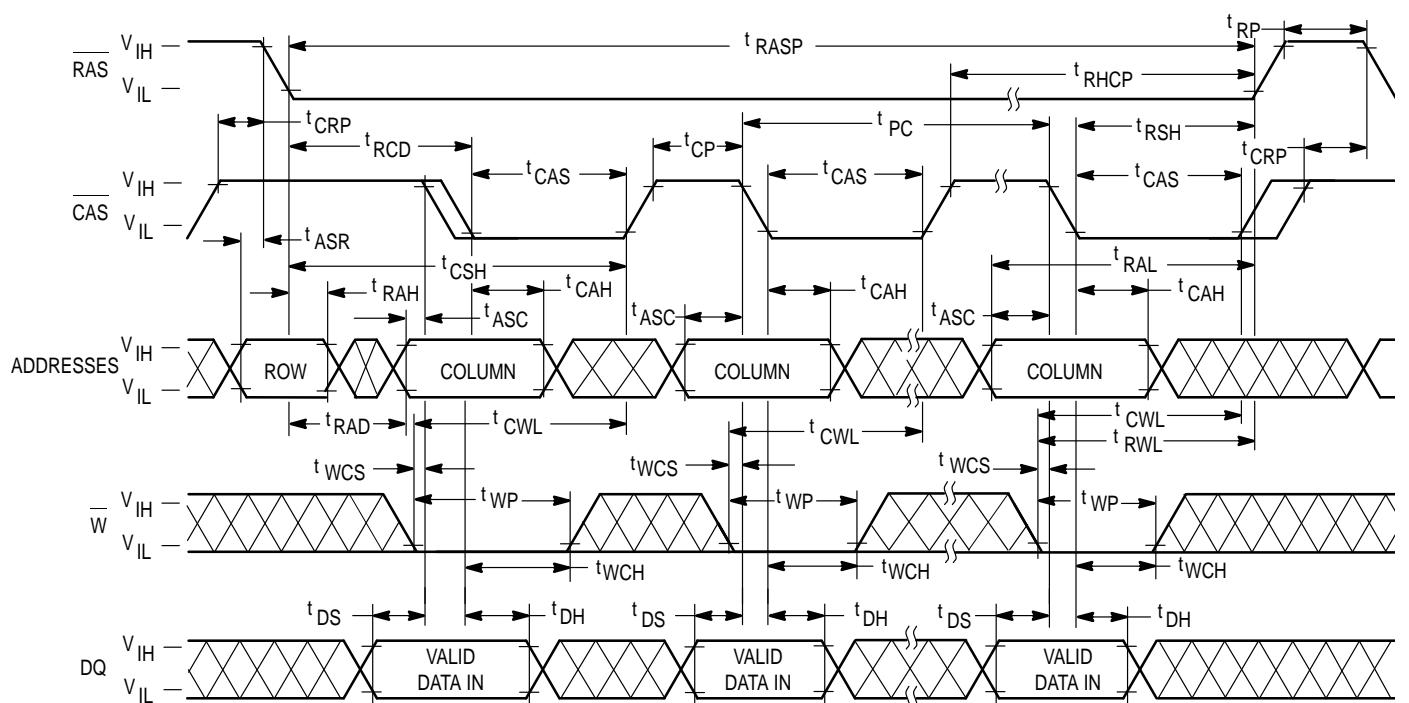

## FAST PAGE MODE EARLY WRITE CYCLE

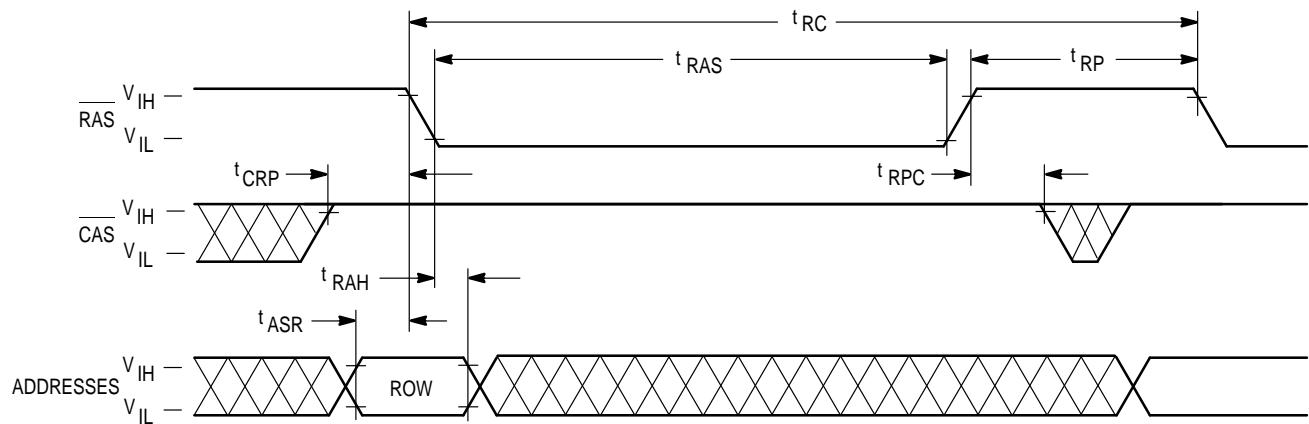

**RAS ONLY REFRESH CYCLE**

(W is Don't Care)

**CAS BEFORE RAS REFRESH CYCLE**

(A0 – A9 are Don't Care)

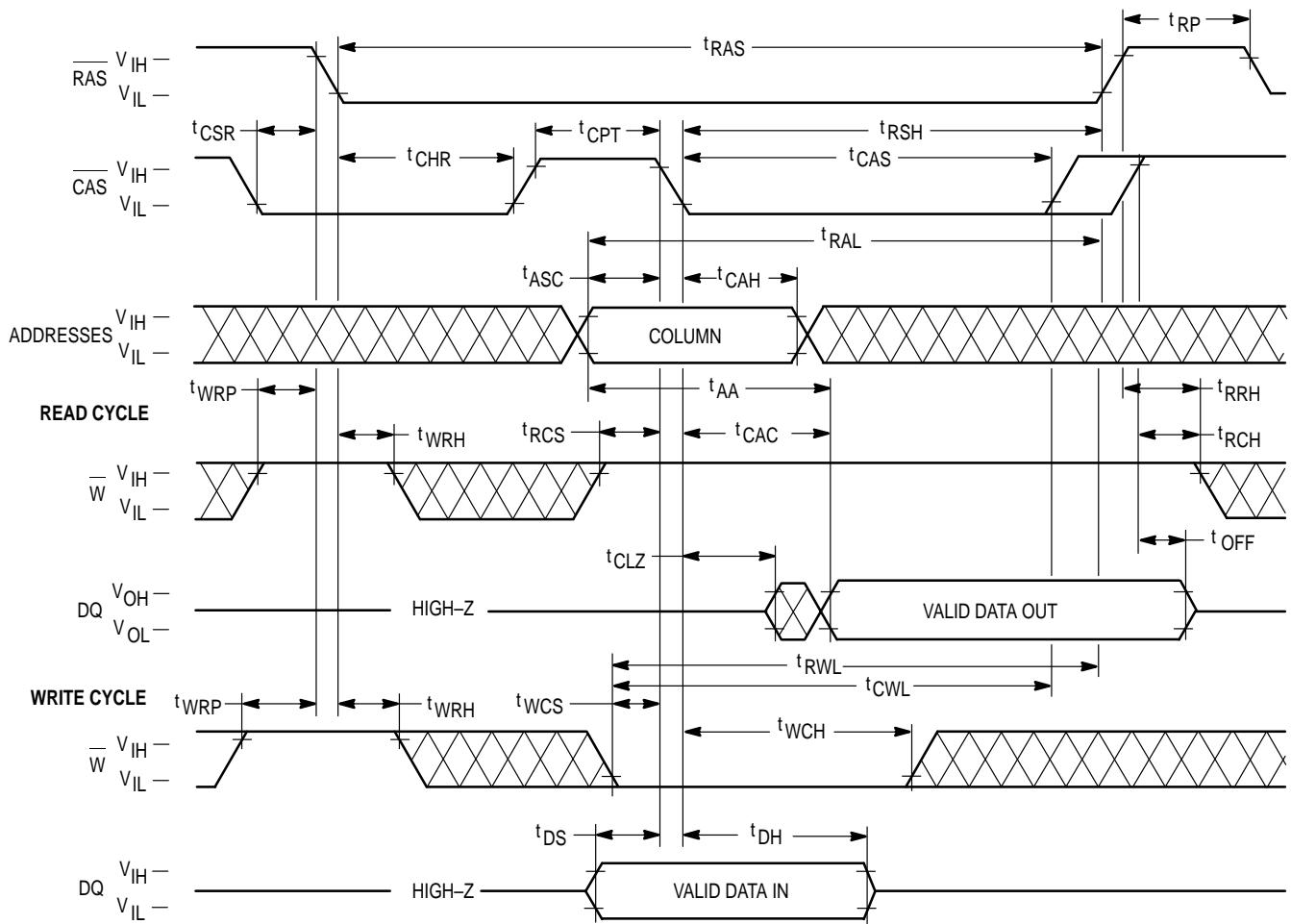

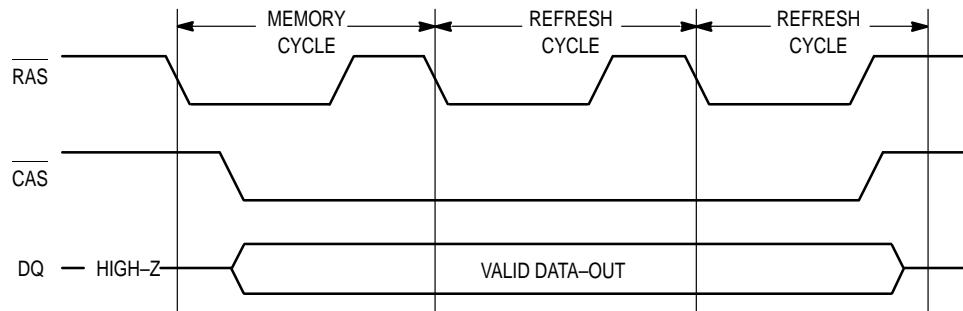

### HIDDEN REFRESH CYCLE (READ)

### HIDDEN REFRESH CYCLE (WRITE)

### CAS BEFORE RAS REFRESH COUNTER TEST CYCLE

## DEVICE INITIALIZATION

On power-up, an initial pause of 200 microseconds for the MCM32100D or two milliseconds for the MCM32103D and MCM32L103D is required for the internal substrate generator to establish the correct bias voltage. This must be followed by a minimum of eight active cycles of the row address strobe (clock) to initialize all dynamic nodes within the module. During an extended inactive state (greater than 16 milliseconds for the MCM32100D or MCM32103D and greater than 128 milliseconds for MCM32L103D with the device powered up), a wake up sequence of eight active cycles is necessary to ensure proper operation.

## ADDRESSING THE RAM

The ten address pins on the device are time multiplexed at the beginning of a memory cycle by two clocks, row address strobe (RAS) and column address strobe (CAS), into two separate 10-bit address fields. A total of twenty address bits, ten rows and ten columns, will decode one of the 1,048,576 word locations in the device. RAS active transition is followed by CAS active transition (active =  $V_{IL}$ ,  $t_{RCD}$  minimum) for all read or write cycles. The delay between RAS and CAS active transitions, referred to as the **multiplex window**, gives a system designer flexibility in setting up the external addresses into the RAM.

The external CAS signal is ignored until an internal RAS signal is available. This "gate" feature on the external CAS clock enables the internal CAS line as soon as the row address hold time ( $t_{RAH}$ ) specification is met (and defines  $t_{RCD}$  minimum). The multiplex window can be used to absorb skew delays in switching the address bus from row to column addresses and in generating the CAS clock.

There are three other variations in addressing the module: **RAS only refresh cycle**, **CAS before RAS refresh cycle**, and **page mode**. All three are discussed in separate sections that follow.

## READ CYCLE

The DRAM may be read with either a "normal" random read cycle or a page mode read cycle. The normal read cycle is outlined here, while the page mode cycle is discussed in a separate section.

The normal read cycle begins as described in **ADDRESSING THE RAM**, with RAS and CAS active transitions latching the desired bit location. The write (W) input level must be high ( $V_{IH}$ ),  $t_{RCS}$  (minimum) before the CAS active transition, to enable read mode.

Both the RAS and CAS clocks trigger a sequence of events which are controlled by several delayed internal clocks. The internal clocks are linked in such a manner that the read access time of the device is independent of the address multiplex window. CAS controls read access time: CAS must be active before or at  $t_{RCD}$  maximum to guarantee valid data out (DQ) at  $t_{RAC}$  (access time from RAS active transition). If the  $t_{RCD}$  maximum is exceeded, read access time is determined by the CAS clock active transition ( $t_{CAC}$ ).

The RAS and CAS clocks must remain active for a minimum time of  $t_{RAS}$  and  $t_{CAS}$  respectively, to complete the read cycle. W must remain high throughout the cycle, and for time  $t_{RRH}$  or  $t_{RCH}$  after RAS or CAS inactive transition, respectively, to maintain the data at that bit location. Once RAS transitions to inactive, it must remain inactive for a minimum

time of  $t_{RP}$  to precharge the internal device circuitry for the next active cycle. DQ is valid, but not latched, as long as the CAS clock is active. When the CAS clock transitions to inactive, the output will switch to High-Z (three-state)  $t_{OFF}$  after the inactive transition.

## WRITE CYCLE

The user can write to the DRAM with either an early write or a page mode early write cycle. Early write mode is discussed here, while page mode write operations are covered in a separate section.

A write cycle begins as described in **ADDRESSING THE RAM**. Write mode is enabled by the transition of W to active ( $V_{IL}$ ). Early write mode is distinguished by the active transition of W, with respect to CAS. Minimum active time  $t_{RAS}$  and  $t_{CAS}$ , and precharge time  $t_{RP}$  apply to write mode, as in the read mode.

An early write cycle is characterized by W active transition at minimum time  $t_{WCS}$  before CAS active transition. Data in (DQ) is referenced to CAS in an early write cycle. RAS and CAS clocks must stay active for  $t_{RWL}$  and  $t_{CWL}$ , respectively, after the start of the early write operation to complete the cycle.

## PAGE MODE CYCLES

Page mode allows fast successive data operations at all 1024 column locations on a selected row of the module. Read access time in page mode ( $t_{CAC}$ ) is typically half the regular RAS clock access time,  $t_{RAC}$ . Page mode operation consists of keeping RAS active while toggling CAS between  $V_{IH}$  and  $V_{IL}$ . The row is latched by RAS active transition, while each CAS active transition allows selection of a new column location on the row.

A page mode cycle is initiated by a normal read or write cycle, as described in prior sections. Once the timing requirements for the first cycle are met, CAS transitions to inactive for minimum  $t_{CP}$ , while RAS remains low ( $V_{IL}$ ). The second CAS active transition while RAS is low initiates the first page mode cycle ( $t_{PC}$ ). Either a read or write operation can be performed in a page mode cycle, subject to the same conditions as in normal operation (previously described). These operations can be intermixed in consecutive page mode cycles and performed in any order. The maximum number of consecutive page mode cycles is limited by  $t_{RASP}$ . Page mode operation is ended when RAS transitions to inactive, coincident with or following CAS inactive transition.

## REFRESH CYCLES

The dynamic RAM design is based on capacitor charge storage for each bit in the array. This charge will tend to degrade with time and temperature. Each bit must be periodically refreshed (recharged) to maintain the correct bit state. Bits in the MCM32100D or MCM32103D require refresh every 16 milliseconds. Bits in the MCM32L103D require refresh every 128 milliseconds.

This is accomplished by cycling through the 1024 row addresses in sequence within the specified refresh time. All the bits on a row are refreshed simultaneously when the row is addressed. Distributed refresh implies a row refresh every 15.6 microseconds for the MCM32100D or MCM32103D and every 124.8 microseconds for the MCM32L103D. Burst refresh, a refresh of all 1024 rows consecutively, must be performed every 16 milliseconds for the MCM32100D or

MCM32103D and every 128 milliseconds for the MCM32L103D.

A normal read or write operation to the RAM will refresh all the bits associated with the particular row decoded. Three other methods of refresh, **RAS-only refresh**, **CAS before RAS refresh**, and **hidden refresh** are available on this device for greater system flexibility.

### RAS-Only Refresh

RAS-only refresh consists of RAS transition to active, latching the row address to be refreshed, while CAS remains high (VIH) throughout the cycle. An external counter is employed to ensure all rows are refreshed within the specified limit.

### CAS Before RAS Refresh

CAS before RAS refresh is enabled by bringing CAS active before RAS. This clock order actives an internal refresh counter that generates the row address to be refreshed. External address lines are ignored during the automatic refresh cycle. The output buffer remains at the same state it was in during the previous cycle (hidden refresh). W must be inactive for time  $t_{WRP}$  before and time  $t_{WRH}$  after RAS active transition to prevent switching the device into a **test mode cycle**.

### Hidden Refresh

Hidden refresh allows refresh cycles to occur while maintaining valid data at the output pin. Holding CAS active at the end of a read or write cycle, while RAS cycles inactive for  $t_{RP}$

and back to active, starts the hidden refresh. This is essentially the execution of a **CAS before RAS refresh** from a cycle in progress (see Figure 1). W is subject to the same conditions with respect to RAS active transition (to prevent test mode cycle) as in **CAS before RAS refresh**.

### CAS BEFORE RAS REFRESH COUNTER TEST

The internal refresh counter of the device can be tested with a **CAS before RAS refresh counter test**. This refresh counter test is performed with read and write operations. During this test, the internal refresh counter generates the row address, while the external address input supplies the column address. The entire array is refreshed after 1024 test cycles, as indicated by the check data written in each row. See **CAS before RAS refresh counter test cycle** timing diagram.

The test can be performed only after a minimum of **8 CAS before RAS** initialization cycles. The test procedure is as follows:

1. Write 0s into all memory cells (normal write mode).

2. Select a column address, and read 0 out of the cell by performing **CAS before RAS refresh counter test, read cycle**. Repeat this operation 1024 times.

3. Select a column address, and write 1 into the cell by performing **CAS before RAS refresh counter test, write cycle**. Repeat this operation 1024 times.

4. Read 1s (normal read mode), which were written at step three.

5. Repeat steps one through four using complement data.

Figure 1. Hidden Refresh Cycle

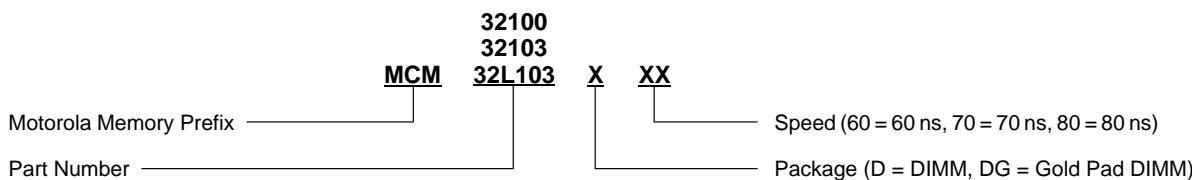

### ORDERING INFORMATION (Order by Full Part Number)

Full Part Numbers —

MCM32100D60

MCM32100DG60

MCM32100D70

MCM32100DG70

MCM32103D80

MCM32103DG80

MCM32L103D80

MCM32L103DG80

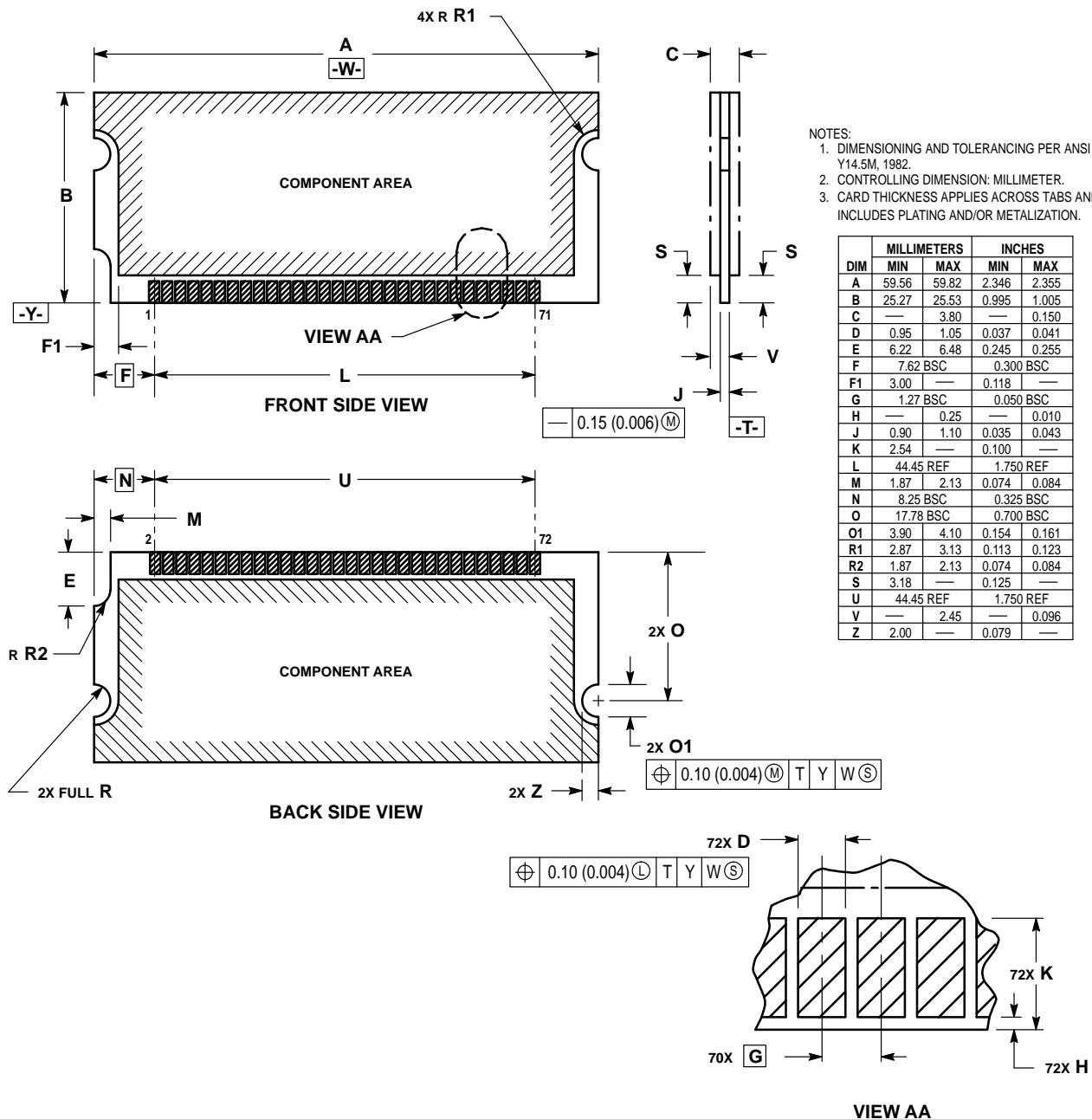

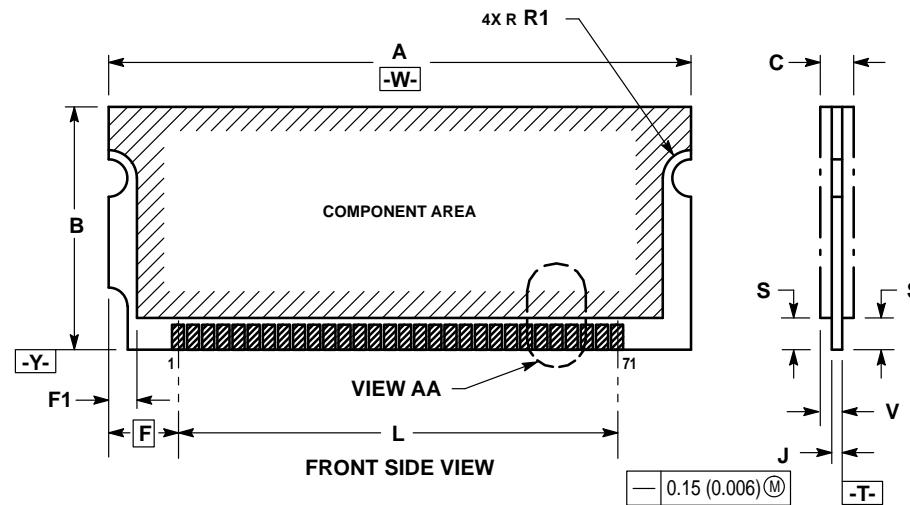

## PACKAGE DIMENSIONS

### D PACKAGE SMALL OUTLINE DIMM MODULE CASE 992-01

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **TM** are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

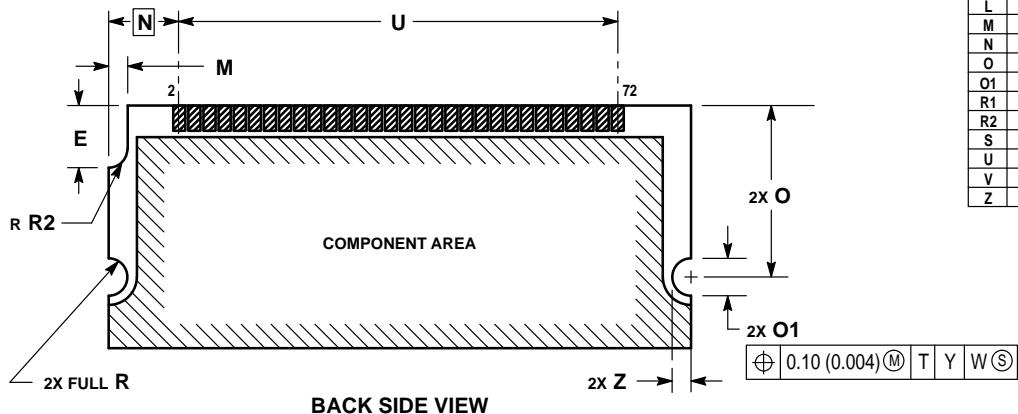

## PACKAGE DIMENSIONS

### DG PACKAGE SMALL OUTLINE DIMM MODULE CASE 992A-01

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. CARD THICKNESS APPLIES ACROSS TABS AND INCLUDES PLATING AND/OR METALIZATION.

| DIM | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

|     | MIN         | MAX   | MIN       | MAX   |

| A   | 59.56       | 59.82 | 2.346     | 2.355 |

| B   | 25.27       | 25.53 | 0.995     | 1.005 |

| C   | —           | 3.80  | —         | 0.150 |

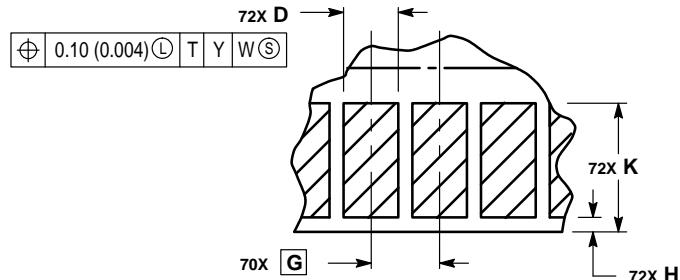

| D   | 0.95        | 1.05  | 0.037     | 0.041 |

| E   | 6.22        | 6.48  | 0.245     | 0.255 |

| F   | 7.62 BSC    | —     | 0.300 BSC | —     |

| F1  | 3.00        | —     | 0.118     | —     |

| G   | 1.27 BSC    | —     | 0.050 BSC | —     |

| H   | —           | 0.25  | —         | 0.010 |

| J   | 0.90        | 1.10  | 0.035     | 0.043 |

| K   | 2.54        | —     | 0.100     | —     |

| L   | 44.45 REF   | —     | 1.750 REF | —     |

| M   | 1.87        | 2.13  | 0.074     | 0.084 |

| N   | 8.25 BSC    | —     | 0.325 BSC | —     |

| O   | 17.78 BSC   | —     | 0.700 BSC | —     |

| O1  | 3.90        | 4.10  | 0.154     | 0.161 |

| R1  | 2.87        | 3.13  | 0.113     | 0.123 |

| R2  | 1.87        | 2.13  | 0.074     | 0.084 |

| S   | 3.18        | —     | 0.125     | —     |

| U   | 44.45 REF   | —     | 1.750 REF | —     |

| V   | —           | 2.45  | —         | 0.096 |

| Z   | 2.00        | —     | 0.079     | —     |

VIEW AA

#### How to reach us:

**USA/EUROPE:** Motorola Literature Distribution;

P.O. Box 20912; Phoenix, Arizona 85036. 1-800-441-2447

**MFAX:** RMFAX0@email.sps.mot.com – TOUCHTONE (602) 244-6609

**INTERNET:** <http://Design-NET.com>

**JAPAN:** Nippon Motorola Ltd.; Tatsumi-SPD-JLDC, Toshikatsu Otsuki,

6F Seibu-Butsuryu-Center, 3-14-2 Tatsumi Koto-Ku, Tokyo 135, Japan. 03-3521-8315

**HONG KONG:** Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park,

51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298