## $512K \times 2$ BANKS $\times$ 16 BITS SDRAM

#### **GENERAL DESCRIPTION**

W981616AH is a high-speed synchronous dynamic random access memory (SDRAM), organized as 512K words  $\times$  2 banks  $\times$  16 bits. Using pipelined architecture and 0.20  $\mu$ m process technology, W981616AH delivers a data bandwidth of up to 332M bytes per second (-6). For different applications the W981616AH is sorted into the following speed grades: -6, -7, and -8.

Accesses to the SDRAM are burst oriented. Consecutive memory location in one page can be accessed at a burst length of 1, 2, 4, 8 or full page when a bank and row is selected by an ACTIVE command. Column addresses are automatically generated by the SDRAM internal counter in burst operation. Random column read is also possible by providing its address at each clock cycle. The multiple bank nature enables interleaving among internal banks to hide the precharging time.

By having a programmable Mode Register, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. W981616AH is ideal for main memory in high performance applications.

#### **FEATURES**

- 3.3V ±0.3V power supply

- Up to 166 MHz clock frequency

- 524,288 words x 2 banks x 16 bits organization

- Auto Refresh and Self Refresh

- CAS latency: 2 and 3

- Burst Length: 1, 2, 4, 8, and full page

- Burst read, Single Write Mode

- Byte data controlled by UDQM and LDQM

- Auto-precharge and controlled precharge

- 4K refresh cycles/64 mS

- Interface: LVTTL

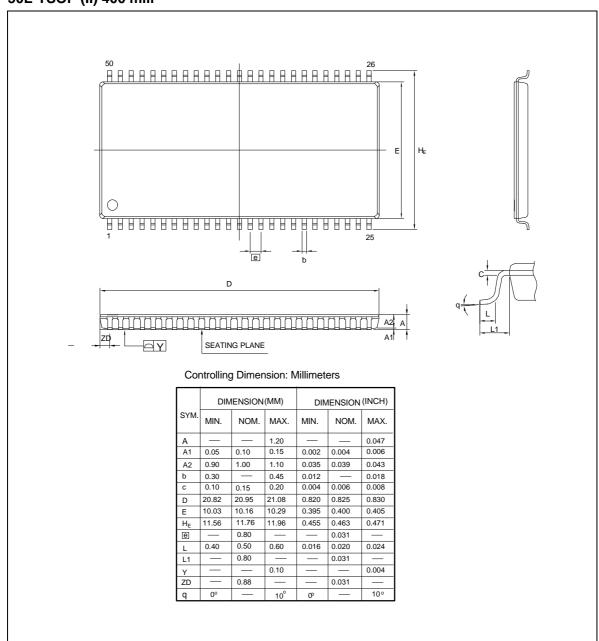

- Packaged in 50-pin, 400 mil TSOP II

### **PIN CONFIGURATION**

| THE COMPTON       |            |       |                     |

|-------------------|------------|-------|---------------------|

|                   | _          |       |                     |

| V <sub>CC</sub> [ | 1          | 50    | □ Vss               |

| DQ0 [             | 2          | I     | DQ15                |

|                   | □ 3        |       | DQ14                |

| VssQ [            | □ 4        | 47    | □ VssQ              |

| DQ2               | <b>□</b> 5 | 46    | □ DQ13              |

| DQ3 [             | □ 6        | 45    | DQ12                |

| VccQ [            | 7          | 44    | □ VccQ              |

| DQ4 [             | 8          | 43    | □ DQ11              |

| DQ5 [             | 9          | 42    | DQ10                |

| VssQ [            | <u> </u>   | 0 41  | □ V <sub>SS</sub> Q |

| DQ6 [             | <u> </u>   | 1 40  | DQ9                 |

| DQ7 [             | <u> </u>   | 2 39  | DQ8                 |

| VccQ [            | □ 13       | 3 38  | □ VccQ              |

| LDQM [            | □ 14       | 4 37  | □ NC                |

| WE [              | □ 15       | 5 36  | UDQM                |

| CAS               | □ 16       | 6 35  | □ CLK               |

|                   | □ 17       | 7 34  | ☐ CKE               |

| CS (              | □ 18       | 8 33  | □ NC                |

| BA [              | ☐ 19       | 9 32  | A9                  |

| A10 [             | 20         | 0 31  | A8                  |

| A0 [              | 21         | 1 30  | A7                  |

| A1 [              | ☐ 22       | 2 29  | A6                  |

| A2 [              | ☐ 23       | 23 28 | A5                  |

| A3 [              | □ 24       | 24 27 | A4                  |

| Vcc [             | ☐ 25       | 25 26 | □ V <sub>SS</sub>   |

|                   | ш          |       |                     |

|                   |            |       |                     |

Publication Release Date: February 2000 Revision A2

# W981616AH

# **PIN DESCRIPTION**

| PIN NUMBER                                                        | PIN NAME      | FUNCTION                        | DESCRIPTION                                                                                                                                                                         |

|-------------------------------------------------------------------|---------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20–24,<br>27–32                                                   | A0-A10        | Address                         | Multiplexed pins for row and column address.<br>Row address: A0–A10. Column address: A0–A7.                                                                                         |

| 19                                                                | ВА            | Bank Select                     | Select bank to activate during row address latch time, or bank to read/write during column address latch time.                                                                      |

| 2, 3, 5, 6, 8, 9,<br>11, 12, 39, 40,<br>42, 43, 45, 46,<br>48, 49 | DQ0-DQ15      | Data Input/<br>Output           | Multiplexed pins for data input and output.                                                                                                                                         |

| 18                                                                | CS            | Chip Select                     | Disable or enable the command decoder. When command decoder is disabled, new command is ignored and previous operation continues.                                                   |

| 17                                                                | RAS           | Row Address<br>Strobe           | Command input. When sampled at the rising edge of the clock, $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ and $\overline{\text{WE}}$ define the operation to be executed.      |

| 16                                                                | CAS           | Column<br>Address Strobe        | Referred to RAS                                                                                                                                                                     |

| 15                                                                | WE            | Write Enable                    | Referred to RAS                                                                                                                                                                     |

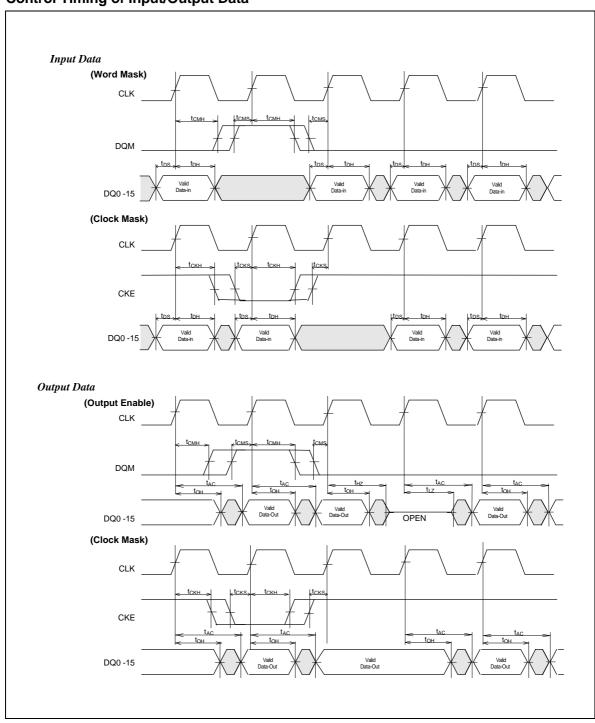

| 36, 14                                                            | UDQM/<br>LDQM | Input/Output<br>Mask            | The output buffer is placed at Hi-Z (with latency of 2) when DQM is sampled high in read cycle. In write cycle, sampling DQM high will block the write operation with zero latency. |

| 35                                                                | CLK           | Clock Inputs                    | System clock used to sample inputs on the rising edge of clock.                                                                                                                     |

| 34                                                                | CKE           | Clock Enable                    | CKE controls the clock activation and deactivation.<br>When CKE is low, Power Down mode, Suspend<br>mode, or Self Refresh mode is entered.                                          |

| 1, 25                                                             | Vcc           | Power (+3.3V)                   | Power for input buffers and logic circuit inside DRAM.                                                                                                                              |

| 26, 50                                                            | Vss           | Ground                          | Ground for input buffers and logic circuit inside DRAM.                                                                                                                             |

| 7, 13, 38, 44,                                                    | VccQ          | Power (+3.3V)<br>for I/O buffer | Separated power from VCC, used for output buffers to improve noise immunity.                                                                                                        |

| 4, 10, 41, 47                                                     | VssQ          | Ground for I/O buffer           | Separated ground from VSS, used for output buffers to improve noise immunity.                                                                                                       |

| 33, 37                                                            | NC            | No Connection                   | No connection                                                                                                                                                                       |

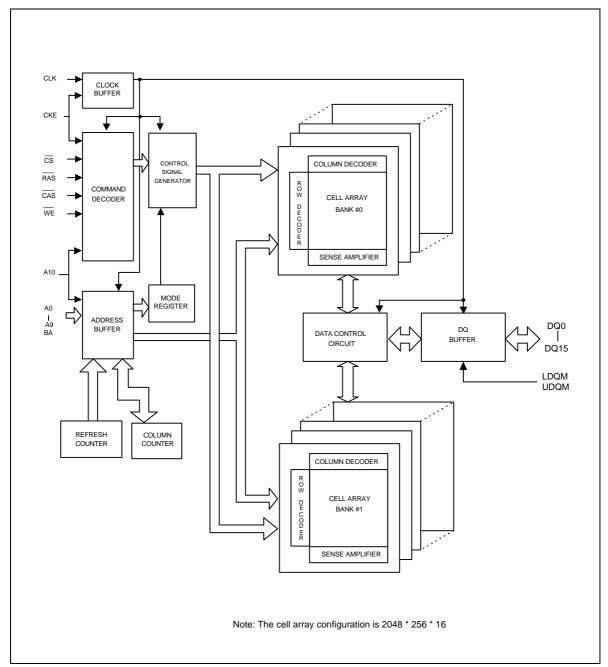

## **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

### **Power Up and Initialization**

The default power up state of the mode register is unspecified. The following power up and initialization sequence need to be followed to guarantee the device being preconditioned to each user specific needs during power up, all VCC and VCCQ pins must be ramp up simultaneously to the specified voltage when the input signals are held in the "NOP" state. The power up voltage must not exceed VCC +0.3V on any of the input pins or VCC supplies. After power up, an initial pause of 200  $\mu S$  is required followed by a precharge of all banks using the precharge command. To prevent data contention on the DQ bus during power up, it is required that the DQM and CKE pins be held high during the initial pause period. Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register. An additional eight Auto Refresh cycles (CBR) are also required before or after programming the Mode Register to ensure proper subsequent operation.

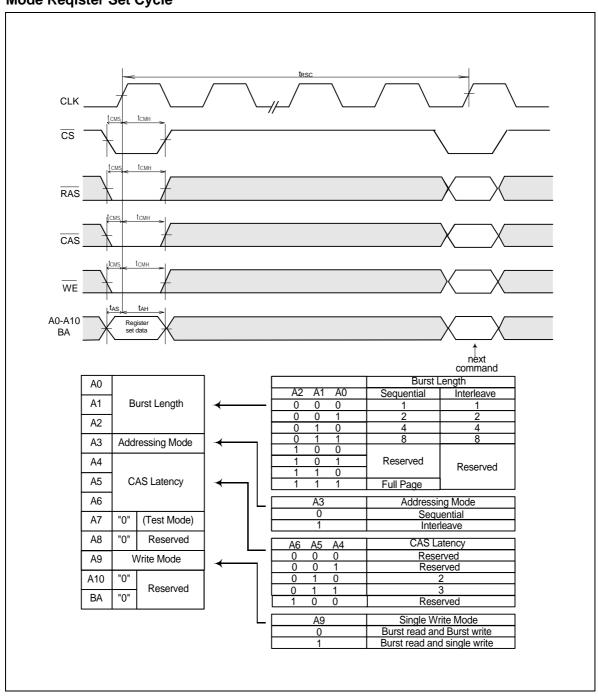

### **Programming Mode Register**

After initial power up, the Mode Register Set Command must be issued for proper device operation. All banks must be in a precharged state and CKE must be high at least one cycle before the Mode Register Set Command can be issued. The Mode Register Set Command is activated by the low signals of  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{CS}$  and  $\overline{WE}$  at the positive edge of the clock. The address input data during this cycle defines the parameters to be set as shown in the Mode Register Operation table. A new command may be issued following the mode register set command once a delay equal to  $t_{RSC}$  has elapsed. Please refer to the next page for Mode Register Set Cycle and Operation Table.

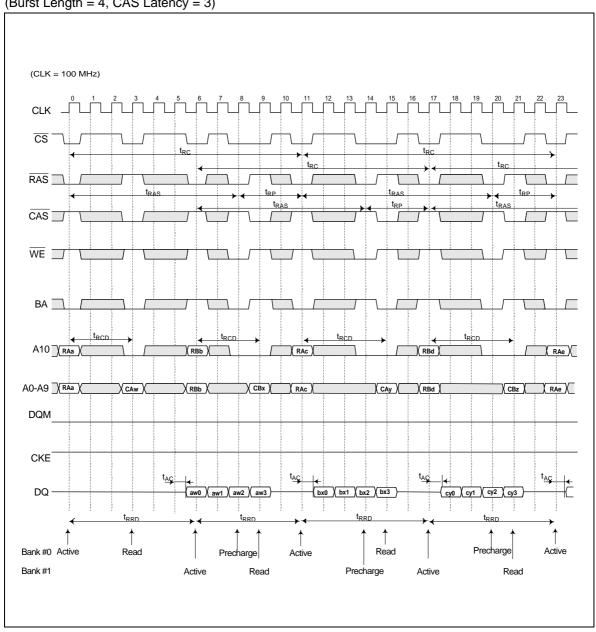

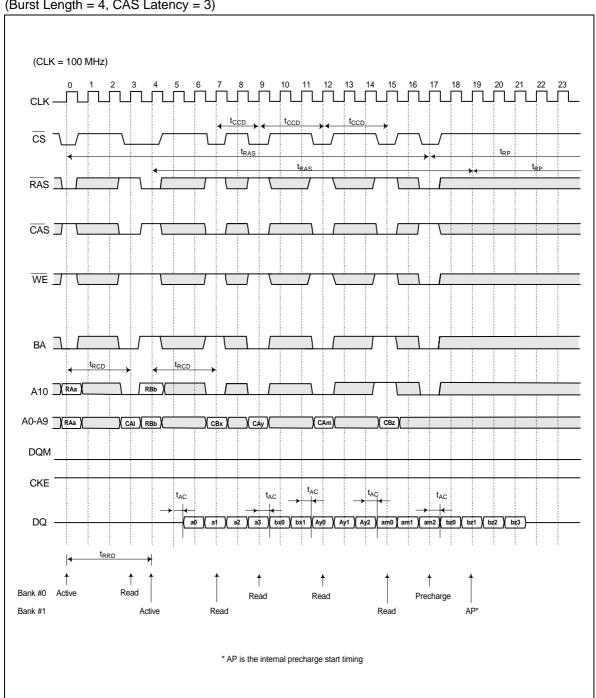

#### **Bank Activate Command**

The Bank Activate command must be applied before any Read or Write operation can be executed. The operation is similar to  $\overline{RAS}$  activate in EDO DRAM. The delay from when the Bank Activate command is applied to when the first read or write operation can begin must not be less than the RAS to CAS delay time (tro). Once a bank has been activated it must be precharged before another Bank Activate command can be issued to the same bank. The minimum time interval between successive Bank Activate commands to the same bank is determined by the RAS cycle time of the device (tro). The minimum time interval between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank-to-Bank delay time (tro). The maximum time that each bank can be held active is specified as tras(max.).

### **Read and Write Access Modes**

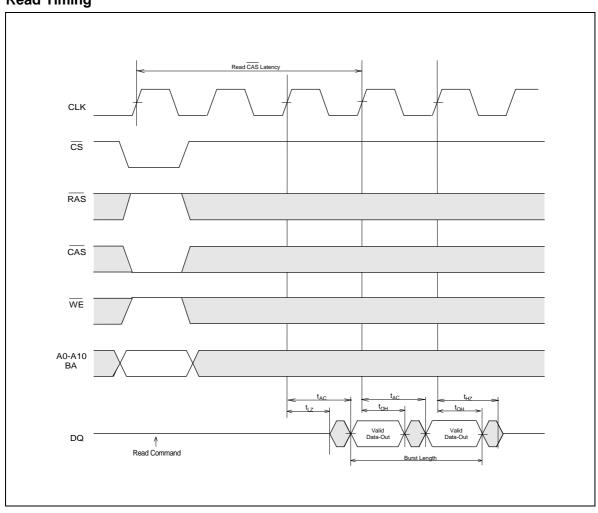

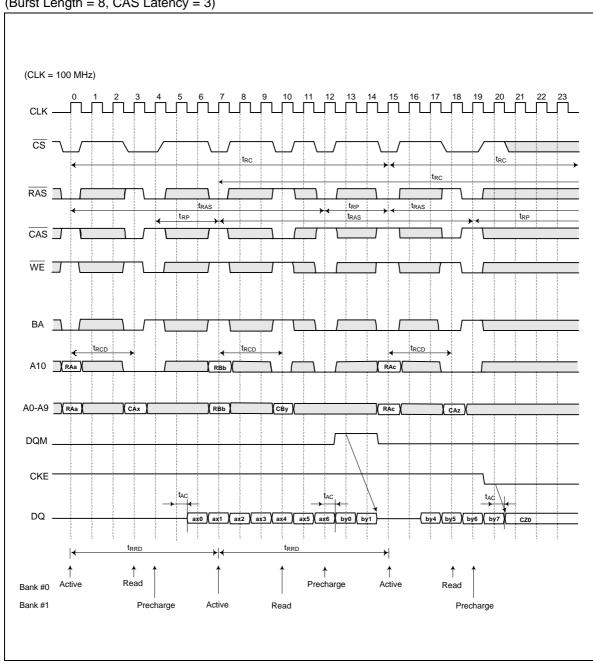

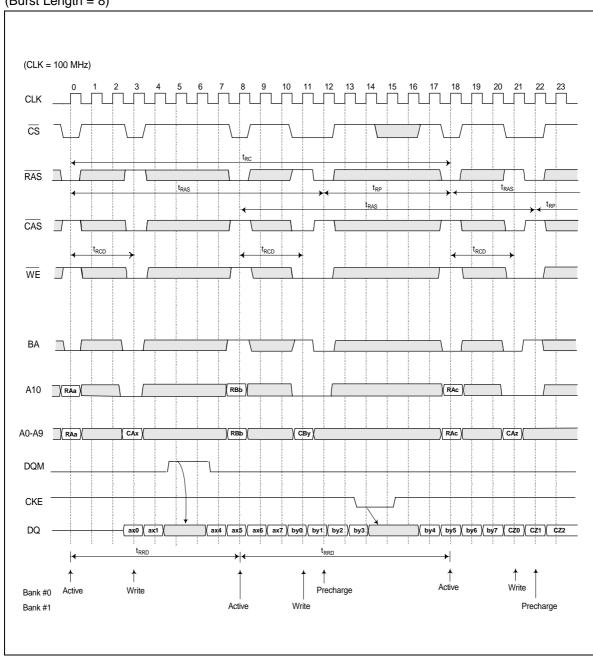

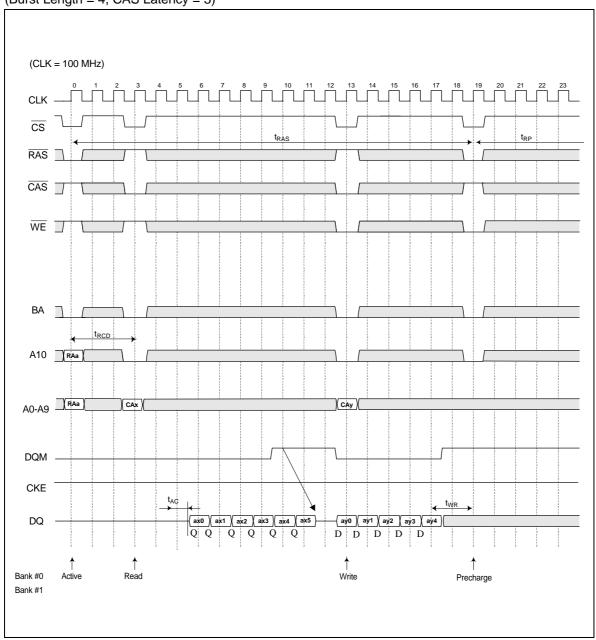

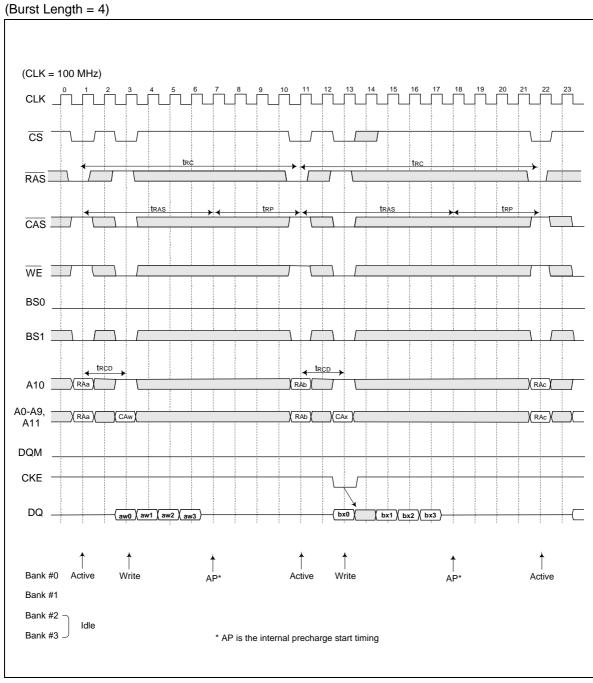

After a bank has been activated, a read or write cycle can be followed. This is accomplished by setting  $\overline{\text{RAS}}$  high and  $\overline{\text{CAS}}$  low at the clock rising edge after minimum of  $t_{\text{RCD}}$  delay.  $\overline{\text{WE}}$  pin voltage level defines whether the access cycle is a read operation ( $\overline{\text{WE}}$  high), or a write operation ( $\overline{\text{WE}}$  low). The address inputs determine the starting column address. Reading or writing to a different row within an activated bank requires the bank be precharged and a new Bank Activate command be issued. When more than one bank is activated, interleaved bank Read or Write operations are possible. By using the programmed burst length and alternating the access and precharge operations between multiple banks, seamless data access operation among many different pages can be realized. Read or Write Commands can also be issued to the same bank or between active banks on every clock cycle.

#### **Burst Read Command**

The Burst Read command is initiated by applying logic low level to  $\overline{\text{CS}}$  and  $\overline{\text{CAS}}$  while holding  $\overline{\text{RAS}}$  and  $\overline{\text{WE}}$  high at the rising edge of the clock. The address inputs determine the starting column address for the burst. The Mode Register sets type of burst (sequential or interleave) and the burst length (1, 2, 4, 8, full page) during the Mode Register Set Up cycle. Table 2 and 3 in the next page explain the address sequence of interleave mode and sequence mode.

#### **Burst Write Command**

The Burst Write command is initiated by applying logic low level to  $\overline{CS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  while holding  $\overline{RAS}$  high at the rising edge of the clock. The address inputs determine the starting column address. Data for the first burst write cycle must be applied on the DQ pins on the same clock cycle that the Write Command is issued. The remaining data inputs must be supplied on each subsequent rising clock edge until the burst length is completed. Data supplied to the DQ pins after burst finishes will be ignored.

### Read Interrupted by a Read

A Burst Read may be interrupted by another Read Command. When the previous burst is interrupted, the remaining addresses are overridden by the new read address with the full burst length. The data from the first Read Command continues to appear on the outputs until the CAS latency from the interrupting Read Command the is satisfied.

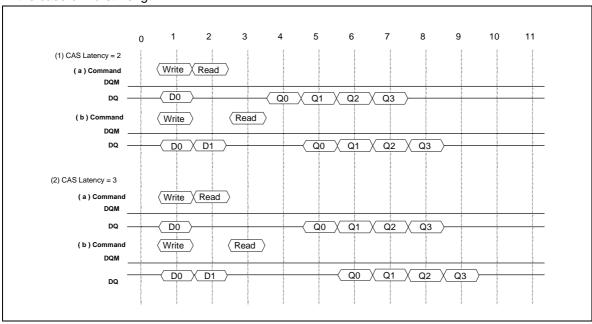

#### Read Interrupted by a Write

To interrupt a burst read with a Write Command, DQM may be needed to place the DQs (output drivers) in a high impedance state to avoid data contention on the DQ bus. If a Read Command will issue data on the first and second clocks cycles of the write operation, DQM is needed to insure the DQs are tri-stated. After that point the Write Command will have control of the DQ bus and DQM masking is no longer needed.

#### Write Interrupted by a Write

A burst write may be interrupted before completion of the burst by another Write Command. When the previous burst is interrupted, the remaining addresses are overridden by the new address and data will be written into the device until the programmed burst length is satisfied.

#### Write Interrupted by a Read

A Read Command will interrupt a burst write operation on the same clock cycle that the Read Command is activated. The DQs must be in the high impedance state at least one cycle before the new read data appears on the outputs to avoid data contention. When the Read Command is activated, any residual data from the burst write cycle will be ignored.

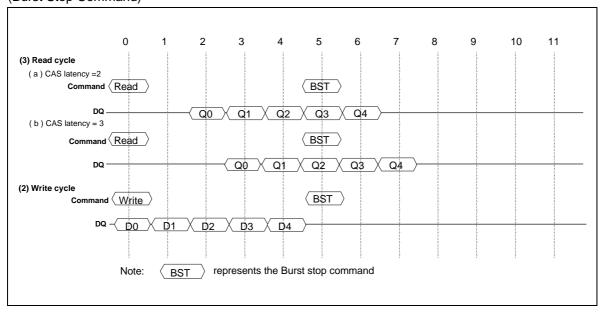

### **Burst Stop Command**

A Burst Stop Command may be used to terminate the existing burst operation but leave the bank open for future Read or Write Commands to the same page of the active bank, if the burst length is full page. Use of the Burst Stop Command during other burst length operations is illegal. The Burst

Publication Release Date: February 2000 Revision A2

Stop Command is defined by having  $\overline{RAS}$  and  $\overline{CAS}$  high with  $\overline{CS}$  and  $\overline{WE}$  low at the rising edge of the clock. The data DQs go to a high impedance state after a delay, which is equal to the  $\overline{CAS}$  Latency in a burst read cycle, interrupted by Burst Stop. If a Burst Stop Command is issued during a full page burst write operation, then any residual data from the burst write cycle will be ignored.

### **Addressing Sequence of Sequential Mode**

A column access is performed by increasing the address from the column address, which is input to the device. The disturb address is varied by the Burst Length as shown in Table 2.

DATA Access Address **Burst Length** Data 0 BL = 2 (disturb address is A0) n n + 1 Data 1 No address carry from A0 to A1 Data 2 n + 2BL = 4 (disturb addresses are A0 and A1) Data 3 No address carry from A1 to A2 n + 3Data 4 n + 4Data 5 n + 5 BL = 8 (disturb addresses are A0, A1 and A2) No address carry from A2 to A3 Data 6 n + 6Data 7 n + 7

**Table 2 Address Sequence of Sequential Mode**

### **Addressing Sequence of Interleave Mode**

A column access is started in the input column address and is performed by inverting the address bit in the sequence shown in Table 3.

|        | Tanada a ta |             |

|--------|----------------------------------------------------------------------------------------------------------------|-------------|

| DATA   | Access Address                                                                                                 | Bust Length |

| Data 0 | A8 A7 A6 A5 A4 A3 A2 A1 A0                                                                                     | BL = 2      |

| Data 1 | A8 A7 A6 A5 A4 A3 A2 A1 A0                                                                                     |             |

| Data 2 | A8 A7 A6 A5 A4 A3 A2 A1 A0                                                                                     | BL = 4      |

| Data 3 | A8 A7 A6 A5 A4 A3 A2 A1 A0                                                                                     |             |

| Data 4 | A8 A7 A6 A5 A4 A3 A2 A1 A0                                                                                     | BL = 8      |

| Data 5 | A8 A7 A6 A5 A4 A3 $\overline{\text{A2}}$ A1 $\overline{\text{A0}}$                                             |             |

| Data 6 | A8 A7 A6 A5 A4 A3 A2 A1 A0                                                                                     |             |

| Data 7 | A8 A7 A6 A5 A4 A3 A2 A1 A0                                                                                     | $\forall$   |

**Table 3 Address Sequence of Interleave Mode**

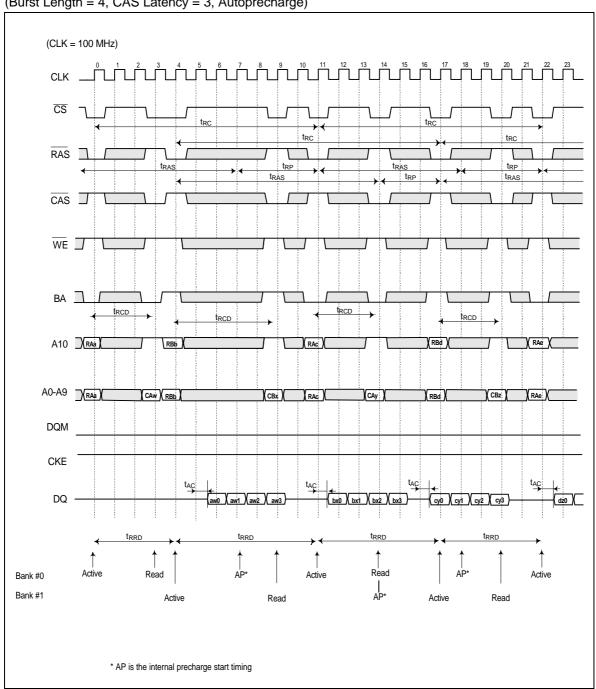

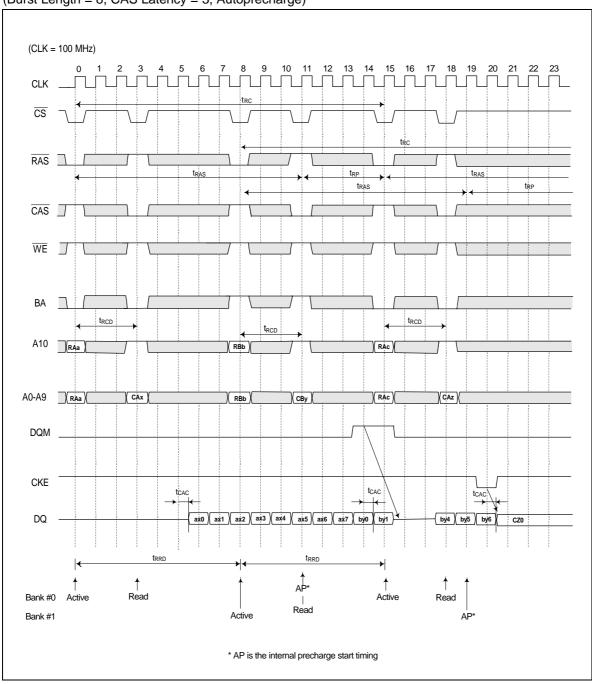

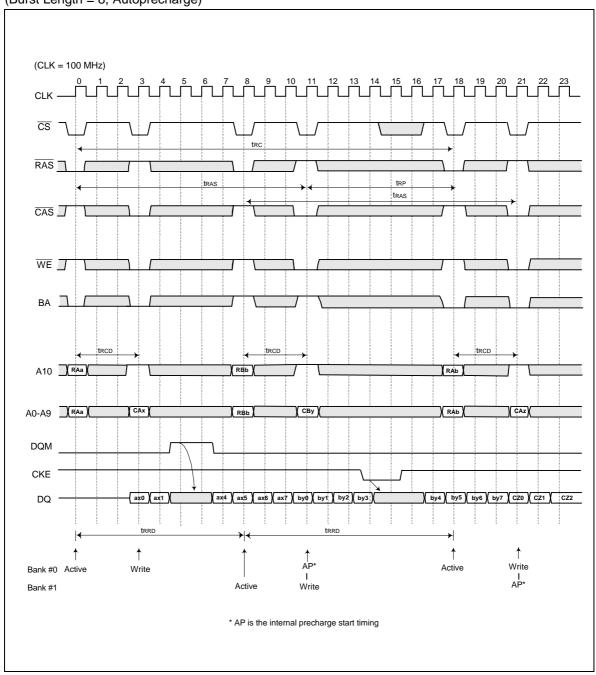

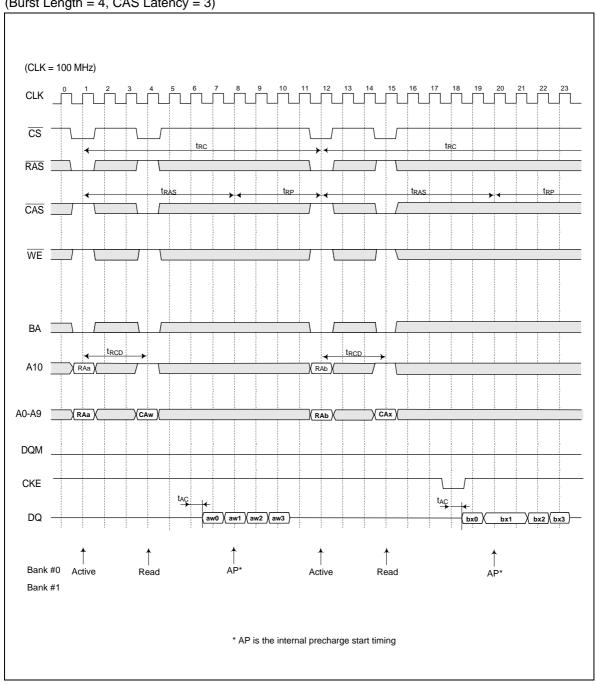

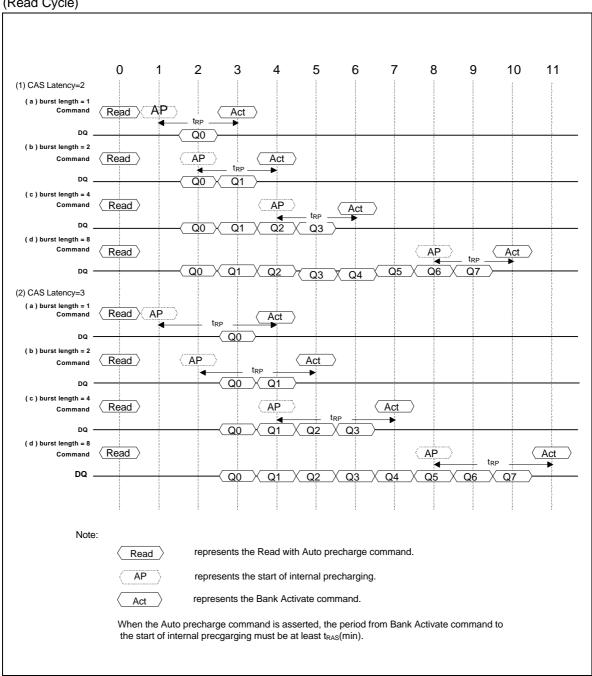

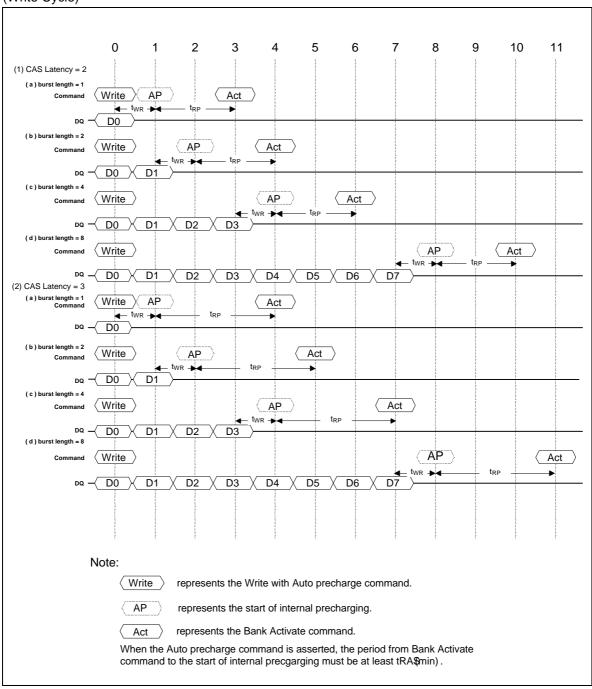

### **Auto-precharge Command**

If A10 is set to high when the Read or Write Command is issued, then the auto-precharge function is entered. During auto-precharge, a Read Command will execute as normal with the exception that the active bank will begin to precharge automatically before all burst read cycles have been completed. Regardless of burst length, it will begin a certain number of clocks prior to the end of the scheduled burst cycle. The number of clocks is determined by  $\overline{\text{CAS}}$  latency.

A Read or Write Command with auto-precharge can not be interrupted before the entire burst operation is completed. Therefore, use of a Read, Write, or Precharge Command is prohibited during a read or write cycle with auto-precharge. Once the precharge operation has started, the bank cannot be reactivated until the Precharge time ( $t_{RP}$ ) has been satisfied. Issue of Auto-Precharge command is illegal if the burst is set to full page length. If A10 is high when a Write Command is issued, the Write with Auto-Precharge function is initiated. The SDRAM automatically enters the precharge operation one clock delay from the last burst write cycle. This delay is referred to as Write  $t_{DPL}$ . The bank undergoing auto-precharge can not be reactivated until  $t_{DPL}$  and  $t_{RP}$  are satisfied. This is referred to as  $t_{DAL}$ , Data-in to Active delay ( $t_{DAL} = t_{DPL} + t_{RP}$ ). When using the Auto-precharge Command, the interval between the Bank Activate Command and the beginning of the internal precharge operation must satisfy  $t_{RAS}$ (min).

#### **Precharge Command**

The Precharge Command is used to precharge or close a bank that has been activated. The Precharge Command is entered when  $\overline{CS}$ ,  $\overline{RAS}$  and  $\overline{WE}$  are low and  $\overline{CAS}$  is high at the rising edge of the clock. The Precharge Command can be used to precharge each bank separately or all banks simultaneously. Three address bits, A10, and BA, are used to define which bank(s) is to be precharged when the command is issued. After the Precharge Command is issued, the precharged bank must be reactivated before a new read or write access can be executed. The delay between the Precharge Command and the Activate Command must be greater than or equal to the Precharge time ( $t_{RP}$ ).

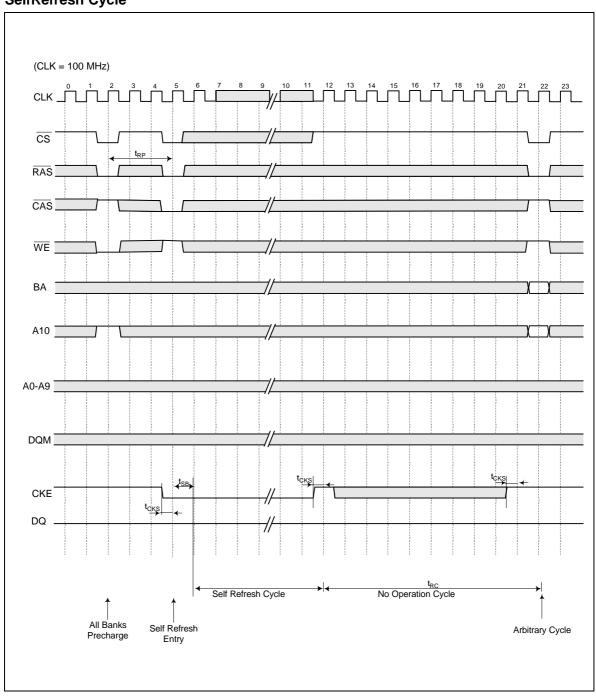

#### **Self Refresh Command**

The Self-Refresh Command is defined by having CS, RAS, CAS and CKE held low with WE high at the rising edge of the clock. All banks must be idle prior to issuing the Self-Refresh Command. Once the command is registered, CKE must be held low to keep the device in Self-Refresh mode. When the SDRAM has entered Self Refresh mode all of the external control signals, except CKE, are disabled. The clock is internally disabled during Self-Refresh Operation to save power. The device will exit Self-Refresh operation after CKE is returned high. Any subsequent commands can be issued after  $t_{\rm RC}$  from the end of Self Refresh command.

If, during normal operation, Auto-Refresh cycles are issued in bursts (as opposed to being evenly distributed), a burst of 4,096 Auto-Refresh cycles should be completed just prior to entering and just after exiting the Self-Refresh mode.

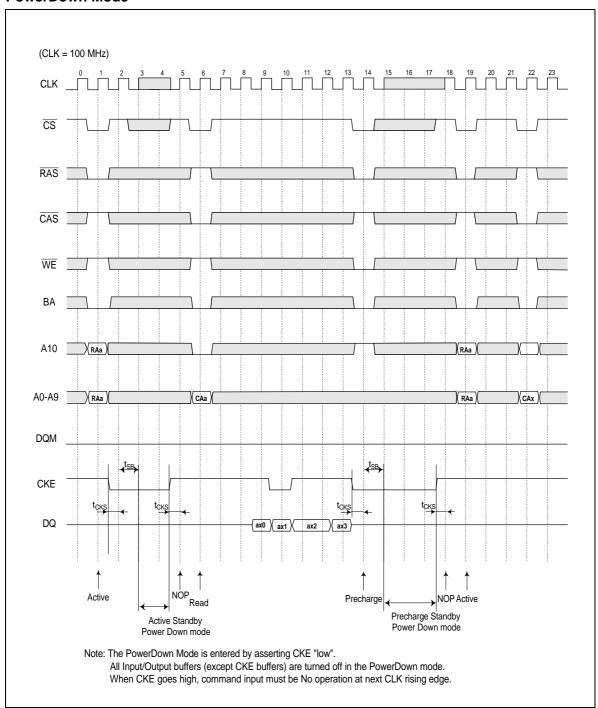

#### **Power Down Mode**

The Power Down mode is initiated by holding CKE low. All of the receiver circuits except CKE are gated off to reduce the power. The Power Down mode does not perform any refresh operations; therefore the device can not remain in Power Down mode longer than the Refresh period (tree) of the device.

Publication Release Date: February 2000 Revision A2

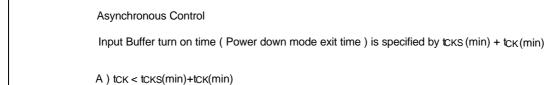

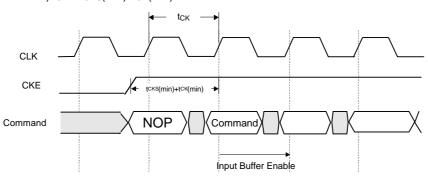

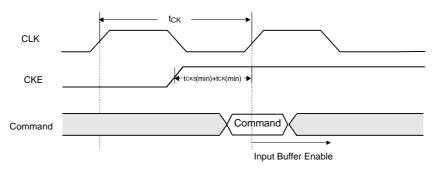

## W981616AH

The Power Down mode is exited by bringing CKE high. When CKE goes high, a No Operation Command is required on the next rising clock edge, depending on tck. The input buffers need to be enabled with CKE held high for a period equal to tces(min) + tck(min).

### **No Operation Command**

The No Operation Command should be used in cases when the SDRAM is in an idle or a wait state to prevent the SDRAM from registering any unwanted commands between operations. A No Operation Command is registered when  $\overline{\text{CS}}$  is low with  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ , and  $\overline{\text{WE}}$  held high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is still executing, such as a burst read or write cycle.

#### **Deselect Command**

The Deselect Command performs the same function as a No Operation Command. Deselect Command occurs when  $\overline{CS}$  is brought high, the  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  signals become don't cares.

#### **Clock Suspend Mode**

During normal access mode, CKE must be held high enabling the clock. When CKE is registered low while at least one of the banks is active, Clock Suspend Mode is entered. The Clock Suspend mode deactivates the internal clock and suspends any clocked operation that was currently being executed. There is a one-clock delay between the registration of CKE low and the time at which the SDRAM operation suspends. While in Clock Suspend mode, the SDRAM ignores any new commands that are issued. The Clock Suspend mode is exited by bringing CKE high. There is a one-clock cycle delay from when CKE returns high to when Clock Suspend mode is exited.

### **TABLE OF OPERATING MODES**

Fully synchronous operations are performed to latch the commands at the positive edges of CLK. Table 1 shows the truth table for the operation commands.

**TABLE 1 TRUTH TABLE (NOTE 1, 2)**

| Command                      | Device<br>State        | CKEn-1 | CKEn   | DQM    | ВА     | A10    | A9-0   | CS     | RAS    | CAS    | WE     |

|------------------------------|------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Bank Active                  | Idle                   | Н      | Х      | X      | V      | V      | V      | L      | L      | Н      | Н      |

| Bank Precharge               | Any                    | Н      | Х      | Х      | V      | L      | Х      | L      | L      | Н      | L      |

| Precharge All                | Any                    | Н      | Х      | Х      | Х      | Н      | Х      | L      | L      | Н      | L      |

| Write                        | Active (3)             | Н      | Х      | Х      | V      | L      | V      | L      | Н      | L      | L      |

| Write with<br>Autoprecharge  | Active (3)             | Н      | Х      | Х      | V      | Н      | V      | L      | Н      | L      | L      |

| Read                         | Active (3)             | Н      | X      | X      | V      | L      | V      | L      | Н      | L      | Н      |

| Read with<br>Autoprecharge   | Active (3)             | Н      | Х      | Х      | V      | Н      | V      | L      | Н      | L      | Н      |

| Mode Register Set            | Idle                   | Н      | X      | X      | V      | V      | V      | L      | L      | L      | L      |

| No-Operation                 | Any                    | Н      | Χ      | X      | Х      | Х      | Χ      | L      | Н      | Н      | Н      |

| Burst Stop                   | Active (4)             | Н      | Χ      | X      | Х      | Х      | Χ      | L      | Н      | Н      | L      |

| Device Deselect              | Any                    | Н      | Χ      | X      | Х      | Х      | Χ      | Н      | Х      | Х      | Χ      |

| Auto-Refresh                 | Idle                   | Н      | Н      | Х      | Х      | Х      | Χ      | L      | L      | L      | Н      |

| Self-Refresh Entry           | Idle                   | Н      | L      | Х      | Х      | Х      | Х      | L      | L      | L      | Н      |

| Self-Refresh Exit            | ldle<br>(S.R)          | L<br>L | H<br>H | X<br>X | X<br>X | X<br>X | X<br>X | H<br>L | X<br>H | X<br>H | X<br>X |

| Clock Suspend Mode<br>Entry  | Active                 | Н      | L      | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Power Down Mode<br>Entry     | Idle<br>Active (5)     | H<br>H | LL     | X<br>X | X      | X      | X      | ΗL     | X      | X<br>H | X      |

| Clock Suspend Mode<br>Exit   | Active                 | L      | Н      | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Power Down Mode Exit         | Any<br>(Power<br>down) | L<br>L | Η<br>Η | X      | X<br>X | X<br>X | X      | H      | X<br>H | X<br>H | X<br>X |

| Data Write/Output<br>Enable  | Active                 | Н      | Х      | L      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Data Write/Output<br>Disable | Active                 | Н      | Х      | Н      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

### Notes:

- (1) V = Valid, X = Don't care, L = Low Level, H = High Level

- (2) CKEn signal is input level when commands are provided.

- (3) These are state of bank designated by BA signals.

- (4) Device state is full page burst operation.

- (5) Power Down Mode can not be entered in the burst cycle.

When this command asserts in the burst cycle, device state is clock suspend mode.

Publication Release Date: February 2000 Revision A2

### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                    | SYMBOL    | RATING     | UNIT | NOTES |

|------------------------------|-----------|------------|------|-------|

| Input, Output Voltage        | VIN, VOUT | -0.3 – 4.6 | V    | 1     |

| Power Supply Voltage         | Vcc, VccQ | -0.3 – 4.6 | V    | 1     |

| Operating Temperature        | TOPR      | 0 – 70     | ۰C   | 1     |

| Storage Temperature          | Tstg      | -55 – 150  | °C   | 1     |

| Soldering Temperature (10s)  | TSOLDER   | 260        | °C   | 1     |

| Power Dissipation            | PD        | 1          | W    | 1     |

| Short Circuit Output Current | IOUT      | 50         | mA   | 1     |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

## RECOMMENDED DC OPERATING CONDITIONS

$(TA = 0 \text{ to } 70 \circ C)$

| PARAMETER                             | SYM. | MIN. | TYP. | MAX.     | UNIT | NOTES |

|---------------------------------------|------|------|------|----------|------|-------|

| Power Supply Voltage                  | Vcc  | 3.0  | 3.3  | 3.6      | ٧    | 2     |

| Power Supply Voltage (for I/O Buffer) | VccQ | 3.0  | 3.3  | 3.6      | V    | 2     |

| Input High Voltage                    | VIH  | 2.0  | -    | Vcc +0.3 | ٧    | 2     |

| Input Low Voltage                     | VIL  | -0.3 | -    | 0.8      | V    | 2     |

Note: VIH (max.) = Vcc/VccQ +1.2V for pulse width  $\leq$  5 nS VIL (min.) = Vss/VssQ -1.2V for pulse width  $\leq$  5 nS

### **CAPACITANCE**

(VCC = 3.3V, TA = 25 °C, f = 1MHz)

| PARAMETER                                                                                                                                                | SYM. | MIN. | MAX. | UNIT |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Input Capacitance (A0 to A10, BA, $\overline{\text{CS}}$ , $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ , $\overline{\text{WE}}$ , UDQM, LDQM, CKE) | СІ   | -    | 4    | pf   |

| Input Capacitance (CLK)                                                                                                                                  |      | -    | 4    | pf   |

| Input/Output capacitance (DQ0 to DQ15)                                                                                                                   | Cio  | -    | 6.5  | pf   |

Note: These parameters are periodically sampled and not 100% tested  $\,$

# **DC CHARACTERISTICS**

$(VCC = 3.3V \pm 0.3V, TA = 0 \circ \sim 70 \circ C)$

| PARAMETE                                                                                          | R                              | SYM.   | -6<br>MAX. | -7<br>MAX. | -8<br>MAX. | UNIT | NOTES |

|---------------------------------------------------------------------------------------------------|--------------------------------|--------|------------|------------|------------|------|-------|

| Operating Current tck = min., tRc = min. Active precharge command cycling without burst operation | 1 bank operation               | ICC1   | 100        | 90         | 80         | mA   | 3     |

| Standby Current  tck = min., CS = VIH  VIH /L = VIH (min.) /VIL (max.)  Bank: inactive state      | CKE = VIH                      | ICC2   | 50         | 45         | 40         |      | 3     |

|                                                                                                   | CKE = VIL<br>(Power down mode) | ICC2P  | 2          | 2          | 2          |      | 3     |

| Standby Current  CLK = VIL, CS = VIH  VIH/L = VIH (min.) /VIL (max.)  Bank: inactive state        | CKE = VIH                      | Icc2s  | 10         | 8          | 6          |      |       |

|                                                                                                   | CKE = VIL<br>(Power down mode) | ICC2PS | 2          | 2          | 2          |      |       |

| No Operating Current tck = min., $\overline{CS}$ = ViH (min.) Bank: active state (2 banks)        | CKE = VIH                      | ICC3   | 55         | 50         | 45         |      |       |

|                                                                                                   | CKE = VIL<br>(Power Down mode) | ICC3P  | 5          | 5          | 5          |      |       |

| Burst Operating Current Read/ Write command cycling                                               | (tck = min.)                   | ICC4   | 130        | 110        | 100        |      | 3, 4  |

| Auto Refresh Current Auto refresh command cycling                                                 | (tck = min.)                   | ICC5   | 90         | 80         | 70         |      | 3     |

| Self Refresh Current<br>Self refresh mode                                                         | (CKE = 0.2V)                   | ICC6   | 2          | 2          | 2          |      |       |

| PARAMETER                                                   | SYM.  | MIN. | MAX. | UNIT | NOTES |

|-------------------------------------------------------------|-------|------|------|------|-------|

| Input Leakage Current                                       | [I(L) | -5   | 5    | μΑ   |       |

| $(0V \le VIN \le VCC$ , all other pins not under test = 0V) |       |      |      |      |       |

| Output Leakage Current                                      | IO(L) | -5   | 5    | μΑ   |       |

| (Output disable , 0V ≤ Vo∪т ≤ VccQ )                        |       |      |      |      |       |

| LVTTL OutputT "H" Level Voltage                             | Vон   | 2.4  | -    | V    |       |

| (IOUT = -2 mA)                                              |       |      |      |      |       |

| LVTTL Output "L" Level Voltage                              | Vol   | -    | 0.4  | V    |       |

| (IOUT = 2 mA)                                               |       |      |      |      |       |

# W981616AH

# **AC CHARACTERISTICS**

(Vcc =  $3.3V \pm 0.3V$ , Vss = 0V, TA = 0 to 70 °C, Notes: 5, 6, 7, 8)

| PARAMETER                               |             | SYM. |      | -6     |      | -7     | -8   |        | UNIT  |

|-----------------------------------------|-------------|------|------|--------|------|--------|------|--------|-------|

|                                         |             |      | MIN. | MAX.   | MIN. | MAX.   | MIN. | MAX.   |       |

| Ref/Active to Ref/Active Comn           | nand Period | tRC  | 60   |        | 70   |        | 72   |        | nS    |

| Active to Precharge Command             | d Period    | tRAS | 42   | 100000 | 48   | 100000 | 48   | 100000 |       |

| Active to Read/Write Commar Time        | nd Delay    | tRCD | 18   |        | 20   |        | 20   |        |       |

| Read/Write(a) to Read/Write(b<br>Period | o)Command   | tCCD | 1    |        | 1    |        | 1    |        | Cycle |

| Precharge to Active(b) Comma            | and Period  | trp  | 18   |        | 20   |        | 20   |        | nS    |

| Active(a) to Active(b) Commar           | nd Period   | tRPD | 12   |        | 14   |        | 16   |        |       |

| Write Recovery Time                     | CL* = 2     | twr  | 10   |        | 10   |        | 10   |        |       |

|                                         | CL* = 3     |      | 6    |        | 7    |        | 8    |        |       |

| CLK Cycle Time                          | CL* = 2     | tcĸ  | 10   | 1000   | 10   | 1000   | 10   | 1000   |       |

|                                         | CL* = 3     |      | 6    | 1000   | 7    | 1000   | 8    | 1000   |       |

| CLK High Level Width                    |             | tCH  | 2.5  |        | 3    |        | 3    |        |       |

| CLK Low Level Width                     |             | tcL  | 2.5  |        | 3    |        | 3    |        |       |

| Access Time from CLK                    | CL* = 2     | tAC  |      | 7      |      | 7      |      | 7      |       |

|                                         | CL* = 3     |      |      | 5.5    |      | 5.5    |      | 6      |       |

| Output Data Hold Time                   |             | tон  | 2    |        | 2.5  |        | 3    |        |       |

| Output Data High Impedance              | Time        | tHZ  | 2    | 6      | 2.5  | 7      | 3    | 8      |       |

| Output Data Low Impedance               | Гіте        | tLZ  | 0    |        | 0    |        | 0    |        |       |

| Power Down Mode Entry Time              | )           | tsB  | 0    | 6      | 0    | 7      | 0    | 8      |       |

| Transition Time of CLK (Rise            | and Fall)   | t⊤   | 0.3  | 10     | 0.3  | 10     | 0.3  | 10     |       |

| Data-in-Set-up Time                     |             | tos  | 1.5  |        | 2    |        | 2    |        |       |

| Data-in Hold Time                       |             | tDH  | 1    |        | 1    |        | 1    |        |       |

| Address Set-up Time                     |             | tAS  | 1.5  |        | 2    |        | 2    |        |       |

| Address Hold Time                       |             | tah  | 1    |        | 1    |        | 1    |        |       |

| CKE Set-up Time                         |             | tcks | 1.5  |        | 2    |        | 2    |        |       |

| CKE Hold Time                           |             | tckh | 1    |        | 1    |        | 1    |        |       |

| Command Set-up Time                     |             | tcms | 1.5  |        | 2    |        | 2    |        |       |

| Command Hold Time                       |             | tCMH | 1    |        | 1    |        | 1    |        |       |

| Refresh Time                            |             | tREF |      | 64     |      | 64     |      | 64     | mS    |

| Mode Register Set Cycle Time            | )           | trsc | 12   |        | 14   |        | 16   |        | nS    |

#### Notes:

- Operation exceeds "ABSOLUTE MAXIMUM RATING" may cause permanent damage to the devices.

- 2. All voltages are referenced to VSS

- 3. These parameters depend on the cycle rate and listed values are measured at a cycle rate with the minimum values of tCK and tRC.

- 4. These parameters depend on the output loading conditions. Specified values are obtained with output open.

- 5. Power up sequence is further described in the "Functional Description" section.

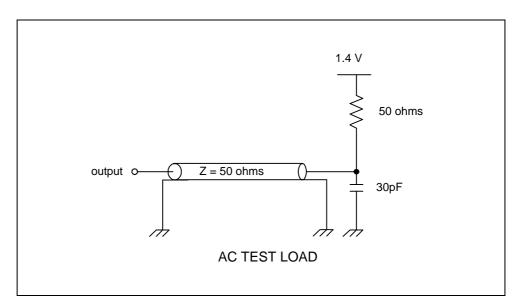

- 6. AC test conditions.

| PARAMETER                                       | CONDITIONS        |

|-------------------------------------------------|-------------------|

| Output Reference Level                          | 1.4V/1.4V         |

| Output Load                                     | See diagram below |

| Input Signal Levels                             | 2.4V/0.4V         |

| Transition Time (Rise and Fall) of Input Signal | 2 nS              |

| Input Reference Level                           | 1.4V              |

- 7. Transition times are measured between VIH and VIL.

- 8. tHZ defines the time at which the outputs achieve the open circuit condition and is not referenced to output level.

# **TIMING WAVEFORMS**

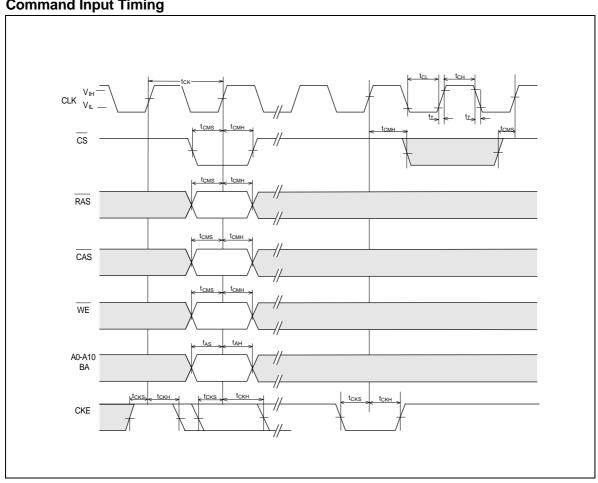

# **Command Input Timing**

# W981616AH

# **Read Timing**

# **Control Timing of Input/Output Data**

# W981616AH

## **Mode Register Set Cycle**

(Burst Length = 4, CAS Latency = 3, Autoprecharge)

(Burst Length = 8, CAS Latency = 3, Autoprecharge)

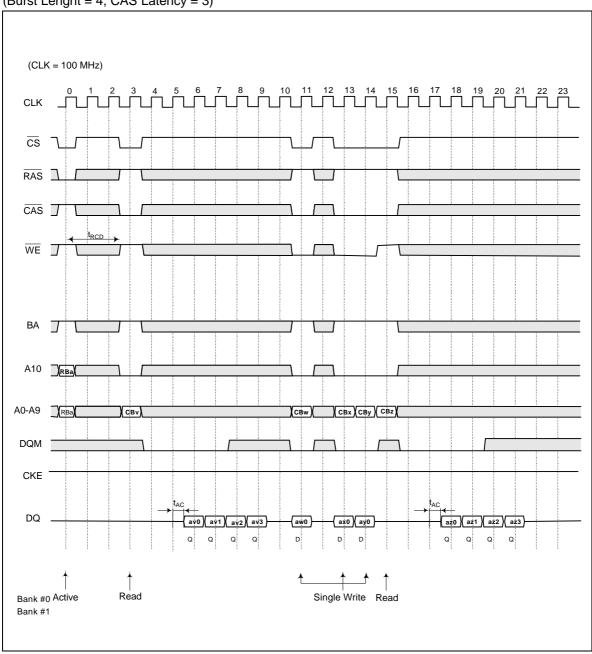

### **Interleaved Bank Write**

(Burst Length = 8)

### **Interleaved Bank Write**

(Burst Length = 8, Autoprecharge)

# Page Mode Read

# Page Mode Read/Write

## **AutoPrecharge Read**

## **AutoPrecharge Write**

# W981616AH

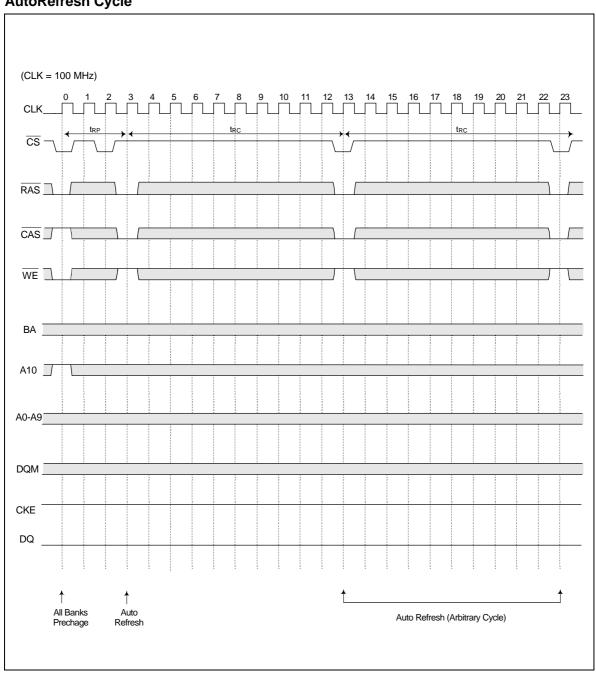

## **AutoRefresh Cycle**

# W981616AH

# SelfRefresh Cycle

# **Bust Read and Single Write**

### **PowerDown Mode**

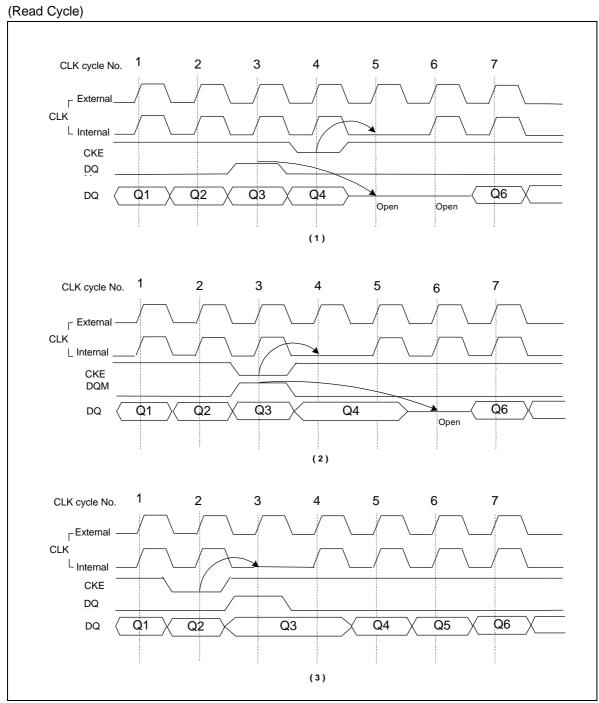

### **Autoprecharge Timing**

(Read Cycle)

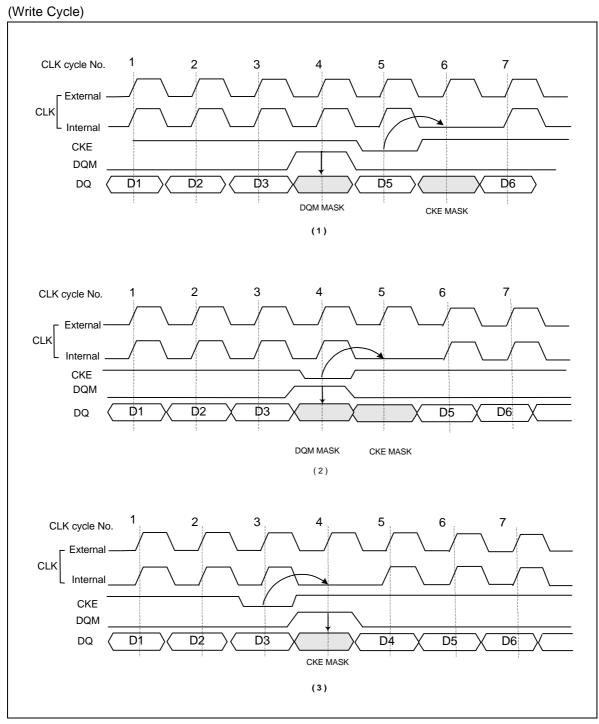

### **Autoprecharge Timing**

(Write Cycle)

# **Timing Chart of Write-to-Read Cycle**

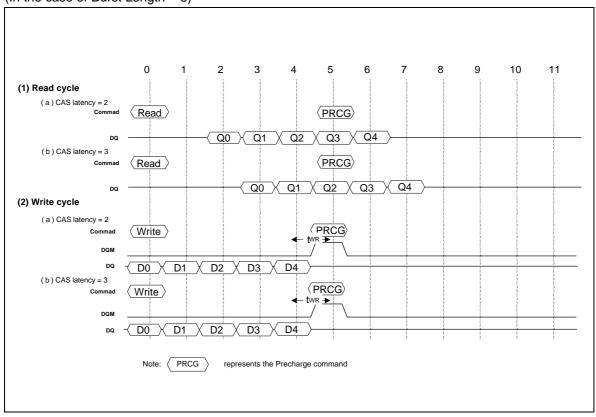

In the case of Burst Length = 4

## **Timing Chart of Burst Stop Cycle**

(Burst Stop Command)

# **Timing Chart of Burst Stop Cycle (Prechare Command)**

(In the case of Burst Length = 8)

# **CK/DQM Input Timing**

# **CK/DQM Input Timing**

## Self Refresh/Power Down Mode Exit Timing

B) tck >= tcks(min) + tck (min)

Note:

All Input Buffer(Include CLK Buffer) are turned off in the Power Down mode and Self Refresh mode

NOP Represents the No-Operation command Represents one command

### **PACKAGE DIMENSIONS**

# 50L-TSOP (II) 400 mill

### Headquarters

No. 4, Creation Rd. III, Science-Based Industrial Park, Hsinchu, Taiwan TEL: 886-3-5770066 FAX: 886-3-5796096

http://www.winbond.com.tw/ Voice & Fax-on-demand: 886-2-27197006

**Taipei Office**

11F, No. 115, Sec. 3, Min-Sheng East Rd., Taipei, Taiwan

TEL: 886-2-27190505

FAX: 886-2-27197502

Winbond Electronics (H.K.) Ltd.

Rm. 803, World Trade Square, Tower II, 123 Hoi Bun Rd., Kwun Tong, Kowloon, Hong Kong TEL: 852-27513100 FAX: 852-27552064

Winbond Electronics North America Corp. Winbond Memory Lab. Winbond Microelectronics Corp. Winbond Systems Lab. 2727 N. First Street, San Jose, CA 95134, U.S.A.

TEL: 408-9436666 FAX: 408-5441798

Note: All data and specifications are subject to change without notice.