# **AVS System Controller**

Check for Samples: LM10000

## **FEATURES**

- Flexible Enable Inputs to Allow Independent Enable Control of External Controller and LM10000

- Fault Input Restores Output Voltage Setting to Default Value

- CNTL\_EN Output That Enables/Disables External Controller

- 7-Bit Current DAC That Can Directly Connect to the Feedback Node of an External Controller and Provide Smooth Voltage Control

- Programmable Slew Rate Control

# **APPLICATIONS**

AVS-Enabled ASICs and FPGAs

## **KEY SPECIFICATIONS**

- PWI 2.0 Interface

- AVS Control for One Output

- Precision Enable

### DESCRIPTION

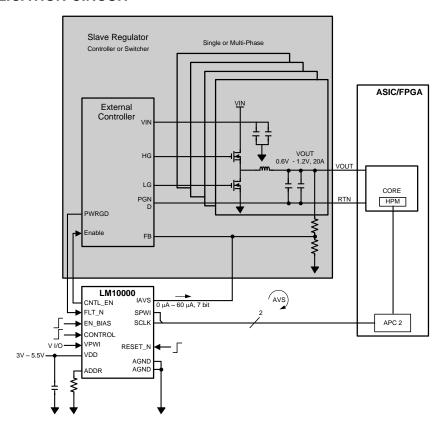

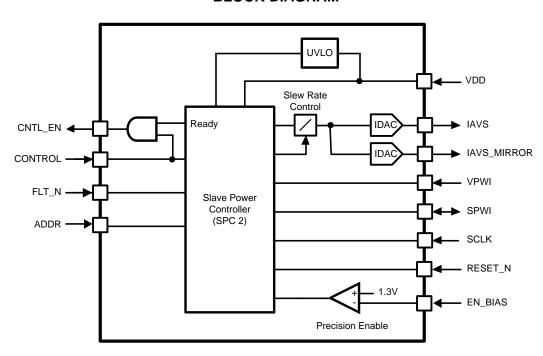

The LM10000 is used to enable Adaptive Voltage Scaling (AVS) to non-AVS regulators. It includes a complete Slave Power Controller (SPC 2.0) to communicate to the PowerWise™ Interface (PWI 2.0), and a programmable current output DAC that allows voltage control to any regulator utilizing a feedback node/resistors to set the output voltage.

In addition to enabling AVS the LM10000 allows the system to control power states such as sleep and shutdown, and to configure the voltage step slew rate from the PWI.

#### TYPICAL APPLICATION CIRCUIT

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerWise is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

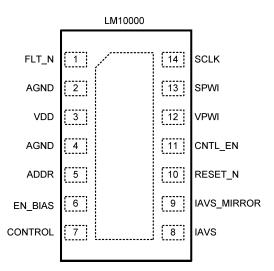

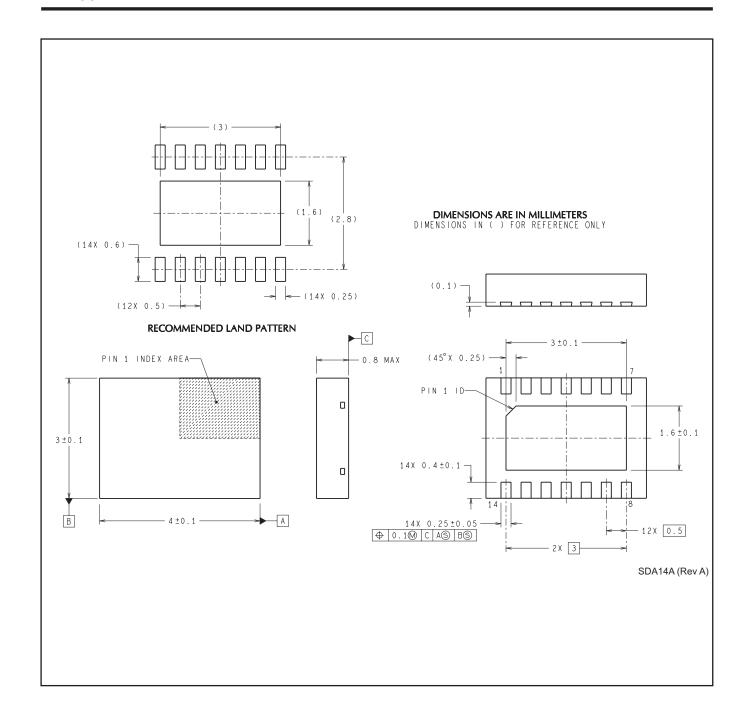

## **CONNECTION DIAGRAM**

Figure 1. 14-Lead Plastic WSON

# **PIN DESCRIPTIONS**

| Pin No. | Pad Name    | Туре   | Pad Description                                                                 |

|---------|-------------|--------|---------------------------------------------------------------------------------|

| 1       | FLT_N       | Input  | External fault input. Usually connected to PWGD output of integrated regulator. |

| 2       | AGND        | GND    |                                                                                 |

| 3       | VDD         | Power  | Analog Bias power input.                                                        |

| 4       | AGND        | GND    |                                                                                 |

| 5       | ADDR        | Input  | PWI address selection                                                           |

| 6       | EN_BIAS     | Input  | Enable input.                                                                   |

| 7       | CONTROL     | Input  | V <sub>OUT</sub> control input from system. Logic level.                        |

| 8       | IAVS        | Output | Current DAC output that connects to feedback node of integrated regulator       |

| 9       | IAVS_MIRROR | Output | Current DAC output that mirrors IAVS output current                             |

| 10      | RESET_N     | Input  | Reset, active low.                                                              |

| 11      | CNTL_EN     | Output | Enable signal that connects to integrated regulator                             |

| 12      | VPWI        | Power  | PWI IO bias power                                                               |

| 13      | SPWI        | I/O    | PWI Data                                                                        |

| 14      | SCLK        | Input  | PWI Clock                                                                       |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# ABSOLUTE MAXIMUM RATINGS (1) (2)(3)

| VPWI to GND                                                   | -0.2V to VDD    |      |  |

|---------------------------------------------------------------|-----------------|------|--|

| FLT_N, VDD, ADR, EN_BIAS, CONTROL, IA'VPWI, SPWI, SCLK to GND | -0.2V to 6V     |      |  |

| Junction Temperature                                          | −45°C to +125°C |      |  |

| Storage Temperature                                           | −45°C to +150°C |      |  |

| Soldering Information: See http://www.ti.com/l                | it/SNOA549      |      |  |

| ESD Ratings <sup>(4)</sup>                                    | 2kV             |      |  |

|                                                               | Machine Model   | 200V |  |

|                                                               |                 |      |  |

- (1) Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions for which the device operates correctly. Operating Ratings do not imply ensured performance limits.

- (2) The power MOSFETs can run on a separate 1V to 14V rail (Input voltage, V<sub>IN</sub>). Practical lower limit of V<sub>IN</sub> depends on selection of the external MOSFET. See the MOSFET GATE DRIVERS section under Application Information for further details.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (4) ESD using the human body model which is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin.

# OPERATING RATINGS (1) (2)

| VDD                 | 3.0V to 5.5V |

|---------------------|--------------|

| VPWI <sup>(3)</sup> | 1.6V to 3.6V |

- (1) Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions for which the device operates correctly. Operating Ratings do not imply ensured performance limits.

- (2) The power MOSFETs can run on a separate 1V to 14V rail (Input voltage, V<sub>IN</sub>). Practical lower limit of V<sub>IN</sub> depends on selection of the external MOSFET. See the MOSFET GATE DRIVERS section under Application Information for further details.

- (3) VPWI cannot be higher than VDD.

# THERMAL PROPERTIES

| Junction-to-Ambient thermal resistance | 54.7°C |

|----------------------------------------|--------|

|                                        |        |

## **ELECTRICAL CHARACTERISTICS**

Limits appearing in standard type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface** type apply over full operating junction temperature range ( $-40^{\circ}C \le T_J \le +125^{\circ}C$ . Unless otherwise noted, specifications apply to the LM10000 Typical Application Circuit (pg. 2) with:  $V_{DD} = 5.0V$ ,  $C_{IN} = 1\mu F$ .

| Symbol            | Parameter                  | Conditions                                | Min                    | Тур   | Max  | Units    |

|-------------------|----------------------------|-------------------------------------------|------------------------|-------|------|----------|

|                   |                            | EN_BIAS = 0V, CONTROL = 0V                |                        | 1.5   | 10   |          |

| I <sub>q</sub>    | Quiescent Current          | EN_BIAS = VDD, CONTROL = VDD<br>R0 = 0x7F |                        | 315   | 410  | μА       |

| 4                 |                            | EN_BIAS = VDD, PWI Sleep Command          |                        | 196   | 300  | <b>I</b> |

|                   |                            | EN_BIAS = VDD, PWI Shutdown Command       | VI Shutdown Command 23 |       | 75   |          |

|                   | Rising Threshold           |                                           |                        | 2.65  | 2.75 | .,       |

| UVLO              | Falling Threshold          |                                           | 2.27                   | 2.40  |      | V        |

|                   | Hysteresis                 |                                           |                        | 257   |      | mV       |

| I <sub>ADDR</sub> | Address pin source current |                                           |                        | 7.5   |      | μΑ       |

| IDAC              |                            |                                           |                        |       |      |          |

| ACC               | Accuracy                   | Measured at full scale                    | -3                     |       | 3    | %        |

| LSB               | DAC Step Size              | $I_{DAC-MAX} / 2^n (1 \le n \le 7)$       |                        | 470   |      | nA       |

|                   | Resolution                 |                                           | 7                      |       |      | Bits     |

| FS                | Full Scale                 |                                           |                        | 59.69 |      | μΑ       |

| INL               | Integral Non-Linearity     |                                           | -2                     |       | 2    | LSB      |

| DNL               | Differential Non-Linearity |                                           | -0.5                   |       | 0.5  | LSB      |

# **ELECTRICAL CHARACTERISTICS (continued)**

Limits appearing in standard type apply for  $T_J = 25^{\circ}\text{C}$ . Limits appearing in **boldface** type apply over full operating junction temperature range ( $-40^{\circ}\text{C} \le T_J \le +125^{\circ}\text{C}$ . Unless otherwise noted, specifications apply to the LM10000 Typical Application Circuit (pg. 2) with:  $V_{DD} = 5.0V$ ,  $C_{IN} = 1\mu\text{F}$ .

| Symbol                | Parameter                    | Conditions                            | Min           | Тур              | Max | Units         |  |

|-----------------------|------------------------------|---------------------------------------|---------------|------------------|-----|---------------|--|

| ZE                    | Zero Code Error/Offset Error |                                       |               | 57               |     | nA            |  |

| LOGIC AND             | CONTROL INPUTS               |                                       |               |                  |     |               |  |

| EN DIAC               | Duration analysis throughold | Rising                                |               | 1.32             | 1.4 | V             |  |

| EN_BIAS <sub>TH</sub> | Precision enable threshold   | Falling                               | 1.09          | <b>1.09</b> 1.19 |     | V             |  |

|                       |                              | FLT_N, RESET_N                        | -10           |                  |     |               |  |

| $I_{\rm IL}$          | Input Current Low            | ENBIAS, CONTROL                       | -1            |                  |     | μA            |  |

|                       |                              | SPWI, SCLK                            | -1            |                  |     |               |  |

|                       |                              | FLT_N, RESET_N                        |               |                  | 1   | μA            |  |

| I <sub>IH</sub>       | Input Current High           | ENBIAS, CONTROL                       |               |                  | 10  |               |  |

|                       |                              | SPWI, SCLK                            |               |                  | 5   |               |  |

| $V_{IL}$              | Input Low Voltage            | CONTROL, FLT_N, RESET_N               |               |                  | 0.5 | V             |  |

| V <sub>IH</sub>       | Input High Voltage           | CONTROL, FLT_N, RESET_N               | 1.1           |                  |     | V             |  |

| V <sub>IL_PWI</sub>   | Input Low Voltage, PWI       | SPWI, SCLK, 1.6 < VPWI < 3.6          |               |                  | 30  | 0/ -f \/D\//I |  |

| V <sub>IH_PWI</sub>   | Input High Voltage, PWI      | SPWI, SCLK, 1.6 < VPWI < 3.6          | 70            |                  |     | % of VPWI     |  |

| f <sub>SCLK</sub>     | PWI2 SCLK                    | **DC useful for testing/debug         | 0             |                  | 15M | Hz            |  |

| LOGIC AND             | CONTROL OUTPUTS              |                                       |               |                  |     |               |  |

| V <sub>OL</sub>       | Output Low Level             | CNTL_EN, I <sub>SINK</sub> ≤ 100 µA   |               |                  | 0.4 |               |  |

| V <sub>OH</sub>       | Output High Level            | CNTL_EN, I <sub>SOURCE</sub> ≤ 100 μA | VDD -<br>0.4  |                  |     | V             |  |

| V <sub>OH_PWI</sub>   | Output High Level, PWI       | SPWI, I <sub>SOURCE</sub> ≤ 1mA       | VPWI -<br>0.4 |                  |     |               |  |

Submit Documentation Feedback

# **BLOCK DIAGRAM**

# TYPICAL PERFORMANCE CHARACTERISTICS

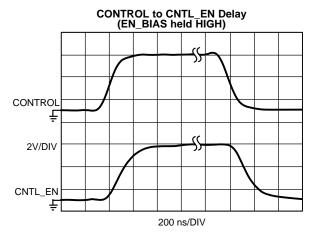

Figure 2.

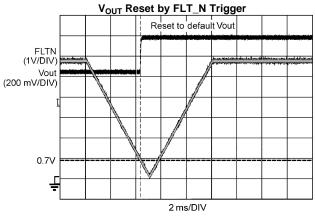

Figure 3.

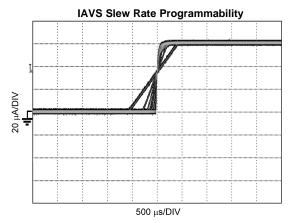

Figure 4.

Figure 5.

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

#### **LM10000 PWI REGISTER MAP**

The PWI 2.0 standard defines 32 8-bit base registers, and up to 256 8-bit extended registers, on each PWI slave. The table below summarizes these registers and shows default register bit values after reset, as programmed by the factory. The following sub-sections provide additional details on the use of each individual register.

Table 1. SUMMARY<sup>(1)</sup>

|          | Base Registers |                          |     |           |                   |           |                     |             |    |   |       |

|----------|----------------|--------------------------|-----|-----------|-------------------|-----------|---------------------|-------------|----|---|-------|

| Register |                |                          |     |           |                   | Reset Def | Reset Default Value |             |    |   |       |

| Address  | Name           |                          | е   | 7         | 6                 | 5         | 4                   | 3           | 2  | 1 | 0     |

| 0x00     | R0             | IAVS                     | R/W | 0*        |                   |           | Со                  | nfigured by | R9 |   |       |

| 0x03     | R3             |                          | R/O | 0         | 0                 | 0         | 0                   | 1           | 1  | 1 | FLT_N |

| 0x04     | R4             | Device Capability        | R/O | 0         | 0                 | 0         | 0                   | 0           | 0  | 1 | 0     |

| 0x09     | R9             | IAVS Default             | R/W | IAVS Defa | IAVS Default Code |           |                     |             |    |   |       |

| 0x0A     | R10            | Ramp Control             | R/W | 1         | 0                 | 0         | 1                   | 1           | 1  | 0 | 0     |

| 0x0F     | R15            | Revision ID              | N/A | 0         | 0                 | 0         | 0                   | 0           | 0  | 0 | 0     |

| 0x1F     | R31            | Reserved Do not write to | R/W | -         | -                 | -         | -                   | -           | -  | - | -     |

(1) A bit with an asterisk (\*) denotes a register bit that is always read as a fixed value. Writes to these bits will be ignored. A bit with a hyphen (-) denotes a bit in an unimplemented register location. A write into unimplemented register(s) will be ignored. A read of an unimplemented register(s) will produce a "No response frame". Please refer to PWI specification version 2.0 for further information.

| R0 - IAVS<br>AVS FEEDBACK CURRENT INJECTION |       |  |  |  |

|---------------------------------------------|-------|--|--|--|

| Address                                     | 0x00  |  |  |  |

| Туре                                        | R/W   |  |  |  |

| Reset Default                               | 8h'7F |  |  |  |

| Bit | Field Name            | Description                                                                                                                                           | Description or Comment |  |  |  |

|-----|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|

| 7   | Sign                  | This bit is fixed to '0'. Reading this bit will result in a '0'. Any data written into this bit position using the Register Write command is ignored. |                        |  |  |  |

|     |                       | Programmed voltage value. Default value is in <b>bold.</b>                                                                                            |                        |  |  |  |

|     |                       | Current Data Code [6:0]                                                                                                                               | Current (μA)           |  |  |  |

| 6:0 | IAVS Sourcing Current | 7h'00                                                                                                                                                 | 60                     |  |  |  |

|     |                       | 7h'xx                                                                                                                                                 | Linear Scaling         |  |  |  |

|     |                       | 7h'7F                                                                                                                                                 | 0 (default)            |  |  |  |

| R3 - STATUS<br>LM10520 ADDRESS |      |

|--------------------------------|------|

| Address                        | 0x03 |

| Туре                           | R/O  |

| Reset Default                  | -    |

| Bit | Field Name | Description or Comment                              |

|-----|------------|-----------------------------------------------------|

| 7:4 | Not Used   | Always read back 0                                  |

| 3:1 | Not Used   | Always read back 1                                  |

| 0   | FLT_N      | 1: FLT_N is high (no fault) 0: FLT_N is low (fault) |

| R4 - DEVICE CAPABILITY REGISTER |       |  |  |  |

|---------------------------------|-------|--|--|--|

| Address                         | 0x04  |  |  |  |

| Type                            | R/O   |  |  |  |

| Reset Default                   | 8h'02 |  |  |  |

| Bit | Field Name | Description or Comment                   |

|-----|------------|------------------------------------------|

| 7:3 |            | Always read back 0                       |

| 2:0 |            | Always read back 010, specifying PWI 2.0 |

| R9 - IAVS DEFAULT REGISTER |       |  |  |  |  |

|----------------------------|-------|--|--|--|--|

| Address 0x09               |       |  |  |  |  |

| Туре                       | R/W   |  |  |  |  |

| Reset Default              | 8h'7F |  |  |  |  |

| Bit | Field Name       | Description or Comment  |                   |  |  |  |  |  |  |

|-----|------------------|-------------------------|-------------------|--|--|--|--|--|--|

| 7   | Sign             | Always read back 0.     | ways read back 0. |  |  |  |  |  |  |

|     | 6:0 IAVS Default | Current Data Code [6:0] | Current (µA)      |  |  |  |  |  |  |

| 6.0 |                  | 7h'00                   | 60                |  |  |  |  |  |  |

| 6.0 |                  | 7h'xx                   | Linear Scaling    |  |  |  |  |  |  |

|     |                  | 7h'7F                   | 0 (Default)       |  |  |  |  |  |  |

| R10 - RAMP CONTROL |       |  |  |  |  |

|--------------------|-------|--|--|--|--|

| Address            | 0x0A  |  |  |  |  |

| Туре               | R/W   |  |  |  |  |

| Reset Default      | 8h'9C |  |  |  |  |

| Bit | Field Name             |                                 | Des                             | cription or Com                  | ment                                   |                                      |  |  |  |

|-----|------------------------|---------------------------------|---------------------------------|----------------------------------|----------------------------------------|--------------------------------------|--|--|--|

| 7   | Ramp Control Enable    | 1: Enabled<br>0: Disabled       |                                 |                                  |                                        |                                      |  |  |  |

| 6   | Not Used               | Always read 0                   | Always read 0                   |                                  |                                        |                                      |  |  |  |

| 5:3 | Ramp Time Step Control | Ramp Time Step                  | Control                         |                                  | Ramp Time Step                         | ) (µs)                               |  |  |  |

|     |                        | 0<br>0<br>0<br>0<br>1<br>1<br>1 |                                 | 1<br>2<br>3<br>4<br>6<br>8<br>12 |                                        |                                      |  |  |  |

| 2:0 | Ramp Code Step Control | Ramp Code Step                  | 1                               | 1                                | Rising Step<br>(LSB)                   | Falling Step<br>(LSB)                |  |  |  |

|     |                        | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0  | 1<br>2<br>3<br>4<br>6<br>8<br>12<br>16 | 1<br>1<br>2<br>3<br>4<br>5<br>6<br>8 |  |  |  |

www.ti.com

| R15 - REVISION ID REGISTER |       |  |  |  |  |

|----------------------------|-------|--|--|--|--|

| Address                    | 0x0F  |  |  |  |  |

| Туре                       | R/O   |  |  |  |  |

| Reset Default              | 8h'00 |  |  |  |  |

| Bit | Field Name | Description or Comment |

|-----|------------|------------------------|

| 7:0 |            | Always read back 0     |

#### OPERATION DESCRIPTION

#### **GENERAL DESCRIPTION**

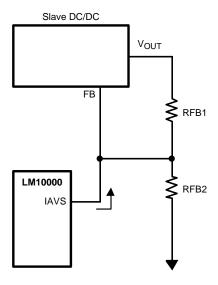

The LM10000 provides all the circuitry needed to enable most DC/DC regulators to work in a PowerWise® Adaptive Voltage Scaling (AVS) system. It communicates via the PowerWise Interface (PWI), and has analog outputs to control the output voltage of a slave power regulator. The slave power regulator can be any device that sets its output voltage with a feedback resistor divider.

#### THEORY OF OPERATION

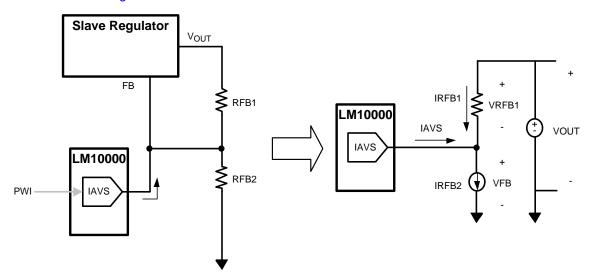

The LM10000 can be thought of as a D/A converter, converting PWI communication to analog outputs. One of the outputs is a current DAC (IAVS), which is connected to the feedback node of a slave regulator. Therefore, all PWI Change Voltage Commands (CVC) are decoded into a 7-bit current DAC output. The impedance of the feedback node at DC appears as the top feedback resistor. This is because the control loop of the slave regulator effectively maintains a constant current/voltage across the bottom feedback resistor, and creates low impedance at the  $V_{\rm OUT}$  node. Therefore, as more current is sourced into the feedback node, the more the output voltage is reduced. See Figure 6.

Figure 6. Output Voltage Is Controlled Via current Injection Into Feedback Node

#### **DIGITAL POWER MANAGEMENT**

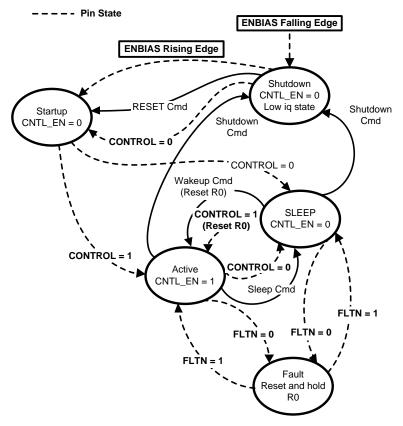

In addition to adaptive voltage scaling, the PWI and LM10000 enhance the slave regulator with basic digital power management control. This includes control of power states such as SHUTDOWN, SLEEP, and ACTIVE, ON/OFF sequencing, and voltage scaling slew rate. Figure 7 shows the LM10000 with available system connectivity options. The LM10000 has a flexible set of logic enable pins to allow the system easy interface to power states and sequencing. A logic CNTL\_EN output is provided to drive the slave regulator enable according the power state of the LM10000. For example, if a PWI SHUTDOWN command is issued to LM10000, the CNTL\_EN output is immediately driven to 0V, which if connected to the slave regulator enable input, will turn off the output voltage and enter a low  $I_q$  state. A summary of the logic inputs and outputs is given is LOGIC INPUTS AND OUTPUTS table.

Product Folder Links: LM10000

Copyright © 2010-2013, Texas Instruments Incorporated

Figure 7. LM10000 provides flexible digital power management via multi-master PWI 2.0, and flexible  $V_{\text{OUT}}$  sequencing control

#### IAVS OUTPUT CURRENT: CONTROLLING THE OUTPUT VOLTAGE

The LM10000 uses a 7-bit current DAC to control the output voltage of a slave power regulator. Since it is a current output, IAVS can be connected directly to the feedback node of the slave power regulator. IAVS has a range of  $0 - 60 \mu A$  with 7 bits of resolution, or a  $0.469 \mu A$  LSB.

A typical connection of the IAVS injection current into a slave regulator is shown in Figure 8. The output voltage VOUT is expressed as:

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R_{FB1}}{R_{FB2}}\right) - I_{AVS} \times R_{FB1}$$

(1)

Where VFB = the regulated feedback voltage of the slave regulator. This equation is valid for  $V_{OUT} > VFB$ .

Figure 8. IAVS Injection Current Into A Slave Regulator

Copyright © 2010–2013, Texas Instruments Incorporated

Submit Documentation Feedback

#### **USING REGISTER R9 TO CHANGE THE DEFAULT OUTPUT VOLTAGE**

The LM10000 default IAVS current is set by R9. R9 is trimmed to 0x7F, so that IAVS =  $0\mu$ A when power is applied to LM10000. Between power cycling, R9 can be changed so that IAVS defaults to values between 0 - 60  $\mu$ A. This can be useful for software trim of the default output voltage of the LM10000 controlled regulator. In order to do this, the system must take care to write to R9 before enabling the output (the output can be enabled/disabled while keeping the LM10000 logic on via the CONTROL input). Therefore, R9 must be written to by some system controller that is on a different power domain than that provided by LM10000. In addition, the "INITIAL\_VDD" register in the Advanced Power Controller (APC) must have the same value as R9 so that the APC and LM10000 default to the same voltage code.

#### IAVS MIRROR OUTPUT CURRENT

IAVS Mirror sources a current equal to IAVS.

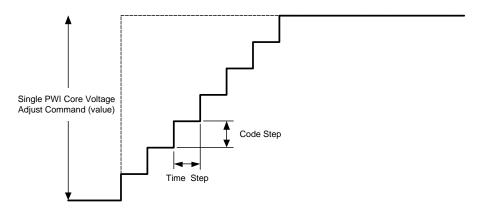

## **DIGITAL SLEW RATE CONTROL**

The IAVS and IAVS Mirror outputs have an adjustable, digital slew rate control. The slew rate control is programmed in register R10. The slew rate of the output voltage will effect both the output and input inrush current needed to scale the output voltage up or down. The amount of output current source or sink needed to scale the output voltage is governed by the equation describing current in a capacitor:

$$iC = C \times dV/dt$$

(2)

Therefore, more current is needed for larger voltage steps (dV) and for smaller settling times (dt). This current is in addition to the load current that the slave regulator is providing. It is recommended that the total current (load current + voltage slew current) not exceed the slave regulator current limit.

Figure 9. Digital Slew Rate Control

#### **PWI ADDRESS**

A resistor from the ADDR pin to ground sets the device's PWI address. The device senses the resistance as it is initializing from the shutdown state. The device will not update the address until it cycles through shutdown again. Use the table below to choose the appropriate resistor to place form ADDR pin to ground.

| PWI Address | Resistance (± 1% tolerance) |

|-------------|-----------------------------|

| 0           | ≤ 40.2 kΩ                   |

| 1           | 60.4 kΩ                     |

| 2           | 80.6 kΩ                     |

| 3           | 100 kΩ                      |

| 4           | 120 kΩ                      |

| 5           | 140 kΩ                      |

| 6           | 160 kΩ                      |

| 7           | 180 kΩ                      |

# INPUTS: ENBIAS, CONTROL, FLT\_N, RESET\_N, SCLK, SPWI

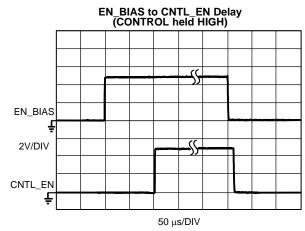

#### **ENBIAS**

The ENBIAS logic input enables the internal circuitry of the LM10000. The LM10000 goes through an initialization procedure upon the rising edge of ENBIAS. Initialization is complete within 100 µsec, after which the device is ready to be used.

If at any point ENBIAS goes low, the device enters a low I<sub>a</sub> shutdown state.

#### **CONTROL**

The CONTROL logic input allows control of the CNTL\_EN output without incurring delays associated with initialization. This signal is effectively ANDed with the internal 'ready' signal, which is high once initialization is complete.

The CONTROL pin level toggles the device between Active and Sleep states, and will reset the R0 register

#### FLT N

The FLT\_N logic input resets and holds the R0 register when its input signal is low. It has no effect on CNTL\_EN. This provides a convenient way to support automatic fault recovery modes in the slave power regulator. When connected to a standard PWGD pin of a DC/DC regulator, FLT\_N will reset and hold R0 as long as PWGD is low, allowing the slave regulator to recover from the fault by returning to the default voltage. Once FLT\_N returns high, R0 can be written to.

#### RESET N

The RESET\_N provides a separate, level controlled logic reset.

#### **SCLK and SPWI**

SCLK and SPWI provide serial PWI communication

## **OUTPUTS: CNTL EN, IAVS**

### CNTL\_EN

The CNTL\_EN output connects to the slave regulator enable pin. CNTL\_EN allows power state control via the PWI interface or ENBIAS/CONTROL logic inputs. For a direct connection from CNTL\_EN to the enable pin of the slave regulator, the enable pin on the slave regulator needs to be level based and active high (a logic high voltage enables the slave regulator). LM10000 will drive CNTL\_EN to the VDD voltage to enable the slave regulator, and to 0V to disable the slave regulator. In the case that the enable/disable on the slave regulator is a different function (impedance based or active low), extra circuitry is required.

#### **UVLO**

The LM10000 includes a UVLO circuit with hysteresis that triggers off of VDD. The system designer should be aware of the different UVLO thresholds of LM10000 and the slave regulator it is controlling. Since LM10000 is controlling the output of the slave regulator, the UVLO circuits in both the LM10000, and the slave regulator can react to severe input voltage transients. This is normally not a problem unless the application is operating very close to the UVLO thresholds of the two devices.

#### STATES

#### **STARTUP**

During the startup state, the LM10000 initializes all its registers and enables its bandgap. This process typically takes 100 µsec. CNTL\_EN is low during startup.

#### **ACTIVE**

During the active state, CNTL\_EN is high, the IAVS DACs are enabled, and PWI registers can be accessed.

#### **SLEEP**

During the sleep state, CNTL\_EN is low, the IAVS DACs are disabled, and PWI registers can be accessed.

#### **FAULT**

During the fault state, the IAVS current register (R0) is reset, after which the LM10000 automatically returns to its previous state.

#### **SHUTDOWN**

During the shutdown state, CNTL\_EN is low, the IAVS DACs are disabled, and most internal circuitry is disabled. Only the PWI state machine is biased to allow register access.

Figure 10. LM10000 State Diagram

Submit Documentation Feedback

### **APPLICATION CIRCUITS**

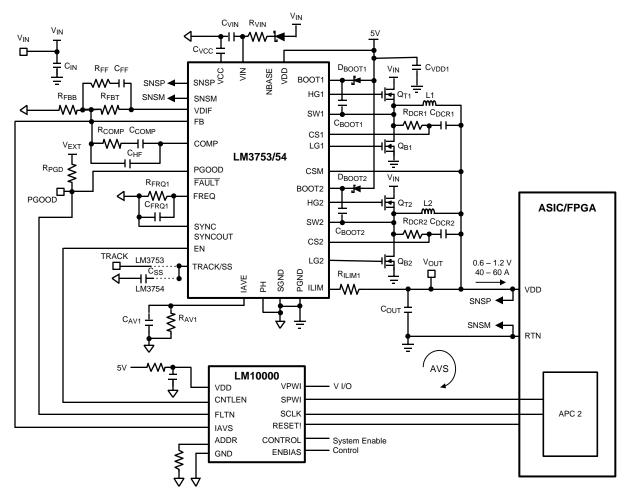

Figure 11. 60A AVS solution using LM10000 paired with LM3573/4 2-Phase Controller

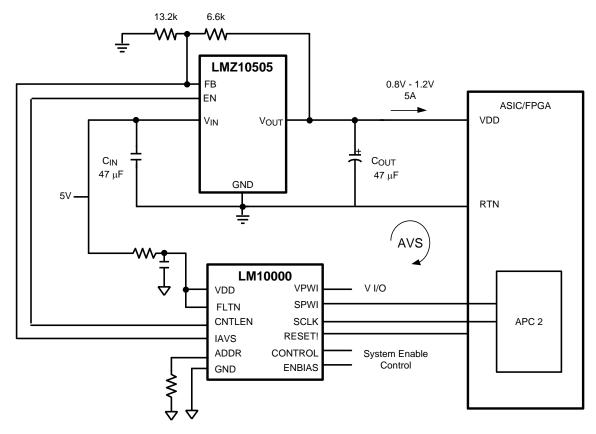

Figure 12. 5A AVS solution LM10000 paired with LMZ10505 Simple Switcher Module

# **REVISION HISTORY**

| CI | anges from Revision B (April 2013) to Revision C   |  |    |  |  |  |  |

|----|----------------------------------------------------|--|----|--|--|--|--|

| •  | Changed layout of National Data Sheet to TI format |  | 16 |  |  |  |  |

www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                |              |              |

| LM10000SD/NOPB        | Active | Production    | WSON (NHK)   14 | 1000   SMALL T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125   | 10000SD      |

| LM10000SD/NOPB.A      | Active | Production    | WSON (NHK)   14 | 1000   SMALL T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125   | 10000SD      |

| LM10000SDE/NOPB       | Active | Production    | WSON (NHK)   14 | 250   SMALL T&R       | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125   | 10000SD      |

| LM10000SDE/NOPB.A     | Active | Production    | WSON (NHK)   14 | 250   SMALL T&R       | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125   | 10000SD      |

| LM10000SDX/NOPB       | Active | Production    | WSON (NHK)   14 | 4500   LARGE T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125   | 10000SD      |

| LM10000SDX/NOPB.A     | Active | Production    | WSON (NHK)   14 | 4500   LARGE T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125   | 10000SD      |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 23-May-2025

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 1-Aug-2025

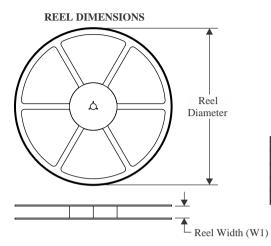

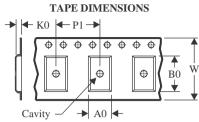

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

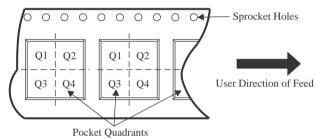

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM10000SD/NOPB  | WSON            | NHK                | 14 | 1000 | 177.8                    | 12.4                     | 3.3        | 4.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LM10000SDE/NOPB | WSON            | NHK                | 14 | 250  | 177.8                    | 12.4                     | 3.3        | 4.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LM10000SDX/NOPB | WSON            | NHK                | 14 | 4500 | 330.0                    | 12.4                     | 3.3        | 4.3        | 1.0        | 8.0        | 12.0      | Q1               |

www.ti.com 1-Aug-2025

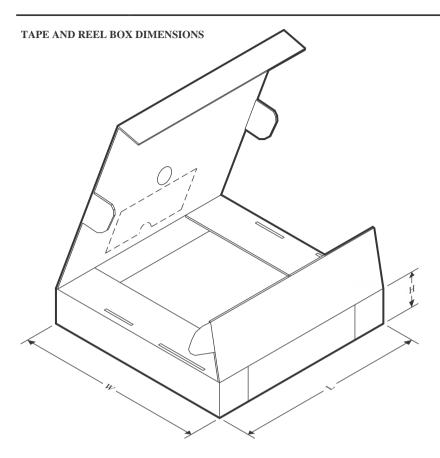

# \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM10000SD/NOPB  | WSON         | NHK             | 14   | 1000 | 210.0       | 185.0      | 35.0        |

| LM10000SDE/NOPB | WSON         | NHK             | 14   | 250  | 210.0       | 185.0      | 35.0        |

| LM10000SDX/NOPB | WSON         | NHK             | 14   | 4500 | 367.0       | 367.0      | 35.0        |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated