4 Mbit (512Kb x8 or 256Kb x16, Boot Block)

single supply Flash memory

## Features

- Single 5 V  $\pm$  10% supply voltage for program, erase and read operations

- Access time: 45 ns

- Programming time

- 8  $\mu$ s per Byte/Word typical

- 11 memory blocks

- 1 Boot Block (Top or Bottom Location)

- 2 Parameter and 8 Main Blocks

- Program/erase controller

- Embedded Byte/Word Program algorithm

- Embedded Multi-Block/Chip Erase algorithm

- Status Register Polling and Toggle Bits

- Ready/Busy Output Pin

- Erase Suspend and Resume modes

- Read and Program another Block during Erase Suspend

- Unlock Bypass Program command

- Faster Production/Batch Programming

- Temporary block unprotection mode

- Low power consumption

- Standby and Automatic Standby

- 100,000 program/erase cycles per block

- 20-year data retention

- Defectivity below 1 ppm/year

- Electronic signature

- Manufacturer Code: 0020h

- Top Device Code M29F400BT: 00D5h

- Bottom Device Code M29F400BB: 00D6h

- ECOPACK® packages available

## Contents

|          |                                                |           |

|----------|------------------------------------------------|-----------|

| <b>1</b> | <b>Description</b>                             | <b>6</b>  |

| <b>2</b> | <b>Signal descriptions</b>                     | <b>10</b> |

| 2.1      | Address inputs (A0-A17)                        | 10        |

| 2.2      | Data inputs/outputs (DQ0-DQ7)                  | 10        |

| 2.3      | Data inputs/outputs (DQ8-DQ14)                 | 10        |

| 2.4      | Data input/output or address input (DQ15A-1)   | 10        |

| 2.5      | Chip Enable ( $\bar{E}$ )                      | 10        |

| 2.6      | Output Enable ( $\bar{G}$ )                    | 10        |

| 2.7      | Write Enable ( $\bar{W}$ )                     | 11        |

| 2.8      | Reset/Block Temporary Unprotect ( $\bar{RP}$ ) | 11        |

| 2.9      | Ready/Busy output ( $R\bar{B}$ )               | 11        |

| 2.10     | Byte/Word organization select ( $\bar{BYTE}$ ) | 11        |

| 2.11     | $V_{CC}$ supply voltage                        | 12        |

| 2.12     | $V_{SS}$ ground                                | 12        |

| <b>3</b> | <b>Bus operations</b>                          | <b>13</b> |

| 3.1      | Bus Read                                       | 13        |

| 3.2      | Bus Write                                      | 13        |

| 3.3      | Output Disable                                 | 13        |

| 3.4      | Standby                                        | 13        |

| 3.5      | Automatic Standby                              | 14        |

| 3.6      | Special bus operations                         | 14        |

| 3.6.1    | Electronic Signature                           | 14        |

| 3.6.2    | Block Protection and Blocks Unprotection       | 14        |

| <b>4</b> | <b>Command interface</b>                       | <b>16</b> |

| 4.1      | Read/Reset command                             | 16        |

| 4.2      | Auto Select command                            | 16        |

| 4.3      | Program command                                | 17        |

| 4.4      | Unlock Bypass command                          | 17        |

| 4.5      | Unlock Bypass Program command                  | 17        |

---

|                               |                                                               |           |

|-------------------------------|---------------------------------------------------------------|-----------|

| 4.6                           | Unlock Bypass Reset command .....                             | 17        |

| 4.7                           | Chip Erase command .....                                      | 18        |

| 4.8                           | Block Erase command .....                                     | 18        |

| 4.9                           | Erase Suspend command .....                                   | 19        |

| 4.10                          | Erase Resume command .....                                    | 19        |

| 4.11                          | Read/Reset .....                                              | 20        |

| 4.12                          | Auto Select .....                                             | 20        |

| 4.13                          | Program, Unlock Bypass Program, Chip Erase, Block Erase ..... | 20        |

| 4.14                          | Unlock Bypass .....                                           | 21        |

| 4.15                          | Unlock Bypass Reset .....                                     | 21        |

| 4.16                          | Erase Suspend .....                                           | 21        |

| 4.17                          | Erase Resume .....                                            | 21        |

| <b>5</b>                      | <b>Status Register .....</b>                                  | <b>22</b> |

| 5.1                           | Data Polling Bit (DQ7) .....                                  | 22        |

| 5.2                           | Toggle Bit (DQ6) .....                                        | 22        |

| 5.3                           | Error Bit (DQ5) .....                                         | 23        |

| 5.4                           | Erase Timer Bit (DQ3) .....                                   | 23        |

| 5.5                           | Alternative Toggle Bit (DQ2) .....                            | 23        |

| <b>6</b>                      | <b>Maximum rating .....</b>                                   | <b>26</b> |

| <b>7</b>                      | <b>Program and erase times and endurance cycles .....</b>     | <b>27</b> |

| <b>8</b>                      | <b>DC and AC parameters .....</b>                             | <b>28</b> |

| <b>9</b>                      | <b>Package mechanical .....</b>                               | <b>35</b> |

| <b>10</b>                     | <b>Part numbering .....</b>                                   | <b>37</b> |

| <b>Appendix A</b>             | <b>Block address tables .....</b>                             | <b>38</b> |

| <b>Revision history .....</b> |                                                               | <b>39</b> |

## List of tables

|           |                                                                                              |    |

|-----------|----------------------------------------------------------------------------------------------|----|

| Table 1.  | Signal names . . . . .                                                                       | 7  |

| Table 2.  | Bus operations, $\overline{\text{BYTE}} = V_{IL}$ . . . . .                                  | 14 |

| Table 3.  | Bus operations, $\overline{\text{BYTE}} = V_{IH}$ . . . . .                                  | 15 |

| Table 4.  | Commands, 16-bit mode, $\overline{\text{BYTE}} = V_{IH}$ . . . . .                           | 19 |

| Table 5.  | Commands, 8-bit mode, $\overline{\text{BYTE}} = V_{IL}$ . . . . .                            | 20 |

| Table 6.  | Status Register bits. . . . .                                                                | 24 |

| Table 7.  | Absolute maximum ratings . . . . .                                                           | 26 |

| Table 8.  | Program/ Erase times endurance cycles . . . . .                                              | 27 |

| Table 9.  | AC measurement conditions . . . . .                                                          | 28 |

| Table 10. | Capacitance . . . . .                                                                        | 29 |

| Table 11. | DC characteristics. . . . .                                                                  | 30 |

| Table 12. | Read AC characteristics . . . . .                                                            | 31 |

| Table 13. | Write AC characteristics, Write Enable controlled . . . . .                                  | 32 |

| Table 14. | Write AC characteristics, Chip Enable controlled . . . . .                                   | 33 |

| Table 15. | Reset/Block Temporary Unprotect AC characteristics . . . . .                                 | 34 |

| Table 16. | TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20mm, package mechanical data. . . . .     | 35 |

| Table 17. | SO44 - 44 lead Plastic Small Outline, 500 mils body width, package mechanical data . . . . . | 36 |

| Table 18. | Ordering information scheme . . . . .                                                        | 37 |

| Table 19. | Top boot block addresses, M29F400BT. . . . .                                                 | 38 |

| Table 20. | Bottom boot block addresses, M29F400BB . . . . .                                             | 38 |

| Table 21. | Document revision history . . . . .                                                          | 39 |

## List of figures

|            |                                                                                      |    |

|------------|--------------------------------------------------------------------------------------|----|

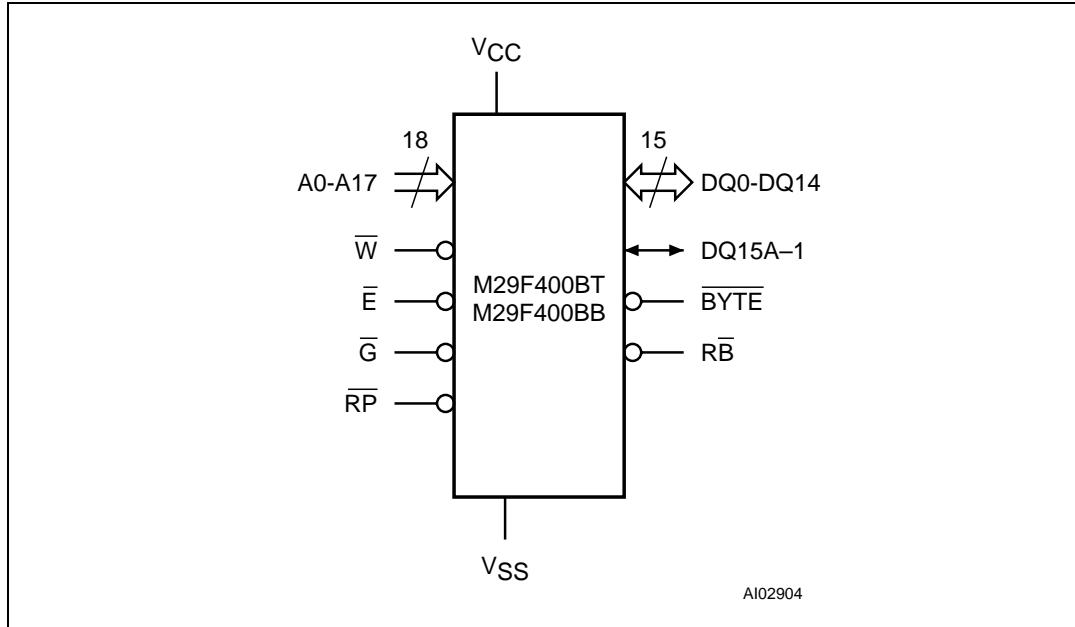

| Figure 1.  | Logic diagram . . . . .                                                              | 7  |

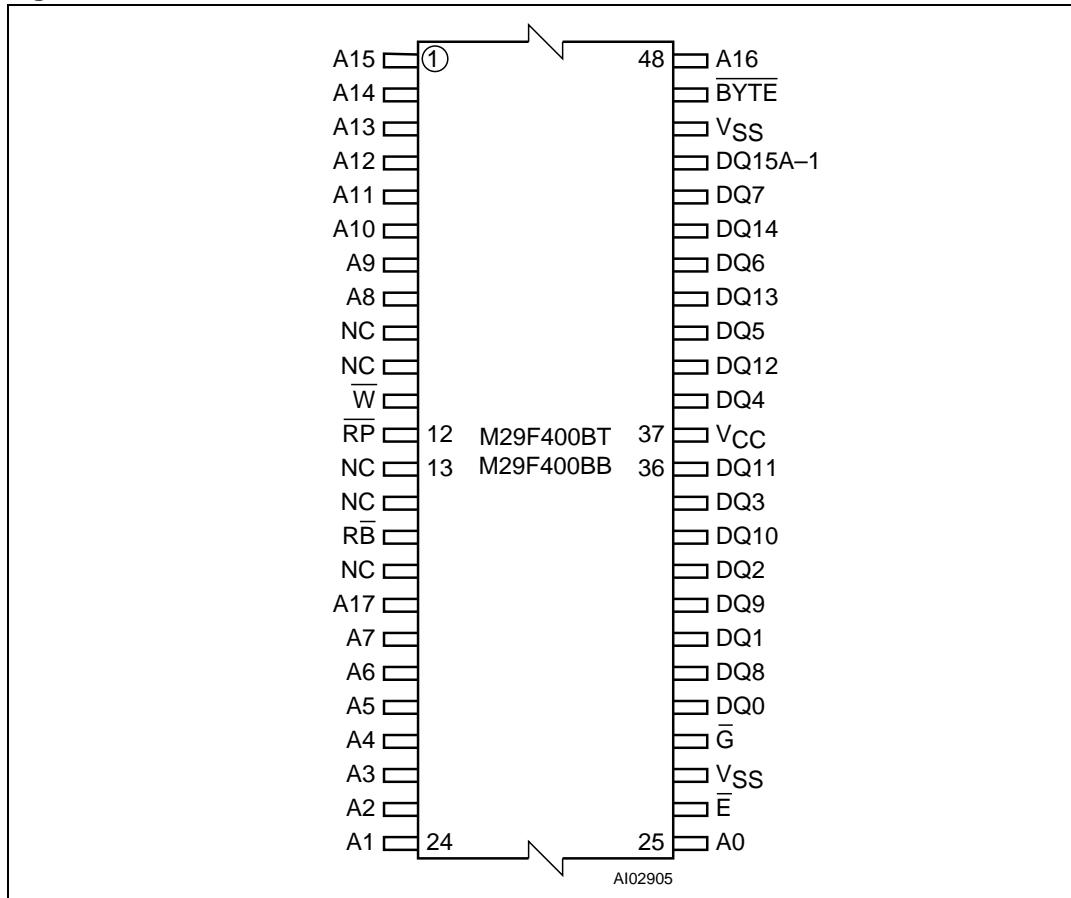

| Figure 2.  | TSOP connections . . . . .                                                           | 8  |

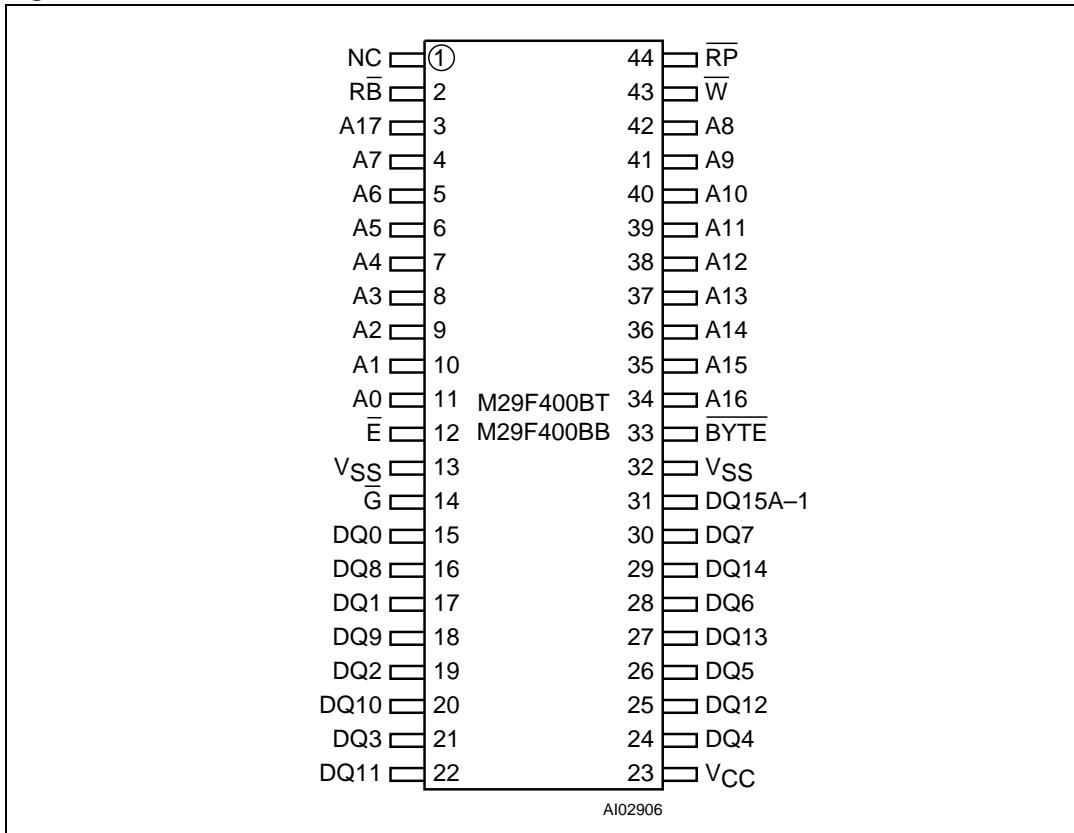

| Figure 3.  | SO connections . . . . .                                                             | 9  |

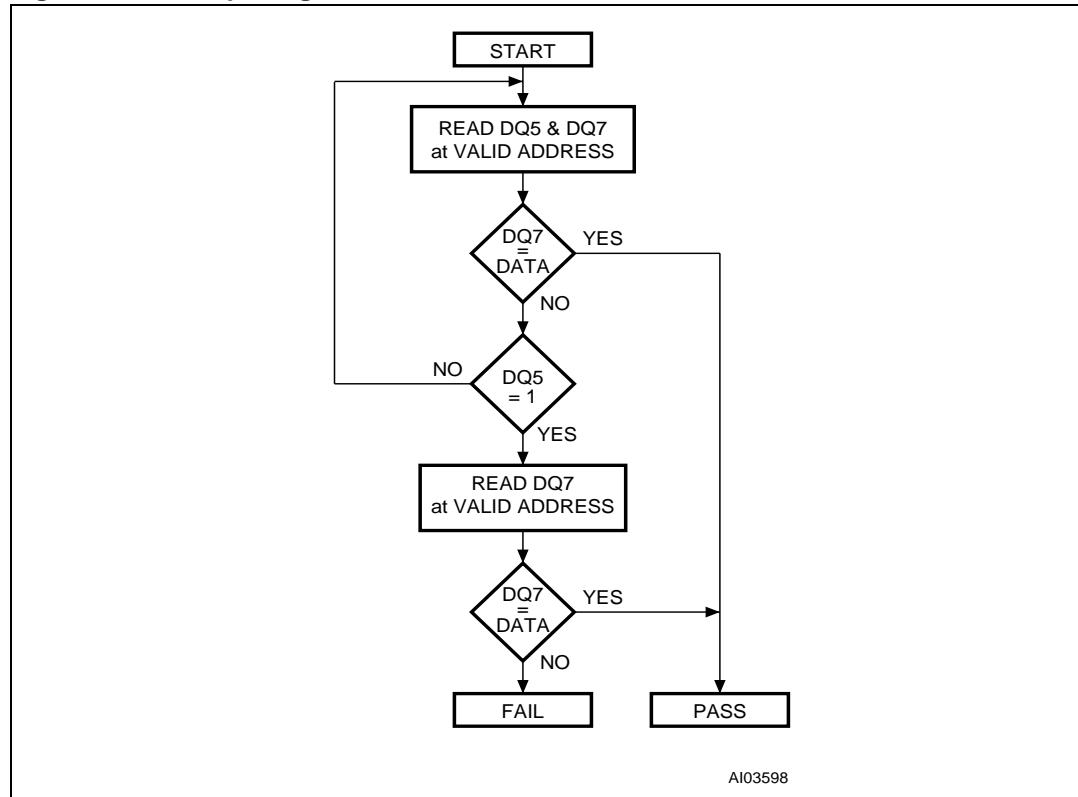

| Figure 4.  | Data polling flowchart . . . . .                                                     | 24 |

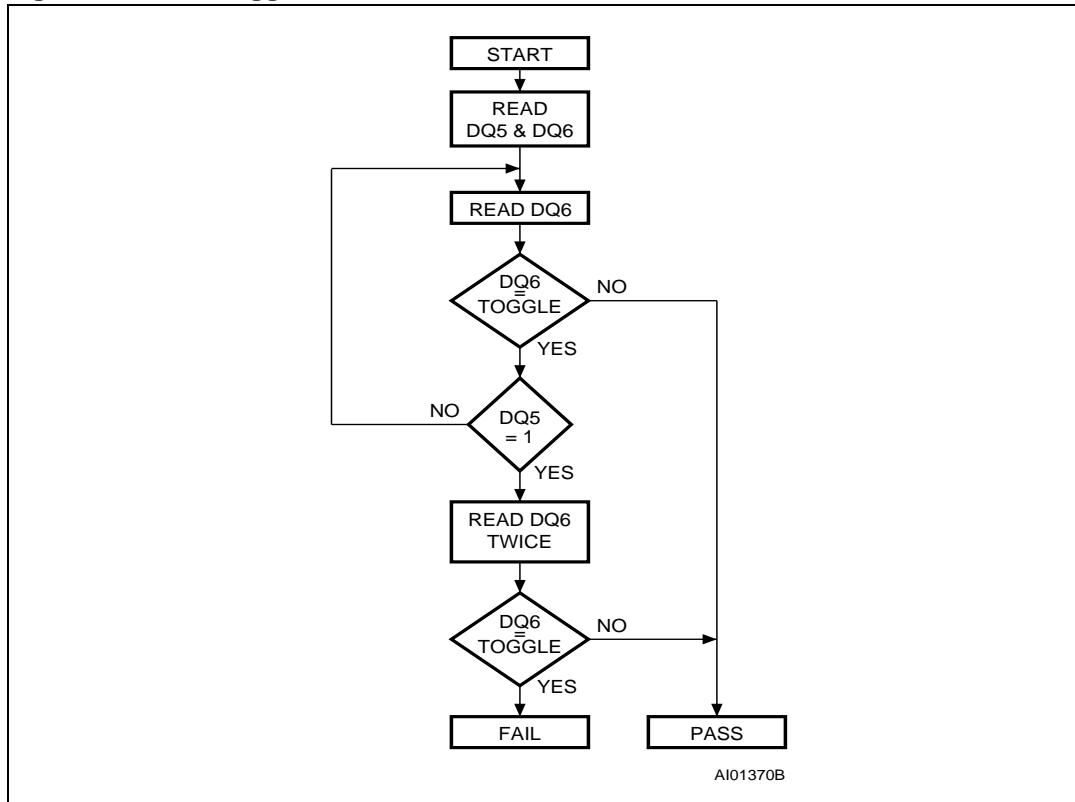

| Figure 5.  | Data toggle flowchart . . . . .                                                      | 25 |

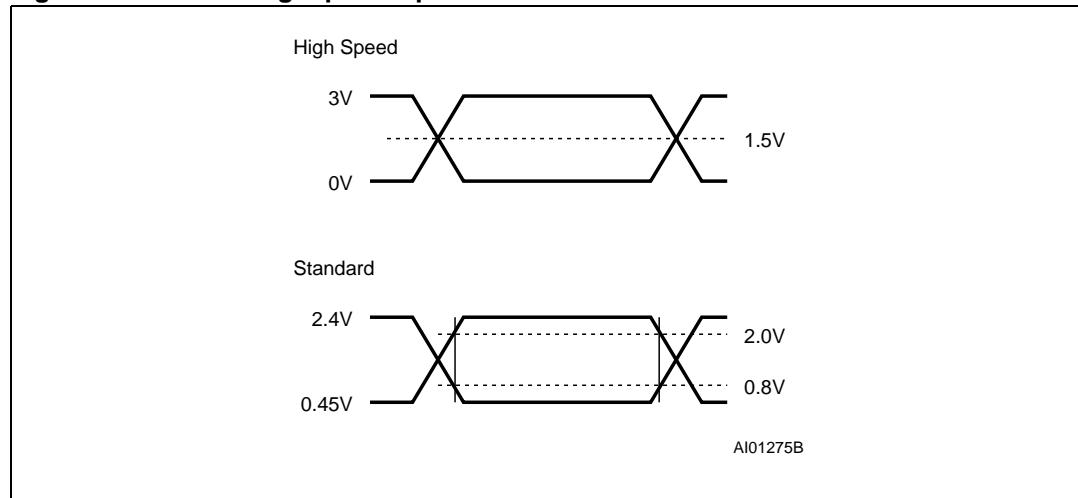

| Figure 6.  | AC testing input output waveform . . . . .                                           | 28 |

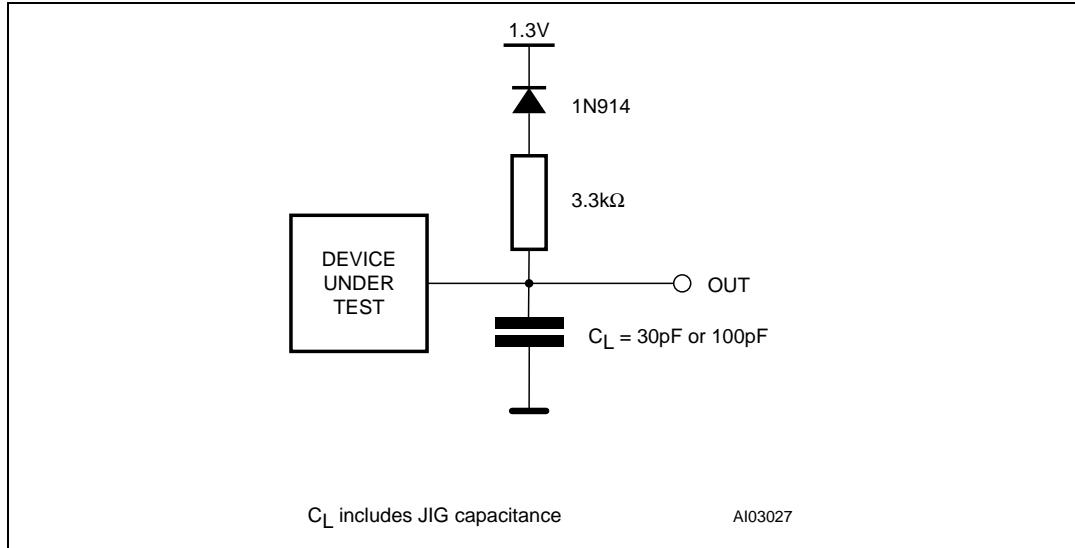

| Figure 7.  | AC testing load circuit . . . . .                                                    | 29 |

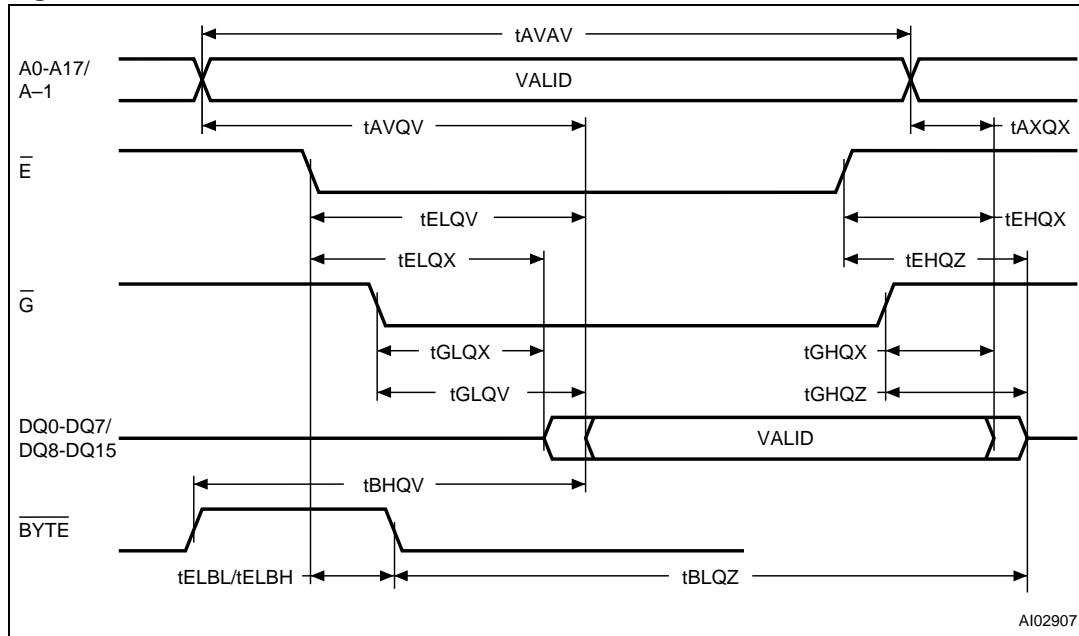

| Figure 8.  | Read mode AC waveforms . . . . .                                                     | 31 |

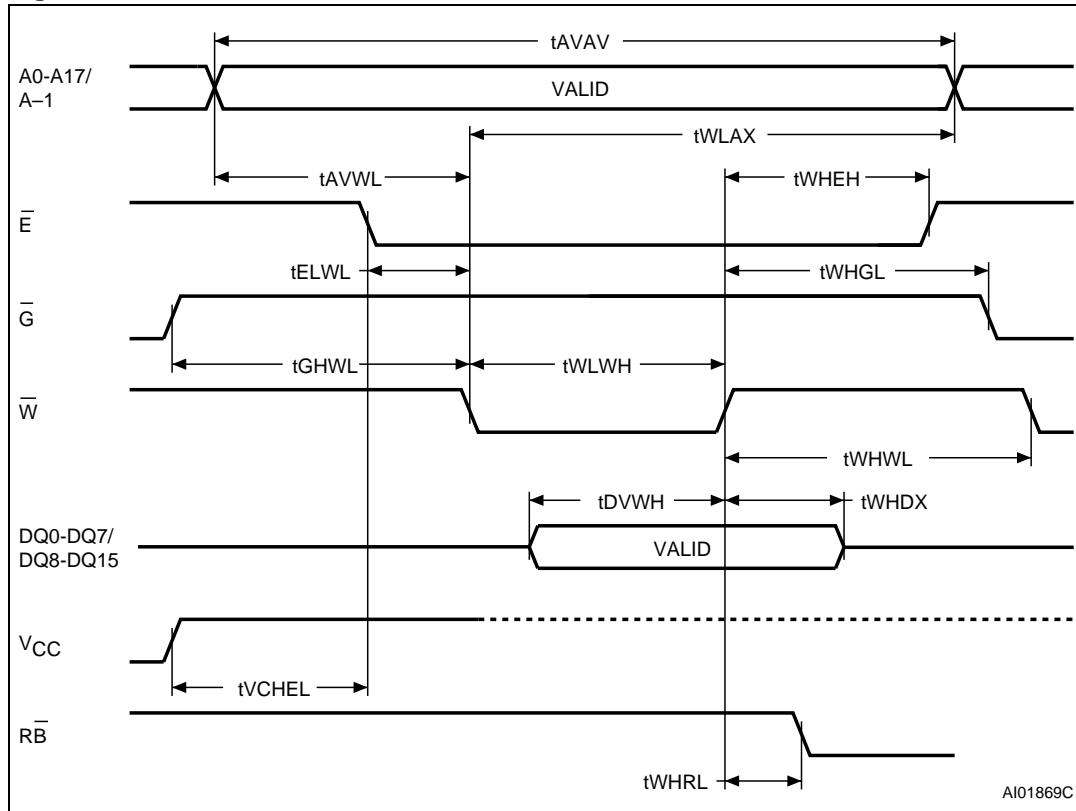

| Figure 9.  | Write AC waveforms, Write Enable controlled . . . . .                                | 32 |

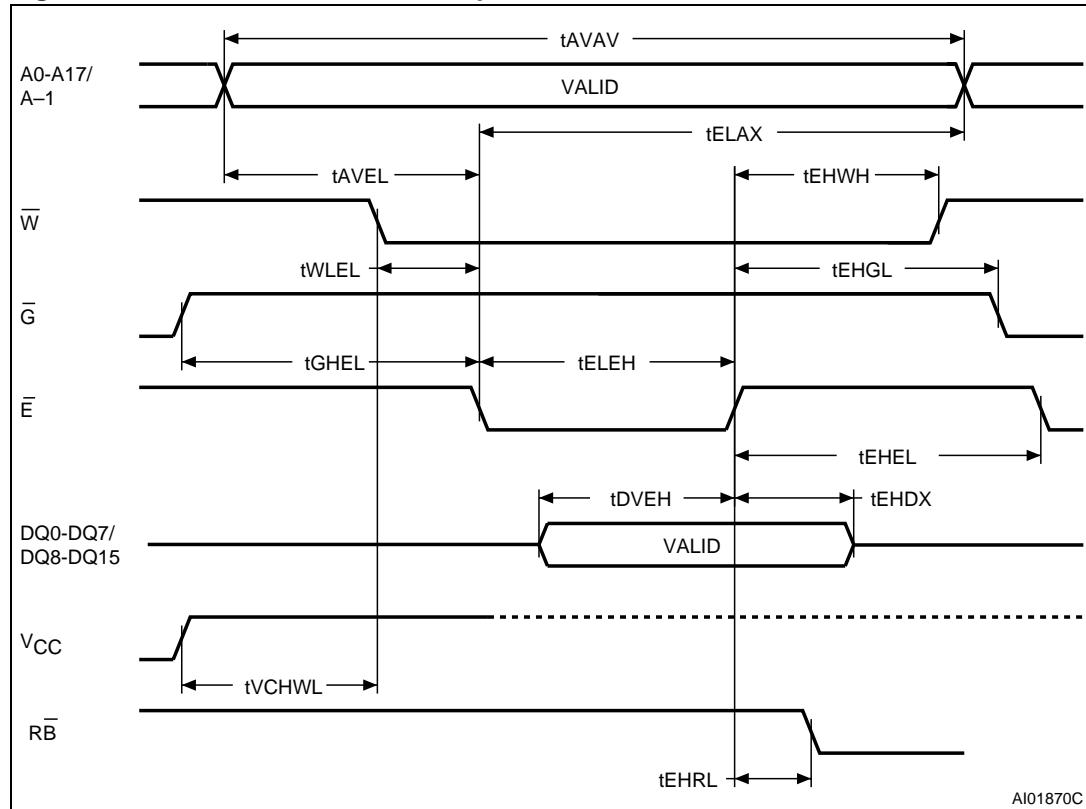

| Figure 10. | Write AC waveforms, Chip Enable controlled . . . . .                                 | 33 |

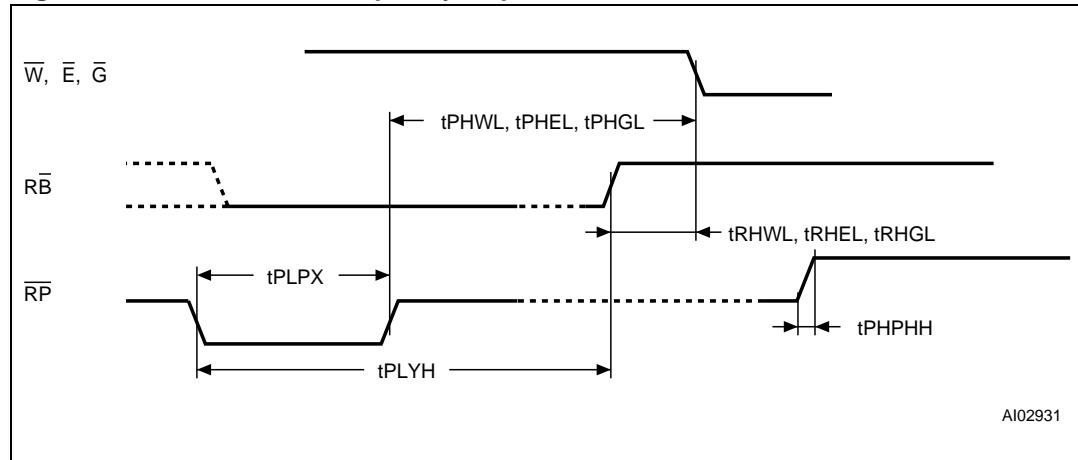

| Figure 11. | Reset/Block Temporary Unprotect AC waveforms . . . . .                               | 34 |

| Figure 12. | TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20mm, package outline . . . . .    | 35 |

| Figure 13. | SO44 - 44 lead Plastic Small Outline, 500 mils body width, package outline . . . . . | 36 |

## 1 Description

The M29F400B is a 4 Mbit (512 Kb x8 or 256 Kb x16) non-volatile memory that can be read, erased and reprogrammed. These operations can be performed using a single 5V supply. On power-up the memory defaults to its Read mode where it can be read in the same way as a ROM or EPROM. The M29F400B is fully backward compatible with the M29F400.

The memory is divided into blocks that can be erased independently so it is possible to preserve valid data while old data is erased. Each block can be protected independently to prevent accidental Program or Erase commands from modifying the memory. Program and Erase commands are written to the Command Interface of the memory. An on-chip Program/Erase Controller simplifies the process of programming or erasing the memory by taking care of all of the special operations that are required to update the memory contents. The end of a program or erase operation can be detected and any error conditions identified. The command set required to control the memory is consistent with JEDEC standards.

The blocks in the memory are asymmetrically arranged, see [Table 19.](#) and [Table 20.](#), Block Addresses. The first or last 64 Kbytes have been divided into four additional blocks. The 16 Kbyte Boot Block can be used for small initialization code to start the microprocessor, the two 8 Kbyte Parameter Blocks can be used for parameter storage and the remaining 32 K is a small Main Block where the application may be stored.

Chip Enable, Output Enable and Write Enable signals control the bus operation of the memory. They allow simple connection to most microprocessors, often without additional logic.

The memory is offered in TSOP48 (12 x 20 mm) and SO44 packages and it is supplied with all the bits erased (set to '1').

In order to meet environmental requirements, ST offers the M29F400B in ECOPACK® packages.

ECOPACK packages are Lead-free. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at: [www.st.com](http://www.st.com).

Figure 1. Logic diagram

Table 1. Signal names

|            |                                    |

|------------|------------------------------------|

| A0-A17     | Address Inputs                     |

| DQ0-DQ7    | Data Inputs/Outputs                |

| DQ8-DQ14   | Data Inputs/Outputs                |

| DQ15A-1    | Data Input/Output or Address Input |

| $\bar{E}$  | Chip Enable                        |

| $\bar{G}$  | Output Enable                      |

| $\bar{W}$  | Write Enable                       |

| $\bar{RP}$ | Reset/Block Temporary Unprotect    |

| $\bar{RB}$ | Ready/Busy Output                  |

| BYTE       | Byte/Word Organization Select      |

| $V_{CC}$   | Supply voltage                     |

| $V_{SS}$   | Ground                             |

| NC         | Not Connected Internally           |

Figure 2. TSOP connections

Figure 3. SO connections

## 2 Signal descriptions

See [Figure 1.](#), Logic Diagram, and [Table 1.](#), Signal Names, for a brief overview of the signals connected to this device.

### 2.1 Address inputs (A0-A17)

The Address Inputs select the cells in the memory array to access during Bus Read operations. During Bus Write operations they control the commands sent to the Command Interface of the internal state machine.

### 2.2 Data inputs/outputs (DQ0-DQ7)

The Data Inputs/Outputs output the data stored at the selected address during a Bus Read operation. During Bus Write operations they represent the commands sent to the Command Interface of the internal state machine.

### 2.3 Data inputs/outputs (DQ8-DQ14)

The Data Inputs/Outputs output the data stored at the selected address during a Bus Read operation when  $\overline{\text{BYTE}}$  is High,  $V_{IH}$ . When  $\overline{\text{BYTE}}$  is Low,  $V_{IL}$ , these pins are not used and are high impedance. During Bus Write operations the Command Register does not use these bits. When reading the Status Register these bits should be ignored.

### 2.4 Data input/output or address input (DQ15A-1)

When  $\overline{\text{BYTE}}$  is High,  $V_{IH}$ , this pin behaves as a Data Input/Output pin (as DQ8-DQ14). When  $\overline{\text{BYTE}}$  is Low,  $V_{IL}$ , this pin behaves as an address pin; DQ15A-1 Low will select the LSB of the Word on the other addresses, DQ15A-1 High will select the MSB. Throughout the text consider references to the Data Input/Output to include this pin when  $\overline{\text{BYTE}}$  is High and references to the Address Inputs to include this pin when  $\overline{\text{BYTE}}$  is Low except when stated explicitly otherwise.

### 2.5 Chip Enable ( $\overline{E}$ )

The Chip Enable,  $\overline{E}$ , activates the memory, allowing Bus Read and Bus Write operations to be performed. When Chip Enable is High,  $V_{IH}$ , all other pins are ignored.

### 2.6 Output Enable ( $\overline{G}$ )

The Output Enable,  $\overline{G}$ , controls the Bus Read operation of the memory.

## 2.7 Write Enable ( $\overline{W}$ )

The Write Enable,  $\overline{W}$ , controls the Bus Write operation of the memory's Command Interface.

## 2.8 Reset/Block Temporary Unprotect ( $\overline{RP}$ )

The Reset/Block Temporary Unprotect pin can be used to apply a Hardware Reset to the memory or to temporarily unprotect all Blocks that have been protected.

A Hardware Reset is achieved by holding Reset/Block Temporary Unprotect Low,  $V_{IL}$ , for at least  $t_{PLPX}$ . After Reset/Block Temporary Unprotect goes High,  $V_{IH}$ , the memory will be ready for Bus Read and Bus Write operations after  $t_{PHEL}$  or  $t_{RHEL}$ , whichever occurs last. See the Ready/Busy Output section, [Table 15.](#) and [Figure 11.](#), Reset/Temporary Unprotect AC Characteristics for more details.

Holding  $\overline{RP}$  at  $V_{ID}$  will temporarily unprotect the protected Blocks in the memory. Program and Erase operations on all blocks will be possible. The transition from  $V_{IH}$  to  $V_{ID}$  must be slower than  $t_{PHPHH}$ .

## 2.9 Ready/Busy output ( $\overline{RB}$ )

The Ready/Busy pin is an open-drain output that can be used to identify when the memory array can be read. Ready/Busy is high-impedance during Read mode, Auto Select mode and Erase Suspend mode.

After a Hardware Reset, Bus Read and Bus Write operations cannot begin until Ready/Busy becomes high-impedance. See [Table 15.](#) and [Figure 11.](#), Reset/Temporary Unprotect AC Characteristics.

During Program or Erase operations Ready/Busy is Low,  $V_{OL}$ . Ready/Busy will remain Low during Read/Reset commands or Hardware Resets until the memory is ready to enter Read mode.

The use of an open-drain output allows the Ready/Busy pins from several memories to be connected to a single pull-up resistor. A Low will then indicate that one, or more, of the memories is busy.

## 2.10 Byte/Word organization select (BYTE)

The Byte/Word Organization Select pin is used to switch between the 8-bit and 16-bit Bus modes of the memory. When Byte/Word Organization Select is Low,  $V_{IL}$ , the memory is in 8-bit mode, when it is High,  $V_{IH}$ , the memory is in 16-bit mode.

## 2.11 **V<sub>CC</sub> supply voltage**

The V<sub>CC</sub> Supply Voltage supplies the power for all operations (Read, Program, Erase etc.).

The Command Interface is disabled when the V<sub>CC</sub> Supply Voltage is less than the Lockout Voltage, V<sub>LKO</sub>. This prevents Bus Write operations from accidentally damaging the data during power up, power down and power surges. If the Program/Erase Controller is programming or erasing during this time then the operation aborts and the memory contents being altered will be invalid.

A 0.1 $\mu$ F capacitor should be connected between the V<sub>CC</sub> Supply Voltage pin and the V<sub>SS</sub> Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations, I<sub>CC4</sub>.

## 2.12 **V<sub>SS</sub> ground**

The V<sub>SS</sub> Ground is the reference for all voltage measurements.

## 3 Bus operations

There are five standard bus operations that control the device. These are Bus Read, Bus Write, Output Disable, Standby and Automatic Standby. See [Table 2.](#) and [Table 3.](#), Bus Operations, for a summary. Typically glitches of less than 5ns on Chip Enable or Write Enable are ignored by the memory and do not affect bus operations.

### 3.1 Bus Read

Bus Read operations read from the memory cells, or specific registers in the Command Interface. A valid Bus Read operation involves setting the desired address on the Address Inputs, applying a Low signal,  $V_{IL}$ , to Chip Enable and Output Enable and keeping Write Enable High,  $V_{IH}$ . The Data Inputs/Outputs will output the value, see [Figure 8.](#), Read Mode AC Waveforms, and [Table 12.](#), Read AC Characteristics, for details of when the output becomes valid.

### 3.2 Bus Write

Bus Write operations write to the Command Interface. A valid Bus Write operation begins by setting the desired address on the Address Inputs. The Address Inputs are latched by the Command Interface on the falling edge of Chip Enable or Write Enable, whichever occurs last. The Data Inputs/Outputs are latched by the Command Interface on the rising edge of Chip Enable or Write Enable, whichever occurs first. Output Enable must remain High,  $V_{IH}$ , during the whole Bus Write operation. See [Figure 9.](#) and [Figure 10.](#), Write AC Waveforms, and [Table 13.](#) and [Table 14.](#), Write AC Characteristics, for details of the timing requirements.

### 3.3 Output Disable

The Data Inputs/Outputs are in the high impedance state when Output Enable is High,  $V_{IH}$ .

### 3.4 Standby

When Chip Enable is High,  $V_{IH}$ , the Data Inputs/Outputs pins are placed in the high-impedance state and the Supply Current is reduced to the Standby level.

When Chip Enable is at  $V_{IH}$  the Supply Current is reduced to the TTL Standby Supply Current,  $I_{CC2}$ . To further reduce the Supply Current to the CMOS Standby Supply Current,  $I_{CC3}$ , Chip Enable should be held within  $V_{CC} \pm 0.2V$ . For Standby current levels see [Table 11.](#), DC Characteristics.

During program or erase operations the memory will continue to use the Program/Erase Supply Current,  $I_{CC4}$ , for Program or Erase operations until the operation completes.

### 3.5 Automatic Standby

If CMOS levels ( $V_{CC} \pm 0.2V$ ) are used to drive the bus and the bus is inactive for 150ns or more the memory enters Automatic Standby where the internal Supply Current is reduced to the CMOS Standby Supply Current,  $I_{CC3}$ . The Data Inputs/Outputs will still output data if a Bus Read operation is in progress.

### 3.6 Special bus operations

Additional bus operations can be performed to read the Electronic Signature and also to apply and remove Block Protection. These bus operations are intended for use by programming equipment and are not usually used in applications. They require  $V_{ID}$  to be applied to some pins.

#### 3.6.1 Electronic Signature

The memory has two codes, the manufacturer code and the device code, that can be read to identify the memory. These codes can be read by applying the signals listed in [Table 2](#). and [Table 3](#), Bus Operations.

#### 3.6.2 Block Protection and Blocks Unprotection

Each block can be separately protected against accidental Program or Erase. Protected blocks can be unprotected to allow data to be changed.

There are two methods available for protecting and unprotecting the blocks, one for use on programming equipment and the other for in-system use. For further information refer to Application Note AN1122, Applying Protection and Unprotection to M29 Series Flash.

**Table 2. Bus operations,  $\overline{BYTE} = V_{IL}^{(1)}$**

| Operation              | $\overline{E}$ | $\overline{G}$ | $\overline{W}$ | Address Inputs<br>DQ15A-1, A0-A17                                                  | Data Inputs/Outputs |                                    |

|------------------------|----------------|----------------|----------------|------------------------------------------------------------------------------------|---------------------|------------------------------------|

|                        |                |                |                |                                                                                    | DQ14-DQ8            | DQ7-DQ0                            |

| Bus Read               | $V_{IL}$       | $V_{IL}$       | $V_{IH}$       | Cell Address                                                                       | Hi-Z                | Data Output                        |

| Bus Write              | $V_{IL}$       | $V_{IH}$       | $V_{IL}$       | Command Address                                                                    | Hi-Z                | Data Input                         |

| Output Disable         | X              | $V_{IH}$       | $V_{IH}$       | X                                                                                  | Hi-Z                | Hi-Z                               |

| Standby                | $V_{IH}$       | X              | X              | X                                                                                  | Hi-Z                | Hi-Z                               |

| Read Manufacturer Code | $V_{IL}$       | $V_{IL}$       | $V_{IH}$       | $A0 = V_{IL}, A1 = V_{IL}, A9 = V_{ID}, \text{ Others } V_{IL} \text{ or } V_{IH}$ | Hi-Z                | 20h                                |

| Read Device Code       | $V_{IL}$       | $V_{IL}$       | $V_{IH}$       | $A0 = V_{IH}, A1 = V_{IL}, A9 = V_{ID}, \text{ Others } V_{IL} \text{ or } V_{IH}$ | Hi-Z                | D5h (M29F400BT)<br>D6h (M29F400BB) |

1.  $X = V_{IL}$  or  $V_{IH}$ .

Table 3. Bus operations,  $\overline{\text{BYTE}} = V_{IH}^{(1)}$

| Operation              | $\overline{E}$ | $\overline{G}$ | $\overline{W}$ | Address Inputs<br>A0-A17                                                    | Data Inputs/Outputs<br>DQ15A-1, DQ14-DQ0 |

|------------------------|----------------|----------------|----------------|-----------------------------------------------------------------------------|------------------------------------------|

| Bus Read               | $V_{IL}$       | $V_{IL}$       | $V_{IH}$       | Cell Address                                                                | Data Output                              |

| Bus Write              | $V_{IL}$       | $V_{IH}$       | $V_{IL}$       | Command Address                                                             | Data Input                               |

| Output Disable         | X              | $V_{IH}$       | $V_{IH}$       | X                                                                           | Hi-Z                                     |

| Standby                | $V_{IH}$       | X              | X              | X                                                                           | Hi-Z                                     |

| Read Manufacturer Code | $V_{IL}$       | $V_{IL}$       | $V_{IH}$       | A0 = $V_{IL}$ , A1 = $V_{IL}$ , A9 = $V_{ID}$ , Others $V_{IL}$ or $V_{IH}$ | 0020h                                    |

| Read Device Code       | $V_{IL}$       | $V_{IL}$       | $V_{IH}$       | A0 = $V_{IH}$ , A1 = $V_{IL}$ , A9 = $V_{ID}$ , Others $V_{IL}$ or $V_{IH}$ | 00D5h (M29F400BT)<br>00D6h (M29F400BB)   |

1. X =  $V_{IL}$  or  $V_{IH}$ .

## 4 Command interface

All Bus Write operations to the memory are interpreted by the Command Interface. Commands consist of one or more sequential Bus Write operations. Failure to observe a valid sequence of Bus Write operations will result in the memory returning to Read mode. The long command sequences are imposed to maximize data security.

The address used for the commands changes depending on whether the memory is in 16-bit or 8-bit mode. See either [Table 4.](#), or [Table 5.](#), depending on the configuration that is being used, for a summary of the commands.

### 4.1 Read/Reset command

The Read/Reset command returns the memory to its Read mode where it behaves like a ROM or EPROM. It also resets the errors in the Status Register. Either one or three Bus Write operations can be used to issue the Read/Reset command.

If the Read/Reset command is issued during a Block Erase operation or following a Programming or Erase error then the memory will take upto  $10\mu\text{s}$  to abort. During the abort period no valid data can be read from the memory. Issuing a Read/Reset command during a Block Erase operation will leave invalid data in the memory.

### 4.2 Auto Select command

The Auto Select command is used to read the Manufacturer Code, the Device Code and the Block Protection Status. Three consecutive Bus Write operations are required to issue the Auto Select command. Once the Auto Select command is issued the memory remains in Auto Select mode until another command is issued.

From the Auto Select mode the Manufacturer Code can be read using a Bus Read operation with  $A0 = V_{IL}$  and  $A1 = V_{IL}$ . The other address bits may be set to either  $V_{IL}$  or  $V_{IH}$ . The Manufacturer Code for STMicroelectronics is 0020h.

The Device Code can be read using a Bus Read operation with  $A0 = V_{IH}$  and  $A1 = V_{IL}$ . The other address bits may be set to either  $V_{IL}$  or  $V_{IH}$ . The Device Code for the M29F400BT is 00D5h and for the M29F400BB is 00D6h.

The Block Protection Status of each block can be read using a Bus Read operation with  $A0 = V_{IL}$ ,  $A1 = V_{IH}$ , and  $A12-A17$  specifying the address of the block. The other address bits may be set to either  $V_{IL}$  or  $V_{IH}$ . If the addressed block is protected then 01h is output on Data Inputs/Outputs DQ0-DQ7, otherwise 00h is output.

### 4.3 Program command

The Program command can be used to program a value to one address in the memory array at a time. The command requires four Bus Write operations, the final write operation latches the address and data in the internal state machine and starts the Program/Erase Controller.

If the address falls in a protected block then the Program command is ignored, the data remains unchanged. The Status Register is never read and no error condition is given.

During the program operation the memory will ignore all commands. It is not possible to issue any command to abort or pause the operation. Typical program times are given in [Table 8.](#). Bus Read operations during the program operation will output the Status Register on the Data Inputs/Outputs. See the section on the Status Register for more details.

After the program operation has completed the memory will return to the Read mode, unless an error has occurred. When an error occurs the memory will continue to output the Status Register. A Read/Reset command must be issued to reset the error condition and return to Read mode.

Note that the Program command cannot change a bit set at '0' back to '1'. One of the Erase Commands must be used to set all the bits in a block or in the whole memory from '0' to '1'.

### 4.4 Unlock Bypass command

The Unlock Bypass command is used in conjunction with the Unlock Bypass Program command to program the memory. When the access time to the device is long (as with some EPROM programmers) considerable time saving can be made by using these commands. Three Bus Write operations are required to issue the Unlock Bypass command.

Once the Unlock Bypass command has been issued the memory will only accept the Unlock Bypass Program command and the Unlock Bypass Reset command. The memory can be read as if in Read mode.

### 4.5 Unlock Bypass Program command

The Unlock Bypass Program command can be used to program one address in memory at a time. The command requires two Bus Write operations, the final write operation latches the address and data in the internal state machine and starts the Program/Erase Controller.

The Program operation using the Unlock Bypass Program command behaves identically to the Program operation using the Program command. A protected block cannot be programmed; the operation cannot be aborted and the Status Register is read. Errors must be reset using the Read/Reset command, which leaves the device in Unlock Bypass Mode. See the Program command for details on the behavior.

### 4.6 Unlock Bypass Reset command

The Unlock Bypass Reset command can be used to return to Read/Reset mode from Unlock Bypass Mode. Two Bus Write operations are required to issue the Unlock Bypass Reset command.

## 4.7 Chip Erase command

The Chip Erase command can be used to erase the entire chip. Six Bus Write operations are required to issue the Chip Erase Command and start the Program/Erase Controller.

If any blocks are protected then these are ignored and all the other blocks are erased. If all of the blocks are protected the Chip Erase operation appears to start but will terminate within about 100µs, leaving the data unchanged. No error condition is given when protected blocks are ignored.

During the erase operation the memory will ignore all commands. It is not possible to issue any command to abort the operation. Typical chip erase times are given in [Table 8.](#) All Bus Read operations during the Chip Erase operation will output the Status Register on the Data Inputs/Outputs. See the section on the Status Register for more details.

After the Chip Erase operation has completed the memory will return to the Read Mode, unless an error has occurred. When an error occurs the memory will continue to output the Status Register. A Read/Reset command must be issued to reset the error condition and return to Read Mode.

The Chip Erase Command sets all of the bits in unprotected blocks of the memory to '1'. All previous data is lost.

## 4.8 Block Erase command

The Block Erase command can be used to erase a list of one or more blocks. Six Bus Write operations are required to select the first block in the list. Each additional block in the list can be selected by repeating the sixth Bus Write operation using the address of the additional block. The Block Erase operation starts the Program/Erase Controller about 50µs after the last Bus Write operation. Once the Program/Erase Controller starts it is not possible to select any more blocks. Each additional block must therefore be selected within 50µs of the last block. The 50µs timer restarts when an additional block is selected. The Status Register can be read after the sixth Bus Write operation. See the Status Register for details on how to identify if the Program/Erase Controller has started the Block Erase operation.

If any selected blocks are protected then these are ignored and all the other selected blocks are erased. If all of the selected blocks are protected the Block Erase operation appears to start but will terminate within about 100µs, leaving the data unchanged. No error condition is given when protected blocks are ignored.

During the Block Erase operation the memory will ignore all commands except the Erase Suspend and Read/Reset commands. Typical block erase times are given in [Table 8.](#) All Bus Read operations during the Block Erase operation will output the Status Register on the Data Inputs/Outputs. See the section on the Status Register for more details.

After the Block Erase operation has completed the memory will return to the Read Mode, unless an error has occurred. When an error occurs the memory will continue to output the Status Register. A Read/Reset command must be issued to reset the error condition and return to Read mode.

The Block Erase Command sets all of the bits in the unprotected selected blocks to '1'. All previous data in the selected blocks is lost.

## 4.9 Erase Suspend command

The Erase Suspend Command may be used to temporarily suspend a Block Erase operation and return the memory to Read mode. The command requires one Bus Write operation.

The Program/Erase Controller will suspend within 15µs of the Erase Suspend Command being issued. Once the Program/Erase Controller has stopped the memory will be set to Read mode and the Erase will be suspended. If the Erase Suspend command is issued during the period when the memory is waiting for an additional block (before the Program/Erase Controller starts) then the Erase is suspended immediately and will start immediately when the Erase Resume Command is issued. It will not be possible to select any further blocks for erasure after the Erase Resume.

During Erase Suspend it is possible to Read and Program cells in blocks that are not being erased; both Read and Program operations behave as normal on these blocks. Reading from blocks that are being erased will output the Status Register. It is also possible to enter the Auto Select mode: the memory will behave as in the Auto Select mode on all blocks until a Read/Reset command returns the memory to Erase Suspend mode.

## 4.10 Erase Resume command

The Erase Resume command must be used to restart the Program/Erase Controller from Erase Suspend. An erase can be suspended and resumed more than once.

**Table 4. Commands, 16-bit mode,  $\overline{\text{BYTE}} = \text{V}_{\text{IH}}$**

| Command               | Length | Bus Write operations |      |      |      |      |      |      |      |      |      |      |      |

|-----------------------|--------|----------------------|------|------|------|------|------|------|------|------|------|------|------|

|                       |        | 1st                  |      | 2nd  |      | 3rd  |      | 4th  |      | 5th  |      | 6th  |      |

|                       |        | Addr                 | Data | Addr | Data | Addr | Data | Addr | Data | Addr | Data | Addr | Data |

| Read/Reset            | 1      | X                    | F0   |      |      |      |      |      |      |      |      |      |      |

|                       | 3      | 555                  | AA   | 2AA  | 55   | X    | F0   |      |      |      |      |      |      |

| Auto Select           | 3      | 555                  | AA   | 2AA  | 55   | 555  | 90   |      |      |      |      |      |      |

| Program               | 4      | 555                  | AA   | 2AA  | 55   | 555  | A0   | PA   | PD   |      |      |      |      |

| Unlock Bypass         | 3      | 555                  | AA   | 2AA  | 55   | 555  | 20   |      |      |      |      |      |      |

| Unlock Bypass Program | 2      | X                    | A0   | PA   | PD   |      |      |      |      |      |      |      |      |

| Unlock Bypass Reset   | 2      | X                    | 90   | X    | 00   |      |      |      |      |      |      |      |      |

| Chip Erase            | 6      | 555                  | AA   | 2AA  | 55   | 555  | 80   | 555  | AA   | 2AA  | 55   | 555  | 10   |

| Block Erase           | 6+     | 555                  | AA   | 2AA  | 55   | 555  | 80   | 555  | AA   | 2AA  | 55   | BA   | 30   |

| Erase Suspend         | 1      | X                    | B0   |      |      |      |      |      |      |      |      |      |      |

| Erase Resume          | 1      | X                    | 30   |      |      |      |      |      |      |      |      |      |      |

Table 5. Commands, 8-bit mode,  $\overline{\text{BYTE}} = V_{IL}$ <sup>(1)</sup><sup>(2)</sup>

| Command               | Length | Bus Write Operations |      |      |      |      |      |      |      |      |      |      |      |

|-----------------------|--------|----------------------|------|------|------|------|------|------|------|------|------|------|------|

|                       |        | 1st                  |      | 2nd  |      | 3rd  |      | 4th  |      | 5th  |      | 6th  |      |

|                       |        | Addr                 | Data | Addr | Data | Addr | Data | Addr | Data | Addr | Data | Addr | Data |

| Read/Reset            | 1      | X                    | F0   |      |      |      |      |      |      |      |      |      |      |

|                       | 3      | AAA                  | AA   | 555  | 55   | X    | F0   |      |      |      |      |      |      |

| Auto Select           | 3      | AAA                  | AA   | 555  | 55   | AAA  | 90   |      |      |      |      |      |      |

| Program               | 4      | AAA                  | AA   | 555  | 55   | AAA  | A0   | PA   | PD   |      |      |      |      |

| Unlock Bypass         | 3      | AAA                  | AA   | 555  | 55   | AAA  | 20   |      |      |      |      |      |      |

| Unlock Bypass Program | 2      | X                    | A0   | PA   | PD   |      |      |      |      |      |      |      |      |

| Unlock Bypass Reset   | 2      | X                    | 90   | X    | 00   |      |      |      |      |      |      |      |      |

| Chip Erase            | 6      | AAA                  | AA   | 555  | 55   | AAA  | 80   | AAA  | AA   | 555  | 55   | AAA  | 10   |

| Block Erase           | 6+     | AAA                  | AA   | 555  | 55   | AAA  | 80   | AAA  | AA   | 555  | 55   | BA   | 30   |

| Erase Suspend         | 1      | X                    | B0   |      |      |      |      |      |      |      |      |      |      |

| Erase Resume          | 1      | X                    | 30   |      |      |      |      |      |      |      |      |      |      |

1. X = Don't Care, PA = Program Address, PD = Program Data, BA = Any address in the Block.

2. All values are in hexadecimal.

The Command Interface only uses A-1, A0-A10 and DQ0-DQ7 to verify the commands; A11-A17, DQ8-DQ14 and DQ15 are Don't Care. DQ15A-1 is A-1 when  $\overline{\text{BYTE}}$  is  $V_{IL}$  or DQ15 when  $\overline{\text{BYTE}}$  is  $V_{IH}$ .

## 4.11 Read/Reset

After a Read/Reset command, read the memory as normal until another command is issued.

## 4.12 Auto Select

After an Auto Select command, read Manufacturer ID, Device ID or Block Protection Status.

## 4.13 Program, Unlock Bypass Program, Chip Erase, Block Erase

After these commands read the Status Register until the Program/Erase Controller completes and the memory returns to Read Mode. Add additional Blocks during Block Erase Command with additional Bus Write Operations until Timeout Bit is set.

#### **4.14    Unlock Bypass**

After the Unlock Bypass command issue Unlock Bypass Program or Unlock Bypass Reset commands.

#### **4.15    Unlock Bypass Reset**

After the Unlock Bypass Reset command read the memory as normal until another command is issued.

#### **4.16    Erase Suspend**

After the Erase Suspend command read non-erasing memory blocks as normal, issue Auto Select and Program commands on non-erasing blocks as normal.

#### **4.17    Erase Resume**

After the Erase Resume command the suspended Erase operation resumes, read the Status Register until the Program/Erase Controller completes and the memory returns to Read Mode.

## 5 Status Register

Bus Read operations from any address always read the Status Register during Program and Erase operations. It is also read during Erase Suspend when an address within a block being erased is accessed.

The bits in the Status Register are summarized in [Table 6.](#), Status Register Bits.

### 5.1 Data Polling Bit (DQ7)

The Data Polling Bit can be used to identify whether the Program/Erase Controller has successfully completed its operation or if it has responded to an Erase Suspend. The Data Polling Bit is output on DQ7 when the Status Register is read.

During Program operations the Data Polling Bit outputs the complement of the bit being programmed to DQ7. After successful completion of the Program operation the memory returns to Read mode and Bus Read operations from the address just programmed output DQ7, not its complement.

During Erase operations the Data Polling Bit outputs '0', the complement of the erased state of DQ7. After successful completion of the Erase operation the memory returns to Read Mode.

In Erase Suspend mode the Data Polling Bit will output a '1' during a Bus Read operation within a block being erased. The Data Polling Bit will change from a '0' to a '1' when the Program/Erase Controller has suspended the Erase operation.

[Figure 4.](#), Data Polling Flowchart, gives an example of how to use the Data Polling Bit. A Valid Address is the address being programmed or an address within the block being erased.

### 5.2 Toggle Bit (DQ6)

The Toggle Bit can be used to identify whether the Program/Erase Controller has successfully completed its operation or if it has responded to an Erase Suspend. The Toggle Bit is output on DQ6 when the Status Register is read.

During Program and Erase operations the Toggle Bit changes from '0' to '1' to '0', etc., with successive Bus Read operations at any address. After successful completion of the operation the memory returns to Read mode.

During Erase Suspend mode the Toggle Bit will output when addressing a cell within a block being erased. The Toggle Bit will stop toggling when the Program/Erase Controller has suspended the Erase operation.

[Figure 5.](#), Data Toggle Flowchart, gives an example of how to use the Data Toggle Bit.

### 5.3 Error Bit (DQ5)

The Error Bit can be used to identify errors detected by the Program/Erase Controller. The Error Bit is set to '1' when a Program, Block Erase or Chip Erase operation fails to write the correct data to the memory. If the Error Bit is set a Read/Reset command must be issued before other commands are issued. The Error bit is output on DQ5 when the Status Register is read.

Note that the Program command cannot change a bit set at '0' back to '1' and attempting to do so may or may not set DQ5 at '1'. In both cases, a successive Bus Read operation will show the bit is still '0'. One of the Erase commands must be used to set all the bits in a block or in the whole memory from '0' to '1'.

### 5.4 Erase Timer Bit (DQ3)

The Erase Timer Bit can be used to identify the start of Program/Erase Controller operation during a Block Erase command. Once the Program/Erase Controller starts erasing the Erase Timer Bit is set to '1'. Before the Program/Erase Controller starts the Erase Timer Bit is set to '0' and additional blocks to be erased may be written to the Command Interface. The Erase Timer Bit is output on DQ3 when the Status Register is read.

### 5.5 Alternative Toggle Bit (DQ2)

The Alternative Toggle Bit can be used to monitor the Program/Erase controller during Erase operations. The Alternative Toggle Bit is output on DQ2 when the Status Register is read.

During Chip Erase and Block Erase operations the Toggle Bit changes from '0' to '1' to '0', etc., with successive Bus Read operations from addresses within the blocks being erased. Once the operation completes the memory returns to Read mode.

During Erase Suspend the Alternative Toggle Bit changes from '0' to '1' to '0', etc. with successive Bus Read operations from addresses within the blocks being erased. Bus Read operations to addresses within blocks not being erased will output the memory cell data as if in Read mode.

After an Erase operation that causes the Error Bit to be set the Alternative Toggle Bit can be used to identify which block or blocks have caused the error. The Alternative Toggle Bit changes from '0' to '1' to '0', etc. with successive Bus Read Operations from addresses within blocks that have not erased correctly. The Alternative Toggle Bit does not change if the addressed block has erased correctly.

Table 6. Status Register bits<sup>(1)</sup>

| Operation                    | Address              | DQ7 | DQ6       | DQ5 | DQ3 | DQ2                 | R <sup>–</sup> |

|------------------------------|----------------------|-----|-----------|-----|-----|---------------------|----------------|

| Program                      | Any Address          | DQ7 | Toggle    | 0   | –   | –                   | 0              |

| Program During Erase Suspend | Any Address          | DQ7 | Toggle    | 0   | –   | –                   | 0              |

| Program Error                | Any Address          | DQ7 | Toggle    | 1   | –   | –                   | 0              |

| Chip Erase                   | Any Address          | 0   | Toggle    | 0   | 1   | Toggle              | 0              |

| Block Erase before timeout   | Erasing Block        | 0   | Toggle    | 0   | 0   | Toggle              | 0              |

|                              | Non-Erasing Block    | 0   | Toggle    | 0   | 0   | No Toggle           | 0              |

| Block Erase                  | Erasing Block        | 0   | Toggle    | 0   | 1   | Toggle              | 0              |

|                              | Non-Erasing Block    | 0   | Toggle    | 0   | 1   | No Toggle           | 0              |

| Erase Suspend                | Erasing Block        | 1   | No Toggle | 0   | –   | Toggle              | 1              |

|                              | Non-Erasing Block    |     |           |     |     | Data read as normal | 1              |

| Erase Error                  | Good Block Address   | 0   | Toggle    | 1   | 1   | No Toggle           | 0              |

|                              | Faulty Block Address | 0   | Toggle    | 1   | 1   | Toggle              | 0              |

1. Unspecified data bits should be ignored.

Figure 4. Data polling flowchart

Figure 5. Data toggle flowchart

## 6 Maximum rating

Stressing the device above the rating listed in the Absolute Maximum Ratings table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

**Table 7. Absolute maximum ratings**

| Symbol         | Parameter                                                  | Value        | Unit |

|----------------|------------------------------------------------------------|--------------|------|

| $T_A$          | Ambient Operating Temperature (Temperature Range Option 1) | 0 to 70      | °C   |

|                | Ambient Operating Temperature (Temperature Range Option 6) | –40 to 85    | °C   |

|                | Ambient Operating Temperature (Temperature Range Option 3) | –40 to 125   | °C   |

| $T_{BIAS}$     | Temperature Under Bias                                     | –50 to 125   | °C   |

| $T_{STG}$      | Storage Temperature                                        | –65 to 150   | °C   |

| $V_{IO}^{(1)}$ | Input or Output Voltage                                    | –0.6 to 6    | V    |

| $V_{CC}$       | Supply Voltage                                             | –0.6 to 6    | V    |

| $V_{ID}$       | Identification Voltage                                     | –0.6 to 13.5 | V    |

1. Minimum Voltage may undershoot to –2V during transition and for less than 20ns during transitions.

## 7 Program and erase times and endurance cycles

The Program and Erase times and the number of Program/ Erase cycles per block are shown in [Table 8](#). Exact erase times may change depending on the memory array condition.

**Table 8. Program/ Erase times endurance cycles<sup>(1)</sup>**

| Parameter                                      | Min     | Typ <sup>(2)</sup> | Typical after<br>100k W/E Cycles<br>(2) | Max | Unit   |

|------------------------------------------------|---------|--------------------|-----------------------------------------|-----|--------|

| Chip Erase (All bits in the memory set to '0') |         | 1.5                | 1.5                                     |     | s      |

| Chip Erase                                     |         | 5                  | 5                                       | 20  | s      |

| Block Erase (64 Kbytes)                        |         | 0.6                | 0.6                                     | 4   | s      |

| Program (Byte or Word)                         |         | 8                  | 8                                       | 150 | μs     |

| Chip Program (Byte by Byte)                    |         | 4.5                | 4.5                                     | 18  | s      |

| Chip Program (Word by Word)                    |         | 2.3                | 2.3                                     | 9   | s      |

| Program/Erase Cycles (per Block)               | 100,000 |                    |                                         |     | cycles |

1.  $T_A = 0$  to  $70^\circ\text{C}$ ,  $-40$  to  $85^\circ\text{C}$  or  $-40$  to  $125^\circ\text{C}$

2.  $T_A = 25^\circ\text{C}$ ,  $V_{CC} = 5\text{V}$ .

## 8 DC and AC parameters

This section summarizes the operating measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC characteristics Tables that follow, are derived from tests performed under the Measurement Conditions summarized in [Table 9: AC measurement conditions](#). Designers should check that the operating conditions in their circuit match the operating conditions when relying on the quoted parameters.

**Table 9. AC measurement conditions**

| Parameter                             | M29F400B           |                    |

|---------------------------------------|--------------------|--------------------|

|                                       | 45 / 55            | 70 / 90            |

| AC Test Conditions                    | High Speed         | Standard           |

| Load Capacitance ( $C_L$ )            | 30pF               | 100pF              |

| Input Rise and Fall Times             | $\leq 10\text{ns}$ | $\leq 10\text{ns}$ |

| Input Pulse Voltages                  | 0 to 3V            | 0.45 to 2.4V       |

| Input and Output Timing Ref. Voltages | 1.5V               | 0.8V and 2.0V      |

**Figure 6. AC testing input output waveform**

Figure 7. AC testing load circuit

Table 10. Capacitance<sup>(1) (2)</sup>

| Symbol    | Parameter          | Test Condition        | Min | Max | Unit |

|-----------|--------------------|-----------------------|-----|-----|------|

| $C_{IN}$  | Input Capacitance  | $V_{IN} = 0\text{V}$  |     | 6   | pF   |

| $C_{OUT}$ | Output Capacitance | $V_{OUT} = 0\text{V}$ |     | 12  | pF   |

1.  $T_A = 25^\circ\text{C}$ ,  $f = 1\text{ MHz}$

2. Sampled only, not 100% tested.

Table 11. DC characteristics<sup>(1)</sup>

| Symbol          | Parameter                               | Test Condition                                          | Min            | Typ <sup>(2)</sup> | Max            | Unit    |

|-----------------|-----------------------------------------|---------------------------------------------------------|----------------|--------------------|----------------|---------|

| $I_{LI}$        | Input Leakage Current                   | $0V \leq V_{IN} \leq V_{CC}$                            |                |                    | $\pm 1$        | $\mu A$ |

| $I_{LO}$        | Output Leakage Current                  | $0V \leq V_{OUT} \leq V_{CC}$                           |                |                    | $\pm 1$        | $\mu A$ |

| $I_{CC1}$       | Supply Current (Read)                   | $\bar{E} = V_{IL}, \bar{G} = V_{IH}, f = 6MHz$          |                | 7                  | 20             | $mA$    |

| $I_{CC2}$       | Supply Current (Standby)<br>TTL         | $\bar{E} = V_{IH}$                                      |                |                    | 1              | $mA$    |

| $I_{CC3}$       | Supply Current (Standby)<br>CMOS        | $\bar{E} = V_{CC} \pm 0.2V, \bar{RP} = V_{CC} \pm 0.2V$ |                | 30                 | 100            | $\mu A$ |

| $I_{CC4}^{(3)}$ | Supply Current<br>(Program/Erase)       | Program/Erase<br>Controller active                      |                |                    | 20             | $mA$    |

| $V_{IL}$        | Input Low Voltage                       |                                                         | -0.5           |                    | 0.8            | $V$     |

| $V_{IH}$        | Input High Voltage                      |                                                         | 2              |                    | $V_{CC} + 0.5$ | $V$     |

| $V_{OL}$        | Output Low Voltage                      | $I_{OL} = 5.8mA$                                        |                |                    | 0.45           | $V$     |

| $V_{OH}$        | Output High Voltage TTL                 | $I_{OH} = -2.5mA$                                       | 2.4            |                    |                | $V$     |

|                 | Output High Voltage<br>CMOS             | $I_{OH} = -100\mu A$                                    | $V_{CC} - 0.4$ |                    |                | $V$     |

| $V_{ID}$        | Identification Voltage                  |                                                         | 11.5           |                    | 12.5           | $V$     |

| $I_{ID}$        | Identification Current                  | $A9 = V_{ID}$                                           |                |                    | 100            | $\mu A$ |

| $V_{LKO}^{(3)}$ | Program/Erase Lockout<br>Supply Voltage |                                                         | 3.2            |                    | 4.2            | $V$     |

1.  $T_A = 0$  to  $70^\circ C$ ,  $-40$  to  $85^\circ C$  or  $-40$  to  $125^\circ C$ 2.  $T_A = 25^\circ C$ ,  $V_{CC} = 5V$ .

3. Sampled only, not 100% tested.

Figure 8. Read mode AC waveforms

Table 12. Read AC characteristics<sup>(1)</sup>

| Symbol                                                      | Alt                                    | Parameter                                                             | Test Condition                             |     | M29F400B |    |         | Unit |

|-------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------|--------------------------------------------|-----|----------|----|---------|------|

|                                                             |                                        |                                                                       |                                            |     | 45       | 55 | 70 / 90 |      |

| t <sub>AVAV</sub>                                           | t <sub>RC</sub>                        | Address Valid to Next Address Valid                                   | $\bar{E} = V_{IL}$ ,<br>$\bar{G} = V_{IL}$ | Min | 45       | 55 | 70      | ns   |

| t <sub>AVQV</sub>                                           | t <sub>ACC</sub>                       | Address Valid to Output Valid                                         | $\bar{E} = V_{IL}$ ,<br>$\bar{G} = V_{IL}$ | Max | 45       | 55 | 70      | ns   |

| t <sub>ELQX</sub> <sup>(2)</sup>                            | t <sub>LZ</sub>                        | Chip Enable Low to Output Transition                                  | $\bar{G} = V_{IL}$                         | Min | 0        | 0  | 0       | ns   |

| t <sub>ELQV</sub>                                           | t <sub>CE</sub>                        | Chip Enable Low to Output Valid                                       | $\bar{G} = V_{IL}$                         | Max | 45       | 55 | 70      | ns   |

| t <sub>GLQX</sub> <sup>(2)</sup>                            | t <sub>OLZ</sub>                       | Output Enable Low to Output Transition                                | $\bar{E} = V_{IL}$                         | Min | 0        | 0  | 0       | ns   |

| t <sub>GLQV</sub>                                           | t <sub>OE</sub>                        | Output Enable Low to Output Valid                                     | $\bar{E} = V_{IL}$                         | Max | 25       | 30 | 30      | ns   |

| t <sub>EHQZ</sub> <sup>(2)</sup>                            | t <sub>HZ</sub>                        | Chip Enable High to Output Hi-Z                                       | $\bar{G} = V_{IL}$                         | Max | 15       | 18 | 20      | ns   |

| t <sub>GHQZ</sub> <sup>(2)</sup>                            | t <sub>DF</sub>                        | Output Enable High to Output Hi-Z                                     | $\bar{E} = V_{IL}$                         | Max | 15       | 18 | 20      | ns   |

| t <sub>EHQX</sub><br>t <sub>GHQX</sub><br>t <sub>AXQX</sub> | t <sub>OH</sub>                        | Chip Enable, Output Enable or Address Transition to Output Transition |                                            | Min | 0        | 0  | 0       | ns   |

| t <sub>ELBL</sub><br>t <sub>ELBH</sub>                      | t <sub>ELFL</sub><br>t <sub>ELFH</sub> | Chip Enable to BYTE Low or High                                       |                                            | Max | 5        | 5  | 5       | ns   |

| t <sub>BLQZ</sub>                                           | t <sub>FLQZ</sub>                      | BYTE Low to Output Hi-Z                                               |                                            | Max | 15       | 15 | 20      | ns   |

| t <sub>BHQV</sub>                                           | t <sub>FHQV</sub>                      | BYTE High to Output Valid                                             |                                            | Max | 30       | 30 | 30      | ns   |

1. TA = 0 to 70°C, -40 to 85°C or -40 to 125°C

2. Sampled only, not 100% tested.

Figure 9. Write AC waveforms, Write Enable controlled

Table 13. Write AC characteristics, Write Enable controlled<sup>(1)</sup>

| Symbol                    | Alt        | Parameter                              | M29F400B |    |         | Unit       |

|---------------------------|------------|----------------------------------------|----------|----|---------|------------|

|                           |            |                                        | 45       | 55 | 70 / 90 |            |

| $t_{AVAV}$                | $t_{WC}$   | Address Valid to Next Address Valid    | Min      | 45 | 55      | 70 ns      |

| $t_{ELWL}$                | $t_{CS}$   | Chip Enable Low to Write Enable Low    | Min      | 0  | 0       | 0 ns       |

| $t_{WLWH}$                | $t_{WP}$   | Write Enable Low to Write Enable High  | Min      | 40 | 40      | 45 ns      |

| $t_{DVWH}$                | $t_{DS}$   | Input Valid to Write Enable High       | Min      | 25 | 25      | 30 ns      |

| $t_{WHDX}$                | $t_{DH}$   | Write Enable High to Input Transition  | Min      | 0  | 0       | 0 ns       |

| $t_{WHEH}$                | $t_{CH}$   | Write Enable High to Chip Enable High  | Min      | 0  | 0       | 0 ns       |

| $t_{WHWL}$                | $t_{WPH}$  | Write Enable High to Write Enable Low  | Min      | 20 | 20      | 20 ns      |

| $t_{AVWL}$                | $t_{AS}$   | Address Valid to Write Enable Low      | Min      | 0  | 0       | 0 ns       |

| $t_{WLAX}$                | $t_{AH}$   | Write Enable Low to Address Transition | Min      | 40 | 40      | 45 ns      |

| $t_{GHWL}$                |            | Output Enable High to Write Enable Low | Min      | 0  | 0       | 0 ns       |

| $t_{WHGL}$                | $t_{OEH}$  | Write Enable High to Output Enable Low | Min      | 0  | 0       | 0 ns       |

| $t_{WHRL}$ <sup>(2)</sup> | $t_{BUSY}$ | Program/Erase Valid to RB Low          | Max      | 30 | 30      | 30 ns      |

| $t_{VCHEL}$               | $t_{VCS}$  | $V_{CC}$ High to Chip Enable Low       | Min      | 50 | 50      | 50 $\mu$ s |

1.  $T_A = 0$  to  $70^\circ\text{C}$ ,  $-40$  to  $85^\circ\text{C}$  or  $-40$  to  $125^\circ\text{C}$

2. Sampled only, not 100% tested.

Figure 10. Write AC waveforms, Chip Enable controlled

Table 14. Write AC characteristics, Chip Enable controlled<sup>(1)</sup>

| Symbol                           | Alt               | Parameter                                | M29F400B |    |         | Unit |    |

|----------------------------------|-------------------|------------------------------------------|----------|----|---------|------|----|

|                                  |                   |                                          | 45       | 55 | 70 / 90 |      |    |

| t <sub>AVAV</sub>                | t <sub>WC</sub>   | Address Valid to Next Address Valid      | Min      | 45 | 55      | 70   | ns |

| t <sub>WLEL</sub>                | t <sub>WS</sub>   | Write Enable Low to Chip Enable Low      | Min      | 0  | 0       | 0    | ns |

| t <sub>ELEH</sub>                | t <sub>CP</sub>   | Chip Enable Low to Chip Enable High      | Min      | 40 | 40      | 45   | ns |

| t <sub>DVEH</sub>                | t <sub>DS</sub>   | Input Valid to Chip Enable High          | Min      | 25 | 25      | 30   | ns |

| t <sub>EHDX</sub>                | t <sub>DH</sub>   | Chip Enable High to Input Transition     | Min      | 0  | 0       | 0    | ns |

| t <sub>EHWL</sub>                | t <sub>WH</sub>   | Chip Enable High to Write Enable High    | Min      | 0  | 0       | 0    | ns |

| t <sub>EHGL</sub>                | t <sub>CPH</sub>  | Chip Enable High to Chip Enable Low      | Min      | 20 | 20      | 20   | ns |

| t <sub>AVEL</sub>                | t <sub>AS</sub>   | Address Valid to Chip Enable Low         | Min      | 0  | 0       | 0    | ns |

| t <sub>ELAX</sub>                | t <sub>AH</sub>   | Chip Enable Low to Address Transition    | Min      | 40 | 40      | 45   | ns |

| t <sub>GHEL</sub>                |                   | Output Enable High Chip Enable Low       | Min      | 0  | 0       | 0    | ns |

| t <sub>EHGL</sub>                | t <sub>OEH</sub>  | Chip Enable High to Output Enable Low    | Min      | 0  | 0       | 0    | ns |

| t <sub>EHRL</sub> <sup>(2)</sup> | t <sub>BUSY</sub> | Program/Erase Valid to RB Low            | Max      | 30 | 30      | 30   | ns |

| t <sub>VCHWL</sub>               | t <sub>VCS</sub>  | V <sub>CC</sub> High to Write Enable Low | Min      | 50 | 50      | 50   | μs |

1. T<sub>A</sub> = 0 to 70 °C, -40 to 85 °C or -40 to 125 °C

2. Sampled only, not 100% tested.

Figure 11. Reset/Block Temporary Unprotect AC waveforms

Table 15. Reset/Block Temporary Unprotect AC characteristics<sup>(1)</sup>

| Symbol                                                   | Alt         | Parameter                                                                    | M29F400B |     |         | Unit |         |

|----------------------------------------------------------|-------------|------------------------------------------------------------------------------|----------|-----|---------|------|---------|

|                                                          |             |                                                                              | 45       | 55  | 70 / 90 |      |         |

| $t_{PHWL}^{(2)}$<br>$t_{PHEL}^{(2)}$<br>$t_{PHGL}^{(2)}$ | $t_{RH}$    | $\overline{RP}$ High to Write Enable Low, Chip Enable Low, Output Enable Low | Min      | 50  | 50      | 50   | ns      |

| $t_{RHWL}^{(2)}$<br>$t_{RHEL}^{(2)}$<br>$t_{RHGL}^{(2)}$ | $t_{RB}$    | $\overline{RB}$ High to Write Enable Low, Chip Enable Low, Output Enable Low | Min      | 0   | 0       | 0    | ns      |

| $t_{PLPX}$                                               | $t_{RP}$    | $\overline{RP}$ Pulse Width                                                  | Min      | 500 | 500     | 500  | ns      |

| $t_{PLYH}^{(2)}$                                         | $t_{READY}$ | $\overline{RP}$ Low to Read Mode                                             | Max      | 10  | 10      | 10   | $\mu s$ |

| $t_{PHPHH}^{(2)}$                                        | $t_{VIDR}$  | $\overline{RP}$ Rise Time to $V_{ID}$                                        | Min      | 500 | 500     | 500  | ns      |

1.  $T_A = 0$  to  $70^\circ C$ ,  $-40$  to  $85^\circ C$  or  $-40$  to  $125^\circ C$

2. Sampled only, not 100% tested.

## 9 Package mechanical

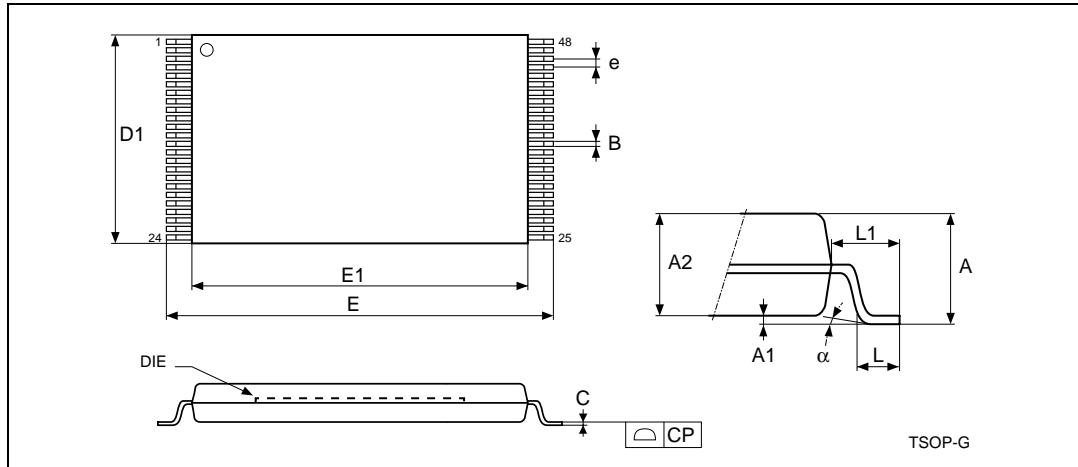

Figure 12. TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20mm, package outline

1. Drawing is not to scale.

Table 16. TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20mm, package mechanical data

| Symbol | millimeters |        |        | inches |        |        |

|--------|-------------|--------|--------|--------|--------|--------|

|        | Typ         | Min    | Max    | Typ    | Min    | Max    |

| A      |             |        | 1.200  |        |        | 0.0472 |

| A1     | 0.100       | 0.050  | 0.150  | 0.0039 | 0.0020 | 0.0059 |

| A2     | 1.000       | 0.950  | 1.050  | 0.0394 | 0.0374 | 0.0413 |

| B      | 0.220       | 0.170  | 0.270  | 0.0087 | 0.0067 | 0.0106 |

| C      |             | 0.100  | 0.210  |        | 0.0039 | 0.0083 |

| CP     |             |        | 0.100  |        |        | 0.0039 |

| D1     | 12.000      | 11.900 | 12.100 | 0.4724 | 0.4685 | 0.4764 |

| E      | 20.000      | 19.800 | 20.200 | 0.7874 | 0.7795 | 0.7953 |

| E1     | 18.400      | 18.300 | 18.500 | 0.7244 | 0.7205 | 0.7283 |

| e      | 0.500       | —      | —      | 0.0197 | —      | —      |

| L      | 0.600       | 0.500  | 0.700  | 0.0236 | 0.0197 | 0.0276 |

| L1     | 0.800       |        |        | 0.0315 |        |        |

| α      | 3°          | 0°     | 5°     | 3°     | 0°     | 5°     |

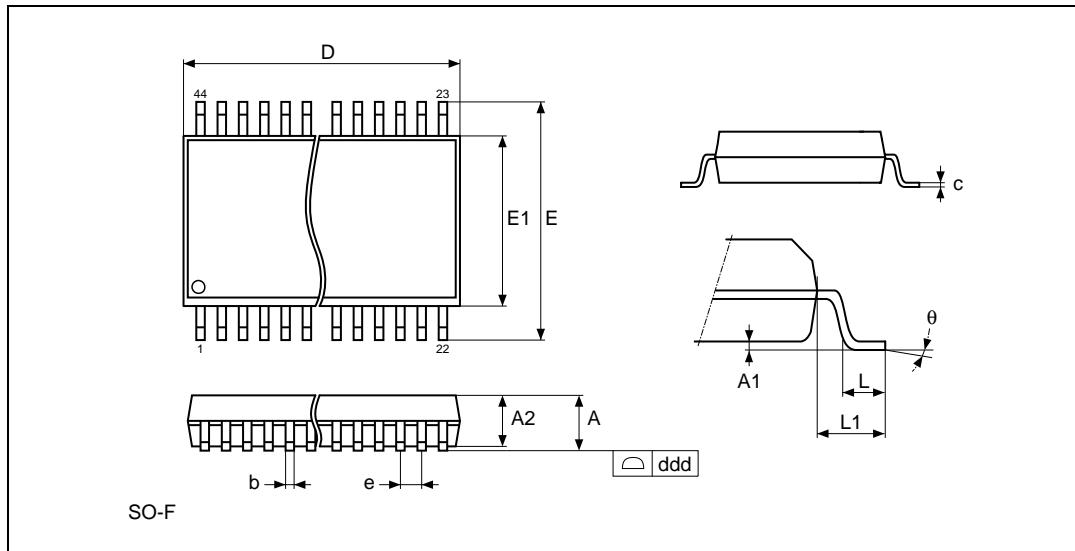

**Figure 13. SO44 - 44 lead Plastic Small Outline, 500 mils body width, package outline**

1. Drawing is not to scale.

**Table 17. SO44 - 44 lead Plastic Small Outline, 500 mils body width, package mechanical data**

| Symbol | millimeters |       |       | inches |       |       |

|--------|-------------|-------|-------|--------|-------|-------|

|        | Typ         | Min   | Max   | Typ    | Min   | Max   |

| A      |             |       | 3.00  |        |       | 0.118 |

| A1     | 0.10        |       |       | 0.004  |       |       |

| A2     | 2.69        | 2.56  | 2.79  | 0.106  | 0.101 | 0.110 |

| b      |             | 0.35  | 0.50  |        | 0.014 | 0.020 |

| c      |             | 0.18  | 0.28  |        | 0.007 | 0.011 |

| D      | 28.50       | 28.37 | 28.63 | 1.122  | 1.117 | 1.127 |

| ddd    |             |       | 0.10  |        |       | 0.004 |

| E      | 16.03       | 15.77 | 16.28 | 0.631  | 0.621 | 0.641 |

| E1     | 12.60       | 12.47 | 12.73 | 0.496  | 0.491 | 0.501 |

| e      | 1.27        | —     | —     | 0.050  | —     | —     |

| L      | 0.79        |       |       | 0.031  |       |       |

| L1     | 1.73        |       |       | 0.068  |       |       |

| Θ      |             |       | 8°    |        |       | 8°    |

| N      | 44          |       |       | 44     |       |       |

## 10 Part numbering

**Table 18. Ordering information scheme**

Example:

**Device Type**

M29

**Operating Voltage**

$F = V_{CC} = 5V \pm 10\%$

**Device Function**

400B = 4 Mbit (512Kb x8 or 256Kb x16), Boot Block

**Array Matrix**

T = Top Boot

B = Bottom Boot

**Speed**

45 = 45 ns

55 = 55 ns

70 = 70 ns

90 = 90 ns

**Package**

N = TSOP48: 12 x 20 mm

M = SO44

**Temperature Range**

1 = 0 to 70 °C

3 = -40 to 125 °C

6 = -40 to 85 °C

**Option**

Blank = Standard Packing

T = Tape & Reel Packing

E = ECOPACK Package, Standard Packing

F = ECOPACK Package, Tape & Reel Packing

**Note:**

*The last two characters of the ordering code may be replaced by a letter code for preprogrammed parts, otherwise devices are shipped from the factory with the memory content bits erased to '1'.*

For a list of available options (Speed, Package, etc...) or for further information on any aspect of this device, please contact the ST Sales Office nearest to you.

## Appendix A Block address tables

**Table 19. Top boot block addresses, M29F400BT**

| #  | Size<br>(Kbytes) | Address Range<br>(x8) | Address Range<br>(x16) |

|----|------------------|-----------------------|------------------------|

| 10 | 16               | 7C000h-7FFFFh         | 3E000h-3FFFFh          |

| 9  | 8                | 7A000h-7BFFFh         | 3D000h-3DFFFh          |

| 8  | 8                | 78000h-79FFFh         | 3C000h-3CFFFh          |

| 7  | 32               | 70000h-77FFFh         | 38000h-3BFFFh          |

| 6  | 64               | 60000h-6FFFFh         | 30000h-37FFFh          |

| 5  | 64               | 50000h-5FFFFh         | 28000h-2FFFFh          |

| 4  | 64               | 40000h-4FFFFh         | 20000h-27FFFh          |

| 3  | 64               | 30000h-3FFFFh         | 18000h-1FFFFh          |

| 2  | 64               | 20000h-2FFFFh         | 10000h-17FFFh          |

| 1  | 64               | 10000h-1FFFFh         | 08000h-0FFFFh          |

| 0  | 64               | 00000h-0FFFFh         | 00000h-07FFFh          |

**Table 20. Bottom boot block addresses, M29F400BB**

| #  | Size<br>(Kbytes) | Address Range<br>(x8) | Address Range<br>(x16) |

|----|------------------|-----------------------|------------------------|

| 10 | 64               | 70000h-7FFFFh         | 38000h-3FFFFh          |

| 9  | 64               | 60000h-6FFFFh         | 30000h-37FFFh          |

| 8  | 64               | 50000h-5FFFFh         | 28000h-2FFFFh          |

| 7  | 64               | 40000h-4FFFFh         | 20000h-27FFFh          |

| 6  | 64               | 30000h-3FFFFh         | 18000h-1FFFFh          |

| 5  | 64               | 20000h-2FFFFh         | 10000h-17FFFh          |

| 4  | 64               | 10000h-1FFFFh         | 08000h-0FFFFh          |

| 3  | 32               | 08000h-0FFFFh         | 04000h-07FFFh          |

| 2  | 8                | 06000h-07FFFh         | 03000h-03FFFh          |

| 1  | 8                | 04000h-05FFFh         | 02000h-02FFFh          |

| 0  | 16               | 00000h-03FFFh         | 00000h-01FFFh          |

## Revision history

**Table 21. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 1999   |          | First Issue                                                                                                                                                                                                                                                                                                                                                                  |

| 09/21/99    |          | Chip Erase Max. specification added ( <a href="#">Table 8.</a> )<br>Block Erase Max. specification added ( <a href="#">Table 8.</a> )<br>Program Max. specification added ( <a href="#">Table 8.</a> )<br>Chip Program Max. specification added ( <a href="#">Table 8.</a> )<br>I <sub>CC1</sub> and I <sub>CC3</sub> Typ. specification added ( <a href="#">Table 11.</a> ) |

| 10/04/99    |          | I <sub>CC3</sub> Test Condition change ( <a href="#">Table 11.</a> )                                                                                                                                                                                                                                                                                                         |

| 07/28/00    | 1.1      | New document template<br>Document type: from Preliminary Data to Data Sheet<br>Status Register bit DQ5 clarification<br>Data Polling Flowchart diagram change ( <a href="#">Figure 4.</a> )<br>Data Toggle Flowchart diagram change ( <a href="#">Figure 5.</a> )                                                                                                            |

| 19-Sep-2005 | 2.0      | Table 18. Ordering Information Scheme: standard package added and ECOPACK version added for both standard package and Tape & Reel packing.<br>TSOP48 Mechanical Data updated. SO44 525mm width changed to 500mm width.                                                                                                                                                       |

| 20-Jul-2006 | 3        | Document converted to new ST template. Small text changes.<br><a href="#">Figure 12: TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20mm, package outline</a> updated.                                                                                                                                                                                                    |

| 12-Dec-2006 | 4        | Updated <a href="#">Table 18: Ordering information scheme.</a>                                                                                                                                                                                                                                                                                                               |