## TVP5147M1PFP

NTSC/PAL/SECAM 2×10-Bit Digital Video Decoder With Macrovision ™ Detection, YPbPr Inputs, and 5-Line Comb Filter

# Data Manual

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated

### **Contents**

| 1.1       Detailed Functionality       2         1.2       TVP5147M1 Applications       3         1.3       Related Products       3         1.4       Ordering Information       3         1.5       Functional Block Diagram       4         1.6       Terminal Assignments       5         1.7       Terminal Functions       6         2       Functional Description       9         2.1       Analog Processing and A/D Converters       5         2.1.1       Video Input Switch Control       6         2.1.2       Analog Input Clamping       10         2.1.3       Automatic Gain Control       10         2.1.4       Analog Video Output       10         2.1.5       A/D Converters       10         2.2.1       A Converters       10         2.2.2       Digital Video Processing       11         2.2.2       Zy Decimation Filter       11         2.2.2       Zy Decimation Filter       11         2.2.2       Zy Decimation Filter       11         2.2.2       Composite Processor       11         2.2.3       Luminance Processing       14         2.2.4       Coor Transient Improvement                                                                                                                      | Se | ection |                      |                                                  | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------|----------------------|--------------------------------------------------|------|

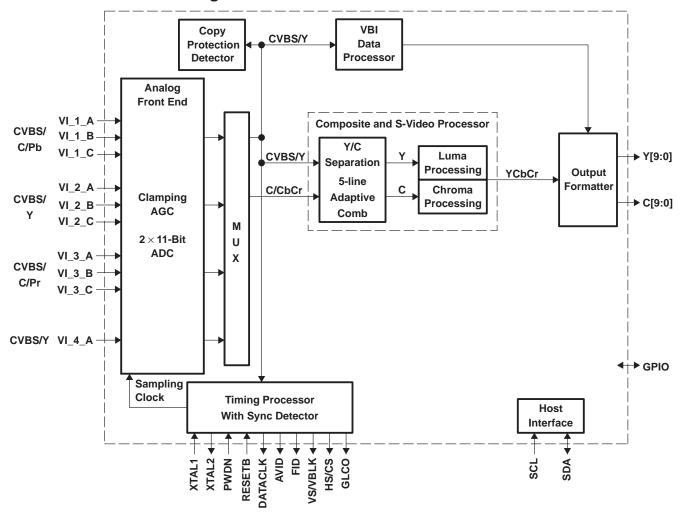

| 1.2       TVP5147M1 Applications       3         1.3       Related Products       3         1.4       Ordering Information       3         1.5       Functional Block Diagram       4         1.6       Terminal Assignments       5         1.7       Terminal Functions       6         2 Functional Description       9         2.1       Analog Processing and A/D Converters       9         2.1.1       Video Input Switch Control       9         2.1.2       Analog Input Clamping       10         2.1.3       Automatic Gain Control       10         2.1.4       Analog Video Output       10         2.1.5       A/D Converters       10         2.2       Digital Video Processing       11         2.2.1       2 Decimation Filter       11         2.2.2       Composite Processor       11         2.2.2       2 Composite Processing       14         2.2.2       2 Composite Processing       14         2.2.2       2 Composite Processing       14         2.2.2       2 Composite Processing       15         2.2.3       Luminance Processing       16         2.2.1       2 Color Transient Improvement                                                                                                           | 1  | Introd | uction               |                                                  | 1    |

| 1.3       Related Products       3         1.4       Ordering Information       3         1.5       Functional Blosko Diagram       4         1.6       Terminal Functions       5         1.7       Terminal Functions       6         2 Functional Description       9         2.1       Analog Processing and A/D Converters       9         2.1.1       Video Input Switch Control       9         2.1.2       Analog Input Clamping       10         2.1.3       Automatic Gain Control       10         2.1.4       Analog Video Output       10         2.1.5       A/D Converters       10         2.2.1       A Decimation Filter       11         2.2.1       2.2       Digital Video Processing       11         2.2.1       2.2       Decimation Filter       11         2.2.2.1       2.2       Decimation Filter       11         2.2.2.2       Composite Processor       11         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5 <td></td> <td>1.1</td> <td>Detailed</td> <td>d Functionality</td> <td>2</td>                                              |    | 1.1    | Detailed             | d Functionality                                  | 2    |

| 1.4       Ordering Information       3.6         1.5       Functional Block Diagram       4.6         1.6       Terminal Assignments       5.6         1.7       Terminal Functions       6.7         2 Functional Description       9.7         2.1       Analog Processing and A/D Converters       9.7         2.1.1       Video Input Switch Control       9.7         2.1.2       Analog Input Clamping       10.7         2.1.3       Automatic Gain Control       10.7         2.1.4       Analog Video Output       10.7         2.1.5       A/D Converters       10.7         2.2       Digital Video Processing       11.7         2.2.1       2.9 Decimation Filter       11.7         2.2.2       Composite Processor       11.7         2.2.3       Luminance Processing       11.7         2.2.3       Luminance Processing       14.7         2.2.4       Color Transient Improvement       14.7         2.3       Clock Circuits       15.7         2.4       Real-Time Control (RTC)       15.7         2.5       Output Formatter       15.7         2.5       Output Formatter       15.7         2.5       2 Em                                                                                                      |    | 1.2    | TVP514               | 47M1 Applications                                | 3    |

| 1.4       Ordering Information       3.1         1.5       Functional Block Diagram       4.6         1.7       Terminal Assignments       5.6         2       Functional Description       9.7         2.1       Analog Processing and A/D Converters       9.7         2.1.1       Video Input Switch Control       9.7         2.1.2       Analog Input Clamping       10.7         2.1.3       Automatic Gain Control       10.7         2.1.4       Analog Video Output       10.7         2.1.5       A/D Converters       10.7         2.2       Digital Video Processing       11.7         2.2.1       2y Decimation Filter       11.7         2.2.2       Composite Processor       11.7         2.2.3       Luminance Processing       14.7         2.2.3       Luminance Processing       14.7         2.2.4       Color Transient Improvement       14.7         2.3       Clock Circuits       15.7         2.4       Real-Time Control (RTC)       15.7         2.5       Output Formatter       15.7         2.5       Output Formatter       15.7         2.5       Output Formatter       15.7         2.5                                                                                                             |    | 1.3    | Related              | Products                                         | 3    |

| 1.5       Functional Block Diagram       4         1.6       Terminal Assignments       5         1.7       Terminal Functions       6         2       Functional Description       9         2.1       Analog Processing and A/D Converters       9         2.1.1       Video Input Switch Control       9         2.1.2       Analog Input Clamping       10         2.1.3       Automatic Gain Control       10         2.1.4       Analog Video Output       10         2.1.5       A/D Converters       10         2.2.1       20 Poigital Video Processing       11         2.2.2       2.2       Description       11         2.2.2.1       20 Poetimation Filter       11         2.2.2       2.0       Processing       11         2.2.2.1       2.0       Processor       11         2.2.2.2       2.0       Processor       11         2.2.3       Luminance Processing       14         2.2.4       Rolar Time Control (RTC)       15         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       2       Embedded Syncs       21                                                                                                                                         |    | 1.4    |                      |                                                  | 3    |

| 1.6       Terminal Functions       5.5         1.7       Terminal Functions       6.7         2       Functional Description       9.8         2.1.1       Analog Processing and A/D Converters       9.2         2.1.1       Video Input Switch Control       9.1         2.1.2       Analog Input Clamping       10.1         2.1.3       Automatic Gain Control       10.2         2.1.4       Analog Video Output       10.2         2.1.5       A/D Converters       10.2         2.1.5       A/D Converters       10.2         2.2.1       2y Decimation Filter       11.2         2.2.2       Composite Processing       11.2         2.2.2       Composite Processor       11.2         2.2.2       Composite Processing       14.2         2.2.1       Color Transient Improvement       14.2         2.2.2       Color Transient Improvement       14.2         2.3       Clock Circuits       15.2         2.4       Real-Time Control (RTC)       15.2         2.5       Deparate Syncs       16.2         2.5       2.1       Separate Syncs       16.2         2.5       2.5       2.5       2.5                                                                                                                           |    | 1.5    |                      |                                                  | 4    |

| 1.7       Terminal Functions       6         2 Functional Description       9         2.1       Analog Processing and A/D Converters       9         2.1.1       Video Input Switch Control       9         2.1.2       Analog Input Clamping       10         2.1.3       Automatic Gain Control       10         2.1.4       Analog Video Output       10         2.1.5       A/D Converters       10         2.2       Digital Video Processing       11         2.2.1       2y Decimation Filter       11         2.2.2       Composite Processor       11         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Lucities       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5       2.5       Embedded Syncs       16         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6       1/2 Host Interface       21         2.6.1       Reset and Interface       22         2.6.2       1/2 Operation       22                                                                                                                                       |    | 1.6    |                      |                                                  | 5    |

| 2 Functional Description         9           2.1 Analog Processing and A/D Converters         9           2.1.1 Video Input Switch Control         9           2.1.2 Analog Input Clamping         10           2.1.3 Automatic Gain Control         10           2.1.4 Analog Video Output         10           2.1.5 A/D Converters         10           2.2. Digital Video Processing         11           2.2.1 2y Decimation Filter         11           2.2.2 Composite Processor         11           2.2.2 Composite Processing         14           2.2.2 Composite Processing         14           2.2.2 Control (RTC)         15           2.3 Clock Circuits         16           2.4 Real-Time Control (RTC)         15           2.5 Output Formatter         15           2.5 Output Formatter         16           2.5.1 Separate Syncs         16           2.5.2 Embedded Syncs         21           2.6.1 Pest Interface         22           2.6.2 IPC Operation         22           2.6.3 VBUS Access         22           2.7.1 VBI FIFO and Ancillary Data in Video Stream         25           2.7.2 VBI Raw Data Output         26           2.8 Reset and Initialization         26                           |    |        |                      |                                                  | 6    |

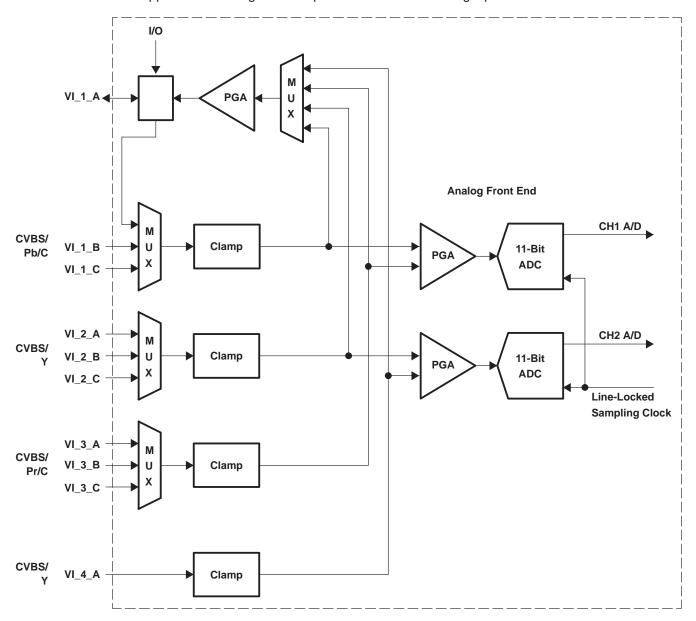

| 2.1       Analog Processing and A/D Converters       2         2.1.1       Video Input Switch Control       9         2.1.2       Analog Input Clamping       10         2.1.3       Automatic Gain Control       10         2.1.4       Analog Video Output       10         2.1.5       A/D Converters       10         2.2.1       2 V Decimation Filter       11         2.2.2       2 Digital Video Processing       11         2.2.1       2 V Decimation Filter       11         2.2.2       2 Composite Processor       11         2.2.3       Luminance Processing       14         2.2.2       2 Composite Processor       11         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs                                                                                                                           | 2  |        |                      |                                                  |      |

| 2.1.1       Video Input Switch Control       9         2.1.2       Analog Input Clamping       10         2.1.3       Automatic Gain Control       10         2.1.4       Analog Video Output       10         2.1.5       A/D Converters       10         2.2       Digital Video Processing       11         2.2.1       2y Decimation Filter       11         2.2.2       Composite Processor       11         2.2.2       Composite Processor       11         2.2.2       Coor Transient Improvement       14         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.1       Separate Syncs       16         2.5.1       Separate Syncs       21         2.6.1       Reset and Interface       21         2.6.1       Reset and Interface       22         2.6.2       I <sup>2</sup> C Operation       22         2.6.3       VBUS Access       22                                                                                                                            | _  |        |                      | ·                                                |      |

| 2.1.2       Analog İnput Clamping       10         2.1.3       Automatic Gain Control       10         2.1.4       Analog Video Output       10         2.1.5       A/D Converters       10         2.2. Digital Video Processing       11         2.2.1       2y Decimation Filter       11         2.2.1       2y Decimation Filter       11         2.2.2       Composite Processor       11         2.2.1       2 Up Composite Processor       11         2.2.2       Composite Processor       11         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6       1/2 Host Interface       21         2.6.1       Reset and I2C Bus Address Selection       22      <                                                                                                                             |    | 2.1    | _                    |                                                  |      |

| 2.1.3       Automatic Gain Control       10         2.1.4       Analog Video Output       10         2.1.5       A/D Converters       10         2.2       Digital Video Processing       11         2.2.1       2y Decimation Filter       11         2.2.2       Composite Processor       11         2.2.3       Luminance Processing       14         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.1       Separate Syncs       16         2.5.1       Separate Syncs       21         2.5.1       Reset and Initraface       21         2.6.1       Reset and Initraface       22         2.6.1       Reset and Packet and Syncs       22         2.7       VBI Data Processor       22         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization </td <td></td> <td></td> <td></td> <td>·</td> <td></td>                                                         |    |        |                      | ·                                                |      |

| 2.1.4       Analog Video Output       10         2.1.5       A/D Converters       10         2.2       Digital Video Processing       11         2.2.1       2y Decimation Filter       11         2.2.2       Composite Processor       11         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.5.1       Separate Syncs       21         2.5.2       Embedded Syncs       22         2.6.1       Reset and IPC Bus Address Selection       22         2.6.2       I <sup>2</sup> C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       22         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       <                                                                                                         |    |        |                      |                                                  |      |

| 2.1.5       A/D Converters       10         2.2       Digital Video Processing       11         2.2.1       2y Decimation Filter       11         2.2.2       Composite Processor       11         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5       Output Formatter       16         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6       I <sup>2</sup> C Host Interface       21         2.6.1       Reset and I <sup>2</sup> C Bus Address Selection       22         2.6.2       I <sup>2</sup> C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       22         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Register </td <td></td> <td></td> <td>_</td> <td></td> <td></td>                        |    |        | _                    |                                                  |      |

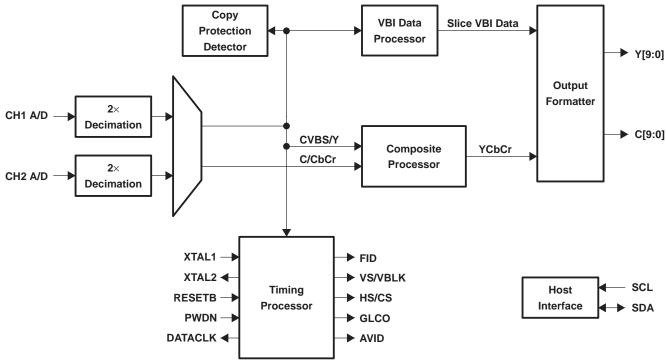

| 2.2       Digital Video Processing       11         2.2.1       2y Decimation Filter       11         2.2.2       Composite Processor       11         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6.1       Reset and IPC Bus Address Selection       22         2.6.2       I²C Operation       22         2.6.2       I²C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       26         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.2       AFE Gain Control R                                                                                                               |    |        |                      | ·                                                |      |

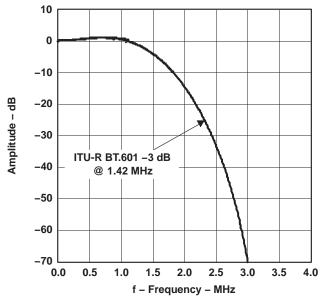

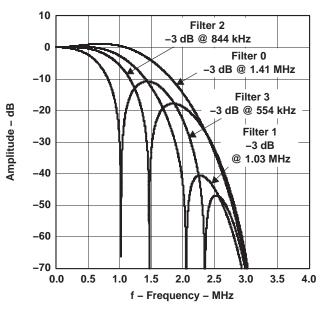

| 2.2.1       2y Decimation Filter       11         2.2.2       Composite Processor       11         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6.1       Reset and I <sup>2</sup> C Bus Address Selection       22         2.6.1       Reset and I <sup>2</sup> C Bus Address Selection       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       33         2.11.2       AFE Gain Control Register       32         2                                                                                |    | 0.0    | _                    |                                                  |      |

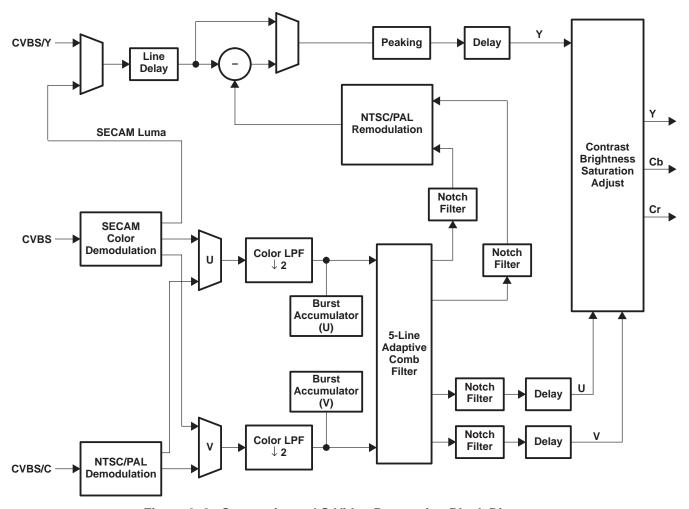

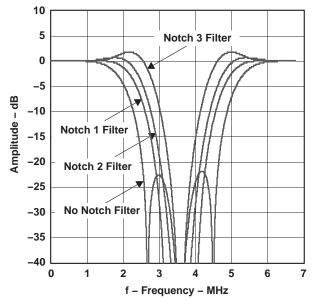

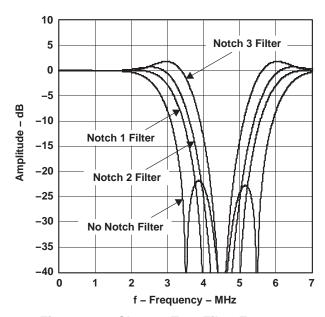

| 2.2.2       Composite Processor       11         2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6       I²C Host Interface       21         2.6.1       Reset and I²C Bus Address Selection       22         2.6.2       I²C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       32         2.11.3       Video Standard                                                                                                               |    | 2.2    | •                    |                                                  |      |

| 2.2.3       Luminance Processing       14         2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6       I <sup>2</sup> C Host Interface       21         2.6.1       Reset and I <sup>2</sup> C Bus Address Selection       22         2.6.2       I <sup>2</sup> C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       32         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       33         2.11.4 <t< td=""><td></td><td></td><td>·</td><td></td></t<>                              |    |        |                      | ·                                                |      |

| 2.2.4       Color Transient Improvement       14         2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6       I²C Host Interface       21         2.6.1       Reset and I²C Bus Address Selection       22         2.6.2       I²C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       32         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6 <td< td=""><td></td><td></td><td></td><td>•</td><td></td></td<>                                                     |    |        |                      | •                                                |      |

| 2.3       Clock Circuits       15         2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6       I²C Host Interface       21         2.6.1       Reset and I²C Bus Address Selection       22         2.6.2       I²C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       32         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Co                                                                                                               |    |        |                      |                                                  |      |

| 2.4       Real-Time Control (RTC)       15         2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6       I²C Host Interface       21         2.6.1       Reset and I²C Bus Address Selection       22         2.6.2       I²C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       32         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7                                                                                                              |    |        |                      | ·                                                |      |

| 2.5       Output Formatter       15         2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6       I²C Host Interface       21         2.6.1       Reset and I²C Bus Address Selection       22         2.6.2       I²C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34                                                                                                          |    |        |                      |                                                  |      |

| 2.5.1       Separate Syncs       16         2.5.2       Embedded Syncs       21         2.6       I²C Host Interface       21         2.6.1       Reset and I²C Bus Address Selection       22         2.6.2       I²C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35 <td></td> <td>2.4</td> <td>Real-Tir</td> <td>me Control (RTC)</td> <td>15</td> |    | 2.4    | Real-Tir             | me Control (RTC)                                 | 15   |

| 2.5.2       Embedded Syncs       21         2.6       I²C Host Interface       21         2.6.1       Reset and I²C Bus Address Selection       22         2.6.2       I²C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       32         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Regi                                                                   |    | 2.5    | Output I             | Formatter                                        | 15   |

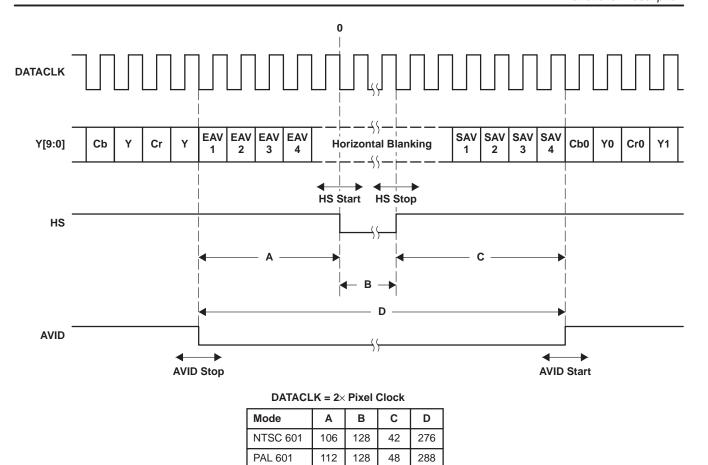

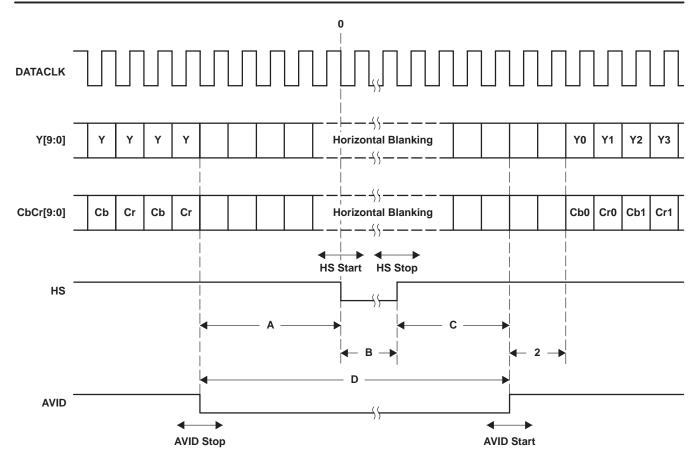

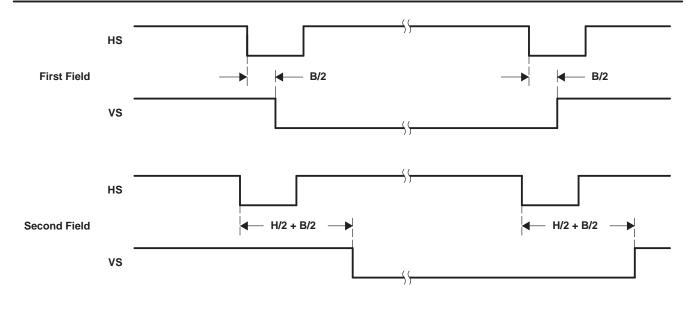

| 2.6       I²C Host Interface       21         2.6.1       Reset and I²C Bus Address Selection       22         2.6.2       I²C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       32         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                  |    |        | 2.5.1                | Separate Syncs                                   | 16   |

| 2.6.1       Reset and I <sup>2</sup> C Bus Address Selection       22         2.6.2       I <sup>2</sup> C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                      |    |        | 2.5.2                | Embedded Syncs                                   | 21   |

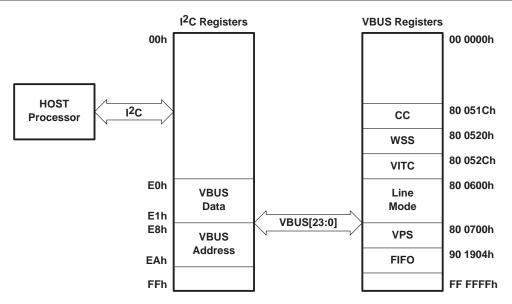

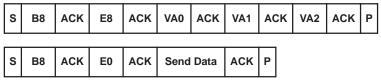

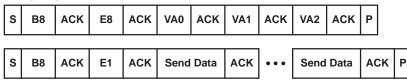

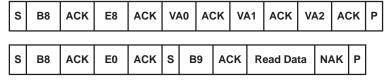

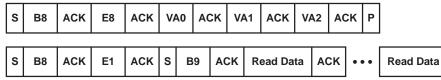

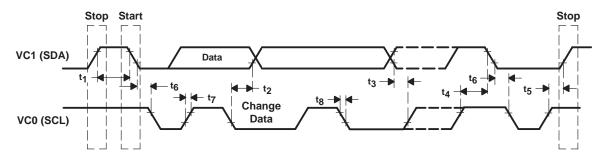

| 2.6.2       I <sup>2</sup> C Operation       22         2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                    |    | 2.6    | I <sup>2</sup> C Hos | st Interface                                     | 21   |

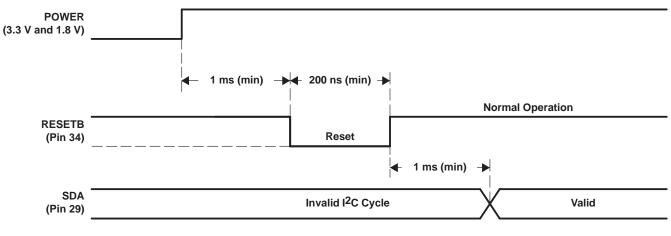

| 2.6.3       VBUS Access       22         2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                            |    |        | 2.6.1                | Reset and I <sup>2</sup> C Bus Address Selection | 22   |

| 2.7       VBI Data Processor       24         2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                     |    |        | 2.6.2                | I <sup>2</sup> C Operation                       | 22   |

| 2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                   |    |        | 2.6.3                | VBUS Access                                      | 22   |

| 2.7.1       VBI FIFO and Ancillary Data in Video Stream       25         2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                   |    | 2.7    | VBI Dat              | a Processor                                      | 24   |

| 2.7.2       VBI Raw Data Output       26         2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                                                                                            |    |        |                      |                                                  | 25   |

| 2.8       Reset and Initialization       26         2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |        | 2.7.2                | ·                                                | 26   |

| 2.9       Adjusting External Syncs       27         2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 2.8    | Reset a              | ·                                                | 26   |

| 2.10       Internal Control Registers       27         2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | _      |                      |                                                  | 27   |

| 2.11       Register Definitions       31         2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |        | -                    |                                                  |      |

| 2.11.1       Input Select Register       31         2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |        |                      | · · · · · · · · · · · · · · · · · · ·            |      |

| 2.11.2       AFE Gain Control Register       32         2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 2      | -                    |                                                  |      |

| 2.11.3       Video Standard Register       32         2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |        |                      |                                                  |      |

| 2.11.4       Operation Mode Register       33         2.11.5       Autoswitch Mask Register       33         2.11.6       Color Killer Register       34         2.11.7       Luminance Processing Control 1 Register       34         2.11.8       Luminance Processing Control 2 Register       35         2.11.9       Luminance Processing Control 3 Register       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |        |                      |                                                  |      |

| 2.11.5Autoswitch Mask Register332.11.6Color Killer Register342.11.7Luminance Processing Control 1 Register342.11.8Luminance Processing Control 2 Register352.11.9Luminance Processing Control 3 Register35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |        |                      |                                                  |      |

| 2.11.6Color Killer Register342.11.7Luminance Processing Control 1 Register342.11.8Luminance Processing Control 2 Register352.11.9Luminance Processing Control 3 Register35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |        |                      |                                                  |      |

| 2.11.7Luminance Processing Control 1 Register342.11.8Luminance Processing Control 2 Register352.11.9Luminance Processing Control 3 Register35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |        |                      |                                                  |      |

| 2.11.8Luminance Processing Control 2 Register352.11.9Luminance Processing Control 3 Register35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |        | _                    |                                                  |      |

| 2.11.9 Luminance Processing Control 3 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |        |                      |                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |        |                      |                                                  |      |

| 2.11.10 Luminance Brightness Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |        |                      |                                                  | 35   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |        | 2.11.10              | Luminance Brightness Register                    | 35   |

| Section |         |                                           | Page     |

|---------|---------|-------------------------------------------|----------|

|         | 2.11.11 | Luminance Contrast Register               | 36       |

|         | 2.11.12 | Chrominance Saturation Register           | 36       |

|         | 2.11.13 | Chroma Hue Register                       | 36       |

|         | 2.11.14 | Chrominance Processing Control 1 Register | 36       |

|         | 2.11.15 | Chrominance Processing Control 2 Register | 37       |

|         | 2.11.16 | AVID Start Pixel Register                 | 37       |

|         | 2.11.17 | AVID Stop Pixel Register                  | 38       |

|         | 2.11.18 | HSYNC Start Pixel Register                | 38       |

|         | 2.11.19 | HSYNC Stop Pixel Register                 | 38       |

|         | 2.11.20 | VSYNC Start Line Register                 | 38       |

|         | 2.11.21 | VSYNC Stop Line Register                  | 39       |

|         | 2.11.22 | VBLK Start Line Register                  | 39       |

|         | 2.11.23 | VBLK Stop Line Register                   | 39       |

|         | 2.11.24 | CTI Delay Register                        | 39       |

|         | 2.11.25 | CTI Control Register                      | 40       |

|         | 2.11.26 | Sync Control Register                     | 40       |

|         | 2.11.27 | Output Formatter 1 Register               | 41       |

|         | 2.11.28 | Output Formatter 2 Register               | 41       |

|         | 2.11.29 | Output Formatter 3 Register               | 42       |

|         | 2.11.30 | Output Formatter 4 Register               | 43       |

|         | 2.11.31 | Output Formatter 5 Register               | 44       |

|         | 2.11.32 | Output Formatter 6 Register               | 45       |

|         | 2.11.33 | Clear Lost Lock Detect Register           | 45       |

|         | 2.11.34 | Status 1 Register                         | 46       |

|         | 2.11.35 | Status 2 Register                         | 47       |

|         | 2.11.36 | AGC Gain Status Register                  | 47       |

|         | 2.11.37 | Video Standard Status Register            | 48       |

|         | 2.11.38 | GPIO Input 1 Register                     | 48       |

|         | 2.11.39 | GPIO Input 2 Register                     | 49       |

|         | 2.11.40 | AFE Coarse Gain for CH 1 Register         | 50       |

|         | 2.11.41 | AFE Coarse Gain for CH 2 Register         | 50       |

|         | 2.11.42 | AFE Coarse Gain for CH 3 Register         | 51       |

|         | 2.11.42 | AFE Coarse Gain for CH 4 Register         | 51       |

|         | 2.11.44 | AFE Fine Gain for Pb Register             | 52       |

|         | 2.11.45 | AFE Fine Gain for Y_Chroma Register       | 52       |

|         | 2.11.46 | AFE Fine Gain for Pr Register             | 52       |

|         | 2.11.40 | AFE Fine Gain for CVBS_Luma Register      | 53       |

|         | 2.11.47 |                                           | 53       |

|         | 2.11.49 | Field ID Control Register                 | 54       |

|         | 2.11.49 | F-bit and V-bit Control 1 Register        | 55       |

|         |         | Back-End AGC Control Register             |          |

|         | 2.11.51 | AGC Decrement Speed Control Register      | 55<br>55 |

|         | 2.11.52 | ROM Version Register                      | 55<br>50 |

|         | 2.11.53 | AGC White Peak Processing Register        | 56       |

|         | 2.11.54 | F and V Bit Control Register              | 57<br>50 |

|         | 2.11.55 | VCR Trick Mode Control Register           | 58       |

|         | 2.11.56 | Horizontal Shake Increment Register       | 58       |

|         | 2.11.57 | AGC Increment Speed Register              | 58       |

|         | 2.11.58 | AGC Increment Delay Register              | 58       |

|         |         |                                           |          |

| Se | ction |         |                                                          | Page |

|----|-------|---------|----------------------------------------------------------|------|

|    |       | 2.11.59 | Analog Output Control 1 Register                         | 59   |

|    |       | 2.11.60 | Chip ID MSB Register                                     | 59   |

|    |       | 2.11.61 | Chip ID LSB Register                                     | 59   |

|    |       | 2.11.62 | CPLL Speed Control Register                              | 59   |

|    |       | 2.11.63 | Status Request Register                                  | 60   |

|    |       | 2.11.64 | Vertical Line Count Register                             | 60   |

|    |       | 2.11.65 | AGC Decrement Delay Register                             | 60   |

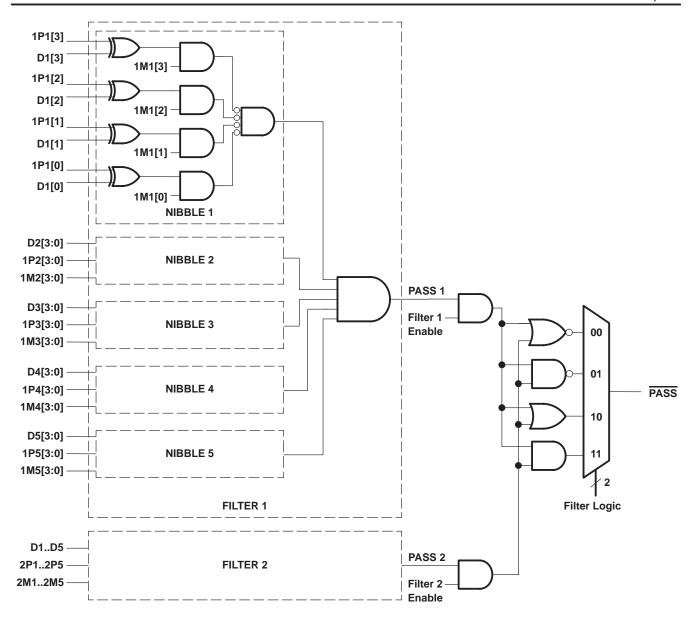

|    |       | 2.11.66 | VDP TTX Filter And Mask Registers                        | 61   |

|    |       | 2.11.67 | VDP TTX Filter Control Register                          | 62   |

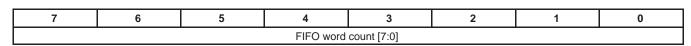

|    |       | 2.11.68 | VDP FIFO Word Count Register                             | 63   |

|    |       | 2.11.69 | VDP FIFO Interrupt Threshold Register                    | 64   |

|    |       | 2.11.70 | VDP FIFO Reset Register                                  | 64   |

|    |       | 2.11.71 | VDP FIFO Output Control Register                         | 64   |

|    |       | 2.11.72 | VDP Line Number Interrupt Register                       | 64   |

|    |       | 2.11.73 | VDP Pixel Alignment Register                             | 65   |

|    |       | 2.11.74 | VDP Line Start Register                                  | 65   |

|    |       | 2.11.75 | VDP Line Stop Register                                   | 65   |

|    |       | 2.11.76 | VDP Global Line Mode Register                            | 65   |

|    |       | 2.11.77 | VDP Full Field Enable Register                           | 66   |

|    |       | 2.11.78 | VDP Full Field Mode Register                             | 66   |

|    |       | 2.11.79 | VBUS Data Access With No VBUS Address Increment Register | 66   |

|    |       | 2.11.80 | VBUS Data Access With VBUS Address Increment Register    | 66   |

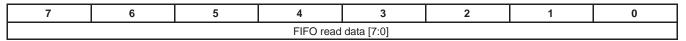

|    |       | 2.11.81 | FIFO Read Data Register                                  | 67   |

|    |       | 2.11.82 | VBUS Address Access Register                             | 67   |

|    |       | 2.11.83 | Interrupt Raw Status 0 Register                          | 67   |

|    |       | 2.11.84 | Interrupt Raw Status 1 Register                          | 68   |

|    |       | 2.11.85 | Interrupt Status 0 Register                              | 68   |

|    |       | 2.11.86 | Interrupt Status 1 Register                              | 69   |

|    |       | 2.11.87 | Interrupt Mask 0 Register                                | 70   |

|    |       | 2.11.88 | Interrupt Mask 1 Register                                | 71   |

|    |       | 2.11.89 | Interrupt Clear 0 Register                               | 71   |

|    |       | 2.11.90 | Interrupt Clear 1 Register                               | 72   |

|    | 2.12  |         | egister Definitions                                      | 73   |

|    |       | 2.12.1  | VDP Closed Caption Data Register                         | 73   |

|    |       | 2.12.2  | VDP WSS Data Register                                    | 73   |

|    |       | 2.12.3  | VDP VITC Data Register                                   | 74   |

|    |       | 2.12.4  | VDP V-Chip TV Rating Block 1 Register                    | 74   |

|    |       | 2.12.5  | VDP V-Chip TV Rating Block 2 Register                    | 74   |

|    |       | 2.12.6  | VDP V-Chip TV Rating Block 3 Register                    | 75   |

|    |       | 2.12.7  | VDP V-CHIP MPAA Rating Data Register                     | 75   |

|    |       | 2.12.8  | VDP General Line Mode and Line Address Register          | 76   |

|    |       | 2.12.9  | VDP VPS/Gemstar Data Register                            | 77   |

|    |       | 2.12.10 | Analog Output Control 2 Register                         | 78   |

| _  |       | 2.12.11 | Interrupt Configuration Register                         | 78   |

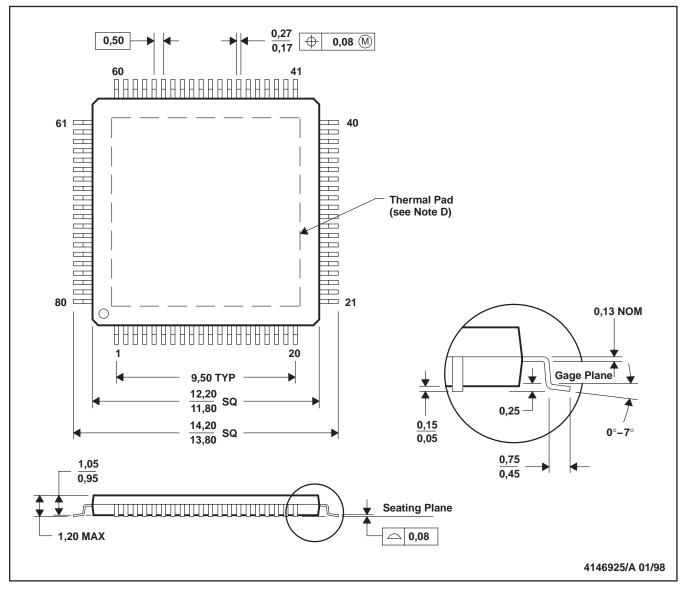

| 3  |       |         | fications                                                | 79   |

|    | 3.1   |         | Maximum Ratings†                                         | 79   |

|    | 3.2   |         | ended Operating Conditions                               | 79   |

|    |       | 3.2.1   | Crystal Specifications                                   | 79   |

#### Contents

| Se | ection |                                  |                                      | Page |  |  |  |  |

|----|--------|----------------------------------|--------------------------------------|------|--|--|--|--|

|    | 3.3    | Electric                         | al Characteristics                   | 80   |  |  |  |  |

|    |        | 3.3.1                            | DC Electrical Characteristics        | 80   |  |  |  |  |

|    |        | 3.3.2                            | Analog Processing and A/D Converters | 80   |  |  |  |  |

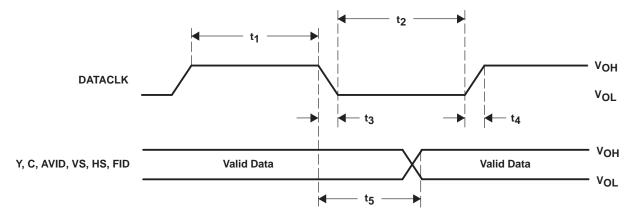

|    |        | 3.3.3                            | Timing                               | 81   |  |  |  |  |

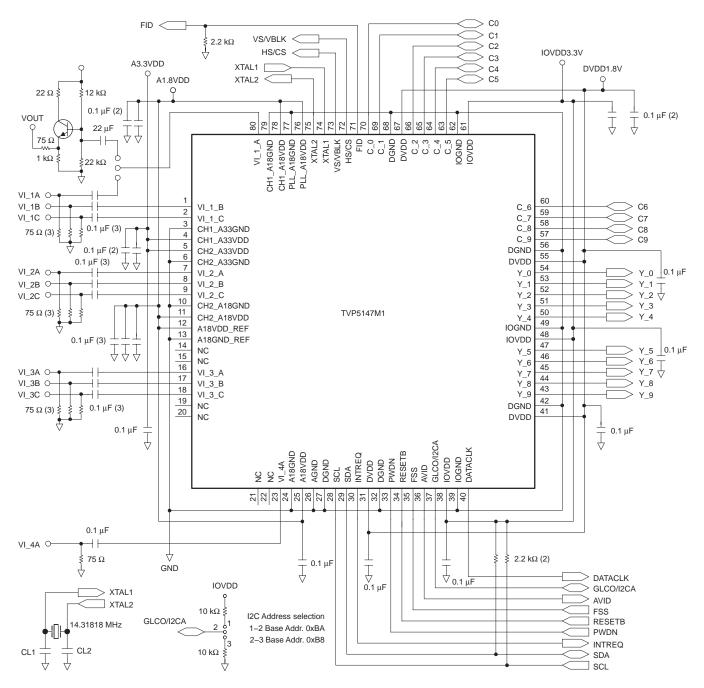

| 4  | Exam   | ple Regis                        | ster Settings                        | 83   |  |  |  |  |

|    | 4.1    | Exampl                           | e 1                                  | 83   |  |  |  |  |

|    |        | 4.1.1                            | Assumptions                          | 83   |  |  |  |  |

|    |        | 4.1.2                            | Recommended Settings                 | 83   |  |  |  |  |

|    | 4.2    | Exampl                           | e 2                                  | 83   |  |  |  |  |

|    |        | 4.2.1                            | Assumptions                          | 83   |  |  |  |  |

|    |        | 4.2.2                            | Recommended Settings                 | 83   |  |  |  |  |

|    | 4.3    | Exampl                           | e 3                                  | 84   |  |  |  |  |

|    |        | 4.3.1                            | Assumptions                          | 84   |  |  |  |  |