# MOS INTEGRATED CIRCUIT $\mu$ PD75402A(A)

## 4 BIT SINGLE-CHIP MICROCOMPUTER

The  $\mu$ PD75402A(A) is a CMOS single-chip microcomputer which uses the 75X series architecture. It operates at high speed with a minimum instruction execution time of 0.95  $\mu$ s.

The  $\mu$ PD75P402 is also available for system development evaluation. It contains one-time PROM instead of mask ROM used in the  $\mu$ PD75402A(A).

The following user's manual describes the details of the functions of the  $\mu$ PD75402A(A). Be sure to read it before designing an application system.

μPD75402A User's Manual: IEU-644

#### **FEATURES**

- More reliable than the  $\mu$ PD75402A

- High-speed operation with a minimum instruction execution time of 0.95  $\mu$ s (when the microcomputer operates at 4.19 MHz)

- Low voltage and low-speed instruction execution time of 15.3  $\mu$ s (when the microcomputer operates at 4.19 MHz)

- · Memory mapping by on-chip peripheral hardware

- · NEC standard serial bus interface (SBI)

- 8-bit basic interval timer (watchdog timer applicable)

- · Interrupt function

- Three vectored interrupts (one external and two internal interrupts)

- · One external test input

- Clock output function (remote controller output applicable)

- Capable of specifying the incorporation of 16 pull-up resistors by software

#### **APPLICATIONS**

Electronic units for automobiles, and suchlike

#### ORDERING INFORMATION

| Part number                                      | Package                                | Quality grade |

|--------------------------------------------------|----------------------------------------|---------------|

| $\mu$ PD75402AC(A)- $\times\!\!\times\!\!\times$ | 28-pin plastic DIP (600 mil)           | Special       |

| $\mu$ PD75402ACT(A)- $\times\!\!\times\!\!$      | 28-pin plastic shrink DIP (400 mil)    | Special       |

| $\mu$ PD75402AGB(A)- $\times$ $\times$ -3B4      | 44-pin plastic QFP (10 $\times$ 10 mm) | Special       |

Remark xxx indicates the ROM code number.

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

The information in this document is subject to change without notice.

# DIFFERENCES BETWEEN THE $\mu$ PD75402A(A) AND $\mu$ PD75402A

| Product       | μPD75402A(A) | μPD75402A |

|---------------|--------------|-----------|

| Quality grade | Special      | Standard  |

# **FUNCTIONAL OVERVIEW**

| Item                          |       | Function                                                                                                                                                                                                                                                         |  |

|-------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of basic instructions  |       | 37                                                                                                                                                                                                                                                               |  |

| Minimum instru execution time | ction | <ul> <li>0.95, 1.91, or 15.3 μs (when operating at 4.19 MHz)</li> <li>Switchable among three speeds</li> </ul>                                                                                                                                                   |  |

| Built-in                      | ROM   | 1920 × 8 bits                                                                                                                                                                                                                                                    |  |

| memory                        | RAM   | 64 × 4 bits                                                                                                                                                                                                                                                      |  |

| General register              | -     | 4 bits $\times$ 4 or 8 bits $\times$ 2 (memory mapping)                                                                                                                                                                                                          |  |

| I/O line                      |       | CMOS input ports : 6 lines     CMOS I/O ports : 12 lines (8 lines can drive the LED directly.)     N-ch open-drain I/O ports : 4 lines (All lines can drive the LED directly.)                                                                                   |  |

| Pull-up resistor              |       | <ul> <li>Capable of controlling the incorporation of 16 pull-up resistors by software</li> <li>Capable of controlling the incorporation of 4 pull-up resistors by mask option</li> </ul>                                                                         |  |

| Clock output                  |       | 1.05 MHz, 524 kHz, or 65.5 kHz (when operating at 4.19 MHz)     Applicable to remote controller output                                                                                                                                                           |  |

| Timer/counter                 |       | 8-bit basic interval timer (watchdog timer applicable)                                                                                                                                                                                                           |  |

| Serial interface              |       | 8 bits     Two transfer modes (three-wire synchronous mode and SBI mode)                                                                                                                                                                                         |  |

| Vectored interrupt            |       | One external and two internal interrupts                                                                                                                                                                                                                         |  |

| Test input                    |       | One external input (See Chapter 6 for details.)                                                                                                                                                                                                                  |  |

| Standby                       |       | STOP/HALT mode                                                                                                                                                                                                                                                   |  |

| Instruction set               |       | <ul> <li>Bit manipulation instructions (set, clear, test, and Boolean operation)</li> <li>1-byte relative branch instructions</li> <li>4-bit operation instructions (add, Boolean operation, and compare)</li> <li>4- and 8-bit transfer instructions</li> </ul> |  |

| Package                       |       | <ul> <li>28-pin plastic DIP (600 mil)</li> <li>28-pin plastic shrink DIP (400 mil)</li> <li>44-pin plastic QFP (10 × 10 mm)</li> </ul>                                                                                                                           |  |

# CONTENTS

| 1.  | PIN CONFIGURATION (TOP VIEW)                                          | 4  |

|-----|-----------------------------------------------------------------------|----|

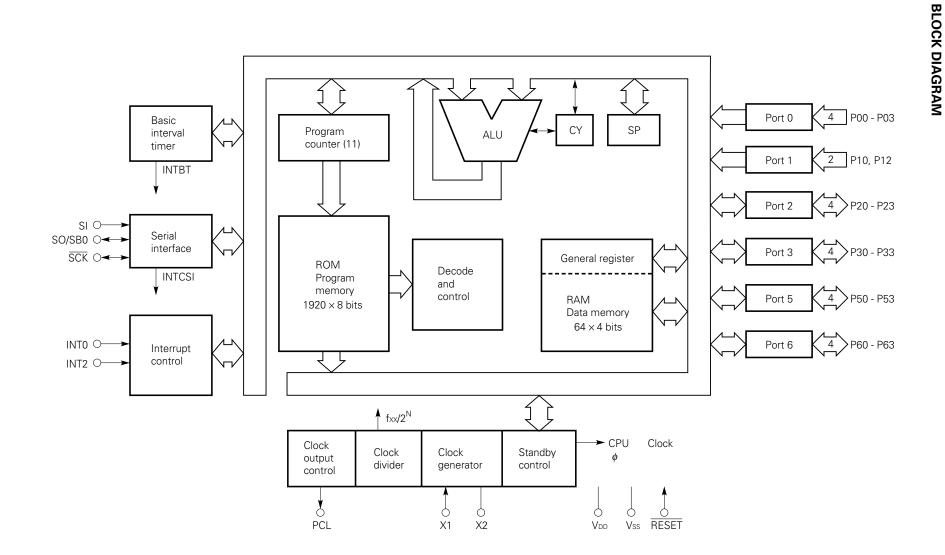

| 2.  | BLOCK DIAGRAM                                                         | 6  |

| 3.  | PIN FUNCTIONS                                                         | 7  |

|     | 3.1 PORT PINS                                                         | 7  |

|     | 3.2 NON-PORT PINS                                                     | 8  |

|     | 3.3 PIN INPUT/OUTPUT CIRCUITS                                         | 8  |

|     | 3.4 SELECTION OF A MASK OPTION                                        | 10 |

|     | 3.5 HANDLING UNUSED PINS                                              | 11 |

|     | 3.6 NOTES ON USING THE P00 AND RESET PINS                             | 11 |

| 4.  | MEMORY CONFIGURATION                                                  | 12 |

| 5.  | PERIPHERAL HARDWARE FUNCTIONS                                         | 14 |

|     | 5.1 PORTS                                                             | 14 |

|     | 5.2 CLOCK GENERATOR                                                   | 15 |

|     | 5.3 CLOCK OUTPUT CIRCUIT                                              | 16 |

|     | 5.4 BASIC INTERVAL TIMER                                              | 17 |

|     | 5.5 SERIAL INTERFACE                                                  | 18 |

| 6.  | INTERRUPT FUNCTION                                                    | 20 |

| 7.  | STANDBY FUNCTION                                                      | 22 |

| 8.  | RESET FUNCTION                                                        | 23 |

| 9.  | INSTRUCTION SET                                                       | 25 |

| 10. | ELECTRICAL CHARACTERISTICS                                            | 29 |

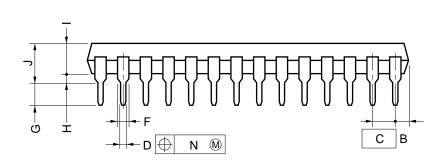

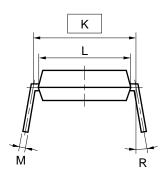

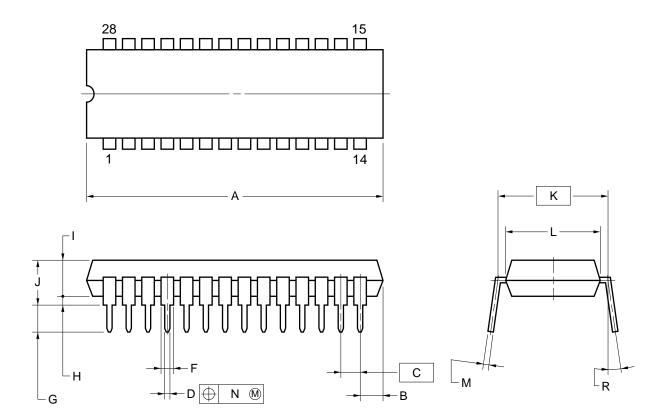

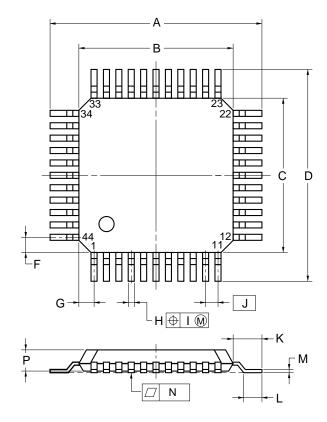

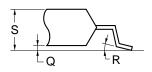

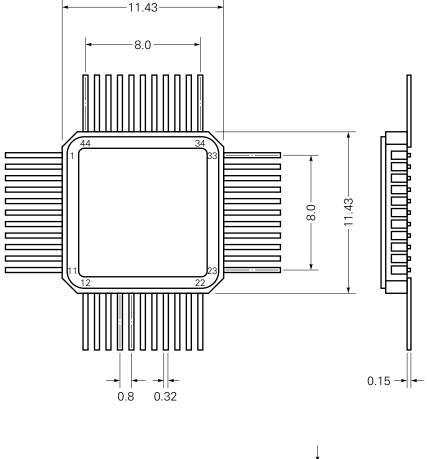

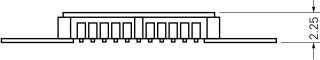

| 11. | PACKAGE DIMENSIONS                                                    | 38 |

| 12. | RECOMMENDED SOLDERING CONDITIONS                                      | 42 |

| AP  | PENDIX A DIFFERENCES BETWEEN THE $\mu$ PD75402A(A) AND $\mu$ PD75P402 | 43 |

| AP  | PENDIX B DEVELOPMENT TOOLS                                            | 44 |

| AP  | PENDIX C RELATED DOCUMENTS                                            | 45 |

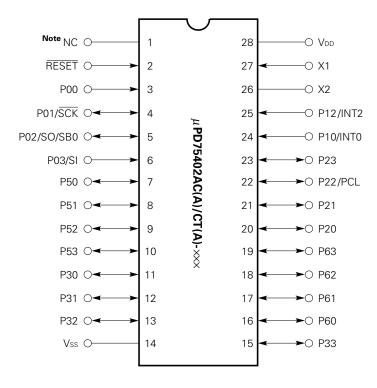

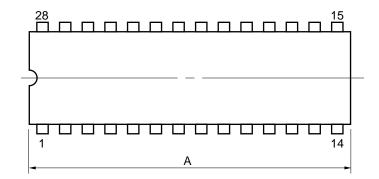

## 1. PIN CONFIGURATION (TOP VIEW)

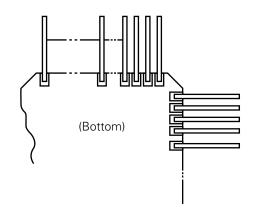

28-pin plastic DIP (600 mil), 28-pin plastic shrink DIP (400 mil)

P00 - P03 : Port 0  $\overline{SCK}$  : Serial clock I/O

P10 and P12: Port 1 SO/SB0 : Serial output/input-output

P50 - P53 : Port 5 INT0 : External vectored interrupt input

P60 - P63 : Port 6 INT2 : External test input

X1 and X2: Oscillating pins

RESET : Reset input

RESET : Reset input

VDD : Power supply

Vss : Ground

NC : No connection

**Note** When the  $\mu$ PD75402A(A) shares the printed circuit board with the  $\mu$ PD75P402, connect the NC pin directly to the Vss pin.

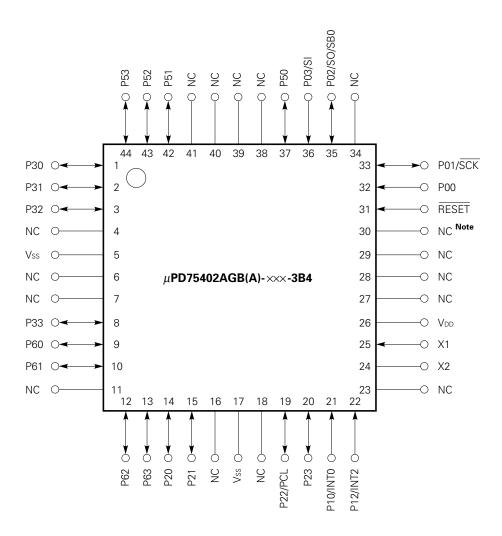

## 44-pin plastic QFP (10 $\times$ 10 mm)

Note When the  $\mu$ PD75402A(A) shares the printed circuit board with the  $\mu$ PD75P402, connect the NC pin (pin 30) directly to the Vss pin.

## 3. PIN FUNCTIONS

## 3.1 PORT PINS

| Pin       | I/O   | Dual-<br>function pin | Function                                                                                                                                                                                                     |  |

|-----------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P00       | Input | _                     | 4-bit input port (port 0)                                                                                                                                                                                    |  |

| P01       | I/O   | SCK                   | P01 to P03 allow the connection of built-in pull-up resistors to be                                                                                                                                          |  |

| P02       | I/O   | SO/SB0                | specified in units of three bits by software.                                                                                                                                                                |  |

| P03       | Input | SI                    |                                                                                                                                                                                                              |  |

| P10       | Input | INT0                  | 2-bit input port (port 1) P10 connects with the built-in noise eliminator using a sampling clock.                                                                                                            |  |

| P12       |       | INT2                  | P12 connects with the built-in noise eliminator using an analog dela P12 allows the connection of built-in pull-up resistor to be specified software.                                                        |  |

| P20       | I/O   | -                     | 4-bit I/O port (port 2)                                                                                                                                                                                      |  |

| P21       |       | _                     | Allow I/O specification in units of four bits.                                                                                                                                                               |  |

| P22       |       | PCL                   | Allow the connection of built-in pull-up resistors to be specified in units of four bits by software.                                                                                                        |  |

| P23       |       | _                     | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                      |  |

| P30 - P33 | I/O   | -                     | Programmable 4-bit I/O port (port 3) Allow I/O specification bit by bit. Allow the connection of built-in pull-up resistors to be specified in units of four bits by software. Can directly drive LED.       |  |

| P50 - P53 | I/O   | -                     | 4-bit N-ch open-drain I/O port (port 5) Allow I/O specification in units of four bits. Allow the connection of built-in pull-up resistors to be specified bit by bit by mask option. Can directly drive LED. |  |

| P60 - P63 | I/O   | -                     | 4-bit I/O port (port 6) Allow I/O specification in units of four bits. Allow the connection of built-in pull-up resistors to be specified in units of four bits by software. Can directly drive LED.         |  |

**Remarks 1.** The  $\mu$ PD75402A(A) cannot perform 8-bit I/O with two ports as a pair.

2. See Chapter 8 for each pin status during resetting.

#### 3.2 NON-PORT PINS

| Pin     | I/O   | Dual-<br>function pin | Function                                                                                                                                                                         |  |

|---------|-------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

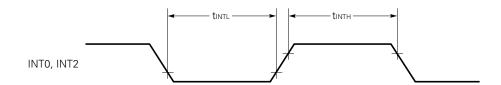

| INTO    | Input | P10                   | Edge detection vectored interrupt request input pin (A detected edge can be selected by the mode register.)  Connects with the built-in noise eliminator using a sampling clock. |  |

| INT2    | Input | P12                   | Edge detection external test input pin (A rising edge is detected.)                                                                                                              |  |

| SI      | Input | P03                   | Serial data input pin                                                                                                                                                            |  |

| so      | I/O   | P02/SB0               | Serial data output pin                                                                                                                                                           |  |

| SCK     | I/O   | P01                   | Serial clock I/O pin                                                                                                                                                             |  |

| SB0     | I/O   | P02/SO                | Serial bus I/O pin                                                                                                                                                               |  |

| PCL     | I/O   | P22                   | Clock output pin                                                                                                                                                                 |  |

| X1, X2  | Input | _                     | Pin for connection to a crystal/ceramic resonator for system clock generation. An external clock is applied to X1, and its reverse phase to X2.                                  |  |

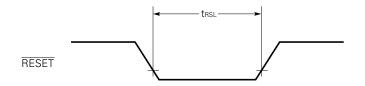

| RESET   | Input | -                     | System reset input pin, which connects with the built-in noise eliminator using an analog delay.                                                                                 |  |

| VDD     | _     | -                     | Positive power supply pin                                                                                                                                                        |  |

| Vss     | _     | _                     | Ground potential pin                                                                                                                                                             |  |

| NC Note | _     | _                     | No connection                                                                                                                                                                    |  |

Remark See Chapter 8 for each pin status during resetting.

**Note** Connect the NC pin directly to the Vss pin when the  $\mu$ PD75402A(A) shares the printed circuit board with the  $\mu$ PD75P402 in emulation.

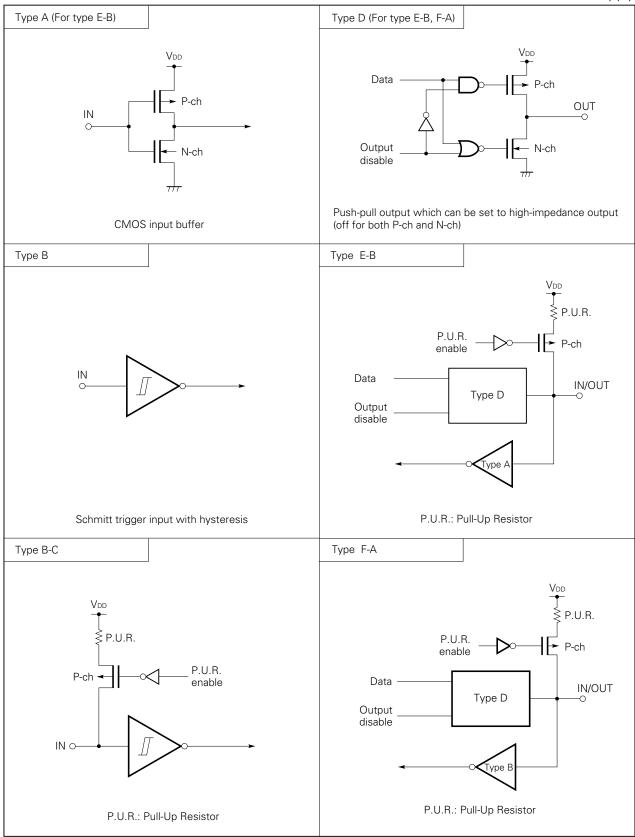

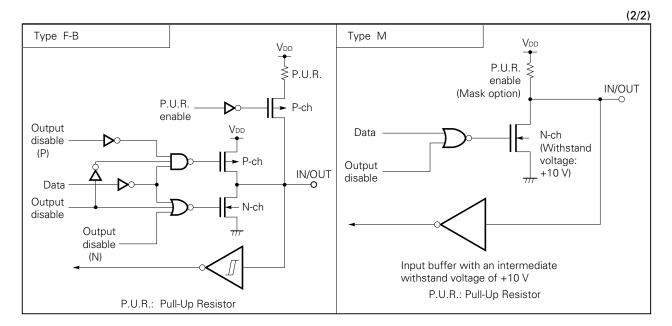

## 3.3 PIN INPUT/OUTPUT CIRCUITS

The I/O circuits of the  $\mu$ PD75402A(A) are roughly shown on the next and subsequent pages.

Table 1-1 I/O Circuit Type of Pin

| Pin        | I/O type | Pin               | I/O type |

|------------|----------|-------------------|----------|

| P00        | B        | P20, P21, and P23 | E-B      |

| P01/SCK    | F-A      | P22/PCL           |          |

| P02/SO/SB0 | F-B      | P30 - P33         | E-B      |

| P03/SI     | B-C      | P50 - P53         | M        |

| P10/INT0   | B        | P60 - P63         | E-B      |

| P12/INT2   | B-C      | RESET             | B        |

Remark The types in circles have a Schmitt-triggered input.

(1/2)

## 3.4 SELECTION OF A MASK OPTION

The following mask options are provided for pins:

| (Either can be specified bit by bit.) | P50 - P53 | ① Pull-up resistors connected (Either can be specified bit by bit.) | ② No pull-up resistors connected |

|---------------------------------------|-----------|---------------------------------------------------------------------|----------------------------------|

|---------------------------------------|-----------|---------------------------------------------------------------------|----------------------------------|

#### 3.5 HANDLING UNUSED PINS

| Pin       | Recommended connection method                                            |  |

|-----------|--------------------------------------------------------------------------|--|

| P00       | Connected to the Vss pin                                                 |  |

| P01 - P03 | When a pull-up resistor is contained     Connected to the VDD pin        |  |

| P10, P12  | When a pull-up resistor is not contained Connected to the Vss or VDD pin |  |

| P20 - P23 | When a pull-up resistor is contained                                     |  |

| P30 - P33 | Input mode : Connected to the VDD pin Output mode: Open                  |  |

| P50 - P53 | When a pull-up resistor is not contained                                 |  |

| P60 - P63 | Input mode : Connected to the Vss or Vdd pin Output mode: Open           |  |

| NC        | Open or directly connected to the Vss pin Note                           |  |

Note When the  $\mu$ PD75402A(A) shares the printed circuit board with the  $\mu$ PD75P402, connect the NC pin directly to Vss pin.

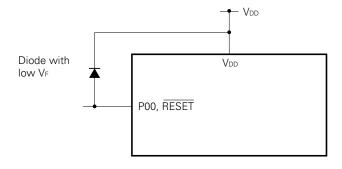

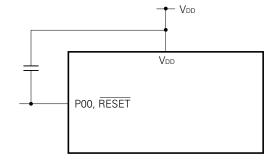

#### 3.6 NOTES ON USING THE POO AND RESET PINS

The P00 and  $\overline{\text{RESET}}$  pins have the test mode selecting function for testing the internal operation of the  $\mu$ PD75402A(A) (IC test), besides the functions shown in **Sections 3.1 and 3.2**.

Applying a voltage exceeding V<sub>DD</sub> to the P00 and/or  $\overline{\text{RESET}}$  pin causes the  $\mu$ PD75402A(A) to enter the test mode. When noise exceeding V<sub>DD</sub> comes in during normal operation, the device is switched to the test mode.

For example, when the wiring from the P00 or RESET pin is too long, noise voltage induced on the wiring is applied to the pin, driving the voltage at the pin above VDD, which may cause malfunction.

When installing the wiring, lay the wiring in such a way that noise is suppressed as much as possible. If noise yet arises, use an external part to suppress it as shown below.

Connect a diode with low V<sub>F</sub> (0.3 V or lower) between the pin and V<sub>DD</sub>. Connect a capacitor between the pin and VDD.

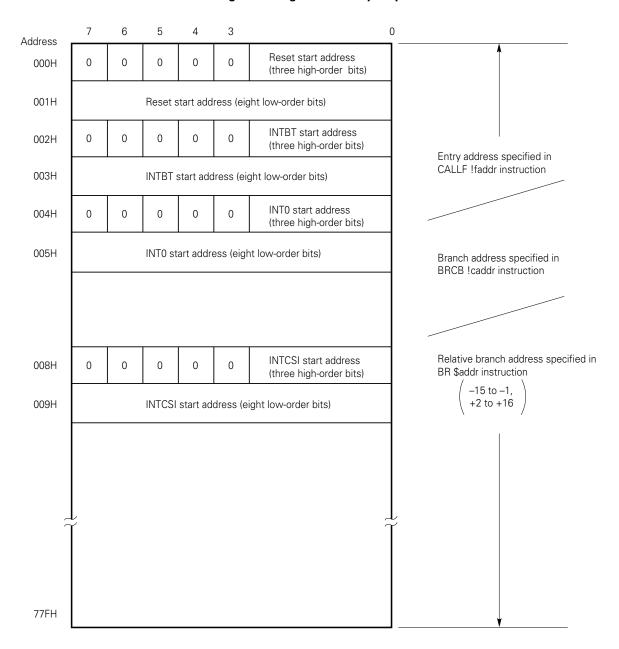

#### 4. MEMORY CONFIGURATION

• Program memory (ROM): 1920 × 8 bits (000H to 77FH)

· 000H and 001H: Vector table which contains the program start address after reset

• 002H to 009H : Vector table which contains the program start addresses when interrupts occur

Data memory

• Data area :  $64 \times 4$  bits (000H to 03FH) • Peripheral hardware area:  $128 \times 4$  bits (F80H to FFFH)

Fig. 4-1 Program Memory Map

Fig. 4-2 Data Memory Map 000H General register  $(4 \times 4)$ area 003H 004H Data area Static RAM (64 × 4) Bank 0 (64 × 4) 020H Stack area  $(32 \times 4)$ 03FH No memory F80H Peripheral hardware Bank 15  $128 \times 4$ area FFFH

13

## 5. PERIPHERAL HARDWARE FUNCTIONS

## 5.1 PORTS

The  $\mu$ PD75402A(A) has the following three types of I/O port:

- 6 CMOS input pins (PORT0 and PORT1)

- 12 CMOS I/O pins (PORT2, PORT3, and PORT6)

- 4 N-ch open-drain I/O pins (PORT5)

Total: 22 pins

**Table 5-1 Functions of Ports**

| Port name           | Function                                                                  | Operation and feature                                                                     | Remarks                                                                   |

|---------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| PORT0<br>PORT1      | 4-bit Input                                                               | Allows read and test at any time regardless of the operation modes of dual function pins. | Also used for SO/SB0, SI, SCK, INT0, and INT2.                            |

| PORT3 Note          | 4-bit I/O                                                                 | Allows input or output mode setting bit by bit.                                           | _                                                                         |

| PORT2<br>PORT6 Note |                                                                           | Allows input or output mode setting in units of 4 bits.                                   | Port 2 is also used for PCL.                                              |

| PORT5 Note          | 4-bit I/O (N-ch<br>open-drain I/O<br>with a withstand<br>voltage of 10 V) | Allows input or output mode setting in units of 4 bits.                                   | This port can incorporate a pull-up resistor as a mask option bit by bit. |

Note PORT3, PORT5, and PORT6 can directly drive the LED.

#### **5.2 CLOCK GENERATOR**

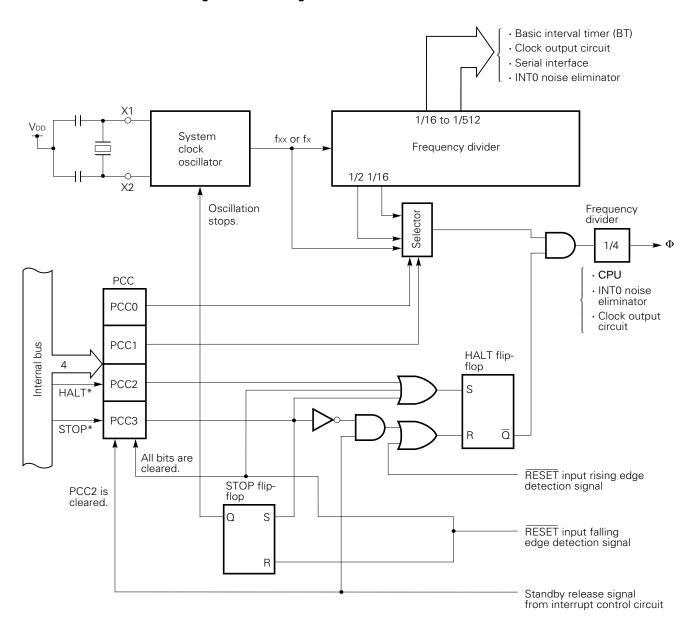

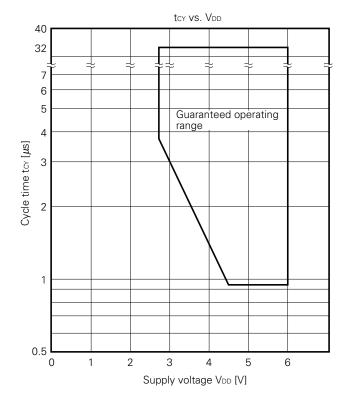

Operation of the clock generator is specified by the processor clock control register (PCC). The instruction execution time is variable.

• 0.95  $\mu$ s, 1.91  $\mu$ s, 15.3  $\mu$ s (when fxx is 4.19 MHz.)

Fig. 5-1 Block Diagram of the Clock Generator

**Remarks 1.** fxx = Crystal/ceramic oscillated frequency

- 2. fx = External clock frequency

- 3.  $\Phi = CPU clock$

- 4. An asterisk (\*) indicates instruction execution.

- 5. PCC: Processor clock control register

- **6.** One clock cycle (tcy) of  $\Phi$  is equal to one machine cycle of an instruction. See AC characteristics of **Chapter 10** for details of tcy.

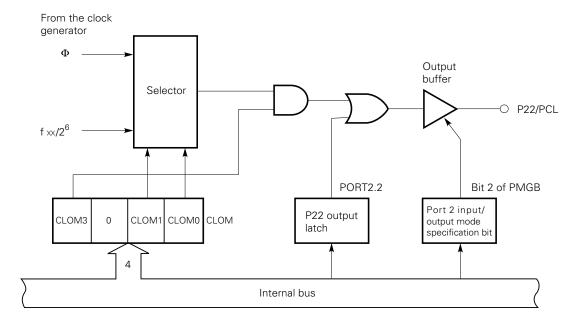

#### 5.3 CLOCK OUTPUT CIRCUIT

The clock output circuit, which outputs clock pulses from pin P22/PCL, is used for supplying clock pulses for peripheral LSIs or for remote control output.

• Clock output (PCL): 1.05 MHz, 524 kHz, 65.5 kHz (when fxx is 4.19 MHz).

Fig. 5-2 shows the configuration of the clock output circuit.

Fig. 5-2 Configuration of the Clock Output Circuit

**Remark** The clock output circuit is designed not to output high-frequency pulses when clock output is switched between the enable and disable states.

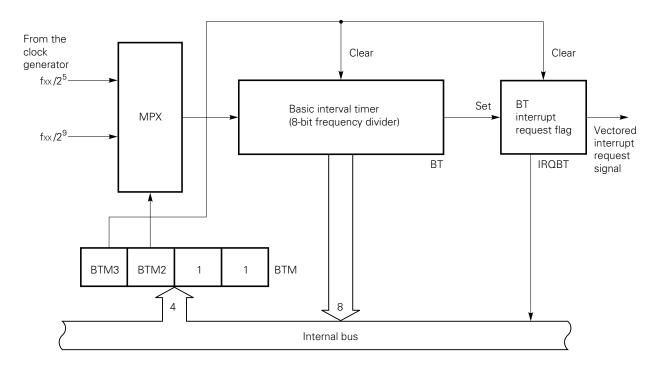

#### 5.4 BASIC INTERVAL TIMER

The basic interval timer provides the following functions:

- · Interval timer operation that generates a reference time interrupt

- Can be used as a watchdog timer for detecting program crashes

- · Reading the count value

Fig. 5-3 Configuration of the Basic Interval Timer

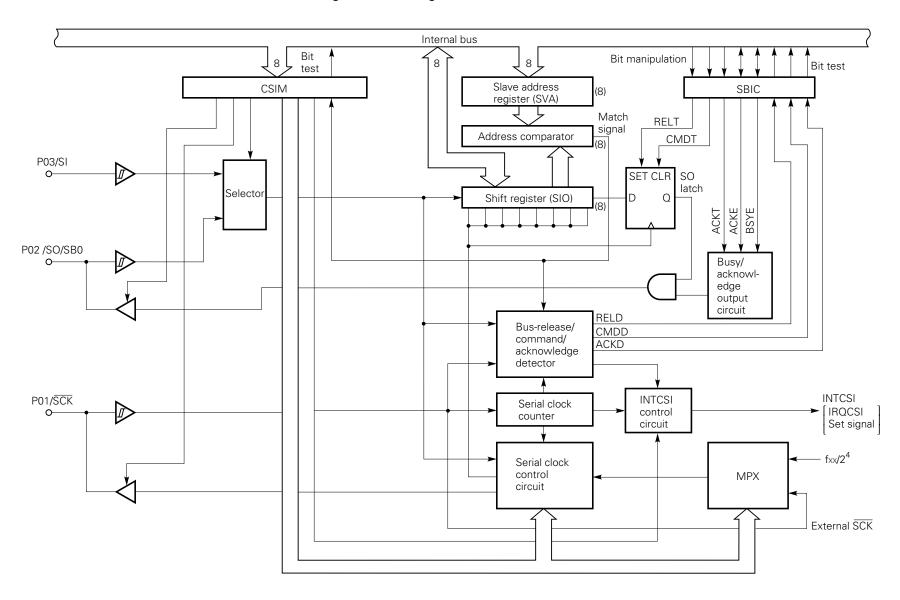

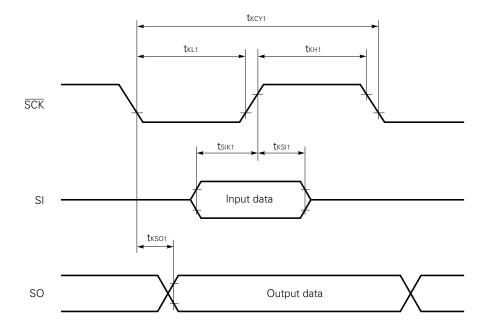

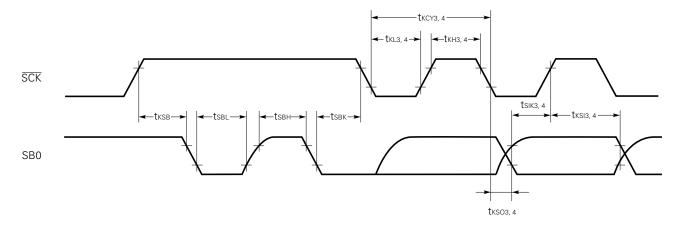

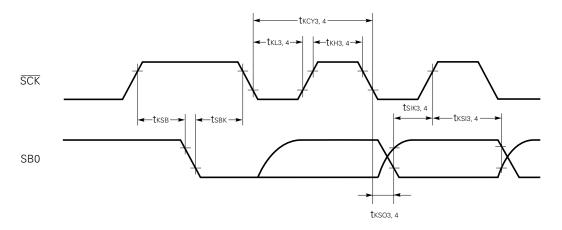

## 5.5 SERIAL INTERFACE

The serial interface has the following modes:

- Three-wire serial I/O mode (MSB is transferred first.)

- SBI mode (MSB is transferred first.)

The three-wire serial I/O mode enables connections to be made with the 75X series, 78K series, and many other types of peripheral I/O devices.

The SBI mode enables communication with two or more devices.

Fig. 5-4 Block Diagram of the Serial Interface

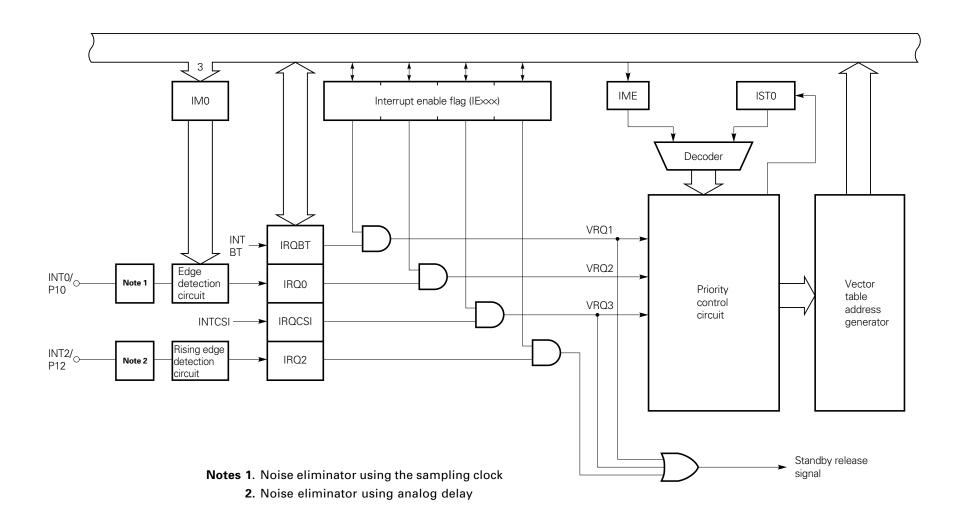

#### 6. INTERRUPT FUNCTION

The  $\mu$ PD75402A(A) has three interrupt sources and each of them has the interrupt vector table.

The  $\mu$ PD75402A(A) is also provided with one edge-sensitive testable input signal.

When a vectored interrupt request is issued, the PC and PSW are saved in the stack, and the contents of the vector table which corresponds to the issued vectored interrupt are set in the PC as a start address. The program branches to the interrupt service routine. These operations are performed automatically by the hardware.

The flag is set by detecting the edge of the testable input signal, but a vectored interrupt request is not issued.

During execution of the interrupt service routine, the  $\mu$ PD75402A(A) does not accept the other interrupt requests. Unlike the other 75X series, the  $\mu$ PD75402A(A) cannot handle multiple interrupts.

The interrupt control circuit of the  $\mu$ PD75402A(A) has the following functions.

- Vectored interrupt function under hardware control which can determine whether to accept an interrupt by an interrupt enable flag (IExxx) and an interrupt master enable flag (IME).

- · Any interrupt start address can be set.

- Test function of an interrupt request flag (IRQxxx) (Software can confirm that an interrupt occurs.)

- Release of the standby (HALT) mode (An interrupt to be released by an interrupt enable flag can be selected from interrupts other than INT0.)

Fig. 6-1 Block Diagram of Interrupt Control Circuit

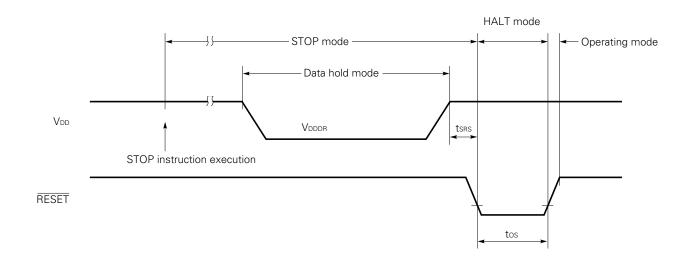

## 7. STANDBY FUNCTION

To reduce the power consumption when the program is in the wait state, the  $\mu$ PD75402A(A) has two standby modes, STOP and HALT.

Table 7-1 Operation Statuses in the Standby Mode

|                                                                                                       |                      | STOP mode                                    | HALT mode                                                                      |

|-------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------|--------------------------------------------------------------------------------|

| Instruction set mode                                                                                  | on to be used to     | STOP instruction                             | HALT instruction                                                               |

| Opera-<br>tion                                                                                        | Clock generator      | Oscillation of the system clock stops.       | Only the CPU clock $(\Phi)$ stops, but oscillation continues.                  |

| status                                                                                                | Basic interval timer | Operation stops.                             | Operates. (IRQBT is set at every reference time interval.)                     |

| Serial interface Operable only when the external SCK operable input is selected for the serial clock. |                      | Operable                                     |                                                                                |

| Clock output circuit                                                                                  |                      | Operation stops.                             | Clocks other than CPU clock $(\Phi)$ can be output.                            |

|                                                                                                       | External interrupt   | INT2 pin is usable. INT0 pin cannot be used. | INT2 pin is usable. INT0 pin cannot be used.                                   |

| CPU                                                                                                   |                      | Operation stops.                             |                                                                                |

| Release signal                                                                                        |                      | RESET input                                  | RESET input or interrupt request signals enabled by the interrupt enable flags |

#### 8. RESET FUNCTION

When a low level signal is input to the RESET input pin, the state changes to the system reset. Table 8-1 shows the statuses of the hardware.

When the RESET signal rises from the low level to the high level, the reset state is released. The three low-order bits of the reset vector table whose address is 000H is set in bits 10 to 8 of the program counter (PC) and the contents of the reset vector table whose address is 001H is set in bits 7 to 0 of the PC. The program branches to that address and starts execution, i.e., the reset start address is programmable.

Initialize contents of registers in a program if necessary.

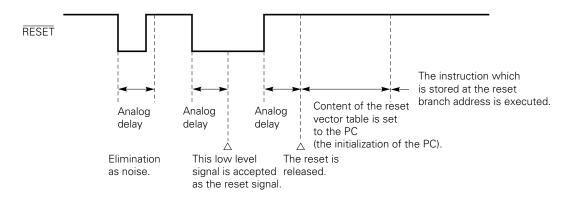

The RESET pin connects to the Schmitt-trigger circuit whose threshold level has hysteresis in the chip. This pin is also connected to the noise eliminator using an analog delay to eliminate narrow noise and prevent errors caused by noise. (See Fig. 8-1.)

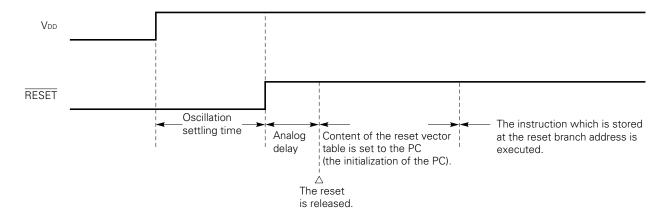

For the power-on reset operation, be sure to allow sufficient time for oscillation to settle between power on and acceptance of the reset signal (see Fig. 8-2).

Fig. 8-1 Acceptance of the Reset Signal

Fig. 8-2 Power-On Reset Operation

Table 8-1 Hardware Statuses after Reset Operations

|                         | Hardware                                                     | RESET input in standby mode                                                                                                               | RESET input during operations                                                                                                             |

|-------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                                                              | Set the three low-order bits of address 000H in program memory in PC bits 10 to 8 and set the contents of address 001H in PC bits 7 to 0. | Set the three low-order bits of address 000H in program memory in PC bits 10 to 8 and set the contents of address 001H in PC bits 7 to 0. |

| PSW                     | Carry flag (CY)                                              | Retained                                                                                                                                  | Undefined                                                                                                                                 |

| İ                       | Skip flag (SK0 - SK2)                                        | 0                                                                                                                                         | 0                                                                                                                                         |

| i                       | Interrupt status flag (IST0)                                 | 0                                                                                                                                         | 0                                                                                                                                         |

| Stack poi               | nter (SP)                                                    | Undefined                                                                                                                                 | Undefined                                                                                                                                 |

| Data men                | nory (RAM)                                                   | Retained Note                                                                                                                             | Undefined                                                                                                                                 |

| General r               | egister (X, A, H, L)                                         | Retained                                                                                                                                  | Undefined                                                                                                                                 |

| Basic inte              | rval Counter (BT)                                            | Undefined                                                                                                                                 | Undefined                                                                                                                                 |

| timer                   | Mode register (BTM)                                          | 0                                                                                                                                         | 0                                                                                                                                         |

| Serial                  | Shift register (SIO)                                         | Retained                                                                                                                                  | Undefined                                                                                                                                 |

| interface               | Operation mode register (CSIM)                               | 0                                                                                                                                         | 0                                                                                                                                         |

|                         | SBI control register (SBIC)                                  | 0                                                                                                                                         | 0                                                                                                                                         |

|                         | Slave address register (SVA)                                 | Retained                                                                                                                                  | Undefined                                                                                                                                 |

| Clock gen<br>tor and cl |                                                              | 0                                                                                                                                         | 0                                                                                                                                         |

| output cir              | Clock output mode register (CLOM)                            | 0                                                                                                                                         | 0                                                                                                                                         |

| Interrupt               | Interrupt request flag (IRQ×××)                              | Reset (0)                                                                                                                                 | Reset (0)                                                                                                                                 |

|                         | Interrupt enable flag (IExxx)                                | 0                                                                                                                                         | 0                                                                                                                                         |

|                         | Interrupt master enable flag (IME)                           | 0                                                                                                                                         | 0                                                                                                                                         |

|                         | INT0 mode register (IM0)                                     | 0                                                                                                                                         | 0                                                                                                                                         |

| Digital I/O             | Output buffer                                                | Off                                                                                                                                       | Off                                                                                                                                       |

| port                    | Output latch                                                 | Cleared (0)                                                                                                                               | Cleared (0)                                                                                                                               |

|                         | I/O mode register<br>(PMGA, PMGB)                            | 0                                                                                                                                         | 0                                                                                                                                         |

|                         | Pull-up resistor specification register (POGA)               | 0                                                                                                                                         | 0                                                                                                                                         |

| States of               | pins P00 - P03, P10, P12, P20 - P23,<br>P30 - P33, P60 - P63 | Used as inputs                                                                                                                            | Used as inputs                                                                                                                            |

|                         | P50 - P53                                                    | <ul> <li>High level when pull-up resistor is built in</li> <li>High impedance when open drain is used in the internal circuit</li> </ul>  | <ul> <li>High level when pull-up resistor is built in</li> <li>High impedance when open drain is used in the internal circuit</li> </ul>  |

**Note** Data in the data memory whose addresses are 38H to 3DH is not defined when the standby mode is released by the RESET input signal.

#### 9. INSTRUCTION SET

#### (1) Representation format and description method of operands

An operand is described in the operand field of each instruction according to the description method corresponding to the operand representation format of the instruction refer to "RA75X Assembler Package User's Manual, Language" (EEU-1363) for details. When two or more elements are described in the description method field, select one of them. Upper-case letters, a number sign (#), and at mark (@), an exclamation mark (!), and a dollar sign (\$) are keywords, so they can be used without alteration. Specify an appropriate numeric value or label for immediate data.

The symbols of registers and flags can be used as labels instead of mem, fmem, and bit (refer to the "µPD75402A User's Manual" (IEU-644) for details). Some labels, however, cannot be specified in fmem.

| Representation format | Description method                              |

|-----------------------|-------------------------------------------------|

| reg                   | X, A, H, L                                      |

| reg1                  | X, H, L                                         |

| rp                    | XA, HL                                          |

| n4                    | 4-bit immediate data or label                   |

| n8                    | 8-bit immediate data or label                   |

| mem                   | 8-bit immediate data or label Note              |

| bit                   | 2-bit immediate data or label                   |

| fmem                  | FB0H - FBFH/FF0H - FFFH immediate data or label |

| addr                  | 11-bit immediate data or label                  |

| caddr                 | 11-bit immediate data or label                  |

| faddr                 | 11-bit immediate data or label                  |

| PORTn                 | PORT0 - PORT3, PORT5, PORT6                     |

| IE×××                 | IEBT, IECSI, IE0, IE2                           |

Note Only an even address can be written in mem when 8-bit data is processed.

#### (2) Legend

A : A register, 4-bit accumulator

H : H registerL : L registerX : X register

XA : Register pair (XA), 8-bit accumulator

HL : Register pair (HL)PC : Program counterSP : Stack pointer

CY: Carry flag, bit accumulator

PSW: Program status word

PORTn: Port n (n = 0 to 3, 5, 6)

IME: Interrupt master enable flag

IExxx : Interrupt enable flag

PCC : Processor clock control register

· : Address/bit delimiter ( $\times\times$ ) : Contents addressed by  $\times\times$

××H : Hexadecimal data

## (3) Explanation of the symbols in the addressing area field

| *1 | MB = 0                                                                                   | <b>^</b>                  |

|----|------------------------------------------------------------------------------------------|---------------------------|

| *2 | MB = 0 (00H - 3FH)<br>MB = 15 (80H - FFH)                                                | Data memory<br>addressing |

| *3 | MB = 15, fmem = FB0H - FBFH or<br>FF0H - FFFH                                            | addressing                |

| *4 | addr = 000H - 77FH                                                                       | <u> </u>                  |

| *5 | addr = (Current PC) – 15 to (Current PC) – 1 or<br>(Current PC) + 16 to (Current PC) + 2 | Program memory            |

| *6 | caddr = 000H - 77FH                                                                      | addressing<br>            |

| *7 | faddr = 000H - 77FH                                                                      | ↓                         |

Remarks 1. MB indicates an accessible memory bank.

2. \*4 to \*7 indicate each addressable area.

## (4) Explanation of the machine cycle field

S indicates the number of machine cycles required for a skip instruction to perform skipping. The following shows the values of S.

- · When the next instruction is not skipped, S is 0.

- When the next instruction is skipped, S is 1.

A machine cycle is equal to one cycle (= tcv) of CPU clock  $\Phi$ . A PCC setting determines the machine cycle. It can be set to one of three different periods.

| Instruc-<br>tion<br>group   | Mne-<br>monic | Operand   | Number<br>of<br>bytes | Ma-<br>chine<br>cycle | Operation                                                            | Address-<br>ing area | Skip<br>condition |

|-----------------------------|---------------|-----------|-----------------------|-----------------------|----------------------------------------------------------------------|----------------------|-------------------|

| Transfer                    | MOV           | A, #n4    | 1                     | 1                     | A ← n4                                                               |                      | String A          |

| instruc-                    |               | XA, #n8   | 2                     | 2                     | XA ← n8                                                              |                      | String A          |

| tion                        |               | HL, #n8   | 2                     | 2                     | HL ← n8                                                              |                      | String B          |

|                             |               | A, @HL    | 1                     | 1                     | A ← (HL)                                                             | *1                   |                   |

|                             |               | @HL, A    | 1                     | 1                     | (HL) ← A                                                             | *1                   |                   |

|                             |               | A, mem    | 2                     | 2                     | A ← (mem)                                                            | *2                   |                   |

|                             |               | XA, mem   | 2                     | 2                     | XA ← (mem)                                                           | *2                   |                   |

|                             |               | mem, A    | 2                     | 2                     | (mem) ← A                                                            | *2                   |                   |

|                             |               | mem, XA   | 2                     | 2                     | (mem) ← XA                                                           | *2                   |                   |

|                             | хсн           | A, @HL    | 1                     | 1                     | $A \leftrightarrow (HL)$                                             | *1                   |                   |

|                             |               | A, mem    | 2                     | 2                     | $A \leftrightarrow (mem)$                                            | *2                   |                   |

|                             |               | XA, mem   | 2                     | 2                     | XA ↔ (mem)                                                           | *2                   |                   |

|                             |               | A, reg1   | 1                     | 1                     | A ↔ reg1                                                             |                      |                   |

|                             | MOVT          | XA, @PCXA | 1                     | 3                     | XA ← (PC <sub>10-8</sub> + XA) <sub>ROM</sub>                        |                      |                   |

| Arithme- ADDS               |               | A, #n4    | 1                     | 1 + S                 | A ← A + n4                                                           |                      | carry             |

| tic/                        |               | A, @HL    | 1                     | 1 + S                 | A ← A + (HL)                                                         | *1                   | carry             |

| logical<br>instruc-         | ADDC          | A, @HL    | 1                     | 1                     | $A, CY \leftarrow A + (HL) + CY$                                     | *1                   |                   |

| tion                        | AND           | A, @HL    | 1                     | 1                     | $A \leftarrow A \wedge (HL)$                                         | *1                   |                   |

|                             | OR            | A, @HL    | 1                     | 1                     | $A \leftarrow A \lor (HL)$                                           | *1                   |                   |

|                             | XOR           | A, @HL    | 1                     | 1                     | $A \leftarrow A \forall (HL)$                                        | *1                   |                   |

| Accumu-<br>lator<br>manipu- | RORC          | A         | 1                     | 1                     | $CY \leftarrow \ A_0, \ A_3 \leftarrow CY, \ A_{n-1} \leftarrow A_n$ |                      |                   |

| lation<br>instruc-<br>tion  | NOT           | А         | 2                     | 2                     | $A \leftarrow \overline{A}$                                          |                      |                   |

| Incre-<br>ment/             | INCS          | reg       | 1                     | 1 + S                 | reg ← reg + 1                                                        |                      | reg = 0           |

| decre-<br>ment              |               | mem       | 2                     | 2 + S                 | (mem) ← (mem) + 1                                                    | *2                   | (mem) = 0         |

| instruc-<br>tion            | DECS          | reg       | 1                     | 1 + S                 | reg ← reg – 1                                                        |                      | reg = FH          |

| Compari-<br>son             | SKE           | reg, #n4  | 2                     | 2 + S                 | Skip if reg = n4                                                     |                      | reg = n4          |

| instruc-<br>tion            |               | A, @HL    | 1                     | 1 + S                 | Skip if A = (HL)                                                     | *1                   | A = (HL)          |

| Carry flag                  | SET1          | CY        | 1                     | 1                     | CY ← 1                                                               |                      |                   |

| manipu-                     | CLR1          | CY        | 1                     | 1                     | CY ← 0                                                               |                      |                   |

| lation<br>instruc-          | SKT           | CY        | 1                     | 1 + S                 | Skip if CY = 1                                                       |                      | CY = 1            |

| tion                        | NOT1          | CY        | 1                     | 1                     | $CY \leftarrow \overline{CY}$                                        |                      |                   |

| Instruc-<br>tion<br>group   | Mne-<br>monic | Operand      | Number<br>of<br>bytes | Ma-<br>chine<br>cycle | Operation                                                                                                                                                   | Address-<br>ing area | Skip<br>condition    |

|-----------------------------|---------------|--------------|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|

| Memory                      | SET1          | mem.bit      | 2                     | 2                     | (mem.bit) ← 1                                                                                                                                               | *2                   |                      |

| bit                         |               | fmem.bit     | 2                     | 2                     | (fmem.bit) ← 1                                                                                                                                              | *3                   |                      |

| manipu-<br>lation           | CLR1          | mem.bit      | 2                     | 2                     | (mem.bit) ← 0                                                                                                                                               | *2                   |                      |

| instruc-                    |               | fmem.bit     | 2                     | 2                     | (fmem.bit) ← 0                                                                                                                                              | *3                   |                      |

| tion                        | SKT           | mem.bit      | 2                     | 2 + S                 | Skip if (mem.bit) = 1                                                                                                                                       | *2                   | (mem.bit) = 1        |

|                             |               | fmem.bit     | 2                     | 2 + S                 | Skip if (fmem.bit) = 1                                                                                                                                      | *3                   | (fmem.bit) = 1       |

|                             | SKF           | mem.bit      | 2                     | 2 + S                 | Skip if (mem.bit) = 0                                                                                                                                       | *2                   | (mem.bit) = 0        |

|                             |               | fmem.bit     | 2                     | 2 + S                 | Skip if (fmem.bit) = 0                                                                                                                                      | *3                   | (fmem.bit) = 0       |

|                             | SKTCLR        | fmem.bit     | 2                     | 2 + S                 | Skip if (fmem.bit) = 1 and clear                                                                                                                            | *3                   | (fmem.bit) = 1       |

|                             | AND1          | CY, fmem.bit | 2                     | 2                     | $CY \leftarrow CY \land (fmem.bit)$                                                                                                                         | *3                   |                      |

|                             | OR1           | CY, fmem.bit | 2                     | 2                     | $CY \leftarrow CY \lor (fmem.bit)$                                                                                                                          | *3                   |                      |

|                             | XOR1          | CY, fmem.bit | 2                     | 2                     | CY ← CY ♥ (fmem.bit)                                                                                                                                        | *3                   |                      |

| Branch<br>instruc-<br>tion  | BR            | addr         | -                     | -                     | PC <sub>10-0</sub> ← addr<br>(The assembler selects an<br>appropriate instruction from the<br>BRCB !caddr and BR \$addr<br>instructions.)                   | *4                   |                      |

|                             |               | \$addr       | 1                     | 2                     | PC₁₀₋₀ ← addr                                                                                                                                               | *5                   |                      |

|                             | BRCB          | !caddr       | 2                     | 2                     | PC <sub>10-0</sub> ← caddr                                                                                                                                  | *6                   |                      |

| Subrou-<br>tine<br>stack    | CALLF         | !faddr       | 2                     | 2                     | $(SP - 4)(SP - 1)(SP - 2) \leftarrow 0$ , PC <sub>10-0</sub><br>$(SP - 3) \leftarrow 0000$<br>PC <sub>10-0</sub> $\leftarrow$ faddr, SP $\leftarrow$ SP - 4 | *7                   |                      |

| control<br>instruc-<br>tion | RET           |              | 1                     | 3                     | $\times$ , PC <sub>10-0</sub> $\leftarrow$ (SP)(SP + 3)(SP + 2)<br>SP $\leftarrow$ SP + 4                                                                   |                      |                      |

| tion                        | RETS          |              | 1                     | 3 + S                 | $\times$ , PC <sub>10-0</sub> $\leftarrow$ (SP)(SP + 3)(SP + 2)<br>SP $\leftarrow$ SP + 4, then skip unconditionally                                        |                      | Uncondition-<br>ally |

|                             | RETI          |              | 1                     | 3                     | $\times$ , PC <sub>10-0</sub> $\leftarrow$ (SP)(SP + 3)(SP + 2)<br>PSW $\leftarrow$ (SP + 4)(SP + 5), SP $\leftarrow$ SP + 6                                |                      |                      |

|                             | PUSH          | rp           | 1                     | 1                     | $(SP - 1)(SP - 2) \leftarrow rp, SP \leftarrow SP - 2$                                                                                                      |                      |                      |

|                             | POP           | rp           | 1                     | 1                     | $rp \leftarrow (SP + 1)(SP), SP \leftarrow SP + 2$                                                                                                          |                      |                      |

| Interrupt                   | EI            |              | 2                     | 2                     | IME (IPS.3) ← 1                                                                                                                                             |                      |                      |

| control<br>instruc-         |               | IExxx        | 2                     | 2                     | IExxx ← 1                                                                                                                                                   |                      |                      |

| tion                        | DI            |              | 2                     | 2                     | IME (IPS.3) ← 0                                                                                                                                             |                      |                      |

|                             |               | IE×××        | 2                     | 2                     | IE××× ← 0                                                                                                                                                   |                      |                      |

| Input/<br>output            | IN            | A, PORTn     | 2                     | 2                     | A ← PORTn (n = 0 - 3, 5, 6)                                                                                                                                 |                      |                      |

| instruc-<br>tion            | OUT           | PORTn, A     | 2                     | 2                     | PORT n ← A (n = 2, 3, 5, 6)                                                                                                                                 |                      |                      |

| CPU                         | HALT          |              | 2                     | 2                     | Set HALT mode (PCC.2 ← 1)                                                                                                                                   |                      |                      |

| control instruction         | STOP          |              | 2                     | 2                     | Set STOP mode (PCC.3 ← 1)                                                                                                                                   |                      |                      |

| moti dottori                | NOP           |              | 1                     | 1                     | No operation                                                                                                                                                |                      |                      |

#### 10. ELECTRICAL CHARACTERISTICS

## ABSOLUTE MAXIMUM RATINGS $(T_a = 25 \degree C)$

| Parameter                | Symbol           |                               | Conditions              |                               | Rated value                   | Unit |

|--------------------------|------------------|-------------------------------|-------------------------|-------------------------------|-------------------------------|------|

| Supply voltage           | V <sub>DD</sub>  |                               |                         |                               | -0.3 to +7.0                  | V    |

| Input voltage            | Vıı              | Ports ot                      | her than port 5         |                               | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                          | Vı2              | Port 5                        | Built-in pull-up resis  | tor                           | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                          |                  |                               | Open drain              |                               | -0.3 to +11.0                 | V    |

| Output voltage           | Vo               |                               |                         | -0.3 to V <sub>DD</sub> + 0.3 | V                             |      |

| High-level output        | Іон              | Each pir                      | 1                       |                               | -15                           | mA   |

| current                  |                  | Total of                      | all output pins         | -30                           | mA                            |      |

| Low-level output current | loL Note         | One pin of port 0, 3, 5, or 6 |                         | Peak value                    | 30                            | mA   |

|                          |                  |                               |                         | rms                           | 15                            | mA   |

|                          |                  | One pin                       | of port 2               | Peak value                    | 20                            | mA   |

|                          |                  |                               |                         | rms                           | 10                            | mA   |

|                          |                  | Total of                      | all pins of ports 0, 3, | Peak value                    | 100                           | mA   |

|                          |                  | and 5 (e                      | xcl. P33)               | rms                           | 60                            | mA   |

|                          |                  | Total of                      | all pins of ports 2, 6, | Peak value                    | 100                           | mA   |

|                          |                  | and P33                       |                         | rms                           | 60                            | mA   |

| Operating temperature    | Topt             |                               |                         |                               | -40 to +85                    | °C   |

| Storage tempera-<br>ture | T <sub>stg</sub> |                               |                         |                               | -65 to +150                   | °C   |

**Note** Calculate rms with [rms] = [peak value]  $\times \sqrt{\text{duty.}}$

Caution Absolute maximum ratings are rated values beyond which some physical damages may be caused to the product; if any of the parameters in the table above exceeds its rated value even for a moment, the quality of the product may deteriorate. Be sure to use the product within the rated values.

#### CHARACTERISTICS OF THE OSCILLATION CIRCUIT (Ta = -40 to +85 °C, V DD = 2.7 to 6.0 V)

| Resonator            | Recommended constant | Parameter                                         | Conditions                                                                  | Min. | Тур. | Max.       | Unit |

|----------------------|----------------------|---------------------------------------------------|-----------------------------------------------------------------------------|------|------|------------|------|

| Ceramic<br>resonator | C1                   | Oscillator<br>frequency<br>(fxx) Note 1           | V <sub>DD</sub> = oscillation<br>voltage range                              | 2.0  |      | 5.0 Note 3 | MHz  |

|                      |                      | Oscillation<br>settling time<br>Note 2            | After V <sub>DD</sub> reaches<br>MIN. of the oscilla-<br>tion voltage range |      |      | 4          | ms   |

| Crystal              | X1 X2                | Oscillator<br>frequency<br>(fxx) Note 1           |                                                                             | 2.0  | 4.19 | 5.0 Note 3 | MHz  |

|                      | C1 C2                | Oscillation settling time Note 2                  | V <sub>DD</sub> = 4.5 to 6.0 V                                              |      |      | 10         | ms   |

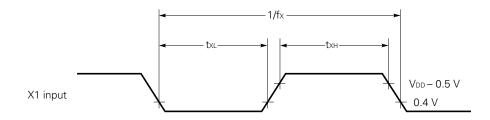

| External<br>clock    | X1 X2                | X1 input<br>frequency<br>(fx) Note 1              |                                                                             | 2.0  |      | 5.0 Note 3 | MHz  |

|                      | μPD74HCU04           | X1 input<br>high/low<br>level width<br>(txH, txL) |                                                                             | 100  |      | 250        | ns   |

- **Notes 1.** The oscillator frequency and X1 input frequency indicate only the oscillator characteristics. See the item of AC characteristics for the instruction execution time.

- 2. The oscillation settling time means the time required for the oscillation to settle after VDD is applied or after the STOP mode is released.

- 3. When 4.19 MHz <  $fx \le 5.0$  MHz, do not select PCC = 0011 as the instruction execution time. When PCC = 0011, one machine cycle falls short of 0.95  $\mu$ s, the minimum value for the standard.

- ★ Caution When the clock oscillator is used, conform to the following guidelines when wiring at the portions surrounded by dotted lines in the figures above to eliminate the influence of the wiring capacity.

- · The wiring must be as short as possible.

- Other signal lines must not run in these areas.

- · Any line carrying a high fluctuating current must be kept away as far as possible.

- The grounding point of the capacitor of the oscillator must have the same potential as that of Vss. It must not be grounded to ground patterns carrying a large current.

- · No signal must be taken from the oscillator.

#### **CAPACITANCE** $(T_a = 25 \, ^{\circ}C, \, V_{DD} = 0 \, V)$

| Parameter          | Symbol | Conditions                         | Min. | Тур. | Max. | Unit |

|--------------------|--------|------------------------------------|------|------|------|------|

| Input capacitance  | Cin    | f = 1 MHz                          |      |      | 15   | pF   |

| Output capacitance | Соит   | 0 V for pins other than pins to be |      |      | 15   | pF   |

| I/O capacitance    | Сю     | measured                           |      |      | 15   | pF   |

## **DC CHARACTERISTICS** ( $T_a = -40 \text{ to } +85 \text{ °C}$ , $V_{DD} = 2.7 \text{ to } 6.0 \text{ V}$ )

| Parameter                           | Symbol            |                                              | Condit                                                                 | tions                         | Min.                  | Тур. | Max.               | Unit |

|-------------------------------------|-------------------|----------------------------------------------|------------------------------------------------------------------------|-------------------------------|-----------------------|------|--------------------|------|

| High-level input                    | V <sub>IH1</sub>  | Ports 2, 3, an                               | d 6                                                                    |                               | 0.7V <sub>DD</sub>    |      | V <sub>DD</sub>    | ٧    |

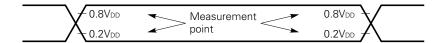

| voltage                             | V <sub>IH2</sub>  | Ports 0 and 1                                | , and RE                                                               | SET                           | 0.8V <sub>DD</sub>    |      | V <sub>DD</sub>    | V    |

|                                     | V <sub>IH3</sub>  | Port 5                                       | Built-in                                                               | pull-up resistor              | 0.7V <sub>DD</sub>    |      | V <sub>DD</sub>    | V    |

|                                     |                   |                                              | Open d                                                                 | rain                          | 0.7V <sub>DD</sub>    |      | 10                 | V    |

|                                     | V <sub>IH4</sub>  | X1 and X2                                    |                                                                        |                               | V <sub>DD</sub> - 0.5 |      | V <sub>DD</sub>    | V    |

| Low-level input                     | VIL1              | Ports 2, 3, 5,                               | and 6                                                                  |                               | 0                     |      | 0.3V <sub>DD</sub> | V    |

| voltage                             | VIL2              | Ports 0 and 1                                | , and RES                                                              | SET                           | 0                     |      | 0.2V <sub>DD</sub> | V    |

|                                     | VIL3              | X1 and X2                                    |                                                                        |                               | 0                     |      | 0.4                | V    |

| High-level output                   | Vон               | Ports 0, 2,                                  | V <sub>DD</sub> = 4.5                                                  | 5 to 6.0 V, Iон = -1 mA       | V <sub>DD</sub> - 1.0 |      |                    | ٧    |

| voltage                             |                   | 3, and 6                                     | Іон = −10                                                              | 00 μΑ                         | V <sub>DD</sub> - 0.5 |      |                    | V    |

| Low-level output voltage            | Vol               | Ports 3, 5,<br>and 6                         | V <sub>DD</sub> = 4.5                                                  | 5 to 6.0 V, IoL = 15 mA       |                       | 0.6  | 2.0                | V    |

|                                     |                   | Ports 0, 2,                                  | V <sub>DD</sub> = 4.5                                                  | 5 to 6.0 V, loL = 1.6 mA      |                       |      | 0.4                | V    |

|                                     |                   | 3, 5, and 6                                  | loL = 40                                                               | IoL = 400 μA                  |                       |      | 0.5                | V    |

|                                     |                   | SB0 (Open drain)                             | Pull-up resistor : 1 k $\Omega$ or more V <sub>DD</sub> = 4.5 to 6.0 V |                               |                       |      | 0.2V <sub>DD</sub> | V    |

| High-level input<br>leakage current | ILIH1             | VIN = VDD                                    | Other th                                                               | nan X1 and X2                 |                       |      | 3                  | μΑ   |

|                                     | ILIH2             |                                              | X1 and                                                                 | X1 and X2                     |                       |      | 20                 | μΑ   |

|                                     | Ілнз              | Vin = 10 V                                   | Port 5 (open drain)                                                    |                               |                       |      | 20                 | μΑ   |

| Low-level input                     | ILIL1             | Vin = 0 V                                    | Other th                                                               | nan X1 and X2                 |                       |      | - 3                | μΑ   |

| leakage current                     | I <sub>LIL2</sub> |                                              | X1 and X2                                                              |                               |                       |      | - 20               | μΑ   |

| High-level output                   | Ісон1             | Vout = Vdd                                   | Other th                                                               | nan port 5                    |                       |      | 3                  | μΑ   |

| leakage current                     | Ігон2             | Vout = 10 V                                  | Port 5 (                                                               | open drain)                   |                       |      | 20                 | μΑ   |

| Low-level output leakage current    | ILOL              | Vout = 0 V                                   |                                                                        |                               |                       |      | - 3                | μΑ   |