# **MP28262** 2A, 21V, 1.1MHz

# **Synchronous Step-down Converter**

#### **DESCRIPTION**

The MP28262 is a high frequency synchronous rectified step-down switch mode converter with built in internal power MOSFETs. It offers a very compact solution to achieve 2A continuous output current over a wide input supply range with excellent load and line regulation. The MP28262 operates at high efficiency over a wide output current load range.

Current mode operation provides fast transient response and eases loop stabilization.

Full protection features include OCP and thermal shut down.

The MP28262 requires a minimum number of readily available standard external components and is available in a space saving 3mm x 4mm 14-pin QFN package.

#### **FEATURES**

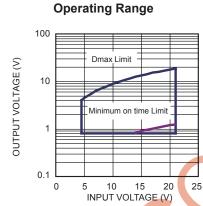

- Wide 4.5V to 21V Operating Input Range

- 2A Output Current

- Low R<sub>DS</sub>(ON) Internal Power MOSFETs

- Proprietary Switching Loss Reduction Technique

- Fixed 1.1MHz Switching Frequency

- Svnc from 400kHz to 2MHz External Clock

- Internal Compensation

- OCP Protection and Thermal Shutdown

- Output Adjustable from 0.8V

- Available in 14-pin QFN3x4 Package

#### **APPLICATIONS**

- Notebook Systems and I/O Power

- Networking Systems

- Digital Set Top Boxes

- Personal Video Recorders

- Flat Panel Television and Monitors

- Distributed Power Systems

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

The information in this datasheet about the product and its associated technologies are proprietary and intellectual property of Monolithic Power Systems and are protected by copyright and pending patent applications

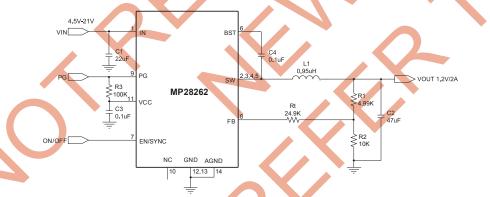

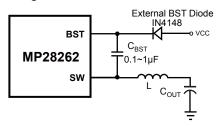

### TYPICAL APPLICATION

| Part Number* | Package   | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|--------------|-----------|-------------|----------------------------------------|

| MP28262EL    | 3x4 QFN14 | 28262       | –20°C to +85°C                         |

ORDERING INFORMATION

\* For Tape & Reel, add suffix –Z (e.g. MP28262EL–Z). For RoHS compliant packaging, add suffix –LF (e.g. MP28262EL–LF–Z)

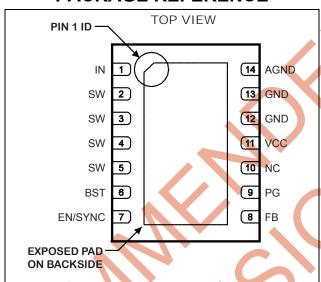

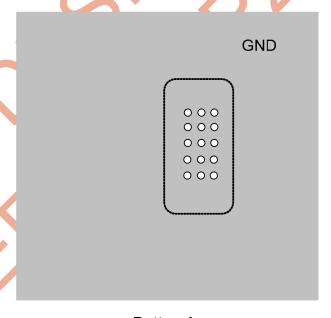

#### **PACKAGE REFERENCE**

# ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage V <sub>IN</sub> |                  | 22V                  |

|--------------------------------|------------------|----------------------|

| V <sub>SW</sub> 0.3            |                  |                      |

| V <sub>BS</sub>                |                  | V <sub>SW</sub> + 6V |

| All Other Pins                 | 0.3              | 8V to +6V            |

| Operating Temperature          | 20°C             | to +85°C             |

| Continuous Power Dissip        | ation $(T_A = +$ | 25°C) <sup>(2)</sup> |

|                                |                  | 2.6W                 |

| Junction Temperature           |                  | 150°C                |

| Lead Temperature               |                  | 260°C                |

| Storage Temperature            |                  |                      |

|                                |                  | (0)                  |

**Recommended Operating Conditions** (3) Supply Voltage V<sub>IN</sub>......4.5V to 21V Operating Junct. Temp (T<sub>J</sub>) .....-20°C to +125°C

| The | ermal Resistance <sup>(4)</sup> | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|-----|---------------------------------|-------------------------|-------------------------|------|

| 3x4 | QFN14                           | 48                      | . 11                    | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

© 2010 MPS. All Rights Reserved.

### **ELECTRICAL CHARACTERISTICS**

$V_{\text{IN}}$  = 12V,  $T_{\text{A}}$  = +25°C, unless otherwise noted.

| Parameters                                                 | Symbol                 | Condition                                      | Min | Тур  | Max | Units           |

|------------------------------------------------------------|------------------------|------------------------------------------------|-----|------|-----|-----------------|

| Supply Current (Shutdown)                                  | I <sub>IN</sub>        | V <sub>EN</sub> = 0V                           |     | 0    |     | μA              |

| Supply Current (Quiescent)                                 | I <sub>IN</sub>        | $V_{EN}$ = 2V, $V_{FB}$ = 1V                   |     | 0.7  |     | mA              |

| HS Switch On Resistance                                    | HS <sub>RDS-ON</sub>   |                                                |     | 190  |     | mΩ              |

| LS Switch On Resistance                                    | LS <sub>RDS-ON</sub>   |                                                |     | 90   |     | mΩ              |

| Switch Leakage                                             | SW <sub>LKG</sub>      | $V_{EN} = 0V, V_{SW} = 0V \text{ or } 12V$     |     | 0    | 10  | μΑ              |

| Current Limit (5)                                          | I <sub>LIMIT</sub>     |                                                | 3.5 |      |     | Α               |

| Oscillator Frequency                                       | F <sub>sw</sub>        | V <sub>FB</sub> = 0.75V                        | 0.9 | 1.1  | 1.3 | MHz             |

| Fold-back Frequency                                        | F <sub>FB</sub>        | V <sub>FB</sub> = 300mV                        |     | 0.25 |     | f <sub>SW</sub> |

| Maximum Duty Cycle                                         | $D_{MAX}$              | V <sub>FB</sub> = 700mV                        | 85  | 90   |     | %               |

| Sync Frequency Range                                       | F <sub>SYNC</sub>      |                                                | 0.4 |      | 2   | MHz             |

| Feedback Voltage                                           | $V_{FB}$               | $T_A = -20^{\circ}C \text{ to } + 85^{\circ}C$ | 789 | 805  | 821 | mV              |

| Feedback Current                                           | I <sub>FB</sub>        | V <sub>FB</sub> = 800mV                        |     | 10   | 50  | nA              |

| EN Rising Threshold                                        | V <sub>EN_RISING</sub> |                                                | 1.1 | 1.3  | 1.6 | V               |

| EN Threshold Hysteresis                                    | V <sub>EN_HYS</sub>    |                                                |     | 0.4  |     | V               |

| EN Input Current                                           | I <sub>EN</sub>        | V <sub>EN</sub> = 2V                           |     | 2    |     | μA              |

|                                                            |                        | $V_{EN} = 0V$                                  |     | 0    |     |                 |

| EN Turn Off Delay                                          | $EN_{Td\text{-}Off}$   |                                                |     | 5    |     | μŝ              |

| Power Good Rising Threshold                                | $PG_{Vth-Hi}$          |                                                |     | 0.9  |     | $V_{FB}$        |

| Power Good Falling Threshold                               | $PG_{Vth-Lo}$          |                                                |     | 0.7  |     | $V_{FB}$        |

| Power Good Delay                                           | $PG_{Td}$              |                                                |     | 20   |     | μs              |

| Power Good Sink Current Capability                         | $V_{PG}$               | Sink 4mA                                       |     | 7    | 0.4 | V               |

| Power Good Leakage Current                                 | I <sub>PG_LEAK</sub>   | $V_{PG} = 3.3V$                                |     |      | 10  | nA              |

| V <sub>IN</sub> Under Voltage Lockout Threshold Rising     |                        |                                                | 3.8 | 4.0  | 4.2 | V               |

| V <sub>IN</sub> Under Voltage Lockout Threshold Hysteresis | INUV <sub>HYS</sub>    |                                                |     | 880  |     | mV              |

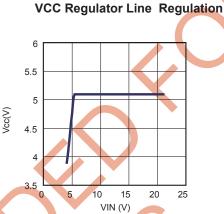

| VCC Regulator                                              | Vcc                    |                                                |     | 5    |     | V               |

| VCC Load Regulation                                        |                        | Icc=5mA                                        |     | 5    |     | %               |

| Soft-Start Period                                          |                        |                                                | 2   | 4    | 6.5 | ms              |

| Thermal Shutdown                                           | $T_{SD}$               |                                                |     | 150  |     | °C              |

| Notes                                                      |                        |                                                |     |      |     |                 |

#### Note:

5) Guaranteed by design.

# **PIN FUNCTIONS**

| Pin #   | Name           | Description                                                                                                                                                                                                                                                                                   |  |  |  |

|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | IN             | Supply Voltage. The MP28262 operates from a +4.5V to +21V input rail. C1 is needed to decouple the input rail. Use wide PCB traces and multiple vias to make the connection.                                                                                                                  |  |  |  |

| 2,3,4,5 | SW             | Switch Output. Use wide PCB traces and multiple vias to make the connection.                                                                                                                                                                                                                  |  |  |  |

| 6       | BST            | Bootstrap. A capacitor connected between SW and BS pins is required to form a floating supply across the high-side switch driver.                                                                                                                                                             |  |  |  |

| 7       | EN/SYNC        | EN=1 to enable the chip. External clock can be applied to EN pin for changing switching frequency. For automatic start-up, connect EN pin to VIN by proper EN resistor divider as Figure 2 shows.                                                                                             |  |  |  |

| 8       | FB             | Feedback. An external resistor divider from the output to GND, tapped to the FB pin, sets the output voltage. To prevent current limit run away during a short circuit fault condition the frequency fold-back comparator lowers the oscillator frequency when the FB voltage is below 500mV. |  |  |  |

| 9       | PG             | Power Good Output, the output of this pin is open drain. Power good threshold is 90% low to high and 70% high to low of regulation value.                                                                                                                                                     |  |  |  |

| 10      | NC             | No Internal Connection.                                                                                                                                                                                                                                                                       |  |  |  |

| 11      | VCC            | Bias Supply. Decouple with 0.1uF~0.22uF cap. And the capacitance should be no more than 0.22uF.                                                                                                                                                                                               |  |  |  |

| 12,13   | GND            | System Ground. This pin is the reference ground of the regulated output voltage. For this reason care must be taken in PCB layout.                                                                                                                                                            |  |  |  |

| 14      | AGND           | Signal Ground, AGND is not internally connected to System Ground, make sure AGND connected to system Ground in PCB layout.                                                                                                                                                                    |  |  |  |

|         | Exposed<br>Pad | No Internal Connection. It is recommended to connect exposed pad to GND plane for optimal thermal performance.                                                                                                                                                                                |  |  |  |

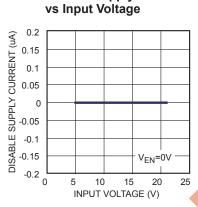

**Disable Supply Current**

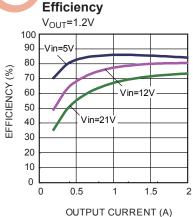

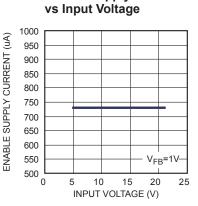

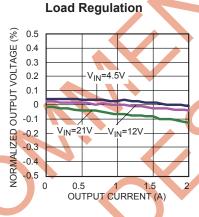

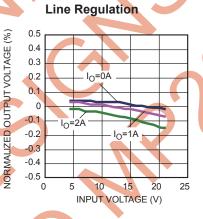

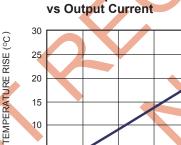

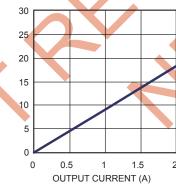

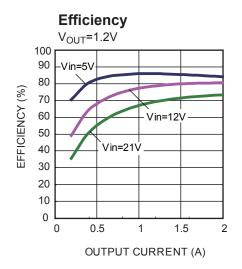

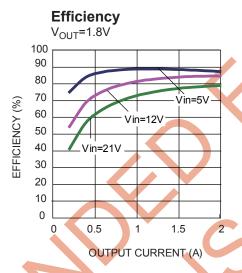

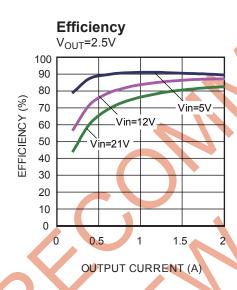

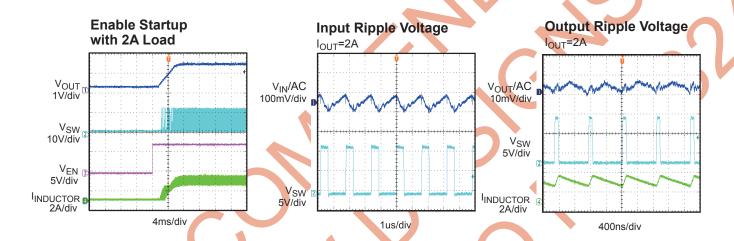

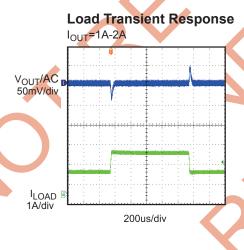

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$  = 12V,  $V_{OUT}$  = 1.2V, L = 0.95 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

**Enable Supply Current**

Case Temperature Rise

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 1.2V, L = 0.95 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 1.2V, L = 0.95 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

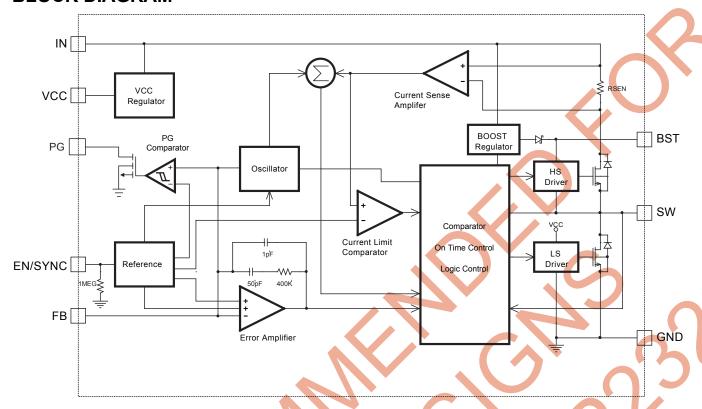

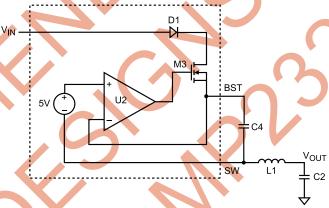

## **BLOCK DIAGRAM**

Figure 1—Functional Block Diagram

#### **OPERATION**

The MP28262 is a high frequency synchronous rectified step-down switch mode converter with built in internal power MOSFETs. It offers a very compact solution to achieve 2A continuous output current over a wide input supply range with excellent load and line regulation.

The MP28262 operates in a fixed frequency, peak current control mode to regulate the output voltage. A PWM cycle is initiated by the internal clock. The integrated high-side power MOSFET is turned on and remains on until its current reaches the value set by the COMP voltage. When the power switch is off, it remains off until the next clock cycle starts. If, in 90% of one PWM period, the current in the power MOSFET does not reach the COMP set current value, the power MOSFET will be forced to turn off

#### **Power Good Indicator**

When the FB is below 0.7V<sub>FB</sub>, the PG pin will be internally pulled low. When the FB is above 0.9V<sub>FB</sub>, the PG becomes an open-drain output.

#### **Internal Regulator**

Most of the internal circuitries are powered from the 5V internal regulator. This regulator takes the VIN input and operates in the full VIN range. When VIN is greater than 5.0V, the output of the regulator is in full regulation. When VIN is lower than 5.0V, the output decreases, 0.1uF ceramic capacitor for decoupling purpose is required.

#### **Error Amplifier**

The error amplifier compares the FB pin voltage with the internal FB reference (V<sub>FB</sub>) and outputs a current proportional to the difference between the two. This output current is then used to charge or discharge the internal compensation network to form the COMP voltage, which is used to control the power MOSFET current. The optimized internal compensation network minimizes the external component counts and simplifies the control loop design.

#### **Enable/Sync Control**

EN/Sync is a digital control pin that turns the regulator on and off. Drive EN high to turn on the regulator, drive it low to turn it off. There is an internal 1MEG resistor from EN/Sync to GND thus EN/Sync can be floated to shut down the chip.

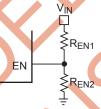

### 1) Enabled by external logic H/L signal

The chip starts up once the enable signal goes higher than EN/SYNC input high voltage (2V), and is shut down when the signal is lower than EN/SYNC input low voltage (0.4V). To disable the chip, EN must be pulled low for at least 5µs. The input is compatible with both CMOS and TTL. 2) Enabled by Vin through voltage divider.

Connect EN with VIN through a resistive voltage divider for automatic startup as the figure 2 shows.

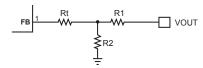

Figure 2—Enable Divider Circuit

Choose the value of the pull-up resistor Rent and pull-down resistor R<sub>EN2</sub> to reset the automatic start-up voltage:

$$V_{\text{IN\_START}} = V_{\text{EN\_RISING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN1}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN2}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN2}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{IN\_STOP}} = V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN2}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

$$V_{\text{EN-FALLING}} \cdot \frac{(R_{\text{EN2}} + R_{\text{EN2}} \parallel 1\text{M}\Omega)}{R_{\text{EN2}}}$$

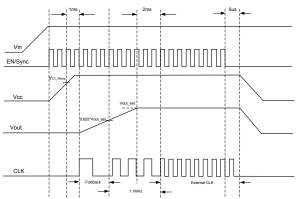

Figure 3—Startup Sequence Using EN Divider

3) Synchronized by External Sync Clock Signal The chip can be synchronized to external clock range from 400kHz up to 2MHz through this pin 2ms right after output voltage is set, with the internal clock rising edge synchronized to the external clock rising edge.

Figure 4—Startup Sequence Using External Sync Clock Signal

#### **Under-Voltage Lockout (UVLO)**

Under-voltage lockout (UVLO) is implemented to protect the chip from operating at insufficient supply voltage. The MP28262 UVLO comparator monitors the output voltage of the internal regulator, VCC. The UVLO rising threshold is about 4.0V while its falling threshold is a consistent 3.2V.

#### Internal Soft-Start

The soft-start is implemented to prevent the converter output voltage from overshooting during startup. When the chip starts, the internal circuitry generates a soft-start voltage (SS) ramping up from 0V to 1.2V. When it is lower than the internal reference (REF), SS overrides REF so the error amplifier uses SS as the reference. When SS is higher than REF, REF regains control. The SS time is internally fixed to 4ms.

#### Over-Current-Protection and Hiccup

The MP28262 has cycle-by-cycle over current limit when the inductor current peak value exceeds the set current limit threshold. Meanwhile, output voltage starts to drop until FB is below the Under-Voltage (UV) threshold, typically 30% below the reference. Once a UV is triggered, the MP28262 enters hiccup mode to periodically restart the part. This protection mode is especially useful when the output is dead-short to ground. The average short circuit current is greatly reduced to alleviate the thermal issue and to protect the regulator. The MP28262 exits the hiccup mode once the over current condition is removed.

#### **Thermal Shutdown**

Thermal shutdown is implemented to prevent the chip from operating at exceedingly high temperatures. When the silicon die temperature is higher than 150°C, it shuts down the whole chip. When the temperature is lower than its lower threshold, typically 140°C, the chip is enabled again.

#### Floating Driver and Bootstrap Charging

The floating power MOSFET driver is powered by an external bootstrap capacitor. This floating driver has its own UVLO protection. This UVLO's rising threshold is 2.2V with a hysteresis of 150mV. The bootstrap capacitor voltage is regulated internally by VIN through D1, M3, C4, L1 and C2 (Figure 5). If (VIN-VSW) is more than 5V, U2 will regulate M3 to maintain a 5V BST voltage across C4.

Figure 5—Internal Bootstrap Charging Circuit

#### Startup and Shutdown

If both VIN and EN are higher than their appropriate thresholds, the chip starts. The reference block starts first, generating stable reference voltage and currents, and then the internal regulator is enabled. The regulator provides stable supply for the remaining circuitries.

Three events can shut down the chip: EN low, VIN low and thermal shutdown. In the shutdown procedure, the signaling path is first blocked to avoid any fault triggering. The COMP voltage and the internal supply rail are then pulled down. The floating driver is not subject to this shutdown command.

#### APPLICATION INFORMATION

#### **Setting the Output Voltage**

The external resistor divider is used to set the output voltage (see Typical Application on page 1). The feedback resistor R1 also sets the feedback loop bandwidth with the internal compensation capacitor (see Typical Application on page 1). Choose R1 to be around  $40.2k\Omega$  for optimal transient response. R2 is then given by:

$$R2 = \frac{R1}{\frac{V_{OUT}}{V_{FR}} - 1}$$

The T-type network is highly recommended when Vo is low, as Figure 6 shows.

Figure 6— T-type Network

Table 1 lists the recommended T-type resistors value for common output voltages.

Table 1—Resistor Selection for Common **Output Voltages**

| V <sub>OUT</sub> (V) | R1<br>(kΩ) | R2<br>(kΩ) | Rt<br>(kΩ) | L<br>(uH) | C <sub>OUT</sub><br>(uF, Ceramic) |

|----------------------|------------|------------|------------|-----------|-----------------------------------|

| 1.05                 | 4.99       | 16.5       | 24.9       | 1-4.7     | 47                                |

| 1.2                  | 4.99       | 10.2       | 24.9       | 1-4.7     | 47                                |

| 1.5                  | 4.99       | 5.76       | 24.9       | 1-4.7     | 47                                |

| 1.8                  | 4.99       | 4.02       | 24.9       | 1-4.7     | 47                                |

| 2.5                  | 40.2       | 19.1       | 0          | 1-4.7     | 47                                |

| 3.3                  | 40.2       | 13         | 0          | 1-4.7     | 47                                |

| 5                    | 40.2       | 7.68       | 0          | 1-4.7     | 47                                |

The above feedback resistor table applies to a specific load capacitor condition as shown in the table 1. Other capacitive loading conditions will require different values.

#### Selecting the Inductor

A 1µH to 10µH inductor with a DC current rating of at least 25% percent higher than the maximum current is recommended for most applications. For highest efficiency, the inductor DC resistance should be less than  $15m\Omega$ . For most designs, the inductance value can be derived from the following equation.

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_{L} \times f_{OSC}}$$

Where  $\Delta I_1$  is the inductor ripple current.

Choose inductor ripple current approximately 30% if the maximum load current, 2A. The maximum inductor peak current is:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_L}{2}$$

Under light load conditions below 100mA, larger inductance is recommended for improved efficiency.

#### Selecting the Input Capacitor

The input current to the step-down converter is discontinuous, therefore a capacitor is required to supply the AC current to the step-down converter while maintaining the DC input voltage. Use low ESR capacitors for the best performance. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. For most applications, a 22µF capacitor is sufficient.

Since the input capacitor (C1) absorbs the input switching current it requires an adequate ripple current rating. The RMS current in the input capacitor can be estimated by:

$$I_{C1} = I_{LOAD} \times \sqrt{\frac{V_{OUT}}{V_{IN}}} \times 1 - \frac{V_{OUT}}{V_{IN}}$$

The worse case condition occurs at VIN = 2VOUT, where:

$$I_{C1} = \frac{I_{LOAD}}{2}$$

For simplification, choose the input capacitor whose RMS current rating greater than half of the maximum load current.

The input capacitor can be electrolytic, tantalum or ceramic. When electrolytic or tantalum capacitors is used, a small, high quality ceramic capacitor, i.e. 0.1µF, should be placed as close to the IC as possible. When using ceramic capacitors, make sure that they have enough capacitance to provide sufficient charge to prevent excessive voltage ripple at input. The input voltage ripple caused by capacitance can be estimated by:

$$\Delta V_{\text{IN}} = \frac{I_{\text{LOAD}}}{f_{\text{S}} \times \text{C1}} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

#### **Selecting the Output Capacitor**

The output capacitor (C2) is required to maintain the DC output voltage. Ceramic, tantalum, or low ESR electrolytic capacitors are recommended. Low ESR capacitors are preferred to keep the output voltage ripple low. The output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_S \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times \left(R_{ESR} + \frac{1}{8 \times f_S \times C2}\right)$$

Where L is the inductor value and  $R_{\text{ESR}}$  is the equivalent series resistance (ESR) value of the output capacitor.

In the case of ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance. The output voltage ripple is mainly caused by the capacitance. For simplification, the output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 \times f_S^2 \times L \times C2} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

In the case of tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated to:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_S \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times R_{ESR}$$

The characteristics of the output capacitor also affect the stability of the regulation system. The MP28262 can be optimized for a wide range of capacitance and ESR values.

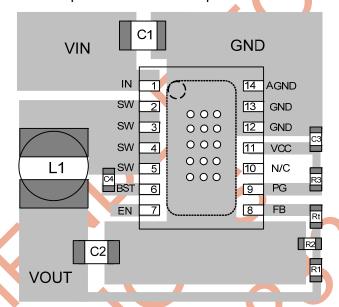

#### **PCB Layout**

PCB layout is very important to achieve stable operation. Please follow these guidelines and take Figure 7 for references.

- 1) Keep the connection of input ground and GND pin as short and wide as possible.

- Keep the connection of input capacitor and IN pin as short and wide as possible.

- 3) Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close to the chip as possible.

- 4) Route SW away from sensitive analog areas such as FB.

- 5) Connect IN, SW, and especially GND respectively to a large copper area to cool the chip to improve thermal performance and long-term reliability.

- 6) Adding RC snubber circuit from IN pin to SW pin can reduce SW spikes.

Top Layer

Bottom Layer

Figure 7—PCB Layout

#### **External Bootstrap Diode**

An external bootstrap diode may enhance the efficiency of the regulator, the applicable conditions of external BST diode is:

• Duty cycle is high:  $D = \frac{V_{OUT}}{V_{IN}} > 65\%$

In this case, an external BST diode is recommended from the VCC pin to BST pin, as shown in Figure 8

Figure 8—Add Optional External Bootstrap

Diode to Enhance Efficiency

The recommended external BST diode is IN4148, and the BST cap is  $0.1\sim1\mu$ F.

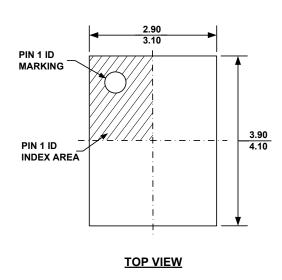

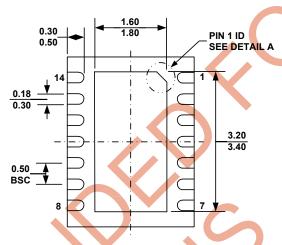

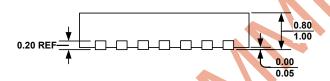

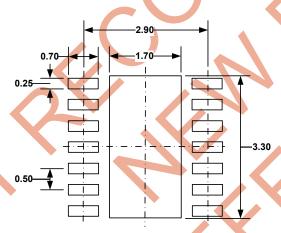

### **PACKAGE INFORMATION**

### **BOTTOM VIEW**

#### SIDE VIEW

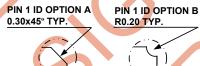

DETAIL A

### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) JEDEC REFERENCE IS MO-229, VARIATION VGED-3.

- 5) DRAWING IS NOT TO SCALE.

RECOMMENDED LAND PATTERN

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Monolithic Power Systems (MPS): MP28262EL-LF-Z