32768-word × 8-bit Electrically Erasable and Programmable CMOS ROM

## **HITACHI**

ADE-203-410C (Z) Rev. 3.0 May. 20, 1997

#### **Description**

The Hitachi HN58C256A and HN58C257A are electrically erasable and programmable ROMs organized as 32768-word  $\times$  8-bit. They have realized high speed low power consumption and high reliability by employing advanced MNOS memory technology and CMOS process and circuitry technology. They also have a 64-byte page programming function to make their write operations faster.

#### **Features**

Single 5 V supply: 5 V ±10%

Access time: 85 ns/100 ns (max)

Power dissipation

— Active: 20 mW/MHz, (typ)— Standby: 110 μW (max)

• On-chip latches: address, data,  $\overline{CE}$ ,  $\overline{OE}$ ,  $\overline{WE}$

Automatic byte write: 10 ms max

• Automatic page write (64 bytes): 10 ms max

• Ready/Busy (only the HN58C257A series)

Data polling and Toggle bit

• Data protection circuit on power on/off

Conforms to JEDEC byte-wide standard

Reliable CMOS with MNOS cell technology

• 10<sup>5</sup> erase/write cycles (in page mode)

10 years data retention

Software data protection

• Write protection by  $\overline{RES}$  pin (only the HN58C257A series)

• Industrial versions (Temperatur range: −20 to 85°C and −40 to 85°C) are also available.

#### **Ordering Information**

| Type No.                         | Access time     | Package                                  |

|----------------------------------|-----------------|------------------------------------------|

| HN58C256AP-85<br>HN58C256AP-10   | 85 ns<br>100 ns | 600 mil 28-pin plastic DIP (DP-28)       |

| HN58C256AFP-85<br>HN58C256AFP-10 | 85 ns<br>100 ns | 400 mil 28-pin plastic SOP (FP-28D)      |

| HN58C256AT-85<br>HN58C256AT-10   | 85 ns<br>100 ns | 28-pin plastic TSOP (TFP-28DB)           |

| HN58C257AT-85<br>HN58C257AT-10   | 85 ns<br>100 ns | 8 × 14 mm 32-pin plastic TSOP (TFP-32DA) |

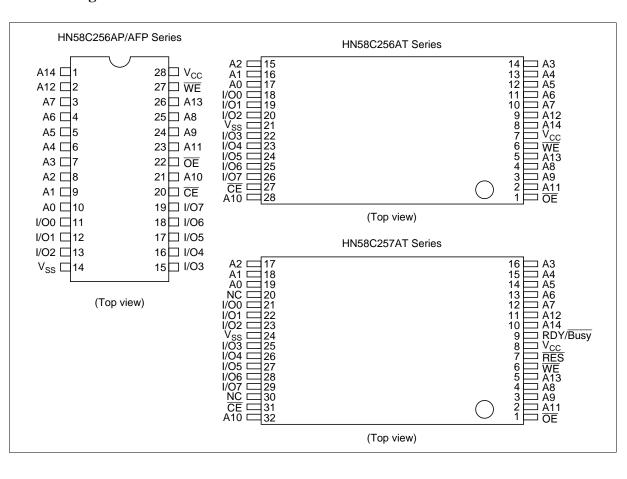

#### **Pin Arrangement**

#### **Pin Description**

| Pin name        | Function          |

|-----------------|-------------------|

| A0 to A14       | Address input     |

| I/O0 to I/O7    | Data input/output |

| ŌĒ              | Output enable     |

| CE              | Chip enable       |

| WE              | Write enable      |

| V <sub>cc</sub> | Power supply      |

| V <sub>SS</sub> | Ground            |

| RDY/Busy*1      | Ready busy        |

| RES*1           | Reset             |

| NC              | No connection     |

Note: 1. This function is supported by only the HN58C257A series.

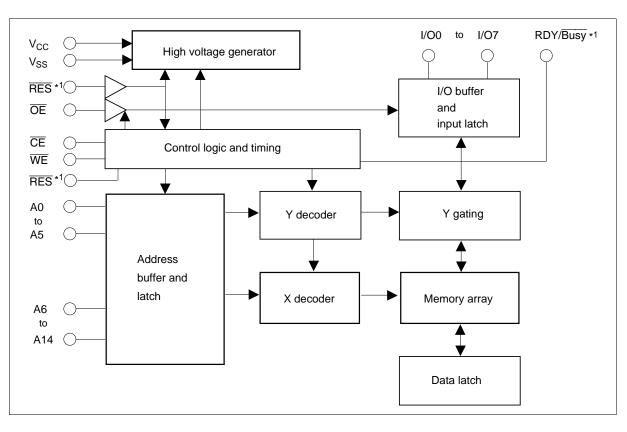

#### **Block Diagram**

Note: This function is supported by only the HN58C257A series.

#### **Operation Table**

| Operation     | CE              | OE              | WE              | RES*3           | RDY/Busy*3                | I/O         |

|---------------|-----------------|-----------------|-----------------|-----------------|---------------------------|-------------|

| Read          | $V_{IL}$        | $V_{\text{IL}}$ | $V_{\text{IH}}$ | $V_H^{*1}$      | High-Z                    | Dout        |

| Standby       | V <sub>IH</sub> | X*2             | ×               | ×               | High-Z                    | High-Z      |

| Write         | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>H</sub>  | High-Z to V <sub>oL</sub> | Din         |

| Deselect      | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>H</sub>  | High-Z                    | High-Z      |

| Write inhibit | ×               | ×               | V <sub>IH</sub> | ×               | _                         | _           |

|               | ×               | V <sub>IL</sub> | ×               | ×               | _                         | _           |

| Data polling  | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>H</sub>  | V <sub>OL</sub>           | Dout (I/O7) |

| Program reset | ×               | ×               | ×               | V <sub>IL</sub> | High-Z                    | High-Z      |

Notes: 1. Refer to the recommended DC operating condition.

2. x: Don't care

3. This function is supported by only the HN58C257A series.

#### **Absolute Maximum Ratings**

| Parameter                                        | Symbol          | Value            | Unit |

|--------------------------------------------------|-----------------|------------------|------|

| Power supply voltage rerative to V <sub>ss</sub> | V <sub>cc</sub> | -0.6 to +7.0     | V    |

| Input voltage rerative to V <sub>SS</sub>        | Vin             | -0.5*1 to +7.0*3 | V    |

| Operationg temperature range*2                   | Topr            | 0 to +70         | °C   |

| Storage temperature range                        | Tstg            | -55 to +125      | °C   |

Notes: 1. Vin min = -3.0 V for pulse width  $\le 50$  ns

2. Including electrical characteristics and data retention

3. Should not exceed  $V_{CC}$  + 1 V.

#### **Recommended DC Operating Conditions**

| Parameter             | Symbol                       | Min                   | Тур | Max                   | Unit  |

|-----------------------|------------------------------|-----------------------|-----|-----------------------|-------|

| Supply voltage        | V <sub>cc</sub>              | 4.5                   | 5.0 | 5.5                   | V     |

|                       | $\overline{V_{\mathtt{SS}}}$ | 0                     | 0   | 0                     | V     |

| Input voltage         | V <sub>IL</sub>              | -0.3*1                | _   | 0.8                   | V     |

|                       | $V_{IH}$                     | 2.2                   | _   | V <sub>cc</sub> + 0.3 | 3*2 V |

|                       | V <sub>H</sub> *3            | V <sub>cc</sub> - 0.5 | _   | V <sub>cc</sub> + 1.0 | ) V   |

| Operating temperature | Topr                         | 0                     | _   | 70                    | °C    |

Notes: 1.  $V_{IL}$  min: -1.0 V for pulse width  $\leq$  50 ns.

2.  $V_{IH}$  max:  $V_{CC}$  + 1.0 V for pulse width  $\leq$  50 ns.

3. This function is supported by only the HN58C257A series.

#### **DC Characteristics** (Ta = 0 to +70°C, $V_{CC} = 5.0 \text{ V} \pm 10\%$ )

| Parameter                         | Symbol           | Min | Тур | Max             | Unit | Test conditions                                                       |

|-----------------------------------|------------------|-----|-----|-----------------|------|-----------------------------------------------------------------------|

| Input leakage current             | I <sub>LI</sub>  | _   | _   | 2* <sup>1</sup> | μΑ   | $V_{CC} = 5.5 \text{ V}, \text{ Vin} = 5.5 \text{ V}$                 |

| Output leakage current            | I <sub>LO</sub>  | _   | _   | 2               | μΑ   | V <sub>CC</sub> = 5.5 V, Vout = 5.5/0.4 V                             |

| Standby V <sub>cc</sub> current   | I <sub>CC1</sub> | _   | _   | 20              | μΑ   | CE = V <sub>cc</sub>                                                  |

|                                   | I <sub>CC2</sub> | _   | _   | 1               | mA   | CE = V <sub>IH</sub>                                                  |

| Operating V <sub>cc</sub> current | I <sub>CC3</sub> | _   | _   | 12              | mA   | lout = 0 mA, Duty = 100%,<br>Cycle = 1 $\mu$ s at $V_{cc}$ = 5.5 V    |

|                                   |                  | _   | _   | 30              | mA   | lout = 0 mA, Duty = 100%,<br>Cycle = 85 ns at V <sub>cc</sub> = 5.5 V |

| Output low voltage                | V <sub>OL</sub>  | _   | _   | 0.4             | V    | I <sub>OL</sub> = 2.1 mA                                              |

| Output high voltage               | V <sub>OH</sub>  | 2.4 | _   | _               | V    | $I_{OH} = -400 \ \mu A$                                               |

Note: 1.  $I_{LI}$  on  $\overline{RES}$  = 100  $\mu$ A max (only the HN58C257A series)

### **Capacitance** (Ta = +25°C, f = 1 MHz)

| Parameter            | Symbol | Min | Тур | Max | Unit | Test conditions |

|----------------------|--------|-----|-----|-----|------|-----------------|

| Input capacitance*1  | Cin    | _   | _   | 6   | pF   | Vin = 0 V       |

| Output capacitance*1 | Cout   | _   | _   | 12  | pF   | Vout = 0 V      |

Note: 1. This parameter is periodically sampled and not 100% tested.

AC Characteristics (Ta = 0 to +70°C,  $V_{CC} = 5 \text{ V} \pm 10\%$ )

#### **Test Conditions**

• Input pulse levels: 0.4 V to 3.0 V

0 V to V<sub>CC</sub> (RES pin\*2)

• Input rise and fall time:  $\leq 20 \text{ ns}$

• Input timing reference levels: 0.8, 2.0 V

• Output load: 1TTL Gate +100 pF

• Output reference levels: 1.5 V, 1.5 V

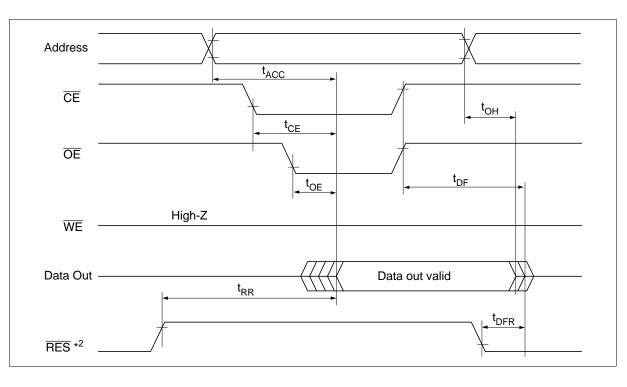

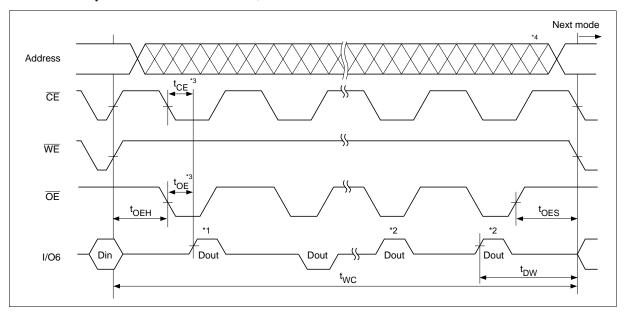

#### **Read Cycle**

|                                |                  | HN58C | 256A/HN | 158C257 | A   |      |                                                                                             |

|--------------------------------|------------------|-------|---------|---------|-----|------|---------------------------------------------------------------------------------------------|

|                                |                  | -85   |         | -10     |     | _    |                                                                                             |

| Parameter                      | Symbol           | Min   | Max     | Min     | Max | Unit | Test conditions                                                                             |

| Address to output delay        | t <sub>ACC</sub> | _     | 85      | _       | 100 | ns   | $ \overline{\overline{CE}} = \overline{OE} = V_{IL}, \\ \overline{WE} = V_{IH} $            |

| CE to output delay             | t <sub>CE</sub>  | _     | 85      | _       | 100 | ns   | $\overline{OE} = V_{IL}, \overline{WE} = V_{IH}$                                            |

| OE to output delay             | t <sub>oe</sub>  | 10    | 40      | 10      | 50  | ns   | $\overline{CE} = V_{IL}, \overline{WE} = V_{IH}$                                            |

| Address to output hold         | t <sub>oh</sub>  | 0     | _       | 0       | _   | ns   | $ \overline{\overline{CE}} = \overline{OE} = V_{IL}, \\ \overline{WE} = V_{IH} $            |

| OE (CE) high to output float*1 | t <sub>DF</sub>  | 0     | 40      | 0       | 40  | ns   | $\overline{CE} = V_{IL}, \overline{WE} = V_{IH}$                                            |

| RES low to output float*1,2    | t <sub>DFR</sub> | 0     | 350     | 0       | 350 | ns   | $ \overline{\overline{CE}} = \overline{OE} = V_{IL}, \\ \overline{WE} = V_{IH} $            |

| RES to output delay*2          | t <sub>RR</sub>  | 0     | 450     | 0       | 450 | ns   | $ \overline{\overline{CE}} = \overline{\overline{OE}} = V_{IL}, \\ \overline{WE} = V_{IH} $ |

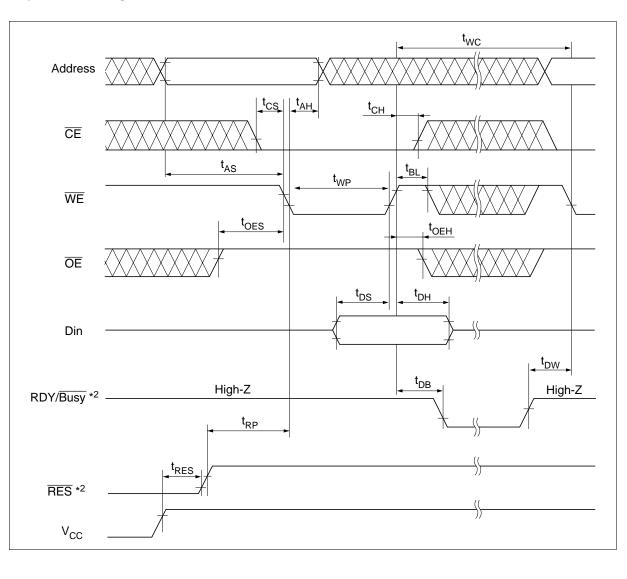

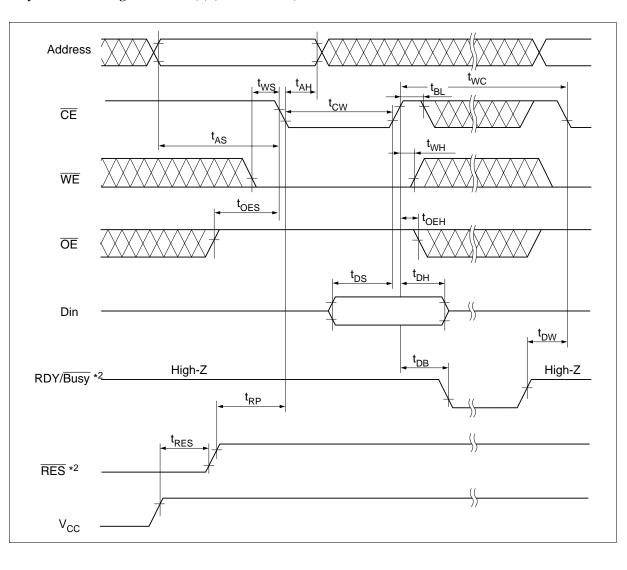

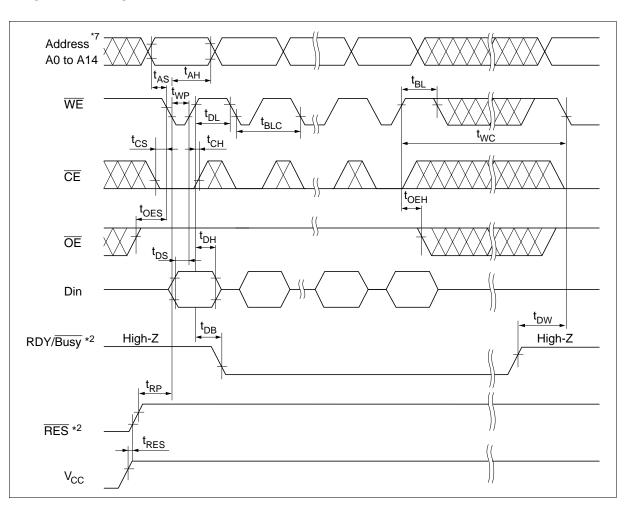

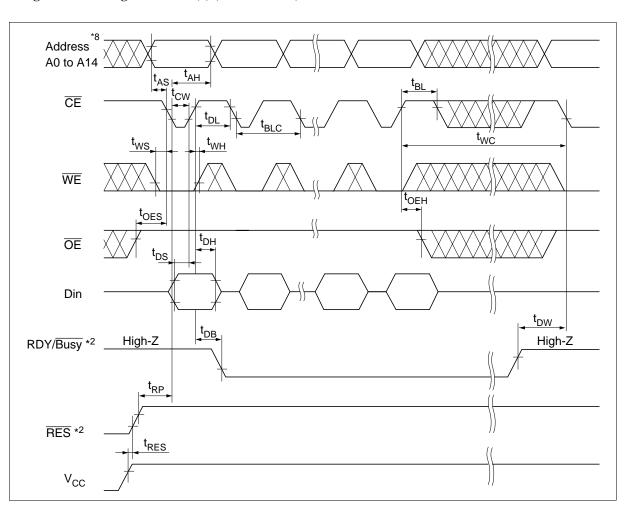

#### Write Cycle

| Parameter                              | Symbol           | Min*³ | Тур | Max  | Unit | Test conditions |

|----------------------------------------|------------------|-------|-----|------|------|-----------------|

| Address setup time                     | t <sub>AS</sub>  | 0     | _   | _    | ns   | _               |

| Address hold time                      | t <sub>AH</sub>  | 50    | _   | _    | ns   |                 |

| CE to write setup time (WE controlled) | t <sub>cs</sub>  | 0     | _   | _    | ns   |                 |

| CE hold time (WE controlled)           | t <sub>CH</sub>  | 0     | _   | _    | ns   |                 |

| WE to write setup time (CE controlled) | t <sub>ws</sub>  | 0     | _   | _    | ns   |                 |

| WE hold time (CE controlled)           | t <sub>wH</sub>  | 0     | _   | _    | ns   |                 |

| OE to write setup time                 | t <sub>OES</sub> | 0     | _   | _    | ns   |                 |

| OE hold time                           | t <sub>OEH</sub> | 0     | _   | _    | ns   |                 |

| Data setup time                        | t <sub>DS</sub>  | 50    | _   | _    | ns   |                 |

| Data hold time                         | t <sub>DH</sub>  | 0     | _   | _    | ns   |                 |

| WE pulse width (WE controlled)         | $t_{WP}$         | 100   | _   | _    | ns   |                 |

| CE pulse width (CE controlled)         | t <sub>cw</sub>  | 100   | _   | _    | ns   |                 |

| Data latch time                        | t <sub>DL</sub>  | 50    | _   | _    | ns   |                 |

| Byte load cycle                        | t <sub>BLC</sub> | 0.2   | _   | 30   | μs   |                 |

| Byte load window                       | t <sub>BL</sub>  | 100   | _   | _    | μs   |                 |

| Write cycle time                       | t <sub>wc</sub>  | _     | _   | 10*4 | ms   |                 |

| Time to device busy                    | t <sub>DB</sub>  | 120   | _   | _    | ns   |                 |

| Write start time                       | t <sub>DW</sub>  | 0*5   | _   | _    | ns   |                 |

| Reset protect time*2                   | t <sub>RP</sub>  | 100   | _   | _    | μs   |                 |

| Reset high time*2,6                    | t <sub>RES</sub> | 1     | _   | _    | μs   |                 |

|                                        |                  |       |     |      |      |                 |

Notes: 1.  $t_{DF}$  and  $t_{DFR}$  are defined as the time at which the outputs achieve the open circuit conditions and are no longer driven.

- 2. This function is supported by only the HN58C257A series.

- 3. Use this device in longer cycle than this value.

- t<sub>wc</sub> must be longer than this value unless polling techniques or RDY/Busy (only the HN58C257A series) are used. This device automatically completes the internal write operation within this value.

- Next read or write operation can be initiated after t<sub>DW</sub> if polling techniques or RDY/Busy (only the HN58C257A series) are used.

- 6. This parameter is sampled and not 100% tested.

- A6 through A14 are page address and these addresses are latched at the first falling edge of WE.

- 8. A6 through A14 are page address and these addresses are latched at the first falling edge of  $\overline{\text{CE}}$ .

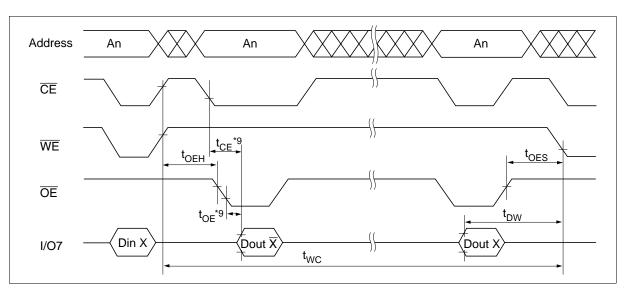

- 9. See AC read characteristics.

#### **Read Timing Waveform**

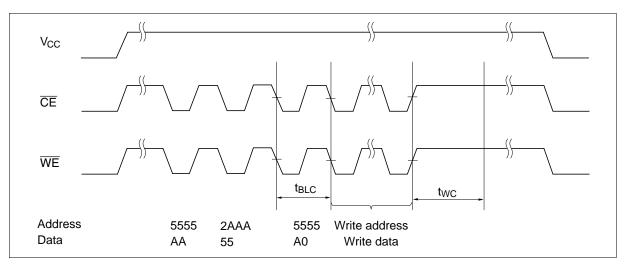

#### Byte Write Timing Waveform (1) (WE Controlled)

#### Byte Write Timing Waveform (2) (CE Controlled)

#### Page Write Timing Waveform (1) (WE Controlled)

#### Page Write Timing Waveform (2) (\overline{CE} Controlled)

## **Data** Polling Timing Waveform

#### Toggle bit

This device provide another function to determine the internal programming cycle. If the EEPROM is set to read mode during the internal programming cycle, I/O6 will charge from "1" to "0" (toggling) for each read. When the internal programming cycle is finished, toggling of I/O6 will stop and the device can be accessible for next read or program.

#### Toggle bit Waveform

Notes: 1. I/O6 beginning state is "1".

- 2. I/O6 ending state will vary.

- 3. See AC read characteristics.

- 4. Any address location can be used, but the address must be fixed.

#### Software Data Protection Timing Waveform (1) (in protection mode)

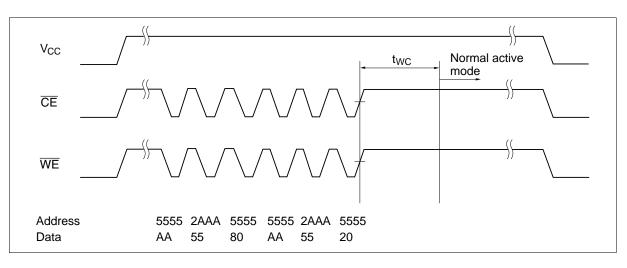

#### **Software Data Protection Timing Waveform (2)** (in non-protection mode)

#### **Functional Description**

#### **Automatic Page Write**

Page-mode write feature allows 1 to 64 bytes of data to be written into the EEPROM in a single write cycle. Following the initial byte cycle, an additional 1 to 63 bytes can be written in the same manner. Each additional byte load cycle must be started within 30  $\mu$ s from the preceding falling edge of  $\overline{WE}$  or  $\overline{CE}$ . When  $\overline{CE}$  or  $\overline{WE}$  is high for 100  $\mu$ s after data input, the EEPROM enters write mode automatically and the input data are written into the EEPROM.

#### Data Polling

Data polling indicates the status that the EEPROM is in a write cycle or not. If EEPROM is set to read mode during a write cycle, an inversion of the last byte of data outputs from I/O7 to indicate that the EEPROM is performing a write operation.

#### **RDY/Busy Signal** (only the HN58C257A series)

RDY/ $\overline{Busy}$  signal also allows status of the EEPROM to be determined. The RDY/ $\overline{Busy}$  signal has high impedance except in write cycle and is lowered to  $V_{OL}$  after the first write signal. At the end of a write cycle, the RDY/ $\overline{Busy}$  signal changes state to high impedance.

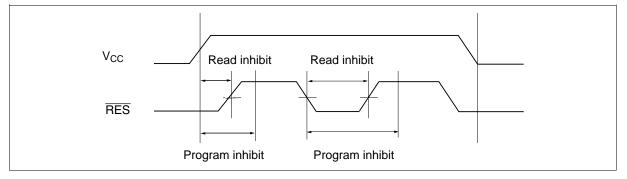

#### **RES** Signal (only the HN58C257A series)

When  $\overline{RES}$  is low, the EEPROM cannot be read or programmed. Therefore, data can be protected by keeping  $\overline{RES}$  low when  $V_{CC}$  is switched.  $\overline{RES}$  should be high during read and programming because it doesn't provide a latch function.

#### $\overline{\mathrm{WE}}$ , $\overline{\mathrm{CE}}$ Pin Operation

During a write cycle, addresses are latched by the falling edge of  $\overline{WE}$  or  $\overline{CE}$ , and data is latched by the rising edge of  $\overline{WE}$  or  $\overline{CE}$ .

#### Write/Erase Endurance and Data Retention Time

The endurance is 10<sup>5</sup> cycles in case of the page programming and 10<sup>4</sup> cycles in case of the byte programming (1% cumulative failure rate). The data retention time is more than 10 years when a device is page-programmed less than 10<sup>4</sup> cycles.

#### **Data Protection**

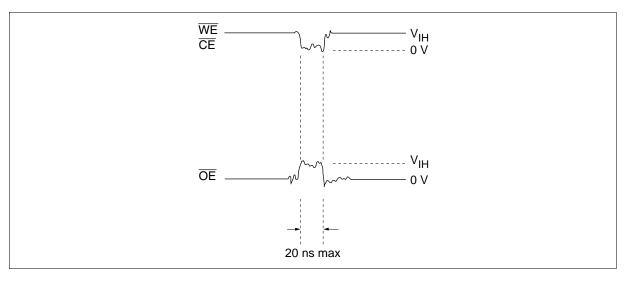

1. Data Protection against Noise on Control Pins ( $\overline{CE}$ ,  $\overline{OE}$ ,  $\overline{WE}$ ) during Operation During readout or standby, noise on the control pins may act as a trigger and turn the EEPROM to programming mode by mistake.

To prevent this phenomenon, this device has a noise cancelation function that cuts noise if its width is 20 ns or less.

Be careful not to allow noise of a width of more than 20 ns on the control pins.

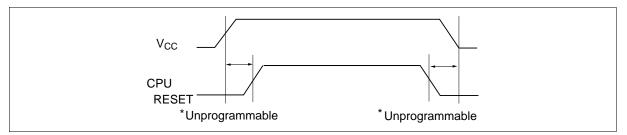

#### 2. Data Protection at V<sub>CC</sub> On/Off

When  $V_{CC}$  is turned on or off, noise on the control pins generated by external circuits (CPU, etc) may act as a trigger and turn the EEPROM to program mode by mistake. To prevent this unintentional programming, the EEPROM must be kept in an unprogrammable state while the CPU is in an unstable state.

Note: The EEPROM shoud be kept in unprogrammable state during  $V_{\rm CC}$  on/off by using CPU RESET signal.

#### (1) Protection by $\overline{CE}$ , $\overline{OE}$ , $\overline{WE}$

To realize the unprogrammable state, the input level of control pins must be held as shown in the table below.

| CE | V <sub>cc</sub> | ×               | ×               |

|----|-----------------|-----------------|-----------------|

| ŌĒ | ×               | V <sub>ss</sub> | ×               |

| WE | ×               | ×               | V <sub>cc</sub> |

×: Don't care.

$V_{cc}$ : Pull-up to  $V_{cc}$  level.

$V_{ss}$ : Pull-down to  $V_{ss}$  level.

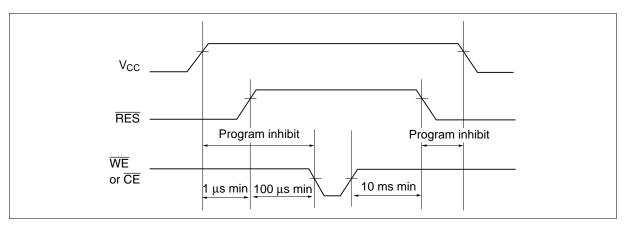

#### (2) Protection by $\overline{RES}$ (only the HN58C257A series)

The unprogrammable state can be realized by that the CPU's reset signal inputs directly to the EEPROM's  $\overline{RES}$  pin.  $\overline{RES}$  should be kept  $V_{SS}$  level during  $V_{CC}$  on/off.

The EEPROM breaks off programming operation when  $\overline{RES}$  becomes low, programming operation doesn't finish correctly in case that  $\overline{RES}$  falls low during programming operation.  $\overline{RES}$  should be kept high for 10 ms after the last data input.

#### 3. Software data protection

To prevent unintentional programming, this device has the software data protection (SDP) mode. The SDP is enabled by inputting the following 3 bytes code and write data. SDP is not enabled if only the 3 bytes code is input. To program data in the SDP enable mode, 3 bytes code must be input before write data.

| Address       | Data                           |

|---------------|--------------------------------|

| 5555          | AA<br>↓                        |

| 2AAA          | 55<br>↓                        |

| 5555<br>↓     | A0<br>↓                        |

| Write address | Write data } Normal data input |

The SDP mode is disabled by inputting the following 6 bytes code. Note that, if data is input in the SDP disable cycle, data can not be written.

| Address | Data               |

|---------|--------------------|

| 5555    | AA                 |

| 2AAA    | 5 <del>5</del> 5   |

| 5555    | 80                 |

| 5555    | AĂ                 |

| 2AAA    | 55<br><del>-</del> |

| 5555    | 20                 |

The software data protection is not enabled at the shipment.

Note: There are some differences between Hitachi's and other company's for enable/disable sequence of software data protection. If there are any questions, please contact with Hitachi sales offices.

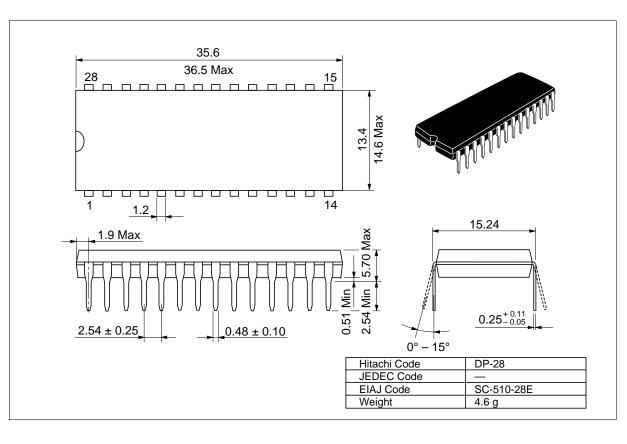

#### **Package Dimensions**

#### HN58C256AP Series (DP-28)

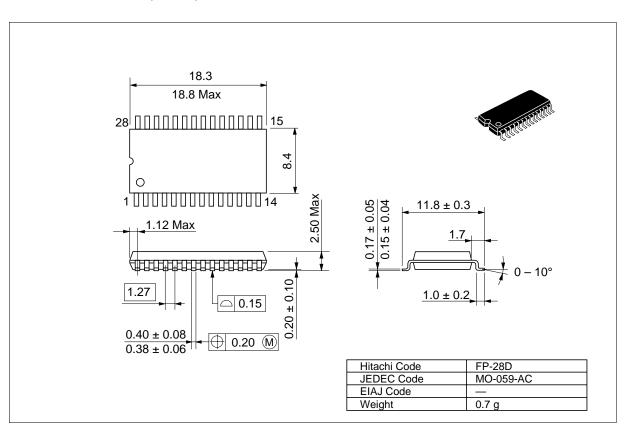

#### HN58C256AFP Series (FP-28D)

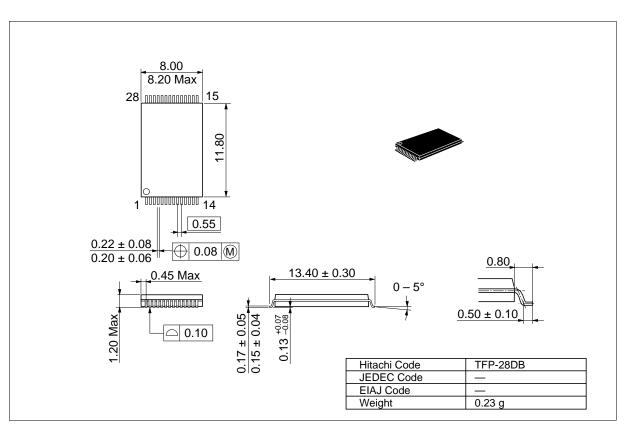

#### HN58C256AT Series (TFP-28DB)

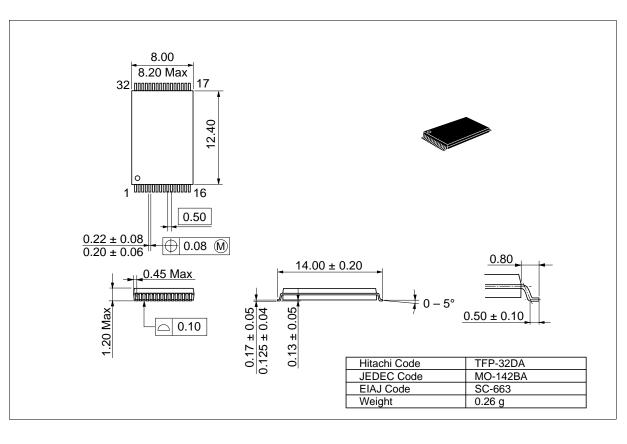

#### HN58C257AT Series (TFP-32DA)

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## HITACHI

#### Hitachi, Ltd.

Semiconductor & IC Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100, Japan Tel: Tokyo (03) 3270-2111

Fax: (03) 3270-5109

#### For further information write to:

Hitachi America, Ltd. Semiconductor & IC Div. 2000 Sierra Point Parkway Brisbane, CA. 94005-1835 U S A

Tel: 415-589-8300 Fax: 415-583-4207 Hitachi Europe GmbH Electronic Components Group Continental Europe Dornacher Straße 3 D-85622 Feldkirchen München

Tel: 089-9 91 80-0 Fax: 089-9 29 30 00 Hitachi Europe Ltd.

Electronic Components Div.

Northern Europe Headquarters

Whitebrook Park

Lower Cookham Road

Maidenhead

Berkshire SL6 8YA

United Kingdom

Tel: 0628-585000

Fax: 0628-778322

Hitachi Tower Singapore 0104 Tel: 535-2100 Fax: 535-1533

Hitachi Asia Pte. Ltd.

16 Collyer Quay #20-00

Hitachi Asia (Hong Kong) Ltd. Unit 706, North Tower, World Finance Centre, Harbour City, Canton Road Tsim Sha Tsui, Kowloon Hong Kong

Tel: 27359218 Fax: 27306071

Copyright © Hitachi, Ltd., 1997. All rights reserved. Printed in Japan.

## **Revision Record**

| Rev. | Date          | Contents of Modification                                                                                                                                                                                                                                                                                                                                                                                                                     | Drawn by | Approved by |

|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|

| 0.0  | Jun. 19, 1995 | Initial issue                                                                                                                                                                                                                                                                                                                                                                                                                                | Y. Nagai | T. Muto     |

| 1.0  | May. 17, 1996 | Change of format Absolute Maximun Ratings Addition of note 4 Recommended DC Operating Conditions $V_{IH}$ (min): $3.0 \text{ V}$ to $2.2 \text{ V}$ AC Characteristics $V_{OH}$ (min): $V_{CC} \times 0.8 \text{ V}$ to $2.4 \text{ V}$ AC Characteristics Input pulse levels: $0 \text{ V}$ to $3.0 \text{ V}$ to $0.4 \text{ V}$ to $3.0 \text{ V}$ Data Polling Timing Waveform Addition of note 1 Toggle bit Waveform Addition of note 4 | Y. Nagai | T. Wada     |

| 2.0  | Feb. 27, 1997 | Recommended DC Operating Conditions V <sub>IL</sub> (max): 0.6 V to 0.8 V Functional Description Data Protection 3: Addition of note                                                                                                                                                                                                                                                                                                         | Y. Nagai | K. Furusawa |

| 3.0  | May. 20, 1997 | Functional Description Data Protection 3: Change of Description                                                                                                                                                                                                                                                                                                                                                                              |          |             |