# **ICs for Communications**

ISDN PC Adapter Circuit IPAC

**PSB 2115 Version 1.1**

Data Sheet 11.97

| PSB 2115<br>Revision His         | story:                      | Current Version: 11.97                       |

|----------------------------------|-----------------------------|----------------------------------------------|

| Previous Ver                     | sion: Prelimir              | nary Data Sheet 03.97                        |

| Page<br>(in previous<br>Version) | Page<br>(in new<br>Version) | Subjects (major changes since last revision) |

|                                  |                             |                                              |

|                                  |                             |                                              |

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide: see our webpage at http://www.siemens.de/Semiconductor/address/address.htm.

Edition 11.97

Published by Siemens AG, HL TS,

Balanstraße 73,

81541 München

© Siemens AG 1997. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| Table of Contents |                                                          | Page       |

|-------------------|----------------------------------------------------------|------------|

| 1                 | Overview                                                 | 14         |

| 1.1               | Features                                                 |            |

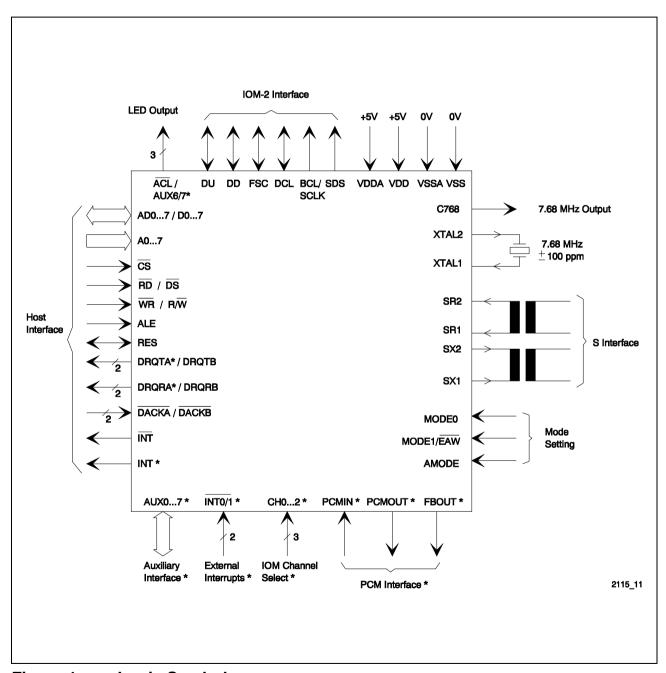

| 1.2               | Logic Symbol                                             |            |

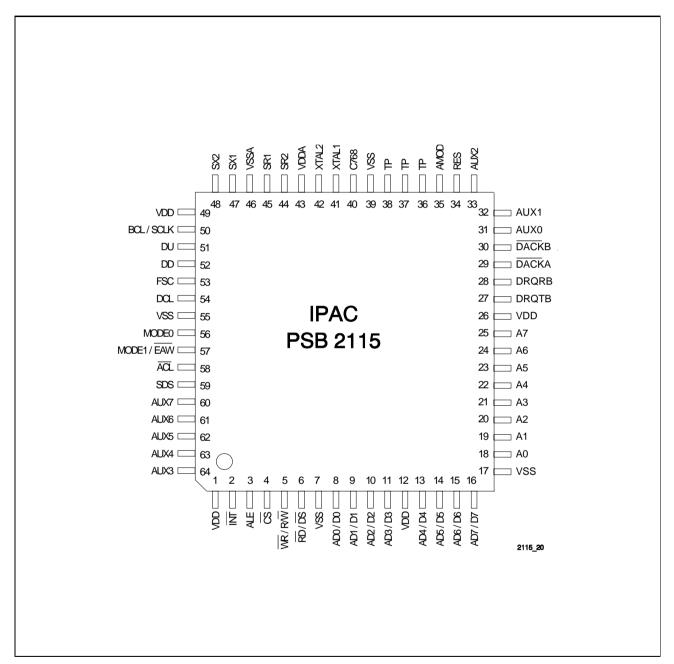

| 1.3               | Pin Configuration                                        |            |

| 1.4               | Pin Definitions and Functions                            |            |

| 1.5               | Functional Block Diagram                                 |            |

| 1.6               | System Integration                                       |            |

| 2                 | Functional Description                                   | 32         |

|                   |                                                          |            |

| 2.1               | B-Channel Operation                                      |            |

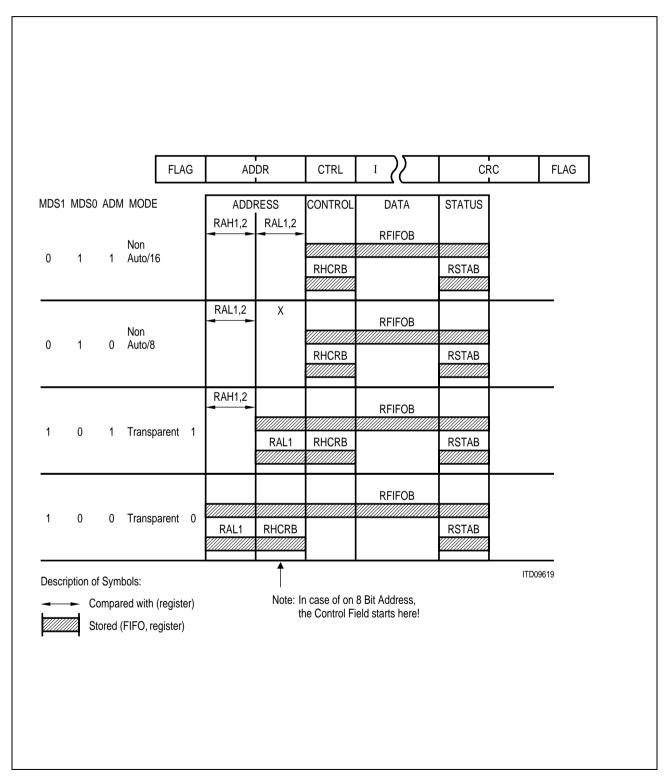

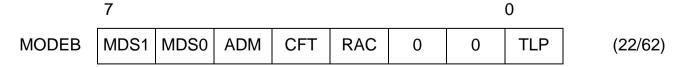

| 2.1.1             | Non-Auto Mode (MODEB: MDS1, MDS0 = 01)                   |            |

| 2.1.2             | Transparent Mode 1 (MODEB: MDS1, MDS0, ADM = 101)        |            |

| 2.1.3             | Transparent Mode 0 (MODEB: MDS1, MDS0, ADM = 100)        |            |

| 2.1.4             | Extended Transparent Modes 0, 1 (MODEB: MDS1, MDS0 = 11) |            |

| 2.1.5             | Receive Data Flow                                        |            |

| 2.1.6             | Transmit Data Flow                                       |            |

| 2.1.7             | Serial Interface                                         |            |

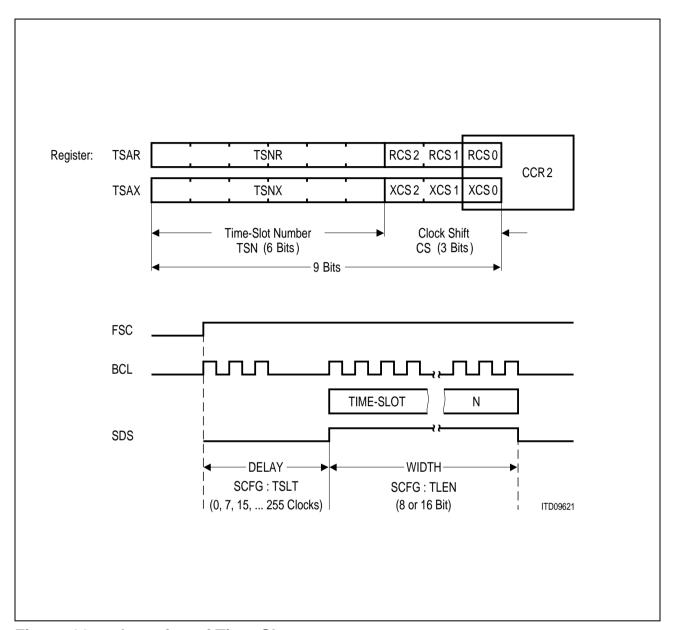

| 2.1.7.1           | Clock Mode 5 (Time-Slots)                                |            |

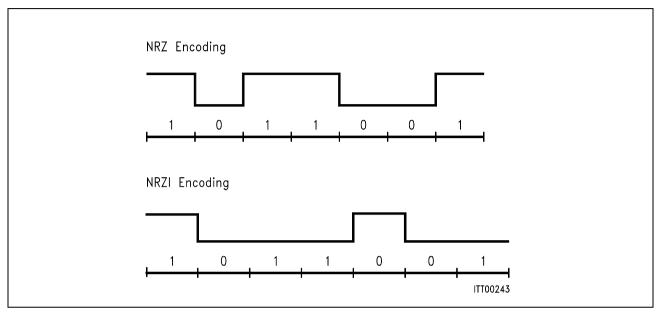

| 2.1.7.2           | Data Encoding                                            |            |

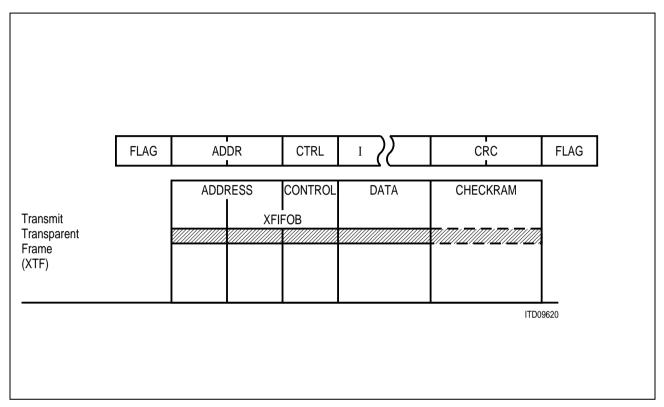

| 2.1.8             | Fully Transparent Transmission and Reception             |            |

| 2.1.9             | Cyclic Transmission (Fully Transparent)                  |            |

| 2.1.10            | Continuous Transmission (DMA Mode only)                  | 40         |

| 2.1.11            | Receive Length Check Feature                             | 40         |

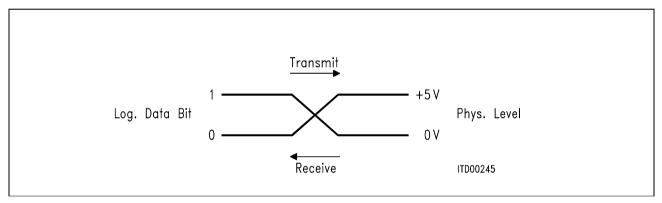

| 2.1.12            | Data Inversion                                           | 41         |

| 2.2               | D-Channel Operation                                      | 42         |

| 2.2.1             | Layer-2 Functions for HDLC                               |            |

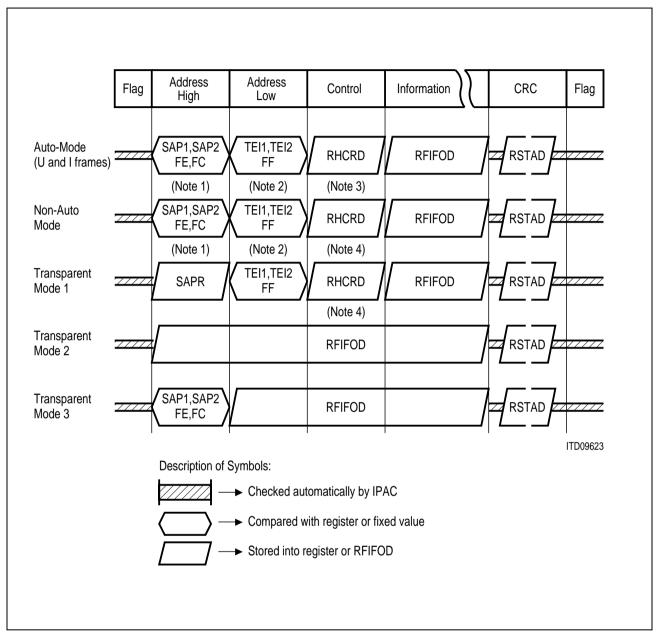

| 2.2.1.1           | Message Transfer Modes                                   |            |

|                   | Reception of Frames                                      |            |

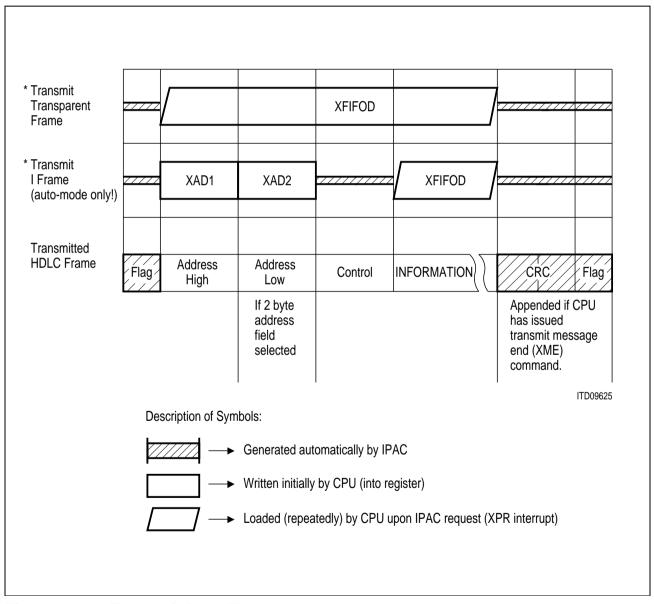

|                   | Transmission of Frames                                   |            |

|                   |                                                          | <b>5</b> 0 |

| 2.3               | Control Procedures                                       |            |

| 2.3.1             | Activation Initiated by Exchange (LT-S)                  |            |

| 2.3.2             | Activation Initiated by Terminal (TE/LT-T)               |            |

| 2.3.3             | Deactivation                                             |            |

| 2.3.4             | D-Channel Access Control                                 | 54         |

| 2.3.4.1           | TIC Bus D-Channel Control in TE                          |            |

| 2.3.4.2           | ,                                                        |            |

|                   | S-Bus D-channel Control in TEs                           |            |

|                   | S-Bus D-Channel Control in LT-T                          |            |

|                   | D-Channel Control in the Intelligent NT (TIC- and S-Bus) |            |

| 2.3.5             | IOM-2 Interface Channel Switching                        | 65         |

| 2.4       S/T Interface       68         2.4.1       Operating Modes       68         2.4.2       S/T-Interface Coding       69         2.4.3       S/T-Interface Multiframing       71         2.4.4       S/T Transceiver Control       72         2.4.4.1       MON-8 Commands (Internal Register Access)       72         2.4.4.2       MON-8 Configuration Register       74         2.4.4.3       MON-8 Loop-Back Register       76         2.4.4.4       MON-8 Loop-Back Register       78         2.4.4.5       MON-8 Loop-Back Register       78         2.4.4.5       MON-8 Loop-Back Register       78         2.4.4.5       MON-8 Loop-Back Register       76         2.5.2       Exper-Interface Register       76         2.5.2       Exper-Interface Register       78         2.5.2       S/T Interface Register       80         2.5.1       Arinerface Register       80         2.5.2       External Protections                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.4.1       Operating Modes       68         2.4.2       S/T-Interface Coding       69         2.4.3       S/T-Interface Multiframing       71         2.4.4       S/T Transceiver Control       72         2.4.4.1       MON-8 Commands (Internal Register Access)       72         2.4.4.2       MON-8 Configuration Register       74         2.4.4.3       MON-8 Loop-Back Register       76         2.4.4.4       MON-8 IOM-2 Channel Register       78         2.4.4.5       MON-8 SM/CI Register       79         2.5       Layer-1 Functions for the S/T Interface       80         2.5.1       Analog Functions       82         2.5.2       S/T Interface Circuitry       84         2.5.2.1       S/T Interface Pre-Filter Compensation       84         2.5.2.2       External Protection Circuitry       84         2.5.2.1       Receiver Functions       87         2.5.3       Receiver Characteristics       87         2.5.3.1       Receiver Characteristics       87         2.5.3.2       Level Detection Power Down (TE mode)       88         2.5.4       S/T Transmitter Disable       89         2.5.5       Timing Recovery       90         2.5.6                           |

| 2.4.2       S/T-Interface Coding       69         2.4.3       S/T-Interface Multiframing       .71         2.4.4       S/T Transceiver Control       .72         2.4.4.1       MON-8 Commands (Internal Register Access)       .72         2.4.4.2       MON-8 Configuration Register       .74         2.4.4.3       MON-8 Loop-Back Register       .76         2.4.4.4       MON-8 IOM-2 Channel Register       .78         2.4.4.5       MON-8 SM/CI Register       .79         2.5       Layer-1 Functions for the S/T Interface       80         2.5.1       Analog Functions       .82         2.5.2       S/T Interface Circuitry       .84         2.5.2.1       S/T Interface Pre-Filter Compensation       .84         2.5.2.2       External Protection Circuitry       .84         2.5.3       Receiver Functions       .87         2.5.3.1       Receiver Characteristics       .87         2.5.3.2       Level Detection Power Down (TE mode)       .88         2.5.4       S/T Transmitter Disable       .89         2.5.5       Timing Recovery       .90         2.5.6       Activation/Deactivation       .92         2.5.7       Activation Indication via Pin ACL       .93        |

| 2.4.3       S/T-Interface Multiframing       .71         2.4.4       S/T Transceiver Control       .72         2.4.4.1       MON-8 Commands (Internal Register Access)       .72         2.4.4.2       MON-8 Configuration Register       .74         2.4.4.3       MON-8 Loop-Back Register       .76         2.4.4.4       MON-8 IOM-2 Channel Register       .78         2.4.4.5       MON-8 SM/CI Register       .79         2.5       Layer-1 Functions for the S/T Interface       .80         2.5.1       Analog Functions       .82         2.5.2       S/T Interface Circuitry       .84         2.5.2.1       S/T Interface Pre-Filter Compensation       .84         2.5.2.2       External Protection Circuitry       .84         2.5.2.1       Receiver Functions       .87         2.5.3       Receiver Functions       .87         2.5.3.1       Receiver Characteristics       .87         2.5.3.2       Level Detection Power Down (TE mode)       .88         2.5.4       S/T Transmitter Disable       .89         2.5.5       Timing Recovery       .90         2.5.6       Activation/Deactivation       .92         2.5.7       Activation Indication via Pin ACL       .93      |

| 2.4.4       S/T Transceiver Control       72         2.4.4.1       MON-8 Commands (Internal Register Access)       72         2.4.4.2       MON-8 Configuration Register       74         2.4.4.3       MON-8 Loop-Back Register       76         2.4.4.4       MON-8 IOM-2 Channel Register       78         2.4.4.5       MON-8 SM/CI Register       79         2.5       Layer-1 Functions for the S/T Interface       80         2.5.1       Analog Functions       82         2.5.2       S/T Interface Circuitry       84         2.5.2.1       S/T Interface Pre-Filter Compensation       84         2.5.2.2       External Protection Circuitry       84         2.5.3       Receiver Functions       87         2.5.3.1       Receiver Functions       87         2.5.3.2       Level Detection Power Down (TE mode)       88         2.5.4       S/T Transmitter Disable       89         2.5.5       Timing Recovery       90         2.5.6       Activation/Deactivation       92         2.5.7       Activation Indication via Pin ACL       93         2.5.9       Test Functions       96         2.5.9.1       B-Channel Test Mode       96         2.5.9.2                           |

| 2.4.4.1       MON-8 Commands (Internal Register Access)       .72         2.4.4.2       MON-8 Configuration Register       .74         2.4.4.3       MON-8 Loop-Back Register       .76         2.4.4.4       MON-8 IOM-2 Channel Register       .78         2.4.4.5       MON-8 SM/CI Register       .79         2.5       Layer-1 Functions for the S/T Interface       .80         2.5.1       Analog Functions       .82         2.5.2       S/T Interface Circuitry       .84         2.5.2.1       S/T Interface Pre-Filter Compensation       .84         2.5.2.2       External Protection Circuitry       .84         2.5.3       Receiver Functions       .87         2.5.3.1       Receiver Characteristics       .87         2.5.3.2       Level Detection Power Down (TE mode)       .88         2.5.4       S/T Transmitter Disable       .89         2.5.5       Timing Recovery       .90         2.5.6       Activation/Deactivation       .92         2.5.7       Activation Indication via Pin ACL       .93         2.5.9       Test Functions       .96         2.5.9.1       B-Channel Test Mode       .96         2.5.9.2       D-Channel and S/T Interface Test Mode       .96 |

| 2.4.4.2       MON-8 Configuration Register       74         2.4.4.3       MON-8 Loop-Back Register       76         2.4.4.4       MON-8 IOM-2 Channel Register       78         2.4.4.5       MON-8 SM/CI Register       79         2.5       Layer-1 Functions for the S/T Interface       80         2.5.1       Analog Functions       82         2.5.2       S/T Interface Circuitry       84         2.5.2.1       S/T Interface Pre-Filter Compensation       84         2.5.2.2       External Protection Circuitry       84         2.5.3       Receiver Functions       87         2.5.3.1       Receiver Characteristics       87         2.5.3.2       Level Detection Power Down (TE mode)       88         2.5.4       S/T Transmitter Disable       89         2.5.5       Timing Recovery       90         2.5.6       Activation/Deactivation       92         2.5.7       Activation Indication via Pin ACL       93         2.5.8       Terminal Specific Functions (TE mode only)       94         2.5.9       Test Functions       96         2.5.9.1       B-Channel Test Mode       96         2.5.9.2       D-Channel and S/T Interface Test Mode       96                      |

| 2.4.4.3 MON-8 Loop-Back Register       76         2.4.4.4 MON-8 IOM-2 Channel Register       78         2.4.4.5 MON-8 SM/CI Register       79         2.5 Layer-1 Functions for the S/T Interface       80         2.5.1 Analog Functions       82         2.5.2 S/T Interface Circuitry       84         2.5.2.1 S/T Interface Pre-Filter Compensation       84         2.5.2.2 External Protection Circuitry       84         2.5.3 Receiver Functions       87         2.5.3.1 Receiver Characteristics       87         2.5.3.2 Level Detection Power Down (TE mode)       88         2.5.4 S/T Transmitter Disable       89         2.5.5 Timing Recovery       90         2.5.6 Activation/Deactivation       92         2.5.7 Activation Indication via Pin ACL       93         2.5.8 Terminal Specific Functions (TE mode only)       94         2.5.9 Test Functions       96         2.5.9.1 B-Channel Test Mode       96         2.5.9.2 D-Channel and S/T Interface Test Mode       96                                                                                                                                                                                                    |

| 2.4.4.4 MON-8 IOM-2 Channel Register       78         2.4.4.5 MON-8 SM/CI Register       79         2.5 Layer-1 Functions for the S/T Interface       80         2.5.1 Analog Functions       82         2.5.2 S/T Interface Circuitry       84         2.5.2.1 S/T Interface Pre-Filter Compensation       84         2.5.2.2 External Protection Circuitry       84         2.5.3 Receiver Functions       87         2.5.3.1 Receiver Characteristics       87         2.5.3.2 Level Detection Power Down (TE mode)       88         2.5.4 S/T Transmitter Disable       89         2.5.5 Timing Recovery       90         2.5.6 Activation/Deactivation       92         2.5.7 Activation Indication via Pin ACL       93         2.5.8 Terminal Specific Functions (TE mode only)       94         2.5.9 Test Functions       96         2.5.9.1 B-Channel Test Mode       96         2.5.9.2 D-Channel and S/T Interface Test Mode       96                                                                                                                                                                                                                                                      |

| 2.5       Layer-1 Functions for the S/T Interface       80         2.5.1       Analog Functions       82         2.5.2       S/T Interface Circuitry       84         2.5.2.1       S/T Interface Pre-Filter Compensation       84         2.5.2.2       External Protection Circuitry       84         2.5.3       Receiver Functions       87         2.5.3.1       Receiver Characteristics       87         2.5.3.2       Level Detection Power Down (TE mode)       88         2.5.4       S/T Transmitter Disable       89         2.5.5       Timing Recovery       90         2.5.6       Activation/Deactivation       92         2.5.7       Activation Indication via Pin ACL       93         2.5.8       Terminal Specific Functions (TE mode only)       94         2.5.9       Test Functions       96         2.5.9.1       B-Channel Test Mode       96         2.5.9.2       D-Channel and S/T Interface Test Mode       96                                                                                                                                                                                                                                                          |

| 2.5.1       Analog Functions       .82         2.5.2       S/T Interface Circuitry       .84         2.5.2.1       S/T Interface Pre-Filter Compensation       .84         2.5.2.2       External Protection Circuitry       .84         2.5.3       Receiver Functions       .87         2.5.3.1       Receiver Characteristics       .87         2.5.3.2       Level Detection Power Down (TE mode)       .88         2.5.4       S/T Transmitter Disable       .89         2.5.5       Timing Recovery       .90         2.5.6       Activation/Deactivation       .92         2.5.7       Activation Indication via Pin ACL       .93         2.5.8       Terminal Specific Functions (TE mode only)       .94         2.5.9       Test Functions       .96         2.5.9.1       B-Channel Test Mode       .96         2.5.9.2       D-Channel and S/T Interface Test Mode       .96                                                                                                                                                                                                                                                                                                              |

| 2.5.1       Analog Functions       .82         2.5.2       S/T Interface Circuitry       .84         2.5.2.1       S/T Interface Pre-Filter Compensation       .84         2.5.2.2       External Protection Circuitry       .84         2.5.3       Receiver Functions       .87         2.5.3.1       Receiver Characteristics       .87         2.5.3.2       Level Detection Power Down (TE mode)       .88         2.5.4       S/T Transmitter Disable       .89         2.5.5       Timing Recovery       .90         2.5.6       Activation/Deactivation       .92         2.5.7       Activation Indication via Pin ACL       .93         2.5.8       Terminal Specific Functions (TE mode only)       .94         2.5.9       Test Functions       .96         2.5.9.1       B-Channel Test Mode       .96         2.5.9.2       D-Channel and S/T Interface Test Mode       .96                                                                                                                                                                                                                                                                                                              |

| 2.5.2       S/T Interface Circuitry       .84         2.5.2.1       S/T Interface Pre-Filter Compensation       .84         2.5.2.2       External Protection Circuitry       .84         2.5.3       Receiver Functions       .87         2.5.3.1       Receiver Characteristics       .87         2.5.3.2       Level Detection Power Down (TE mode)       .88         2.5.4       S/T Transmitter Disable       .89         2.5.5       Timing Recovery       .90         2.5.6       Activation/Deactivation       .92         2.5.7       Activation Indication via Pin ACL       .93         2.5.8       Terminal Specific Functions (TE mode only)       .94         2.5.9       Test Functions       .96         2.5.9.1       B-Channel Test Mode       .96         2.5.9.2       D-Channel and S/T Interface Test Mode       .96                                                                                                                                                                                                                                                                                                                                                             |

| 2.5.2.1       S/T Interface Pre-Filter Compensation       .84         2.5.2.2       External Protection Circuitry       .84         2.5.3       Receiver Functions       .87         2.5.3.1       Receiver Characteristics       .87         2.5.3.2       Level Detection Power Down (TE mode)       .88         2.5.4       S/T Transmitter Disable       .89         2.5.5       Timing Recovery       .90         2.5.6       Activation/Deactivation       .92         2.5.7       Activation Indication via Pin ACL       .93         2.5.8       Terminal Specific Functions (TE mode only)       .94         2.5.9       Test Functions       .96         2.5.9.1       B-Channel Test Mode       .96         2.5.9.2       D-Channel and S/T Interface Test Mode       .96                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.5.2.2 External Protection Circuitry       84         2.5.3 Receiver Functions       87         2.5.3.1 Receiver Characteristics       87         2.5.3.2 Level Detection Power Down (TE mode)       88         2.5.4 S/T Transmitter Disable       89         2.5.5 Timing Recovery       90         2.5.6 Activation/Deactivation       92         2.5.7 Activation Indication via Pin ACL       93         2.5.8 Terminal Specific Functions (TE mode only)       94         2.5.9 Test Functions       96         2.5.9.1 B-Channel Test Mode       96         2.5.9.2 D-Channel and S/T Interface Test Mode       96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.5.3       Receiver Functions       87         2.5.3.1       Receiver Characteristics       87         2.5.3.2       Level Detection Power Down (TE mode)       88         2.5.4       S/T Transmitter Disable       89         2.5.5       Timing Recovery       90         2.5.6       Activation/Deactivation       92         2.5.7       Activation Indication via Pin ACL       93         2.5.8       Terminal Specific Functions (TE mode only)       94         2.5.9       Test Functions       96         2.5.9.1       B-Channel Test Mode       96         2.5.9.2       D-Channel and S/T Interface Test Mode       96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.5.3.1Receiver Characteristics872.5.3.2Level Detection Power Down (TE mode)882.5.4S/T Transmitter Disable892.5.5Timing Recovery902.5.6Activation/Deactivation922.5.7Activation Indication via Pin ACL932.5.8Terminal Specific Functions (TE mode only)942.5.9Test Functions962.5.9.1B-Channel Test Mode962.5.9.2D-Channel and S/T Interface Test Mode96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.5.3.2       Level Detection Power Down (TE mode)       .88         2.5.4       S/T Transmitter Disable       .89         2.5.5       Timing Recovery       .90         2.5.6       Activation/Deactivation       .92         2.5.7       Activation Indication via Pin ACL       .93         2.5.8       Terminal Specific Functions (TE mode only)       .94         2.5.9       Test Functions       .96         2.5.9.1       B-Channel Test Mode       .96         2.5.9.2       D-Channel and S/T Interface Test Mode       .96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.5.4S/T Transmitter Disable.892.5.5Timing Recovery.902.5.6Activation/Deactivation.922.5.7Activation Indication via Pin ACL.932.5.8Terminal Specific Functions (TE mode only).942.5.9Test Functions.962.5.9.1B-Channel Test Mode.962.5.9.2D-Channel and S/T Interface Test Mode.96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.5.5Timing Recovery.902.5.6Activation/Deactivation.922.5.7Activation Indication via Pin ACL.932.5.8Terminal Specific Functions (TE mode only).942.5.9Test Functions.962.5.9.1B-Channel Test Mode.962.5.9.2D-Channel and S/T Interface Test Mode.96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.5.6       Activation/Deactivation       .92         2.5.7       Activation Indication via Pin ACL       .93         2.5.8       Terminal Specific Functions (TE mode only)       .94         2.5.9       Test Functions       .96         2.5.9.1       B-Channel Test Mode       .96         2.5.9.2       D-Channel and S/T Interface Test Mode       .96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.5.7Activation Indication via Pin ACL.932.5.8Terminal Specific Functions (TE mode only).942.5.9Test Functions.962.5.9.1B-Channel Test Mode.962.5.9.2D-Channel and S/T Interface Test Mode.96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.5.8Terminal Specific Functions (TE mode only).942.5.9Test Functions.962.5.9.1B-Channel Test Mode.962.5.9.2D-Channel and S/T Interface Test Mode.96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.5.9Test Functions2.5.9.1B-Channel Test Mode2.5.9.2D-Channel and S/T Interface Test Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.5.9.1 B-Channel Test Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.5.9.2 D-Channel and S/T Interface Test Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.C. Migropyogogor Interfess                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.6 Microprocessor Interface98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.6.1 Operation Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.6.2 Register Set99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.6.3 Data Transfer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.6.4 Interrupt Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.6.5 DMA Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.6.6 FIFO Structure for B-Channels108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.6.7 Timer Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.6.8 Software Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

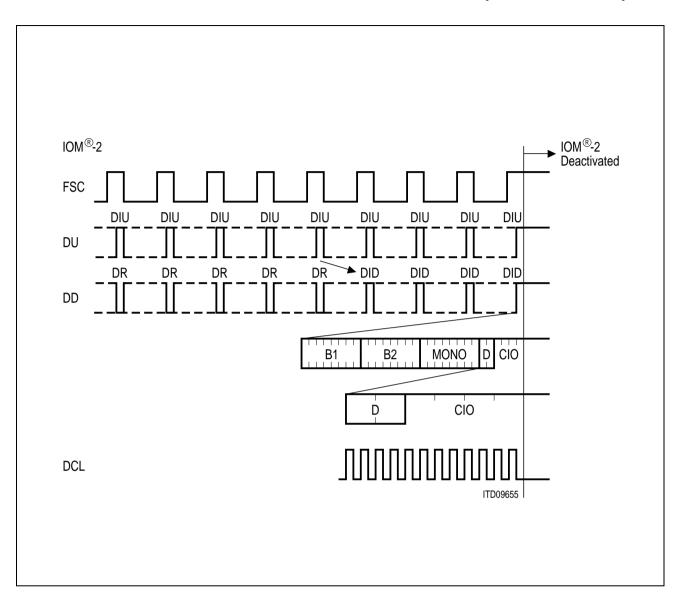

| 2.7 IOM-2 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

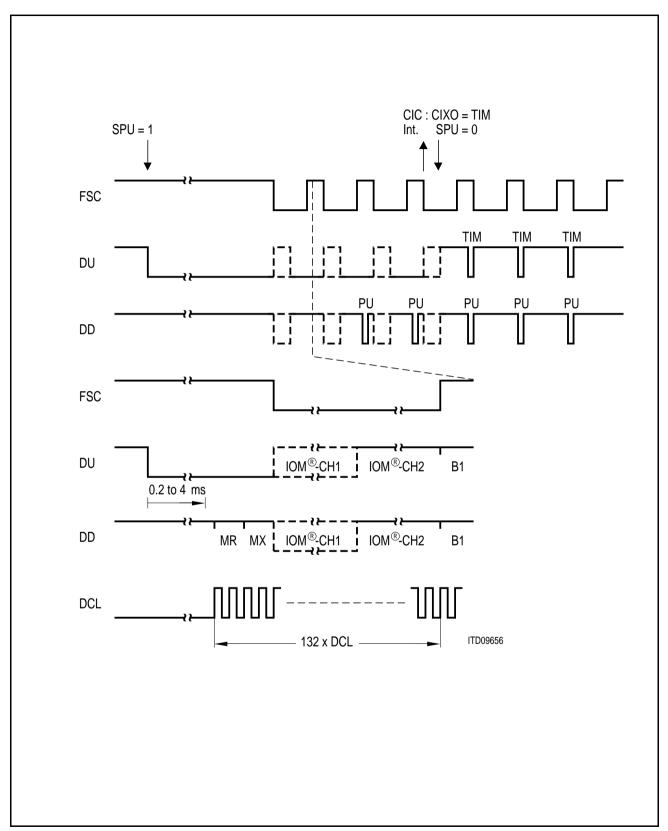

| 2.7.1 IOM-2 Frame Structure / Timing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.7.2 IOM-2 Interface Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.7.3 Microprocessor Access to B and IC Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table o                                                             | f Contents                                                                                                                                                                                         | Page                                 |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 2.7.4<br>2.7.4.1<br>2.7.4.2<br>2.7.4.3<br>2.7.4.4<br>2.7.5<br>2.7.6 | MONITOR Channel Handling  Handshake Procedure  Monitor Procedure Timeout (TOD)  MON-1, MON-2 Commands (S/Q Channel Access)  MON-8 Commands (Register Access)  C/I-Channel Handling  TIC Bus Access | .133<br>.136<br>.137<br>.138<br>.139 |

|                                                                     | Auxiliary Interface  Mode Dependent Functions  PCM Interface  PCM Lines  Clock Generation  Switching of Timeslots                                                                                  | .143<br>.146<br>.146<br>.150         |

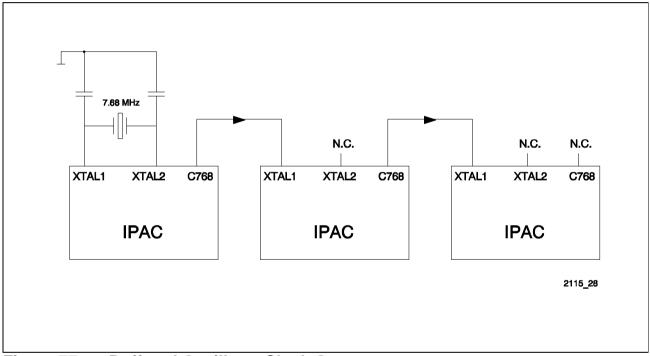

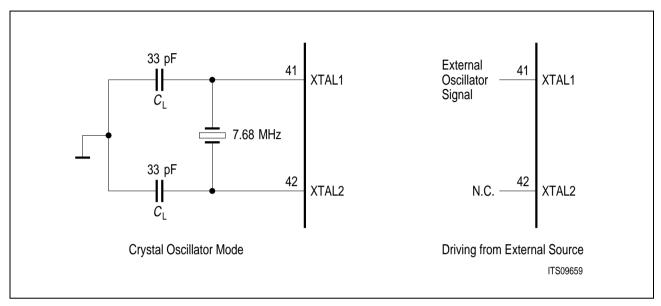

| 2.9                                                                 | Oscillator Circuit                                                                                                                                                                                 | .154                                 |

| 3                                                                   | Operational Description                                                                                                                                                                            | .155                                 |

| 3.1                                                                 | RESET                                                                                                                                                                                              | .155                                 |

| 3.2                                                                 | Initialization                                                                                                                                                                                     | .158                                 |

| 3.3<br>3.3.1<br>3.3.2<br>3.3.3                                      | Interrupt Structure and Logic                                                                                                                                                                      | .165<br>.167                         |

| <b>3.4</b><br>3.4.1<br>3.4.2                                        | B-Channel Data Transfer                                                                                                                                                                            | .174                                 |

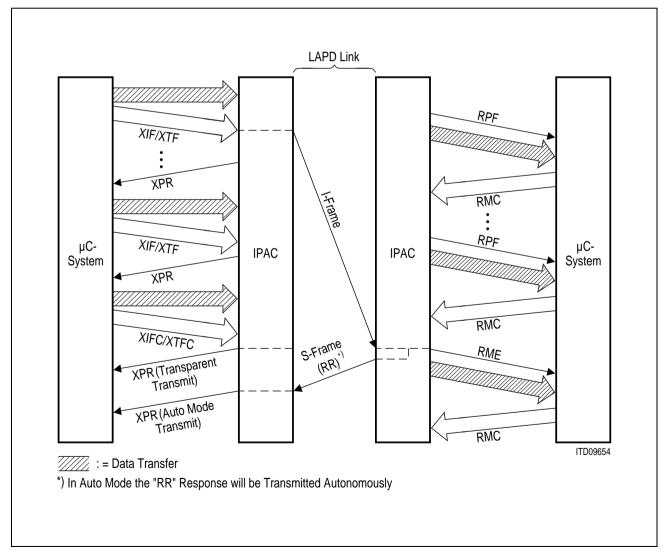

| <b>3.5</b> 3.5.1 3.5.2                                              | D-Channel Data Transfer                                                                                                                                                                            | .183                                 |

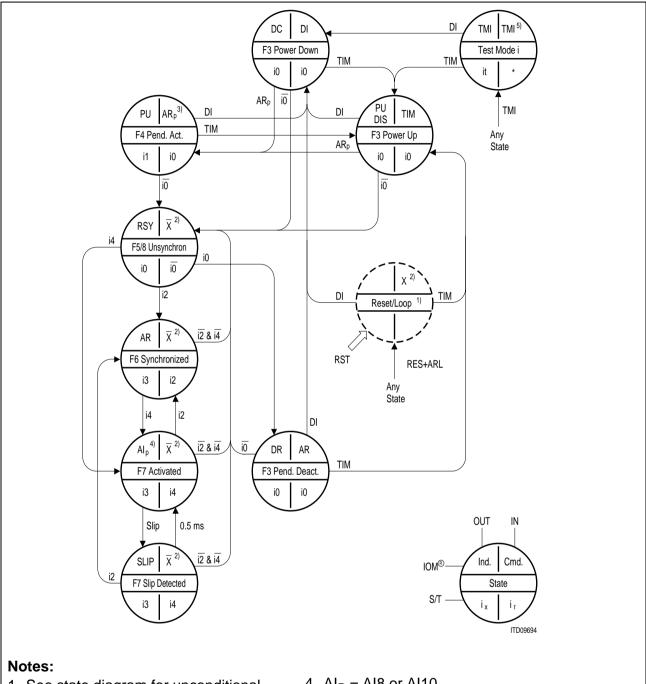

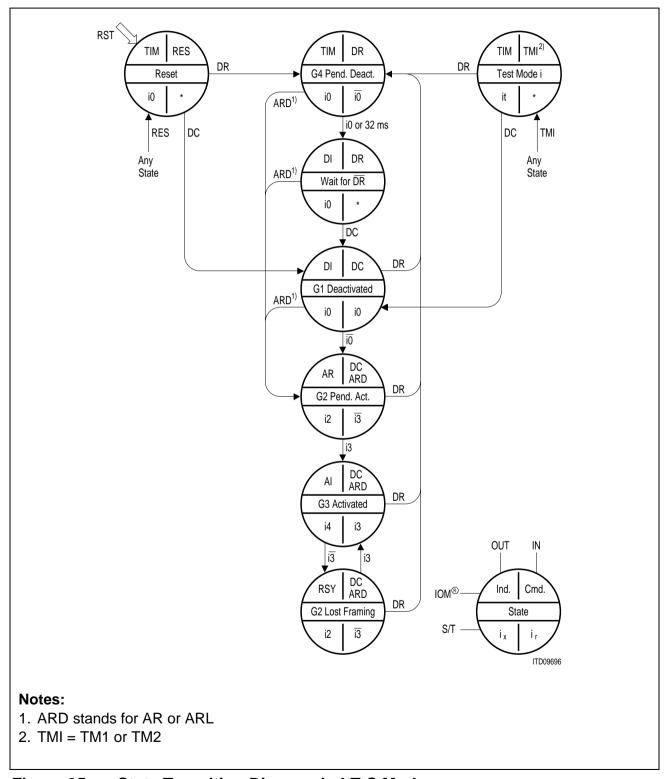

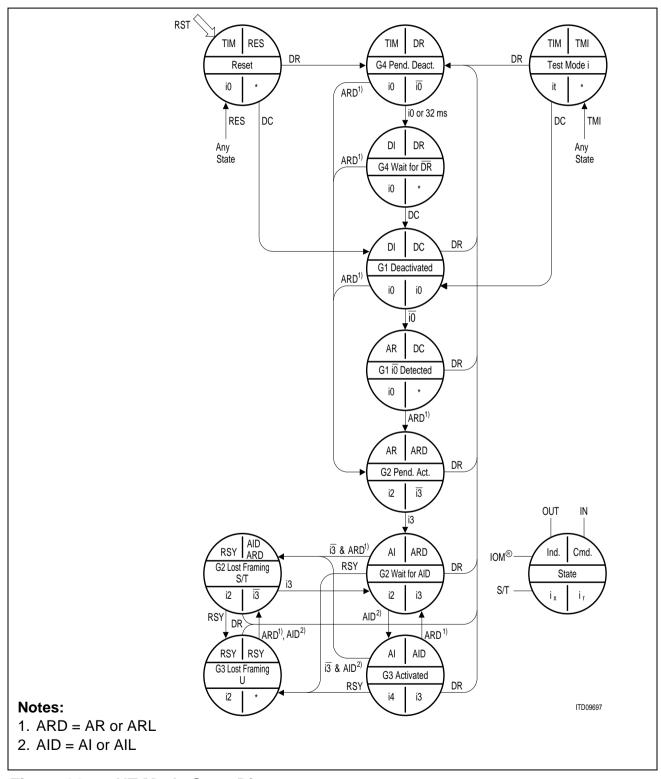

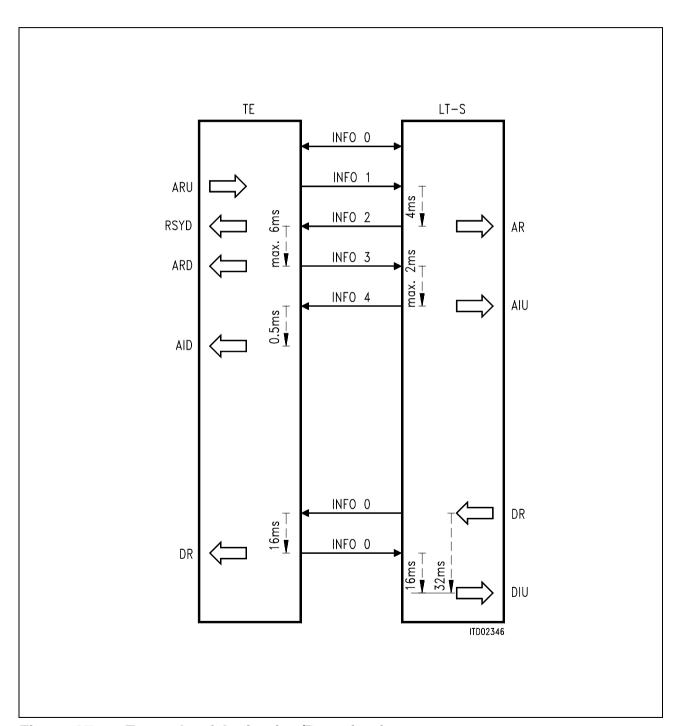

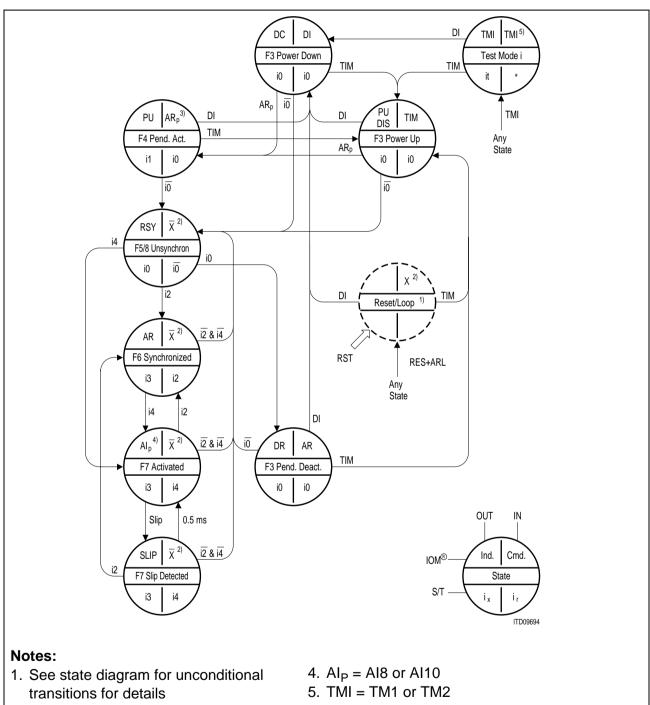

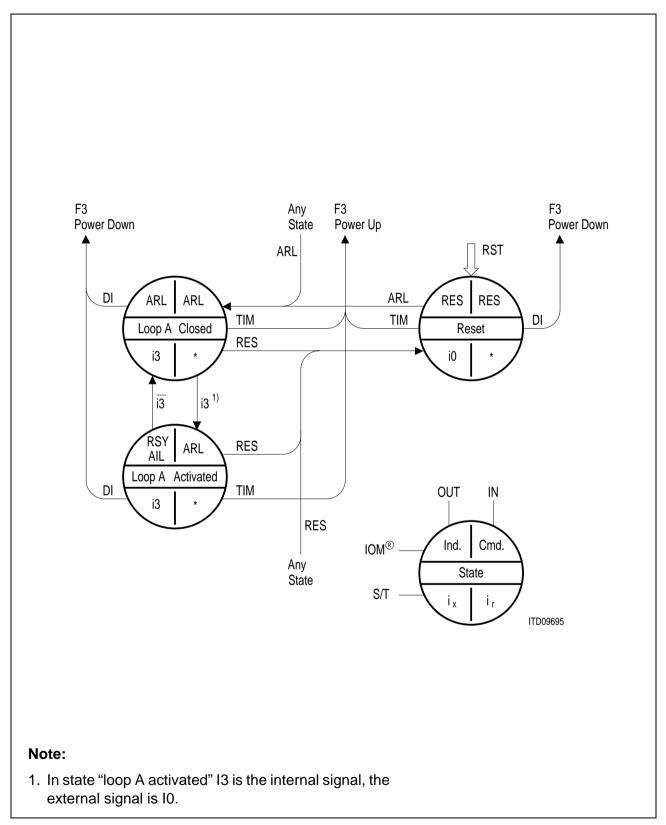

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.3.1                           | Control of Layer-1  Activation/Deactivation of IOM-2 Interface  Activation/Deactivation of S/T Interface  State Machine TE/LT-T Modes  TE/LT-T Modes State Diagram                                 | .188<br>.191<br>.193                 |

| Table of Contents |                                                            | Page |

|-------------------|------------------------------------------------------------|------|

| 3.6.3.2           | TE/LT-T Modes Transition Criteria                          | 196  |

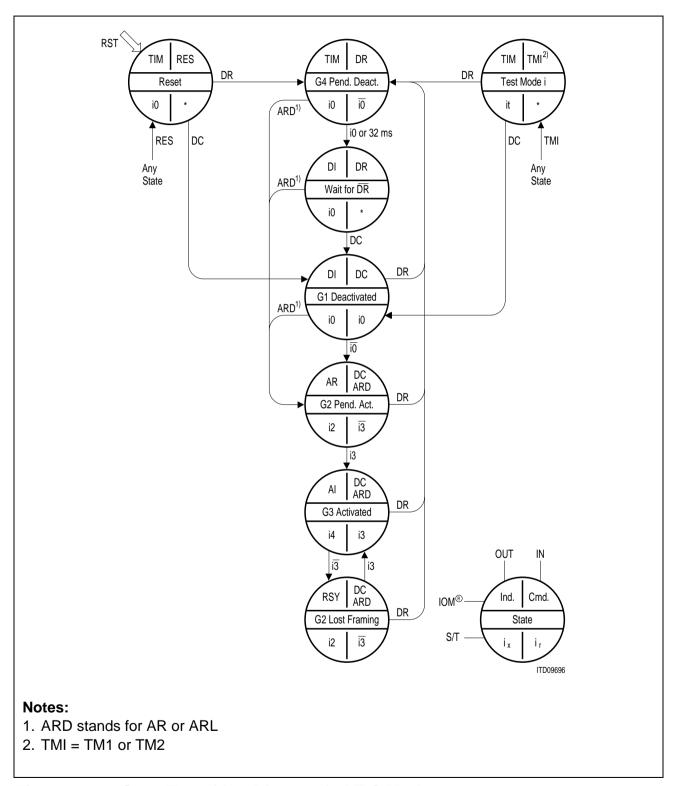

| 3.6.4             | State Machine LT-S Mode                                    | 202  |

| 3.6.4.1           | LT-S Mode State Diagram                                    | 202  |

| 3.6.4.2           | LT-S Mode Transition Criteria                              | 203  |

| 3.6.4.3           | Transmitted Signals and Indications in LT-S Mode           | 204  |

| 3.6.4.4           |                                                            |      |

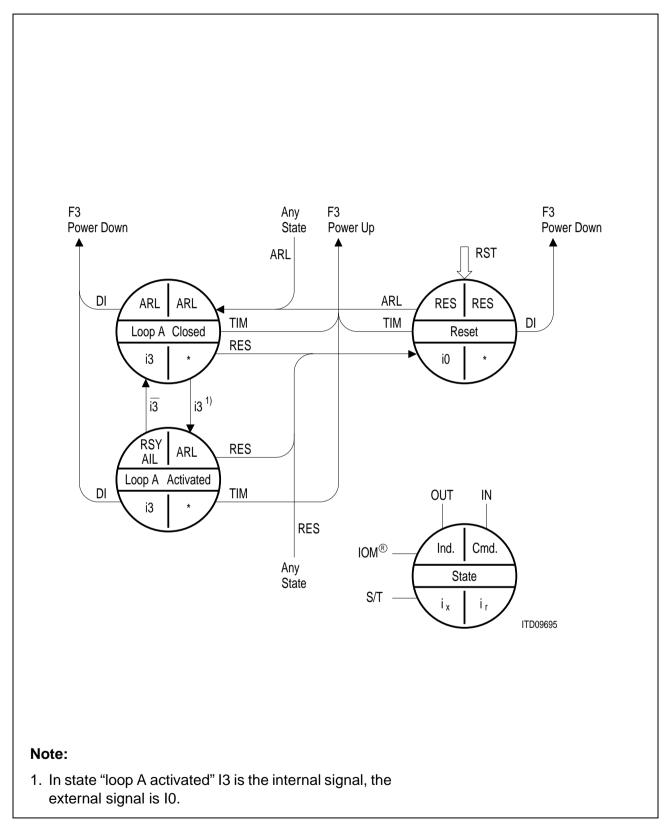

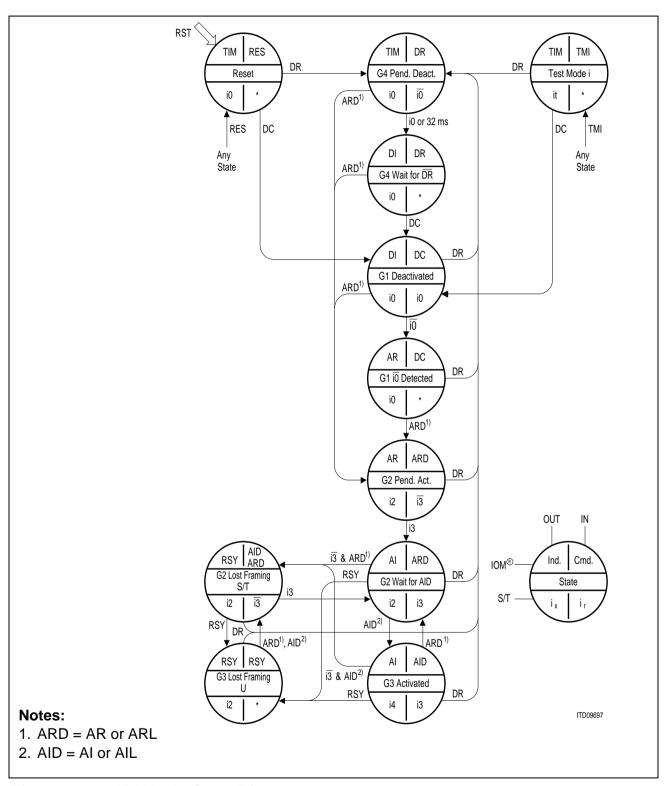

| 3.6.5             | State Machine Intelligent NT Mode                          | 206  |

| 3.6.5.1           | Intelligent NT Mode State Diagram                          | 206  |

| 3.6.5.2           | <b>O</b>                                                   |      |

| 3.6.5.3           | 3                                                          |      |

| 3.6.5.4           | <u> </u>                                                   |      |

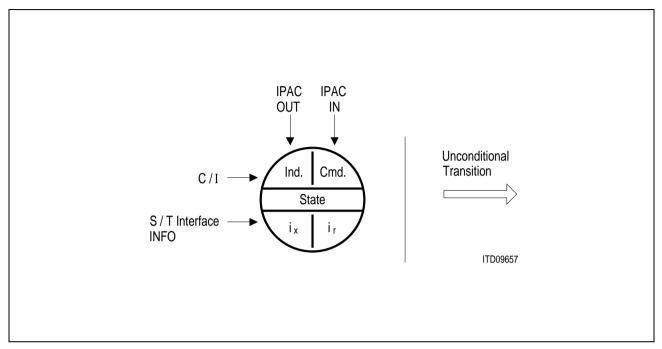

| 3.6.6             | Command/Indicate Channel                                   |      |

| 3.6.7             | Example of Activation/Deactivation                         | 212  |

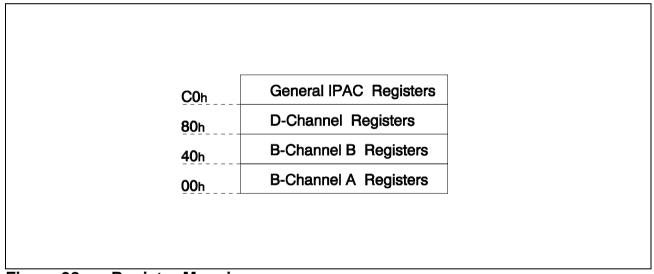

| 4                 | Detailed Register Description                              | 213  |

| 4.1               | Register Address Arrangement                               | 213  |

| 4.2               | B-Channel Registers                                        | 218  |

| 4.2.1             | RFIFOB - Receive FIFO B-Channel (Read))                    |      |

| 4.2.2             | XFIFOB - Transmit FIFO B-Channel (WRITE))                  |      |

| 4.2.3             | ISTAB - Interrupt Status Register for B-Channel (READ)     |      |

| 4.2.4             | MASKB - Mask Register for B-Channel (WRITE)                |      |

| 4.2.5             | STARB - Status Register for B-Channel (READ)               |      |

| 4.2.6             | CMDRB - Command Register for B-Channel (WRITE)             |      |

| 4.2.7             | MODEB - Mode Register for B-Channel (READ/WRITE)           |      |

| 4.2.8             | EXIRB - Extended Interrupt Register for B-Channel (READ)   |      |

| 4.2.9             | RBCLB - Receive Byte Count Low for B-Channel (READ)        |      |

| 4.2.10            | RAH1 - Receive Address Byte High Register 1 (WRITE)        |      |

| 4.2.11            | RAH2 - Receive Address Byte High Register 2 (WRITE)        |      |

| 4.2.12            | RSTAB - Receive Status Register for B-Channel (READ)       |      |

| 4.2.13            | RAL1 - Receive Address Byte Low Register 1 (READ/WRITE)    |      |

| 4.2.14            | RAL2 - Receive Address Byte Low Register 2 (WRITE)         | 229  |

| 4.2.15            | RHCRB - Receive HDLC Control Register for B-Channel (READ) |      |

| 4.2.16            | XBCL - Transmit Byte Count Low (WRITE)                     |      |

| 4.2.17            | CCR2 - Channel Configuration Register 2 (READ/WRITE)       | 231  |

| 4.2.18            | RBCHB - Received Byte Count High for B-Channel (READ)      | 232  |

| 4.2.19            | XBCH - Transmit Byte Count High (WRITE)                    |      |

| 4.2.20            | RLCR - Receive Length Check Register (WRITE)               | 233  |

| 4.2.21            | CCR1 - Channel Configuration Register 1 (READ/WRITE)       | 234  |

| 4.2.22            | TSAX - Time-Slot Assignment Register Transmit (WRITE)      | 234  |

| 4.2.23            | TSAR - Time-Slot Assignment Register Receive (WRITE)       | 235  |

| Table of Contents |                                                            | Page |

|-------------------|------------------------------------------------------------|------|

| 4.2.24            | XCCR - Transmit Channel Capacity Register (WRITE)          | 235  |

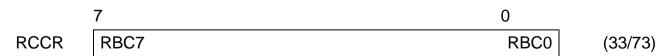

| 4.2.25            | RCCR - Receive Channel Capacity Register (WRITE)           | 235  |

| 4.3               | D-Channel Registers                                        | 236  |

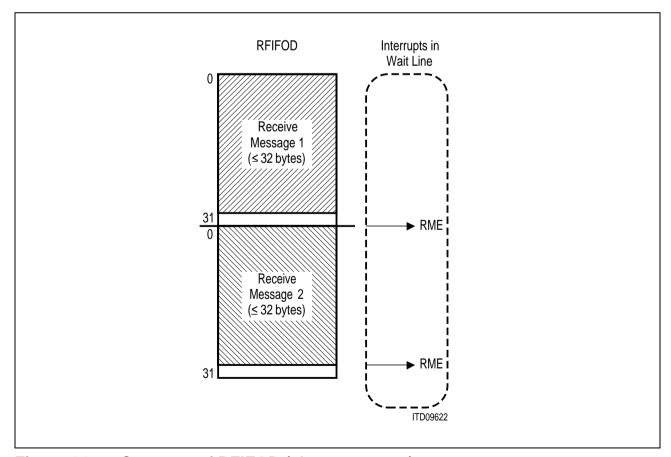

| 4.3.1             | RFIFOD - Receive FIFO D-Channel (Read)                     |      |

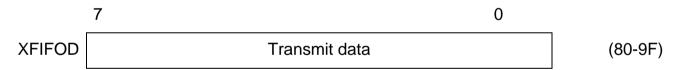

| 4.3.2             | XFIFOD - Transmit FIFO D-Channel (Write)                   | 236  |

| 4.3.3             | ISTAD - Interrupt Status Register D-Channel (Read)         | 237  |

| 4.3.4             | MASKD - Mask Register D-Channel (Write)                    | 238  |

| 4.3.5             | STARD - Status Register D-Channel (Read)                   | 239  |

| 4.3.6             | CMDRD - Command Register (Write)                           | 240  |

| 4.3.7             | MODED - Mode Register (Read/Write)                         | 242  |

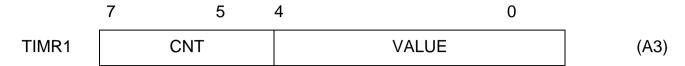

| 4.3.8             | TIMR1 - Timer 1 Register (Read/Write)                      | 244  |

| 4.3.9             | EXIRD - Extended Interrupt Register (Read)                 | 245  |

| 4.3.10            | XAD1 - Transmit Address 1 (Write)                          | 247  |

| 4.3.11            | XAD2 - Transmit Address 1 (Write)                          | 248  |

| 4.3.12            | RBCLD - Receive Frame Byte Count Low for D-Channel (Read)  | 248  |

| 4.3.13            | SAPR - Received SAPI Register (Read)                       | 249  |

| 4.3.14            | SAP1 - SAPI1 Register (Write)                              | 249  |

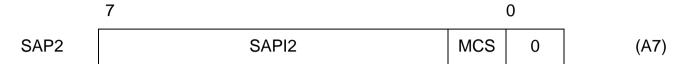

| 4.3.15            | SAP2 - SAPI2 Register (Write)                              | 250  |

| 4.3.16            | RSTAD - Receive Status Register (Read)                     | 250  |

| 4.3.17            | TEI1 - TEI1 Register 1 (Write)                             |      |

| 4.3.18            | TEI2 - TEI2 Register (Write)                               | 252  |

| 4.3.19            | RHCRD - Receive HDLC Control Register for D-Channel (Read) | 253  |

| 4.3.20            | RBCHD - Receive Frame Byte Count High for D-Channel (Read) | 254  |

| 4.3.21            | STAR2 - Status Register 2 (Read)                           | 255  |

| 4.3.22            | SPCR - Serial Port Control Register (Read/Write)           | 256  |

| 4.3.23            | CIR0 - Command/Indication Receive 0 (Read)                 | 258  |

| 4.3.24            | CIX0 - Command/Indication Transmit 0 (Write)               | 259  |

| 4.3.25            | MOR0 - MONITOR Receive Channel 0 (Read)                    | 260  |

| 4.3.26            | MOX0 - MONITOR Transmit Channel 0 (Write)                  | 260  |

| 4.3.27            | CIR1 - Command/Indication Receive 1 (Read)                 | 260  |

| 4.3.28            | CIX1 - Command/Indication Transmit 1 (Write)               | 261  |

| 4.3.29            | MOR1 - MONITOR Receive Channel 1 (Read)                    | 261  |

| 4.3.30            | MOX1 - MONITOR Transmit Channel 1 (Write)                  | 261  |

| 4.3.31            | C1R - Channel Register 1 (Read/Write)                      | 262  |

| 4.3.32            | C2R - Channel Register 2 (Read/Write)                      | 262  |

| 4.3.33            | STCR - Synchronous Transfer Control Register (Write)       | 263  |

| 4.3.34            | B1CR - B1 Channel Register (Read)                          |      |

| 4.3.35            | B2CR - B2 Channel Register (Read)                          |      |

| 4.3.36            | ADF1 - Additional Feature Register 1 (Write)               |      |

| 4.3.37            | MOSR - MONITOR Status Register (Read)                      |      |

| 4.3.38            | MOCR - MONITOR Control Register (Write)                    |      |

| Table of Contents |                                                              | Page |  |

|-------------------|--------------------------------------------------------------|------|--|

| 4.4               | General IPAC Registers                                       | 268  |  |

| 4.4.1             | CONF - IPAC Configuration Register (Read/Write)              |      |  |

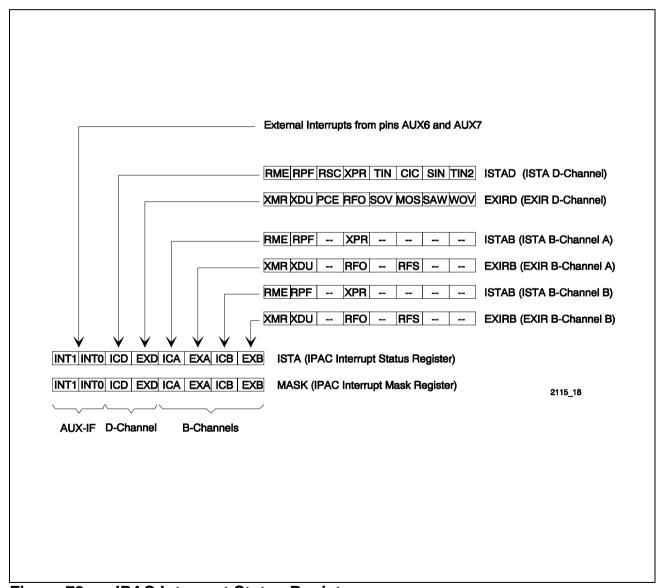

| 4.4.2             | ISTA - IPAC Interrupt Status Register (Read)                 |      |  |

| 4.4.3             | MASK - IPAC Mask Register (Write)                            |      |  |

| 4.4.4             | ID - Identification Register (Read)                          |      |  |

| 4.4.5             | ACFG - Auxiliary Interface Configuration (Read/Write)        |      |  |

| 4.4.6             | AOE - Auxiliary Output Enable (Read/Write)                   |      |  |

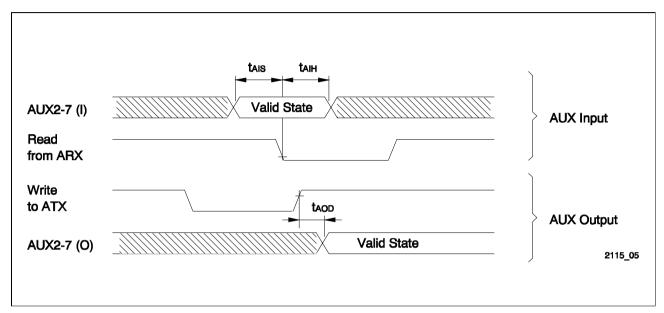

| 4.4.7             | ARX - Auxiliary Interface Receive Register (Read)            |      |  |

| 4.4.8             | ATX - Auxiliary Interface Transmit Register (Write)          |      |  |

| 4.4.9             | PITA1/2 - PCM Input Time Slot Assignment B1/B2 (Read/Write)  |      |  |

| 4.4.10            | POTA1/2 - PCM Output Time Slot Assignment B1/B2 (Read/Write) |      |  |

| 4.4.11            | PCFG - PCM Configuration Register (Read/Write)               |      |  |

| 4.4.12            | SCFG - SDS Configuration Register (Read/Write)               |      |  |

| 4.4.13            | TIMR2 - Timer 2 Register (Read/Write)                        |      |  |

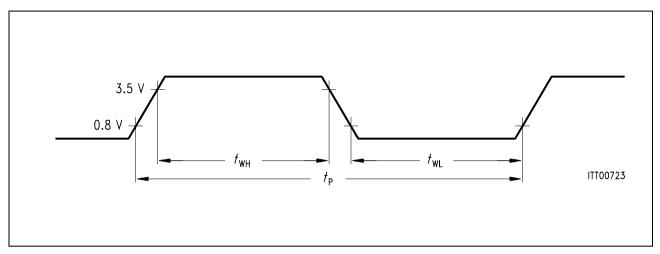

| 5                 | Electrical Characteristics                                   | 279  |  |

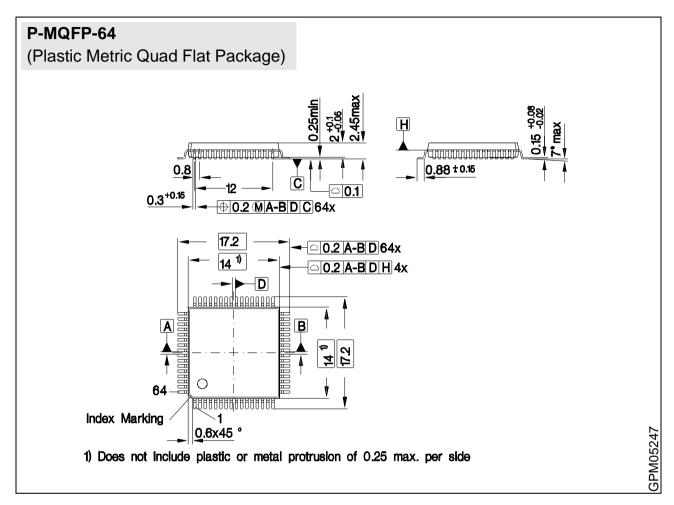

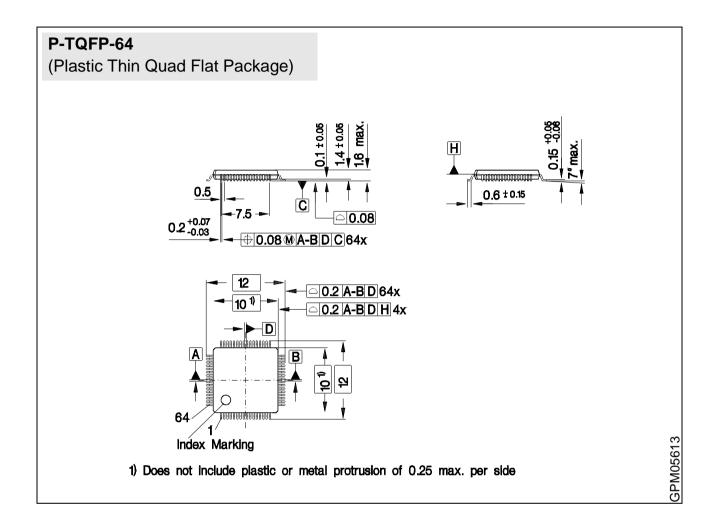

| 6                 | Package Outlines                                             | 299  |  |

| 7                 | Appendix                                                     | 301  |  |

| 7.1               | MON-8 Registers                                              |      |  |

| 7.2               | Register Address Arrangement                                 |      |  |

| 7.3               | State Diagrams                                               |      |  |

| 7.4               | C/I Codes                                                    |      |  |

|                   |                                                              |      |  |

IOM®, IOM®-1, IOM®-2, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4 $\mu$ C, SLICOFI®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, EPIC®-1, EPIC®-S, ELIC®, IPAT®-2, ITAC®, ISAC®-S, ISAC®-S TE, ISAC®-P, ISAC®-P TE, IDEC®, SICAT®, OCTAT®-P, QUAT®-S are registered trademarks of Siemens AG.

MUSAC™-A, FALC™54, IWE™, SARE™, UTPT™, ASM™, ASP™, DigiTape™ are trademarks of Siemens AG.

| List of Fig | ures                                                                | Page |

|-------------|---------------------------------------------------------------------|------|

| Figure 1:   | Logic Symbol                                                        | . 16 |

| Figure 2:   | Pin Configuration                                                   | . 17 |

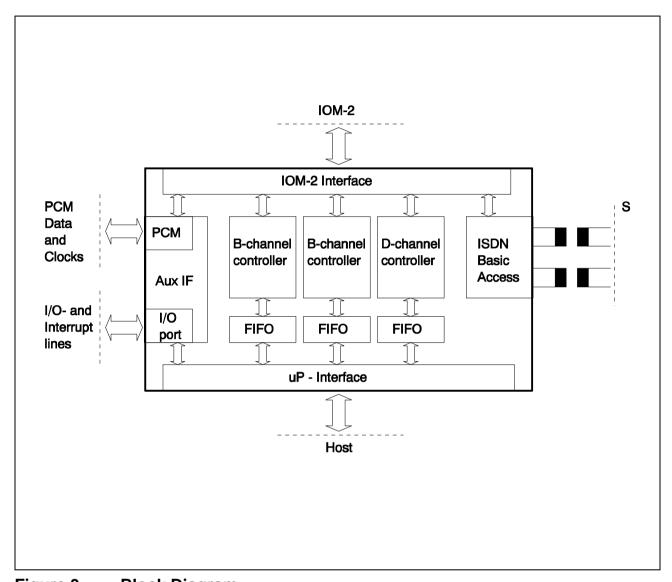

| Figure 3:   | Block Diagram                                                       | . 26 |

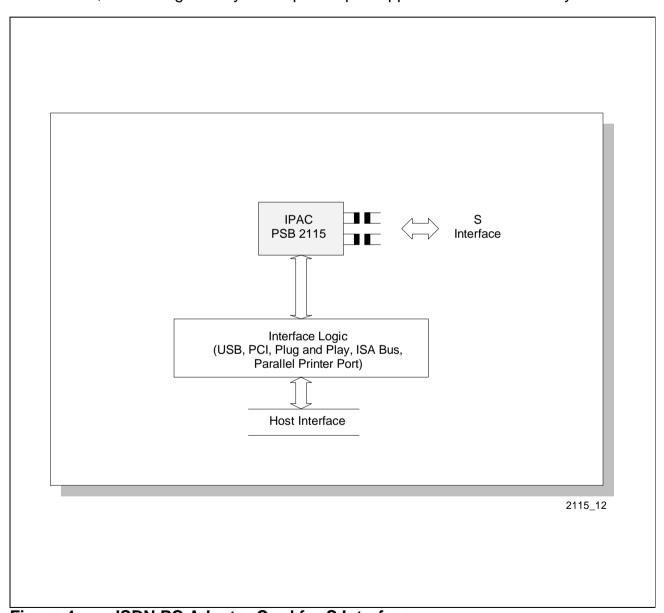

| Figure 4:   | ISDN PC Adapter Card for S Interface                                | . 27 |

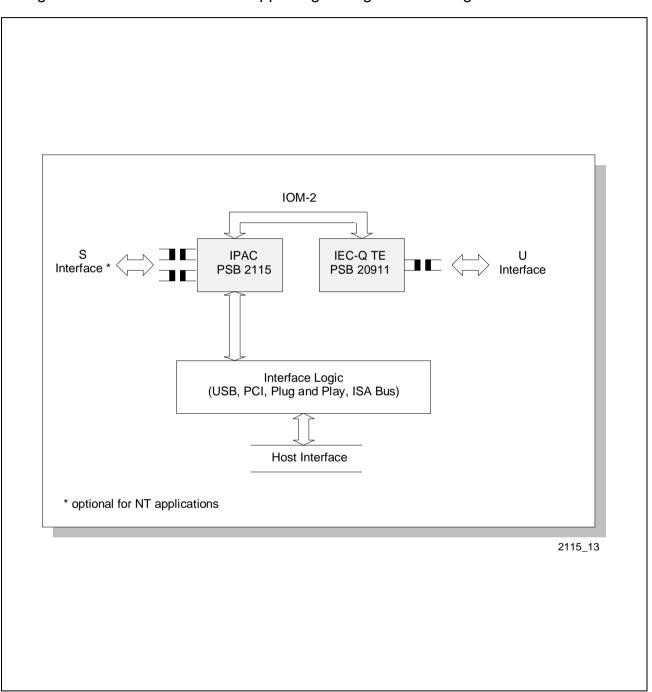

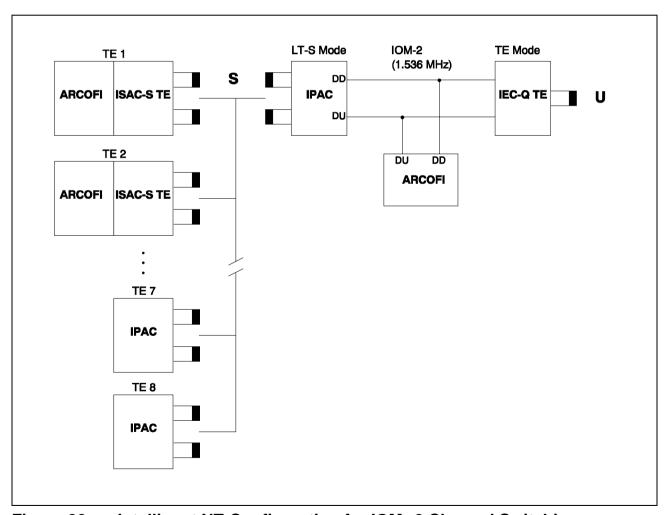

| Figure 5:   | ISDN PC Adapter Card for U or S interface                           | . 28 |

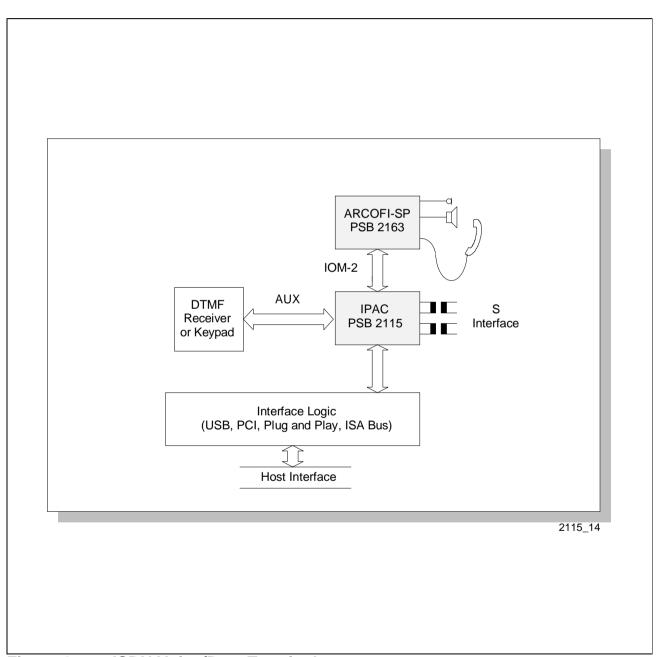

| Figure 6:   | ISDN Voice/Data Terminal                                            | . 29 |

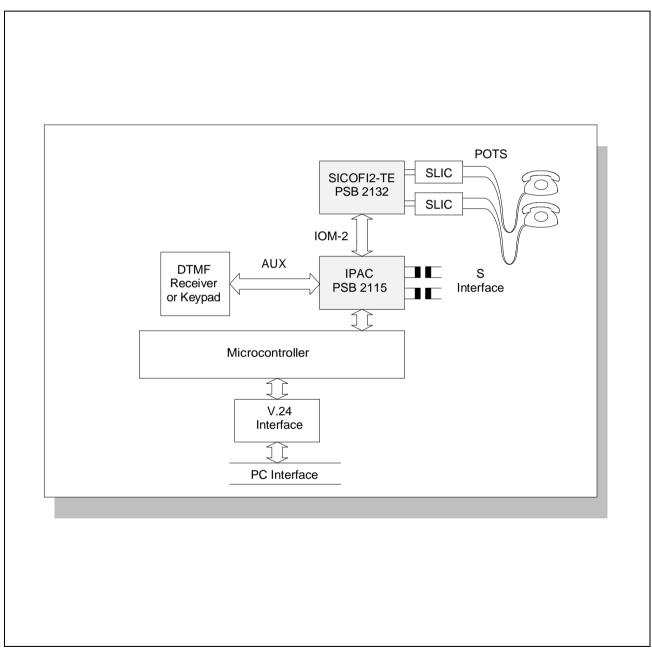

| Figure 7:   | ISDN Stand-Alone Terminal with POTS interface                       | . 30 |

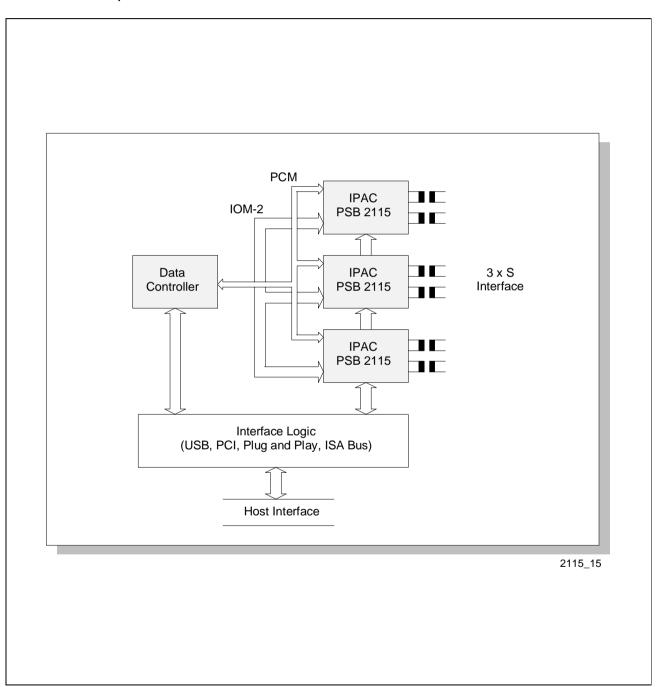

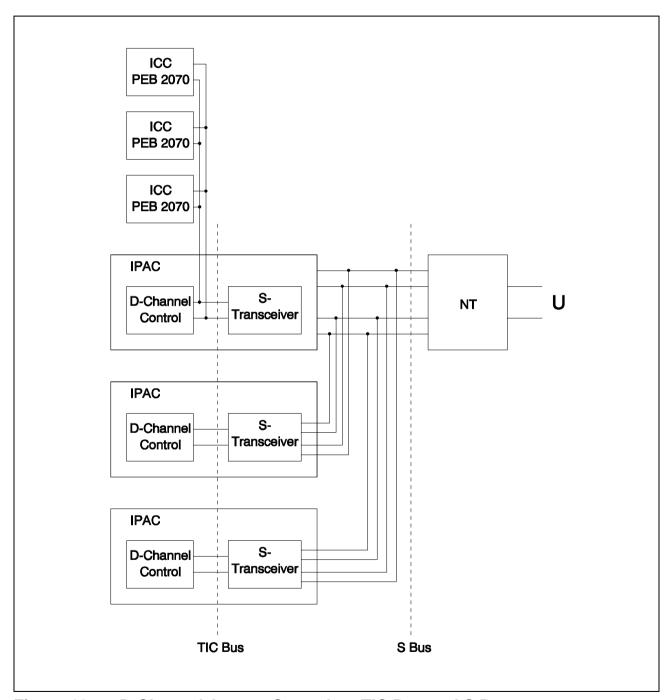

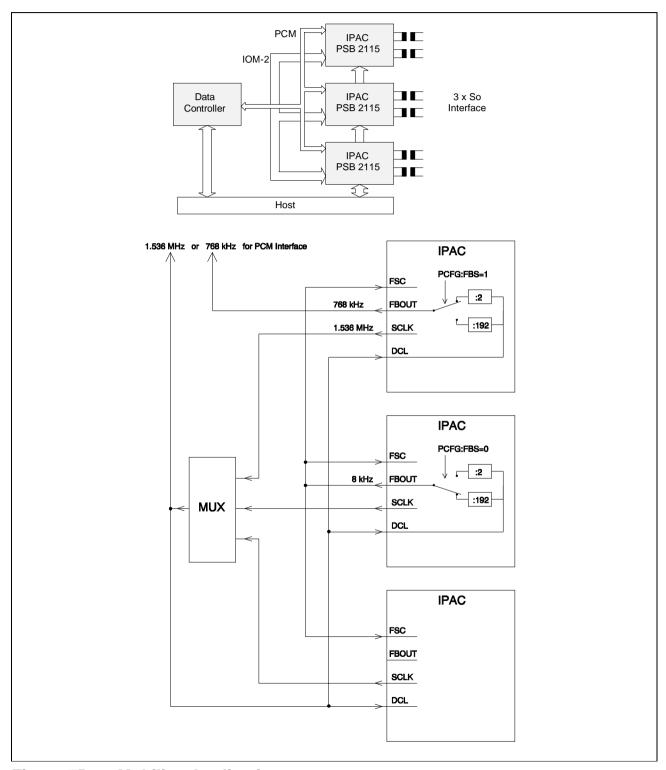

| Figure 8:   | Multiline PC-Adapter                                                |      |

| Figure 9:   | Receive Data Flow of IPAC                                           | . 34 |

| Figure 10:  | Transmit Data Flow of IPAC                                          | . 35 |

| Figure 11:  | Location of Time-Slots                                              | . 37 |

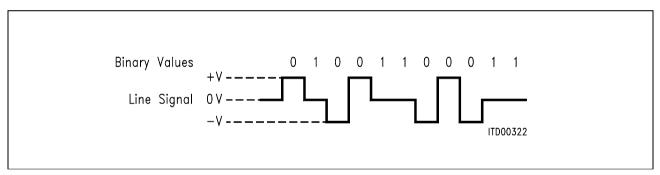

| Figure 12:  | NRZ Encoding/NRZI Encoding                                          | . 38 |

| Figure 13:  | Data Inversion                                                      | . 41 |

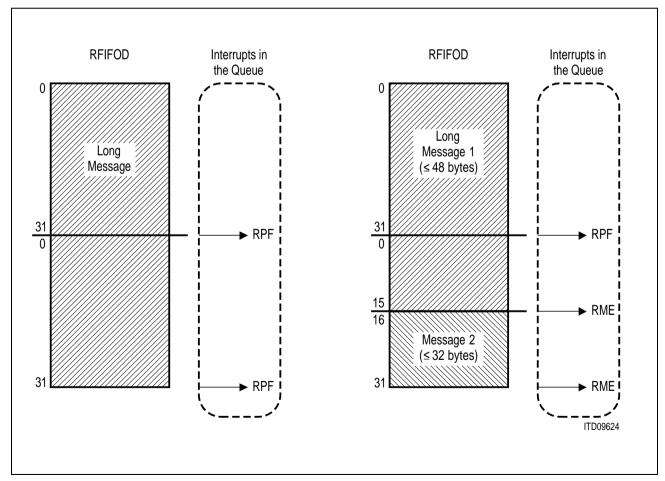

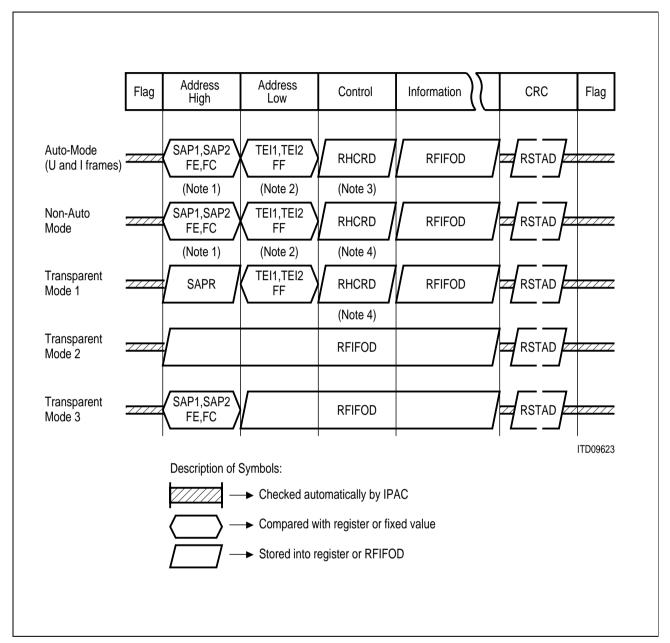

| Figure 14:  | Contents of RFIFOD (short message)                                  | . 45 |

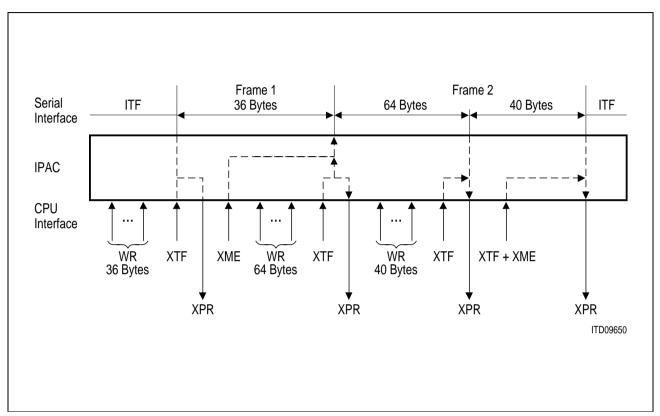

|             | Receive Data Flow                                                   |      |

| Figure 16:  | Contents of RFIFOD (long message)                                   | . 47 |

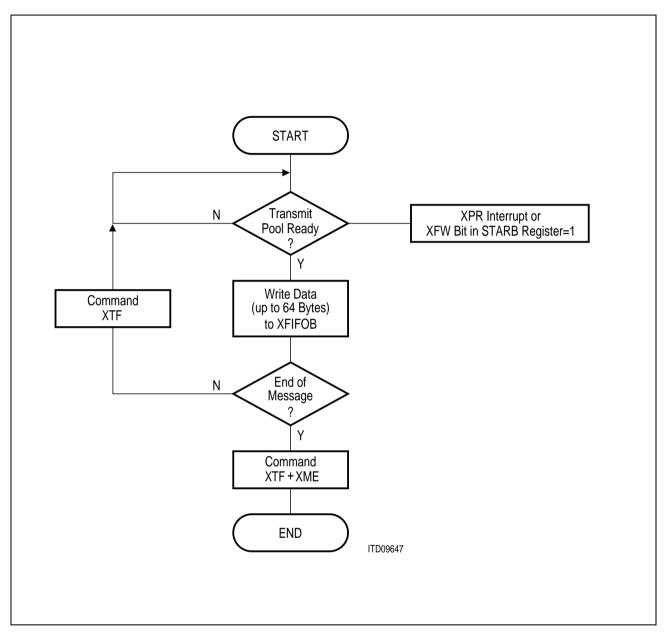

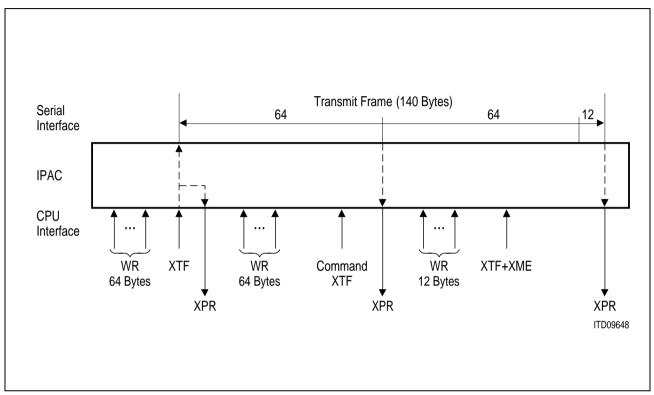

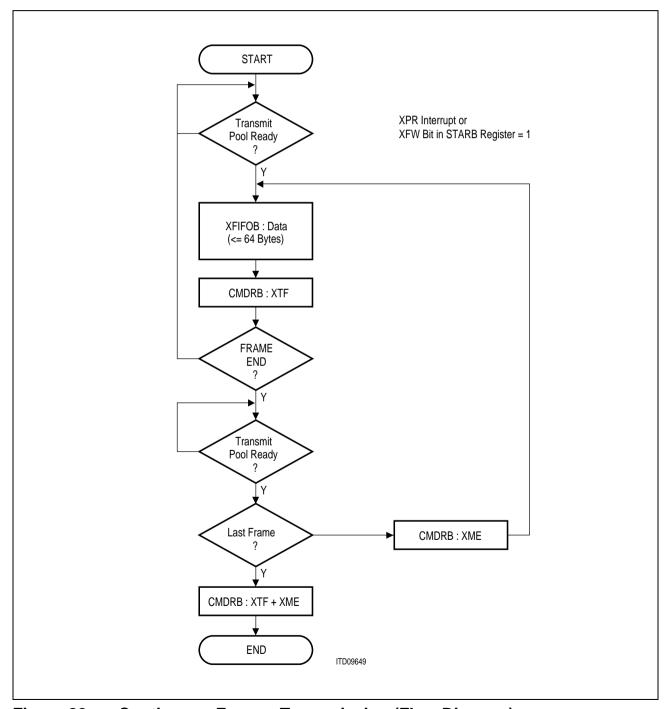

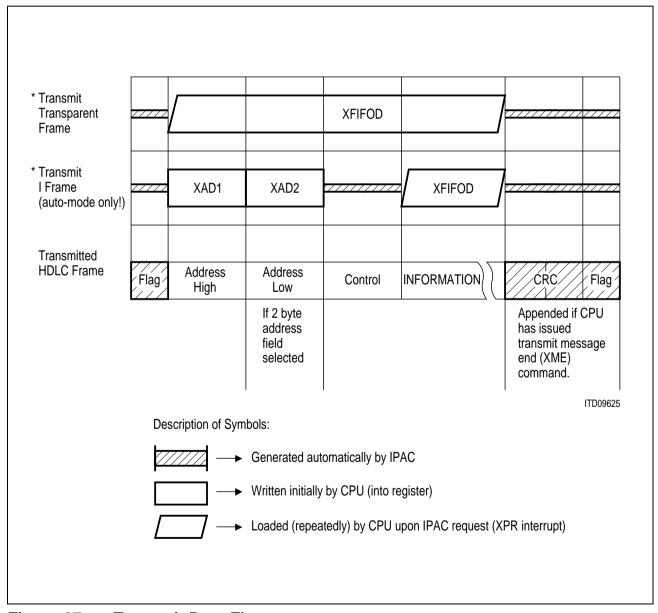

| Figure 17:  | Transmit Data Flow                                                  | . 49 |

| Figure 18:  | D-Channel Access Control on TIC Bus and S Bus                       | . 54 |

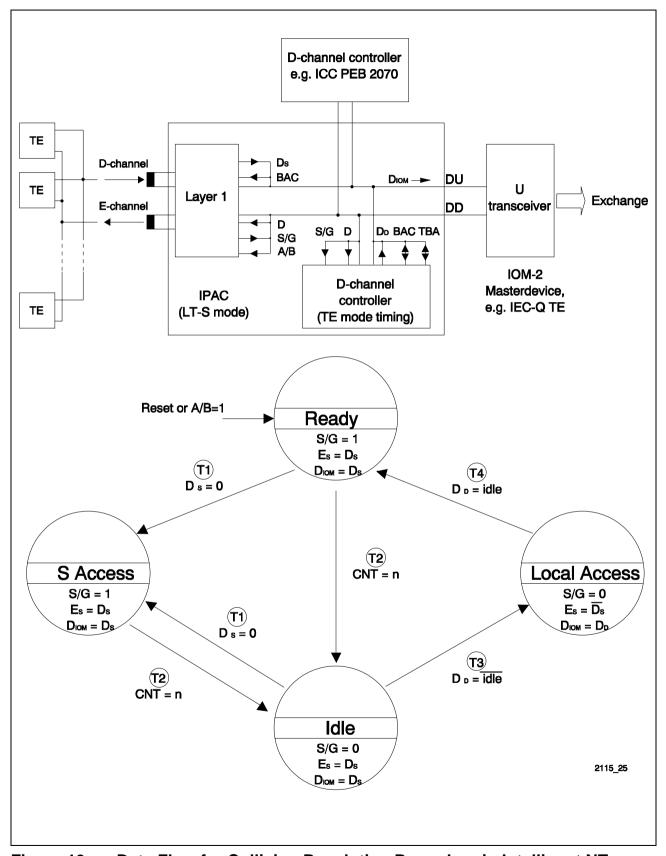

| Figure 19:  | Data Flow for Collision Resolution Procedure in Intelligent NT      | . 63 |

| Figure 20:  | Intelligent NT-Configuration for IOM-2 Channel Switching            | . 65 |

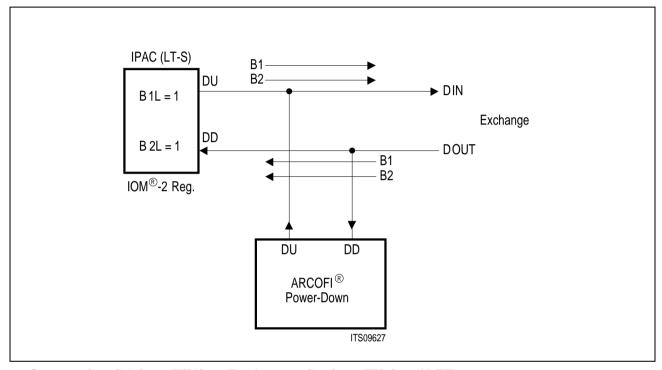

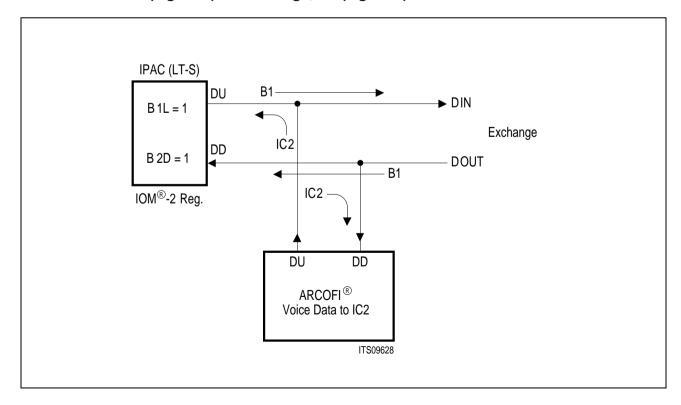

| Figure 21:  | Data Path Switching                                                 | . 68 |

| Figure 22:  | S/T -Interface Line Code (without code violation)                   | . 69 |

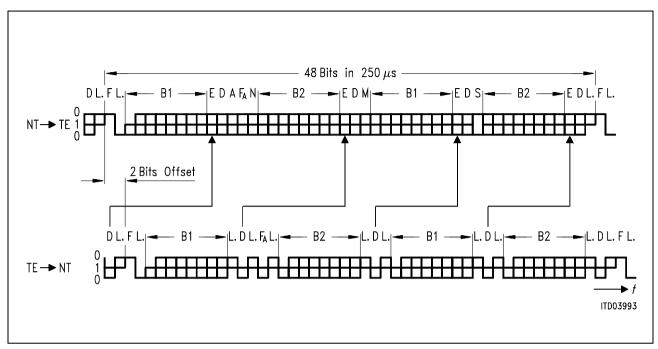

| Figure 23:  | Frame Structure at Reference Points S and T (ITU I.430)             | . 70 |

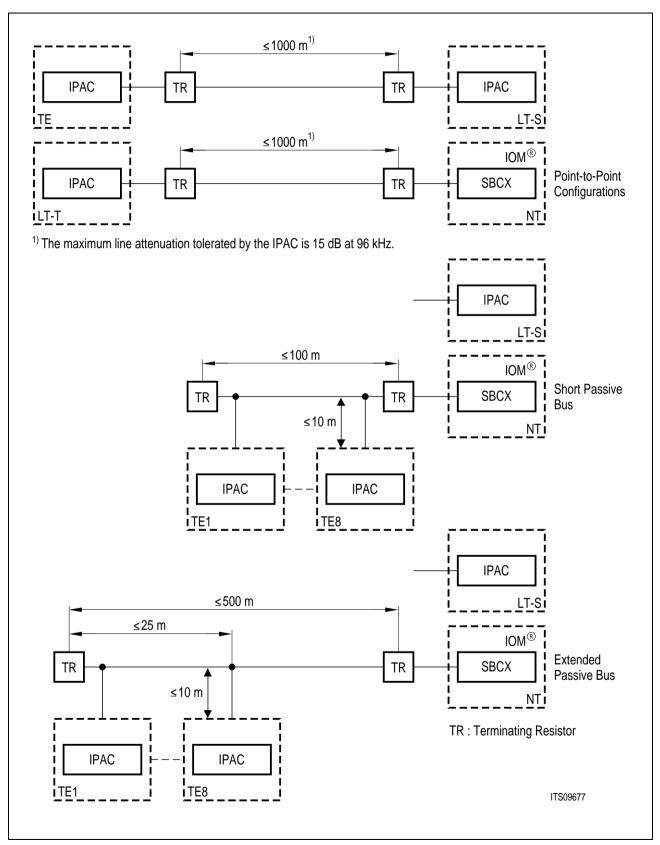

| Figure 24:  | Wiring Configurations in User Premises                              | . 81 |

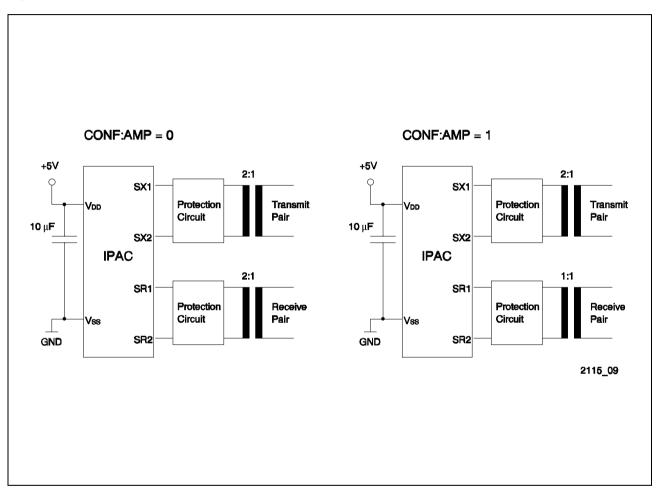

| Figure 25:  | Connection of the Line Transformers and Power Supply to the IPAC    | . 82 |

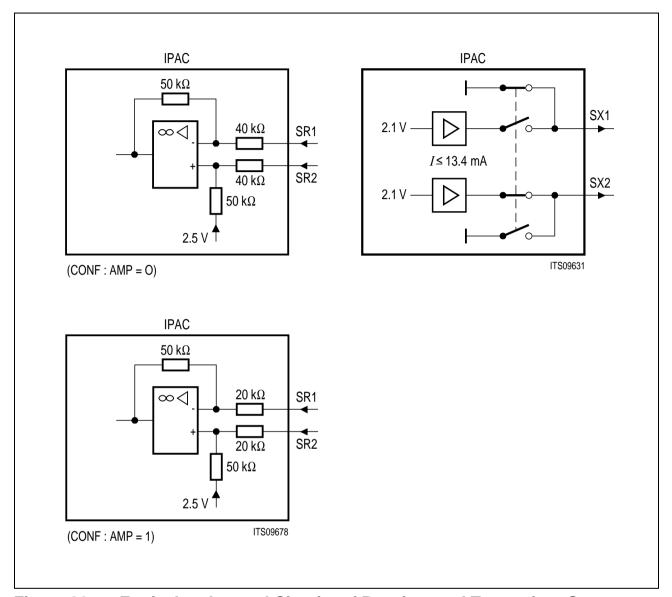

| Figure 26:  | Equivalent Internal Circuits of Receiver and Transmitter Stages     | . 83 |

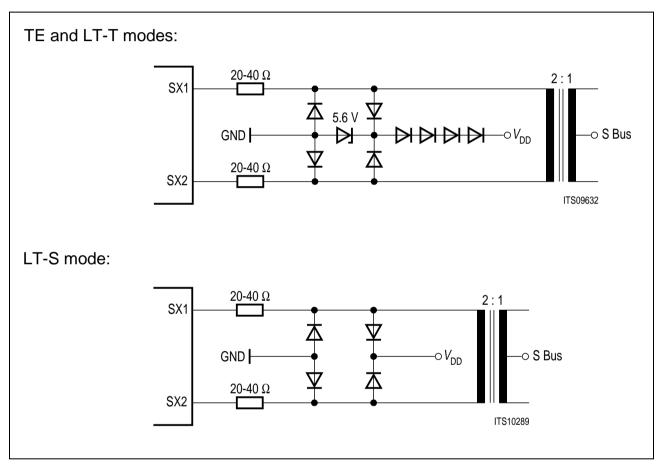

| Figure 27:  | External Circuitry for Transmitters                                 | . 85 |

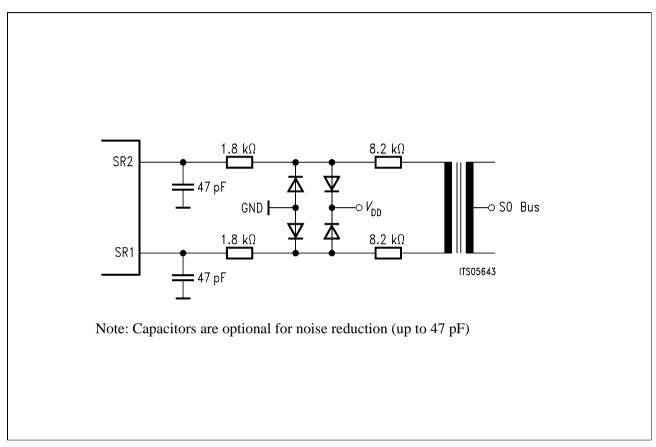

| Figure 28:  | External Circuitry for Symmetrical Receivers                        | . 86 |

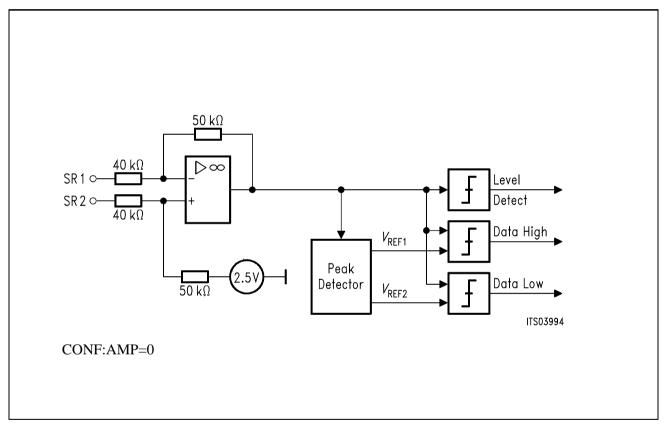

| •           | Receiver Circuit                                                    |      |

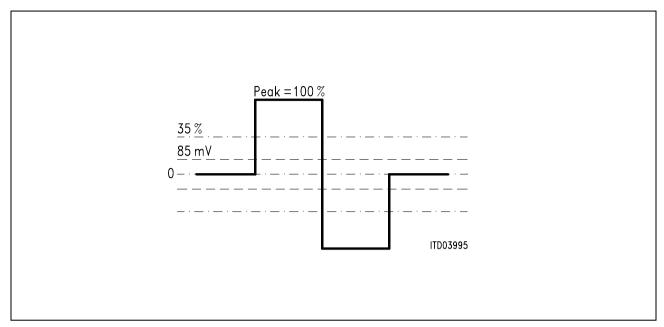

| •           | Receiver Thresholds                                                 |      |

|             | Disabling of S/T Transmitter                                        |      |

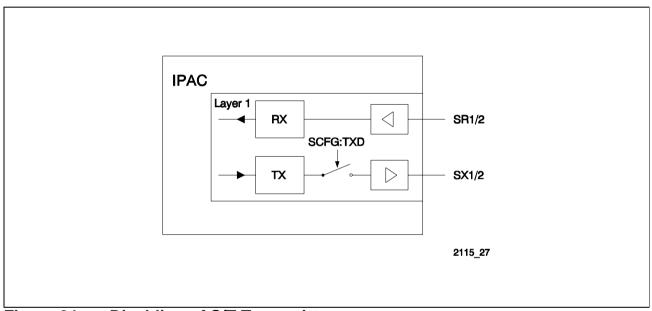

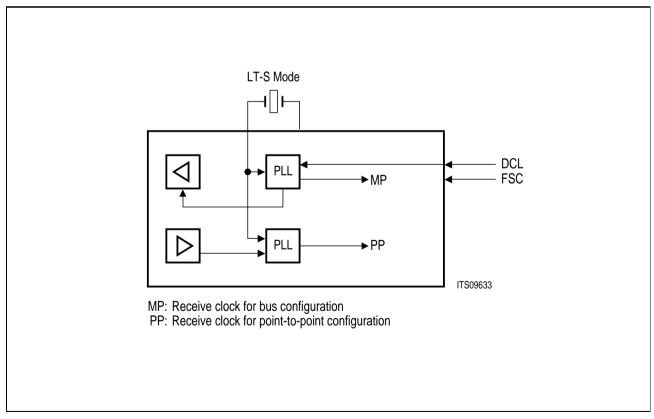

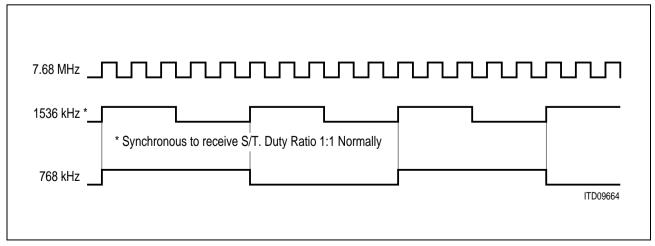

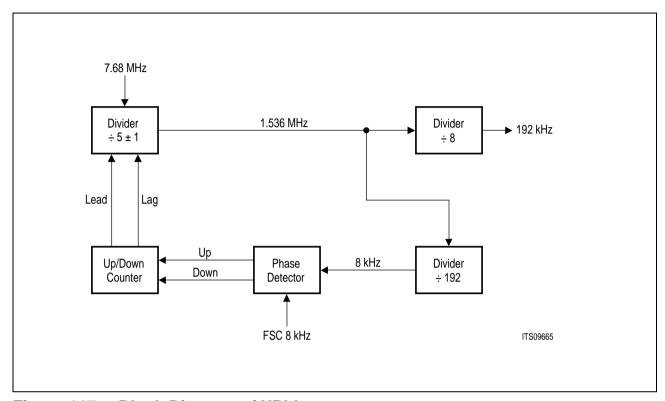

| Figure 32:  | Clock System of the IPAC in LT-S Mode                               | . 90 |

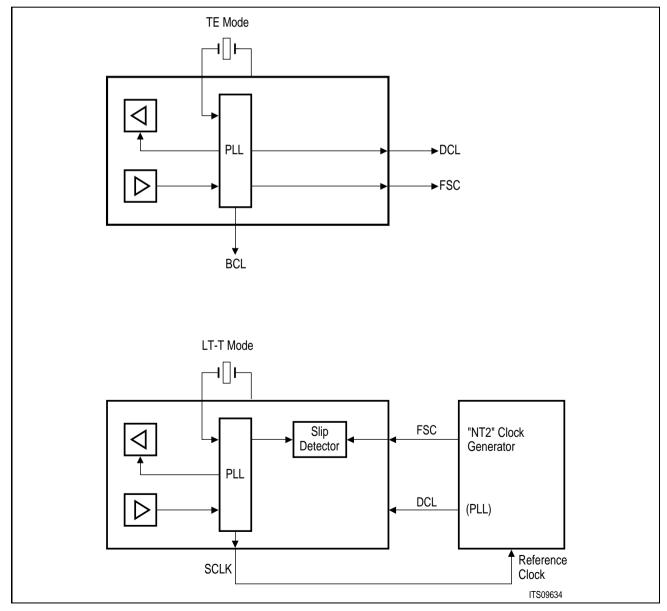

| Figure 33:  | Clock System of the IPAC in TE and LT-T Modes                       | . 91 |

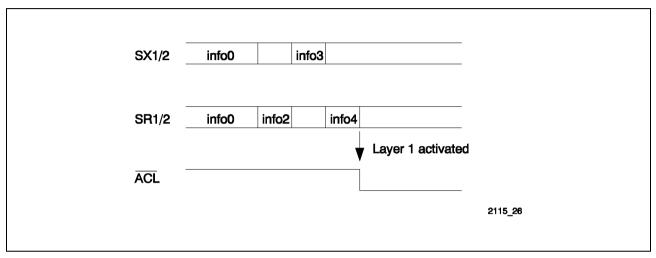

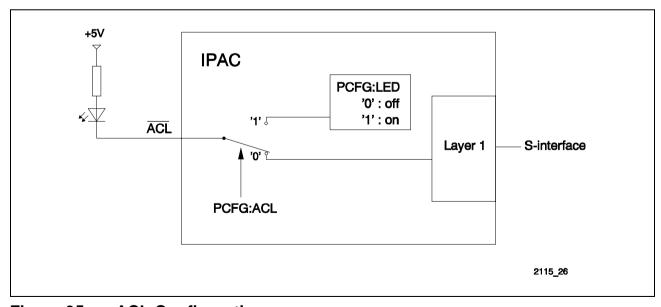

| Figure 34:  | ACL Indication of Activated Layer 1                                 | . 93 |

| Figure 35:  | ACL Configuration                                                   | . 93 |

| Figure 36:  | Layer 2 Test Loops                                                  | . 96 |

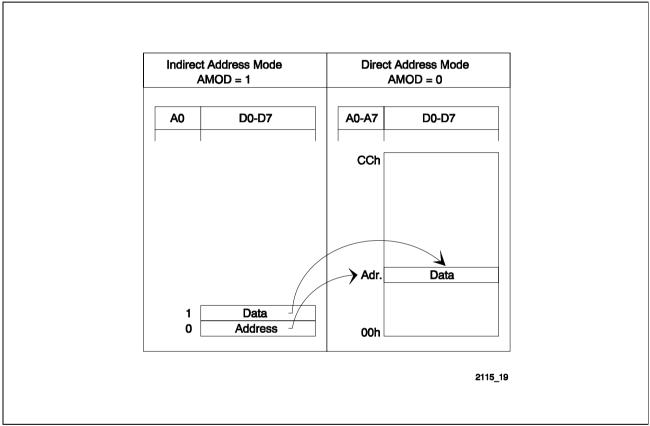

| Figure 37:  | Indirect Register Address Mode                                      | . 99 |

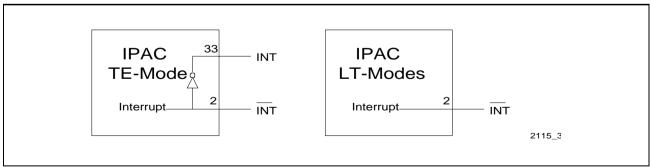

|             | High and Low Active Interrupt Output                                |      |

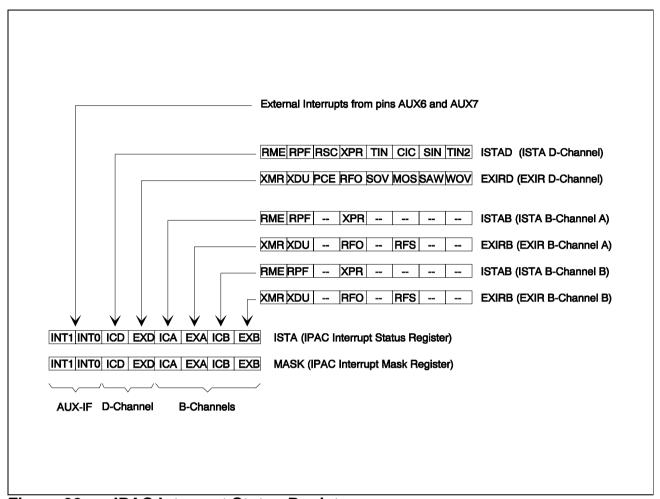

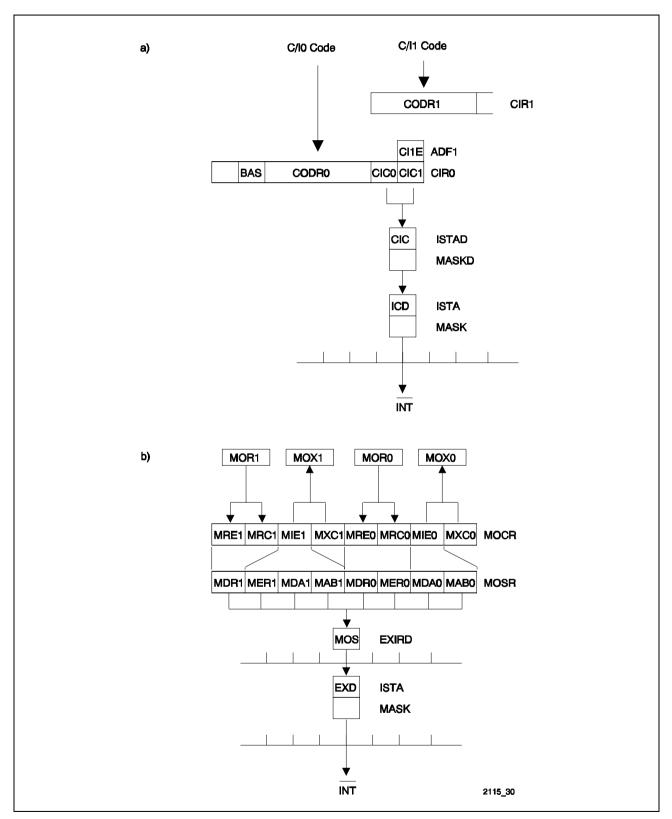

| _           | IPAC Interrupt Status Registers                                     |      |

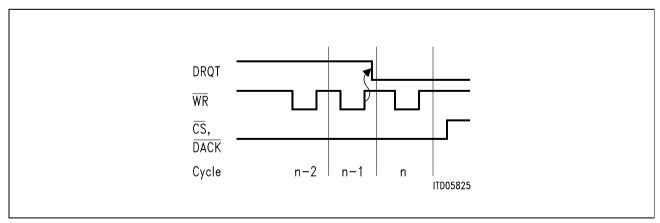

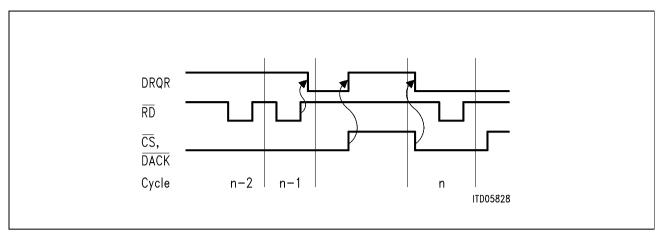

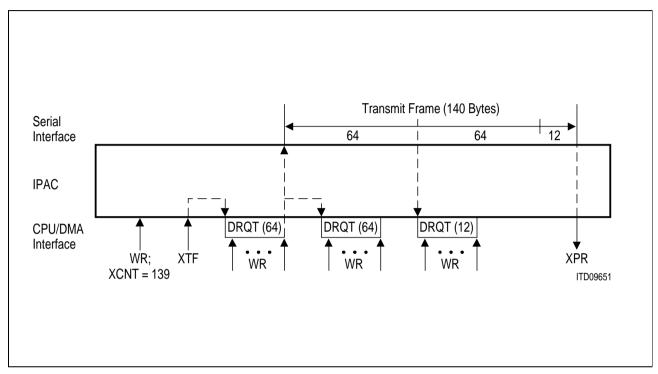

| •           | Timing Diagram for DMA-Transfers (fast) Transmit (n < 64, remainder |      |

| -           | of a long message or $n = k \times 64$ )                            | 104  |

| List of Fig    | ures                                                                     | Page |

|----------------|--------------------------------------------------------------------------|------|

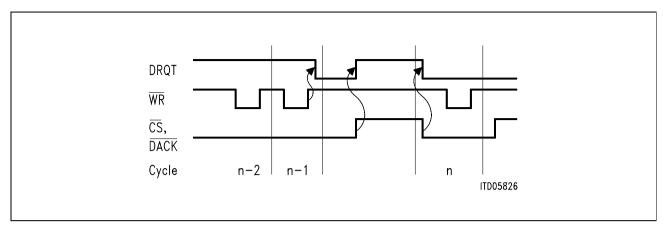

| Figure 41:     | Timing Diagram for DMA-Transfers (slow) Transmit (n < 64, remainder      |      |

|                | of a long message or $n = k \times 64$ )                                 | 105  |

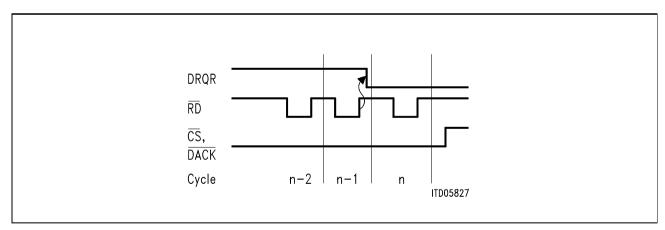

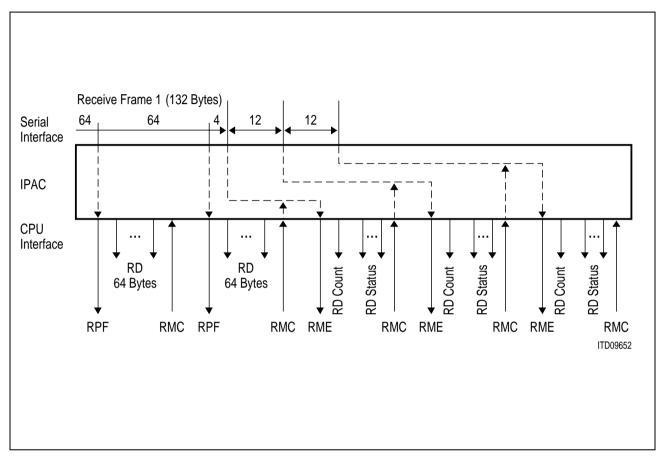

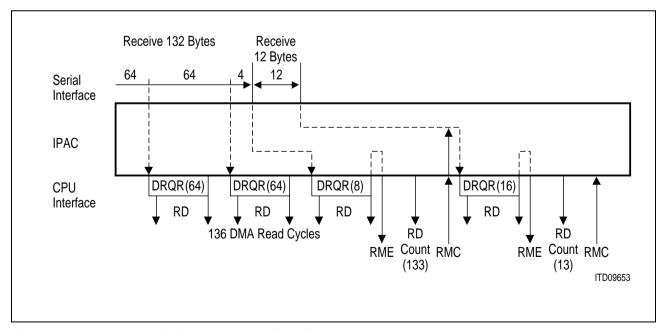

| •              | Timing Diagram for DMA-Transfer (fast) Receive (n = $k \times 64$ )      | 105  |

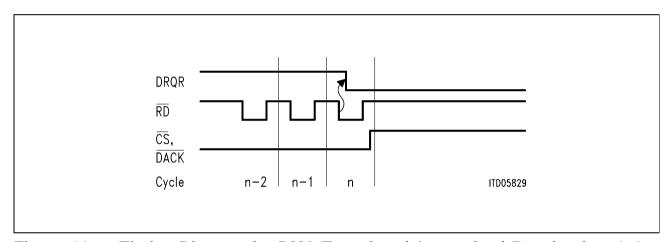

| •              | Timing Diagram for DMA-Transfers (slow) Receive (n = $k \times 64$ )     | 106  |

| Figure 44:     | Timing Diagram for DMA-Transfers (slow or fast) Receive ( $n = 4, 8, 16$ |      |

|                | or 32)                                                                   | 106  |

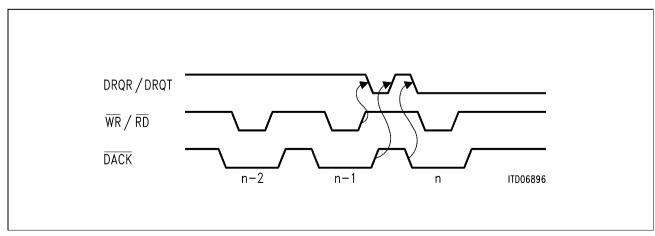

|                | DMA-Transfers with Pulsed DACK (read or write)                           | 106  |

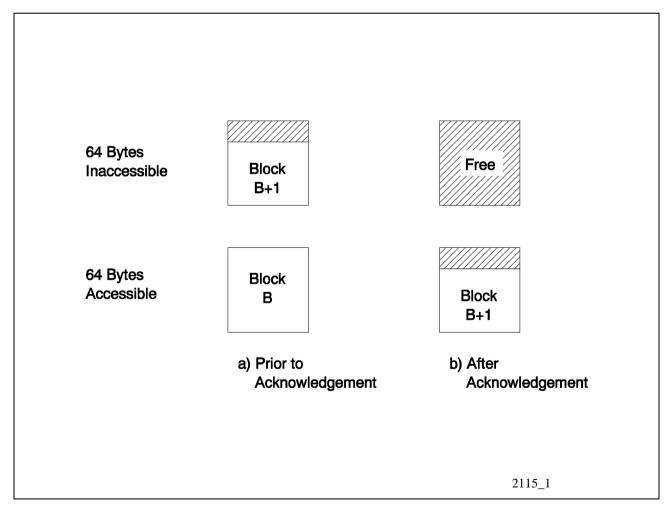

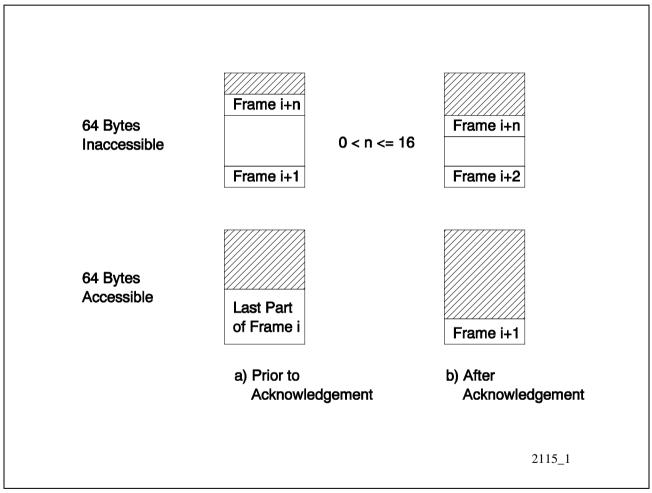

|                | Configuration of RFIFOB (Long Frames)                                    |      |

| -              | Configuration of RFIFOB (Short Frames)                                   |      |

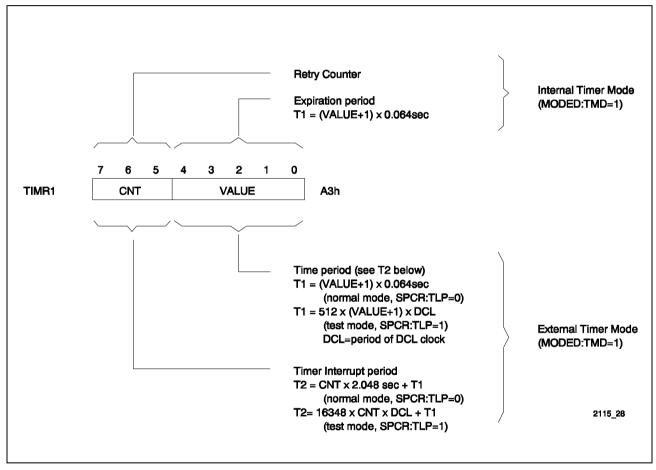

| -              | Timer 1 Register                                                         |      |

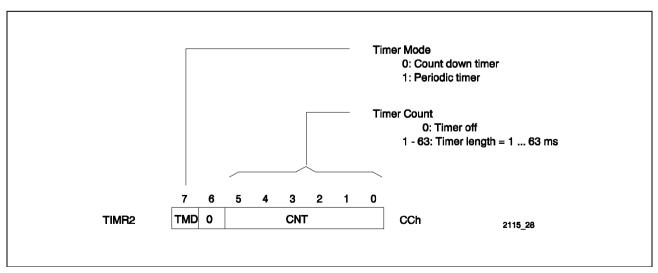

|                | Timer 2 Register                                                         |      |

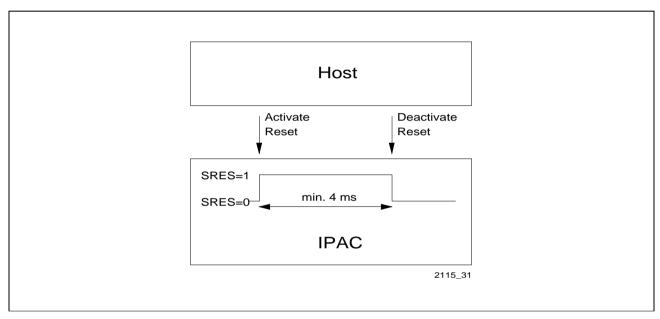

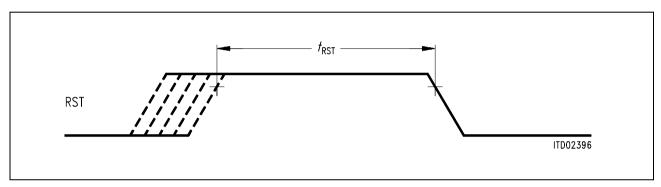

|                | Reset Timing                                                             |      |

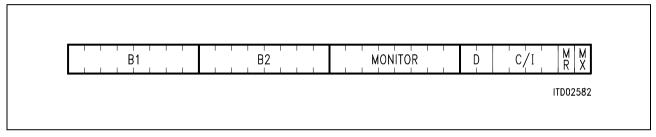

| -              | Channel Structure of IOM-2                                               | 113  |

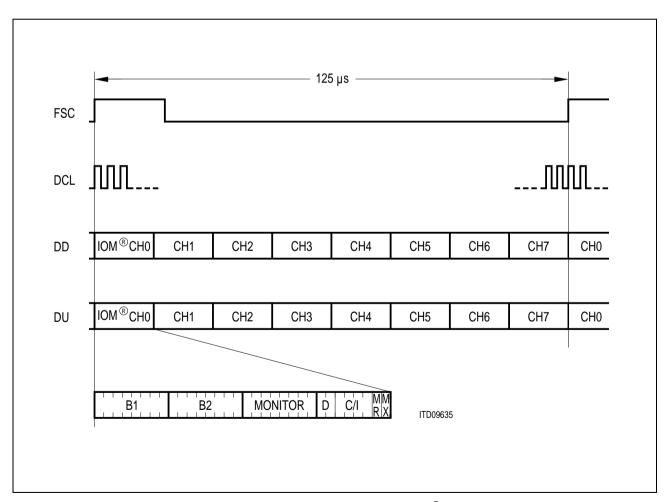

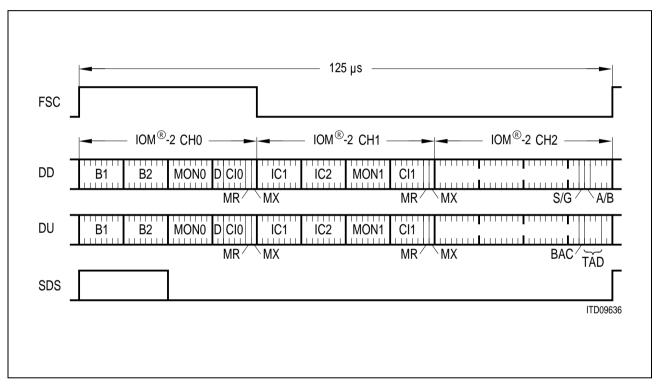

| Figure 52:     | Multiplexed Frame Structure of the IOM-2 Interface in Non-TE             |      |

| F: 50          | Timing Mode                                                              | 114  |

| •              | Definition of IOM-2 Channels in Terminal Timing Mode                     | 115  |

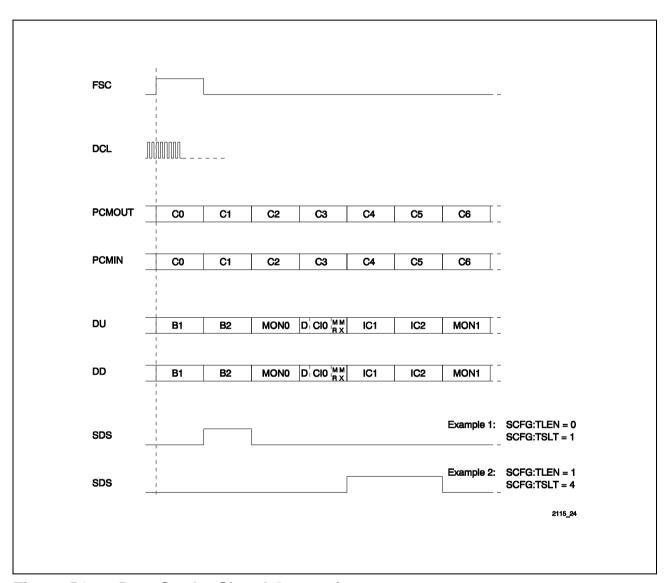

| •              | Data Strobe Signal Generation                                            | 116  |

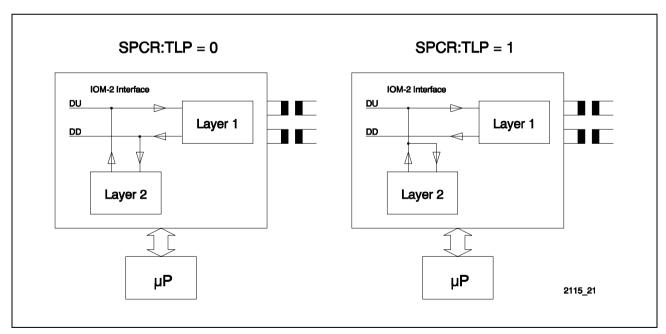

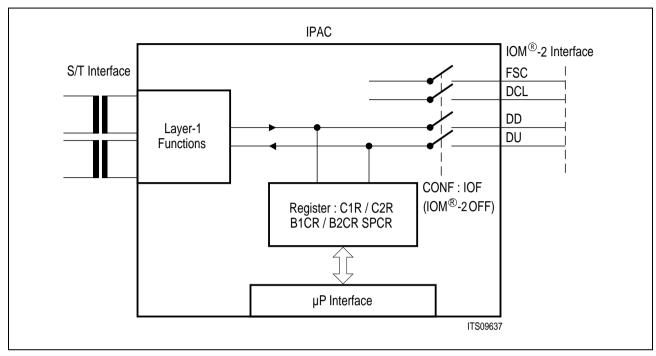

| •              | IOM-2 Direction Control                                                  | 118  |

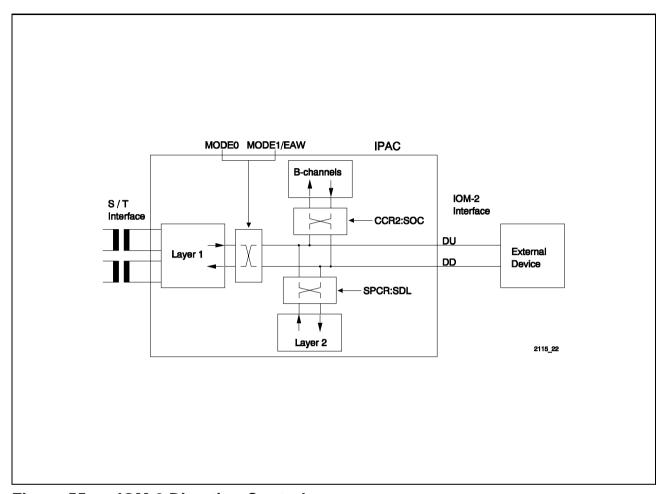

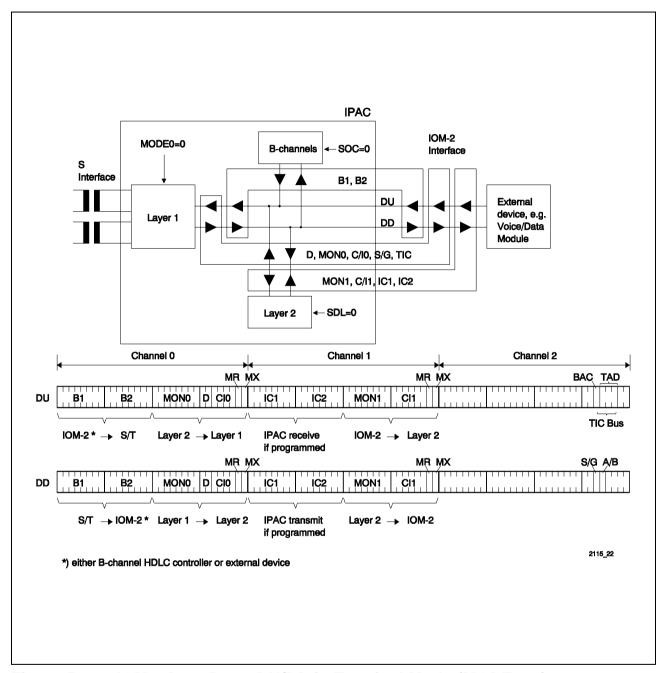

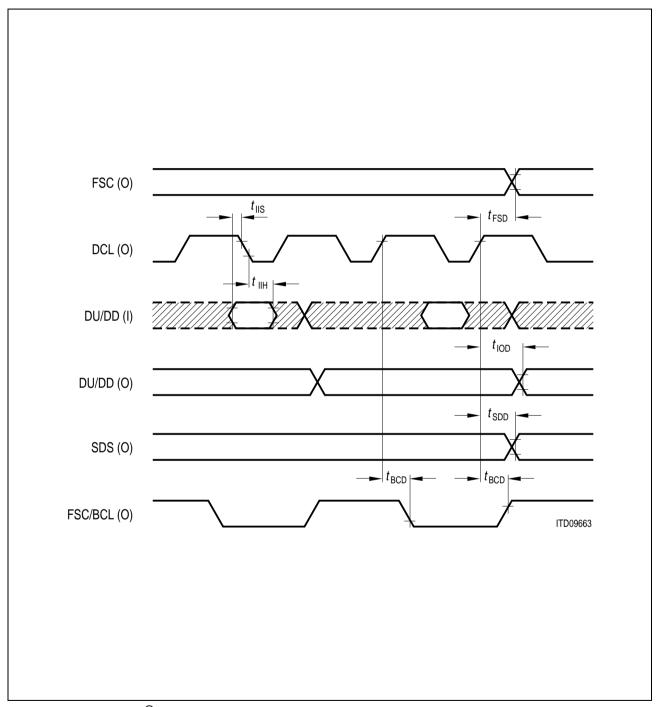

| •              | IOM-2 Data Ports DU/DD in Terminal Mode (MODE0=0)                        | 120  |

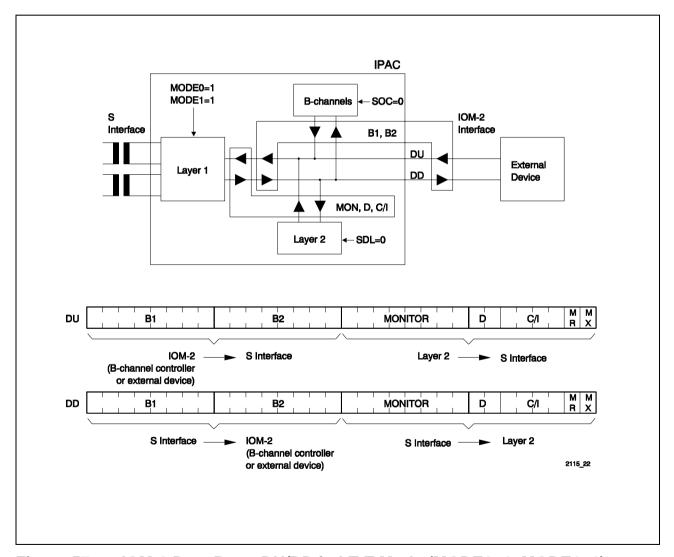

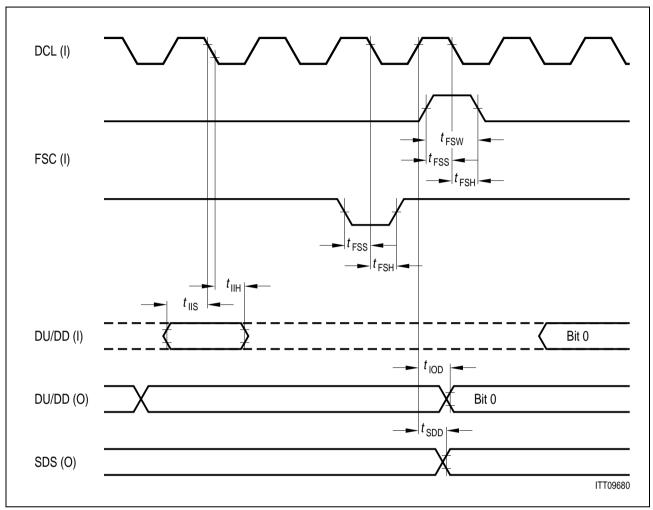

| •              | IOM-2 Data Ports DU/DD in LT-T Mode (MODE0=1, MODE1=1)                   | 121  |

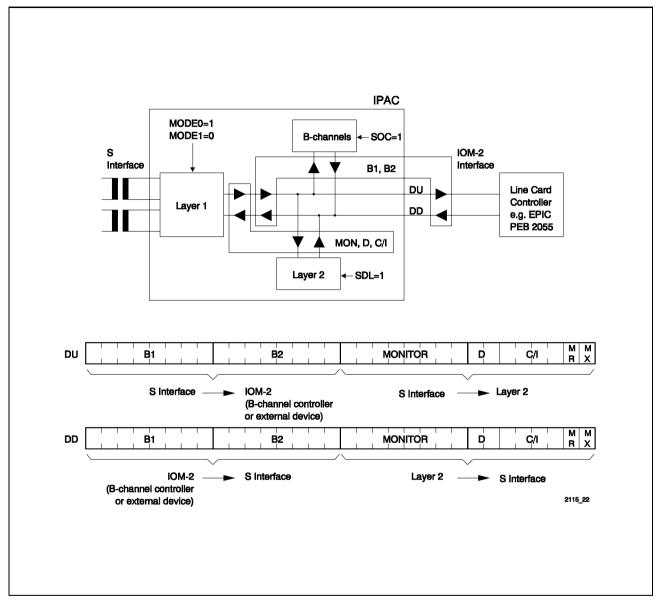

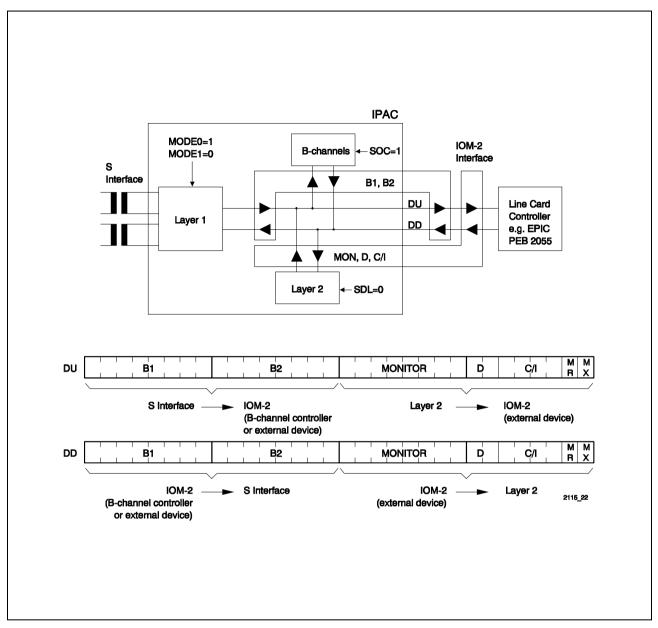

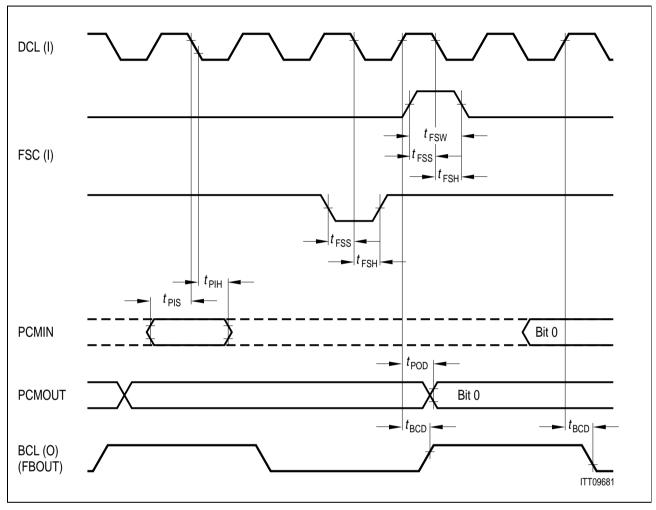

| Figure 58:     | IOM-2 Data Ports DU/DD in LT-S Mode (MODE0=1, MODE1=0) with              | 400  |

| <del>-</del> : | Normal Layer 2 Direction (SPCR:SDL=1)                                    | 123  |

| Figure 59:     | IOM-2 Data Ports DU/DD in LT-S Mode (MODE0=1, MODE1=0) with              | 404  |

| <b>-</b> : 00  | Inversed Layer 2 Direction (SPCR:SDL=0)                                  | 124  |

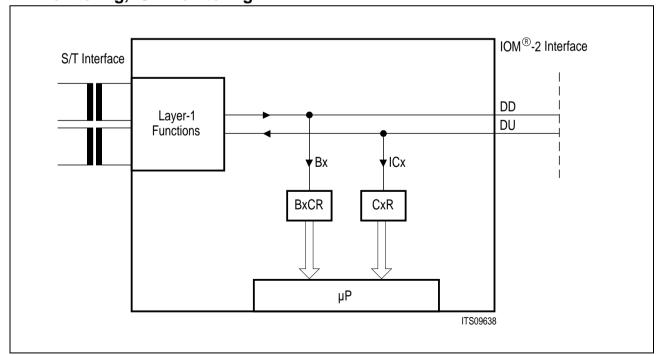

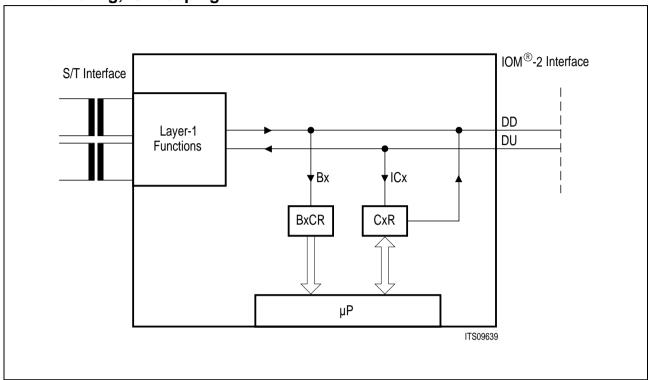

| •              | Principle of B/IC Channel Access in IOM-2 Terminal Mode                  | 126  |

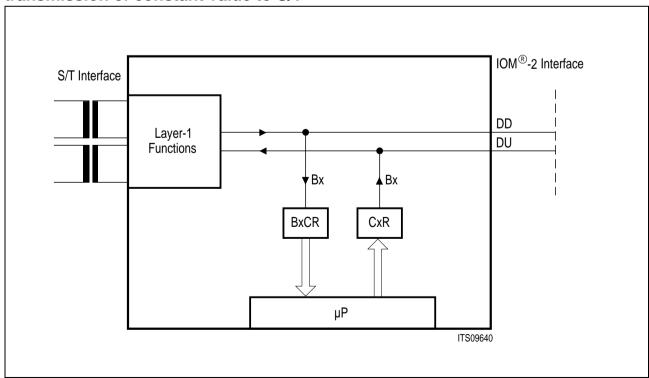

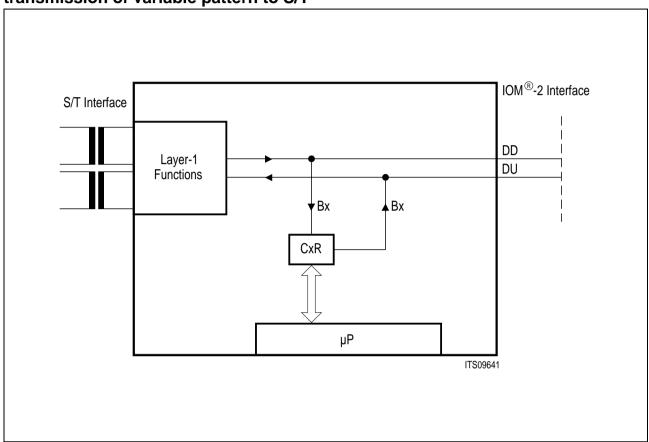

| •              | Access to B and IC Channels in IOM-2 Terminal Mode                       | 126  |

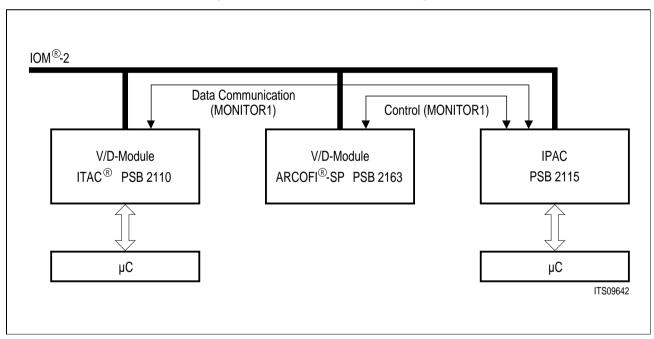

| -              | Examples of MONITOR Channel Applications in IOM-2 TE Mode                |      |

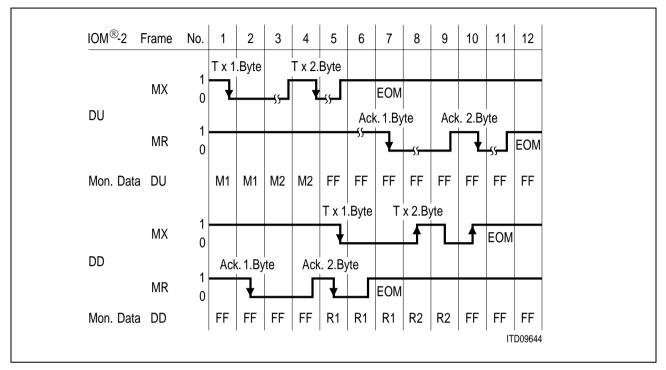

| •              | MONITOR Channel Protocol (IOM-2)                                         | 131  |

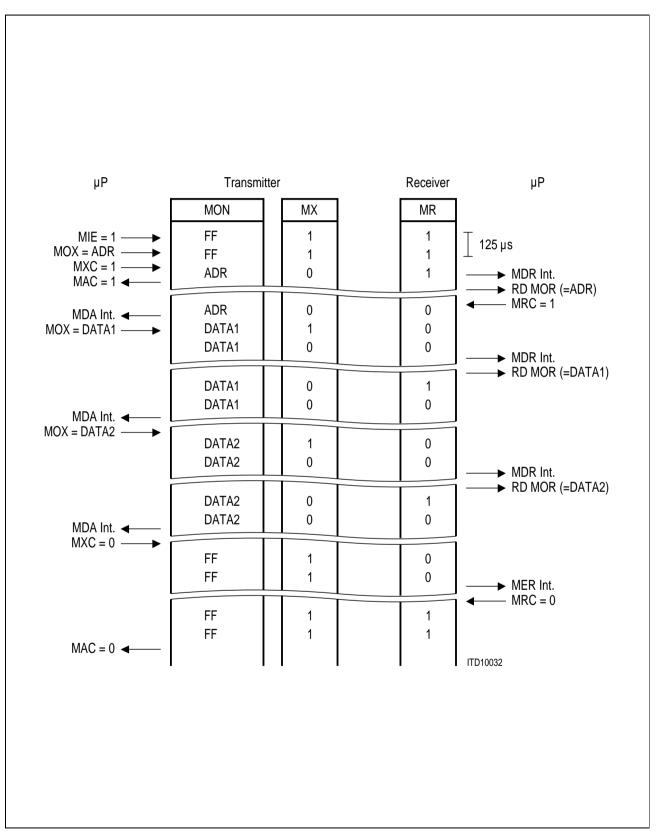

| -              | Handshake Protocol with a 2-Byte Monitor Message/Response                |      |

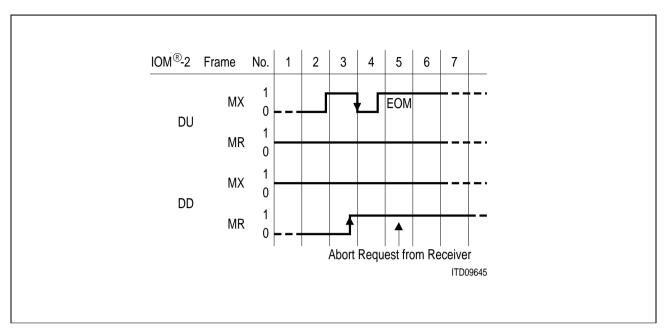

| •              | Abortion of Monitor Channel Transmission                                 |      |

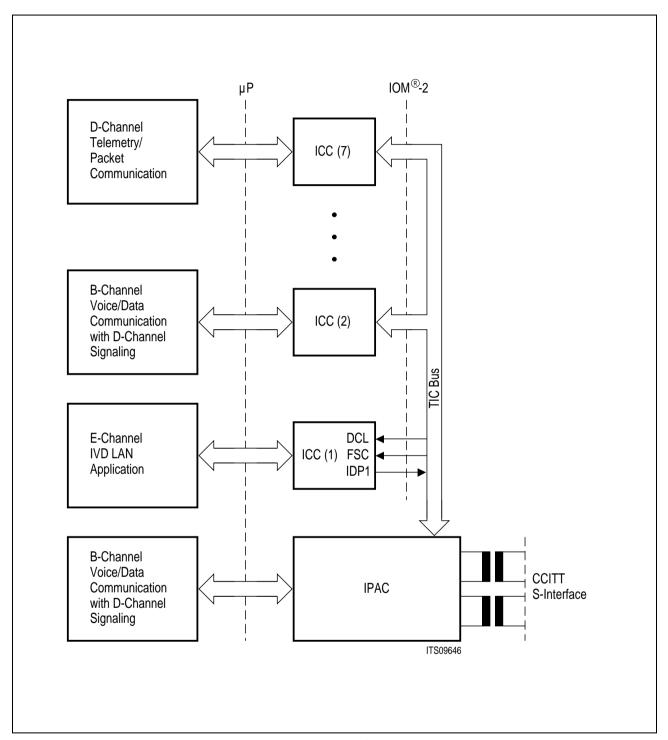

|                | Applications of TIC Bus in IOM-2 Bus Configuration                       |      |

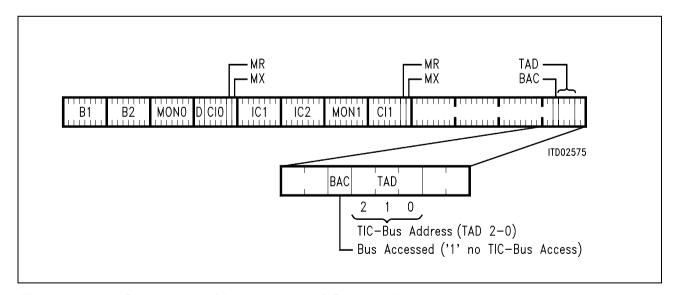

|                | Structure of Last Octet of Ch2 on DU                                     | 141  |

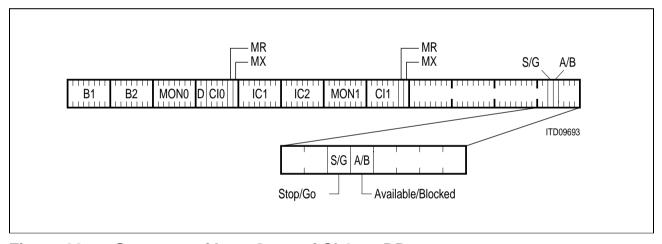

|                | Structure of Last Octet of Ch2 on DD                                     |      |

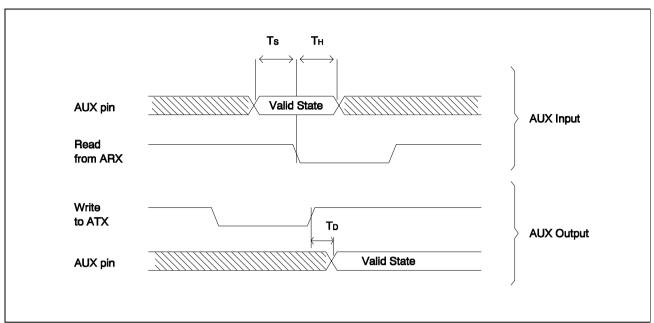

| -              | Input/Output Characteristic of AUX Pins                                  |      |

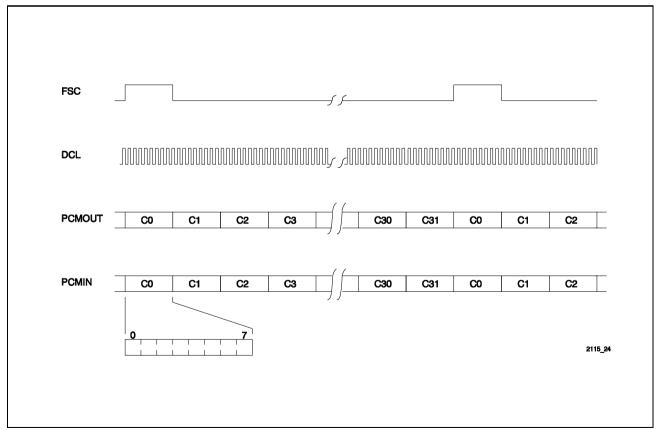

| •              | PCM Frame Alignment                                                      | 147  |

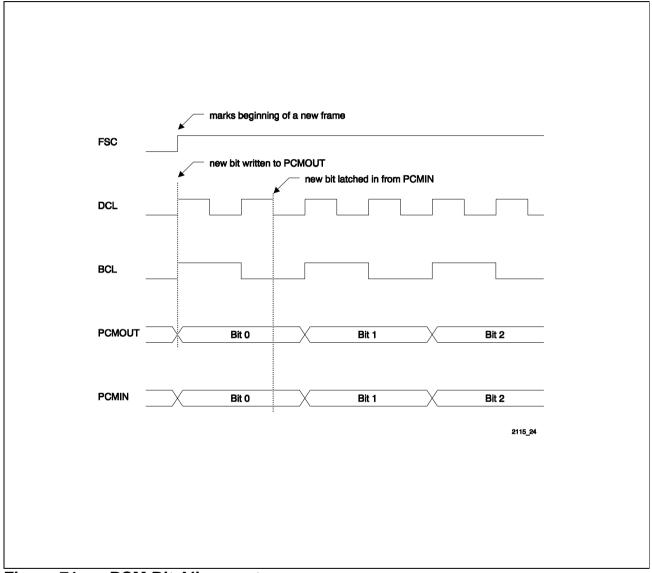

| •              | PCM Bit Alignment                                                        | 148  |

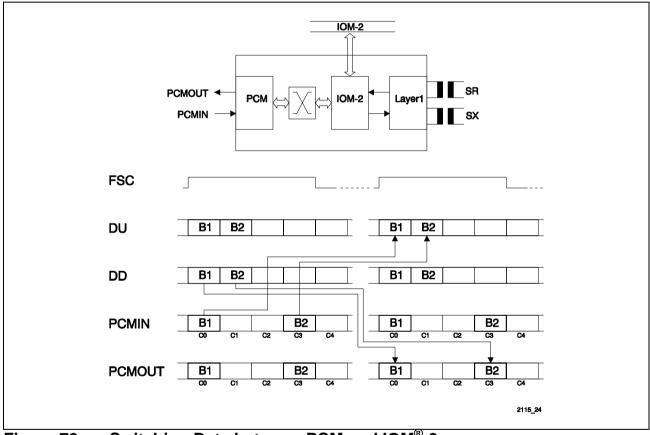

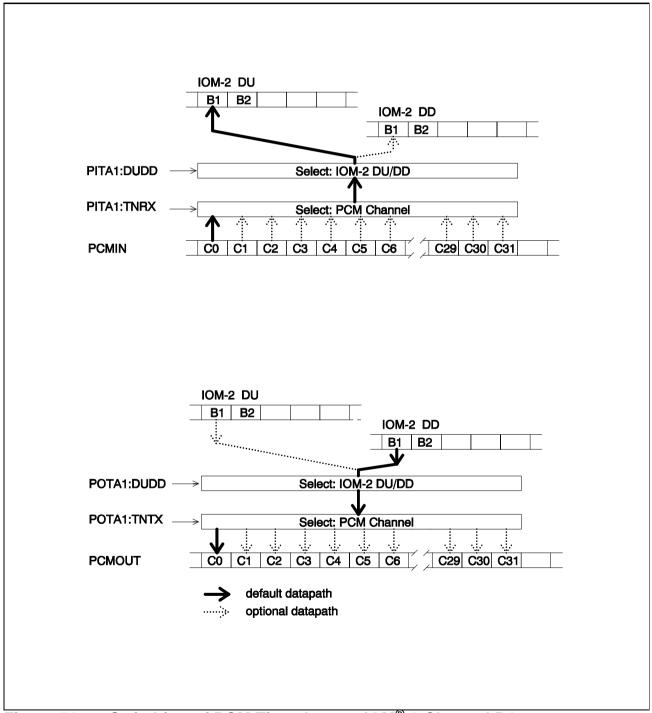

| -              | Switching Data between PCM and IOM-2                                     | 149  |

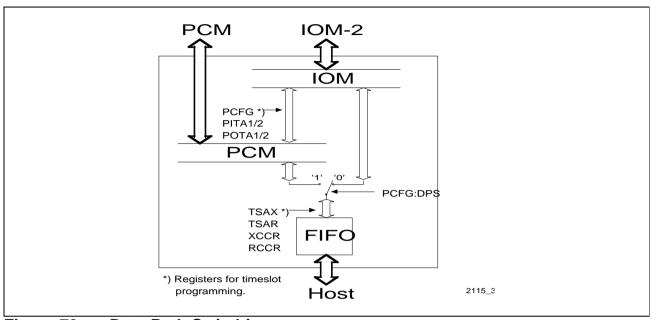

| -              | Data Path Switching                                                      | 150  |

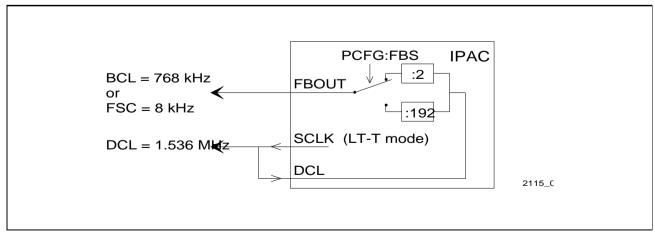

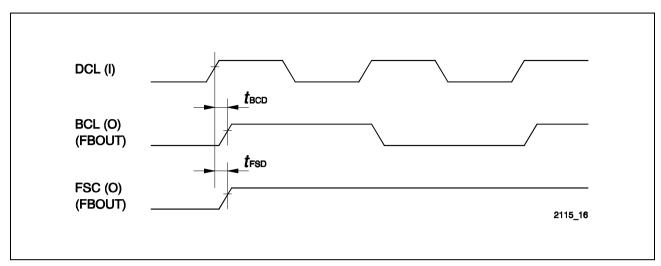

| •              | Generation of FSC and BCL in LT-T mode                                   | 150  |

|                | Multiline Application                                                    | 151  |

| -              | Switching of PCM Timeslots on IOM-2 Channel B1                           |      |

| Figure 77:     | Buffered Oscillator Clock Output                                         | 154  |

| List of Figures                                                                | Page   |

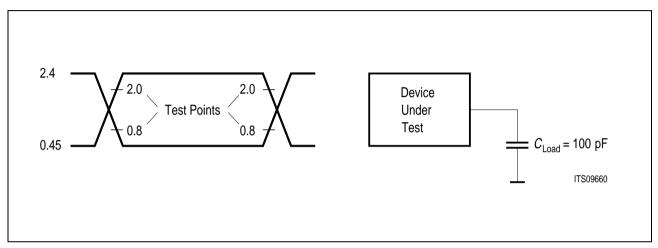

|--------------------------------------------------------------------------------|--------|