# EVRTH020/050/060

# Track and Hold Evaluation Board

#### **Features**

- ♦ SMA connectors for all signal / clock inputs and signal output.

- ◆ TMS (Track Mode Selection).

- Fully Assembled and Tested.

## **Product Description**

The EVRTH-HD is an evaluation board designed to demonstrate the performance of the Teledyne Scientific's HSD packaged track and holds, RTH020, RTH050 and RTH060. The board comes fully assembled and tested, providing an easy way to

evaluate the track and hold performance. All is needed are power, differential input and clock signals. A jumper is provided to easily toggle the TMS signal that puts the track and hold into track mode.

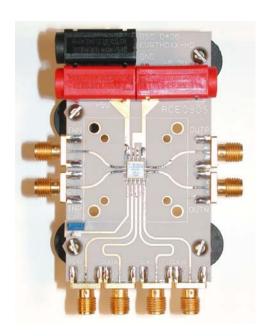

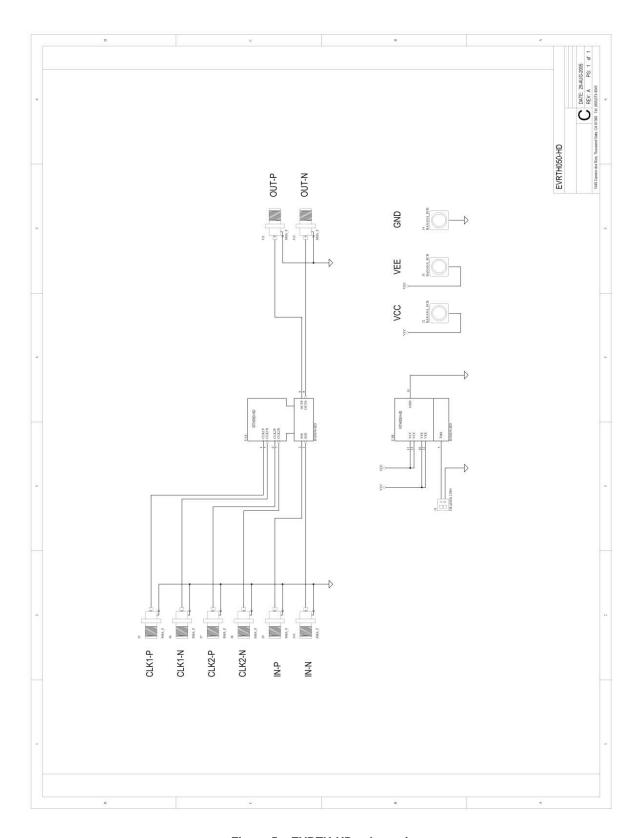

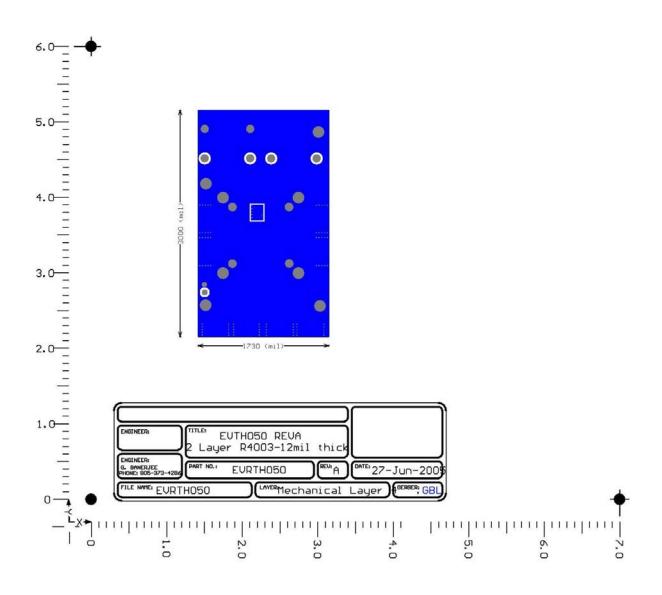

Figure 1 - EVRTH for HD packages

# Ordering information

| PART NUMBER | DESCRIPTION                                      |

|-------------|--------------------------------------------------|

| EVRTH020-HD | Track and Hold Evaluation Board with a RTH020-HD |

| EVRTH050-HD | Track and Hold Evaluation Board with a RTH050-HD |

| EVRTH060-HD | Track and Hold Evaluation Board with a RTH060-HD |

## Signal Description

#### **Power Supplies**

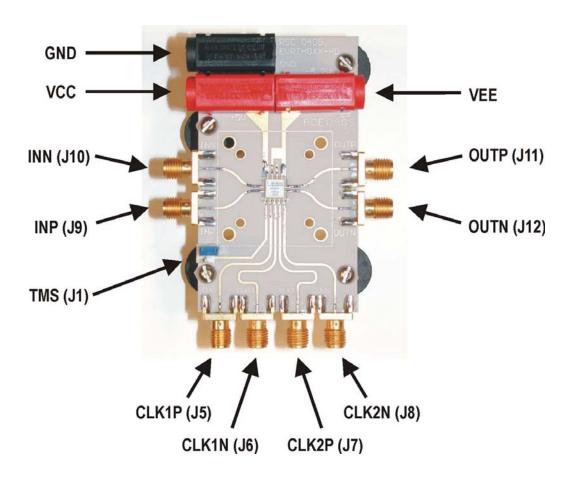

The evaluation board requires both a negative and positive supply voltage. VEE is the a -5.2V supply (250mA nominal) and VCC is a +5.0V supply (75mA nominal). The evaluation board also requires a ground connection. These connections are made using cables with banana plugs.

#### Inputs

The EVRTH-HD evaluation board has high performance, gold plated SMA connectors for the differential clocks, input and output signal. The clock and signal inputs are terminated on-chip with a  $50\Omega$  resistor to ground.

The track mode select (TMS) is a digital input that is controlled by a two pin header with an accompanying post shunt. The TMS signal can be left open for default sample mode or it can be shorted, putting both track and hold in track mode.

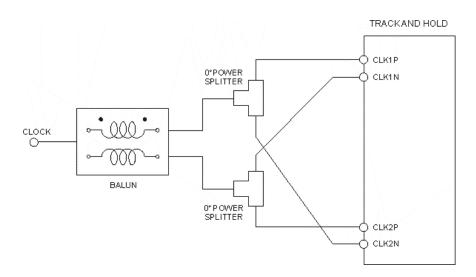

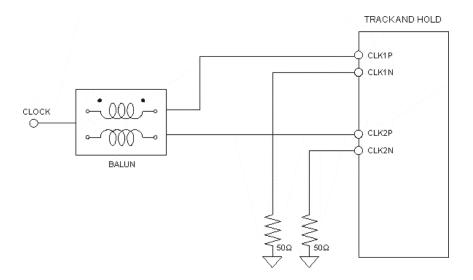

The clocks CLK1P, CLK1N, CLK2P and CLK2N are the clocks for the two individual track and hold. The two track and hold can be clocked independently (as long as the phase relationship is maintained). Single ended or differential clock schemes can be used,

although better dynamic performance is achieved with a differential clock. Figure 2 and Figure 3 illustrates simple out of phase clocking schemes, both differential and single ended. In the case of single ended clocking, the balun provide the CLK1P and CLK2P and the complementary inputs should be terminated with a  $50\Omega$  resistance to ground for optimum performance. Another option for a single ended configuration is to use a 180 degree power splitter instead of the balun. It is possible however to operate the evaluation board with single ended clocking by connecting the complementary clock inputs directly to ground, or even leaving them open (they are terminated on chip with a  $50\Omega$  resistor to ground, providing a sufficiently low impedance path to ground).

### **Outputs**

The EVRTH-HD has complementary voltage outputs, OUTP and OUTN, accessible through high performance SMA connectors. Both outputs should be terminated with a  $50\Omega$  resistance to ground. For single ended applications an output balun may be used.

Figure 2 – Setup for simple out of phase differential clocking

Figure 3 - Setup for single ended clocking

### **Components**

**Table 1: Jumper List**

| DESIGNATOR / SIGNAL | SETTINGS                                       | FUNCTION          |

|---------------------|------------------------------------------------|-------------------|

| J1 / TMS            | Open – Track Mode Off<br>Close – Track Mode On | Track Mode Select |

**Table 2: Component List**

| DESIGNATOR                        | QTY | DESCRIPTION                                 |

|-----------------------------------|-----|---------------------------------------------|

| J5, J6, J7, J8, J9, J10, J11, J12 | 8   | SMA Connector                               |

| J2, J3, J4                        | 3   | Banana Plug Sockets                         |

| J1                                | 1   | 2 Pin Header                                |

| U1                                | 1   | HD Packaged Track and Hold (RTH020/050/060) |

# **Board Configuration**

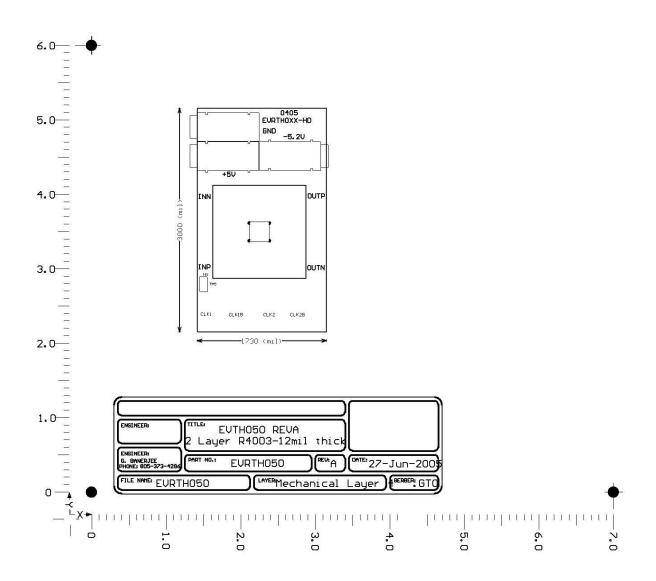

Figure 4 - EVRTH-HD board configuration

Figure 5 - EVRTH-HD schematic

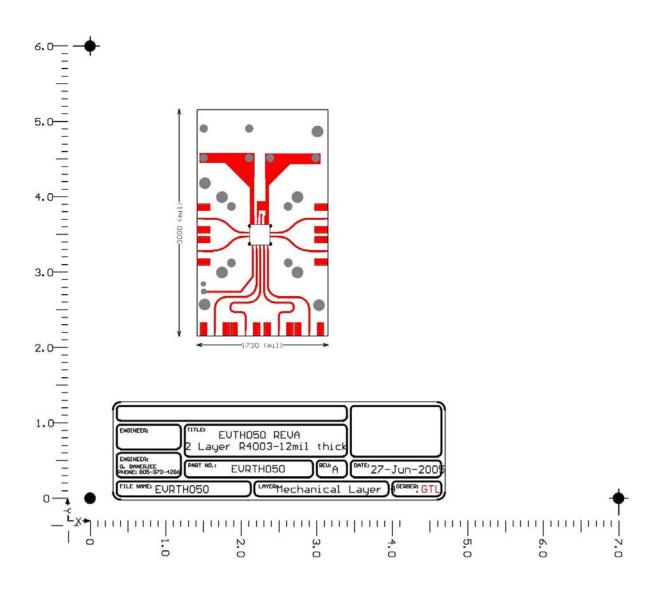

Figure 6 - Top layer stencil

Figure 7 - Top layer

Figure 8 - Drill

Figure 9 - Bottom Layer