# 32-Channel ±40V Liquid Crystal Display Row Driver

### **Ordering Information**

|        | Package Options                      |                                  |  |  |  |  |  |

|--------|--------------------------------------|----------------------------------|--|--|--|--|--|

| Device | 44-Lead<br>Quad Plastic Chip Carrier | 44-Lead<br>Quad Plastic Gullwing |  |  |  |  |  |

| HV6008 | HV6008PJ                             | HV6008PG                         |  |  |  |  |  |

### **Features**

- ☐ Symmetrical ± 40V output swing

- □ Active return to GND

- ☐ 15mA peak source/sink/GND current per channel

- → +5V control logic

- Special shift register with clear

- Phase shift control

- Output enable

- Data out enable

- 1MHz shift register

- Surface mount package available

### Absolute Waxing Parings

| Supply voltage, V <sub>DD1</sub>                | -6V                                          |  |  |  |

|-------------------------------------------------|----------------------------------------------|--|--|--|

| Supply voltage V <sub>DD2</sub> <sup>1</sup>    | +6V                                          |  |  |  |

| Supply vallage, v 1,2                           | +42V                                         |  |  |  |

| Supply voltage.                                 | -42V                                         |  |  |  |

| Logic input levels                              | $V_{\rm DD1}$ - 0.3V to $V_{\rm DD2}$ + 0.3V |  |  |  |

| Ground currrent <sup>2</sup>                    | 700mA                                        |  |  |  |

| Continuous total power dissipation <sup>3</sup> | 1W                                           |  |  |  |

| Operating temperature range                     | -40°C to +85°C                               |  |  |  |

| Storage temperature range                       | -65°C to +150°C                              |  |  |  |

| ·                                               | ·                                            |  |  |  |

#### Notes:

- 1. All voltages are referenced to GND.

- Duty cycle is limited by the total power dissipated in the package.

- 3. For operation above 25°C ambient derate linearly to 85°C at 16.7mW/°C.

### General Description

Not recommend ew designs.

The HV60 is 22-ch and lich id crystal display driver with 3-state DMOS or F outrocan be set to +40V, -40V, or GND.

The HV60 is 22-ch and lich id crystal display driver with 3-state be set to +40V, -40V, or GND.

The HV60 is 22-ch and lich id crystal display driver with 3-state be set to +40V, -40V, or GND.

The HV60 is 22-ch and lich id crystal display driver with 3-state be set to +40V, -40V, or GND.

The HV60 is 22-ch and lich id crystal display driver with 3-state be set to +40V, -40V, or GND.

The HV60 is 22-ch and lich id crystal display driver with 3-state be set to +40V, -40V, or GND.

The HV60 is 22-ch and lich id crystal display driver with 3-state be set to +40V, -40V, or GND.

The HV60 is 22-ch and lich id crystal display driver with 3-state be set to +40V, -40V, or GND.

The HV60 is 22-ch and lich id crystal display driver with 3-state be set to +40V, -40V, or GND.

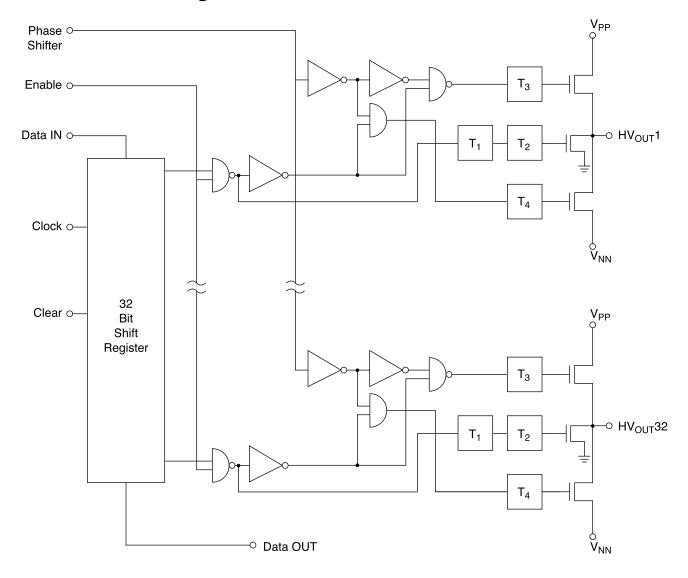

Ph. logic, and 32-bit shift register with Clear, Enable, and Ph. logic, and 32 high voltage output buffers. With the nable of low, all outputs are placed in the return to zero (D) s. e. When Enable is high, each output reflects the data shift register bit. All outputs with a logic "0" in their shift er will be in the return to zero state. Outputs with a logic "1" neir shift register will reflect the state of the phase shift pin. These outputs will be switched to V<sub>PP</sub> when phase shift is high and V<sub>NN</sub> when phase shift is logic "0".

Additional functions provided are Shift Register Clear and Data Out. All bits of the shift register are changed to logic "0" when Clear is pulled low. With Clear at a logic "1", normal shift register operation proceeds. The data output reflects the status of the 32nd shift register stage.

## Electrical Characteristics (over recommended operating conditions unless noted)

### **DC Characteristics**

| Symbol             | Para                           | meter                         | Min              | Тур  | Max       | Units | Conditions                                                 |

|--------------------|--------------------------------|-------------------------------|------------------|------|-----------|-------|------------------------------------------------------------|

| I <sub>DD1,2</sub> | V <sub>DD</sub> supply current | V <sub>DD1</sub>              | _                |      | 500       | μΑ    | $V_{I} = 4V, V_{DD1} = -6V$<br>$V_{I} = 4V, V_{DD2} = +6V$ |

| V <sub>IH</sub>    | Logic input high               |                               | +2               |      | $V_{DD2}$ | V     | $V_{DD1} = -4.5V,$                                         |

| V <sub>IL</sub>    | Logic input low                |                               | V <sub>DD1</sub> |      | -2        | V     | V <sub>DD2</sub> = +4.5V                                   |

| V <sub>OH</sub>    | Logic output high              |                               | +2               |      |           | V     | $V_{DD1} = -4.5V$<br>$V_{DD2} = +4.5V$                     |

| V <sub>OL</sub>    | Logic output low               |                               |                  |      | -2        | V     | $I_{OH} = -15\mu A$ $I_{OL} = 250\mu A$                    |

| I <sub>IH</sub>    | High-level logic input         | current                       |                  |      | +3        | μΑ    | $V_I = V_{DD}$ , $V_{DD1,2} = max$                         |

| I <sub>IL</sub>    | Low-level logic input          | current                       |                  |      | -50       | μΑ    | $V_I = 0V$ , $V_{DD1,2} = max$                             |

| I <sub>PP</sub>    | High voltage supply            | current                       |                  |      | +1        | mA    | Static, no load                                            |

| I <sub>NN</sub>    | High voltage supply            | current                       |                  |      | -1        | mA    | Static, no load                                            |

| V <sub>OH</sub>    | Output voltage high            |                               | +39              |      |           | V     | $V_{PP}, V_{NN} = \pm 40$                                  |

| V <sub>CL</sub>    | Output voltage clam            | )                             | -20              |      | +20       | mV    | No load                                                    |

| V <sub>OL</sub>    | Output voltage low             |                               |                  |      | -39       | V     |                                                            |

| Z <sub>OH</sub>    | Output switch imped            | ence high                     |                  | 1000 |           |       |                                                            |

| Z <sub>CL</sub>    | Output switch imped            | Output switch impedance clamp |                  |      |           | Ω     | $V_{PP}$ , $V_{NN} = \pm 40$                               |

| Z <sub>OL</sub>    | Output switch imped            | ance low                      |                  | 700  |           |       | $I_O = \pm 15 \text{mA}$                                   |

| Io                 | DC output current              | Output H or L                 |                  |      | 5         | mA    | 1 output only                                              |

|                    |                                | Data out H or L               |                  |      | 150       | μΑ    |                                                            |

### **AC Characteristics**

| Symbol          | Parameter                           | Min | Тур | Max | Units | Conditions |

|-----------------|-------------------------------------|-----|-----|-----|-------|------------|

| t <sub>WH</sub> | Width of high data pulse            | 500 |     |     | ns    |            |

| t <sub>WL</sub> | Width of low data pulse             | 500 |     |     | ns    |            |

| t <sub>SU</sub> | Data set-up time before clock falls | 25  |     |     | ns    |            |

| t <sub>H</sub>  | Data hold time after clock falls    | 10  |     |     | ns    |            |

|                 | Phase shift duty cycle              |     | 50  |     | %     |            |

# **Recommended Operating Conditions**

| Symbol             | Parameter                       | Min | Тур | Max              | Units |

|--------------------|---------------------------------|-----|-----|------------------|-------|

| $V_{DD1}$          | Logic supply voltage            | -4  |     | -6               | V     |

| $V_{DD2}$          | Logic supply voltage            | +4  |     | +6               | V     |

| V <sub>PP</sub>    | High voltage supply             | +10 |     | +40              | V     |

| V <sub>NN</sub>    | High voltage supply             | -10 |     | -40              | V     |

| V <sub>IH</sub>    | High-level input voltage        | +2V |     | $V_{DD2}$        | V     |

| V <sub>IL</sub>    | Low-level input voltage         | -2V |     | V <sub>DD1</sub> | V     |

| I <sub>O Pk.</sub> | Peak output current (any state) |     |     | ±80              | mA    |

| T <sub>A</sub>     | Operating free-air temperature  | -40 |     | +70              | °C    |

| f <sub>DIN</sub>   | Input data rate                 |     |     | 1                | MHz   |

| f <sub>PS</sub>    | Phase shift rate                |     |     | 20               | KHz   |

Note:

Power-up sequence should be the following:

- 1. Connect ground.

- 2. Apply V<sub>DD</sub>.

- 3. Set all inputs (Data, CLK, Enable, etc.) to a known state.

- 4. Apply V<sub>PP</sub> and V<sub>NN</sub>.

Power-down sequence should be the reverse of the above.

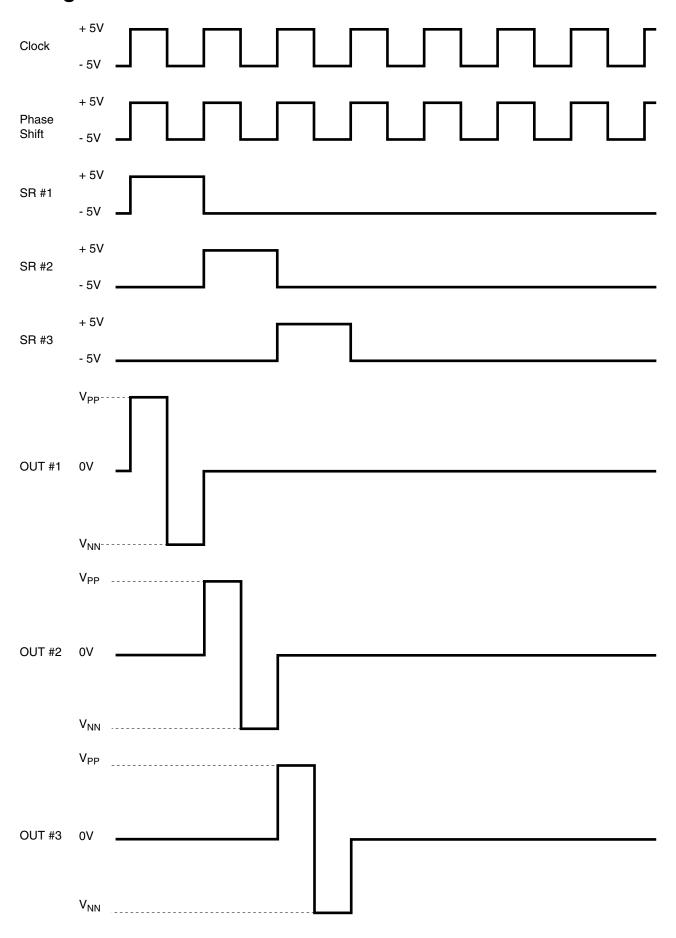

# **Switching Waveform**

# **Functional Block Diagram**

### **Function Table**

|                |        |          | Inputs |        |       | i         |                                                 |          |

|----------------|--------|----------|--------|--------|-------|-----------|-------------------------------------------------|----------|

| Function       | Data   | CLK      | CLR    | Enable | Phase | Shift Reg | HV Outputs                                      | Data Out |

|                | ln     |          |        |        | Shift | 1 232     | 1 232                                           |          |

| CLR Reg        | X      | Х        | Н      | Х      | Х     | ALL L     | ALL GND                                         | Г        |

| All output GND | Х      | Х        | Х      | L      | Х     | * * *     | ALL GND                                         | *        |

| Load S/R       | H or L | <b>↓</b> | L      | L      | Х     | H or L ** | ALL GND                                         | *        |

|                |        |          |        |        | Х     | L LL      | GND GNDGND                                      | *        |

| Output State   | X      | H or L   | L      | Н      | Н     | Н НН      | $V_{PP} V_{PP}V_{PP}$                           | *        |

|                |        |          |        |        | L     | Н НН      | V <sub>NN</sub> V <sub>NN</sub> V <sub>NN</sub> | *        |

#### Notes:

- X = Irrelevant

\* = Dependent

- \* = Dependent on previous stage's state before the last CLK

- = High to low transition

- H = High level

- L = Low level

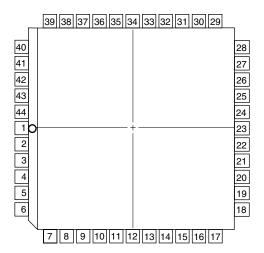

# **Pin Configurations**

#### 44-Pin J-Lead

| Pin | Function             | Pin | Function             |

|-----|----------------------|-----|----------------------|

| 1   | HV <sub>OUT</sub> 16 | 23  | $V_{DD\ 1}$          |

| 2   | HV <sub>OUT</sub> 15 | 24  | Enable               |

| 3   | HV <sub>OUT</sub> 14 | 25  | $V_{DD\ 2}$          |

| 4   | HV <sub>OUT</sub> 13 | 26  | GND                  |

| 5   | HV <sub>OUT</sub> 12 | 27  | Data Out             |

| 6   | HV <sub>OUT</sub> 11 | 28  | HV <sub>OUT</sub> 32 |

| 7   | HV <sub>OUT</sub> 10 | 29  | HV <sub>OUT</sub> 31 |

| 8   | $V_{PP}$             | 30  | HV <sub>OU</sub> 30  |

| 9   | HV <sub>OUT</sub> 9  | 31  | HV <sub>OUT</sub> 29 |

| 10  | HV <sub>OUT</sub> 8  | 32  | HV <sub>OUT</sub> 28 |

| 11  | HV <sub>OUT</sub> 7  | 33  | HV <sub>OUT</sub> 27 |

| 12  | HV <sub>OUT</sub> 6  | 34  | HV <sub>OUT</sub> 26 |

| 13  | HV <sub>OUT</sub> 5  | 35  | HV <sub>OUT</sub> 25 |

| 14  | HV <sub>OUT</sub> 4  | 36  | HV <sub>OUT</sub> 24 |

| 15  | HV <sub>OUT</sub> 3  | 37  | $V_{NN}$             |

| 16  | HV <sub>OUT</sub> 2  | 38  | HV <sub>OUT</sub> 23 |

| 17  | HV <sub>OUT</sub> 1  | 39  | HV <sub>OUT</sub> 22 |

| 18  | Data In              | 40  | HV <sub>OUT</sub> 21 |

| 19  | GND                  | 41  | HV <sub>OUT</sub> 20 |

| 20  | Phase Shift          | 42  | HV <sub>OUT</sub> 19 |

| 21  | Clock                | 43  | HV <sub>OUT</sub> 18 |

| 22  | Clear                | 44  | HV <sub>OUT</sub> 17 |

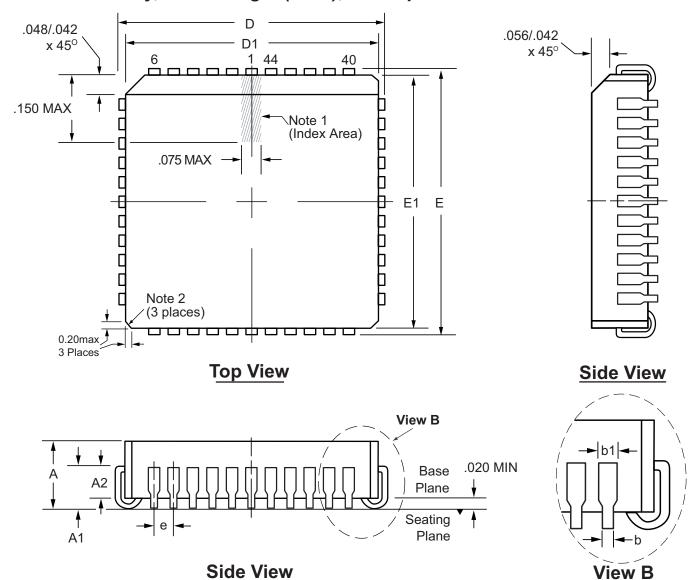

# **Package Outlines**

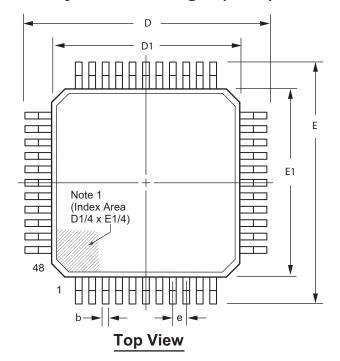

top view 44-pin J Lead Package

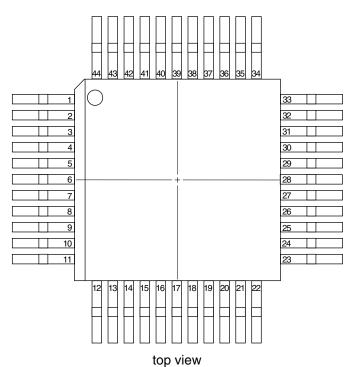

### 44-Pin Quad Palstic Package

| Pin | Function             | Pin | <b>Function</b>      |

|-----|----------------------|-----|----------------------|

| 1   | HV <sub>OUT</sub> 21 | 23  | Data In              |

| 2   | HV <sub>OUT</sub> 20 | 24  | GND                  |

| 3   | HV <sub>OUT</sub> 19 | 25  | Phase Shift          |

| 4   | HV <sub>OUT</sub> 18 | 26  | Clock                |

| 5   | HV <sub>OUT</sub> 17 | 27  | Clear                |

| 6   | HV <sub>OUT</sub> 16 | 28  | $V_{DD1}$            |

| 7   | HV <sub>OUT</sub> 15 | 29  | Enable               |

| 8   | HV <sub>OUT</sub> 14 | 30  | $V_{DD2}$            |

| 9   | HV <sub>OUT</sub> 13 | 31  | GND                  |

| 10  | HV <sub>OUT</sub> 12 | 32  | Data Out             |

| 11  | HV <sub>OUT</sub> 11 | 33  | HV <sub>OUT</sub> 32 |

| 12  | HV <sub>OUT</sub> 10 | 34  | HV <sub>OUT</sub> 31 |

| 13  | $V_{PP}$             | 35  | HV <sub>OUT</sub> 30 |

| 14  | HV <sub>OUT</sub> 9  | 36  | HV <sub>OUT</sub> 29 |

| 15  | HV <sub>OUT</sub> 8  | 37  | HV <sub>OUT</sub> 28 |

| 16  | HV <sub>OUT</sub> 7  | 38  | HV <sub>OUT</sub> 27 |

| 17  | HV <sub>OUT</sub> 6  | 39  | HV <sub>OUT</sub> 26 |

| 18  | HV <sub>OUT</sub> 5  | 40  | HV <sub>OUT</sub> 25 |

| 19  | HV <sub>OUT</sub> 4  | 41  | HV <sub>OUT</sub> 24 |

| 20  | HV <sub>OUT</sub> 3  | 42  | $V_{NN}$             |

| 21  | HV <sub>OUT</sub> 2  | 43  | HV <sub>OUT</sub> 23 |

| 22  | HV <sub>OUT</sub> 1  | 44  | HV <sub>OUT</sub> 22 |

44-pin Quad Plastic Gullwing Package

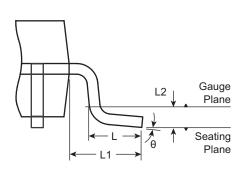

# 44-Lead PQFP Package Outline (PG)

10x10mm body, 2.45mm height (max.), 0.80mm pitch

View B

View B

Note 1: A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier may be either a mold, or an embedded metal or marked feature.

| Symbo          | ol  | Α    | A1   | A2   | b    | D     | D1    | Е     | E1    | е           | L    | L1          | L2          | θ    | θ1  |

|----------------|-----|------|------|------|------|-------|-------|-------|-------|-------------|------|-------------|-------------|------|-----|

| Dimension (mm) | MIN | -    | 0.25 | 1.95 | 0.30 | 13.65 | 9.80  | 13.65 | 9.80  | 0.00        | 0.73 | 4.05        | 0.05        | 3.5° | 5°  |

|                | NOM | -    | -    | 2.00 | -    | 13.90 | 10.00 | 13.90 | 10.00 | 0.80<br>BSC | 0.88 | 1.95<br>REF | 0.25<br>BSC | -    | -   |

| (11111)        | MAX | 2.45 | -    | 2.10 | 0.45 | 14.15 | 10.20 | 14.15 | 10.20 | ВОО         | 1.03 | IXLI        | Воо         | 7°   | 16° |

JEDEC Registration M0-112, Variation AA-2, Issue B, Sep.1995. Drawings not to scale.

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell its products for use in such applications, unless it receives an adequate "product liability indemnification insurance agreement". Supertex does not assume responsibility for use of devices described and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the **Supertex** website: http://www.supertex.com.

©2007 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

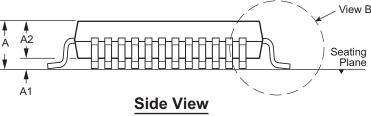

## 44-Lead PLCC Package Outline (PJ)

.653x.653in body, .180in height (max.), .050in pitch

#### Note:

1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier may be either a mold, or an embedded metal or marked feature. 2. Exact shape of this feature is optional.

| Sym                | bol | Α    | A1   | A2   | b    | b1   | D    | D1   | E    | E1   | е           |

|--------------------|-----|------|------|------|------|------|------|------|------|------|-------------|

| Dimension (inches) | MIN | .165 | .090 | .062 | .013 | .026 | .685 | .650 | .685 | .650 | 050         |

|                    | NOM | .172 | .105 | -    | -    | -    | .690 | .653 | .690 | .653 | .050<br>BSC |

| (inches)           | MAX | .180 | .120 | .083 | .021 | .036 | .695 | .656 | .695 | .656 |             |

JEDEC Registration MS-018, Variation AC, Issue A, June, 1993. Drawings are not to scale.

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell its products for use in such applications, unless it receives an adequate "product liability indemnification insurance agreement". Supertex does not assume responsibility for use of devices described and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the **Supertex** website: http://www.supertex.com.

©2007 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

View B

Doc. #: DSPD-44PLCCPJ

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

### Supertex:

HV6008PG-M914 HV6008PJ-M903 HV6008PJ HV6008PG