SLUS529 - MAY 2002

## OPTICAL NETWORK HOT SWAP POWER MANAGER

#### **FEATURES**

- Enables Hot Swap in High Availability Optical Network Systems

- Programmable Current Slew Rate

- Power Supply Sequencing

- Sense Resistors Set Peak Current (IMAX)

- Overcurrent Circuit Breaker at 2× IMAX

- Precharge Output

- Logic Low Power Good Output

- Logic Low Enable Input

- On-Chip Charge Pump

- Low Sleep Mode Current

- Undervoltage Lockout (UVLO)

- Minimal External Parts Count

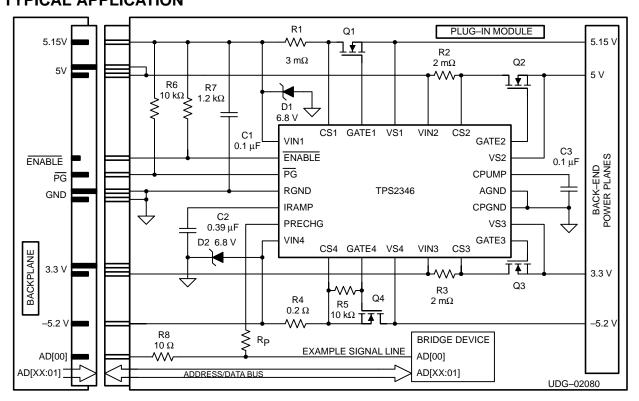

- 24-pin TSSOP Package TYPICAL APPLICATION

#### DESCRIPTION

The TPS2346 Optical Network Hot Swap Power Manager (HSPM) provides highly-integrated supply control of three positive (3.3-V, 5-V, and 5.15-V) and one negative (-5.2-V) supply rails with a minimum number of external components. A linear current amplifier (LCA) in each of the four device channels provides closed-loop control of load current during insertion and extraction events. This allows the designer to configure the plug-in card's maximum inrush slew rate and magnitude according to the requirements of the system supplies.

#### **APPLICATIONS**

- Hot Swap of ONET Modules

- Supply Power-Up/Power-Down Sequencing

## description (continued)

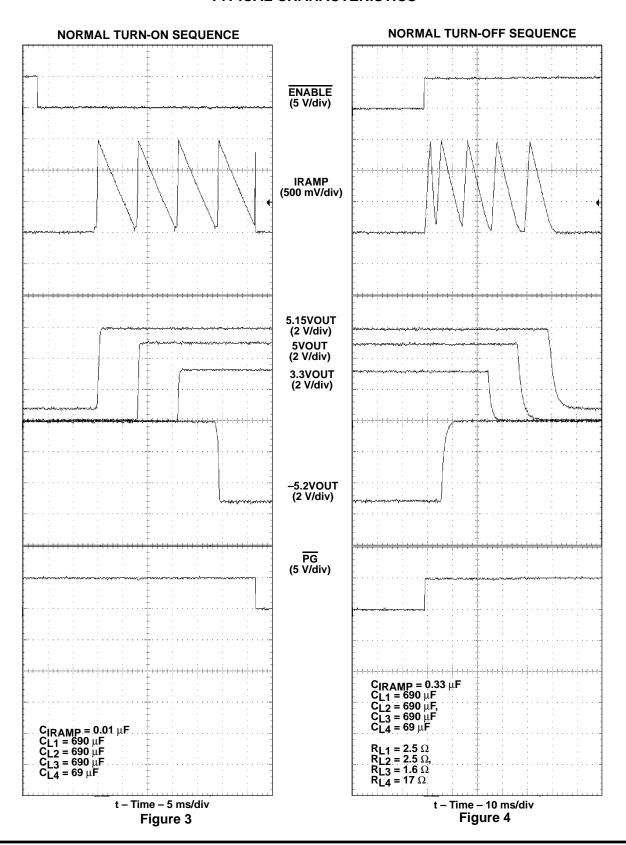

Fully programmed sequencing control ramps the back-end plane voltages in order, and during shutdown from a healthy state, turns off the back-end supplies in the reverse order. In addition, electronic circuit breakers provide continuous protection for the system supplies during the plug-in operation. The TTL/CMOS-compatible ENABLE input and the board power good signal (PG) can interface directly to the individual backplane slot control and status signals. A precharge pin (PRECHG) provides a 1-V bias supply for the I/O signals.

## absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Input voltage range,  | VIN1, VIN2, VIN3, ENABLE, PG, PRECHG                  |                                                        |

|-----------------------|-------------------------------------------------------|--------------------------------------------------------|

|                       | VS1, VS2, VS3, CS1, CS2, CS30.3 V to V <sub>I</sub> N | +0.3 V of corresponding channel                        |

|                       | CPUMP, GATE1, GATE2, GATE3                            | –0.3 V to 25 V                                         |

|                       | VIN4, VS4, GATE4, CS4                                 | –15 V to 0.3 V                                         |

|                       | IRAMP                                                 | $-0.3 \text{ V to V}_{\text{I(VIN1)}} + 0.3 \text{ V}$ |

| Operating junction to | emperature range, T <sub>J</sub>                      | –55°C to 150°C                                         |

| Storage temperature   | range, T <sub>stq</sub>                               | –65°C to 150°C                                         |

| Lead temperature so   | oldering 1,6 mm (1/16 inch) from case for 10 seconds  | 300°C                                                  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to GND. Currents are positive into, and negative out of the specified terminal.

#### **AVAILABLE OPTIONS**

| <b>TA</b> -40°C to 85°C | PACKAGED DEVICES |  |  |

|-------------------------|------------------|--|--|

| I A                     | TSSOP (PW)       |  |  |

| –40°C to 85°C           | TPS2346PW        |  |  |

†The PW package is available taped and reeled. Add TR suffix to device type (e.g. TPS2346PWTR) to order quantities of 2,000 devices per reel and 90 units per tube.

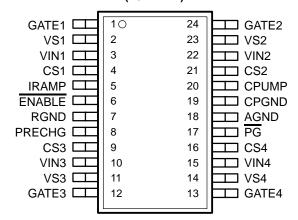

#### PW PACKAGE (TOP VIEW)

# electrical characteristics $V_{I(VIN1)}=5.15$ V, $V_{I(VIN2)}=5$ V, $V_{I(VIN3)}=3.3$ V, $V_{I(VIN4)}=-5.2$ V

## input supply

|                  | PARAMETER                | TEST CONDITIONS                                 | MIN | TYP  | MAX | UNIT |

|------------------|--------------------------|-------------------------------------------------|-----|------|-----|------|

| lCC1             | Supply current, VIN1     |                                                 |     | 6    | 8   |      |

| ICC2             | Supply current, VIN2     |                                                 |     | 1    | 2   |      |

| lCC3             | Input current, VIN3      |                                                 |     | 0.5  | 1   |      |

| I <sub>CC4</sub> | Input current, VIN4      |                                                 |     | -1.5 | -3  | mA   |

| ICC1(SLP)        | Sleep mode current, VIN1 | $V_{I}(\overline{\text{ENABLE}}) = 5 \text{ V}$ |     | 0.5  |     |      |

| ICC2(SLP)        | Sleep mode current, VIN2 | $V_{I}(\overline{\text{ENABLE}}) = 5 \text{ V}$ |     | 1    |     |      |

| ICC3(SLP)        | Sleep mode current, VIN3 | $V_{I}(\overline{\text{ENABLE}}) = 5 \text{ V}$ |     | 100  |     |      |

| ICC4(SLP)        | Sleep mode current, VIN4 | VI(ENABLE) = 5 V                                |     | -400 |     | μΑ   |

## charge pump

|                | PARAMETER                    | TEST CONDITIONS                                                                                         | MIN | TYP  | MAX | UNIT |

|----------------|------------------------------|---------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| VO(MAX)        | Maximum output voltage       | $IO(CPUMP) = -25 \mu A$                                                                                 | 17  |      | 23  | V    |

| ISOURCE        | Peak output current          | VO(CPUMP) = 15 V                                                                                        |     | -120 |     | μΑ   |

| z <sub>O</sub> | Charge pump source impedance | $\frac{1 \text{ V}}{\left(I_{O (CPUMP=17 \text{ V})}\right) - \left(I_{O (CPUMP=16 \text{ V})}\right)}$ |     | 200  |     | kΩ   |

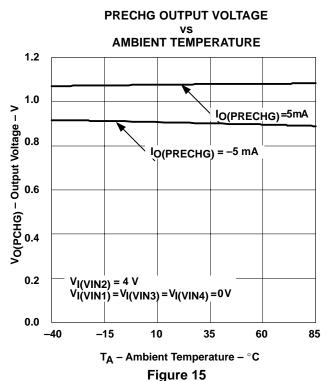

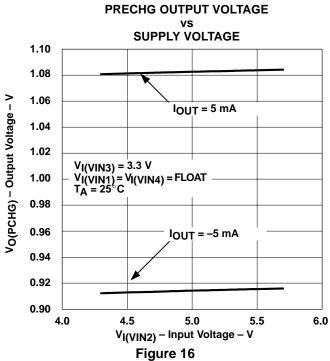

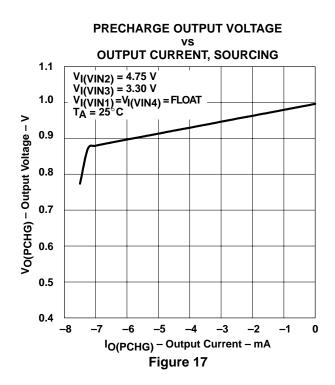

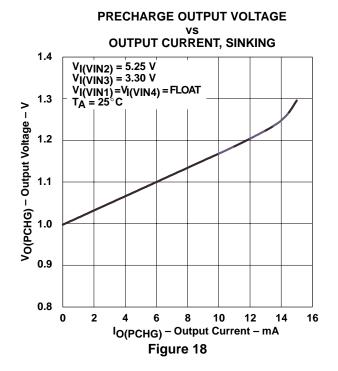

## precharge output

|                    | _                        |                                                          |                          |     |     |     |      |

|--------------------|--------------------------|----------------------------------------------------------|--------------------------|-----|-----|-----|------|

|                    | PARAMETER                | TEST CO                                                  | NDITIONS                 | MIN | TYP | MAX | UNIT |

| VO(PCHG)1          | Output voltage           | $V_{I(VIN2)} = 4 V$                                      | $V_{I(VIN1/3/4)} = 0 V$  | 0.9 | 1   | 1.1 |      |

| VO(PCHG)2          | Output voltage, sourcing | $V_{I(VIN2)} = 4 V$ ,<br>$I_{O(PRECHG)} = -5 \text{ mA}$ | $V_{I(VIN1/3/4)} = 0 V,$ | 0.8 | 1   | 1.2 | V    |

| VO(PCHG)3          | Output voltage, sinking  | $V_{I(VIN2)} = 4 V$ ,<br>$I_{O(PRECHG)} = 5 \text{ mA}$  | $V_{I(VIN1/3/4)} = 0 V,$ | 0.8 | 1   | 1.2 |      |

| <sup>t</sup> START | Startup time             | $V_{I(VIN2)} = 4 V,$                                     | $V_{I(VIN1/3/4)} = 0 V$  |     | 200 | ·   | μs   |

## linear current amplifiers 1, 2, 3

|                   | PARAMETER                       | TEST C                    | CONDITIONS                     | MIN               | TYP | MAX        | UNIT |

|-------------------|---------------------------------|---------------------------|--------------------------------|-------------------|-----|------------|------|

| V <sub>MAX1</sub> | IMAX sense voltage (VIN1 – CS1) |                           |                                | 16                | 20  | 24         |      |

| V <sub>MAX2</sub> | IMAX sense voltage (VIN2 – CS2) |                           |                                | 16                | 20  | 24         | mV   |

| V <sub>MAX3</sub> | IMAX sense voltage (VIN3 – CS3) |                           |                                | 16                | 20  | 24         |      |

| l <sub>PK</sub>   | Output peak current             |                           |                                | -25               |     | <b>–</b> 5 |      |

| ISINK             | Output current sink             |                           |                                | 0.2               |     | 10         | mA   |

| IFAULT            | Output current sink             | Fault shutdown            |                                |                   | 150 |            |      |

| VOL               | Low-level output voltage        | Fault shutdown,           | I <sub>O</sub> (GATEx) = 10 mA |                   |     | 0.5        | .,   |

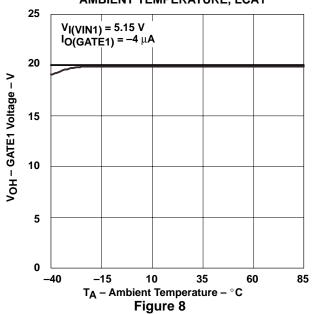

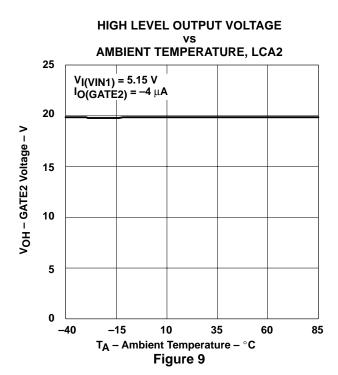

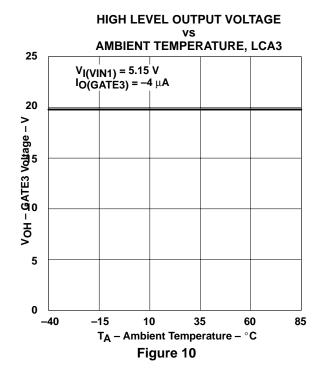

| VOH               | High-level output voltage       | $I_{O(GATEx)} = -4 \mu A$ | ·                              | V <sub>CPUM</sub> | p–1 |            | V    |

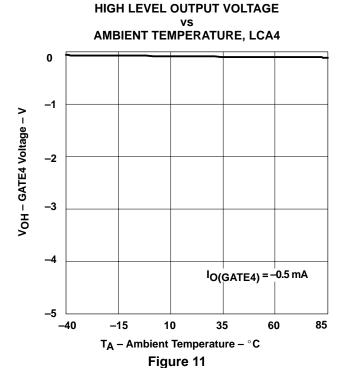

## linear current amplifier 4

|                  | PARAMETER                       | TEST CONDITIONS | MIN | TYP  | MAX  | UNIT |

|------------------|---------------------------------|-----------------|-----|------|------|------|

| VMAX4            | IMAX sense voltage (VIN4 - CS4) |                 | -75 | -150 | -225 | mV   |

| I <sub>OL1</sub> | Output leakage current          | Fault shutdown  | -10 |      | 10   | •    |

| I <sub>OL2</sub> | Output leakage current          | Sleep mode      | -10 |      | 10   | μΑ   |

electrical characteristics  $V_{I(VIN1)}=5.15$  V,  $V_{I(VIN2)}=5$  V,  $V_{I(VIN3)}=3.3$  V,  $V_{I(VIN4)}=-5.2$  V,  $V_{A}=-40$  C to 85 C (unless otherwise noted) (continued)

## overcurrent comparators 1, 2, 3

|                  | PARAMETER                                  | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------|--------------------------------------------|-----------------|-----|-----|-----|------|

| V <sub>OC1</sub> | Overcurrent threshold voltage (VIN1 – CS1) |                 | 34  | 45  | 56  |      |

| V <sub>OC2</sub> | Overcurrent threshold voltage (VIN2 – CS2) |                 | 29  | 40  | 51  | mV   |

| V <sub>OC3</sub> | Overcurrent threshold voltage (VIN3 – CS3) |                 | 29  | 40  | 51  |      |

| tR               | Response time                              |                 | 1   |     | 5   | μs   |

#### overcurrent comparator 4

|                  | PARAMETER                                                    | TEST CONDITIONS | MIN             | TYP | MAX  | UNIT |

|------------------|--------------------------------------------------------------|-----------------|-----------------|-----|------|------|

| V <sub>OC4</sub> | Overcurrent threshold voltage (VIN4 – CS4) relative to VMAX4 |                 | <del>-</del> 50 |     | -225 | mV   |

| tR               | Response time                                                |                 | 1               | •   | 5    | μs   |

## undervoltage (UV)

|                  | PARAMETER                    | TEST CONDITIONS | MIN   | TYP   | MAX   | UNIT |

|------------------|------------------------------|-----------------|-------|-------|-------|------|

| V <sub>UV1</sub> | Channel 1 undervoltage limit |                 | 4.35  | 4.53  | 4.71  |      |

| V <sub>UV2</sub> | Channel 2 undervoltage limit |                 | 4.22  | 4.40  | 4.58  | .,   |

| V <sub>UV3</sub> | Channel 3 undervoltage limit |                 | 2.78  | 2.90  | 3.02  | V    |

| V <sub>UV4</sub> | Channel 4 undervoltage limit |                 | -4.76 | -4.58 | -4.30 |      |

## overvoltage (OV)

|                               | PARAMETER                   | TEST CONDITIONS | MIN   | TYP   | MAX   | UNIT |

|-------------------------------|-----------------------------|-----------------|-------|-------|-------|------|

| V <sub>O</sub> V <sub>1</sub> | Channel 1 overvoltage limit |                 | 5.54  | 5.77  | 6.00  |      |

| V <sub>OV2</sub>              | Channel 2 overvoltage limit |                 | 5.38  | 5.60  | 5.82  | .,   |

| V <sub>OV3</sub>              | Channel 3 overvoltage limit |                 | 3.55  | 3.70  | 3.85  | V    |

| V <sub>OV4</sub>              | Channel 4 overvoltage limit |                 | -7.00 | -5.82 | -5.54 |      |

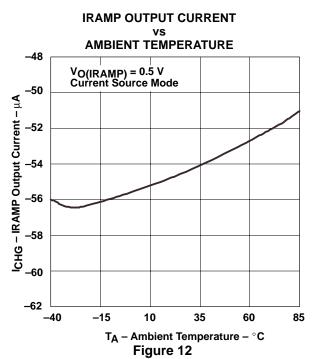

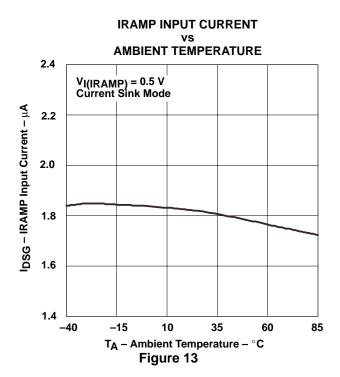

## **IRAMP** output

|                  | PARAMETER                 | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |

|------------------|---------------------------|------------------------|-----|-----|-----|------|

| ICHG             | Source current, charging  | VO(IRAMP) = 0.5 V      | -46 | -58 | -68 | •    |

| I <sub>DSG</sub> | Sink current, discharging | $V_{O(IRAMP)} = 0.5 V$ | 1.3 | 1.8 | 2.5 | μΑ   |

## undervoltage lockout (UVLO)

|                         | PARAMETER              | TEST CONDITIONS                                 | MIN  | TYP  | MAX  | UNIT |

|-------------------------|------------------------|-------------------------------------------------|------|------|------|------|

| V <sub>UVLO-L</sub> VIN | I1 UVLO, input rising  |                                                 | 2.1  | 2.4  | 2.9  | İ    |

| V <sub>UVLO-H</sub> VIN | I1 UVLO, input falling | $V_{I(VIN2)} = V_{I(VIN3)} = V_{I(VIN4)} = 0 V$ | 1.90 | 2.25 | 2.70 | V    |

| V <sub>HYS</sub> VIN    | 11 UVLO hysteresis     |                                                 |      | •    |      |      |

## **ENABLE** input

| PARAMETER |                                  | TEST CONDITIONS  |   | TYP | MAX | UNIT |

|-----------|----------------------------------|------------------|---|-----|-----|------|

| $V_{IL}$  | Low-level input voltage          |                  |   |     | 8.0 | .,   |

| VIH       | High-level input voltage         |                  | 2 |     |     | V    |

| lн        | High-level input leakage current | VI(ENABLE) = 5 V |   | 50  |     | μΑ   |

# electrical characteristics $V_{I(VIN1)} = 5.15$ V, $V_{I(VIN2)} = 5$ V, $V_{I(VIN3)} = 3.3$ V, $V_{I(VIN4)} = -5.2$ V, $V_{I($

## PG output

|     | PARAMETER                           | TEST CONDITIONS                   |                         |   | TYP | MAX | UNIT |

|-----|-------------------------------------|-----------------------------------|-------------------------|---|-----|-----|------|

| ІОН | High-level output (leakage) current | $V_{I}(\overline{ENABLE}) = 5 V,$ | V <sub>OH</sub> = 5 V   |   | 1   |     | μΑ   |

| VOL | Low-level output voltage            | $V_{I}(\overline{ENABLE}) = 0 V,$ | ISINK = 0.1 mA          |   | 0.5 |     | V    |

| loL | Low-level output (sink) current     | $V_{I(ENABLE)} = 0 V,$            | V <sub>OL</sub> = 0.5 V | 4 | 10  |     | mA   |

## **Terminal Functions**

| TERMINAL |     |     | DECODINE                                               |  |

|----------|-----|-----|--------------------------------------------------------|--|

| NAME     | NO. | I/O | DESCRIPTION                                            |  |

| AGND     | 18  | 1   | Analog ground                                          |  |

| ENABLE   | 6   | 1   | Logic low enable input for back-end power              |  |

| CPGND    | 19  | I   | Charge pump ground                                     |  |

| CPUMP    | 20  | I/O | Charge pump resevoir capacitor connection              |  |

| CS1      | 4   | I   | Channel 1 (5.15-V) current sense input                 |  |

| CS2      | 21  | ı   | Channel 2 (5-V) current sense input                    |  |

| CS3      | 9   | ı   | Channel 3 (3.3-V) current sense input                  |  |

| CS4      | 16  | ı   | Channel 4 (–5.2-V) current sense input                 |  |

| GATE1    | 1   | 0   | Gate drive for Channel 1 (5.15-V) external pass FET    |  |

| GATE2    | 24  | 0   | Gate drive for Channel 2 (5-V) external pass FET       |  |

| GATE3    | 12  | 0   | Gate drive for Channel 3 (3.3-V) external pass FET     |  |

| GATE4    | 13  | 0   | Gate drive for Channel 4 (–5.2-V) external pass FET    |  |

| PG       | 17  | 0   | Open drain output asserted low for back-end power good |  |

| IRAMP    | 5   | 0   | Current ramp programming pin                           |  |

| PRECHG   | 8   | 0   | Bias supply of 1V for bus signal precharge             |  |

| RGND     | 7   | I   | Reference ground                                       |  |

| VIN1     | 3   | I   | Channel 1 supply (5.15-V) input voltage sense          |  |

| VIN2     | 22  | I   | Channel 2 supply (5-V) input voltage sense             |  |

| VIN3     | 10  | ı   | Channel 3 supply (3.3-V) input voltage sense           |  |

| VIN4     | 15  | ı   | Channel 4 supply (–5.2-V) input voltage sense          |  |

| VS1      | 2   | ı   | 5.15-V supply back-end voltage sense                   |  |

| VS2      | 23  | 1   | 5-V supply back-end voltage sense                      |  |

| VS3      | 11  | I   | 3.3-V supply back-end voltage sense                    |  |

| VS4      | 14  | 1   | -5.2-V supply back-end voltage sense                   |  |

#### **DISSIPATION RATING TABLE**

| PACKAGE    | T <sub>A</sub> 25°C | DERATING FACTOR | T <sub>A =</sub> 85°C |

|------------|---------------------|-----------------|-----------------------|

| TSSOP (PW) | 800 mW              | 10 mW/°C        | 200 mW                |

### pin descriptions

**AGND**: Analog ground reference for the device.

**CPGND**: Charge pump ground pin for the device.

**CPUMP**: Charge pump resevoir capacitor connection. An external capacitor of value 0.1  $\mu$ F to 1  $\mu$ F must be connected between this pin and CPGND. The capacitor provides charge storage for the internal charge pump for gate drive of the external N-channel FETs in line with the three positive-voltage loads.

**CS1**, **CS2**, **CS3**: These pins tie to the load side of the Channel 1, 2, and 3 current sense resistors, respectively. They are used in conjunction with the VIN1, VIN2 and VIN3 inputs to provide load current magnitude information to each of the positive rail LCAs.

**CS4**: This pin ties to the more positive side of the Channel 4 current sense resistor (common with the pass FET source). It is used in conjunction with the VIN4 input to provide Channel 4 current magnitude information to the negative rail LCA.

**ENABLE**: Logic low enable input for back-end power. This pin ties to the module enable input at the plug-in slot. When the input supplies are above the device minimums, and this pin is asserted low the TPS2346 begins the sequential ramp—up of the back-end supplies. Pulling this input high (>2 V) turns off power to the back-end planes, and puts the TPS2346 into low-power sleep mode.

**GATE1, GATE2, GATE3, GATE4**: Gate drive outputs for the Channel 1 through Channel 4 pass FETs, respectively. The gates are driven according to the supply voltage, enable, sequence programming and load current conditions of the add-in board.

**IRAMP**: Current ramp programming pin. A capacitor connected between this pin and ground determines the maximum slew rate of the load current during ramp-up and ramp-down of the three positive back-end voltages. This same capacitor is also used to establish the time limit for ramping each of the supply outputs.

**PG**: Open-drain output asserted low to signal a back-end power-good condition. During a turn-on event, if each of the load rails ramps up successfully to within the factory-programmed tolerances of the undervoltage (UV) and overvoltage (OV) comparators, this output is subsequently asserted low. The output is false when back-end power is not enabled, if any of the back-end voltages is not within its UV/OV window, as a result of an overcurrent indication on any supply controller, or as a result of a fault timeout during linear ramp-up of any load voltage.

**PRECHG**: Bias supply of 1 V for bus signal precharge. During plug-in insertion and extraction events, this output provides a bias supply that can be used to precharge the signal and control lines of the system's address/data bus.

**RGND**: Reference ground input for the device.

**VIN1**: Channel 1 supply (5.15-V) input voltage sense. This pin is connected to the 5.15-V power supply input to the add-in card. The supply potential is tested against the undervoltage limits prior to ramping voltage to the back-end 5.15-V plane. The input supply also serves as the reference potential for the internally generated current limit (IMAX) reference of the Channel 1 LCA. This pin also serves as the VCC supply for the TPS2346.

**VIN2**: Channel 2 supply (5-V) input voltage sense. This pin is connected to the 5-V power supply input to the add-in card. The supply potential is tested against the undervoltage limits prior to ramping voltage to the back-end 5-V plane. The input supply also serves as the reference potential for the internally generated current limit (IMAX) reference of the Channel 2 LCA. This pin also serves as the supply input for the precharge bias output.

**VIN3**: Channel 3 supply (3.3-V) input voltage sense. This pin is connected to the 3.3-V power supply input to the add-in card. The supply potential is tested against the undervoltage limits prior to ramping voltage to the back-end 3.3-V plane. The input supply also serves as the reference potential for the internally generated current limit (IMAX) reference of the Channel 3 LCA.

#### pin descriptions (continued)

**VIN4**: Channel 4 supply (–5.2-V) input voltage sense. This pin is connected to the –5.2-V power supply input to the add-in card. The supply potential is tested against the undervoltage limits prior to ramping voltage to the back-end –5.2-V plane. The input supply also serves as the reference potential for the internally generated current limit (IMAX) reference of the Channel 4 LCA.

**VS1, VS2, VS3**: Voltage sense inputs for the positive back-end power busses. These pins connect to the source nodes (load side) of the external pass FETs. After the programmed voltage ramp period for each supply, these inputs are monitored to verify that the load voltages remain within the specified tolerances.

**VS4**: Voltage sense input for the negative back-end power bus. This pin connects to the drain (load side) of the Channel 4 external pass FET. After the programmed voltage ramp period for the negative supply, this input is monitored to verify that the load voltage remains within the specified tolerance.

#### functional overview

When an add-in printed circuit board (PCB) is inserted into a live chassis slot, the discharged supply bulk capacitance on the board can draw huge transient currents from the system supplies. Limited only by the ESR of the bulk capacitors and the impedance of the interconnect, these transients can reach sufficient magnitude to cause immediate damage to connector pins, PCB etch and plug-in and supply components, or cause latent defects reducing long-term reliability. In addition, current spikes can cause glitches on the power busses, causing other boards in the system to reset.

The TPS2346 is designed to actively limit inrush current slew rate and magnitude during insertion and extraction processes, in order to manage the safe, reliable hot swap of four supply voltages. N-channel MOSFETs in series with each supply provide isolation between the system supply planes (the backplane) and the back-end power planes during hot swap events. Back-end power refers to the switched side of a board's power bus. With the exception of the interface circuitry itself, all the board's load (logic, processors, modules, etc) derives power from the back-end planes. Consequently, the majority of the bulk capacitance is also on these planes. The in-line FETs on each supply function as switches for the back-end power, and transition to a low-impedance supply path once a board is fully seated and enabled, until such time as it is extracted. Low ohmic-value sense resistors between each input and pass MOSFET feed back current information to the device. The TPS2346 uses load current sensing along with the peripheral slot enable command, ENABLE, to determine the appropriate gate drive status for each of the four MOSFETs. In this manner, the device provides for the controlled application of power to and removal from the back-end planes.

The TPS2346 derives its VCC power from the 5.15–V supply; however, the absence of any one of the supplies, including the VCC supply, causes the device to maintain pull-downs on the four gate pins, keeping the pass MOSFETs off. A pull-up on the ENABLE pin, which should be provided on-board, also keeps the gate outputs off even after all supply voltages are present. Once the plug-in is powered, a system-generated logic low signal on the ENABLE input starts the turn-on of power to the back-end loads.

During a ramp-up sequence, the four supply inputs are validated against the pre-programmed undervoltage (UV) and overvoltage (OV) thresholds. As each positive voltage load is enabled, current to the load is ramped at a user-programmable rate, easily set by a capacitor on the current ramp control pin, IRAMP. The supplies are sequenced up in the following order: 5.15-V, 5-V, 3.3-V and –5.2-V. The ramp of supply current on each channel is limited to a maximum value, herein referred to as IMAX. The IMAX limit is individually selectable for each channel, by selecting the appropriate value of the sense resistor. If the IMAX current level is attained on any channel during an insertion, charging of that channel's input bulk capacitance completes at that current limit, as required.

SLUS529 - MAY 2002

## functional overview (continued)

As each back-end voltage is ramped, its level is validated to ensure it is within the established UV and OV tolerances at the expiration of a programmable time period, protecting against start-up into faulted loads. The same capacitor at the IRAMP pin which sets the current ramp rate is also used to establish this ramp-up time limit. If all four supplies successfully reach a known good state, the  $\overline{PG}$  output signal is pulled low to allow enumeration of the add-in card.

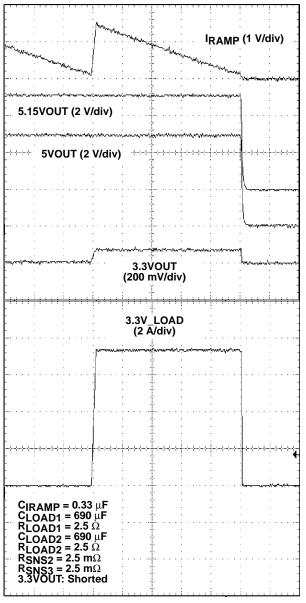

To protect the backplane power bus, the TPS2346 provides an electronic circuit breaker that trips upon detecting an overcurrent event. The detection threshold of an overcurrent event is internally set to approximately two times (2x) IMAX. The -5.2-V channel also includes a circuit breaker function; its trip threshold is always a minimum of 50 mV above the current-limit sense voltage. If any channel trips the circuit breaker, all supply outputs are rapidly turned off, and remain latched off. Also, the  $\overline{PG}$  output becomes high-impedance. The TPS2346 can be reset by cycling either the  $\overline{ENABLE}$  input or power to the device.

The low, 20-mV (150 mV on the -5.2-V channel) nominal sense voltage limit allows the use of low-value sense resistors, or for high-current applications, the use of PC board copper trace. This helps minimize the insertion loss across the hot swap interface. Further insertion loss reduction is achieved via the on-chip charge pump, which ensures maximum gate overdrive on each of the three external pass MOSFETs on the positive supply channels. This feature helps users obtain lower R<sub>DS(on)</sub> characteristics with their preferred N-channel MOSFETs.

Under a normal PC board shutdown event, the TPS2346 also turns off power in a controlled manner. To initiate a shutdown, ENABLE is brought to a logic high during a healthy supply state (outputs on and no faults present). The supply outputs are then sequentially ramped off in the reverse order of the ramp-up sequence. After all supply outputs are off, the TPS2346 goes into a low-current sleep mode.

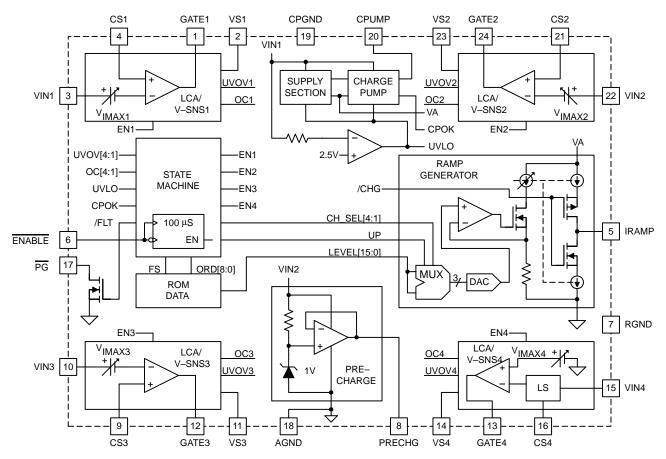

### detailed description

The primary circuit blocks of the TPS2346 include internal supply generation, a charge pump, a state machine, programmable ramp generator, precharge circuitry, and a ROM data cell. In addition, each of the four channels contains a gate control block which includes the linear control amplifier (LCA), programmable current source, and the voltage sense circuitry (see Figure 1). The gate drive blocks are virtually identical, except that the Channel 4 block, controlling the negative voltage channel, adds some scaling and level shift circuitry to adjust the polarity of the sense signals to that of the internal circuitry.

Figure 1. TPS2346 block diagram

The supply generation block contains voltage regulators and references to generate the various bias voltages used internally by the TPS2346. An undervoltage lockout (UVLO) function is used to ensure proper device turn-on once the VIN1 input has attained the UVLO threshold of about 2.5 V. In addition, an on-chip charge pump steps up the VIN1 input to generate the high voltage used by the LCAs to drive the pass MOSFET gates. Burst regulation of the charge pump limits the output to about 20.5 V (peak), with about a 1-V hysteresis. During steady-state load operation, sufficient gate overdrive is ensured to fully enhance the external MOSFETs, while not exceeding the typical 20-V VGS rating of common N-channel MOSFETs.

The state machine block contains the logic to control the ramp-up and ramp-down sequencing, ramp generator operation, and fault management. It uses voltage and current monitor outputs, along with the device enable status and programmed order information to determine which channel is to be acted on, whether ramp-up, ramp-down or steady-state operation is required, and the present healthy or faulted states of the back-end supplies. A nominal 100–µS digital filter is applied to the ENABLE input to help protect against false triggering in systems not implementing hardware connection control. The filter acts on both high-to-low and low-to-high transitions of the enable input.

## detailed description (continued)

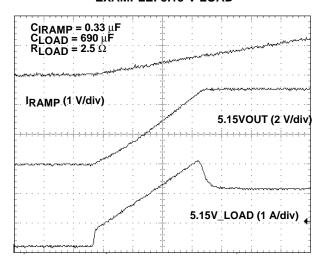

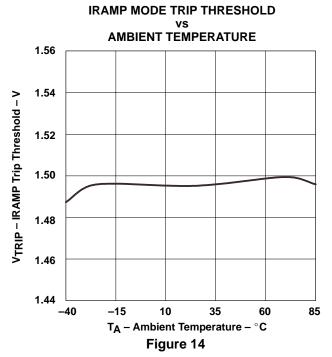

The ramp generator consists of a series of multiplexers feeding a digital-to-analog converter (DAC) circuit which sets the magnitude of an internal current source. When active, the current source is used to establish a constant value source or sink current at the IRAMP pin. This current is used to alternately charge and discharge a capacitor connected between IRAMP and ground, generating a series of sawtooth timing pulses. During turn-on of the back-end voltages, the capacitor is charged with a 58-µA current, then subsequently discharged with a 1.8-µA load. A comparator in the ramp generator circuit monitors the IRAMP voltage against two alternating thresholds, such that the voltage charges up to 1.5 V and back down to 0 V. During the rising edge of this waveform, the voltage at IRAMP is used to develop the reference threshold at the inverting input of the active channel's LCA. The other input is connected to the channel's current sense (CSx) input. The LCA slews the GATEx output to maintain the CSx pin at the reference value. Since the CSx voltage is developed as the drop across the external sense resistor due to load current, the current to the load is therefore ramped at a linear rate set by the dV/dt on the IRAMP pin. Therefore, inrush slew rate limiting is easily programmed by the user with the IRAMP capacitor, C<sub>IRAMP</sub>. For Channel 4, internal device offsets may cause the inrush profile to deviate from the programmed curve, particularly at initial turn-on. However, the maximum sourcing limit imposed by the VMAX4 threshold still applies.

During a load turn-on, the current sense voltage, if required in order to fully charge the back-end plane, can track the IRAMP waveform up to approximately 1.35 V on the IRAMP pin. If the charging current achieves that level, the LCA reference is switched automatically to the fixed IMAX reference. Load charging then continues at that fixed level until complete or until timer expiration, whichever occurs first. For Channels 1, 2 and 3, the IMAX level has been set to 20 mV at the CSx pin, referenced to VINx. For Channel 4, the IMAX level is 150 mV.

The precharge circuitry is powered from the VIN2 supply input. Therefore, when the 5-V supply and GND pins mate during an insertion, or until they break contact during an extraction, the precharge actively biases the bus signal lines to 1.0 V. The precharge block consists of a 1-V reference generator and a unity gain amplifier. The amplifier provides source and sink capability up to 5 mA.

The ROM data cell sets the configuration information for the TPS2346. These parameters include the order of channel sequencing, the magnitude of the charge and discharge currents at IRAMP, and the nominal voltage range of each channel. This information is all pre-programmed at the factory; no programming by the user is necessary.

UDG-02004

## detailed description (continued)

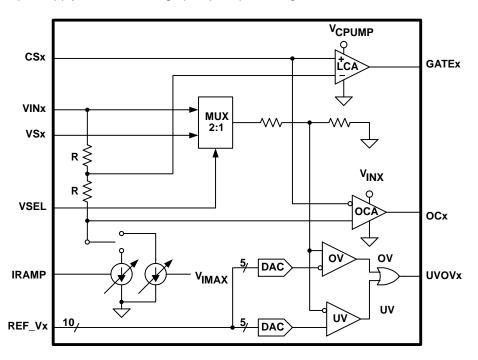

The basic functional blocks of the LCA/voltage sense circuits is shown in greater detail in Figure 2. The LCA has as its inputs the reference voltage generated by the current sources, and the current sense input. During a supply turn-on, it slews the pass MOSFET gate to force the load current to track the selected source. After load charging completes, and the current decays to the nominal operating level, the LCA drives the GATEx output to its input supply level, the charge pump output voltage.

Figure 2. Linear Control Amplifier Block

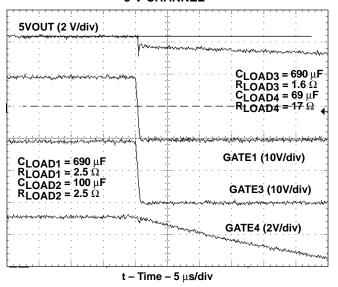

The supply voltage is monitored by the undervoltage (UV) and overvoltage (OV) comparators. A voltage multiplexer (MUX) selects from either the input supply voltage (VINx) or the load voltage (VSx), and provides that signal to the comparator inputs. Once the Channel 1 supply is above the UVLO threshold, and the ENABLE input has been pulled low, but prior to the ramp-up of the first channel, the comparators monitor the input supplies. Any supply outside its UV/OV window causes all pass MOSFETs to be held off. If all inputs are within tolerance, a ramp-up sequence can start, at which time the comparator inputs are switched over to the load, or VSx, voltages. Within the state machine, monitoring of the ORed status of the UV and OV comparators of any channel is enabled at the turn-on of the next channel, or approximately at the leading edge of the next IRAMP pulse.

Finally, a fast overcurrent comparator (OCA in the diagram) also monitors the CSx input. This comparator threshold is set to approximately 2 times the current limit threshold,  $(2 \times IMAX)$  for the three positive supplies. In the event of a short-circuit or other fast overcurrent event, the OCA trips, disabling the LCA, and causing additional gate discharge paths to be turned on for a rapid shutdown of the loads.

A 1- $\mu$ S to 2- $\mu$ S filter is applied to all overcurrent and voltage faults to guard against nuisance trips. If the duration of a fault condition on any one channel exceeds the filter length, the fault is latched, the open-drain device at the  $\overline{PG}$  output is turned off, and all four channels are shut down.

#### LOAD CURRENT LINEAR RAMP EXAMPLE: 5.15-V LOAD

t - Time - 1 ms/div Figure 5

#### START-UP INTO A SHORT ON 3.3 V LOAD

t - Time - 50 ms/div

Figure 6

#### UNDERVOLTAGE FAULT RESPONSE 5-V CHANNEL

Figure 7

## HIGH LEVEL OUTPUT VOLTAGE vs AMBIENT TEMPERATURE, LCA1

#### **APPLICATION INFORMATION**

The connections to set up the TPS2346 for operation in an ONET plug-in are shown in the typical application diagram. The TPS2346 works in conjunction with four external N-channel MOSFETs to provide isolation of the back-end power planes when disabled, and to provide a low-impedance power path when the load voltages are at the full-input dc potential. For proper operation, each channel of the device must be connected to the appropriate supply as listed in Table 1.

Table 1. TPS2346 Channel to Back-Plane Supply Connections

| TPS2346<br>CHANNEL | BACKPLANE<br>SUPPLY |

|--------------------|---------------------|

| 1                  | 5.15 V              |

| 2                  | 5 V                 |

| 3                  | 3.3 V               |

| 4                  | −5.2 V              |

The TPS2346 is shown in the typical application diagram being used in conjunction with a connector providing three levels of pin staging. Although not an absolute requirement for device operation, pin staging provides several benefits to the overall performance of the hot swap circuit. In order to use the precharge function provided by the TPS2346, a minimum of two levels of staging is needed. The precharge supply is derived from the 5-V supply input (VIN2); therefore, this supply must be present at some time before the board's bus lines make contact with the backplane address/data bus in order to allow precharge before mating. A second benefit of pin staging is it provides a mechanism for current-limited charging of the early power planes. Early power is any plane which is on the unswitched side of the hot swap interface. Parasitic capacitance associated with the interconnect system and the PCB planes, along with any bypass capacitance of the interface devices (e.g., the hot swap controller, bus switches, the bridge device) appears on the input side of the connection hardware. Therefore, it can still induce current spikes during hot swap even though the bulk capacitance is isolated. If longer power pins are provided by the connector, they can be used for charging this smaller input capacitance via simple resistive limiting. The resistors are subsequently bypassed when shorter power pins mate to establish the low impedance power connection.

Finally, if a third level of staging is implemented, one of the shortest pins should be assigned to the ENABLE input, as shown in the diagram. This helps ensure that all four supply voltages are stabilized at the controller inputs before the ENABLE can be asserted. It also allows this input to be grounded on the backplane in systems not implementing individual slot control of plug-in electrical connection status.

Sense resistors R1 through R4 connect between the VINx and CSx pins of their respective supplies, and provide load current magnitude information to the TPS2346. To turn on the negative voltage channel, the device pulls the gate of MOSFET Q4 towards ground potential. Resistor R5 provides a gate pull down when the LCA turns off, as the Channel 4 LCA does not drive to the negative rail.

Resistor R7 provides a pull-up on the  $\overline{\text{ENABLE}}$  pin. This should be provided on-board, so that it is present regardless of the connection status of this pin during hot swap events. Resistor R6 provides a pull-up on the open–drain  $\overline{\text{PG}}$  signal; a 10-k $\Omega$  resistor should suffice for this function. These two pull-ups are shown connected to the early 5.15-V supply; they could conceivably be connected to any of the positive early plane voltages. For most reliable operation, R7 should be connected to any of the earliest power pins, if pin timing is established via a staged-pin connector; otherwise, it should be tied to VIN1 as shown.

A capacitor with a value between 0.1  $\mu$ F and 1  $\mu$ F (C3 in the diagram) is required between the CPUMP pin and ground. This capacitor provides charge storage for the on-board charge pump. A 0.1- $\mu$ F ceramic is sufficient for most applications.

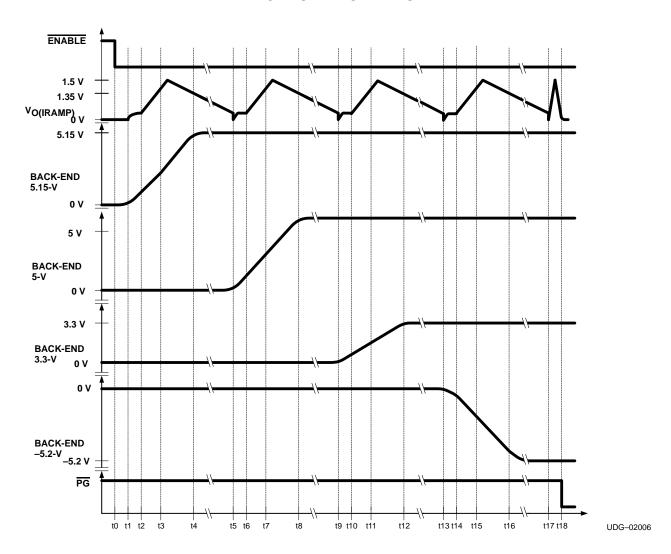

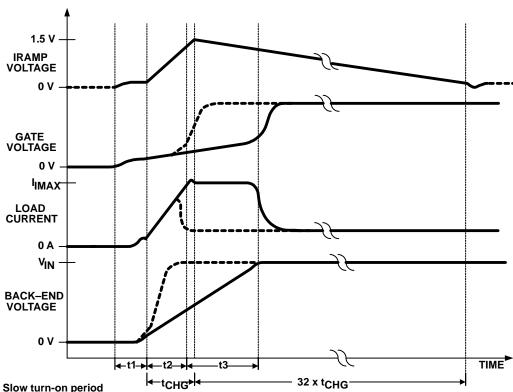

#### ramp-up sequence

A successful ramp-up of the four back-end supplies consists of five pulses on the TPS2346 IRAMP pin. One load voltage is ramped up during each of the first four IRAMP pulses. The fifth pulse enables the fault logic of the last channel to turn on (Channel 4). This is shown graphically in Figure 19.

- **ENABLE** input brought low to initiate a turn-on sequence.

- Channel 1 (5.15V) gate enabled; IRAMP capacitor starts charging with slow turn-on clamp. Slow charging of load voltage (back-end 5.15V) begins.

- t2: Slow turn-on period ends; linear ramp of current to the load begins.

- Constant di/dt period ends; load voltage ramping continues at IMAX rate. t3:

- Back-End 5.15 V reaches input DC potential. t4·

- Channel 2 (5V) gate is enabled. Slow charging of load voltage (back-end 5V) begins. Fault monitoring on Ch. 1 enabled. t5:

- Slow turn-on period ends; linear ramp of current to load begins.

- Constant di/dt period ends. Load voltage ramping continues at IMAX rate. t7:

- Back-End 5V reaches input DC potential. t8:

- Channel 3 (3.3V) gate is enabled. Slow charging of load voltage (back-end 3.3V) begins. Fault monitoring on Ch. 2 enabled.

- t10: Slow turn-on period ends; linear ramp of current to the load begins.

t11: Constant di/dt period ends. Load voltage ramping continues at IMAX rate.

- t12: Back-End 3.3V reaches input DC potential.

- t13: Channel 4 (-5.2V) gate is enabled. Slow charging of load voltage (back-end -5.2V) begins. Fault monitoring on Ch. 3 enabled.

- t14: Slow turn-on period ends; linear ramp of current to load begins.

- t15: Constant di/dt period ends; load voltage ramping continues at IMAX rate. t16: Back-end –5.2 V reaches input DC potential.

- t17: Channel 4 UV/OV fault enable pulse.

- t18: PG output pulled low.

Figure 19. TPS2346 Ramp-Up Sequence

A turn-on sequence is initiated when the  $\overline{\text{ENABLE}}$  input is brought low (less than 0.8 V), assuming that all four input supplies (at the VINx pins) are within their UV/OV tolerance windows. A voltage fault at any input supply causes all loads to be held off. When  $\overline{\text{ENABLE}}$  is asserted, the Channel 1 amplifier is enabled, and a 58- $\mu$ A current source begins charging the IRAMP capacitor to generate the first IRAMP pulse. During the linear rising edge portion of the IRAMP waveform, current is linearly ramped to the 5.15-V back-end plane. Once the voltage at IRAMP reaches 1.5 V, the source is replaced with a 1.8- $\mu$ A sink that discharges IRAMP to 0 V. During this discharge period, load charging current, if still required, is limited to IMAX, the current sense voltage (VMAX) divided by the sense resistor value,  $R_{SNSx}$ , or IMAXx = VMAXx /  $R_{SNSx}$ , where "x" refers to any of the four channels.

At the completion of the first pulse on IRAMP, the TPS2346 moves to the second voltage to be ramped up, Channel 2, enables its LCA and begins generating the second pulse in the IRAMP train. At this time, fault monitoring is enabled on the Channel 1 output. Therefore, if Channel 1 has failed to attain at least the undervoltage threshold potential, a fault is detected, any active channels turned off, and the turn-on sequence aborted. In this manner, the maximum time allowed for ramp-up of any of the channels is the duration of one (1) IRAMP pulse. This protects against indefinite sourcing into faulted loads. The TPS2346 latches off in response to faults, and can be reset either by toggling the ENABLE input high and then low again, or by cycling power to the device.

After the Channel 2 ramp pulse, the back–end planes for Channel 3 and Channel 4 are ramped up in similar fashion. Channel 2 fault detection is enabled at the start of the Channel 3 ramp pulse, and so on. Once all four supplies are ramped up, Channel 4 fault detection is enabled on the fifth IRAMP pulse. This last pulse is of relatively short duration, as charge and discharge currents of approximately 256  $\mu$ A are selected for the UV/OV4 enable pulse. If all four channels reach a known good state, the  $\overline{PG}$  output is asserted low.

Each load current waveform, at load turn-on, may have up to three distinct periods, as shown in Figure 20. Initially after being enabled, the ramp generator output voltage is clamped to less than 100 mV. This results in a corresponding clamp on load current of about 7% of the programmed IMAX value (with some variance due to internal device offset). This temporary limit applies during approximately the first 500 µs of output ramping time. The purpose of this slow ramp period is to ensure the LCA is pulled out of saturation, and is closely tracking the CS input, prior to enabling fast charging of the load. During this time, appreciable ramping of the back-end voltage may or may not occur, depending on a number of factors including the IMAX value, the amount of bulk capacitance on the load, and the magnitude and polarity of inherent offsets in the current control loop.

t1: Slow turn-on period

t2: Linear current ramp (di/dt)

t3: Constant-current load charging

$t_{CHG}$ : IRAMP capacitor charge time, (1.4  $\times$  C<sub>IRAMP</sub>/58)

UDG-02005

Figure 20. Load Current at Startup

Once the slow ramp period has expired, the clamp is removed, and the IRAMP voltage continues to ramp up at a constant rate of:

$$\frac{I_O}{C_{IRAMP}} = \frac{58 \, \mu A}{C_{IRAMP}}$$

Since the linear amplifier acts to maintain equal voltages at its inputs (see Figure 2), it slews the GATEx output such that the CSx voltage tracks the internally generated reference at its inverting input. Therefore, the linear voltage ramp at the IRAMP pin results in a linear current ramp to the three positive loads.

The LCA reference ramp tracks the IRAMP pin voltage up to a level of  $V_{O(IRAMP)} \cong 1.35$  V. This corresponds to the maximum sense voltage (VINx – CSx) of 20 mV (150 mV for Channel 4). If charging of the load input bulk capacitance completes during the constant di/dt section of channel turn-on (the set of dashed lines in Figure 20), the load current decays to the steady-state operating level. With decreasing load current, the CSx input is pulled to the VINx potential, and the pass MOSFET gate is driven to the LCA supply rail, fully enhancing the external MOSFET. However, under certain combinations of bulk capacitance, IMAX, and inrush di/dt relative values, the current ramp may reach the IMAX limit. The variable current source is switched out for the constant current source which sets the VMAX reference level (see Figure 2). This defines the third stage of the load current waveform. Load voltage ramping completes at the IMAX level, as shown by the set of solid lines in Figure 20. Again, once the current demand rolls off, the LCA drives the pass MOSFET gate high to fully enhance the MOSFET.

#### ramp-down sequence

A normal shutdown sequence occurs when the ENABLE input is brought high (greater than 2 V) with the output supplies in a healthy state (no overvoltage, undervoltage or overcurrent faults). PG is deasserted and the back-end voltages are sequenced off in the reverse order of turn on: -5.2-V, 3.3-V, 5-V and 5.15-V (Channel 4, Channel 3, Channel 2 and then Channel 1). The turn off is also controlled by five pulses at the IRAMP pin. The first pulse, which is of short duration, disables the voltage fault monitoring on Channel 4 (-5.2 V). Starting with the second pulse, each supply is turned off in order. At the start of each pulse at IRAMP, voltage fault monitoring is disabled for the next successive channel to be turned off. The IRAMP capacitor is charged rapidly, up to the 1.5-V threshold, at which point the variable current source in the LCA block is reselected to generate the current limit reference. At the same time, the charging source at IRAMP is replaced with a 58-uA discharge load, such that the IRAMP capacitor is discharged at the same rate used for di/dt control during turn on. This causes the current limit to decrease linearly, so that available load current is forced off no faster than the falling edge at IRAMP. The LCA is disabled, and additional pull-downs applied to the GATEx pin, when either the output voltage has decayed to less than 0.9 V, or the IRAMP waveform has decayed to approximately 0.1 V. Under conditions of light loading during turn off, the bulk capacitance may hold up the back-end voltage even after the MOSFET switch is turned off. In this situation, the TPS2346 waits for load discharge to less than 0.9 V prior to proceeding to the next channel. Channel 4 is the exception to this operation; the VS4 status is not monitored during turn off, and the device sequences to Channel 3 turn-off once the second IRAMP pulse ends.

#### setting the sense resistor values

Due to the current limiting operation of the internal LCAs, the maximum allowable load current for the application is easily programmed by selecting the appropriate value sense resistors. The LCA acts to limit the CSx voltage (relative to VINx) to the internal reference, which during steady-state operation is VMAX. Therefore, a sense resistor for each channel can be calculated from equation (1).

$$R_{SNSx} = \frac{VMAXx}{IMAXx} \tag{1}$$

where

R<sub>SNSx</sub> is the the sense resistor value for Channel x,

VMAXx is the IMAX sense voltage limit, and

IMAXx is the Channel x maximum load current.

When setting the current limits, it is important to consider the device minimum that may be imposed by the TPS2346. Using the values given in the electrical tables, equations (2) and (3) follow from equation (1).

For Channels 1, 2 and 3:

$$R_{SNSx} = \frac{16 \text{ mV}}{IMAXx} \tag{2}$$

where:

x = 1, 2 or 3.

For Channel 4:

$$R_{SNS4} = \frac{75 \text{ mV}}{IMAX4} \tag{3}$$

To ensure proper operation across the range of anticipated load currents on each channel, the maximum load under normal operating conditions must also be considered. To avoid current-limit operation during steady-state loading, the IMAX level must be set above the expected load. For example, if the 5-V (Channel 2) and 3.3-V (Channel 3) supplies of the typical application diagram each need to deliver up to 7.5 A, and a 500-mA margin is desired, using equation (2) yields:

$$R2 = R3 = \frac{16 \text{ mV}}{8 \text{ A}} = 2 \text{ m}\Omega$$

Similarly, for up to 5-A capability on Channel 1, equation (2) indicates R1  $\cong$  3 m $\Omega$ . Setting R4 = 200 m $\Omega$ , provides some margin over a 250 mA load.

#### setting the inrush slew rate

The TPS2346 is easily programmed for the desired maximum current slew rate during turn-on and turn-off events. A single capacitor at the IRAMP pin (C2 in the diagram) controls the di/dt for all three positive channels. Once the sense resistor values have been established, the value for C<sub>IRAMP</sub>, in microfarads, can be determined from equation (4).

For Channels 1, 2, and 3:

$$C_{IRAMPx} = \frac{68}{67.5 \times R_{SNSx} \times \left(\frac{di}{dt}\right)_{x}}$$

(4)

where:

C<sub>IRAMPx</sub> = the capacitor value indicated to achieve the (di/dt)x limit value,

R<sub>SNSx</sub> = sense resistor in ohms and

$(di/dt)_X$  = the maximum di/dt rate, in amps/second.

To complete the design of the power interface for the plug–in shown in the typical application diagram, assume that a maximum slew rate of 1.5 A/ms is specified for each of the three positive-voltage loads. A value for capacitor C2 must still be determined. Inspection of equation (4) indicates that, given the same di/dt requirement on all supplies, the supply channel(s) with the lowest-value sense resistor dictates the minimum value for the IRAMP capacitor. Therefore, the 5-V and 3.3-V supplies are suggested in this case for obtaining an initial estimate for C<sub>IRAMP</sub>. Using the associated values, equation (4) produces the result shown in equation (5).

$$C_{IRAMP2,3} = \frac{68}{67.5 \times (0.002 \,\Omega) \times (1500 \,A/s)} \cong 0.336 \,\mu F$$

(5)

A value of  $0.33~\mu F$  can be used, or the next available standard value of  $0.39~\mu F$  provides some margin for capacitor and sense-resistor tolerances. In either case, equation (4) can be rewritten as equation (6), which is used here to verify that the 5.15-V slew rate is still within specification.

$$\left(\frac{\text{di}}{\text{dt}}\right)_{x} = \frac{68}{67.5 \times R_{SNSx} \times C_{IRAMPx}}$$

(6)

where:

R<sub>SNSx</sub> is in ohms,

CIRAMPx is the value suggested by equation (5) in microfarads, and

(di/dt)x is given in amps/second.

For a  $C_{IRAMP}$  of 0.39  $\mu$ F, the maximum di/dt for the 5.15-V supply is approximately 860 mA/ms which is well within the example requirement.

#### protection against faulted loads

The TPS2346 allows the time period of one IRAMP pulse for each back-end plane's voltage to ramp-up to its minimum level. After this delay period, the device latches off if an undervoltage fault is subsequently detected. This nominal delay time, t<sub>TIMER</sub>, is set by the constant-current charging and subsequent discharging of C<sub>IRAMP</sub>, and is therefore determined from equation (7).

$$t_{\text{TIMER}} = C_{\text{IRAMP}} \times 1.4 \times \left(\frac{1}{58} + \frac{1}{1.8}\right) \tag{7}$$

where:

CIRAMP is in microfarads.

The resultant fault timer period should be sufficient for most applications; however, it is good design practice to verify that the delay is long enough for each load.

Due to the potential three-phase nature of the load current ramp (refer to Figure 20), the increasing load voltage may also have three distinct periods. The first phase is during the slow turn-on period at the start of each IRAMP cycle. Depending on a number of factors, significant voltage ramping may or may not occur during this time. For verification of the fault timeout delay, the worst case situation is no appreciable load charging (i.e., a longer overall charge time); therefore it is assumed that no voltage ramp occurs here.

The next phase is the linear load current ramp period. For any device channel x, if the IMAX level is not reached while charging a given load capacitor of  $C_{Lx}$ , then the time to reach the input dc level,  $V_{INx}$ , is estimated by equation (8).

$$t_{SSx} = \sqrt{\frac{2 \times C_{Lx} \times C_{IRAMP} \times K_{X} \times R_{SNSx} \times V_{INx}}{58 \,\mu\text{A}}}$$

(8)

where:

$K_X = 67.5$  for Channels 1, 2, and 3, and

$K_X = 7.5$  for Channel 4.

For example, assuming the 5-V back-end plane in this application has  $220 - \mu F$  bulk capacitance, the anticipated typical ramp-up time is about 1.41 ms.

During inrush slewing, the load current ramp tracks the voltage ramp on the IRAMP capacitor, up to a voltage of about 1.35 V on the IRAMP pin. Therefore, the time duration of this ramp activity, t<sub>IRAMP</sub>, is given by equation (9).

$$t_{IRAMP} = \frac{C_{IRAMP} \times (1.25 \text{ V})}{58} \tag{9}$$

where:

C<sub>IRAMP</sub> is in microfarads.

If, for any channel, the time for soft-start charging of the load voltage is greater than the current ramp period,  $(t_{SSx} > t_{IRAMP})$ , back-end plane ramp-up completes at the dc IMAX level. In this case, the following procedure can be used to estimate load ramp-up time.

First, equation (10) is used to determine the load voltage level, v<sub>I x</sub>(t), attained during the current ramp period.

$$v_{Lx}(t_{IRAMP}) = \frac{58 \,\mu\text{A}}{2 \times C_{Lx} \times C_{IRAMP} \times K_X \times R_{SNSx}} \times (t_{IRAMP})^2 \tag{10}$$

Once this voltage level is known, it can be used to estimate the additional charging time required at constant current to reach the input dc potential,  $t_{CCx}$ . This time is calculated from equation (11).

$$t_{CCx} = \frac{C_{Lx} \times \left(V_{INx} - V_{Lx} \left(t_{IRAMP}\right)\right)}{IMAXx}$$

(11)

The sum of  $t_{IRAMP}$  and  $t_{CCx}$  can then be used to estimate the total load ramp-up time for Channel x.

## precharge circuit

The precharge pin generates a 1-V bias voltage intended to be used for precharging the bus signals during hot swap. The pin's output stage has both source and sink capability, enabling it to pull lines up from 0 V or down from the I/O supply potential as needed. In typical implementations, each I/O line requiring precharge is isolated from the PRECHG source with a biasing resistor,  $R_P$  in the typical application diagram. Common values for  $R_P$  range from 10 k $\Omega$  to 50 k $\Omega$ . However, a number of factors influence precharge resistor value, including the number of lines requiring precharge, the parasitic capacitance associated with each line (both stub and I/O device), the precharge rate needed, and the system requirements for high- and low-level input current ( $I_{IH}$ ,  $I_{IL}$ ) on each I/O line. Several manufacturers offer integrated bus switches useful for precharge disconnect wherever input current is an issue.

A stub resistor (R8) is also shown, which is inserted in each I/O line to provide some series damping. Typical stub resistor value is 10  $\Omega$ , and it should be placed close to the connector.

### protecting ICs from voltage transients

Parasitic inductance associated with the power distribution network can cause large voltage spikes on the supply rails if the current is suddenly interrupted by the TPS2346 during a fault condition. Since the absolute maximum voltage rating of the device is 15 V, there should be sufficient margin from the supply nominal values to prevent damage. However, it may be necessary in certain applications to protect either the TPS2346 or other low-voltage devices connected directly to the plug-in's input rails. There are several techniques that may be used to improve the transient performance of the plug-in and host system.

- As a general rule, always use dedicated PCB planes for the power supply and ground nodes, and maximize

the trace width of high-current runs. This minimizes the parasitic inductance of the power distribution

network. This is recommended on both the backplane and plug-in modules.

- Add small-value capacitors to the supply pins of devices needing protection from transients, connected to ground. To reduce inrush, these capacitors should be 0.1 μF or less. For this function, higher ESR capacitors are actually preferable to low-ESR capacitors, as they provide some RC damping against high-frequency ringing of the supply voltage. As these capacitors generally reside on the input (non-isolated) side of a plug-in module, ESR also limits inrush current generated by the added capacitance.

- In some cases, it may be necessary to add a resistor in series with the input capacitor to improve the damping response of the circuit. Generally, this is a low-value resistor of about 10  $\Omega$  or less.

- Clamp the voltage at sensitive IC supply pins with a Zener diode. The maximum breakdown of these protection devices must be less than the absolute maximum rating of the device being protected. If possible, select a clamp which is inactive during normal steady-state operation of the module to minimize or eliminate power dissipation in the protection circuitry. For example, if the VIN1 or VIN2 pins of the TPS2346 require protection, a 6.8 V, 6% Zener (e.g., BZX84C series) clamps spikes well below the 15-V threshold, but is off when the supplies are at nominal levels. In addition, even with worst-case tolerances and accounting for some temperature coefficient, this device should not inhibit the OV detection function of the TPS2346 on these rails.

- Place any protection devices, capacitors or diodes, close to the device being protected, with short trace lengths back to the V<sub>CC</sub>/V<sub>DD</sub> and GND pins.

## layout considerations

To optimize the performance of the TPS2346, care should be taken to use good layout practice with the parts placement and etch routing of the hot swap circuit components. This includes any protection devices as well as the sense and pass elements. Protection devices should be located close to the hot swap controller, and trace-lengths back to their respective pins kept to a minimum. If a decoupling capacitor is used on the VIN1 supply, it also should be placed close to the part.

Mount the charge pump reservoir capacitor (C6 in the application diagram) close to the TPS2346, with minimal trace lengths back to the CPUMP and CPGND pins.

For proper operation, the three ground pins of the TPS2346 must be connected together near the device. The ground leads of the ramp and charge pump capacitors, protection diodes, and any decoupling capacitors should also tie into this node close to the part. This junction should be routed separately back to the J1 connector, where it can tie into the PCB GND node, as opposed to tying into the ground plane elsewhere in the high-current return path.

Use wide traces when connecting the sense resistors and power FETs into their respective current paths. When feeding these connections through from an internal power plane, use multiple vias to reduce the overall impedance of the current path. This helps reduce insertion loss across the hot swap interface, and improve the thermal performance of the PCB. Additional copper plane used on the land patterns of these devices can significantly reduce their thermal impedance, reducing temperature rise in the module and improving overall reliability of the power devices.

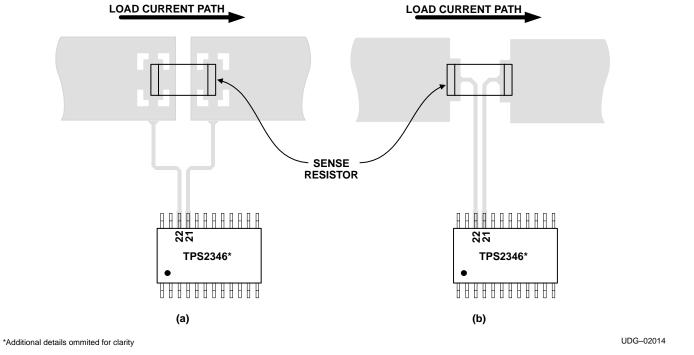

Connections to the sense resistors for the VINx and CSx device pins should be made with good Kelvin connections to optimize the accuracy of the current-limit thresholds and slew-rate control. This is especially important on high-current supplies. When typical load levels on these supplies are high, board trace resistance between elements in the supply current paths becomes significant. The two sense traces for each supply should connect symmetrically to the sense resistor land pattern, in close proximity to the element leads, and not upstream or downstream from the device. Trace routing back to the TPS2346 should be fairly well balanced. Figure 22 illustrates two recommendations for the current sense layout.

Figure 21. Recommended Layout for SMD Chip-Sense Resistor for 5-V Rail

#### PACKAGE OPTION ADDENDUM

3-Nov-2008

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|------------------------------|

| TPS2346PW        | NRND                  | TSSOP           | PW                 | 24                  | TBD                     | Call TI          | Call TI                      |

| TPS2346PWG4      | NRND                  | TSSOP           | PW                 | 24                  | TBD                     | Call TI          | Call TI                      |

| TPS2346PWR       | NRND                  | TSSOP           | PW                 | 24                  | TBD                     | Call TI          | Call TI                      |

| TPS2346PWRG4     | NRND                  | TSSOP           | PW                 | 24                  | TBD                     | Call TI          | Call TI                      |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL. Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated