- State-of-the-Art EPIC-II<sup>B</sup>™ BICMOS Design Significantly Reduces Power Dissipation

- ESD Protection Exceeds 2000 V Per MIL-STD-883C, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R = 0)

- Latch-Up Performance Exceeds 500 mA Per JEDEC Standard JESD-17

- Typical  $V_{OLP}$  (Output Ground Bounce) < 1 V at  $V_{CC} = 5$  V,  $T_A = 25^\circ\text{C}$

- High-Drive Outputs (-32-mA  $I_{OH}$ , 64-mA  $I_{OL}$ )

- Parity Error Flag With Parity Generator/Checker

- Latch for Storage of the Parity Error Flag

- Package Options Include Plastic Small-Outline (DW) and Shrink Small-Outline (DB) Packages, Ceramic Chip Carriers (FK), and Plastic (NT) and Ceramic (JT) DIPs

#### description

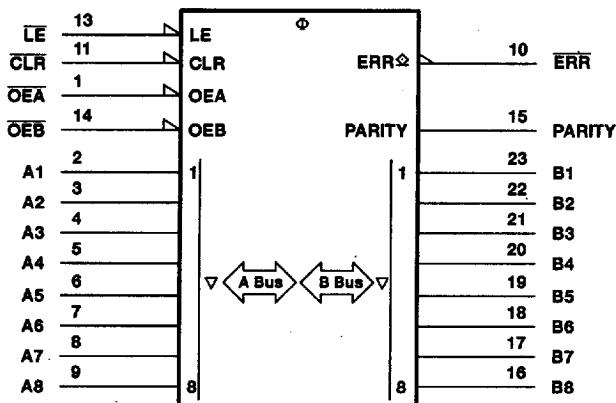

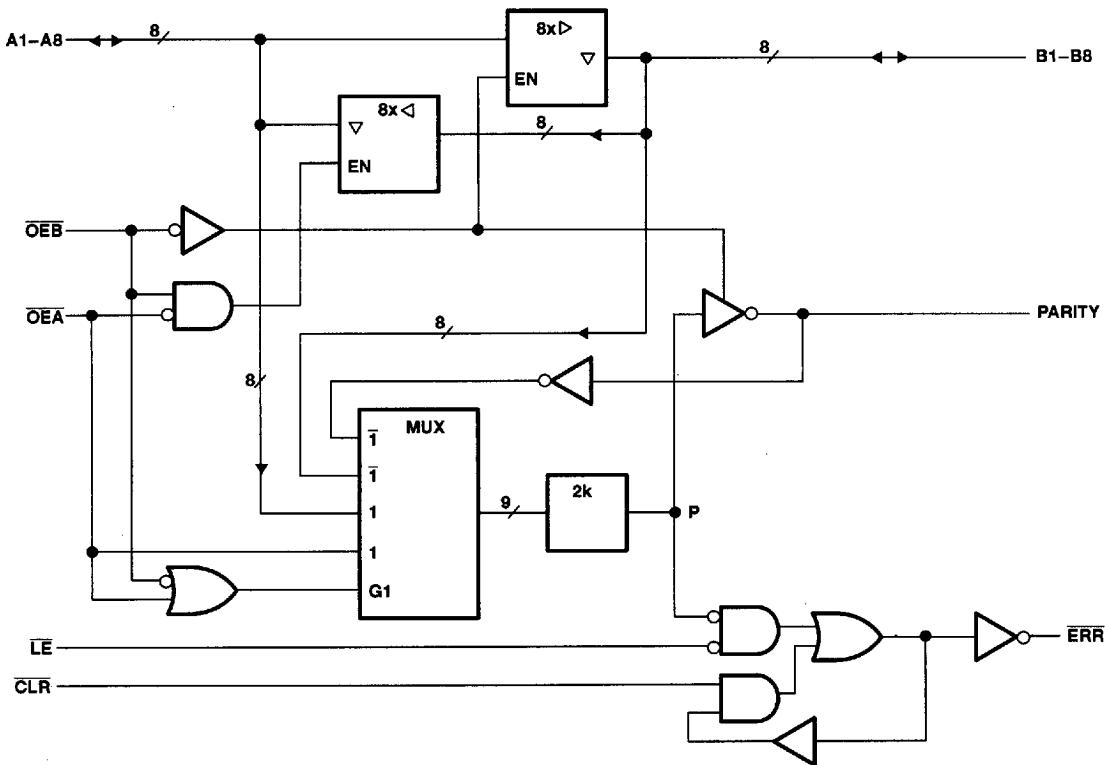

The 'ABT853 8-bit to 9-bit parity transceivers are designed for communication between data buses. When data is transmitted from the A bus to the B bus, a parity bit is generated. When data is transmitted from the B bus to the A bus with its corresponding parity bit, the open-collector parity-error (ERR) output indicates whether or not an error in the B data has occurred. The output-enable ( $\overline{OEA}$  and  $\overline{OEB}$ ) inputs can be used to disable the device so that the buses are effectively isolated. The 'ABT853 transceivers provide true data at their outputs.

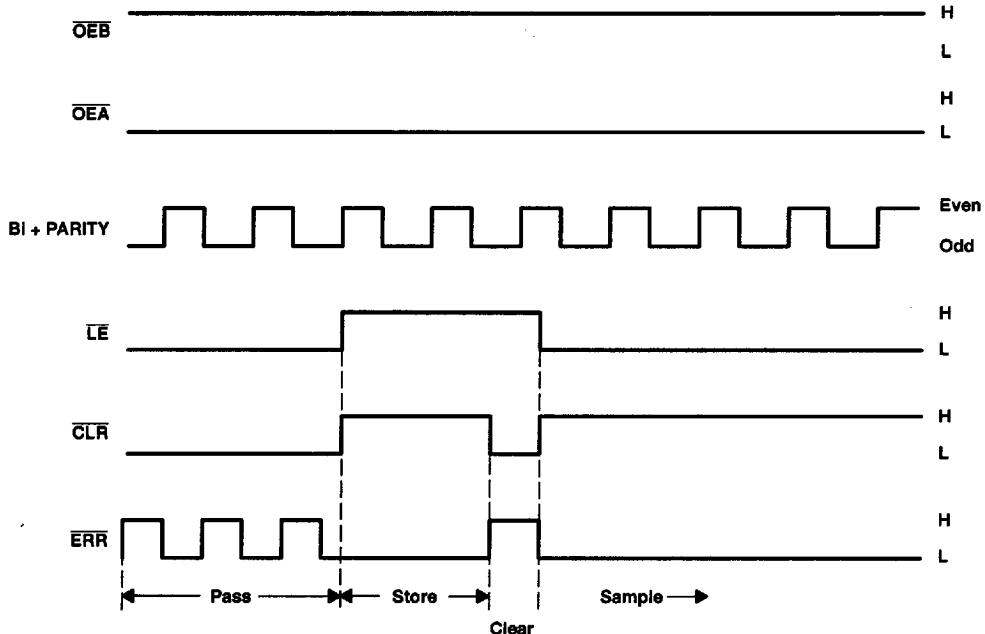

A 9-bit parity generator/checker generates a parity-odd (PARITY) output and monitors the parity of the I/O ports with the ERR flag. The parity-error output can be passed, sampled, stored, or cleared from the latch using the latch-enable (LE) and clear (CLR) control inputs. When both  $\overline{OEA}$  and  $\overline{OEB}$  are low, data is transferred from the A bus to the B bus and inverted parity is generated. Inverted parity is a forced error condition that gives the designer more system diagnostic capability.

To ensure the high-impedance state during power up or power down,  $\overline{OE}$  should be tied to  $V_{CC}$  through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN74ABT853 is available in TI's shrink small-outline package (DB), which provides the same I/O pin count and functionality of standard small-outline packages in less than half the printed-circuit-board area.

The SN54ABT853 is characterized for operation over the full military temperature range of  $-55^\circ\text{C}$  to  $125^\circ\text{C}$ . The SN74ABT853 is characterized for operation from  $-40^\circ\text{C}$  to  $85^\circ\text{C}$ .

EPIC-II<sup>B</sup> is a trademark of Texas Instruments Incorporated.

PRODUCT PREVIEW Information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

Copyright © 1994, Texas Instruments Incorporated

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

2-215

8961723 0095392 256

## **SN54ABT853, SN74ABT853 8-BIT TO 9-BIT PARITY BUS TRANSCEIVERS**

SCBS198A – FEBRUARY 1991 – REVISED JULY 1994

## FUNCTION TABLE

| INPUTS          |                 |     |    |              | OUTPUTS AND I/Os |    |    |        | FUNCTION |                                              |

|-----------------|-----------------|-----|----|--------------|------------------|----|----|--------|----------|----------------------------------------------|

| OE <sub>B</sub> | OE <sub>A</sub> | CLR | LE | AI<br>Σ OF H | BIT<br>Σ OF H    | A  | B  | PARITY | ERR#     |                                              |

| L               | H               | X   | X  | Odd<br>Even  | NA               | NA | A  | L<br>H | NA       | A data to B bus and generate parity          |

| H               | L               | X   | L  | NA           | Odd<br>Even      | B  | NA | NA     | H<br>L   | B data to A bus and check parity             |

| H               | L               | H   | H  | NA           | X                | X  | NA | NA     | NC       | Store error flag                             |

| X               | X               | L   | H  | X            | X                | X  | NA | NA     | H        | Clear error flag register                    |

| H               | H               | H   | H  | X            |                  |    |    |        | NC       | Isolation\$<br>(parity check)                |

|                 |                 | L   | H  | X            |                  |    |    |        | H        |                                              |

|                 |                 | X   | L  | L Odd        | X                | Z  | Z  | Z      | H        |                                              |

|                 |                 | X   | L  | H Even       |                  |    |    |        | L        |                                              |

| L               | L               | X   | X  | Odd<br>Even  | NA               | NA | A  | H<br>L | NA       | A data to B bus and generate inverted parity |

NA = not applicable, NC = no change, X = don't care

<sup>†</sup> Summation of high-level inputs includes PARITY along with Bi inputs.

† Output states shown assume the EBB output was previously high.

§ In this mode, the ERR output (when clocked) shows inverted parity of the A bus.

## PRODUCT REVIEW

### logic symbol

¶ This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the DB, DW, JT, and NT packages.

POST OFFICE BOX 855303 • DALLAS, TEXAS 75285

logic diagram (positive logic)

PRODUCT PREVIEW

ERROR-FLAG FUNCTION TABLE

| INPUTS | INTERNAL<br>TO DEVICE | OUTPUT<br>PRE-STATE | OUTPUT<br>ERR        | FUNCTION |

|--------|-----------------------|---------------------|----------------------|----------|

|        |                       |                     |                      |          |

| CLR    | LE                    | POINT P             | ERR <sub>n-1</sub> † |          |

| L      | L                     | L                   | X                    | Pass     |

|        |                       | H                   |                      |          |

| H      | L                     | L                   | X                    | Sample   |

|        |                       | X                   | L                    |          |

| L      | H                     | H                   | H                    |          |

|        |                       | X                   | X                    | Clear    |

| H      | H                     | X                   | L                    | Store    |

|        |                       |                     | H                    |          |

† The state of the ERR output before any changes at CLR, LE, or point P.

**TEXAS

INSTRUMENTS**

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

2-217

■ 8961723 0095394 029 ■

## **SN54ABT853, SN74ABT853 8-BIT TO 9-BIT PARITY BUS TRANSCEIVERS**

SCBS198A – FEBRUARY 1991 – REVISED JULY 1994

### error-flag waveforms

## PRODUCT PREVIEW

**absolute maximum ratings over operating free-air temperature range (unless otherwise noted)**

|                                                                                                                                 |                          |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Supply voltage range, $V_{CC}$ .....                                                                                            | -0.5 V to 7 V            |

| Input voltage range, $V_I$ (except I/O ports) (see Note 1) .....                                                                | -0.5 V to 7 V            |

| Voltage range applied to any output in the high state or power-off state, $V_O$ .....                                           | -0.5 V to 5.5 V          |

| Current into any output in the low state, $I_O$ : SN54ABT853<br>SN74ABT853 .....                                                | 96 mA<br>128 mA          |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ ) .....                                                                               | -18 mA                   |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ ) .....                                                                              | -50 mA                   |

| Maximum power dissipation at $T_A = 55^\circ\text{C}$ (in still air) (see Note 2): DB package<br>DW package<br>NT package ..... | 0.65 W<br>1.7 W<br>1.3 W |

| Storage temperature range .....                                                                                                 | -65°C to 150°C           |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2. The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils, except for the NT package, which has a trace length of zero. For more information, refer to the *Package Thermal Considerations* application note in the 1994 *ABT Advanced BiCMOS Technology Data Book*, literature number SCBDD002B.

8961223 0095395 T65

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

**recommended operating conditions (see Note 3)**

|                 |                                    | SN54ABT853      |                 | SN74ABT853 |                 | UNIT |    |

|-----------------|------------------------------------|-----------------|-----------------|------------|-----------------|------|----|

|                 |                                    | MIN             | MAX             | MIN        | MAX             |      |    |

| V <sub>CC</sub> | Supply voltage                     | 4.5             | 5.5             | 4.5        | 5.5             | V    |    |

| V <sub>IH</sub> | High-level input voltage           |                 | 2               |            | 2               | V    |    |

| V <sub>IL</sub> | Low-level input voltage            |                 | 0.8             |            | 0.8             | V    |    |

| V <sub>I</sub>  | Input voltage                      | 0               | V <sub>CC</sub> | 0          | V <sub>CC</sub> | V    |    |

| V <sub>OH</sub> | High-level output voltage          | ERR             |                 | 5.5        | 5.5             | V    |    |

| I <sub>OH</sub> | High-level output current          | Except ERR      |                 | -24        | -32             | mA   |    |

| I <sub>OL</sub> | Low-level output current           |                 |                 | 48         | 64              | mA   |    |

| Δt/Δv           | Input transition rise or fall rate | Outputs enabled |                 | 5          | 5               | ns/V |    |

| T <sub>A</sub>  | Operating free-air temperature     |                 | -55             | 125        | -40             | 85   | °C |

NOTE 3: Unused or floating pins (input or I/O) must be held high or low.

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER          |                               | TEST CONDITIONS                                                          |                 |        | TA = 25°C        |       |      | SN54ABT853 |      | SN74ABT853 |      | UNIT |  |

|--------------------|-------------------------------|--------------------------------------------------------------------------|-----------------|--------|------------------|-------|------|------------|------|------------|------|------|--|

|                    |                               |                                                                          |                 |        | MIN              | TYPE† | MAX  | MIN        | MAX  | MIN        | MAX  |      |  |

| VIK                |                               | VCC = 4.5 V, I <sub>I</sub> = -18 mA                                     |                 |        | -1.2             |       |      | -1.2       |      | -1.2       |      | V    |  |

| VOH                | All outputs except <u>ERR</u> | VCC = 4.5 V, I <sub>OH</sub> = -3 mA                                     |                 |        | 2.5              |       |      | 2.5        |      | 2.5        |      | V    |  |

|                    |                               | VCC = 5 V, I <sub>OH</sub> = -3 mA                                       |                 |        | 3                |       |      | 3          |      | 3          |      |      |  |

|                    |                               | VCC = 4.5 V                                                              | I <sub>OH</sub> | -24 mA | 2                |       |      | 2          |      |            |      |      |  |

|                    |                               |                                                                          | I <sub>OH</sub> | -32 mA | 2*               |       |      |            |      | 2          |      |      |  |

| VOL                |                               | VCC = 4.5 V                                                              | I <sub>OL</sub> | 24 mA  | 0.55             |       |      | 0.55       |      |            |      | V    |  |

|                    |                               |                                                                          | I <sub>OL</sub> | 64 mA  | 0.55*            |       |      |            |      | 0.55       |      |      |  |

| I <sub>OH</sub>    | <u>ERR</u>                    | VCC = 4.5 V, V <sub>OH</sub> = 5.5 V                                     |                 |        |                  |       |      |            |      |            |      | µA   |  |

| I <sub>I</sub>     | Control inputs                | VCC = 5.5 V, V <sub>I</sub> = VCC or GND                                 |                 |        | ±1               |       |      | ±1         |      | ±1         |      | µA   |  |

|                    | A or B ports                  |                                                                          |                 |        | ±100             |       |      | ±100       |      | ±100       |      |      |  |

| I <sub>IL</sub>    | A or B ports                  | VCC = 0, V <sub>I</sub> = GND                                            |                 |        | -50              |       |      | -50        |      | -50        |      | µA   |  |

| I <sub>OZH</sub> ‡ |                               | VCC = 5.5 V, V <sub>O</sub> = 2.7 V                                      |                 |        | 50               |       |      | 50         |      | 50         |      | µA   |  |

| I <sub>OZL</sub> ‡ |                               | VCC = 5.5 V, V <sub>O</sub> = 0.5 V                                      |                 |        | -50              |       |      | -50        |      | -50        |      | µA   |  |

| I <sub>off</sub>   |                               | VCC = 0, V <sub>I</sub> or V <sub>O</sub> ≤ 4.5 V                        |                 |        | ±100             |       |      |            |      | ±100       |      | µA   |  |

| I <sub>CEX</sub>   |                               | VCC = 5.5 V, V <sub>O</sub> = 5.5 V                                      |                 |        | Outputs high     |       |      | 50         |      | 50         |      | µA   |  |

| I <sub>O\$</sub>   |                               | VCC = 5.5 V, V <sub>O</sub> = 2.5 V                                      |                 |        | -50              | -100  | -180 | -50        | -180 | -50        | -180 | mA   |  |

| I <sub>CC</sub>    | A or B ports                  | VCC = 5.5 V, I <sub>O</sub> = 0, V <sub>I</sub> = V <sub>CC</sub> or GND |                 |        | Outputs high     |       |      | 1          | 250  | 250        | 250  | µA   |  |

|                    |                               |                                                                          |                 |        | Outputs low      |       |      | 24         | 30   | 30         | 30   | mA   |  |

|                    |                               |                                                                          |                 |        | Outputs disabled |       |      | 0.5        | 250  | 250        | 250  | µA   |  |

| ΔICC¶              |                               | VCC = 5.5 V, One input at 3.4 V, Other inputs at V <sub>CC</sub> or GND  |                 |        | 50               |       |      | 50         |      | 50         |      | µA   |  |

| C <sub>I</sub>     | Control Inputs                | V <sub>I</sub> = 2.5 V or 0.5 V                                          |                 |        |                  |       |      |            |      |            |      | pF   |  |

| C <sub>IO</sub>    | A or B ports                  | V <sub>O</sub> = 2.5 V or 0.5 V                                          |                 |        |                  |       |      |            |      |            |      | pF   |  |

\* On products compliant to MIL-STD-883, Class B, this parameter does not apply.

<sup>a</sup> All typical values are at  $V_{CC} = 5$  V.

<sup>†</sup> The parameters  $I_{02H}$  and  $I_{02L}$  include the input leakage current.

+ The parameters  $I_{OZH}$  and  $I_{OZL}$  include the input leakage current.

§ Not more than one output should be tested at a time, and the duration of the test should not exceed one second.

9 Not more than one output should be tested at a time, and the duration of the test should not exceed one second.

10 This is the increase in supply current for each input that is at the specified TTL voltage level rather than  $V_{CC}$  or GND.