DATASHEET

### **Description**

The 9DBV0431 is a member of IDT's SOC-Friendly 1.8V Very-Low-Power (VLP) PCIe family. It can also be used for 50M or 125M Ethernet Applications via software frequency selection. The device has 4 output enables for clock management, and 3 selectable SMBus addresses.

### **Recommended Application**

1.8V PCIe Gen1-2-3 Zero-Delay/Fan-out Buffer (ZDB/FOB)

### **Output Features**

• 4 - 1-200Hz Low-Power (LP) HCSL DIF pairs w/Zo=100ohms

### **Key Specifications**

- DIF cycle-to-cycle jitter <50ps</li>

- DIF output-to-output skew <50ps</li>

- DIF additive phase jitter is <100fs rms for PCIe Gen3

- DIF additive phase jitter <300fs rms for 12k-20MHz

### Features/Benefits

- LP-HCSL outputs save 8 resistors; minimal board space and BOM cost

- 53mW typical power consumption in PLL mode; minimal power consumption

- OE# pins; support DIF power management

- HCSL compatible differential input; can be driven by common clock sources

- Programmable Slew rate for each output; allows tuning for various line lengths

- Programmable output amplitude; allows tuning for various application environments

- Pin/software selectable PLL bandwidth and PLL Bypass; minimize phase jitter for each application

- Outputs blocked until PLL is locked; clean system start-up

- Software selectable 50MHz or 125MHz PLL operation; useful for Ethernet applications

- Configuration can be accomplished with strapping pins; SMBus interface not required for device control

- 3.3V tolerant SMBus interface works with legacy controllers

- Space saving 32-pin 5x5mm VFQFPN; minimal board space

- Selectable SMBus addresses; multiple devices can easily share an SMBus segment

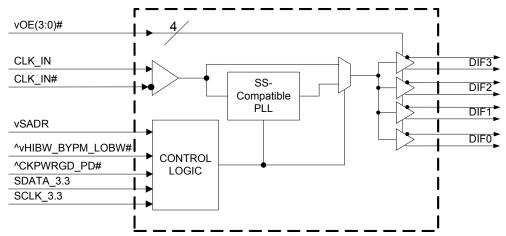

### **Block Diagram**

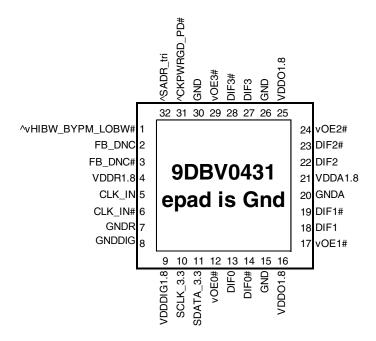

### **Pin Configuration**

#### 32-pin VFQFPN, 5x5 mm, 0.5mm pitch

#### **SMBus Address Selection Table**

|                                       | SADR | Address | + Read/Write bit |

|---------------------------------------|------|---------|------------------|

| State of SADR on first application of | 0    | 1101011 | X                |

| CKPWRGD_PD#                           | M    | 1101100 | X                |

|                                       | 1    | 1101101 | x                |

#### **Power Management Table**

| CKPWRGD PD# | CLK_IN  | SMBus   | OEx# Pin  | DIF      | PLL       |                 |

|-------------|---------|---------|-----------|----------|-----------|-----------------|

| CKFWKGD_FD# | CLK_IN  | OEx bit | OLX# FIII | True O/P | Comp. O/P | FLL             |

| 0           | Х       | Х       | X         | Low      | Low       | Off             |

| 1           | Running | 0       | Х         | Low      | Low       | On <sup>1</sup> |

| 1           | Running | 1       | 0         | Running  | Running   | On <sup>1</sup> |

| 1           | Running | 1       | 1         | Low      | Low       | On <sup>1</sup> |

<sup>1.</sup> If Bypass mode is selected, the PLL will be off, and outputs will be running.

#### **Power Connections**

| Pin Numb | Pin Number  |                       |  |  |  |

|----------|-------------|-----------------------|--|--|--|

| VDD      | GND         | Description           |  |  |  |

| 4        | 7           | Input receiver analog |  |  |  |

| 9        | 8           | Digital Power         |  |  |  |

| 16, 25   | 15,20,26,30 | DIF outputs           |  |  |  |

| 21       | 20          | PLL Analog            |  |  |  |

#### **PLL Operating Mode**

| HiBW_BypM_LoBW# | MODE      | Byte1 [7:6]<br>Readback | Byte1 [4:3]<br>Control |

|-----------------|-----------|-------------------------|------------------------|

| 0               | PLL Lo BW | 00                      | 00                     |

| М               | Bypass    | 01                      | 01                     |

| 1               | PLL Hi BW | 11                      | 11                     |

#### **Frequency Select Table**

| •            |          |          |

|--------------|----------|----------|

| FSEL         | CLK_IN   | DIFx     |

| Byte3 [4:3]  | (MHz)    | (MHz)    |

| 00 (Default) | 100.00   | CLK_IN   |

| 01           | 50.00    | CLK_IN   |

| 10           | 125.00   | CLK_IN   |

| 11           | Reserved | Reserved |

# **Pin Descriptions**

| Pin# | Pin Name         | Туре    | Pin Description                                                                      |

|------|------------------|---------|--------------------------------------------------------------------------------------|

| 4    | AVHIDIM DVDM LOD | LATCHED | Trilevel input to select High BW, Bypass or Low BW mode.                             |

| 1    | ^vHIBW_BYPM_LOB  | IN      | See PLL Operating Mode Table for Details.                                            |

|      | FB_DNC           | DNC     | True clock of differential feedback. The feedback output and feedback input are      |

| 2    | LP_DINC          | DINC    | connected internally on this pin. Do not connect anything to this pin.               |

| 2    | FB DNC#          | DNC     | Complement clock of differential feedback. The feedback output and feedback          |

| 3    | FB_DINC#         | DNC     | input are connected internally on this pin. Do not connect anything to this pin.     |

| 4    | VDDR1.8          | PWR     | 1.8V power for differential input clock (receiver). This VDD should be treated as an |

| 4    | יחטטיי.0         | LAAU    | Analog power rail and filtered appropriately.                                        |

| 5    | CLK_IN           | IN      | True Input for differential reference clock.                                         |

| 6    | CLK_IN#          | IN      | Complementary Input for differential reference clock.                                |

| 7    | GNDR             | GND     | Analog Ground pin for the differential input (receiver)                              |

| 8    | GNDDIG           | GND     | Ground pin for digital circuitry                                                     |

| 9    | VDDDIG1.8        | PWR     | 1.8V digital power (dirty power)                                                     |

| 10   | SCLK_3.3         | IN      | Clock pin of SMBus circuitry, 3.3V tolerant.                                         |

| 11   | SDATA_3.3        | I/O     | Data pin for SMBus circuitry, 3.3V tolerant.                                         |

| 12   | vOE0#            | ZI      | Active low input for enabling DIF pair 0. This pin has an internal pull-down.        |

| 12   | VOE0#            | IIN     | 1 =disable outputs, 0 = enable outputs                                               |

| 13   | DIF0             | OUT     | Differential true clock output                                                       |

| 14   | DIF0#            | OUT     | Differential Complementary clock output                                              |

| 15   | GND              | GND     | Ground pin.                                                                          |

| 16   | VDDO1.8          | PWR     | Power supply for outputs, nominally 1.8V.                                            |

| 17   | VOE1#            | N       | Active low input for enabling DIF pair 1. This pin has an internal pull-down.        |

| 17   | vOE1#            | IIN     | 1 =disable outputs, 0 = enable outputs                                               |

| 18   | DIF1             | OUT     | Differential true clock output                                                       |

| 19   | DIF1#            | OUT     | Differential Complementary clock output                                              |

| 20   | GNDA             | GND     | Ground pin for the PLL core.                                                         |

| 21   | VDDA1.8          | PWR     | 1.8V power for the PLL core.                                                         |

| 22   | DIF2             | OUT     | Differential true clock output                                                       |

| 23   | DIF2#            | OUT     | Differential Complementary clock output                                              |

| 24   | vOE2#            | ZI      | Active low input for enabling DIF pair 2. This pin has an internal pull-down.        |

| 24   | VOE2#            | IIN     | 1 =disable outputs, 0 = enable outputs                                               |

| 25   | VDDO1.8          | PWR     | Power supply for outputs, nominally 1.8V.                                            |

| 26   | GND              | GND     | Ground pin.                                                                          |

| 27   | DIF3             | OUT     | Differential true clock output                                                       |

| 28   | DIF3#            | OUT     | Differential Complementary clock output                                              |

| 20   | v∩E2#            | INI     | Active low input for enabling DIF pair 3. This pin has an internal pull-down.        |

| 29   | vOE3#            | IN      | 1 =disable outputs, 0 = enable outputs                                               |

| 30   | GND              | GND     | Ground pin.                                                                          |

|      |                  |         | Input notifies device to sample latched inputs and start up on first high assertion. |

| 31   | ^CKPWRGD_PD#     | IN      | Low enters Power Down Mode, subsequent high assertions exit Power Down Mode.         |

|      | _                |         | This pin has internal pull-up resistor.                                              |

| 20   | ACADD +ri        | LATCHED |                                                                                      |

| 32   | ^SADR_tri        | IN      | Tri-level latch to select SMBus Address. See SMBus Address Selection Table.          |

| 33   | ePad             | GND     | Connect epad to ground.                                                              |

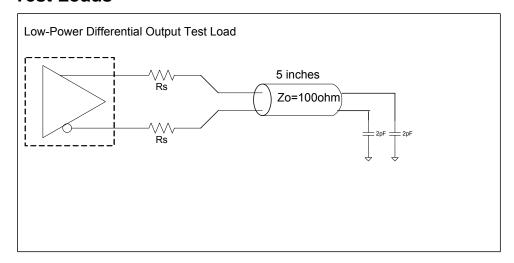

### **Test Loads**

### **Alternate Differential Output Terminations**

| Rs | Zo  | Units  |

|----|-----|--------|

| 33 | 100 | Ohms   |

| 27 | 85  | Onlins |

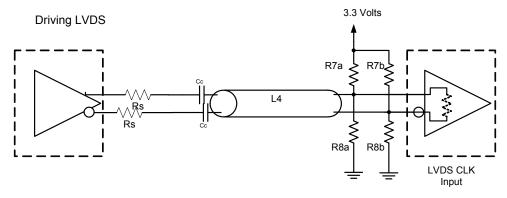

## **Driving LVDS**

#### Driving LVDS inputs with the 9DBV0431

|           | ,            |                   |      |

|-----------|--------------|-------------------|------|

|           | Receiver has | Receiver does not |      |

| Component | termination  | have termination  | Note |

| R7a, R7b  | 10K ohm      | 140 ohm           |      |

| R8a, R8b  | 5.6K ohm     | 75 ohm            |      |

| Cc        | 0.1 uF       | 0.1 uF            |      |

| Vcm       | 1.2 volts    | 1.2 volts         |      |

### **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 9DBV0431. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| PARAMETER                 | SYMBOL          | CONDITIONS                | MIN  | TYP | MAX             | UNITS | NOTES |

|---------------------------|-----------------|---------------------------|------|-----|-----------------|-------|-------|

| Power supply voltage      | VDDxx           | Applies to all VDD pins   | -0.5 |     | 2.5             | V     | 1,2   |

| Input Voltage             | V <sub>IN</sub> |                           | -0.5 |     | $V_{DD} + 0.5V$ | V     | 1, 3  |

| Input High Voltage, SMBus | $V_{IHSMB}$     | SMBus clock and data pins |      |     | 3.6V            | V     | 1     |

| Storage Temperature       | Ts              |                           | -65  |     | 150             | °C    | 1     |

| Junction Temperature      | Tj              |                           |      |     | 125             | °C    | 1     |

| Input ESD protection      | ESD prot        | Human Body Model          | 2000 |     |                 | V     | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

### **Electrical Characteristics-Clock Input Parameters**

TA = T<sub>COM</sub> or T<sub>IND</sub>. Supply Voltage per VDD of normal operation conditions, See Test Loads for Loading Conditions

| The Toom of Tind; Cappiy Voltage per VBB of Hermal operation containence; eco Toot Estating Containence |                    |                                                    |                       |     |      |       |       |

|---------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------|-----------------------|-----|------|-------|-------|

| PARAMETER                                                                                               | SYMBOL             | CONDITIONS                                         | MIN                   | TYP | MAX  | UNITS | NOTES |

| Input High Voltage - DIF_IN                                                                             | V <sub>IHDIF</sub> | Differential inputs (single-ended measurement)     | 600                   | 800 | 1150 | mV    | 1     |

| Input Low Voltage - DIF_IN                                                                              | V <sub>ILDIF</sub> | Differential inputs (single-ended measurement)     | V <sub>SS</sub> - 300 | 0   | 300  | mV    | 1     |

| Input Common Mode Voltage - DIF_IN                                                                      | $V_{COM}$          | Common Mode Input Voltage                          | 300                   |     | 725  | mV    | 1     |

| Input Amplitude - DIF_IN                                                                                | $V_{SWING}$        | Peak to Peak value (VIHDIF - VILDIF), single-ended | 300                   |     | 1450 | mV    | 1     |

| Input Slew Rate - DIF_IN                                                                                | dv/dt              | Measured differentially                            | 0.4                   |     |      | V/ns  | 1,2   |

| Input Leakage Current                                                                                   | I <sub>IN</sub>    | $V_{IN} = V_{DD}$ , $V_{IN} = GND$                 | -5                    |     | 5    | uA    | 1     |

| Input Duty Cycle                                                                                        | $d_{tin}$          | Measurement from differential wavefrom             | 45                    |     | 55   | %     | 1     |

| Input Jitter - Cycle to Cycle                                                                           | $J_{DIFIn}$        | Differential Measurement                           | 0                     |     | 150  | ps    | 1     |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Operation under these conditions is neither implied nor guaranteed.

<sup>&</sup>lt;sup>3</sup> Not to exceed 2.5V.

<sup>&</sup>lt;sup>2</sup> Slew rate measured through +/-75mV window centered around differential zero

# Electrical Characteristics–Input/Supply/Common Parameters–Normal Operating Conditions

$TA = T_{COM}$  or  $T_{IND}$ . Supply Voltage per VDD of normal operation conditions, See Test Loads for Loading Conditions

| THE TOM OF TIND; Cupping to                         | itage per VD          | of normal operation conditions, See Test Loads for                                                                                                   | Loading Con          | uitions |                      |        |       |

|-----------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|----------------------|--------|-------|

| PARAMETER                                           | SYMBOL                | CONDITIONS                                                                                                                                           | MIN                  | TYP     | MAX                  | UNITS  | NOTES |

| 1.8V Supply Voltage                                 | VDD                   | Supply voltage for core, analog and LVCMOS outputs                                                                                                   | 1.7                  | 1.8     | 1.9                  | V      | 1     |

| Ambient Operating                                   | T <sub>COM</sub>      | Commmercial range                                                                                                                                    | 0                    | 25      | 70                   | °C     | 1     |

| Temperature                                         | $T_IND$               | Industrial range                                                                                                                                     | -40                  | 25      | 85                   | °C     | 1     |

| Input High Voltage                                  | $V_{IH}$              | Single-ended inputs, except SMBus                                                                                                                    | 0.75 V <sub>DD</sub> |         | $V_{DD} + 0.3$       | V      | 1     |

| Input Mid Voltage                                   | $V_{IM}$              | Single-ended tri-level inputs ('_tri' suffix)                                                                                                        | $0.4~V_{DD}$         |         | 0.6 V <sub>DD</sub>  | ٧      | 1     |

| Input Low Voltage                                   | $V_{IL}$              | Single-ended inputs, except SMBus                                                                                                                    | -0.3                 |         | 0.25 V <sub>DD</sub> | V      | 1     |

|                                                     | I <sub>IN</sub>       | Single-ended inputs, $V_{IN} = GND$ , $V_{IN} = VDD$                                                                                                 | -5                   |         | 5                    | uA     | 1     |

| Input Current                                       | I <sub>INP</sub>      | Single-ended inputs $V_{IN} = 0 \text{ V}$ ; Inputs with internal pull-up resistors $V_{IN} = \text{VDD}$ ; Inputs with internal pull-down resistors | -200                 |         | 200                  | uA     | 1     |

|                                                     | $F_{ibyp}$            | Bypass mode                                                                                                                                          | 1                    |         | 200                  | MHz    | 2     |

| Input Frequency                                     | F <sub>ipII100</sub>  | 100MHz PLL mode                                                                                                                                      | 50                   | 100     | 140                  | MHz    | 2     |

| input i requency                                    | F <sub>ipll125</sub>  | 125MHz PLL mode                                                                                                                                      | 62.5                 | 125     | 175                  | MHz    | 2     |

|                                                     | F <sub>ipll62</sub>   | 50MHz PLL mode                                                                                                                                       | 25                   | 50      | 65                   | MHz    | 2     |

| Pin Inductance                                      | $L_{pin}$             |                                                                                                                                                      |                      |         | 7                    | nΗ     | 1     |

|                                                     | $C_{IN}$              | Logic Inputs, except DIF_IN                                                                                                                          | 1.5                  |         | 5                    | рF     | 1     |

| Capacitance  Clk Stabilization  Input SS Modulation | C <sub>INDIF_IN</sub> | DIF_IN differential clock inputs                                                                                                                     | 1.5                  |         | 2.7                  | рF     | 1,6   |

|                                                     | C <sub>OUT</sub>      | Output pin capacitance                                                                                                                               |                      |         | 6                    | рF     | 1     |

| Clk Stabilization                                   | T <sub>STAB</sub>     | From V <sub>DD</sub> Power-Up and after input clock stabilization or de-assertion of PD# to 1st clock                                                |                      | 0.6     | 1                    | ms     | 1,2   |

| Input SS Modulation<br>Frequency                    | f <sub>MODIN</sub>    | Allowable Frequency (Triangular Modulation)                                                                                                          | 30                   | 31.5    | 33                   | kHz    | 1     |

| OE# Latency                                         | t <sub>LATOE#</sub>   | DIF start after OE# assertion DIF stop after OE# deassertion                                                                                         | 1                    |         | 3                    | clocks | 1,3   |

| Tdrive_PD#                                          | t <sub>DRVPD</sub>    | DIF output enable after<br>PD# de-assertion                                                                                                          |                      | 175     | 300                  | us     | 1,3   |

| Tfall                                               | t <sub>F</sub>        | Fall time of single-ended control inputs                                                                                                             |                      |         | 5                    | ns     | 1,2   |

| Trise                                               | $t_R$                 | Rise time of single-ended control inputs                                                                                                             |                      |         | 5                    | ns     | 1,2   |

| SMBus Input Low Voltage                             | $V_{ILSMB}$           | $V_{DDSMB} = 3.3V$ , see note 4 for $V_{DDSMB} < 3.3V$                                                                                               |                      |         | 0.8                  | ٧      | 1,4   |

| SMBus Input High Voltage                            | $V_{IHSMB}$           | $V_{DDSMB} = 3.3V$ , see note 5 for $V_{DDSMB} < 3.3V$                                                                                               | 2.1                  |         | 3.6                  | ٧      | 1,5   |

| SMBus Output Low Voltage                            | $V_{OLSMB}$           | @ I <sub>PULLUP</sub>                                                                                                                                |                      |         | 0.4                  | ٧      | 1     |

| SMBus Sink Current                                  | I <sub>PULLUP</sub>   | @ V <sub>OL</sub>                                                                                                                                    | 4                    |         |                      | mA     | 1     |

| Nominal Bus Voltage                                 | $V_{\rm DDSMB}$       |                                                                                                                                                      | 1.7                  |         | 3.6                  | ٧      | 1     |

| SCLK/SDATA Rise Time                                | t <sub>RSMB</sub>     | (Max VIL - 0.15) to (Min VIH + 0.15)                                                                                                                 |                      |         | 1000                 | ns     | 1     |

| SCLK/SDATA Fall Time                                | t <sub>FSMB</sub>     | (Min VIH + 0.15) to (Max VIL - 0.15)                                                                                                                 |                      |         | 300                  | ns     | 1     |

| SMBus Operating Frequency                           | f <sub>MAXSMB</sub>   | Maximum SMBus operating frequency                                                                                                                    |                      |         | 400                  | kHz    | 1,7   |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

$<sup>^2\</sup>mbox{Control}$  input must be monotonic from 20% to 80% of input swing.

<sup>&</sup>lt;sup>3</sup>Time from deassertion until outputs are >200 mV

$<sup>^4</sup>$  For  $V_{\text{DDSMB}} < 3.3 V, \ V_{\text{ILSMB}} <= 0.25 V_{\text{DDSMB}}$

$<sup>^{5}</sup>$  For V<sub>DDSMB</sub> < 3.3V, V<sub>IHSMB</sub> >= 0.7V<sub>DDSMB</sub>

<sup>&</sup>lt;sup>6</sup>DIF\_IN input

<sup>&</sup>lt;sup>7</sup>The differential input clock must be running for the SMBus to be active

### **Electrical Characteristics-DIF 0.7V Low Power HCSL Outputs**

TA = T<sub>COM</sub> or T<sub>IND</sub>: Supply Voltage per VDD of normal operation conditions, See Test Loads for Loading Conditions

| OOW - IND,  -  - J     | 3 - 1 -           |                                                        |      |      |      |        |         |

|------------------------|-------------------|--------------------------------------------------------|------|------|------|--------|---------|

| PARAMETER              | SYMBOL            | CONDITIONS                                             | MIN  | TYP  | MAX  | UNITS  | NOTES   |

| Slew rate              | Trf               | Scope averaging on 3.0V/ns setting                     | 2    | 3.2  | 4    | V/ns   | 1, 2, 3 |

| Siew rate              | 111               | Scope averaging on 2.0V/ns setting                     | 1.3  | 2.3  | 3.3  | V/ns   | 1, 2, 3 |

| Slew rate matching     | ΔTrf              | Slew rate matching, Scope averaging on                 |      | 5.4  | 20   | %      | 1, 2, 4 |

| Voltage High           | V <sub>HIGH</sub> | Statistical measurement on single-ended signal         | 660  | 779  | 850  | mV     | 1,7     |

| Voltage Low            | $V_{LOW}$         | using oscilloscope math function. (Scope averaging on) |      | 21   | 150  | ] "" [ | 1,7     |

| Max Voltage            | Vmax              | Measurement on single ended signal using               |      | 835  | 1150 | mV     | 1       |

| Min Voltage            | Vmin              | absolute value. (Scope averaging off)                  | -300 | -42  |      | 1117   | 1       |

| Vswing                 | Vswing            | Scope averaging off                                    | 300  | 1515 |      | mV     | 1,2,7   |

| Crossing Voltage (abs) | Vcross_abs        | Scope averaging off                                    | 250  | 409  | 550  | mV     | 1,5,7   |

| Crossing Voltage (var) | Δ-Vcross          | Scope averaging off                                    |      | 14   | 140  | mV     | 1, 6    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.  $C_L = 2pF$  with  $R_S = 33Ω$  for Zo = 50Ω (100Ω differential trace impedance).

### **Electrical Characteristics-Current Consumption**

TA = T<sub>COM</sub> or T<sub>IND</sub>; Supply Voltage per VDD of normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER                           | SYMBOL             | CONDITIONS                     | MIN | TYP  | MAX | UNITS | NOTES |

|-------------------------------------|--------------------|--------------------------------|-----|------|-----|-------|-------|

| Operating Supply Current (PLL Mode) | I <sub>DDROP</sub> | VDDR, @100MHz                  |     | 4.2  | 6   | mA    | 1     |

|                                     | I <sub>DDOP</sub>  | VDDA + VDD1.8, @100MHz         |     | 27   | 33  | mA    | 1     |

| Operating Supply Current            | I <sub>DDROP</sub> | VDDR, @100MHz                  |     | 2.2  | 3   | mA    | 1     |

| (PLL-Bypass Mode)                   | I <sub>DDOP</sub>  | VDDA + VDD1.8, @100MHz         |     | 20   | 25  | mA    | 1     |

| Powerdown Current                   | I <sub>DDRPD</sub> | VDDR, CKPWRGD_PD# = 0          |     | 1,2  |     |       |       |

| Powerdown Current                   | I <sub>DDPD</sub>  | VDDA + VDD1.8, CKPWRGD_PD# = 0 |     | 0.95 | 1.2 | mA    | 1, 2  |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Measured from differential waveform

<sup>&</sup>lt;sup>3</sup> Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around differential 0V.

<sup>&</sup>lt;sup>4</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

<sup>&</sup>lt;sup>5</sup> Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

<sup>&</sup>lt;sup>6</sup> The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross\_min/max (Vcross absolute) allowed. The intent is to limit Vcross induced modulation by setting  $\Delta$ -Vcross to be smaller than Vcross absolute.

<sup>&</sup>lt;sup>7</sup> At default SMBus settings.

<sup>&</sup>lt;sup>2</sup> Input clock stopped, and CKPWRGD\_PD# pin low.

### Electrical Characteristics-Output Duty Cycle, Jitter, Skew and PLL Characteristics

TA = T<sub>COM</sub> or T<sub>IND</sub>; Supply Voltage per VDD of normal operation conditions, See Test Loads for Loading Conditions

| TOOM TO TIND, THE POT  | <u> </u>              | ,,,,,,, .                                        |      |      |      |       |       |

|------------------------|-----------------------|--------------------------------------------------|------|------|------|-------|-------|

| PARAMETER              | SYMBOL                | CONDITIONS                                       | MIN  | TYP  | MAX  | UNITS | NOTES |

| PLL Bandwidth          | BW                    | -3dB point in High BW Mode                       | 2    | 2.7  | 4    | MHz   | 1,5   |

| FLL Balldwidth         | DVV                   | -3dB point in Low BW Mode                        | 1    | 1.4  | 2    | MHz   | 1,5   |

| PLL Jitter Peaking     | t <sub>JPEAK</sub>    | Peak Pass band Gain                              |      | 1.2  | 2    | dB    | 1     |

| Duty Cycle             | t <sub>DC</sub>       | Measured differentially, PLL Mode                | 45   | 50.1 | 55   | %     | 1     |

| Duty Cycle Distortion  | t <sub>DCD</sub>      | Measured differentially, Bypass Mode @100MHz     | -1   | -0.1 | 1    | %     | 1,3   |

| Skew, Input to Output  | t <sub>pdBYP</sub>    | Bypass Mode, V <sub>T</sub> = 50%                | 2550 | 3370 | 4200 | ps    | 1     |

| Skew, Input to Output  | t <sub>pdPLL</sub>    | PLL Mode V <sub>T</sub> = 50%                    | 0    | 112  | 200  | ps    | 1,4   |

| Skew, Output to Output | +                     | Commercial Operating Range, V <sub>T</sub> = 50% |      | 33   | 50   | ps    | 1,4   |

| Skew, Output to Output | t <sub>sk3</sub>      | Industrial Operating Range, V <sub>T</sub> = 50% |      | 33   | 55   | ps    | 1,4   |

| Jitter, Cycle to cycle | +.                    | PLL mode                                         |      | 13   | 50   | ps    | 1,2   |

| Jitter, Cycle to Cycle | t <sub>jcyc-cyc</sub> | Additive Jitter in Bypass Mode                   |      | 0.1  | 1    | ps    | 1,2   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

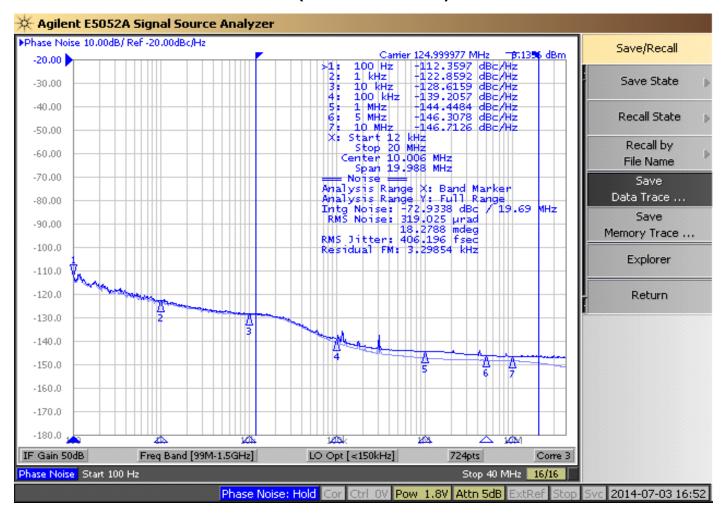

### **Electrical Characteristics-Phase Jitter Parameters**

$TA = T_{COM}$  or  $T_{IND}$ ; Supply Voltage per VDD of normal operation conditions, See Test Loads for Loading Conditions

|                                       |                         |                                                                                       |     |      |     | INDUSTRY |             |       |

|---------------------------------------|-------------------------|---------------------------------------------------------------------------------------|-----|------|-----|----------|-------------|-------|

| PARAMETER                             | SYMBOL                  | CONDITIONS                                                                            | MIN | TYP  | MAX | LIMIT    | UNITS       | Notes |

|                                       | t <sub>iphPCleG1</sub>  | PCIe Gen 1                                                                            |     | 32   | 52  | 86       | ps (p-p)    | 1,2,3 |

|                                       |                         | PCIe Gen 2 Lo Band<br>10kHz < f < 1.5MHz                                              |     | 0.8  | 1.4 | 3        | ps<br>(rms) | 1,2   |

| Phase Jitter, PLL Mode                | t <sub>jphPCleG2</sub>  | PCIe Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz)                                  |     | 2.4  | 2.6 | 3.1      | ps<br>(rms) | 1,2   |

|                                       | t <sub>jphPCleG3</sub>  | PCIe Gen 3<br>(PLL BW of 2-4MHz, CDR = 10MHz)                                         |     | 0.5  | 0.6 | 1        | ps<br>(rms) | 1,2,4 |

|                                       | t <sub>jphSGMII</sub>   | 125MHz, 1.5MHz to 10MHz, -20dB/decade rollover < 1.5MHz, -40db/decade rolloff > 10MHz |     | 1.9  | 2.2 | 3        | ps<br>(rms) | 1,6   |

|                                       | t <sub>jphPCleG1</sub>  | PCle Gen 1                                                                            |     | 0.1  | 5.0 | N/A      | ps (p-p)    | 1,2,3 |

|                                       |                         | PCIe Gen 2 Lo Band<br>10kHz < f < 1.5MHz                                              |     | 0.2  | 0.3 | N/A      | ps<br>(rms) | 1,2,4 |

|                                       | t <sub>jphPCleG2</sub>  | PCIe Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz)                                  |     | 0.05 | 0.1 | N/A      | ps<br>(rms) | 1,2,4 |

| Additive Phase Jitter,<br>Bypass Mode | t <sub>jphPCleG3</sub>  | PCIe Gen 3<br>(PLL BW of 2-4MHz, CDR = 10MHz)                                         |     | 0.05 | 0.1 | N/A      | ps<br>(rms) | 1,2,4 |

|                                       | t <sub>jphSGMIIMO</sub> | 125MHz, 1.5MHz to 10MHz, -20dB/decade rollover < 1.5MHz, -40db/decade rolloff > 10MHz |     | 165  | 200 | N/A      | fs<br>(rms) | 1,6   |

|                                       | t <sub>jphSGMIIM1</sub> | 125MHz, 12kHz to 20MHz, -20dB/decade rollover < 1.5MHz, -40db/decade rolloff > 10MHz  | -   | 251  | 300 | N/A      | fs<br>(rms) | 1,6   |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Measured from differential waveform

<sup>&</sup>lt;sup>3</sup> Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

<sup>&</sup>lt;sup>4</sup> All outputs at default slew rate

<sup>&</sup>lt;sup>5</sup> The MIN/TYP/MAX values of each BW setting track each other, i.e., Low BW MAX will never occur with Hi BW MIN.

<sup>&</sup>lt;sup>2</sup> See http://www.pcisig.com for complete specs

<sup>&</sup>lt;sup>3</sup> Sample size of at least 100K cycles. This figures extrapolates to 108ps pk-pk @ 1M cycles for a BER of 1-12.

<sup>&</sup>lt;sup>4</sup> For RMS figures, additive jitter is calculated by solving the following equation: Additive jitter = SQRT[(total jitter)^2 - (input jitter)^2]

<sup>&</sup>lt;sup>5</sup> Driven by 9FGV0831 or equivalent

<sup>&</sup>lt;sup>6</sup> Driven by Rohde&Schwarz SMA100

### Additive Phase Jitter Plot: 125M (12kHz to 20MHz)

#### **General SMBus Serial Interface Information**

#### **How to Write**

- Controller (host) sends a start bit

- Controller (host) sends the write address

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will acknowledge

- Controller (host) sends the byte count = X

- IDT clock will acknowledge

- Controller (host) starts sending Byte N through Byte N+X-1

- IDT clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

|           | Index Blo  | ock \  | Write Operation      |

|-----------|------------|--------|----------------------|

| Controll  | ler (Host) |        | IDT (Slave/Receiver) |

| Т         | starT bit  |        |                      |

| Slave     | Address    |        |                      |

| WR        | WRite      |        |                      |

|           |            |        | ACK                  |

| Beginnin  | g Byte = N |        |                      |

|           |            |        | ACK                  |

| Data Byte | Count = X  |        |                      |

|           |            |        | ACK                  |

| Beginnir  | ng Byte N  | ×      |                      |

|           |            | X Byte | ACK                  |

| 0         |            |        |                      |

| 0         |            |        | 0                    |

| 0         |            |        | 0                    |

|           |            |        | 0                    |

| Byte N    | I + X - 1  |        |                      |

|           |            |        | ACK                  |

| Р         | stoP bit   |        |                      |

Note: SMBus address is latched on SADR pin.

#### How to Read

- Controller (host) will send a start bit

- Controller (host) sends the write address

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will acknowledge

- Controller (host) will send a separate start bit

- Controller (host) sends the read address

- IDT clock will acknowledge

- IDT clock will send the data byte count = X

- IDT clock sends Byte N+X-1

- IDT clock sends Byte 0 through Byte X (if X<sub>(H)</sub> was written to Byte 8)

- Controller (host) will need to acknowledge each byte

- Controller (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

|     | Index Block R   | ead C  | <b>Operation</b>     |

|-----|-----------------|--------|----------------------|

| Co  | ntroller (Host) |        | IDT (Slave/Receiver) |

| Т   | starT bit       |        |                      |

| S   | ave Address     |        |                      |

| WR  | WRite           |        |                      |

|     |                 |        | ACK                  |

| Beg | inning Byte = N |        |                      |

|     |                 |        | ACK                  |

| RT  | Repeat starT    |        |                      |

| S   | ave Address     |        |                      |

| RD  | ReaD            |        |                      |

|     |                 |        | ACK                  |

|     |                 |        |                      |

|     |                 |        | Data Byte Count=X    |

|     | ACK             |        |                      |

|     |                 |        | Beginning Byte N     |

|     | ACK             |        |                      |

|     |                 | क      | 0                    |

|     | 0               | X Byte | 0                    |

|     | 0               | ×      | 0                    |

|     | 0               |        |                      |

|     |                 |        | Byte N + X - 1       |

| N   | Not acknowledge |        |                      |

| Р   | stoP bit        |        |                      |

### SMBus Table: Output Enable Register <sup>1</sup>

| Byte 0 | Name     | Control Function | Туре | 0       | 1       | Default |  |

|--------|----------|------------------|------|---------|---------|---------|--|

| Bit 7  |          | Reserved         |      |         |         |         |  |

| Bit 6  | DIF OE3  | Output Enable    | RW   | Low/Low | Enabled | 1       |  |

| Bit 5  | DIF OE2  | Output Enable    | RW   | Low/Low | Enabled | 1       |  |

| Bit 4  | Reserved |                  |      |         |         |         |  |

| Bit 3  | DIF OE1  | Output Enable    | RW   | Low/Low | Enabled | 1       |  |

| Bit 2  |          | Reserved         |      |         |         | 1       |  |

| Bit 1  | DIF OE0  | Output Enable    | RW   | Low/Low | Enabled | 1       |  |

| Bit 0  |          | Reserved         |      |         |         | 1       |  |

<sup>1.</sup> A low on these bits will overide the OE# pin and force the differential output Low/Low

#### SMBus Table: PLL Operating Mode and Output Amplitude Control Register

| Byte 1 | Name             | Control Function                                    | Type                  | 0                 | 1                 | Default |  |

|--------|------------------|-----------------------------------------------------|-----------------------|-------------------|-------------------|---------|--|

| Bit 7  | PLLMODERB1       | PLL Mode Readback Bit 1                             | R                     | See PLL Operate   | ting Mode Table   | Latch   |  |

| Bit 6  | PLLMODERB0       | PLL Mode Readback Bit 0                             | R                     | See Fill Opera    |                   | Latch   |  |

| Bit 5  | PLLMODE SWCNTRL  | Enable SW control of PLL Mode                       | RW                    | Values in B1[7:6] | Values in B1[4:3] | 0       |  |

| DIL 3  | T ELMODE_SWONTKE | VIODE_OVIOINTE Eliable SVV control of T EL Mode TVV | 1700                  | set PLL Mode      | set PLL Mode      | U       |  |

| Bit 4  | PLLMODE1         | PLL Mode Control Bit 1                              | RW <sup>1</sup>       | See PLL Operate   | ting Mode Table   | 0       |  |

| Bit 3  | PLLMODE0         | PLL Mode Control Bit 0                              | RW <sup>1</sup>       | See FLL Opera     | ling Mode Table   | 0       |  |

| Bit 2  |                  | Reserved                                            |                       |                   |                   | 1       |  |

| Bit 1  | AMPLITUDE 1      | Controls Output Amplitude                           | RW                    | 00 = 0.6V         | 01 = 0.7V         | 1       |  |

| Bit 0  | AMPLITUDE 0      | Controls Output Amplitude                           | RW 10= 0.8V 11 = 0.9V |                   | 11 = 0.9V         | 0       |  |

<sup>1.</sup> B1[5] must be set to a 1 for these bits to have any effect on the part.

#### SMBus Table: DIF Slew Rate Control Register

| Byte 2 | Name             | Control Function    | Туре | 0      | 1      | Default |  |

|--------|------------------|---------------------|------|--------|--------|---------|--|

| Bit 7  |                  | Reserved            |      |        |        |         |  |

| Bit 6  | SLEWRATESEL DIF3 | Slew Rate Selection | RW   | 2 V/ns | 3 V/ns | 1       |  |

| Bit 5  | SLEWRATESEL DIF2 | Slew Rate Selection | RW   | 2 V/ns | 3 V/ns | 1       |  |

| Bit 4  |                  | Reserved            |      |        |        | 1       |  |

| Bit 3  | SLEWRATESEL DIF1 | Slew Rate Selection | RW   | 2 V/ns | 3 V/ns | 1       |  |

| Bit 2  |                  | Reserved            |      |        |        | 1       |  |

| Bit 1  | SLEWRATESEL DIF0 | Slew Rate Selection | RW   | 2 V/ns | 3 V/ns | 1       |  |

| Bit 0  |                  | Reserved            |      |        |        | 1       |  |

#### SMBus Table: Frequency Select Control Register

| Byte 3 | Name           | Control Function                 | Туре            | 0                                                        | 1              | Default |  |

|--------|----------------|----------------------------------|-----------------|----------------------------------------------------------|----------------|---------|--|

| Bit 7  |                | Reserved                         |                 |                                                          |                |         |  |

| Bit 6  | Reserved       |                                  |                 |                                                          |                | 1       |  |

| Bit 5  | FREQ_SEL_EN    | Enable SW selection of frequency | RW              | SW frequency SW frequency change disabled change enabled |                | 0       |  |

| Bit 4  | FSEL1          | Freq. Select Bit 1               | RW <sup>1</sup> | See Frequency                                            | v Select Table | 0       |  |

| Bit 3  | FSEL0          | Freq. Select Bit 0               | RW <sup>1</sup> | Oce i requerio                                           | y Ociect Table | 0       |  |

| Bit 2  |                | Reserved                         |                 |                                                          |                | 1       |  |

| Bit 1  | Reserved       |                                  |                 |                                                          |                | 1       |  |

| Bit 0  | SLEWRATESEL FB | Adjust Slew Rate of FB           | RW              | 2 V/ns                                                   | 3 V/ns         | 1       |  |

<sup>1.</sup> B3[5] must be set to a 1 for these bits to have any effect on the part.

### Byte 4 is Reserved and reads back 'hFF

### SMBus Table: Revision and Vendor ID Register

| Byte 5 | Name | Control Function | Туре | 0            | 1     | Default |

|--------|------|------------------|------|--------------|-------|---------|

| Bit 7  | RID3 |                  |      |              | 0     |         |

| Bit 6  | RID2 | Revision ID      | R    | A rev = 0000 |       | 0       |

| Bit 5  | RID1 |                  | R    |              |       | 0       |

| Bit 4  | RID0 |                  | R    |              | 0     |         |

| Bit 3  | VID3 |                  | R    |              |       | 0       |

| Bit 2  | VID2 | VENDOR ID        | R    | 0001         | - IDT | 0       |

| Bit 1  | VID1 | VENDORID         | R    | 0001 = IDT   |       | 0       |

| Bit 0  | VID0 |                  | R    |              |       | 1       |

#### SMBus Table: Device Type/Device ID

| Byte 6 | Name         | Control Function | Туре | 0                      | 1                    | Default |  |

|--------|--------------|------------------|------|------------------------|----------------------|---------|--|

| Bit 7  | Device Type1 | Device Type      | R    | 00 = FGV, 01 = DBV,    |                      | 0       |  |

| Bit 6  | Device Type0 | Device Type      | R    | 10 = DMV, 11= Reserved |                      | 1       |  |

| Bit 5  | Device ID5   |                  | R    |                        |                      | 0       |  |

| Bit 4  | Device ID4   |                  | R    |                        |                      |         |  |

| Bit 3  | Device ID3   | Device ID        | R    | 000100 bina            | n, or 04 hey         | 0       |  |

| Bit 2  | Device ID2   | Device ib        | R    | 000100 billa           | 100 binary or 04 hex |         |  |

| Bit 1  | Device ID1   |                  | R    |                        |                      | 0       |  |

| Bit 0  | Device ID0   |                  | R    |                        |                      | 0       |  |

#### SMBus Table: Byte Count Register

| Byte 7 | Name     | Control Function       | Туре | 0                      | 1                     | Default |  |

|--------|----------|------------------------|------|------------------------|-----------------------|---------|--|

| Bit 7  |          | Reserved               |      |                        |                       | 0       |  |

| Bit 6  |          | Reserved               |      |                        |                       |         |  |

| Bit 5  | Reserved |                        |      |                        |                       |         |  |

| Bit 4  | BC4      |                        | RW   |                        |                       | 0       |  |

| Bit 3  | BC3      |                        | RW   | Writing to this regist | er will configure how | 1       |  |

| Bit 2  | BC2      | Byte Count Programming | RW   | many bytes will be i   | read back, default is | 0       |  |

| Bit 1  | BC1      |                        | RW   | = 8 b                  | ytes.                 | 0       |  |

| Bit 0  | BC0      |                        | RW   |                        |                       | 0       |  |

### **Marking Diagrams**

ICS

BV0431AL

YYWW

COO

LOT

#### Notes:

- 1. "LOT" is the lot sequence number.

- 2. "COO" denotes country of origin.

- 3. YYWW is the last two digits of the year and week that the part was assembled.

- 4. Line 2: truncated part number

- 5. "L" denotes RoHS compliant package.

- 6. "I" denotes industrial temperature range device.

### **Thermal Characteristics**

| PARAMETER          | SYMBOL         | CONDITIONS                      | PKG   | TYP<br>VALUE | UNITS | NOTES |

|--------------------|----------------|---------------------------------|-------|--------------|-------|-------|

| Thermal Resistance | $\theta_{JC}$  | Junction to Case                | NLG32 | 42           | °C/W  | 1     |

|                    | $\theta_{Jb}$  | Junction to Base                |       | 2.4          | °C/W  | 1     |

|                    | $\theta_{JA0}$ | Junction to Air, still air      |       | 39           | °C/W  | 1     |

|                    | $\theta_{JA1}$ | Junction to Air, 1 m/s air flow |       | 33           | °C/W  | 1     |

|                    | $\theta_{JA3}$ | Junction to Air, 3 m/s air flow |       | 28           | °C/W  | 1     |

|                    | $\theta_{JA5}$ | Junction to Air, 5 m/s air flow |       | 27           | °C/W  | 1     |

<sup>&</sup>lt;sup>1</sup>ePad soldered to board

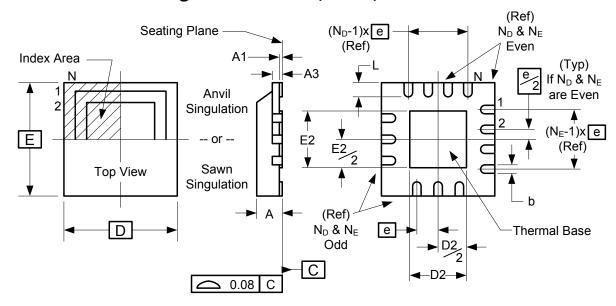

### **Package Outline and Package Dimensions (NLG32)**

|                | Millimeters    |      |  |

|----------------|----------------|------|--|

| Symbol         | Min            | Max  |  |

| Α              | 0.80           | 1.00 |  |

| A1             | 0              | 0.05 |  |

| A3             | 0.20 Reference |      |  |

| b              | 0.18           | 0.3  |  |

| е              | 0.50 BASIC     |      |  |

| D x E BASIC    | 5.00 x 5.00    |      |  |

| D2 MIN./MAX.   | 3.00           | 3.30 |  |

| E2 MIN./MAX.   | 3.00           | 3.30 |  |

| L MIN./MAX.    | 0.30           | 0.50 |  |

| N              | 32             |      |  |

| N <sub>D</sub> | 8              |      |  |

| N <sub>E</sub> | 8              |      |  |

### **Ordering Information**

| Part/Order Number | Shipping Packaging | Package       | Temperature   |  |

|-------------------|--------------------|---------------|---------------|--|

| 9DBV0431AKLF      | Trays              | 32-pin VFQFPN | 0 to +70° C   |  |

| 9DBV0431AKLFT     | Tape and Reel      | 32-pin VFQFPN | 0 to +70° C   |  |

| 9DBV0431AKILF     | Trays              | 32-pin VFQFPN | -40 to +85° C |  |

| 9DBV0431AKILFT    | Tape and Reel      | 32-pin VFQFPN | -40 to +85° C |  |

<sup>&</sup>quot;LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

<sup>&</sup>quot;A" is the device revision designator (will not correlate with the datasheet revision).

# **Revision History**

| Rev. | Initiator | Issue Date | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page #                   |

|------|-----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| A    | RDW       | 8/13/2012  | <ol> <li>Removed "Differential" from DS title and Recommended Application, corrected typo's in Description.</li> <li>Corrected spelling error in pullup/pulldown text under pinout</li> <li>Updated all electrical tables and added "Industry Limit" column to "Phase Jitter Parameters".</li> <li>Updated Byte3[0] to be consistent with Byte 2. Updated Byte6[7:6] definition.</li> <li>Added thermal data to page 12.</li> <li>Added NLG32 to "Package Outline and Package Dimensions" on page 13.</li> <li>Move to final</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1,2,5-<br>8,10,<br>12,13 |

| В    | RDW       | 2/28/2013  | 1. "Input/Supply/Common Parameters" table modified as follows: a. Updated Single-ended input logic thresholds to include missing mid-level on tri-level inputs. Adjusted logic thresholds as follows: i. Changed VIH min. from 0.65*VDD to 0.75*VDD ii. Changed VIL max. from 0.35*VDD to 0.25*VDD iii. Added missing mid-level input voltage spec (VIM) of 0.4*VDD to 0.6*VDD. iv. Clarified conditions for these specifications, accordingly. b. Clarified the operating conditions and voltages of the SMBus to make it clear that the SMBus operates at <3.3V by addition of footnotes 4 and 5 to "Input/Supply/Common Parameters" table. 2. Slight modifications of Slew Rates and typical values in the "DIF 0.7V Low Power Differential Outputs" table. 3. "Current Consumption" table modifed as follows: a. Overall current consumption values lowered b. VDDA is now grouped with VDD1.8 instead of VDDR c. Added separate current specs for PLL bypass mode. d. Clarified that CKPWRDG_PD# is low for power down current. 4. "Output Duty Cycle, Jitter, Skew and PLL Characterisitics" table modifed as follows: a. Bypass mode Input-to-Output skew changed from 3000 to 4500ps to 2550 to 4200ps. Typical value reduced from 3500ps to 3370ps. b. Separate Output-to-Output skew spec added for Industrial temp. c. Additive cycle-to-cycle jitter spec reduced to 1ps max. 5. "Phase Jitter Parameters" modifed as follows: a. Corrected typo in PLL Mode conditions for tjPHSGMII. Frequency integration range is 1.5MHz to 10MHz. Bypass mode conditions were correct. | 5-8                      |

| С    | RDW       | 11/26/2014 | 1. Updated front page text for consistency and updated block diagram resistor colors to highlight internal resistors.  2. Updated max frequency of 100MHz PLL mode from 110MHz to 140MHz  3. Updated max frequency of 125MHz PLL mode from 137.5MHz to 175MHz  4. Updated max frequency of 50MHz PLL mode from 55MHz to 65MHz  5. Updated Key Specifications with additive phase jitter.  6. Added additive phase jitter plot to specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Various                  |

| D    | RDW       | 4/3/2015   | Updated block diagram with new format showing individual outputs instead of bussed outputs.     Updated pin out and pin descriptions to show ePad on package connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-4                      |

| Е    | RDW       | 4/22/2016  | Updated max frequency of 100MHz PLL mode to 140MHz     Updated max frequency of 125MHz PLL mode to 175MHz     Updated max frequency of 50MHz PLL mode to 65MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                        |

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/