# SIR Endec for IrDA® Applications Integrated Interface Circuit

#### **DESCRIPTION**

The TOIM5232 endec IC provides proper pulse shaping for the SIR IrDA front end infrared transceivers as of the 4000-series

For transmitting the TOIM5232 shortens the RS232 output signal to IrDA compatible electrical pulses to drive the infrared transmitter. In the receive mode, the TOIM5232 stretches the received infrared pulses to the proper bit width depending on the operating bit rate. The IrDA bit rate varies from 2.4 kbit/s to 115.2 kbit/s.

The TOIM5232 is using a crystal clock 3.6864 MHz (< 7.5 MHz) for its pulse stretching and shortening. The clock is generated by the internal oscillator. An external clock can be used, too. The TOIM5232 is programmable to operate from 1200 bit/s to 115.2 kbit/s by the communication software through the RS232 port. The output pulses are software programmable as either 1.627  $\mu$ s or 3/16 of bit time. The typical power consumption is very low with about 10 mW in operational state and in the order of a few microwatts in standby mode. TOIM5232 in the tiny QFN-20 package is the space-minimized version of TOIM5232.

**ULC Technology:** High performance gate array package using multiple metal layer CMOS technology featuring sub-micron channel lengths  $(0.35 \mu m)$ .

#### **FEATURES**

Directly interfaces the SIR transceiver to a RS232 port

QFN-20 - package, 4 mm x 4 mm x 0.75 mm

RoHS

- Low operating current

- Programmable baud clock generator (1200 Hz to 115.2 kHz), 13 baud rates

- 3/16 bit pulse duration or 1.627 µs pulse selectable

- For 2.7 V to 3.6 V operation voltage, 5 V tolerant inputs

- Qualified for lead (Pb)-free and Sn/Pb solder processing (MSL3)

- Material categorization: For definitions of compliance please see <a href="https://www.vishay.com/doc?99912"><u>www.vishay.com/doc?99912</u></a>

| PARTS TABLE  |                                |          |

|--------------|--------------------------------|----------|

| PART         | DESCRIPTION                    | QTY/REEL |

| TOIM5232-TR3 | SIR Endec for IrDA application | 6000 pcs |

| PRODUCT SUMMARY |                       |                                           |                      |                             |                                |  |  |  |  |

|-----------------|-----------------------|-------------------------------------------|----------------------|-----------------------------|--------------------------------|--|--|--|--|

| PART NUMBER     | DATA RATE<br>(kbit/s) | DIMENSIONS<br>H x L x W<br>(mm x mm x mm) | LINK DISTANCE<br>(m) | OPERATING<br>VOLTAGE<br>(V) | IDLE SUPPLY<br>CURRENT<br>(mA) |  |  |  |  |

| TOIM5232        | 1.2 to 115            | 4 x 4 x 0.75                              | -                    | 2.7 to 3.6                  | 2                              |  |  |  |  |

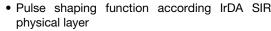

### **BLOCK DIAGRAM**

| PIN NUMBER | SYMBOL             | DISCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O | ACTIVE |

|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|

| 1          | RD_232             | Received signal data output of stretched signal to the RS232 RXD line (using level converter).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0   | High   |

| 2          | TD_232             | Input of the signal to be transmitted from the RS232 port TXD line (passing the level converter).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I   | High   |

| 3          | V <sub>CC_SD</sub> | This pin can be used to shut down a transceiver (e.g., TFDx4xxx).  Output polarity: Inverted RESET input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0   | Low    |

| 4          | X1                 | Crystal input clock, 3.6864 MHz nominal for 9.6 kbit/s default setting. Input for external clock (1). Option: 7.3728 MHz for 19.2 kbit/s default operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I   |        |

| 5          | X2                 | Crystal (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I   |        |

| 7          | GND                | Ground in common with the RS232 port and IrDA transceiver ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |        |

| 9          | TD_LED             | Transmit LED indicator driver. Use 180 $\Omega$ current limiting resistor in series to LED to connect to $V_{CC}$ ( $V_{CC} = 3.3 \text{ V}$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0   | Low    |

| 10         | RD_LED             | Receive LED indicator driver. Use 180 $\Omega$ current limiting resistor in series to LED to connect to V <sub>CC</sub> (V <sub>CC</sub> = 3.3 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0   | Low    |

| 12         | S1                 | User programmable bit. Can be used to turn on/off a front-end infrared transceiver (e.g., an infrared module at the adapter front).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0   | Low    |

| 13         | S2                 | User programmable bit. Can be used to turn on/off a front-end infrared transceiver (e.g., an infrared module at the adapter back).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0   | Low    |

| 14         | TD_IR              | Data output of shortened signal to the infrared transceiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0   | High   |

| 16         | RD_IR              | Data input from the infrared transceiver, min. pulse duration 1.63 µs (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I   | Low    |

| 17         | V <sub>CC</sub>    | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ı   |        |

| 18         | RESET              | Resets all internal registers. Initially must be high ("1") to reset internal registers. When high, the TOIM5232 sets the IrDA default bit rate of 9600 bit/s, sets pulse width to 1.627 µs. The V <sub>CC_SD</sub> output is simply an inverted reset signal which allows shutdown of a TFDx4x00 transceiver when applying the reset signal to the TOIM5232. When using devices with external SD like TFDU4101, the reset line can be used directly as shutdown signal. RESET pin can be controlled by either the RTS or DTR line through RS232 level converter. Minimum hold time for resetting is 1 µs. Disables the oscillator when active.                              |     | High   |

| 19         | BR/D               | Baud rate control/data BR/D = 0, data communication mode: RS232 TXD data line is connected (via a level shifter) to TD_232 input pin. The TXD - signal is appropriately shortened and applied to the output TD_IR, driving the TXD input of the IR transceiver. The RXD line of the transceiver is connected to the RD_IR input. This signal is stretched to the correct bit length according to the programmed bit rate and is routed to the RS232 RXD line at the RD_232 pin. BR/D = 1, programming mode: Data received from the RS232 port is interpreted as control word. The control word programs the baud rate width will be effective as soon as BR/D return to low. |     |        |

### Notes

<sup>(1)</sup> Crystal should be connected as shown in the block diagram or in the recommended application circuit. Connect a 100 k $\Omega$  resistor from pin 4 to pin 5 and from pin 4 and pin 5 a 22 pF capacitor to ground, respectively. When an external clock is available connect it to pin 4 leaving pin 5 open. The external resistor of 100 k $\Omega$  is used to accelerate the start of the oscillation after reset or power-on. The value depends on the "Q" of the resonator. With low Q resonators no resistor is needed. The start-up time of the oscillator is between 30 µs (with piezo resonators) and above 2 ms with high Q quartzes.

<sup>(2)</sup> This condition is fulfilled with all Vishay IR transceivers.

| ABSOLUTE MAXIMUM I              | ABSOLUTE MAXIMUM RATINGS |       |      |                       |      |          |  |  |  |  |  |

|---------------------------------|--------------------------|-------|------|-----------------------|------|----------|--|--|--|--|--|

| PARAMETER                       | SYMBOL                   | MIN.  | TYP. | MAX.                  | UNIT | NOTES    |  |  |  |  |  |

| Supply voltage                  | $V_{CC}$                 | - 0.5 |      | 3.6                   | V    |          |  |  |  |  |  |

| Input voltage                   |                          | - 0.5 |      | 5.5                   | V    | All pins |  |  |  |  |  |

| Output voltage                  |                          | - 0.5 |      | V <sub>CC</sub> + 0.5 | V    | All pins |  |  |  |  |  |

| Output sinking current          | I <sub>OUT</sub>         | 8     |      |                       | mA   | All pins |  |  |  |  |  |

| Junction temperature            | T <sub>J</sub>           |       |      | 125                   | °C   |          |  |  |  |  |  |

| Ambient temperature (operating) | T <sub>amb</sub>         | - 25  |      | 85                    | °C   |          |  |  |  |  |  |

| Storage temperature             | T <sub>stg</sub>         | - 25  |      | 85                    | °C   |          |  |  |  |  |  |

| Soldering temperature           | T <sub>sldr</sub>        |       |      | 260                   | °C   |          |  |  |  |  |  |

| DC CHARACTERISTICS               | DC CHARACTERISTICS                                                                     |                 |               |      |      |      |  |  |  |  |  |

|----------------------------------|----------------------------------------------------------------------------------------|-----------------|---------------|------|------|------|--|--|--|--|--|

| PARAMETER                        | TEST CONDITIONS                                                                        | SYMBOL          | MIN.          | TYP. | MAX. | UNIT |  |  |  |  |  |

| Operating voltage                |                                                                                        | $V_{CC}$        | 2.7           | 3.3  | 3.6  | V    |  |  |  |  |  |

|                                  | $V_{CC} = 3.3 \text{ V} \pm 5 \text{ %, operating to}$                                 | emperature = -  | 25 °C to + 85 | °C   |      |      |  |  |  |  |  |

| Input high voltage               | Inputs tolerate levels as high as 5.5 V maximum. All inputs are Schmitt trigger inputs | V <sub>IH</sub> | 2             |      |      | V    |  |  |  |  |  |

| Input low voltage                |                                                                                        | V <sub>IL</sub> |               |      | 0.8  | V    |  |  |  |  |  |

| Input Schmitt trigger hysteresis |                                                                                        | $V_{hyst}$      |               | 0.6  |      | V    |  |  |  |  |  |

| Input leakage no pull-up/down    | V <sub>IN</sub> = V <sub>CC</sub> or GND                                               | ΙL              | - 10          | ± 1  | 10   | μΑ   |  |  |  |  |  |

| Output high voltage              | I <sub>OH</sub> = - 2 mA                                                               | $V_{OH}$        | 2             |      |      | V    |  |  |  |  |  |

| Output high voltage              | I <sub>OH</sub> = - 0.5 mA                                                             | V <sub>OH</sub> | 2.4           |      |      | V    |  |  |  |  |  |

| Output low voltage               | I <sub>OL</sub> = + 2 mA                                                               | V <sub>OL</sub> |               |      | 0.4  | V    |  |  |  |  |  |

| Consumption current standby      | Inputs grounded, no output load V <sub>CC</sub> = 3.3 V, T = 25 °C                     | I <sub>SB</sub> |               |      | 1    | μΑ   |  |  |  |  |  |

| Consumption current dynamic      | Inputs grounded, no output load V <sub>CC</sub> = 3.3 V, T = 25 °C                     | I <sub>CC</sub> |               | 2    |      | mA   |  |  |  |  |  |

#### **OPERATION DESCRIPTION**

The block diagram shows a typical example of an RS232 port interface. The TOIM5232 connects to an RS232 level converter on one side, and an infrared transceiver on the other. The internal TOIM5232 baud rate generator can be software controlled.

When BR/D = 0, the TOIM5232 interprets the channels TD\_232 to TD\_IR and RD\_IR to RD\_232 as data channels. On the other hand, whenever BR/D = 1, the TOIM5232 interprets TD\_232 as control word for setting the baud rate. The baud rate can be programmed to operate from 1200 bit/s to 115.2 kbit/s. As RS232 level converter, EIA232 or MAX232 or equivalent are recommended.

When using the TOIM5232 directly connected to an UART it is compatible to 5 V TTL and 3.3 V CMOS logic.

Typical external resistors and capacitors are needed as shown in the TFDU4...,TFBS4...-series references.

The output pulse duration can also be programmed, see chapter "operation description". It is strongly recommended using 1.627 µs output pulses to save battery power. As frequency determining component a Vishay XT49M crystal is recommended, when no external clock is available.

We strongly recommend not to use this 3/16 mode because 3/16 pulse length at lower bit rates consumes more power than the shorter pulse. At a data rate of 9600 bit/s, the ratio of power consumption of both modes is a factor of 12 (!)

### **PROGRAMMING THE TOIM5232**

For correct data rate dependent timing the TOIM5232 is using a built-in baud rate generator. This is used when no external clock is not available as in RS232 IR-dongle applications. For programming the BR/D pin has to be set active, BR/D = 1.

In this case the TOIM5232 interprets the 7 LSBs at the TD\_232 input as a control word. The operating baud rate will change to its supposedly new baud rate when the BR/D returns back to low ("0") set the UART to 8 bit, no parity, 1 stop bit.

### www.vishay.com

# Vishay Semiconductors

| CON | CONTROL BYTE (8 BIT) |    |    |    |                  |    |    |  |  |  |  |

|-----|----------------------|----|----|----|------------------|----|----|--|--|--|--|

| FI  | FIRST CHARACTER      |    |    |    | SECOND CHARACTER |    |    |  |  |  |  |

| Х   | S2                   | S1 | S0 | В3 | B2               | B1 | В0 |  |  |  |  |

|     | LSB                  |    |    |    |                  |    |    |  |  |  |  |

X: do not care

S1, S2: user programmable bit to program the outputs S1 and S2

S0: IrDA pulse select

S0 = (1): 1.627 µs output pulses

S0 = (0): 3/16 bit time pulses, not recommended

B0 to B3: baud rate select words according following table.

Example:

To set TOIM5232 at COM2 port (2F8) to 9600 bit/s with 3/16 bit time pulse duration send to the TOIM5232 in programming mode in e.g. "basic"

**OUT &H2F8, (&H6)**

For same port, 9600 bit/s and 1.627 µs pulse duration send

OUT &H2F8, (&H16)

For additionally activating S1 send

**OUT &H2F8, (&H36)**

| BAU | RATE | SELE | CT WO | RDS                     |           |

|-----|------|------|-------|-------------------------|-----------|

| В3  | B2   | B1   | В0    | 2 <sup>nd</sup><br>CHAR | BAUD RATE |

| 0   | 0    | 0    | 0     | 0                       | 115.2 kHz |

| 0   | 0    | 0    | 1     | 1                       | 57.6 kHz  |

| 0   | 0    | 1    | 0     | 2                       | 38.4 kHz  |

| 0   | 0    | 1    | 1     | 3                       | 19.2 kHz  |

| 0   | 1    | 0    | 0     | 4                       | 14.4 kHz  |

| 0   | 1    | 0    | 1     | 5                       | 12.8 kHz  |

| 0   | 1    | 1    | 0     | 6                       | 9.6 kHz   |

| 0   | 1    | 1    | 1     | 7                       | 7.2 kHz   |

| 1   | 0    | 0    | 0     | 8                       | 4.8 kHz   |

| 1   | 0    | 0    | 1     | 9                       | 3.6 kHz   |

| 1   | 0    | 1    | 0     | Α                       | 2.4 kHz   |

| 1   | 0    | 1    | 1     | В                       | 1.8 kHz   |

| 1   | 1    | 0    | 0     | С                       | 1.2 kHz   |

#### Note

IrDA standard only supports 2.4 kbit/s, 9.6 kbit/s, 19.2 kbit/s, 57.6 kbit/s, and 115.2 kbit/s (3.6864 MHz clock). Doubling the baud rates is allowed by doubling the clock frequency.

#### SOFTWARE FOR THE TOIM4232 AND TOIM5232 UART PROGRAMMING

For proper operation, the RS232 must be programmed (using 8 bit, 1 stop, no parity) to send a two character control word, YZ. The control word YZ is composed of two characters, written in hexadecimal, in format: YZ. The transfer rate for programming must be identical with the formerly programmed data rate, or after resetting the TOIM5232, the default rate of 9600 bit/s is used.

| STEP. | RESET | BR/D | TD_UART                                                   | RD_UART | RD_IR | TD_IR | DESCRIPTION AND COMMENTS                                                                                                                                                                                                                                               |

|-------|-------|------|-----------------------------------------------------------|---------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | High  | Х    | Х                                                         | Х       | Х     | Х     | Resets all internal registers. Resets to IrDA default data rate of 9600 bit/s                                                                                                                                                                                          |

| 2     | Low   | Х    | Х                                                         | Х       | Х     | Х     | Wait at least 2 ms, to allow start-up of internal clock. When external clock is used: wait at least 7 µs.                                                                                                                                                              |

| 3     | Low   | High | Х                                                         | Х       | Х     | Х     | Wait at least 7 µs. TOIM5232 now is set to the control word programming mode                                                                                                                                                                                           |

| 4     | Low   | High | YZ<br>with Y = 1:<br>1.627 µs<br>Y = 0<br>3/16 bit length | x       | Х     | x     | Sending the control word YZ. Examples: Send "1Z" if 1.627 µs pulses are intended to be used. Otherwise send "0Z" for 3/16 bit period pulses. "Y6" keeps the 9.6 kbit/s data rate. Z = 0 sets to 115.2 kbit/s, see programming table. Wait at least 1 µs for hold-time. |

| 5     | Low   | Low  | Data                                                      | Data    | Data  | Data  | With BR/D = 0, TOIM5232 is in the data communication mode. Both RESET and BR/D must be kept low ("0") during data transmission. Reprogramming to a new data rate can be resumed by restarting from step 3. The UART itself also must set to the correct data rate (1). |

#### Note

- It is recommended reading the I/O buffer after transmission waiting the specified latency allowance. That avoids receiving unexpected data from pulses stochastically generated by many transceivers during the latency time.

- (1) For programming the UART, refer to e.g., National Semiconductors datasheet of PC 16550 UART.

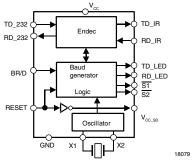

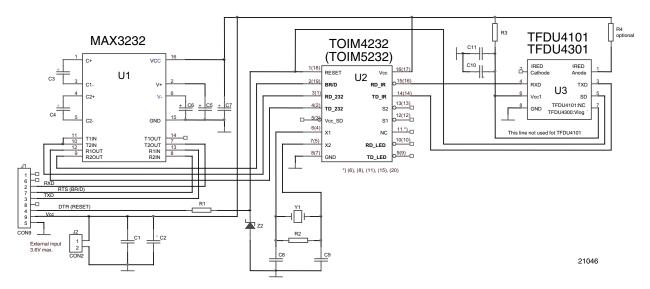

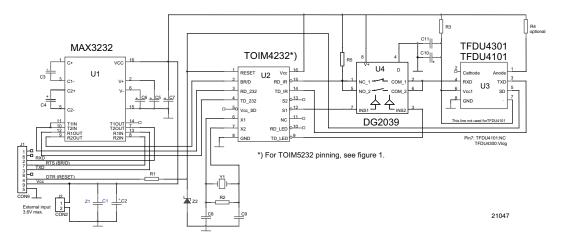

### **RECOMMENDED APPLICATION CIRCUIT FOR TOIM5232**

Application circuit using TFDU4301 with integrated level shifter MAX3232CSE. When used directly with 3 V - or 5 V - logic, the level shifter can be omitted.

| C   | OMPONENT | RECOMMENDED VALUE                      | VISHAY PART NUMBER     |  |

|-----|----------|----------------------------------------|------------------------|--|

| 1.  | C1       | 100 nF                                 | VJ 1206 Y 104 J XXMT   |  |

| 2.  | C2       | 10 μF, 16 V                            | 293D 106X9 016B 2T     |  |

| 3.  | C3       | 100 nF                                 | VJ 1206 Y 104 J XXMT   |  |

| 4.  | C4       | 100 nF                                 | VJ 1206 Y 104 J XXMT   |  |

| 5.  | C5       | 100 nF                                 | VJ 1206 Y 104 J XXMT   |  |

| 6.  | C6       | 100 nF                                 | VJ 1206 Y 104 J XXMT   |  |

| 7.  | C7       | 1 μF, 16 V                             | 293D 105X9 016A 2T     |  |

| 8.  | C8       | 22 pF                                  | VJ 1206 A 220 J XAMT   |  |

| 9.  | C9       | 22 pF                                  | VJ 1206 A 220 J XAMT   |  |

| 10. | C10      | 6.8 µF, 16 V (optional)                | 293D 685X9 016B 2T     |  |

| 11. | C11      | 100 nF                                 | VJ 1206 Y 104 J XXMT   |  |

| 12. | Z1       | 3.6 V                                  | BZT55C3V6              |  |

| 13. | Z2       | 3.6 V                                  | BZT55C3V6              |  |

| 14. | R1       | 5.6 kΩ                                 | CRCW-1206-5601-F-RT1   |  |

| 15. | R2       | 100 kΩ                                 | CRCW-1206-1003-F-RT1   |  |

| 16. | R3       | 47 Ω                                   | CRCW-1206-47R0-F-RT1   |  |

| 17. | R4       | 27 $\Omega$ (for reduced current only) | CRCW-1206-27R0-F-RT1   |  |

| 18. | Y1       | 3.686400 MHz                           | XT49S - 20 - 3.686400M |  |

| 19. | U1       | MAX 3232CSE                            | MAXIM MAX 3232CSE      |  |

| 20. | U2       |                                        | TOIM5232               |  |

| 21. | U3       |                                        | TFDU4301               |  |

| 22. | J1       | 9 pin - connector                      | Cannon                 |  |

| 23. | J2       | Power connector                        | Philmore PHI 211B      |  |

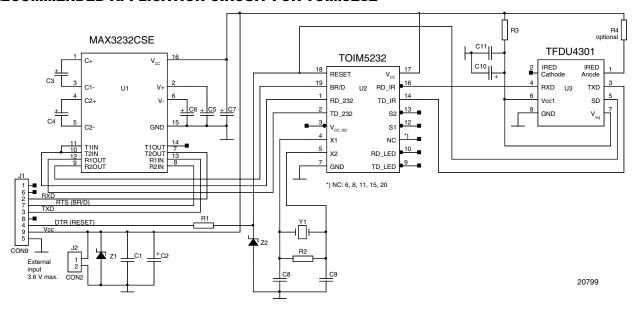

### **PACKAGE DIMENSIONS** in millimeters

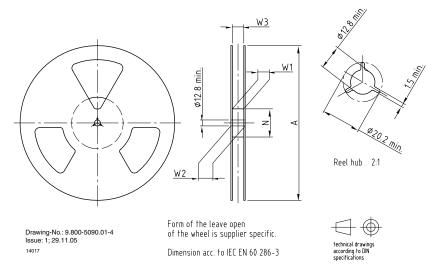

### **REEL DIMENSIONS** in millimeters

| TAPE WIDTH | A MAX. | N    | W <sub>1</sub> MIN. | W <sub>2</sub> MAX. | W <sub>3</sub> MIN. | W <sub>3</sub> MAX. |

|------------|--------|------|---------------------|---------------------|---------------------|---------------------|

| (mm)       | (mm)   | (mm) | (mm)                | (mm)                | (mm)                | (mm)                |

| 12         | 330    | 50   | 12.4                | 22.4                | 11.9                | 15.4                |

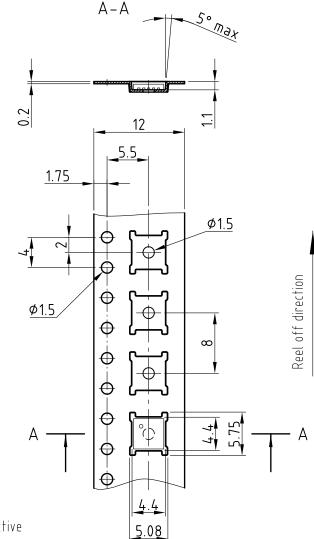

### **TAPE DIMENSIONS** in millimeters

Material of Blistertape: PC Spezialtype ITF , conductive

Drawing-No.: 9.700-5327.01-4

Issue: 1; 13.07.07

20798

technical drawings according to DIN specifications

# TOIM4232 (TOIM5232) ENCODER - DECODER INTERFACE PROGRAMMING AND DATA TRANSMISSION

Operation and programming of the TOIM4232 and TOIM5232 interface devices are described below. Figure 1 shows the basic circuit design with 3 blocks: the RS232 to 3 V logic level shifter, the encoder/decoder (endec) circuit and the transceiver to build a dongle for RS232 IrDA

extension. U1 is the level shifter to convert the RS232 logic levels to unipolar 3 V logic; U2 is the encoder/decoder Interface (endec) converting the NRZ - RS232 logic to IrDA RZI - logic. The transceiver U3 transmits and receives IrDA-compliant optical signals.

Fig. 1 - Circuit Diagram of the Demo Board

#### CIRCUIT DESCRIPTION

This circuit demonstrates the operation of an SIR IrDA transceiver module. The transceiver U3 (e.g., as shown the TFDU4101 or TFDU4301 or any other) converts the digital electrical input signal to an optical output signal to be transmitted, receives the optical signal, and converts these to electrical digital signals. While the IrDA physical layer protocol transmits only the "0" represented by a pulse with a "Return to Zero Inverted (RZI)" logic, the RS232 protocol needs a "No Return to Zero (NRZ)" representation. This decoding/encoding process is done by U2, an interface circuit stretching the received pulses and shortening the pulses to be transmitted according to the IrDA physical layer conditions. U1 interfaces the RS232 logic bipolar levels to the 3 V logic of the Endec U2. The board is connected by CON9 to the RS232 port (of a computer or other equipment. The basic IrDA transmission speed is 9600 bit/s. This is the default state of the Endec in power-on condition. Also, activating the reset line at pin 1 (18) will set the device to this basic state.

Note: The first pin number refers to TOIM4232; the second number in brackets refers to TOIM5232. The crystal Y1 controls the timing of the Endec as a clock reference. The outputs S1 and S2 are programmable outputs for control operations and the outputs RD\_LED and TD\_LED can drive LEDs for indicating data flow.

#### PROGRAMMING THE ENDEC

For decoding data rates other than the default, the endec is to be programmed to set the internal counters and timers. To switch the endec from the data transfer mode to the bit rate programming mode, the input BR/D, pin 2 (19) is set active high (BR/D = "1"). In this case the TOIM5232 interprets the 7 LSBs at the TD\_232 input as a control word. The operating bit rate will change to its supposedly new rate when the BR/D returns back to low ("0"). Set the UART to 8 bit, no parity, 1 stop bit.

The control byte consists of 8 bit after the start bit (STA, which is "0"). Keep in mind that the order is LSB first, MSB last

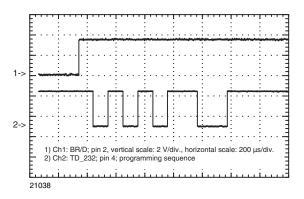

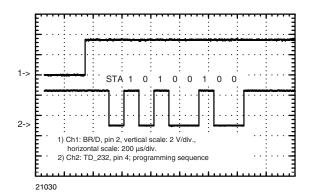

The diagram in figure 2 shows the programming byte "0-1010-1100" in the order STA, B0, B1, B2, B3, S0, S1, S2, X. This order is from right to left in table 1. B0 is sent first as LSB (see figure 2).

The four least significant bits are responsible for the data rate according to table 2 while the four higher bits are for setting the IrDA pulse duration (S0), and the two outputs of the endec S1 and S2. Bit 8 is not used.

### www.vishay.com

# Vishay Semiconductors

| TABLE 1 - CONTROL BYTE (8 BIT) |                              |        |       |                      |     |       |         |        |  |  |

|--------------------------------|------------------------------|--------|-------|----------------------|-----|-------|---------|--------|--|--|

| FIF                            | FIRST CHARACTER SECOND CHARA |        |       |                      |     |       |         | STA    |  |  |

| Χ                              | S2                           | S1     | S0    | В3                   | B2  | B1    | B0      | 0      |  |  |

| MSB                            |                              |        |       |                      |     |       | LSB     |        |  |  |

|                                | Example                      |        |       |                      |     |       |         |        |  |  |

| 0                              | 0                            | 1      | 1     | 0                    | 1   | 0     | 1       | 0      |  |  |

| In the                         | oscillo                      |        |       | be show<br>st, see f |     |       | ed orde | r with |  |  |

| STA                            | FIF                          | RST CH | ARACT | ER                   | SEC | OND C | HARAC   | TER    |  |  |

| 0                              | B0                           | B1     | B2    | В3                   | S0  | S1    | S2      | Χ      |  |  |

|                                | LSB                          |        |       |                      |     |       |         | MSB    |  |  |

|                                | Example                      |        |       |                      |     |       |         |        |  |  |

| 0                              | 1                            | 0      | 1     | 0                    | 1   | 1     | 0       | 0      |  |  |

#### Note

X: do not care

S1, S2: user-programmable bit to program the outputs S1 and S2. In the example, S1 is set active, and S2 is inactive.

S0: IrDA pulse select

S0 = (1): 1.627  $\mu$ s output S0 = (0): 3/16 bit time pulses, not recommended

B0 to B3: baud rate select words according to the following table below.

|    | TABLE 2 - TRANSMISSION RATE SELECT WORDS |    |    |     |                  |  |  |  |  |  |  |

|----|------------------------------------------|----|----|-----|------------------|--|--|--|--|--|--|

| В3 | B2                                       | B1 | B1 | HEX | BIT RATE         |  |  |  |  |  |  |

| 0  | 0                                        | 0  | 0  | 0   | 115.2 kHz        |  |  |  |  |  |  |

| 0  | 0                                        | 0  | 1  | 1   | 57.6 kHz         |  |  |  |  |  |  |

| 0  | 0                                        | 1  | 0  | 2   | 38.4 kHz         |  |  |  |  |  |  |

| 0  | 0                                        | 1  | 1  | 3   | 19.2 kHz         |  |  |  |  |  |  |

| 0  | 1                                        | 0  | 0  | 4   | 14.4 kHz         |  |  |  |  |  |  |

| 0  | 1                                        | 0  | 1  | 5   | <b>12.8 k</b> Hz |  |  |  |  |  |  |

| 0  | 1                                        | 1  | 0  | 6   | 9.6 kHz          |  |  |  |  |  |  |

| 0  | 1                                        | 1  | 1  | 7   | 7.2 kHz          |  |  |  |  |  |  |

| 1  | 0                                        | 0  | 0  | 8   | 4.8 kHz          |  |  |  |  |  |  |

| 1  | 0                                        | 0  | 1  | 9   | 3.6 kHz          |  |  |  |  |  |  |

| 1  | 0                                        | 1  | 0  | Α   | 2.4 kHz          |  |  |  |  |  |  |

| 1  | 0                                        | 1  | 1  | В   | 1.8 kHz          |  |  |  |  |  |  |

| 1  | 1                                        | 0  | 0  | С   | 1.2 kHz          |  |  |  |  |  |  |

#### **Notes**

Bold: See example

IrDA standard only supports 2.4 kbit/s, 9.6 kbit/s, 19.2 kbit/s, 57.6 kbit/s, and 115.2 kbit/s (3.6864 MHz clock). Doubling the baud rates is permissible by doubling the clock frequency.

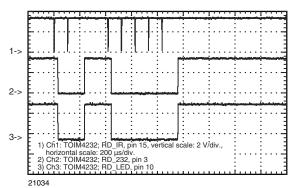

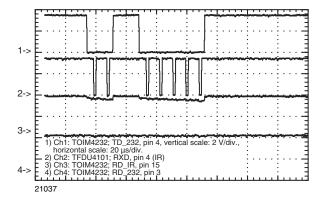

In figure 2 the programming sequence is shown for a bit rate of 12.8 kbit/s.

Fig. 2 - Programming sequence for setting the endec to a bit rate of 12.8 kbit/s. After setting BR/D high (Ch1), the programming sequence with the control byte (Ch2) is applied to TD\_232, pin 4.

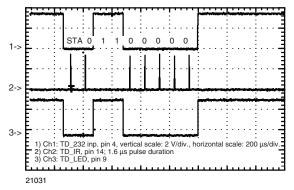

Fig. 3 - Programming sequence for setting the endec to a bit rate of 12.8 kbit/s as in figure 2 but with a 3/16 bit pulse duration (S0 = "0").

| Example |   |   |   |   |   |   |     |     |

|---------|---|---|---|---|---|---|-----|-----|

| 0       | 0 | 1 | 0 | 0 | 1 | 0 | 1   | 0   |

| MSB     |   |   |   |   |   |   | LSB | STA |

When correctly programmed, the endec shortens the pulse to be transmitted from the full bit duration to either 3/16 of the bit length or to 1.627 µs (which is 3/16 of the 115.2 kbit/s bit duration). For power saving, the short pulse is

The received optical pulse shows in case of most of the Vishay SIR transceivers, constant pulse duration. The endec stretches that to the correct bit time according the bit rate setting. This is shown in the following chapters.

### TRANSMIT (TXD) CHANNEL

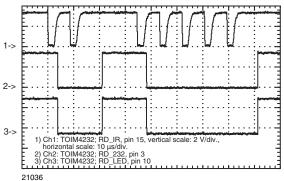

Figure 4 shows the transmission in the default mode. For data transfer, the endec is set to that mode by BR/D = "0". In the examples "6" is always transmitted (binary "00000110"). The "0" is represented in the IrDA protocol by an optical pulse. Also here the LSB is transmitted first after the start bit. "1" is not transmitted.

Fig. 4 - Data transmission with 9.6 kbit/s,1.627 µs pulse duration Channel 1 shows the signal from the RS232 port already converted to 3 V logic by U1. The Endec encodes that signal to the RZI IrDA format where a "0" is represented by a pulse. That is the trace of channel 2. This output is connected the TXD input of the transceiver and this signal is transmitted as optical output signal. Channel 3 is the signal for an indicator lamp connected to the TD\_LED driver output. Use 180  $\Omega$  serial resistor to supply voltage for limiting the current through the LED (not shown in the circuit diagram).

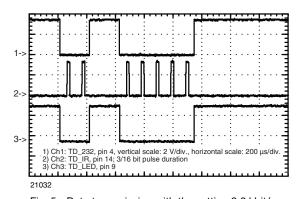

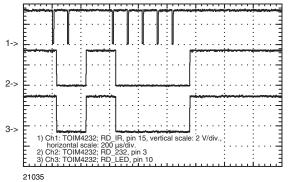

When using the (not recommended) 3/16-bit pulse width the oscillogram looks like figure 5.

Fig. 5 - Data transmission with the setting 9.6 kbit/s, 3/16 bit pulse duration (19.5  $\mu$ s)

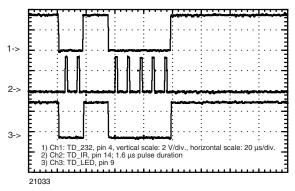

The transmission with the highest SIR bit rate of 115.2 bit/s looks like what is shown in figure 6. However, the horizontal time scale is different.

Fig. 6 - Data transmission with the setting 115.2 kbit/s, 1.627  $\mu$ s pulse duration. By definition, the pulse duration of 1.627  $\mu$ s is identical to the 3/16-bit pulse width.

### RECEIVE (RXD) CHANNEL

In the default 9600 bit/s mode the signals will look like those shown in figure 7 and figure 8.

Fig. 7 - Data reception with the setting 9.6 kbit/s. Short RXD pulse

Fig. 8 - Data reception with the setting 9.6 kbit/s. Same as in figure 7, extended pulse duration

The endec stretches the received pulses of about 2  $\mu$ s duration from the transceiver output (figure 7, channel 1) independent of the pulse duration to the full bit width generating NRZ code (channel 2). Channel 3 is the signal for the indicator lamp.

As shown in figure 8, channels 2 and 3, the final NRZ signal is identical to figure 7, even when longer pulses are received. In the 115.2 kbit/s mode the signals will look like those shown

in figure 7 and figure 8. The difference is just the time scale. It also indicates the delay of the decoded channel 2 vs. channel 1.

Fig. 9 - Data reception with the setting 115.2 kbit/s

Channel 1 shows the signal from the transceiver. In this case it is TFDU4101 with unsymmetrical switching times. TFDU4101 is using tri-state outputs with push-pull drivers with symmetrical pulse switching times. All Vishay IrDA transceivers exhibit constant output pulse duration in SIR mode of about 2  $\mu s$  independent of the duration of the optical input pulse.

#### "ECHO-ON" OR "ECHO-OFF" AND "LATENCY ALLOWANCE"

During transmission, the receiver inside a transceiver package is exposed to very strong irradiance of the transmitter, which causes overload conditions in the receiver circuit. After transmission it takes some time to recover from this condition and return to the specified sensitivity.

During this time the receiver is in an unstable condition, and at the output unexpected signals may arise. Also, during transmission under overload conditions the receiver may show signals on the RXD channel that are similar to or identical with the transmitted signal. To get clean or at least specified conditions for the receive channel during transmission, different terms were defined. The time to allow the receiver to recover from overload conditions is the latency allowance or shorter, just the specified latency. This is covered by the IrDA physical layer specification and is a maximum of 10 ms. IrDA specifies shorter negotiable latency. In SIR the minimum is 0.5 ms. This includes software latency. Transceivers are in general below 0.3 ms. In the first generations, some suppliers did not care for the behavior of the RXD output of the transceivers during transmission and latency time. The software is able to

handle that. The easiest way is to clean up the receiver channel after sending the last pulse and waiting for the latency period.

Later, many transceivers that block the RXD channel during transmission and during the latency period were released to the market. This behavior is called "Echo-off". Unfortunately, some OEMs like to use the signal from the RXD channel during transmission, as a self-test feature for testing the device on board without using the optical domain. Therefore, many new devices have been developed to echo the TXD input signal at the RXD output. Such behavior is called "echo-on".

Some software developed for "echo-off" applications is not able to receive and understand the signals from echo-on devices correctly.

Therefore, an add-on to the circuit shown in figure 1 was generated to suppress the echo from the receiver during transmission. This modification is shown in figure 10.

During transmission, the signal from the RXD output of the transceiver is just gated by the transmit signal, (see the oscilloscope picture in figure 11).

Fig. 10 - Demo Board Circuit with Echo-Suppression to be Used for Echo-On and Echo-Off Transceivers.

www.vishay.com

# Vishay Semiconductors

Additionally, with the programmable output S1 of the endec the echo suppression feature can be switched on and off for testing. The default mode is echo-off. To enable the echo, S1 is to be set inactive/low. (See the chapter for programming the TOIM4232, TOIM5232).

The oscilloscope diagrams are shown in figure 11. Channel 2 shows the echo signal on the RXD output of the TFDU4101 transceiver during transmission.

Channel 1 is the signal used for gating the path from the transceiver RXD output to the endec. On channel 3 the signal at the input of the endec is shown with a residual signal. Finally, the output to the RS232 port, RD\_232, is clean without any noise signal.

Fig. 11 - Echo-Suppression

# **Legal Disclaimer Notice**

Vishay

# **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

# **Material Category Policy**

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.

Revision: 02-Oct-12 Document Number: 91000