### **HIGHLIGHTS**

This section of the manual contains the following major topics:

| 23.1  | Introduction                       | 23-2   |

|-------|------------------------------------|--------|

| 23.2  | Control Register                   | 23-3   |

| 23.3  | Operation                          |        |

| 23.4  | A/D Acquisition Requirements       | ∖23-6  |

| 23.5  | Selecting the A/D Conversion Clock | \23-8  |

|       | Configuring Analog Port Pins       | 23-9   |

| 23.7  | A/D Conversions                    | 23-10  |

| 23.8  | Operation During Sleep             | 23ॅ-14 |

| 23.9  | Effects of a Reset                 | 23-14  |

|       | A/D Accuracy/Error                 | 23-15  |

| 23.11 | Connection Considerations          | 23-16  |

|       | ? Transfer Function                | 23-16  |

| 23.13 | 3 Initialization                   | 23-17  |

| 23.14 | Design Tips                        | 23-18  |

|       | Related Application Notes          | 23-19  |

| 23.16 | Revision History                   | 23-20  |

|       |                                    |        |

Note 1: At present NO released mid range MCU devices are available with this module.

Devices are planned, but there is no schedule for availability. Please refer to Microchip's Web site or BBS for release of Product Briefs which detail the features of devices.

If your current design requires a 10-bit A/D, please look at the PIC17C756 which has a 12-channel 10-bit A/D. This A/D has characteristics which are identical to this module's description.

#### 23.1 Introduction

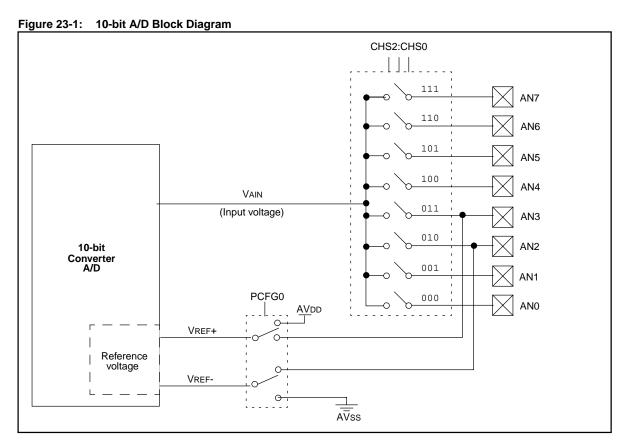

The analog-to-digital (A/D) converter module can have up to eight analog inputs for a device.

The analog input charges a sample and hold capacitor. The output of the sample and hold capacitor is the input into the converter. The converter then generates a digital result of this analog level via successive approximation. This A/D conversion, of the analog input signal, results in a corresponding 10-bit digital number.

The analog reference voltages (positive and negative supply) are software selectable to either the device's supply voltages (AVDD, AVss) or the voltage level on the AN3/VREF+ and AN2/VREF-pins.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode.

The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register0 (ADCON0)

- A/D Control Register1 (ADCON1)

The ADCON0 register, shown in Figure 23-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 23-2, configures the functions of the port pins. The port pins can be configured as analog inputs (AN3 and AN2 can also be the voltage references) or as digital I/O.

### 23.2 Control Register

### Register 23-1: ADCON0 Register

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | _   | ADON  |

| bit 7 |       |       |       |       |         |     | bit 0 |

bit 7:6 ADCS1:ADCS0: A/D Conversion Clock Select bits

00 = Fosc/2

01 = Fosc/8

10 = Fosc/32

11 = FRC (clock derived from the internal A/D RC oscillator)

bit 5:3 CHS2:CHS0: Analog Channel Select bits

000 = channel 0, (AN0)

001 = channel 1, (AN1)

010 = channel 2, (AN2)

011 = channel 3, (AN3)

100 = channel 4, (AN4)

101 = channel 5, (AN5)

110 = channel 6, (AN6)

111 = channel 7, (AN7)

**Note:** For devices that do not implement the full 8 A/D channels, the unimplemented selections are reserved. Do not select any unimplemented channel.

bit 2 GO/DONE: A/D Conversion Status bit

#### When ADON = 1

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion which is automatically cleared by hardware when the A/D conversion is complete)

- 0 = A/D conversion not in progress

- bit 1 Unimplemented: Read as '0'

- bit 0 ADON: A/D On bit

- 1 = A/D converter module is powered up

- 0 = A/D converter module is shut off and consumes no operating current

#### Legend

R = Readable bit W = Writable bit

U = Unimplemented bit, read as '0' - n = Value at POR reset

### Register 23-2: ADCON1 Register

|   | U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---|-------|-----|-------|-----|-------|-------|-------|-------|

|   | _     | _   | ADFM  | _   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| ŀ | nit 7 | •   | •     | •   | •     | •     | •     | hit 0 |

bit 7:6 Unimplemented: Read as '0'

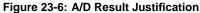

bit 5 ADFM: A/D Result format select (also see Figure 23-6).

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'. 0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

bit 4 Unimplemented: Read as '0'

bit 3:0 PCFG3:PCFG0: A/D Port Configuration Control bits

| PCFG | AN7 | AN6 | AN5 | AN4 | AN3   | AN2   | AN1 | AN0 | VREF+ | VREF- | C/R   |

|------|-----|-----|-----|-----|-------|-------|-----|-----|-------|-------|-------|

| 0000 | Α   | Α   | Α   | Α   | Α     | Α     | Α   | Α   | AVDD  | AVss  | 8/0   |

| 0001 | Α   | Α   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | AVss  | 7/1   |

| 0010 | D   | D   | D   | Α   | Α     | Α     | Α   | Α   | AVDD  | AVss  | 5/0   |

| 0011 | D   | D   | D   | Α   | VREF+ | Α     | Α   | Α   | AN3   | AVss  | 4 / 1 |

| 0100 | D   | D   | D   | D   | Α     | D     | Α   | Α   | AVDD  | AVss  | 3/0   |

| 0101 | D   | D   | D   | D   | VREF+ | D     | Α   | Α   | AN3   | AVss  | 2/1   |

| 011x | D   | D   | D   | D   | D     | D     | D   | D   |       |       | 0/0   |

| 1000 | Α   | Α   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 6/2   |

| 1001 | D   | D   | Α   | Α   | Α     | Α     | Α   | Α   | AVDD  | AVss  | 6/0   |

| 1010 | D   | D   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | AVss  | 5/1   |

| 1011 | D   | D   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 4/2   |

| 1100 | D   | D   | D   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 3/2   |

| 1101 | D   | D   | D   | D   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 2/2   |

| 1110 | D   | D   | D   | D   | D     | D     | D   | Α   | AVDD  | AVss  | 1/0   |

| 1111 | D   | D   | D   | D   | VREF+ | VREF- | D   | Α   | AN3   | AN2   | 1/2   |

A = Analog input D = Digital I/O

C/R = # of analog input channels / # of A/D voltage references

Legend

R = Readable bit W = Writable bit

U = Unimplemented bit, read as '0' - n = Value at POR reset

**Note 1:** On any device reset, the port pins that are multiplexed with analog functions (ANx) are forced to be an analog input.

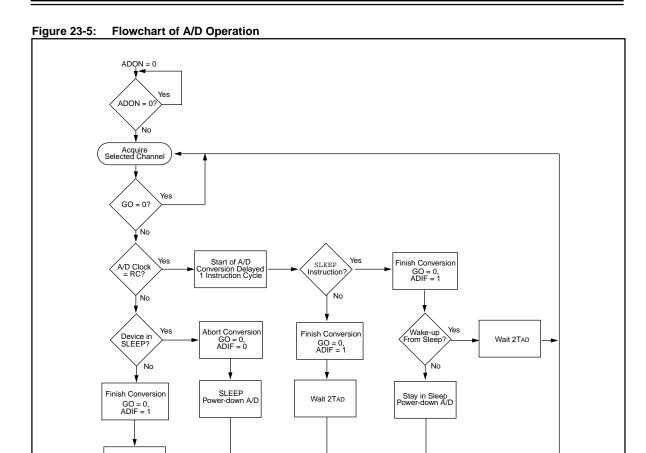

### 23.3 Operation

The ADRESH:ADRESL registers contains the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit, ADIF, is set. The block diagrams of the A/D module are shown in Figure 23-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine sample time, see Subsection 23.4 "A/D Acquisition Requirements." After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference/ and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear the ADIF bit

- · Set the ADIE bit

- · Set the GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set the GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared or ADIF bit to be set

- OF

- Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear the ADIF bit, if required.

- 7. For next conversion, go to step 1 or step 2 as required.

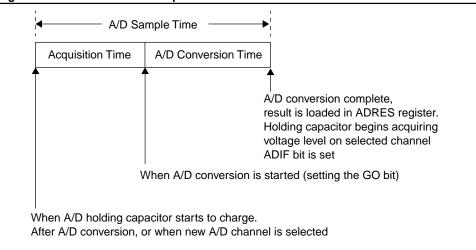

Figure 23-2 shows the conversion sequence, and the terms that are used. Acquisition time is the time that the A/D module's holding capacitor is connected to the external voltage level. Then there is the conversion time of 12 TAD, which is started when the GO bit is set. The sum of these two times is the sampling time. There is a minimum acquisition time to ensure that the holding capacitor is charged to a level that will give the desired accuracy for the A/D conversion.

Figure 23-2: A/D Conversion Sequence

### 23.4 A/D Acquisition Requirements

VHOLD

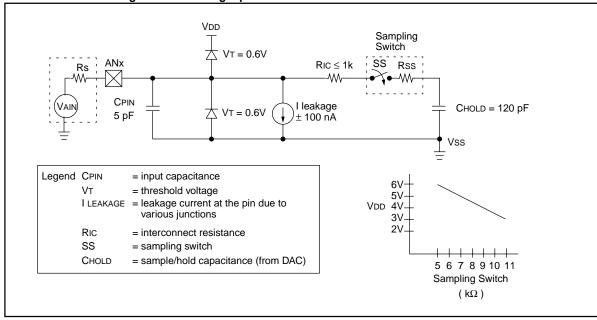

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 23-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 23-3. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 23-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

#### Equation 23-1: Acquisition Time

```

TACQ = Amplifier Settling Time +

Holding Capacitor Charging Time +

Temperature Coefficient

= TAMP + TC + TCOFF

```

### Equation 23-2: A/D Minimum Charging Time

```

\begin{array}{lll} V\text{HOLD} & = & (V\text{REF} - (V\text{REF}/2048)) \bullet (1 - e^{(-\text{Tc/CHOLD}(R\text{IC} + R\text{SS} + R\text{S}))}) \\ \text{or} \\ \text{Tc} & = & -(120 \text{ pF})(1 \text{ k}\Omega + R\text{SS} + R\text{S}) \ln(1/2047) \end{array}

```

Example 23-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following application system assumptions.

```

\begin{array}{lll} \text{CHOLD} & = & 120 \text{ pF} \\ \text{Rs} & = & 10 \text{ k}\Omega \\ \text{Conversion Error} & \leq & 1/2 \text{ LSb} \\ \text{VDD} & = & 5\text{V} \rightarrow \text{Rss} = 7 \text{ k}\Omega & \text{(see graph in Figure 23-3)} \\ \text{Temperature} & = & 50^{\circ}\text{C (system max.)} \end{array}

```

0V @ time = 0

### Example 23-1: Calculating the Minimum Required Acquisition Time (Case 1)

```

Tacq = Tamp + Tc + Tcoff

Temperature coefficient is only required for temperatures > 25°C.

Tacq = 2 \mu s + Tc + [(Temp - 25°C)(0.05 \mu s/°C)]

Tc = -CHOLD (Ric + Rss + Rs) \ln(1/2047)

-120 pF (1 kΩ + 7 kΩ + 10 kΩ) \ln(0.0004885)

-120 pF (18 kΩ) \ln(0.0004885)

-2.16 \mu s (-7.6241)

16.47 \mu s

Tacq = 2 \mu s + 16.47 \mu s + [(50°C - 25°C)(0.05 \mu s/°C)]

18.47 \mu s + 1.25 \mu s

19.72 \mu s

```

Now to get an idea what happens to the acquisition time when the source impedance is a minimal value ( $Rs = 50 \Omega$ ). Example 23-2 shows the same conditions as in Example 23-1 with only the source impedance made a minimal value ( $Rs = 50 \Omega$ ).

Example 23-2: Calculating the Minimum Required Acquisition Time (Case 2)

Tacq = Tamp + Tc + Tcoff

Temperature coefficient is only required for temperatures > 25°C.

Tacq =  $2 \mu s + Tc + [(Temp - 25°C)(0.05 \mu s/°C)]$ Tc = -Chold (Ric + Rss + Rs) ln(1/2047)

-120 pF (1 kΩ + 7 kΩ + 50 Ω) ln(0.0004885)

-120 pF (8050 Ω) ln(0.0004885)

-0.966 μs (-7.6241)

7.36 μs

Tacq =  $2 \mu s + 16.47 \mu s + [(50°C - 25°C)(0.05 \mu s/°C)]$ 9.36 μs + 1.25 μs

10.61 μs

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself

- Note 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **Note 3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **Note 4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

Figure 23-3: Analog Input Model

### 23.5 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11.5TAD per 10-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- · Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6 µs as shown in parameter 130 of the "Electrical Specifications" section.

Table 23-1 show the resultant TAD times derived from the device operating frequencies and the A/D clock source selected. These times are for standard voltage range devices.

Table 23-1: TAD vs. Device Operating Frequencies (for Standard, C, Devices)

| AD Clock S | Source (TAD) | Device Frequency          |                           |                           |                         |  |  |

|------------|--------------|---------------------------|---------------------------|---------------------------|-------------------------|--|--|

| Operation  | ADCS1:ADCS0  | 20 MHz                    | 5 MHz                     | 1.25 MHz                  | 333.33 kHz              |  |  |

| 2Tosc      | 00           | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6 μs                    |  |  |

| 8Tosc      | 01           | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>    |  |  |

| 32Tosc     | 10           | 1.6 μs                    | 6.4 μs                    | 25.6 μs <sup>(3)</sup>    | 96 μs <sup>(3)</sup>    |  |  |

| RC         | 11           | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

- Note 1: The RC source has a typical TAD time of 4 µs.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: For device frequencies above 1 MHz, the device must be in SLEEP for the entire conversion, or the A/D accuracy may be out of specification.

Table 23-2: TAD vs. Device Operating Frequencies (for Extended, LC, Devices)

| AD Clock S | ource (TAD) | Device Frequency          |                           |                           |                           |  |

|------------|-------------|---------------------------|---------------------------|---------------------------|---------------------------|--|

| Operation  | ADCS1:ADCS0 | 4 MHz                     | 2 MHz                     | 1.25 MHz                  | 333.33 kHz                |  |

| 2Tosc      | 00          | 500 ns <sup>(2)</sup>     | 1.0 μs <sup>(2)</sup>     | 1.6 μs <sup>(2)</sup>     | 6 μs                      |  |

| 8Tosc      | 01          | 2.0 μs <sup>(2)</sup>     | 4.0 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>      |  |

| 32Tosc     | 10          | 8.0 μs                    | 16.0 μs                   | 25.6 μs <sup>(3)</sup>    | 96 μs <sup>(3)</sup>      |  |

| RC         | 11          | 3 - 9 μs <sup>(1,4)</sup> |  |

Legend: Shaded cells are outside of recommended range.

- Note 1: The RC source has a typical TAD time of 6 µs.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: For device frequencies above 1 MHz, the device must be in SLEEP for the entire conversion, or the A/D accuracy may be out of specification.

### 23.6 Configuring Analog Port Pins

The ADCON1 and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- **Note 1:** When reading the port register, any pin configured as an analog input channel will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- **Note 2:** Analog levels on any pin that is defined as a digital input (including the AN7:AN0 pins), may cause the input buffer to consume current that is out of the devices specification.

#### 23.7 A/D Conversions

Example 23-3 shows how to perform an A/D conversion for the PIC17C756. The PORTF and lower four PORTG pins are configured as analog inputs. The analog references (VREF+ and VREF-) are the device AVDD and AVSs. The A/D interrupt is enabled, and the A/D conversion clock is FRC. The conversion is performed on the ANO pin (channel 0).

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D, due to the required acquisition time requirement.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, acquisition on the selected channel is automatically started.

#### Example 23-3: A/D Conversion

```

STATUS, RPO ; Select Bank1

BSF

CLRF

ADCON1

; Configure A/D inputs,

result is left justified

PIE1, ADIE

BSF

; Enable A/D interrupts

STATUS, RP0

BCF

; Select BankO

; RC Clock, A/D is on, Channel 0 is selected

0xC1

MOVLW

MOVWF

ADCON0

BCF

PIR1, ADIF

; Clear A/D interrupt flag bit

BSF

INTCON, PEIE ; Enable peripheral interrupts

INTCON, GIE

; Enable all interrupts

BSF

Ensure that the required sampling time for the selected input

channel has elapsed. Then the conversion may be started.

; Start A/D Conversion

BSF

ADCON0, GO

; The ADIF bit will be set and the GO/DONE

; bit is cleared upon completion of the

A/D Conversion.

```

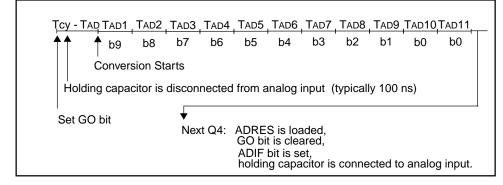

#### Figure 23-4: A/D Conversion TAD Cycles

Wait 2TAD

#### 23.7.1 Faster Conversion - Lower Resolution Trade-off

Not all applications require a result with 10-bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the trade-off of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the clock source of the A/D module may be switched so that the TAD time violates the minimum specified time (see the applicable electrical specification). Once the TAD time violates the minimum specified time, all the following A/D result bits are not valid (see A/D Conversion Timing in the Electrical Specifications section). The clock sources may only be switched between the three oscillator versions (cannot be switched from/to RC). The equation to determine the time before the oscillator can be switched is as follows:

Conversion time =  $TAD + N \cdot TAD + (11 - N)(2TOSC)$ Where: N = number of bits of resolution required.

Since the TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D oscillator may be changed. Example 23-4 shows a comparison of time required for a conversion with 4-bits of resolution, versus the 10-bit resolution conversion. The example is for devices operating at 20 MHz (The A/D clock is programmed for 32Tosc), and assumes that immediately after 6TAD, the A/D clock is programmed for 2Tosc.

The 2Tosc violates the minimum TAD time since the last 4 bits will not be converted to correct values.

Example 23-4: 4-bit vs. 8-bit Conversion Times

|                                  | Freq.                         | Resolution |         |  |

|----------------------------------|-------------------------------|------------|---------|--|

|                                  | Freq.<br>(MHz) <sup>(1)</sup> | 4-bit      | 10-bit  |  |

| TAD                              | 20                            | 1.6 μs     | 1.6 μs  |  |

| Tosc                             | 20                            | 50 ns      | 50 ns   |  |

| 2TAD + N • TAD + (11 - N)(2TOSC) | 20                            | 8.7 μs     | 17.6 μs |  |

Note 1: A minimum TAD time of 1.6 µs is required.

2: If the full 8-bit conversion is required, the A/D clock source should not be changed.

### 23.7.2 A/D Result Registers

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16-bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 23-6 shows the operation of the A/D result justification. The extra bits are loaded with '0's'. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

### 23.8 Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all internal digital switching noise from the conversion. When the conversion is completed the GO/DONE bit will be cleared, and the result is loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off (to conserve power), though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To allow the conversion to occur during SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

### 23.9 Effects of a Reset

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

### 23.10 A/D Accuracy/Error

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator.

The absolute accuracy specified for the A/D converter includes the sum of all contributions for quantization error, integral error, differential error, full scale error, offset error, and monotonicity. It is defined as the maximum deviation from an actual transition versus an ideal transition for any code. The absolute error of the A/D converter is specified at  $< \pm 1$  LSb for VDD = VREF (over the device's specified operating range). However, the accuracy of the A/D converter will degrade as VDD diverges from VREF.

For a given range of analog inputs, the output digital code will be the same. This is due to the quantization of the analog input to a digital code. Quantization error is typically  $\pm$  1/2 LSb and is inherent in the analog to digital conversion process. The only way to reduce quantization error is to increase the resolution of the A/D converter.

Offset error measures the first actual transition of a code versus the first ideal transition of a code. Offset error shifts the entire transfer function. Offset error can be calibrated out of a system or introduced into a system through the interaction of the total leakage current and source impedance at the analog input.

Gain error measures the maximum deviation of the last actual transition and the last ideal transition adjusted for offset error. This error appears as a change in slope of the transfer function. The difference in gain error to full scale error is that full scale does not take offset error into account. Gain error can be calibrated out in software.

Linearity error refers to the uniformity of the code changes. Linearity errors cannot be calibrated out of the system. Integral non-linearity error measures the actual code transition versus the ideal code transition adjusted by the gain error for each code.

Differential non-linearity measures the maximum actual code width versus the ideal code width. This measure is unadjusted.

The maximum pin leakage current is specified in the Device Data Sheet electrical specification parameter D060.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be minimized to reduce inaccuracies due to noise and sampling capacitor bleed off.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

#### 23.11 Connection Considerations

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.3V, then the accuracy of the conversion is out of specification.

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

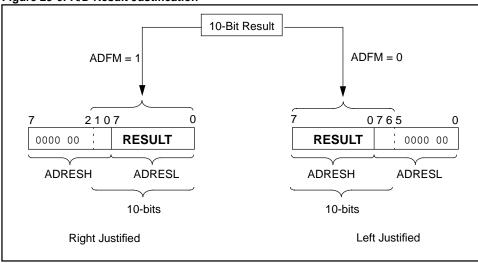

## 23.12 Transfer Function

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the analog input voltage (VAIN) is 1 LSb (or Analog VREF / 1024) (Figure 23-7).

#### 23.13 Initialization

Example 23-5 shows an initialization of the A/D module.

#### Example 23-5: A/D Initialization

```

BSF

STATUS, RP0

; Select Bankl

CLRF

ADCON1

; Configure A/D inputs

; Configure A/D inputs

; Enable A/D interrupts

; Select Bank0

BSF

PIE1, ADIE

BCF

STATUS, RPO

; Select Bank0

MOVLW

0xC1

; RC Clock, A/D is on, Channel 0 is selected

MOVWF

ADCON0

PIR1, ADIF

; Clear A/D interrupt flag bit

BCF

INTCON, PEIE ; Enable peripheral interrupts

BSF

INTCON, GIE

; Enable all interrupts

; Ensure that the required sampling time for the selected input

channel has elapsed. Then the conversion may be started.

BSF

ADCON0, GO

; Start A/D Conversion

; The ADIF bit will be set and the GO/DONE

:

; bit is cleared upon completion of the

A/D Conversion.

```

### 23.14 Design Tips

Question 1: I find that the Analog to Digital Converter result is not always accurate.

What can I do to improve accuracy?

#### Answer 1:

- 1. Make sure you are meeting all of the timing specifications. If you are turning the module off and on, there is a minimum delay you must wait before taking a sample. If you are changing input channels, there is a minimum delay you must wait for this as well, and finally there is TAD, which is the time selected for each bit conversion. This is selected in ADCON0 and should be between 1.6 and 6 μs. If TAD is too short, the result may not be fully converted before the conversion is terminated, and if TAD is made too long the voltage on the sampling capacitor can droop before the conversion is complete. These timing specifications are provided in the "Electrical Specifications" section. See the device data sheet for device specific information.

- 2. Often the source impedance of the analog signal is high (greater than 1k ohms) so the current drawn from the source to charge the sample capacitor can affect accuracy. If the input signal does not change too quickly, try putting a  $0.1\,\mu\text{F}$  capacitor on the analog input. This capacitor will charge to the analog voltage being sampled and supply the instantaneous current needed to charge the 120 pF internal holding capacitor.

- 3. Finally, straight from the data book: "In systems where the device frequency is low, use of the A/D clock derived from the device oscillator is preferred...this reduces, to a large extent, the effects of digital switching noise." and "In systems where the device will enter SLEEP mode after start of A/D conversion, the RC clock source selection is required. This method gives the highest accuracy."

# Question 2: After starting an A/D conversion may I change the input channel (for my next conversion)?

#### Answer 2:

After the holding capacitor is disconnected from the input channel, typically 100 ns after the GO bit is set, the input channel may be changed.

#### Question 3: Do you know of a good reference on A/D's?

### Answer 3:

A very good reference for understanding A/D conversions is the "Analog-Digital Conversion Handbook" third edition, published by Prentice Hall (ISBN 0-13-03-2848-0).

## 23.15 Related Application Notes

This section lists application notes that are related to this section of the manual. These application notes may not be written specifically for the Mid-Range MCU family (that is they may be written for the Base-Line, or High-End families), but the concepts are pertinent, and could be used (with modification and possible limitations). The current application notes related to the 10-bit A/D module are:

Title Application Note #

Using the Analog to Digital Converter AN546

Four Channel Digital Voltmeter with Display and Keyboard AN557

## 23.16 Revision History

**Revision A**

This is the initial released revision of the 10-bit A/D module description.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Microchip:

PIC16C71-20/P PIC16F630-E/ML PIC16F630-I/ML PIC16F630T-I/ML PIC16F72-E/ML PIC16F747-E/ML PIC16F747-E/ML PIC16F747-E/ML PIC16F747-E/SP PIC16F747-E/PT PIC16F76-E/ML PIC16F767-E/SD PIC16F767-E/SP PIC16F767-E/SS PIC16F819-I/MLTSL PIC16F819-I/PTSL PIC16F819-I/SOTSL PIC16F819T-I/SOTSL PIC16F819T-I/SOTSL